(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6702646号

(P6702646)

(45) 発行日 令和2年6月3日(2020.6.3)

(24) 登録日 令和2年5月11日(2020.5.11)

(51) Int.CI.

HO3K 17/687 (2006.01)

F 1

HO3K 17/687

G

請求項の数 23 (全 17 頁)

|                    |                               |

|--------------------|-------------------------------|

| (21) 出願番号          | 特願2014-20289 (P2014-20289)    |

| (22) 出願日           | 平成26年2月5日(2014.2.5)           |

| (65) 公開番号          | 特開2014-155227 (P2014-155227A) |

| (43) 公開日           | 平成26年8月25日(2014.8.25)         |

| 審査請求日              | 平成29年2月3日(2017.2.3)           |

| 審判番号               | 不服2018-11958 (P2018-11958/J1) |

| 審判請求日              | 平成30年9月6日(2018.9.6)           |

| (31) 優先権主張番号       | 13/764,655                    |

| (32) 優先日           | 平成25年2月11日(2013.2.11)         |

| (33) 優先権主張国・地域又は機関 | 米国(US)                        |

|           |                                                                                                                                                                      |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 599034594<br>コーポ ユース、インコーポレイテッド<br>アメリカ合衆国オレゴン州97124・ヒ<br>ルスボロ・ノースイーストブルックウッド<br>パークウェイ 2300<br>2300 NE Brookwood P<br>arkway, Hillsboro, Or<br>egon 97124, U. S. A. |

| (74) 代理人  | 100105924<br>弁理士 森下 賢樹                                                                                                                                               |

| (72) 発明者  | クラウセン、ウィリアム ジェイ.<br>アメリカ合衆国オレゴン州97124・ヒ<br>ルスボロ・ノースイーストブルックウッド<br>パークウェイ 2300                                                                                        |

最終頁に続く

(54) 【発明の名称】ボディバイアスされたスイッチ装置

## (57) 【特許請求の範囲】

## 【請求項 1】

無線周波数(RF)信号をスイッチするように構成される回路であって、ソース端子、ゲート端子、ドレイン端子およびボディ端子を含む電界効果トランジスタ(FET)と、

前記ソース端子、前記ドレイン端子および前記ボディ端子に接続されるボディバイアス回路と、を備え、

前記ボディバイアス回路は、前記ソース端子と前記ボディ端子の間に接続される第1回路要素と、前記ドレイン端子と前記ボディ端子の間に接続される第2回路要素とを有し、

前記第1回路要素および前記第2回路要素は、前記FETに印加されるRF信号に基づく負のバイアス電圧を前記第1回路要素および前記第2回路要素を通じて引き出し、前記FETがオフ状態のときに前記負のバイアス電圧を前記ボディ端子に供給するように構成される、回路。

## 【請求項 2】

前記FETを含み、互いに直列接続される複数のFETをさらに備える、請求項1に記載の回路。

## 【請求項 3】

前記FETは、n型FETである、請求項1または2に記載の回路。

## 【請求項 4】

前記ボディバイアス回路は、前記ソース端子、前記ドレイン端子および前記ボディ端子

10

20

のみに接続される、請求項 1 から 3 のいずれか一項に記載の回路。

**【請求項 5】**

前記回路は、シリコン - オン - インシュレータ ( S O I ) 回路を構成する、請求項 1 から 4 のいずれか一項に記載の回路。

**【請求項 6】**

前記 F E T は、第 1 F E T であり、

前記ボディバイアス回路は、前記ボディ端子に接続されるノードを備え、

前記第 1 回路要素は、前記第 1 F E T のソース端子に接続されるソース端子および前記ノードに接続されるドレイン端子を有する第 2 F E T を含み、

前記第 2 回路要素は、前記ノードに接続されるドレイン端子および前記第 1 F E T のドレイン端子に接続されるソース端子を有する第 3 F E T を含む、請求項 1 から 5 のいずれか一項に記載の回路。 10

**【請求項 7】**

前記第 2 F E T は、前記第 1 F E T のドレイン端子に接続されるゲート端子をさらに含み、

前記第 3 F E T は、前記第 1 F E T のソース端子に接続されるゲート端子をさらに含む、請求項 6 に記載の回路。

**【請求項 8】**

前記第 2 F E T および前記第 3 F E T は、ダイオード接続 F E T であり、

前記第 2 F E T は、前記ノードに接続されるゲート端子をさらに含み、

前記第 3 F E T は、前記ノードに接続されるゲート端子をさらに含む、請求項 6 に記載の回路。 20

**【請求項 9】**

前記ボディバイアス回路は、前記ボディ端子に接続されるノードを備え、

前記第 1 回路要素は、前記ソース端子および前記ノードに接続される第 1 ダイオードを含み、

前記第 2 回路要素は、前記ドレイン端子および前記ノードに接続される第 2 ダイオードを含む、請求項 1 から 5 のいずれか一項に記載の回路。 30

**【請求項 10】**

前記第 1 ダイオードは、前記ソース端子に接続されるカソード端子および前記ノードに接続されるアノード端子を含み、

前記第 2 ダイオードは、前記ドレイン端子に接続されるカソード端子および前記ノードに接続されるアノード端子を含む、請求項 9 に記載の回路。 30

**【請求項 11】**

前記ボディバイアス回路は、R F 信号を整流するように構成されることにより、前記負のバイアス電圧を引き出すよう構成される、請求項 1 から 10 のいずれか一項に記載の回路。

**【請求項 12】**

送受信機と、

アンテナと、

前記送受信機および前記アンテナに接続され、前記送受信機と前記アンテナとの間の信号を通信するように構成される無線周波数 ( R F ) フロントエンドと、を備え、

前記 R F フロントエンドは、シリコン - オン - インシュレータのスイッチ装置を含み、

前記スイッチ装置は、複数のスイッチ電界効果トランジスタ ( F E T S ) をオン状態またはオフ状態に設定するよう構成されるデコーダと、前記複数のスイッチ F E T S からなる F E T およびボディバイアス回路を持つセルと、を有し、

前記ボディバイアス回路は、前記 F E T がオフ状態のときに前記 F E T のボディに負の電圧を供給する第 1 回路要素および第 2 回路要素を含み、前記負の電圧は、前記 F E T に印加される R F 信号から前記第 1 回路要素および前記第 2 回路要素を通じて引き出される、無線通信装置。 50

**【請求項 1 3】**

前記 F E T は、第 1 F E T であり、

前記ボディバイアス回路は、前記第 1 F E T のボディ端子に接続されるノードを備え、

前記第 1 回路要素は、前記第 1 F E T のソース端子に接続されるソース端子および前記ノードに接続されるドレイン端子を有する第 2 F E T を含み、

前記第 2 回路要素は、前記ノードに接続される前記ドレイン端子および前記第 1 F E T のドレイン端子に接続されるソース端子を有する第 3 F E T を含む、請求項 1 2 に記載の無線通信装置。

**【請求項 1 4】**

前記第 2 F E T は、前記第 1 F E T のドレイン端子に接続されるゲート端子をさらに含み、

前記第 3 F E T は、前記第 1 F E T のソース端子に接続されるゲート端子をさらに含む、請求項 1 3 に記載の無線通信装置。

**【請求項 1 5】**

デコーダ回路を用いて、スイッチ電界効果トランジスタ (F E T) をオフ状態に制御し、

ボディバイアス回路を用いて、前記スイッチ F E T がオフ状態の間に、前記スイッチ F E T に印加される無線周波数 (R F) 信号に基づく負のバイアス電圧を前記ボディバイアス回路の第 1 回路要素および第 2 回路要素を通じて引き出し、

前記ボディバイアス回路によって、前記スイッチ F E T がオフ状態の間に、前記負のバイアス電圧を前記スイッチ F E T のボディに供給する、方法。

**【請求項 1 6】**

前記スイッチ F E T に印加される R F 信号を整流し、前記負のバイアス電圧を引き出す、請求項 1 5 に記載の方法。

**【請求項 1 7】**

無線周波数 (R F) 信号をスイッチするように構成される回路であって、

ソース端子、ゲート端子、ドレイン端子およびボディ端子を含む電界効果トランジスタ (F E T) と、

前記ボディ端子に接続されるノードと、前記ドレイン端子および前記ノードに接続される第 1 抵抗と、前記ソース端子および前記ノードに接続される第 2 抵抗と、を有するボディバイアス回路と、を備え、

前記ボディバイアス回路は、前記 F E T に印加される R F 信号に基づくバイアス電圧を前記第 1 抵抗および前記第 2 抵抗を通じて引き出し、前記バイアス電圧を前記ボディ端子に供給するように構成される、回路。

**【請求項 1 8】**

前記第 1 抵抗および前記第 2 抵抗は、同じ大きさである、請求項 1 7 に記載の回路。

**【請求項 1 9】**

前記ボディバイアス回路は、前記バイアス電圧を約 0 V の直流電圧として供給するよう構成される、請求項 1 7 または 1 8 に記載の回路。

**【請求項 2 0】**

前記 F E T の前記ゲート端子はデコーダに接続され、前記 F E T の前記ボディ端子は前記デコーダに接続されない、請求項 1 7 から 1 9 のいずれか一項に記載の回路。

**【請求項 2 1】**

前記ボディバイアス回路は、前記 F E T がオン状態のときに前記ボディ端子を浮遊させることにより前記ボディ端子に約 0 V の D C 電圧を供給するようにさらに構成される、請求項 1 から 1 1 のいずれか一項に記載の回路。

**【請求項 2 2】**

前記ボディバイアス回路は、前記 F E T がオン状態のときに前記 F E T のボディ端子を浮遊させることにより前記ボディ端子に約 0 V の D C 電圧を供給するようにさらに構成される、請求項 1 2 から 1 4 のいずれか一項に記載の無線通信装置回路。

10

20

30

40

50

**【請求項 2 3】**

前記ボディバイアス回路によって、前記スイッチFETがオン状態のときに前記ボディを浮遊させることにより前記ボディに約0VのDC電圧を供給する、請求項15または16に記載の方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本開示の実施の形態は、広くは回路の分野に関し、特に電界効果トランジスタ(FET)を利用したボディバイアスされたスイッチ装置に関する。

**【背景技術】**

10

**【0002】**

シリコン-オン-インシュレータ(SOI)のスイッチ装置において、オフモード動作におけるフローティングボディ効果を緩和するため、負のボディバイアス接続が用いられる。本設計では、負の電圧をボディへ直接的に供給するチャージポンプの使用を求める。この回路要素は、基板のノイズ結合、デコーダ回路への多くの制御線、無線周波数(RF)スイッチコアに侵入する不要な信号(利用可能なルーティング経路の制約による)および大型のダイサイズに関連しうる設計を用いるものであった。

**【発明の概要】****【発明が解決しようとする課題】**

20

**【0003】**

本発明はこうした状況に鑑みてなされたものであり、その目的とするところは、ボディバイアスされたスイッチ装置を提供することにある。

**【課題を解決するための手段】****【0004】**

本発明のある態様の回路は、無線周波数(RF)信号をスイッチするように構成される回路であって、ソース端子、ゲート端子、ドレイン端子およびボディ端子を含む電界効果トランジスタ(FET)と、ソース端子、ドレイン端子およびボディ端子に接続されるボディバイアス回路と、を備える。ボディバイアス回路は、FETに印加されるRF信号に基づく負のバイアス電圧を引き出し、FETがオフ状態のときに負のバイアス電圧をボディ端子に供給するように構成される。

30

**【0005】**

本発明の別の態様は、無線通信装置である。この装置は、送受信機と、アンテナと、送受信機およびアンテナに接続され、送受信機とアンテナとの間の信号を通信するように構成される無線周波数(RF)フロントエンドと、を備える。無線周波数フロントエンドは、シリコン-オン-インシュレータのスイッチ装置を含む。スイッチ装置は、複数のスイッチ電界効果トランジスタ(FET)をオン状態またはオフ状態に設定するよう構成されるデコーダと、複数のFETからなる電界効果トランジスタ(FET)およびボディバイアス回路を持つセルと、を有する。ボディバイアス回路は、FETがオフ状態のときに電界効果トランジスタのボディに負の電圧を供給するように構成され、当該負の電圧は、FETに印加されるRF信号から引き出される。

40

**【0006】**

本発明のさらに別の態様は、方法である。この方法は、デコーダ回路を用いて、スイッチ電界効果トランジスタ(FET)をオフ状態に制御し、ボディバイアス回路を用いて、スイッチFETがオフ状態の間に、スイッチFETに印加される無線周波数(RF)信号に基づく負のバイアス電圧を引き出し、ボディバイアス回路によって、スイッチFETがオフ状態の間に、負のバイアス電圧をスイッチFETのボディに供給する。

**【0007】**

本発明のさらに別の態様は、回路である。この回路は、無線周波数(RF)信号をスイッチするように構成される回路であって、ソース端子、ゲート端子、ドレイン端子およびボディ端子を含む電界効果トランジスタ(FET)と、ボディ端子に接続されるノードと

50

、ドレン端子およびノードに接続される第1抵抗と、ソース端子およびノードに接続される第2抵抗と、を有するボディバイアス回路と、を備える。ボディバイアス回路は、FETに印加されるRF信号に基づくバイアス電圧を引き出し、バイアス電圧をボディ端子に供給するように構成される。

**【図面の簡単な説明】**

**【0008】**

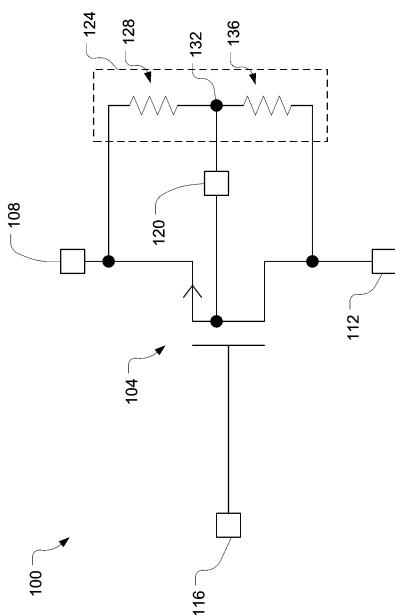

【図1】いくつかの実施の形態に係る単位セルを示す図である。

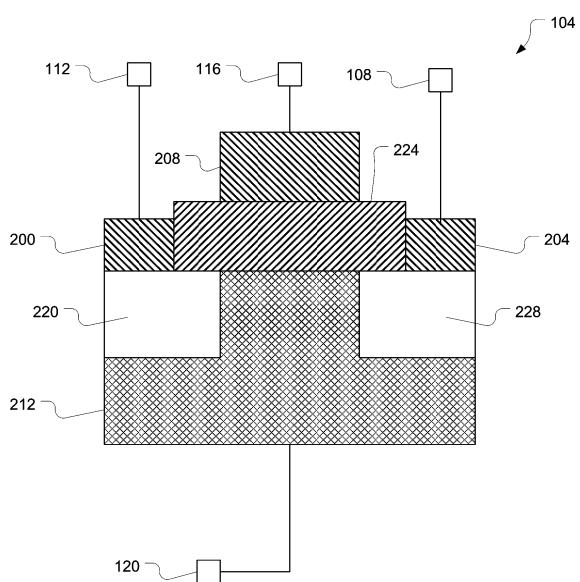

【図2】いくつかの実施の形態に係るスイッチトランジスタの構成を示す図である。

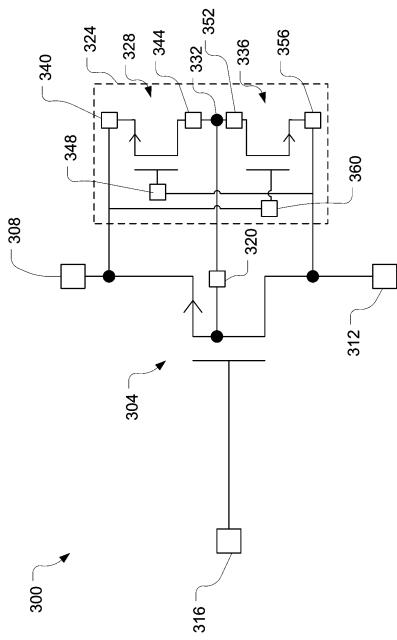

【図3】いくつかの実施の形態に係る単位セルを示す図である。

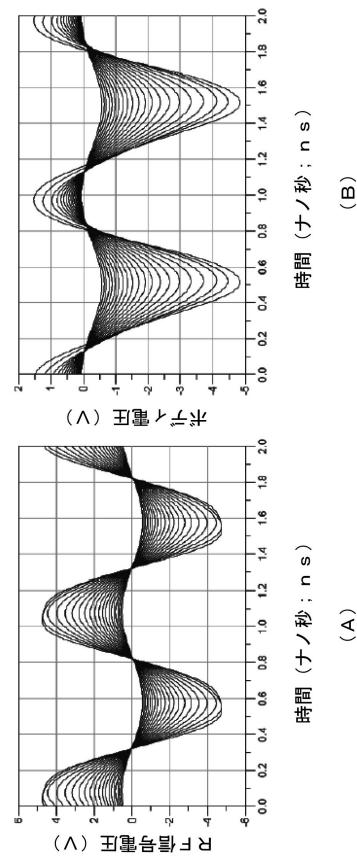

【図4】図4(a)及び図4(b)は、いくつかの実施の形態に係る電圧の時間変化を示すグラフである。10

【図5】他の実施の形態に係る単位セルを示す図である。

【図6】他の実施の形態に係る単位セルを示す図である。

【図7】いくつかの実施の形態に係る動作方法を示すフローチャートである。

【図8】いくつかの実施の形態に係るスイッチ装置を示す図である。

【図9】いくつかの実施の形態に係る無線通信装置を示す図である。

**【発明を実施するための形態】**

**【0009】**

実施の形態は、例示を目的とし、添付図面の形態に限定されないことを目的として、図示される。図面において、同種の符号は、同様な構成要素を示す。20

**【0010】**

例示される実施の形態に係る様々な態様は、当業者にとって一般的に採用される用語を用いて他の当業者に本発明の本質を伝えるために示される。しかしながら、以下に示されるいくつかの要素のみを用いて代替的な実施の形態を実施しうることは、当業者にとって明らかであろう。説明のために、特定の装置または構成は、例示される実施の形態の詳細な理解を与えるために示される。しかし、代替的な実施の形態は具体的な細部を省いて実施しうることは当業者にとって明らかであろう。他の例では、例示される実施の形態を不明確としないために、周知な特徴は除外され、もしくは単純化される。

**【0011】**

さらに、様々な動作は、複数の個別の動作として本開示の理解を最も助ける形で順に示される。しかしながら、記載の順序は、これらの動作が必ずしも順序依存であることを示すものであるとして解釈されるべきはない。特に、これらの動作は、説明される順序で実行される必要はない。30

**【0012】**

「一つの実施の形態において」の語は、繰り返し用いられる。この語は、ほとんどの場合において、同じ実施の形態を参照するものではないが、同じ実施の形態を参照することもある。「備える」、「有する」および「含む」の語は、文脈において別に規定されない限り、同義語である。

**【0013】**

「～と接続される」の語は、ここでは、派生的に用いられる。「接続される」は、以下に示す一以上の意味で用いられる。「接続される」は、二以上の要素が物理的または電気的に直接接触することを意味しうる。しかしながら、「接続される」は、二以上の要素が互いに間接的に接触しつつ互いに協働または相互作用することも意味し、また、一以上の他の要素が、上述の意味で互いに接続された要素間において結合または接続されることを意味しうる。40

**【0014】**

実施の形態は、スイッチ装置で用いられ、電界効果トランジスタ(FET)を含む回路を含んでもよい。FETは、それぞれに接続される個別の端子を有する、ボディ、ソース、ドレンおよびゲートを備えてもよい。スイッチ装置は、シリコン・オン・インシュレータ(SOI)のスイッチ装置であってもよい。また回路は、対となる回路素子を含み、50

FETに印加される無線周波数(RF)信号に基づくバイアス電圧を引き出して、FETがオフのときにFETのボディ端子にバイアス電圧を供給するように構成される、ボディバイアス回路を含んでもよい。いくつかの実施の形態において、引き出されたバイアス電圧は、負のバイアス電圧であってもよい。種々の実施の形態は、図面を参照しながら、以下に詳細に説明される。

#### 【0015】

図1は、種々の実施の形態に係る回路100を示す。回路100は、単位セル100または単純にセル100と呼んでもよい。セル100は、FET104を含んでもよく、また、FET104は、スイッチFET104と呼んでもよい。FET104は、たいていの場合に示されるように、n型の電界効果トランジスタ(n型FET)でもよい。FET104は、符号とともに後述する図2に示されるFETのソース、ドレイン、ゲートおよびボディにそれぞれ接続される、ソース端子108、ドレイン端子112、ゲート端子116およびボディ端子120を含んでもよい。

10

#### 【0016】

セル100は、さらにボディバイアス回路124を含んでもよい。ボディバイアス回路124は、FET104のソース端子108、ドレイン端子112およびボディ端子120に接続されてもよい。ボディバイアス回路124は、後に詳述するように、適切なバイアス電圧をFET104のベースに供給するために用いられてもよい。種々の実施の形態において、ボディバイアス回路124は、FET104の三つの端子にのみ接続される。言い換えれば、ボディバイアス回路124に接続されるべき外部接続または制御線は必要としない。

20

#### 【0017】

ボディバイアス回路124は、第1抵抗128、ノード132および第2抵抗136を含んでもよい。第1抵抗128は、ソース端子108およびノード132の間に接続されてもよい。第2抵抗136は、ドレイン端子112およびノード132の間に接続されてもよい。ノード132は、ボディ端子120に接続されてもよい。第1抵抗128および第2抵抗136は、同じ大きさであってもよい。

#### 【0018】

FET104は、エンハンスマードまたはデプレッションモードのFETであってもよい。いくつかの実施の形態において、FET104は、金属酸化物半導体FET(MOSFET)であってもよく、他の実施の形態では、FET104は、絶縁ゲート型FET(IGFET)、または金属絶縁体半導体FET(MISFET)としてもよい。

30

#### 【0019】

種々の実施の形態は、FET104のボディ電圧のバイアスに用いられるボディバイアス構造を提供する。このバイアス構造は、ここでは、n型FETを参照しながら説明される。しかしながら、他の実施の形態において、このバイアス構造は、p型FETのような別の種類のFETに用いることとしてもよい。

#### 【0020】

種々の実施の形態において、FET104は、以後、無線周波数(RF)信号と呼ぶ伝送信号の切り替えを可能とするため、オフ状態とオン状態との間を選択的に遷移してもよい。たとえば、FET104は、FET104がオン状態であればソース端子108とドレイン端子112との間でRF信号を通過させてもよい。また、FET104は、FET104がオフ状態であれば、ドレイン端子112とソース端子108との間のRF信号の通過を妨げてもよい。

40

#### 【0021】

FET104は、ゲート端子116において、FET104をオフ状態とオン状態との間で遷移させるための制御信号を受信してもよい。たとえば、ドレイン端子112およびソース端子108の直流電圧に対応し、ゲートソース間電圧とも呼ばれる、+2.5Vの直流電圧をゲート端子116に印加してもよい。いくつかの実施の形態では、この電圧は、デコーダ(図1に図示せず)により印加されてもよい。この+2.5Vの電圧は、ドレ

50

イン端子 112 およびソース端子 108 の間の抵抗を極めて小さくし、その結果、R F 信号がドレン端子 112 およびソース端子 108 の間を通過できるようにすることで、F E T 104 をオン状態とする効果を有してもよい。

#### 【0022】

正のゲート - ソース間電圧を印加することで、R F 信号が F E T 104 を通過できるようにもよい。なぜなら、F E T 104 は、S O I スイッチ装置に含まれる場合、図2 に示される要素を一般に備えてもよいためである。F E T 104 は、ドレン端子 112 に接続されるドレン 200 と、ソース端子 108 に接続されるソース 204 と、ゲート端子 116 に接続されるゲート 208 と、より構成されてもよい。実施の形態において、ドレン 200、ソース 204 およびゲート 208 は、例えば、アルミニウムまたは銅などの金属または導電性材料により全て構成されてもよい。実施の形態において、ドレン 200、ソース 204 およびゲート 208 は、同じ材料または異なる材料により構成されてもよい。10

#### 【0023】

F E T 104 は、さらに、ボディ端子 120 に接続されるボディ 212 を備えてもよい。F E T 104 は、詳細を後述するように、さらに、ドレン 200 およびボディ 212 の間に設けられるn型ドレン部 220 と、ソース 204 およびボディ 212 の間に設けられるn型ソース部 228 を備えてもよい。

#### 【0024】

ここで、端子は、回路において他の要素に接続されるF E T 104 の要素の一つである。いくつかの実施の形態において、ドレン 200 およびドレン端子 112 は、同じ要素であると考えてもよく、例えば、F E T 104 は、ドレン 200 と回路内の要素との間の直接接続を通じて、回路内の別の要素と接続してもよい。他の実施の形態においては、ドレン端子 112 は、例えば、導電性のリード線など、電気的にドレン 200 に接続される端子であってもよい。例えば、これらの他の実施の形態において、F E T 104 は、ドレン端子 112 を通じて回路内の別の要素と接続してもよい。このとき、ドレン端子 112 は、銅などの金属のリード線や他の導電性のリード線であってもよく、これらのリード線はドレン 200 と接続されてもよい。同様に、ソース 204 およびソース端子 108 は、ドレン 200 およびドレン端子 112 に関して上述したように、互いに同一であってもよいし、または、互いに電気的に接続されてもよい。同様に、ゲート 208 およびゲート端子 116 は、互いに同一であってもよいし、または、互いに電気的に接続されてもよい。最後に、ボディ 212 およびボディ端子 120 は、互いに同一であってもよいし、または、互いに接続されていてもよい。ここで、各要素に与えられる名称は、F E T 104 の一つの要素を別の要素から識別するためのものであり、異なる実施の形態では異なる名称を用いるかもしれない。例えば、F E T 104 において、n型ドレン部 220 を「ドレン」と呼び、n型ソース部 228 を「ソース」と呼ぶかもしれない。2030

#### 【0025】

F E T 104 を用いる例として、直流電圧は、ゲート端子 116 に印加されるものとして説明され、同時に、ゲート端子 116 によりゲート 208 が特定の電圧を得ることとなる。しかしながら、いくつかの実施の形態において、この直流電圧は、ゲート 208 に直接的に印加されうる。他の例として、R F 信号は、ソース 204 またはソース端子 108 ( または、ドレン 200 またはドレン端子 112 ) において受信されてもよく、F E T 104 がオン状態のときには、F E T 104 を通って、ドレン 200 またはドレン端子 112 ( または、ソース 204 またはソース端子 108 ) へ通過してもよい。40

#### 【0026】

ボディ 212 は、p型材料、例えば、シリコンやゲルマニウムなどのI V族元素に、ホウ素やアルミニウムなどのI I I族元素をドープしたもので構成されてもよい。n型のドレン部 220 およびソース部 228 は、シリコンやゲルマニウムなどのI V族元素に、ヒ素やリンなどのV属元素をドープしたもので構成されてもよい。n型のドレン部 220 およびソース部 228 は、ボディ 212 により互いに分離されてもよい。一般に、p型50

材料は、電子が欠乏し、電子ホールを有すると言われる。n型材料は、n型材料の内外にて電流として移動することのできる余分な電子を有し、その結果、可動電子を有するといわれる。

#### 【0027】

上述したように、FET104のゲート208は、銅やアルミニウムなどの導電性の金属で構成されてもよい。他の実施の形態において、ゲート208は、タンタル、タングステン、窒化タンタルより構成されてもよい。他の実施の形態において、FET104のゲート208は、ポリシリコン材料で構成されてもよい。ドレイン200、ソース204、ゲート208およびボディ212は全て、誘電体224により互いに分離されてもよい。誘電体224は、例えば、二酸化シリコン、酸化窒化シリコン、または、ドレイン200およびソース204の間の電子の流れを妨げることのできる、その他の高誘電率(High-k)の誘電材料などである。10

#### 【0028】

FET104をオンにするため、ゲート208とFET104のその他の部分との間に静電界が形成されてもよい。これは、例えば、2.5Vなどの正の電圧をゲート208に印加するデコーダによりなされてもよい。ドレイン200およびソース204は、例えば、0Vの直流バイアス電圧を有してもよい。ボディ212は、浮遊(float)してもよく、その結果、FET104を通って送信されるRF信号により与えられる低変調のパワーレベルを有する約0Vの直流バイアス電圧となってもよい。20

#### 【0029】

正のゲート-ソース間電圧は、p型材料のボディ212中に含まれる電子ホールを遠ざける一方で、p型材料のボディ212に含まれる自由電子を引きつけうる。同時に、正のゲート-ソース間電圧は、n型のドレイン部220およびソース部228に含まれる可動電子を引きつけうる。ドレイン200およびソース204の直流電圧と比べてゲート208の正電圧が十分に高くなり、閾値電圧として知られる電圧になると、p型材料のボディ212における斥力、および、ボディ212に含まれる自由電子とn型のドレイン部220およびソース部228に含まれる可動電子への引力により、電子チャネルを形成しうる。この電子チャネルは、しばしば、反転層と呼ばれ、n型のドレイン部220およびソース部228の間であって誘電体224の直下に存在しうる。言い換えれば、n型のドレイン部220およびソース部228の間の電子チャネルは、ボディ212および誘電体214のちょうど間に存在しうる。いくつかの実施の形態において、ゲート208に印加する電圧を上げると、静電界の大きさが増大しうる。静電界が増大すると、電子チャネルの大きさが増え、その結果、ドレイン200およびソース204の間を通過できる電流量が増加しうる。30

#### 【0030】

FET104をオフにするため、デコーダは、ゲート208に-2.5Vの電圧を印加してもよい。ドレイン200およびソース204は、0Vの直流電圧にバイアスされたままであってもよい。しかしながら、ボディ212は、第1抵抗128および第2抵抗136を通るRF信号からのエネルギーにより変調されうる。この約0Vでもよいボディバイアス電圧の供給は、RF信号により引き出されるバイアス電圧により完全になされてよく、デコーダからの外部の制御線を必要としない。40

#### 【0031】

図3は、種々の実施の形態に係るセル300を示す。セル300は、実質的に置換可能な同様の名称の構成要素を有するセル100と、同様であってもよい。

#### 【0032】

セル300は、ソース端子308、ドレイン端子312およびゲート端子316を有するスイッチFET304を含んでもよい。セル300は、さらに、第1バイアスFET328と、ボディ端子320に接続されるノード332と、第2バイアスFET336とを含む、ボディバイアス回路324を含んでもよい。バイアスFET328、336は、一般に、n型FETとして示したものとしてもよい。しかしながら、他の実施の形態におい50

ては、p型FETのような、他の種類のFETを用いてもよい。

#### 【0033】

第1バイアスFET328は、ソース端子308に接続されるソース端子340と、ノード332に接続されるドレイン端子344と、ドレイン端子312に接続されるゲート端子348と、を含んでもよい。第2バイアスFET336は、ノード332に接続されるドレイン端子352と、ドレイン端子312に接続されるソース端子356と、ソース端子308に接続されるゲート端子360と、を含んでもよい。

#### 【0034】

スイッチFET304がオフ状態のとき、ボディバイアス回路324は、スイッチFET304に印加されるRF信号に基づいてボディにバイアスをかける、負の電圧を生成してもよい。これは、図示されるように、バイアスFET328、336のゲートを、スイッチFET304の反対側のソースおよびドレイン端子に結合することによりなされてもよい。RF信号の正の電圧を制限ないし縮小し、RF信号の負の電圧を増幅するよう機能しうるようバイアスFET328、336を構成することで、ボディ端子320に負のバイアス電圧が印加される。これは、時間と電圧の関数として、複数のパワーレベルの異なるRF信号をプロットした、図4に示すグラフに見られる。特に、図4(a)は、スイッチFET304に印加されたRF信号の電圧を時間に対してプロットし、図4(b)は、ボディバイアス回路324によりスイッチFET304に印加された対応する電圧の時間に対してプロットしたものである。

#### 【0035】

セル300により実現されるように、負のバイアス電圧をボディに印加することで、セル300の性能を向上しうる。これは、負のソース-ボディ間電圧が、負のゲート-ソース間電圧と協働し、ドレイン端子312およびソース端子308の間ににおいて高抵抗を与える、負の静電界を生成することが原因であるかもしれない。これは、負の静電界がp型ボディに含まれる電子ホールを引きつけると同時に、n型のドレイン部およびソース部に含まれる可動電子を遠ざけることにより、ソース-ドレイン間での電子の移動を禁止する、負の静電界が原因であるかもしれない。n型FETの代わりにp型FETが用いられる他の実施の形態においては、ボディはn型材料であってよく、ドレイン部およびソース部はp型材料であってもよい。

#### 【0036】

上述したように、負の静電界を与えることにより、スイッチFET304のソース-ドレイン間のチャネルを完全に消滅させうる。これにより、大きなRF信号における変調効果を制限することができる。さもないと、スイッチFET304をオフ状態にした場合であって、スイッチFET304が部分的に消滅したチャネルを有する場合に、この変調効果が生じうる。仮に、チャネルが部分的にのみ消滅した場合、スイッチFET304は、NPN接合のP領域としての機能を果たす部分的に消滅したチャネルの一部を有する、横型の寄生バイポーラ接合トランジスタとして機能するおそれがある。

#### 【0037】

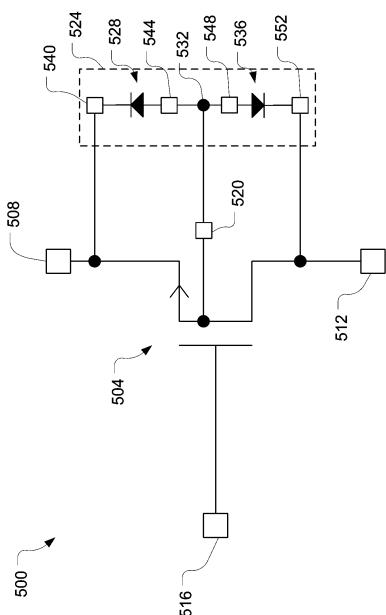

図5は、種々の実施の形態に係るセル500を示す。セル500は、実質的に置換可能な同様の名称の構成要素を有するセル100およびセル300と、同様であってもよい。

#### 【0038】

セル500は、ソース端子508、ドレイン端子512、ゲート端子516およびボディ端子520を有する、FET504を含んでもよい。セル500は、さらに、第1バイアスダイオード528、ボディ端子520と接続されるノード532および第2バイアスダイオード536を有する、ボディバイアス回路524を含んでもよい。

#### 【0039】

第1バイアスダイオード528は、ソース端子508と接続されるカソード端子540と、ノード532に接続されるアノード端子544を含んでもよい。第2バイアスダイオード536は、ノード532と接続されるアノード端子548と、ドレイン端子512に接続されるカソード端子552を含んでもよい。

10

20

30

40

50

**【0040】**

FET504がオン状態のとき、バイアスダイオード528、536は導通せず、ボディは浮遊する。ボディは、一般に、浮遊時に0V近傍に維持されてもよい。FET504がオフ状態のとき、バイアスダイオード528、536は、RF信号を直流信号に整流し、スイッチFET504のボディを駆動して、浮遊状態から平均して負の電圧となる状態にする。この負の電圧は、スイッチFET504を横切るRF信号のピーク電圧に依存する。ボディに印加される電圧の波形は、図4(b)に示される波形と同様であってもよい。

**【0041】**

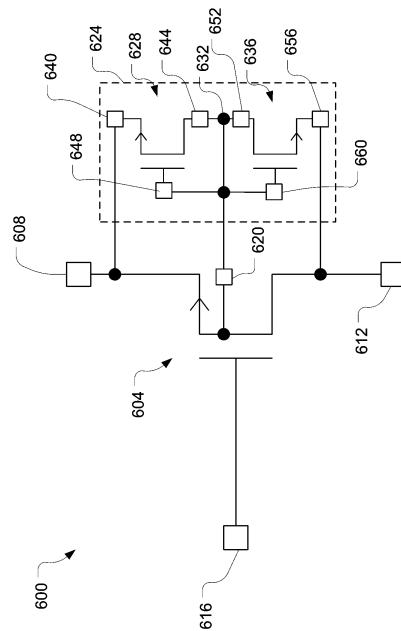

図6は、種々の実施の形態に係るセル600を示す。セル600は、実質的に置換可能な同様の名称の構成要素を有するセル100、300、500と、同様であってもよい。10

**【0042】**

セル600は、ソース端子608、ドレイン端子612、ゲート端子616およびボディ端子620を有し、スイッチFET604とも呼ぶFET604を含んでもよい。セル600は、第1バイアスFET628、ボディ端子620と接続されるノード632および第2バイアスFET636を含むボディバイアス回路624をさらに含んでもよい。バイアスFET628、636は、n型FETであってもよい。他の実施の形態においては、p型FETなどの他の種類のFETを用いてもよい。

**【0043】**

第1バイアスFET628は、ソース端子608に接続されるソース端子640と、ノード632に接続されるドレイン端子644と、ノード632に接続されるゲート端子648とを含んでもよい。第2バイアスFET636は、ノード632に接続されるドレイン端子652と、ドレイン端子612に接続されるソース端子656と、ノード632に接続されるゲート端子660とを含んでもよい。このように、バイアスFET628、636は、スイッチFET604のドレインとソースの間に配置され、スイッチFET604のボディと接続されるボディバイアス回路624の中間点を持つダイオード接続FETであってもよい。20

**【0044】**

ダイオード接続FET628、636は、図5を参照して上述したバイアスダイオードと同様に動作してもよい。しかし、ダイオード接続FETは、バイアスダイオードのオン動作電圧よりも低いオン動作電圧、例えば、0.2Vか0.3Vだけ低いオン動作電圧を有してもよい。その結果、スイッチFET604がオフ状態のとき、より大きな負の電圧がボディに印加されてもよい。30

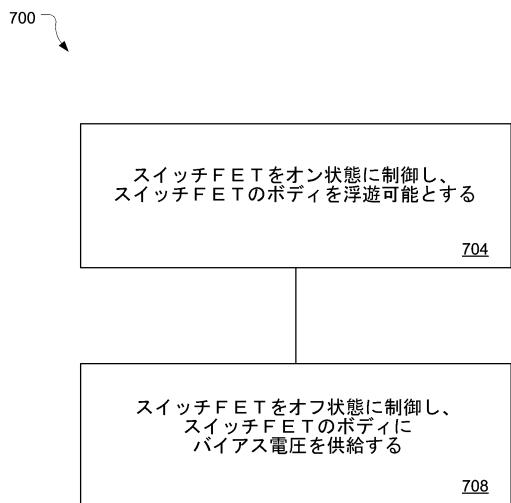

**【0045】**

図7は、単位セルの動作の方法700を示すフローチャートであり、例えば、種々の実施の形態に係るセル100、300、500または600の動作の方法700を示す。

**【0046】**

ブロック704において、方法700は、スイッチFETをオン状態に制御してもよい。これは、例えば、スイッチFETに正のゲート-ソース間電圧を供給するデコーダによりなされてもよい。方法700は、ブロック704において、さらにスイッチFETのボディを浮遊させて、約0Vとしてもよい。これは、例えば、図1、3、5または6に示されるように、スイッチFETのドレイン、ソース、ボディ端子に対して、ボディバイアス回路を接続することによりなされてもよい。40

**【0047】**

ブロック708において、方法700は、スイッチFETをオフ状態に制御してもよい。これは、例えば、スイッチFETに負のゲート-ソース間電圧を供給するデコーダによりなされてもよい。方法700は、ブロック708において、さらにスイッチFETのボディにバイアス電圧を供給してもよい。上述したように、これは、スイッチFETに印加されるRF信号からボディバイアス電圧を引き出す、ボディバイアス回路によりなされてもよい。いくつかの実施の形態において、ボディバイアス電圧は、負のバイアス電圧である。50

つてもよい。

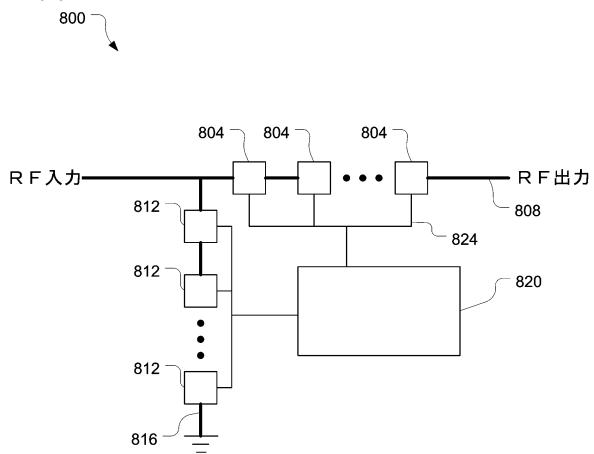

#### 【0048】

図8は、いくつかの実施の形態に係るスイッチ装置800の例を示す。スイッチ装置800は、直列ライン808において互いに直列接続される、複数の直列セル804を含んでもよい。スイッチ装置800は、分岐ライン816において互いに直列接続される複数の分岐セル812をさらに含んでもよい。なお、図示されるように、複数のセルが直列接続されることが望ましい。なぜなら、上述したように、スイッチFETがオフ状態のときにソース端子とドレイン端子との間により大きな抵抗が生成されるからである。RF信号の電流が非常に大きいと、スイッチFETは損傷するかもしれない。複数のFETを直列接続することにより、大きなRF信号により引き起こされる負荷が分散され、それぞれのFETは負荷の一部を担えばよいこととなる。このようにして、FETの寿命は延長されるかもしれない。スイッチ装置800の個々のセルは、セル100、300、500または600と同様であってもよい。

#### 【0049】

スイッチ装置800は、さらに、デコーダ820を含んでもよい。デコーダ820は、デコーダライン824（直列ライン808および分岐ライン816よりも細い線で示される）を通じてセルと接続されてもよい。より具体的には、デコーダライン824は、それぞれのセルのゲート端子に供給されてもよい。直列セル804および分岐セル812におけるボディバイアス回路がRF信号を用いて適切なボディバイアス電圧を引き出す場合、セルは、それぞれのボディ端子に接続されるデコーダラインを必要としない。この制御線の削減は、より小さなダイサイズ、より少ない基板のノイズ結合、そして、オンダイのチャージポンプ回路からRFスイッチコアへ侵入する不要な信号の削減をもたらしうる。

#### 【0050】

スイッチ装置800がオン状態のとき、RF信号を入力から出力に通すため、デコーダ820は、それぞれの直列セル804をオン状態に設定し、それぞれの分岐セル812をオフ状態に設定してもよい。スイッチ装置800がオフ状態のとき、RF信号が入力から出力へ通過するのを妨げるため、デコーダ820は、それぞれの直列セル804をオフ状態に設定し、それぞれの分岐セル812をオン状態に設定してもよい。

#### 【0051】

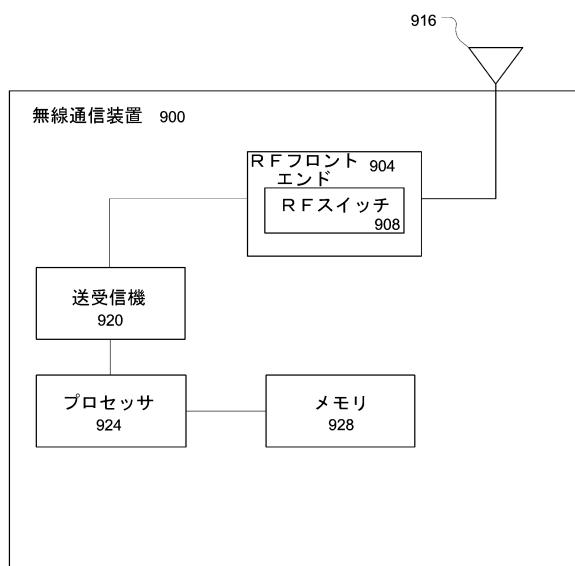

図9は、いくつかの実施の形態に係る無線通信装置900を示す。無線通信装置900は、一以上のRFスイッチ908を含むRFフロントエンド904を有してもよい。RFスイッチ908は、スイッチ装置800と同様であり、スイッチ装置800と実質的に置換可能であってもよい。RFスイッチ908は、アンテナスイッチモジュール、配電スイッチ、送信機、受信機などであって、これらに限定されないRFフロントエンド904の種々の構成要素に展開されてもよい。RFフロントエンド904は、増幅器や変換器、フィルタなどの具体的に示したり説明したりしていない構成要素であって、これらに限定されない他の構成要素を含んでもよい。

#### 【0052】

RFフロントエンド904に加えて、無線通信装置900は、少なくとも図示されるように互いに接続される、アンテナ構造916、送受信機920、プロセッサ924およびメモリ928を有してもよい。

#### 【0053】

プロセッサ924は、無線通信装置900の全体的な動作を制御するために、メモリ928に保存される基本的なOS（operating system）プログラムを実行してもよい。例えば、メインプロセッサ924は、送受信機920による信号の受信および送信を制御してもよい。メインプロセッサ924は、メモリ928に常駐する他のプロセスやプログラムを実行する能力を有してもよく、実行するプロセスの要求に応じて、データをメモリ928に移動したり、メモリ928から取り出したりしてもよい。

#### 【0054】

送受信機920は、送信用データ（例えば、音声データ、ウェブデータ、Eメール、通

10

20

30

40

50

信用データなど)をプロセッサ924から取得し、出力用データを意味するRF信号を生成し、RF入力信号をRFフロントエンド904に供給してもよい。逆に、送受信機920は、RFフロントエンド904から受信用データを意味するRF信号を受信してもよい。送受信機920は、RF信号を処理し、受信した信号をさらなる処理のためにプロセッサ924に送信してもよい。

#### 【0055】

RFフロントエンド904は、種々のフロントエンド機能を提供してもよい。このフロントエンド機能は、RFスイッチ908により実現されるスイッチング機能を含むが、これに限定されない。具体的には、RFスイッチ908は、無線通信装置900の構成要素間または、これらの構成要素への入出力として、RF信号を選択的に通過させてもよい。

10

#### 【0056】

種々の実施の形態において、無線通信装置900は、携帯電話、ページング装置、パーソナルデジタルアシスタント、テキストメッセージ装置、ポータブルコンピュータ、デスクトップコンピュータ、基地局、加入者局、アクセスポイント、レーダー、衛星通信装置、その他、無線によりRF信号を送受信可能な、いかなる装置であってもよいが、これらに限定されるものではない。

#### 【0057】

当業者であれば、無線通信装置900が例示として示されており、簡潔性および明確性のため、無線通信装置900の大半の構成および動作が、実施の形態の理解のために必要とされる程度に示され、記載されていることが認識されるであろう。種々の実施の形態は、無線通信装置900に関連し、具体的なニーズに従う適切な目的を実行する、いかなる適切な要素または要素の結合を考慮する。さらに言えば、無線通信装置900は、具体的に実施されうる種類の装置に限定されるように解釈すべきではないことが理解されよう。

20

#### 【0058】

種々の実施の形態は、無線周波数(RF)信号をスイッチするように構成される回路を示す。この回路は、ソース端子、ゲート端子、ドレイン端子およびボディ端子を含むFETと、ソース端子、ドレイン端子およびボディ端子に接続されるボディバイアス回路とを備え、ボディバイアス回路は、FETに印加されるRF信号に基づく負のバイアス電圧を引き出し、FETがオフ状態のときにボディ端子に負のバイアス電圧を供給するように構成される。

30

#### 【0059】

回路は、FET(例えば、n型FET)を含み、互いに直列接続される複数のFETを含んでもよい。

#### 【0060】

ボディバイアス回路は、ソース端子、ドレイン端子およびボディ端子のみに接続されてもよい。

#### 【0061】

回路は、シリコン-オン-インシュレータ(SOI)回路であってもよい。

#### 【0062】

FETを第1FETとした場合に、ボディバイアス回路は、ボディ端子に接続されるノードと、第1FETのソース端子に接続されるソース端子およびノードと接続されるドレイン端子を有する第2FETと、ノードに接続されるドレイン端子および第1FETのドレイン端子に接続されるソース端子を有する第3FETと、を含んでもよい。

40

#### 【0063】

第2FETは、さらに第1FETのドレイン端子と接続されるゲート端子を含んでもよく、第3FETは、さらに第1FETのソース端子と接続されるゲート端子をさらに含んでもよい。

#### 【0064】

第1FETおよび第2FETは、ダイオード接続FETであってもよく、第2FETは、ノードに接続されるゲート端子をさらに含んでもよく、第3FETは、ノードに接続さ

50

れるゲート端子をさらに含んでもよい。

**【0065】**

ボディバイアス回路は、ボディ端子に接続されるノードと、ソース端子およびノードに接続される第1ダイオードと、ドレイン端子およびノードに接続される第2ダイオードとを含んでもよい。

**【0066】**

第1ダイオードは、ソース端子に接続されるカソード端子およびノードに接続されるアノード端子を含んでもよく、第2ダイオードは、ドレイン端子に接続されるカソード端子およびノードに接続されるアノード端子を含んでもよい。

**【0067】**

ボディバイアス回路は、RF信号を整流することにより負のバイアス電圧を引き出してよい。

10

**【0068】**

種々の実施の形態は、無線通信装置を示す。この無線通信装置は、送受信機と、アンテナと、送受信機およびアンテナに接続され、送受信機とアンテナの間の信号を通信するよう構成される無線周波数(RF)フロントエンドと、備え、無線周波数フロントエンドは、シリコン-オン-インシュレータのスイッチ装置を含み、スイッチ装置は、複数のスイッチFETをオン状態またはオフ状態に設定するデコーダと、複数のFETからなる第1FETおよびボディバイアス回路を含むセルと、を有し、ボディバイアス回路は、第1FETがオフ状態のときに電界効果トランジスタのボディに負の電圧を供給するように構成され、負の電圧は、第1FETに印加されるRF信号により引き出される。

20

**【0069】**

ボディバイアス回路は、第1FETのボディ端子に接続されるノードと、第1FETのソース端子と接続されるソース端子およびノードと接続されるドレイン端子を有する第2FETと、ノードと接続されるドレイン端子および第1FETのドレイン端子に接続されるソース端子を有する第3FETと、を含んでもよい。

**【0070】**

第2FETは、第1FETのドレイン端子に接続されるゲート端子をさらに含んでもよく、第3FETは、第1FETのソース端子に接続されるゲート端子をさらに含んでもよい。

30

**【0071】**

種々の実施の形態は、ある方法を含んでもよい。この方法は、デコーダ回路を用いて、スイッチ電界効果トランジスタ(FET)をオフ状態に制御し、ボディバイアス回路を用いて、スイッチFETがオフ状態の間に、スイッチFETに印加されるRF信号に基づいて負のバイアス電圧を引き出し、ボディバイアス回路によって、スイッチFETがオフ状態の間に、負のバイアス電圧をスイッチFETのボディに供給してもよい。

**【0072】**

負のバイアス電圧を引き出す際に、スイッチFETに印加されるRF信号を整流してもよい。

**【0073】**

種々の実施の形態は、RF信号をスイッチするように構成される回路を示す。この回路は、ソース端子、ゲート端子、ドレイン端子およびボディ端子を含むFETと、ボディ端子に接続されるノードと、ドレイン端子およびノードに接続される第1抵抗と、ソース端子およびノードに接続される第2抵抗とを有するボディバイアス回路を備え、ボディバイアス回路は、FETに印加されるRF信号に基づくバイアス電圧を引き出し、バイアス電圧をボディ端子に供給するように構成される。

40

**【0074】**

第1抵抗および第2抵抗は、同じ大きさであってもよい。

**【0075】**

ボディバイアス回路は、バイアス電圧を約0Vの直流電圧として供給するように構成さ

50

れてもよい。

**【0076】**

FETのゲート端子は、デコーダに接続されてもよく、FETのドレイン端子はデコーダに接続されなくてもよい。

**【0077】**

本開示は、上述の実施の形態の観点から示されたが、本開示の範囲を逸脱しない限りにおいて、同様の目的を実現すると考えられる、さまざまな代替的および／または等価な実施の形態により、上述した特定の実施の形態が置換されてもよいことは、当業者によって理解されるであろう。当業者であれば、本開示によって示された内容が、様々な実施の形態として実施されてもよいことは、すぐに理解されるであろう。本記載は、制限的であるとみなされる代わりに、例示的であるとみなされることを意図する。10

**【符号の説明】**

**【0078】**

100...セル、104...電界効果トランジスタ、108...ソース端子、112...ドレイン端子、116...ゲート端子、120...ボディ端子、124...ボディバイアス回路、128...第1抵抗、132...ノード、136...第2抵抗。

**【図1】**

**【図2】**

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

(72)発明者 フリノ ジュニア、ジェイムズ ピー.

アメリカ合衆国オレゴン州97124・ヒルズボロ・ノースイーストブルックウッドパークウェイ

2300

(72)発明者 ヨー、マイケル ディー.

アメリカ合衆国オレゴン州97124・ヒルズボロ・ノースイーストブルックウッドパークウェイ

2300

合議体

審判長 吉田 隆之

審判官 衣鳩 文彦

審判官 岡本 正紀

(56)参考文献 特開平8-275406(JP,A)

特開2010-212801(JP,A)

特開2012-70181(JP,A)

米国特許出願公開第2012/0086499(US,A1)

(58)調査した分野(Int.Cl., DB名)

H03K 17/00-17/70