(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7221221号

(P7221221)

(45)発行日 令和5年2月13日(2023.2.13)

(24)登録日 令和5年2月3日(2023.2.3)

(51)国際特許分類

|        |                  |        |       |   |

|--------|------------------|--------|-------|---|

| H 02 M | 3/155 (2006.01)  | H 02 M | 3/155 | Y |

| H 02 M | 3/28 (2006.01)   | H 02 M | 3/155 | W |

| H 01 L | 21/822 (2006.01) | H 02 M | 3/28  | Y |

| H 01 L | 27/04 (2006.01)  | H 01 L | 27/04 | U |

請求項の数 23 (全87頁)

|                   |                             |

|-------------------|-----------------------------|

| (21)出願番号          | 特願2019-565153(P2019-565153) |

| (86)(22)出願日       | 平成30年2月6日(2018.2.6)         |

| (65)公表番号          | 特表2020-511110(P2020-511110) |

|                   | A)                          |

| (43)公表日           | 令和2年4月9日(2020.4.9)          |

| (86)国際出願番号        | PCT/US2018/017109           |

| (87)国際公開番号        | WO2018/148218               |

| (87)国際公開日         | 平成30年8月16日(2018.8.16)       |

| 審査請求日             | 令和3年1月18日(2021.1.18)        |

| (31)優先権主張番号       | 15/428,019                  |

| (32)優先日           | 平成29年2月8日(2017.2.8)         |

| (33)優先権主張国・地域又は機関 |                             |

|                   | 米国(US)                      |

| (31)優先権主張番号       | 15/669,838                  |

| (32)優先日           | 平成29年8月4日(2017.8.4)         |

|                   | 最終頁に続く                      |

|          |                                                                                           |

|----------|-------------------------------------------------------------------------------------------|

| (73)特許権者 | 519290219<br>ファラデー セミ、インコーポレイテッド<br>アメリカ合衆国 カリフォルニア州 92<br>618 アーバイン、アーバイン・センター・ドライブ、9541 |

| (74)代理人  | 100121728<br>弁理士 井関 勝守                                                                    |

| (74)代理人  | 100165803<br>弁理士 金子 修平                                                                    |

| (74)代理人  | 100170900<br>弁理士 大西 渉                                                                     |

| (72)発明者  | パルト、パルヴィズ<br>アメリカ合衆国 カリフォルニア州 92<br>677 ラグナニゲル、アギア 33                                     |

| 審査官      | 東 昌秋<br>最終頁に続く                                                                            |

(54)【発明の名称】 チップ埋め込み型電力変換器

## (57)【特許請求の範囲】

## 【請求項 1】

プリント基板 (PCB) を備え、プリント基板は、

下部プリント基板 (PCB) 部分と、

上部プリント基板 (PCB) 部分とを備え、

前記下部 PCB 部分と前記上部 PCB 部分との間の埋め込み型回路とを備え、前記埋め込み型回路は、

1つまたは複数のドライバ信号を生成するように構成されたドライバと、

前記1つまたは複数のドライバ信号により駆動されるように構成された1つまたは複数のスイッチとを備え、前記ドライバは少なくとも1MHzの周波数で前記1つまたは複数のスイッチをトグルし、前記1つまたは複数のスイッチは、第1スイッチ、第2スイッチ、第3スイッチ、および第4スイッチを含み、

前記上部 PCB 部分を通じて延びる1つまたは複数のビアと、

前記上部 PCB 部分に位置決めされた第1インダクタとを備え、

前記1つまたは複数のビアは、前記第1インダクタを前記埋め込み型回路に電気的に連結し、

前記第1インダクタのフットプリントが前記埋め込み型回路のフットプリントに少なくとも部分的に重なり、

第2インダクタと、

キャパシタと、

前記埋め込み型回路に連結された入力ポートであって、入力電圧を受信するように構成された入力ポートと、

前記第1インダクタと前記第2インダクタとに連結された出力ポートであって、前記入力電圧とは異なる出力電圧を提供するように構成された出力ポートとを備え、

前記出力電圧は、前記第1インダクタと前記第2インダクタにエネルギーを充填または放出させる前記1つまたは複数のスイッチに少なくとも部分的に基づき、

前記第1スイッチは、前記入力ポートに連結された第1端と、前記キャパシタにより前記第1インダクタの第1端に連結された第2端とを有し、

前記第2スイッチは、前記第1インダクタの前記第1端に連結された第1端を有し、

前記キャパシタは、AC連結キャパシタとして前記第1スイッチと前記第2スイッチとの間に直列に連結され、

前記第3スイッチは、前記キャパシタおよび前記第1スイッチの前記第2端に連結された第1端と、前記第2インダクタの第1端に連結された第2端とを有し、

前記第4スイッチは、前記第3スイッチの前記第2端および前記第2インダクタの前記第1端に連結された第1端とを有し、

前記第2スイッチの第2端は、前記第4スイッチの第2端に連結され、

前記第1インダクタの第2端と前記第2インダクタの第2端は、前記出力ポートに連結されている、電力変換器。

#### 【請求項2】

請求項1に記載の電力変換器であって、

前記ドライバは1MHz～15MHzの周波数で前記1つまたは複数のスイッチをトグルする、電力変換器。

#### 【請求項3】

請求項1または2に記載の電力変換器であって、

前記1つまたは複数のスイッチは、第1エンハンスト窒化ガリウム(eGaN)スイッチと第2エンハンスト窒化ガリウム(eGaN)スイッチを含む、電力変換器。

#### 【請求項4】

請求項1～3のいずれか一項に記載の電力変換器であって、

前記電力変換器は、電流量を処理するように構成され、

前記電力変換器が電流量のアンペア数当たり $0.1\text{mm}^2$ ～ $10\text{mm}^2$ であるフットプリント領域を有する、電力変換器。

#### 【請求項5】

請求項1～4のいずれか一項に記載の電力変換器であって、

前記埋め込み型回路は、前記第1インダクタまたは前記第2インダクタを通る電流リップルをエミュレートする信号を生成するように構成されたランプ波発生器を備える、電力変換器。

#### 【請求項6】

請求項5に記載の電力変換器であって、

前記ランプ波発生器は、前記第1インダクタまたは前記第2インダクタを通る前記電流リップルをエミュレートする前記信号を生成するように構成され、少なくとも、

前記入力電圧を示す第1入力部と、

前記出力電圧を示す第2入力部と、

前記第1インダクタまたは前記第2インダクタのインダクタンス値を示す第3入力部と、

前記1つまたは複数のスイッチの切替信号の第4入力部とを用いる、電力変換器。

#### 【請求項7】

請求項5または6に記載の電力変換器であって、

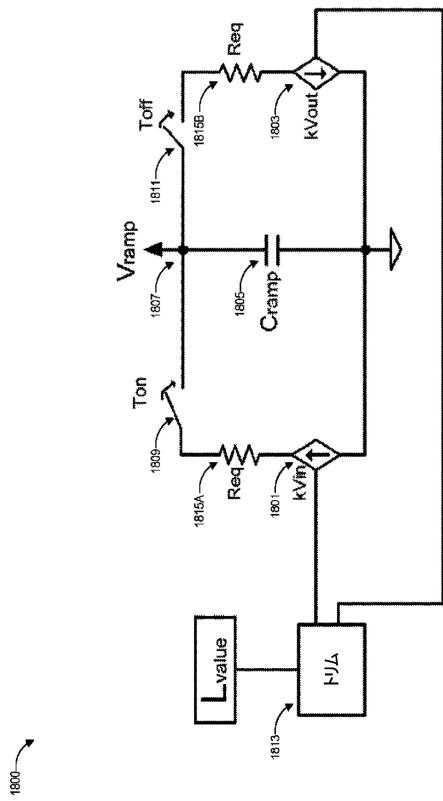

前記ランプ波発生器は、

少なくとも部分的に前記入力電圧に基づいて電流を生成するように構成された第1電流源と、

少なくとも部分的に前記出力電圧に基づいて電流を生成するように構成された第2電流

源と、

前記 1 つまたは複数のドライバ信号の少なくとも 1 つを受信するように構成された第 1 ランプ波発生器スイッチであって、前記第 1 電流源と連結された第 1 ランプ波発生器スイッチと、

前記 1 つまたは複数のドライバ信号の少なくとも 1 つを受信するように構成された第 2 ランプ波発生器スイッチであって、前記第 2 電流源と連結された第 2 ランプ波発生器スイッチと、

前記第 1 ランプ波発生器スイッチおよび前記第 2 ランプ波発生器スイッチと連結されたキャパシタとを備える、電力変換器。

【請求項 8】

請求項 1 ~ 7 のいずれか一項に記載の電力変換器であって、

前記電力変換器は、

電流が前記キャパシタを通って前記第 1 インダクタに流れ、前記キャパシタが充填してエネルギーを蓄積する第 1 動作状態と、

前記キャパシタがエネルギーを放出して電流を前記第 2 インダクタに流す第 2 動作状態とを有する、電力変換器。

【請求項 9】

請求項 1 ~ 8 のいずれか一項に記載の電力変換器であって、

前記電力変換器は、前記電力変換器の入力部と出力部との間の直接的な電気的接続を絶縁するように構成された絶縁トポロジで構成された、電力変換器。

【請求項 10】

請求項 9 に記載の電力変換器であって、

前記絶縁トポロジは、前記第 1 インダクタを通る変更電流が前記第 2 インダクタにおける変更電流を誘発するように構成された前記第 1 インダクタおよび前記第 2 インダクタを含む変圧器を備える、電力変換器。

【請求項 11】

請求項 1 ~ 10 のいずれか一項に記載の電力変換器であって、

前記埋め込み型回路は、1 つまたは複数の PWM 信号を生成するように構成されたパルス幅変調器 ( PWM ) コントローラを備え、

前記 PWM コントローラは、前記ドライバと連結され、

前記ドライバは、少なくとも部分的に前記 PWM 信号に基づいて 1 つまたは複数のドライバ信号を生成するように構成されている、電力変換器。

【請求項 12】

請求項 1 ~ 11 のいずれか一項に記載の電力変換器であって、

前記第 1 インダクタおよび前記埋め込み型回路の一方は、前記第 1 インダクタおよび前記埋め込み型回路の他方のフットプリントに完全に含まれるフットプリントを有する、電力変換器。

【請求項 13】

請求項 1 ~ 12 のいずれか一項に記載の電力変換器であって、

前記第 2 インダクタは前記上部プリント基板 ( PCB ) 部分に位置し、

前記 1 つまたは複数のビアは前記第 2 インダクタを前記埋め込み型回路に電気的に連結し、

前記第 2 インダクタのフットプリントが前記埋め込み型回路のフットプリントに少なくとも部分的に重なる、電力変換器。

【請求項 14】

請求項 1 ~ 13 のいずれか一項に記載の電力変換器であって、

前記第 1 インダクタおよび前記第 2 インダクタは、互いに位相をずらして駆動される、電力変換器。

【請求項 15】

請求項 1 ~ 14 のいずれか一項に記載の電力変換器であって、

10

20

30

40

50

前記第1インダクタは、コアの周囲の第1巻き線を備え、

前記第2インダクタは、同じコアの周囲の第2巻き線を備える、電力変換器。

【請求項16】

請求項8に記載の電力変換器であって、

前記第1動作状態において、前記第1スイッチはオン、前記第2スイッチはオフ、および前記第3スイッチはオフであり、

前記第2動作状態において、前記第3スイッチはオンおよび前記第4スイッチはオフである、電力変換器。

【請求項17】

請求項1～16のいずれか一項に記載の電力変換器であって、

前記電力変換器の出力を調整するための制御信号を受信するように構成された通信インターフェースをさらに備える、電力変換器。

【請求項18】

請求項17に記載の電力変換器であって、

前記第1インダクタまたは前記第2インダクタを通る電流リップルをエミュレートする信号を生成するように構成されたランプ波発生器を有するフィードバックシステムをさらに備え、

前記フィードバックシステムは、前記通信インターフェースを介して受信されるコマンドに応じて前記ランプ波発生器をトリムするように構成されている、電力変換器。

【請求項19】

請求項17または18に記載の電力変換器であって、

前記通信インターフェースは電源管理バス(PM BUS)を備える、電力変換器。

【請求項20】

請求項17～19のいずれか一項に記載の電力変換器であって、

前記通信インターフェースは、集積回路間(I2C)プロトコルを実施するように構成される、電力変換器。

【請求項21】

請求項17～19のいずれか一項に記載の電力変換器であって、

前記通信インターフェースは前記埋め込み型回路と同じパッケージにおける無線通信システムを備える、電力変換器。

【請求項22】

複数の電力変換器を備え、前記複数の電力変換器の各々は、請求項1～21のいずれか一項に記載の電力変換器による電力変換器である電力供給システムであって、

複数のPWM信号を生成するように構成された共用パルス幅変調器(PWM)コントローラとを備え、

前記PWMコントローラは、前記複数の電力変換器の前記ドライバと連結されて、前記複数のPWM信号を前記電力変換器の対応する前記ドライバへ送り、

前記ドライバは、少なくとも部分的に前記PWM信号に基づいて前記1つまたは複数のドライバ信号を生成するように構成されている、電力供給システム。

【請求項23】

請求項1～21のいずれか一項に記載の電力変換器による第1電力変換器を備える電力供給システムであって、

前記第1電力変換器と並列に連結された第2電力変換器と、

電流平衡のために前記第1電力変換器の出力と前記第2電力変換器の出力を調節するように構成された制御システムとをさらに備える、電力供給システム。

【発明の詳細な説明】

【技術分野】

【0001】

[関連出願の相互参照]

この出願は、2017年2月8日に出願された米国特許出願番号第15/428,01

10

20

30

40

50

9号(米国特許第9、729、059号として発行)の一部継続である、2017年8月4日に出願された米国特許出願番号第15/669、838の継続である。これらの出願の全内容を全ての目的のために本願に参照により援用する。

### 【0002】

#### [技術分野]

本開示は、電子システム、直流-直流(DC-DC)変換器、電子デバイス設計、および電子デバイス製造技術に関する。

### 【背景技術】

### 【0003】

種々のDC-DC変換器が知られているが、これらのDC-DC変換器は、寄生損失および非効率性の影響を受ける非理想的な構成要素および/または構造からなる。改善された電力変換器に対する必要性がある。

10

### 【発明の概要】

### 【0004】

いくつかの実施形態は、直流-直流(DC-DC)電力変換器について開示されており、この直流-直流電力変換器は、下面および上面を有する下部プリント基板(PCB)部分と、下面および上面を有する上部プリント基板(PCB)部分と、前記下部PCB部分の前記上面と前記上部PCB部分の前記下面との間の埋め込み型回路とを備え、前記埋め込み型回路は、パルス幅変調器と、少なくとも1つのスイッチとを備え、前記上部PCB部分を通って延びる1つまたは複数のビアと、前記上部PCB部分の前記上面に位置決めされたインダクタとを備え、前記1つまたは複数のビアは、前記インダクタおよび前記埋め込み型回路と電気的に連結されている。本実施形態は、以下の任意の組み合わせを特徴とし得る。すなわち、

20

- ・前記埋め込み型回路は集積回路(IC)を備える。

- ・前記インダクタのフットプリントは前記集積回路のフットプリントに少なくとも部分的に重なる。

- ・ワイヤボンドが前記インダクタと前記埋め込み型回路とを電気的に相互接続しない、

- ・前記回路は少なくとも1MHzの切替速度を有する。

- ・前記回路は少なくとも3MHzの切替速度を有する。

- ・前記回路は少なくとも5MHzの切替速度を有する。

30

- ・前記回路は最大7MHzの切替速度を有する。

- ・前記少なくとも1つのスイッチはエンハンスト窒化ガリウム電界効果トランジスタ(enhanced gallium nitride fieldeffect transistor、eGaNFET)を備える。

- ・前記上部PCB部分の前記上面に設けられた1つまたは複数のキャパシタをさらに備える。

- ・前記下部PCB部分の前記上面と前記上部PCB部分の前記下面との間に設けられたコアをさらに備え、前記コアはその内部に形成された1つまたは複数のポケットを備え、前記埋め込み型回路は前記1つまたは複数のポケットに設けられている。

- ・前記DC-DC電力変換器は25mm<sup>2</sup>未満のフットプリントを有する。

- ・前記DC-DC電力変換器は10mm<sup>2</sup>未満のフットプリントを有し、

40

- ・前記DC-DC電力変換器は5mm<sup>2</sup>未満のフットプリントを有し、

- ・前記DC-DC電力変換器が2mm<sup>2</sup>のように小さいフットプリントを有する。

- ・前記DC-DC電力変換器は電流のアンペア数当たり0.5mm<sup>2</sup>~10mm<sup>2</sup>であるフットプリント領域を有する。

### 【0005】

いくつかの実施形態は、直流-直流(DC-DC)電力変換器パッケージについて開示されており、この直流-直流電力変換器パッケージは、少なくとも1つのプリント基板(PCB)に埋め込まれた集積回路(IC)チップであって、ドライバを備えるICチップと、と、前記チップ埋め込みパッケージの外部に位置決めされ、前記チップ埋め込みパッケージの表面に連結されたインダクタと、前記インダクタを前記ICチップに電気的に連

50

結するビアとを備え、前記インダクタのフットプリントは、前記 I C チップのフットプリントに少なくとも部分的に重なる。本実施形態は、以下のいずれかを特徴とし得る。すなわち、トランジスタは前記少なくとも 1 つの P C B に埋め込みされる、前記インダクタは前記トランジスタと電気的に連結される、前記 I C チップは、前記ドライバに連結されたパルス幅変調器 ( P W M ) コントローラと、前記ドライバの出力部と連結されたスイッチングトランジスタとを備える、エンハンスト窒化ガリウム ( e G a N ) を含むスイッチをさらに備える、前記スイッチは 4 M H z 以上で切り替わるように構成されている、前記スイッチは 5 M H z 以上で切り替わるように構成されている、シリコンまたはヒ化ガリウムの少なくとも 1 つを含むスイッチをさらに備える。

## 【 0 0 0 6 】

10

いくつかの実施形態は、単一のパッケージにおける直流 - 直流 ( D C - D C ) 電力変換器について開示されており、この直流 - 直流電力変換器は、実装基板の内側に、少なくとも部分的に、埋め込まれたエンハンスト窒化ガリウム ( e G a N ) 構成要素と、前記実装基板の外側に搭載されたインダクタと、前記 e G a N 構成要素に前記インダクタを連結するビアとを備え、前記インダクタのフットプリントは、前記 e G a N 構成要素のフットプリントに少なくとも部分的に重なる。本実施形態は、以下の任意の組み合わせを特徴とし得る。すなわち、

- ・前記実装基板は多層 P C B である。

- ・前記 e G a N 構成要素は e G a N を含むスイッチであり、前記 D C - D C 電力変換器は前記スイッチを駆動するドライバ回路をさらに備える。

- ・前記ドライバおよび前記スイッチは、 I C チップの一部である。

- ・前記 I C チップは、パルス幅変調器 ( P W M ) コントローラをさらに備える。

20

## 【 0 0 0 7 】

いくつかの実施形態は、チップ埋め込みパッケージを利用する直流 - 直流 ( D C - D C ) 電力変換器について開示されており、この D C - D C 変換器は、プリント基板 ( P C B ) の内側におけるエンハンスト窒化ガリウム ( e G a N ) スイッチと、パルス幅変調器 ( P W M ) コントローラと、前記 P C B の内部に埋め込まれたドライバとを備え、前記 P W M コントローラおよび前記ドライバは、 1 M H z 以上の周波数で前記 e G a N スイッチを駆動するように構成され、そして、この D C - D C 変換器は、前記チップ埋め込みパッケージの外部に配置され、前記 P C B の表面に連結されたインダクタと、前記インダクタを前記 e G a N スイッチに電気的に連結するビアとを備える。これらの実施形態は、前記ドライバが前記 e G a N スイッチを 5 M H z 以上の周波数で駆動するように構成されていることを特徴とし得る。

30

## 【 0 0 0 8 】

いくつかの実施形態は、直流 - 直流 ( D C - D C ) 電力変換器について開示されており、この直流 - 直流電力変換器は、プリント基板と、前記プリント基板の内側の集積回路とを備え、前記集積回路はドライバを備える。本実施形態は、以下の任意の組み合わせを特徴とし得る。すなわち、

- ・前記プリント基板を通って延びる 1 つまたは複数のビアにより前記集積回路と電気的に連結されたインダクタをさらに備える。

- ・前記インダクタは、前記集積回路のフットプリントに少なくとも部分的に重なるフットプリントを有する。

40

## 【 0 0 0 9 】

いくつかの実施形態は、直流 - 直流 ( D C - D C ) 電力変換器について開示されており、この直流 - 直流電力変換器は、ドライバを備える集積回路と、前記インダクタのフットプリントが前記集積回路のフットプリントに少なくとも部分的に重なるように、前記集積回路に垂直に積層されたインダクタとを備え、前記インダクタは、前記集積回路と電気的に連結されている。本実施形態は、以下の任意の組み合わせを特徴とし得る。すなわち、

- ・第 1 面と前記第 1 面とは反対側の第 2 面とを有するプリント基板 ( P C B ) をさらに備え、前記集積回路は、前記 P C B の前記第 1 面に実装され、前記インダクタは、前記 P C

50

B の前記第 2 側に実装される。

- ・前記インダクタは、前記プリント基板を通って延びる 1 つまたは複数のビアにより前記集積回路と電気的に連結されている。

【 0 0 1 0 】

いくつかの実施形態は、直流 - 直流 ( D C - D C ) バックコンバータについて開示されており、この直流 - 直流電力変換器は、1 つまたは複数のスイッチと、前記 1 つまたは複数のスイッチを駆動するドライバと、前記スイッチと電気的に連結されたインダクタとを備え、前記 D C - D C バックコンバータの前記フットプリントは、65 mm<sup>2</sup> 未満であり、前記 D C - D C バックコンバータは、少なくとも 20 アンペアの電流を受信するよう構成され、前記 D C - D C バックコンバータは、少なくとも 20 アンペアの電流を出力するよう構成されている。

10

【 0 0 1 1 】

いくつかの実施形態は、直流 - 直流 ( D C - D C ) 電力変換器について開示されており、この直流 - 直流電力変換器は、1 つまたは複数のスイッチと、前記 1 つまたは複数のスイッチを 1 MHz 以上 5 MHz 以下の周波数で駆動するよう構成されたドライバと、前記 1 つまたは複数のスイッチと電気的に連結されたインダクタとを備え、前記 D C - D C 変換器の前記フットプリントは、10 mm<sup>2</sup> 以下であり、前記 D C - D C 変換器は少なくとも 5 アンペアの電流を受信するよう構成されており、前記 D C - D C 変換器は少なくとも 5 アンペアの電流を出力するよう構成されている。

20

【 0 0 1 2 】

いくつかの実施形態は、直流 - 直流 ( D C - D C ) 電力変換器について開示されており、この直流 - 直流電力変換器は、第 1 インダクタと連結された第 1 スイッチと、第 2 インダクタと連結された第 2 スイッチと、プリント基板に埋め込まれた集積回路チップとを備え、前記第 1 スイッチおよび前記第 2 スイッチは、変調器と連結され、前記第 1 インダクタおよび前記第 2 インダクタは、電圧出力ノードと連結されている。本実施形態は、以下の任意の組み合わせを特徴とし得る。すなわち、

- ・前記変調器は、前記集積回路チップに含まれる。

- ・前記変調器は、前記第 1 スイッチおよび前記第 2 スイッチに同期期間で位相を出力するよう動作させるよう構成されている。

- ・前記出力ノードにおける出力信号は、第 1 インダクタを介した第 1 信号および第 2 インダクタを介した第 2 信号に重畠される。

30

【 0 0 1 3 】

いくつかの実施形態は、直流 - 直流 ( D C - D C ) 電力変換器について開示されており、この直流 - 直流電力変換器は、プリント基板に埋め込まれた集積回路チップであって、ドライバを備える集積回路チップと、前記ドライバと連結された第 1 スイッチと、前記第 1 スイッチと連結されたインダクタと、出力ノードから変調回路へのフィードバック経路とを備える。本実施形態は、以下の任意の組み合わせを特徴とし得る。すなわち、

- ・前記変調回路は、電圧モード変調回路である。

- ・前記変調回路は、常時オン時間または常時オフ時間変調回路である。

- ・前記変調回路は、前記集積回路チップに含まれる。

- ・前記変調回路および前記インダクタは、前記集積回路チップと共にパッケージに含まれている。

40

【 0 0 1 4 】

いくつかの実施形態は、直流 - 直流 ( D C - D C ) 電力変換器について開示されており、この直流 - 直流電力変換器は、プリント基板に埋め込まれた集積回路チップであって、ドライバを備える集積回路チップと、前記ドライバと連結された第 1 スイッチと、前記第 1 スイッチと連結されたインダクタと、出力ノードから変調回路へのフィードバック経路と、ランプ波発生器とを備える。本実施形態は、以下の任意の組み合わせを特徴とし得る。すなわち、

- ・前記フィードバック経路と、前記ランプ波発生器からの出力とが比較器に連結される。

50

- ・前記比較器と連結された基準電圧源をさらに備える。

- ・前記ランプ波発生器は、前記インダクタを通るリップル電流をエミュレートするように構成される。

- ・前記ランプ波発生器は、第1電流源と、第2電流源と、キャパシタとを備える。

- ・前記第1電流源および前記第2電流源は、少なくとも一部が前記インダクタのインダクタンスに基づいてトリムされるように構成される。

- ・前記ランプ波発生器および前記インダクタは、同じDC - DC電力変換器パッケージに含まれる。

- ・前記ランプ波発生器は、前記インダクタに連結された出力キャパシタにより影響を受けない出力信号を生成するように構成されている。

- ・前記ランプ波発生器は、前記インダクタに連結された出力キャパシタの等価直列抵抗(ESR)から独立した出力信号を生成するように構成されている。

- ・前記出力キャパシタのリップル電圧が小さすぎて変調回路へ確実に提供されないように、十分に低いESRを有する出力キャパシタをさらに備える。

#### 【0015】

いくつかの実施形態は、以下を備えるランプ波発生器について開示されている。すなわち、供給電圧に連結された第1電流源と、アースに連結された第2電流源と、前記第1電流源と前記第2電流源との間に連結されたキャパシタとを備える。本実施形態は、以下の任意の組み合わせを特徴とし得る。すなわち、

- ・前記ランプ波発生器は、DC - DC変換器においてインダクタを通るリップル電流をエミュレートするように構成される。

- ・前記第1電流源の前記出力は、DC - DC変換器に対する入力電圧少なくとも一部が基づいている。

- ・前記第1電流源の前記出力は、DC - DC変換器におけるインダクタのインダクタンスに少なくとも一部が基づいている。

- ・前記第2電流源の前記出力は、DC - DC変換器におけるインダクタのインダクタンスに少なくとも一部が基づいている。

- ・前記第2電流源の前記出力は、DC - DC変換器におけるインダクタのインダクタンスに少なくとも一部が基づいている。

- ・前記第1電流源は、DC - DC変換器に置けるインダクタのインダクタンスに少なくとも一部が基づいてトリムされるように構成されている。

- ・前記第2電流源は、DC - DC変換器におけるインダクタのインダクタンスに少なくとも一部が基づいてトリムされるように構成されている。

#### 【0016】

いくつかの実施形態は、チップ埋め込み型直流 - 直流変換器の作成のための、以下を含む方法について開示されている。すなわち、プリント基板に集積回路チップを埋め込み、前記プリント基板に第1インダクタを連結し、前記プリント基板に第2インダクタを連結し、前記第1インダクタおよび前記第2インダクタの双方は出力ノードに連結されていることを含む。

#### 【0017】

いくつかの実施形態は、第1直流電圧を第2直流電圧に変換する、以下を含む方法について開示されている。すなわち、第1インダクタと連結された第1スイッチを駆動し、第2インダクタと連結された第2スイッチを駆動し、前記第1スイッチおよび前記第2スイッチは、出力ノードに連結され、前記第1スイッチおよび前記第2スイッチを位相をずらして変調し、ドライバまたは変調器の少なくとも1つのがプリント基板に埋め込まれたチップに含まれる。

#### 【0018】

いくつかの実施形態は、チップ埋め込み型直流 - 直流変換器の作成のための、以下を含む方法について開示されている。すなわち、プリント基板に集積回路チップを埋め込み、前記集積回路チップと出力ノードとの間にインダクタを連結し、前記出力ノードから変調

10

20

30

40

50

回路へのフィードバック経路を提供し、前記変調回路がランプ波発生器を含む。本実施形態は、以下の任意の組み合わせを特徴とし得る。すなわち、

- ・前記変調回路は、前記プリント基板に含まれる。

- ・前記変調回路は、常時オン時間または常時オフ時間変調回路である。

- ・前記ランプ波発生器は、前記集積回路に含まれる。

- ・前記ランプ波発生器を少なくとも一部は前記インダクタの特性に基づいてトリムすることをさらに備える。

- ・前記ランプ波発生器は、いずれかの上記実施形態のランプ波発生器である。

#### 【0019】

いくつかの実施形態は、直流 - 直流変換器の使用のための、以下を含む方法について開示されている。すなわち、入力ノードにおいて入力電力を受信し、インダクタヘスイッチを通して電力を提供し、出力電圧が出力キャパシタ両端に生じるように出力キャパシタにエネルギーを格納し、前記出力電圧で出力電力を出力ノードへ提供し、前記出力電圧を変調回路へ提供し、出力キャパシタとは独立したリップル電圧を生成し、前記リップル電圧を前記変調回路へ提供し、前記スイッチを、前記変調回路の出力に少なくとも一部は基づいて変調する。本実施形態は、以下の任意の組み合わせを特徴とし得る。すなわち、

- ・前記リップル電圧、基準電圧、および前記出力電圧のうち少なくとも 2 つを比較することをさらに含む。

- ・電流源を、少なくとも一部は、前記インダクタのインダクタンスに基づいてトリムすることをさらに備える。

- ・前記リップル電圧は、前記インダクタを通る電流をエミュレートするように構成されたランプ波発生器により生成される。

#### 【0020】

いくつかの実施形態は、直流 - 直流 (DC - DC) 電力変換器パッケージについて開示されており、この直流 - 直流電力変換器パッケージは、少なくとも 1 つのプリント基板 (PCB) に埋め込まれた集積回路 (IC) チップであって、ドライバを備える IC チップと、前記チップ埋め込みパッケージの外部に位置決めされ、前記チップ埋め込みパッケージの表面に連結されたインダクタと、前記インダクタへ提供される電流が限界を超えた場合を検出するように構成された過電流保護回路とを備える。本実施形態は、以下の任意の組み合わせを特徴とし得る。すなわち、

- ・前記過電流保護回路は、少なくとも一部が集積回路間または電源管理バスコマンドに基づいて調整またはトリムされるように構成された電流源を備える。

- ・前記インダクタの飽和インダクタンスが前記限界を超えるか、かつ、前記限界を 50 % 未満超える。

- ・前記限界は、最大規定 DC 電流仕様プラス最大交流電流リップル仕様を 50 % 未満超過する。

#### 【0021】

ここに開示されたいくつかの実施形態は、直流 - 直流 (DC - DC) 電力変換器パッケージに関し、この直流 - 直流電力変換器パッケージは、少なくとも 1 つのプリント基板 (PCB) に埋め込まれた集積回路 (IC) チップであって、ドライバを備える前記 IC チップと、前記チップ埋め込みパッケージの外部に位置決めされ、前記チップ埋め込みパッケージの表面に連結されたインダクタと、集積回路間または電源管理バスとを備える。本実施形態は、以下の任意の組み合わせを有し得る。すなわち、

- ・前記集積回路間または電源管理バスは少なくとも 1 つの電流源に連結され、プロトコルコマンドを提供して前記電流源を調節またはトリムするように構成されている。

- ・前記集積回路間または電源管理バスは少なくとも 1 つの電流源に連結され、プロトコルコマンドを提供して比較器へ提供される基準値を設定または調節するように構成されている。

- ・前記集積回路間または電源管理バスは、前記 DC - DC 電力変換器パッケージのオンまたはオフ、前記 DC - DC 電力変換器パッケージの低電力またはスリープモードの変更、

10

20

30

40

50

前記 D C - D C 電力変換器パッケージの電流設定についての情報の読み出し、前記 D C - D C 電力変換器パッケージについて診断および / または技術情報の読み出し、前記 D C - D C 電力変換器パッケージにより提供される出力電圧の設定または変更、の少なくとも 1 つを実施するための指示を含むプロトコルを通信するように構成されている。

- ・集積回路間実装品の上に配線層として電源管理プロトコルを実施する。

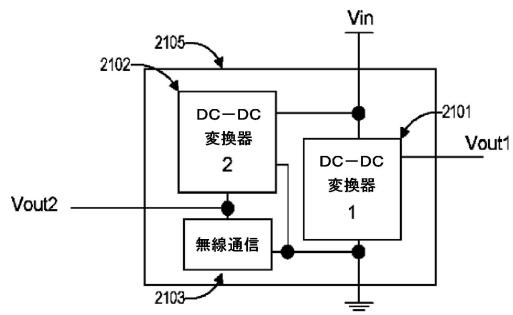

【 0 0 2 2 】

ここに開示されたいくつかの実施形態は、以下を備える電力変換器を特徴とする。すなわち、プリント基板 ( P C B ) ( 前記プリント基板は、下面および上面を有する下部プリント基板 ( P C B ) 部分と、下面および上面を有する上部プリント基板 ( P C B ) 部分とを備える ) と、前記下部 P C B 部分の前記上面と前記上部 P C B 部分の前記下面との間の埋め込み型回路 ( 1 つまたは複数のドライバ信号を生成するように構成されたドライバと、前記 1 つまたは複数のドライバ信号により駆動されるように構成された 1 つまたは複数のスイッチとを備える前記埋め込み型回路 ) と、前記上部 P C B 部分を通じて延びる 1 つまたは複数のビアと、前記上部 P C B 部分の前記上面に位置決めされたインダクタとを備え、前記 1 つまたは複数のビアは、前記インダクタおよび前記埋め込み型回路と電気的に連結され、前記インダクタのフットプリントが前記埋め込み型回路のフットプリントに少なくとも部分的に重なる。本実施形態は、以下の任意の組み合わせを有し得る。すなわち、

- ・前記電力変換器は、前記電力変換器の入力部と出力部との間の直接的な電気的接続を絶縁するように構成された絶縁トポロジで構成される。

- ・前記絶縁トポロジは、フライバックトポロジ、順方向変換器トポロジ、 2 トランジスタ順方向、 L L C 共振変換器、プッシュプルトポロジ、フルブリッジ、ハイブリッド、 P W M 共振変換器、およびハーフブリッジトポロジの少なくとも 1 つを備える。

- ・前記第 1 インダクタを通る変更電流が前記第 2 インダクタにおける変更電流を誘発するように構成された前記第 1 インダクタおよび前記第 2 インダクタを含む変圧器をさらに備える。

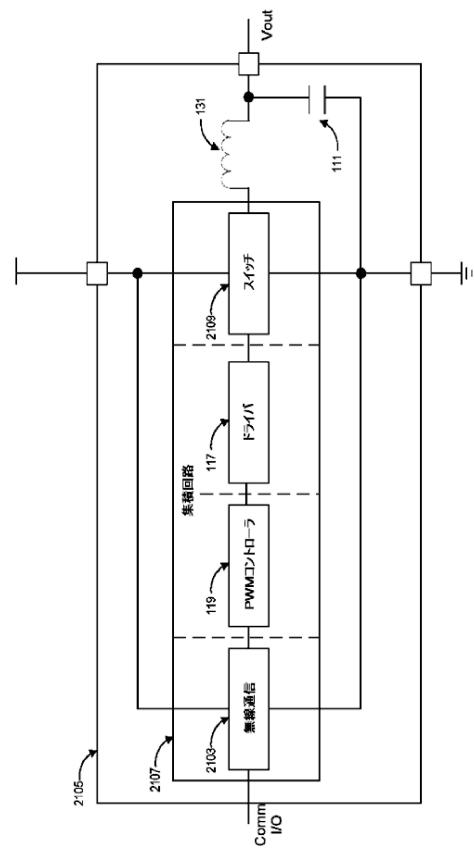

- ・前記埋め込み型回路と同じパッケージにおける無線通信システムをさらに備える。

- ・前記電力変換器の出力は、前記無線信号システムにより受信される無線信号に応じて調整されるように構成される。前記インダクタを通る電流リップルをエミュレートする信号を生成するように構成されたランプ波発生器を有するフィードバックシステムをさらに備え、前記フィードバックシステムは、前記無線通信システムにより受信される無線信号に応じてトリムまたは調整されるように構成された電流源を備える。

- ・前記埋め込み型回路は前記無線通信システムを備える。

- ・前記電力変換器の出力を調整するための制御信号を受信するように構成された通信インターフェースをさらに備える。

- ・前記通信インターフェースは電源管理バス ( P M B U S ) を備える。

- ・前記通信インターフェースは、集積回路間 ( I 2 C ) プロトコルを実施するように構成されている。

- ・前記インダクタを通る電流リップルをエミュレートする信号を生成するように構成されたランプ波発生器を有するフィードバックシステムをさらに備え、前記フィードバックシステムは、前記通信インターフェースを介して受信されるコマンドに応じて前記ランプ波発生器をトリムするように構成されている。

- ・前記埋め込み型回路は、 1 つまたは複数の P W M 信号を生成するように構成されたパルス幅変調器 ( P W M ) コントローラを備え、前記 P W M コントローラは、前記ドライバと連結され、前記ドライバは、少なくとも一部は前記 P W M 信号に基づいて 1 つまたは複数のドライバ信号を生成するように構成される。

- ・前記インダクタは、定格電流を有し、前記インダクタは、飽和定格を有し、前記飽和定格は、前記定格電流よりも 5 0 % 未満高い。

- ・前記インダクタは、定格電流を有し、前記インダクタは、飽和定格を有し、前記飽和定格は、前記定格電流よりも 2 0 % 未満高い。

- ・前記インダクタを通る電流が前記飽和定格を上回るのを防止するように構成された過電

10

20

30

40

50

流保護回路をさらに備える。

・過電流条件の検出に応じて前記1つまたは複数のスイッチの少なくとも1つを開くように構成された過電流保護回路さらに備える。

・前記電力変換器は、直流 - 直流 (DC - DC) 電力変換器である。

・前記電力変換器は、交流 - 直流 (AC - DC) 電力変換器である。

・電流源を有するフィードバックシステムをさらに備え、前記電流源は、前記無線通信システムにより受信される無線信号に少なくとも一部が基づいてトリムまたは調整されるように構成されている。

・前記インダクタを通る電流の指標を提供するように構成された過電流保護システムをさらに備え、前記過電流システムは電流源を備え、前記電流源は、前記無線通信システムにより受信される無線信号に少なくとも一部が基づいてトリムまたは調整されるように構成されている。

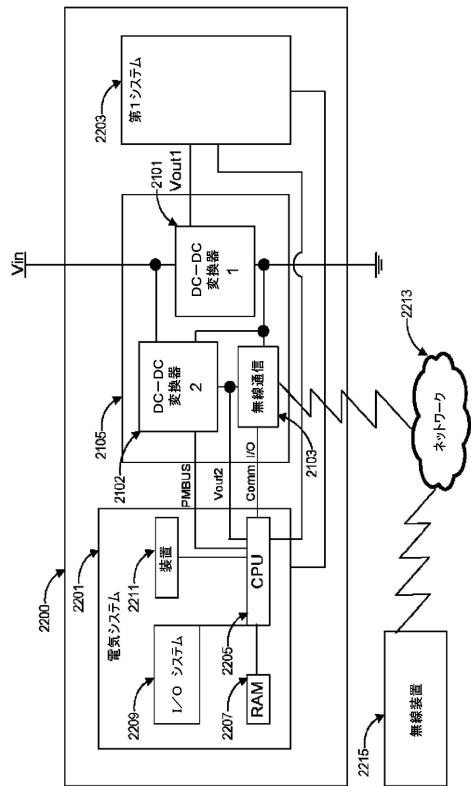

#### 【0023】

ここに開示されたいくつかの実施形態は、以下を備える品目を特徴とし、すなわち、前記パラグラフの前記電力変換器と、電力を用いる物理作用を実施するように構成された第1システムと、前記第1システムを制御するように構成された電気システムとを備え、前記電力変換器は、前記第1システムおよび前記電気システムの一方または双方に電力を提供するように構成され、前記電気システムは、前記電力変換器の前記埋め込み型回路と同じパッケージにある前記無線通信システムにより受信される無線信号に少なくとも一部は基づいて前記第1システムを制御するように構成されている。いくつかの実施形態において、前記品目はインターネット・オブ・シングス装置である。いくつかの実施形態は、以下を備える電力供給システムを特徴とする。すなわち、複数の電力変換器であって、前記パラグラフの電力変換器にそれぞれ応じた電力変換器と、複数のPWM信号を生成するように構成された共用パルス幅変調器 (PWM) コントローラとを備え、前記PWMコントローラは、前記複数の電力変換器の前記ドライバと連結されて、前記複数のPWM信号を前記電力変換器の前記対応するドライバへ送り、前記ドライバは、少なくとも一部は前記PWM信号に基づいて前記1つまたは複数のドライバ信号を生成するように構成されている。いくつかの実施形態は、電力供給システムを特徴とし、この電力供給システムは、請求項1の電力変換器に係る第1電力変換器と、前記第1電力変換器と並列に連結された第2電力変換器とを備える。前記電力供給システムは、電流平衡のために前記第1電力変換器の出力と前記第2電力変換器の出力とを調節するように構成された制御システムを特徴とし得る。

#### 【0024】

ここに開示されたいくつかの実施形態は、以下を備える電力変換器を特徴とする。すなわち、下面および上面を有する下部プリント基板 (PCB) 部分と、下面および上面を有する上部プリント基板 (PCB) 部分とを有するプリント基板 (PCB) と、入力電圧を受信するように構成された入力ポートと、前記入力電圧とは異なる出力電圧を提供するように構成された出力ポートと、前記下部PCB部分の前記上面と前記上部PCB部分の前記下面との間の埋め込み型回路であって、前記入力ポートに連結され、前記入力電圧を変化させるように構成された埋め込み型回路と、前記上部PCB部分を通って延びるビアと、前記上部PCB部分の前記上面に位置決めされたインダクタまたはキャパシタとを備え、前記1つまたは複数のビアは、前記インダクタまたはキャパシタおよび前記埋め込み型回路と電気的に連結され、前記インダクタまたはキャパシタのフットプリントが前記埋め込み型回路のフットプリントに少なくとも部分的に重なる。本実施形態は、以下の任意の組み合わせを有し得る。すなわち、

・前記インダクタは、前記上部PCB部分の前記上面に位置決めされ、前記1つまたは複数のビアは、前記インダクタおよび前記埋め込み型回路と電気的に連結され、発生器前記インダクタのフットプリントが前記埋め込み型回路のフットプリントに少なくとも部分的に重なり、前記埋め込み型回路は、1つまたは複数のドライバ信号を生成するように構成されたドライバと、前記1つまたは複数のドライバ信号により駆動されるように構成され

10

20

30

40

50

た 1 つまたは複数のスイッチとを備える。

- ・前記電力変換器は、直流 - 直流 ( D C - D C ) 変換装置である。

- ・前記電力変換器は、交流 - 直流 ( A C - D C ) 変換装置である。

- ・前記第 1 インダクタを通る変更電流が前記第 2 インダクタにおける変更電流を誘発するように構成された前記第 1 インダクタおよび前記第 2 インダクタを含む変圧器をさらに備える。

- ・前記埋め込み型回路は、交流電流 ( A C ) 入力電圧をパルス D C 電圧に変更するように構成された整流回路を備える。

- ・前記パルス D C 電圧をより安定した D C 電圧に平滑化するように構成された平滑回路を備え、前記平滑回路は、前記上部 P C B 部分の上側の上部に位置決めされたキャパシタまたは前記インダクタを備える。

- ・前記整流回路は、1 つまたは複数のスイッチを備える。

- ・前記整流回路は、ダイオードブリッジを備える。

#### 【 0 0 2 5 】

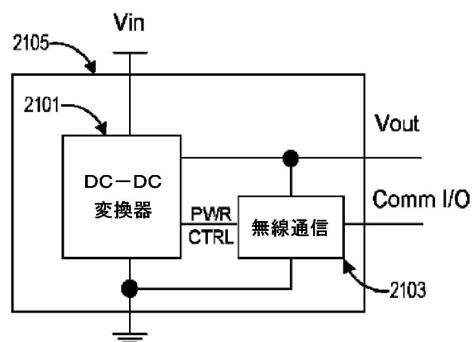

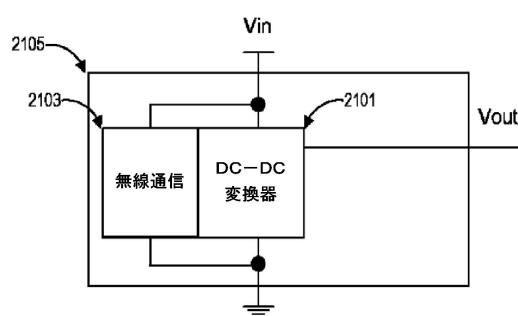

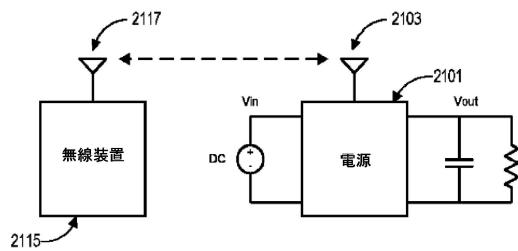

ここに開示されたいくつかの実施形態は、直流 - 直流 ( D C - D C ) 電力変換器を特徴とし、この直流 - 直流電力変換器は、下面および上面を有する下部プリント基板 ( P C B ) 部分と、下面および上面を有する上部プリント基板 ( P C B ) 部分と、前記下部 P C B 部分の前記上面と前記上部 P C B 部分の前記下面との間の埋め込み型回路とを備え、前記埋め込み型回路は、P W M 信号を生成するように構成されたパルス幅変調器 ( P W M ) コントローラと、前記 P W M 信号を受信するように構成され、1 つまたは複数のドライバ信号を生成するように構成されたドライバと、前記 1 つまたは複数のドライバ信号の少なくとも 1 つにより駆動されるように構成された第 1 スイッチと、前記 1 つまたは複数のドライバ信号の少なくとも 1 つにより駆動されるように構成された第 2 スイッチと、前記上部 P C B 部分を通じて延びる 1 つまたは複数のビアと、前記上部 P C B 部分の前記上面に位置決めされたインダクタとを備え、前記 1 つまたは複数のビアは、前記インダクタおよび前記埋め込み型回路と電気的に連結され、発生器前記インダクタのフットプリントが前記埋め込み型回路のフットプリントに少なくとも部分的に重なり、前記埋め込み型回路と同じパッケージにおける無線通信システムと、前記無線通信は、前記 P W M コントローラ、または、前記第 1 スイッチの少なくとも 1 つへ信号を提供して前記 D C - D C 変換器の出力に影響を及ぼすように構成されている。

#### 【 0 0 2 6 】

ここに開示されたいくつかの実施形態は、直流 - 直流 ( D C - D C ) 電力を特徴とし、この直流 - 直流電力は、プリント基板 ( P C B ) の内側に位置決めされた集積回路を備え、前記集積回路は、ドライバからの第 1 信号により駆動されるように構成された第 1 室化ガリウム ( G a N ) スイッチと、前記ドライバからの第 2 信号により駆動されるように構成された第 2 G a N スイッチと、前記集積回路のフットプリントと少なくとも部分的に重なるフットプリントを有するように前記集積回路に位置決めされたインダクタと、前記インダクタを前記 G a N スイッチに電気的に連結するビアとを備える。いくつかの実施形態は以下を含んでいてもよく、すなわち、前記第 1 G a N スイッチが第 1 エンハンスト室化ガリウム ( e G a N ) スイッチであり、前記第 2 G a N スイッチが第 2 e G a N スイッチである。

#### 【 図面の簡単な説明 】

#### 【 0 0 2 7 】

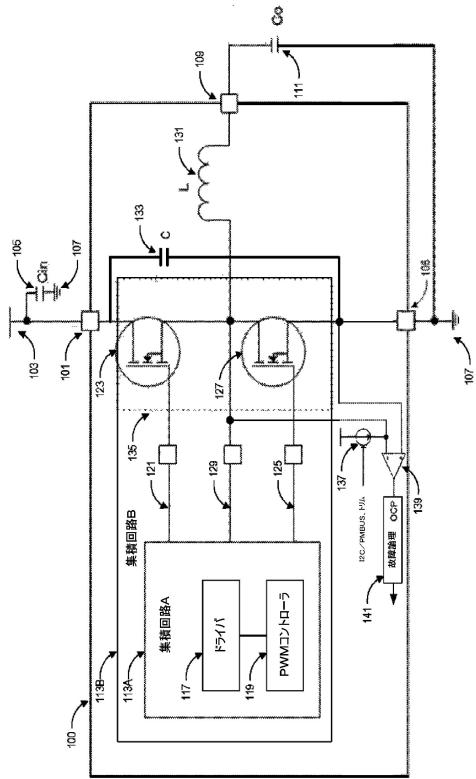

【 図 1 】図 1 は、チップ埋め込み型 D C - D C 変換器パッケージの例示的回路レベルの回路図を示す。

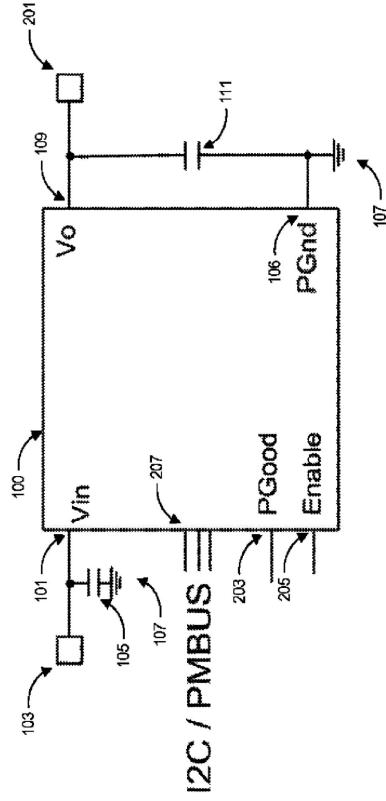

【 図 2 】図 2 は、チップ埋め込み型 D C - D C 変換器パッケージの例示的実施形態のパッケージレベルの回路図を示す。

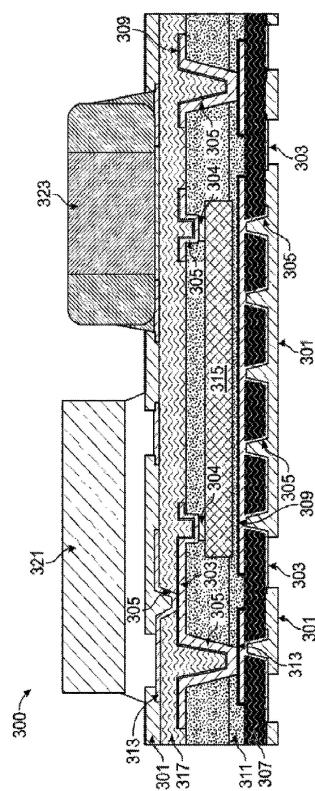

【 図 3 】図 3 は、例示的チップ埋め込み型 D C - D C 変換器の断面図を示す。

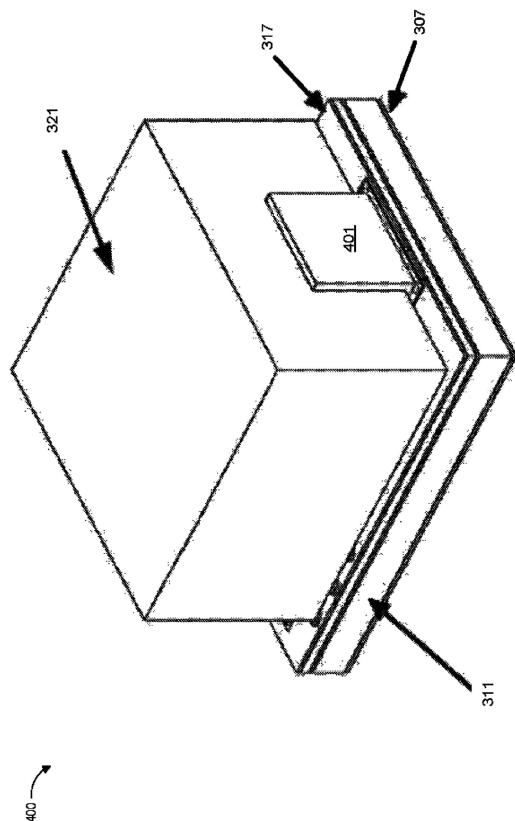

【 図 4 A 】図 4 A は、積層型インダクタを有する例示的チップ埋め込み型 D C - D C 変換器の斜視図を示す。

10

20

30

40

50

【図 4 B】図 4 B は、積層型インダクタを有する例示的なレンダリングされたチップ埋め込み型 DC - DC 変換器の逆斜視図を示す。

【図 4 C】図 4 C は、埋め込み積層型インダクタを有する例示的チップ埋め込み型 DC - DC 変換器の側面図を示す。

【図 4 D】図 4 D は、埋め込み型インダクタを有する例示的チップ埋め込み型 DC - DC 変換器の側面図を示す。

【図 5】図 5 は、例示的チップ埋め込み型 DC - DC 変換器の透過斜視図 500 を示す。

【図 6】図 6 は、例示的チップ埋め込み型 DC - DC 変換器の底面図を示す。

【図 7 A】図 7 A は、記憶装置において使用される DC - DC 変換器の一例を示す。

【図 7 B】図 7 B は、記憶装置において使用されるチップ埋め込み型 DC - DC 変換器の一例を示す。 10

【図 8 A】図 8 A は、回路基板における DC - DC 変換器の例示的適用を示す。

【図 8 B】図 8 B は、回路基板におけるチップ埋め込み型 DC - DC 変換器の例示的適用を示す。

【図 9】図 9 は、チップ埋め込み型 DC - DC 変換器を作成し使用するための例示的方法のフローチャートを示す。

【図 10】図 10 は、チップ埋め込み型 DC - DC 変換器を使用するデュアルバックコンバータ用の例示的デュアルインダクタ設計を示す。

【図 11 A】図 11 A は、デュアルバックコンバータにおける埋め込み型チップ用の第 1 例示的レイアウト設計を示す。 20

【図 11 B】図 11 B は、デュアルバックコンバータにおける埋め込み型チップ用第 2 例示的レイアウト設計を示す。

【図 11 C】図 11 C は、デュアルバックコンバータにおける埋め込み型チップ用第 3 例示的レイアウト設計を示す。

【図 11 D】図 11 D は、デュアルバックコンバータにおける埋め込み型チップ用第 4 例示的レイアウト設計を示す。

【図 12】図 12 は、チップ埋め込み型 DC - DC 変換器を含むデュアルバックコンバータの例示的回路レベル回路図を示す。

【図 13 A】図 13 A は、チップ埋め込み型 DC - DC 変換器を含む DC - DC 変換器の例示的回路レベルの回路図を示す。 30

【図 13 B】図 13 B は、チップ埋め込み型 DC - DC 変換器を含む DC - DC 変換器の例示的回路レベルの回路図を示す。

【図 14】図 14 は、外部リップル電圧フィードバック回路を有する例示的チップ埋め込み型 DC - DC 変換器を示す。

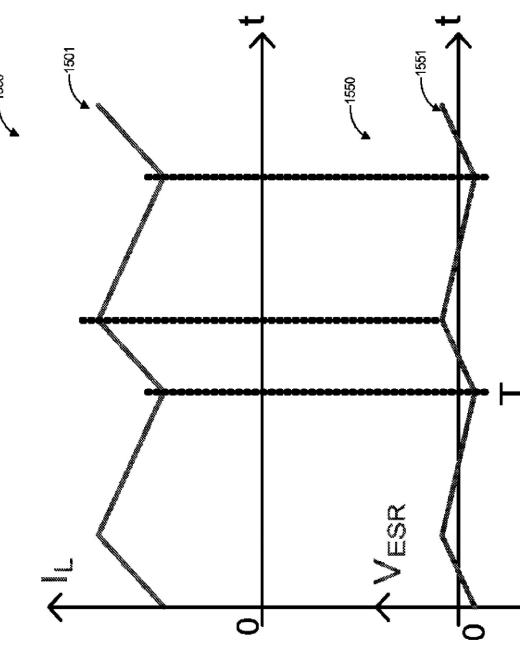

【図 15】図 15 は、時間に対するインダクタ電流  $I_L$  および時間に対する等価直列抵抗電圧  $V_{ESR}$  (リップル電圧とも称する) の例示的グラフを示す。

【図 16】図 16 は、外部リップル電圧フィードバック回路を有する例示的チップ埋め込み型 DC - DC 変換器を示す。

【図 17】図 17 は、内部リップル電圧フィードバック回路を有する例示的チップ埋め込み型 DC - DC 変換器を示す。 40

【図 18】図 18 は、ランプ波発生器の例示的回路レベルの回路図を示す。

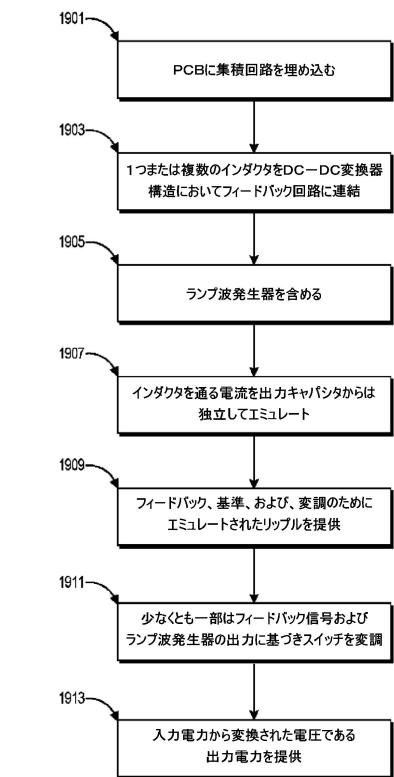

【図 19】図 19 は、DC - DC 変換器を作成し使用するための例示的方法を示す。

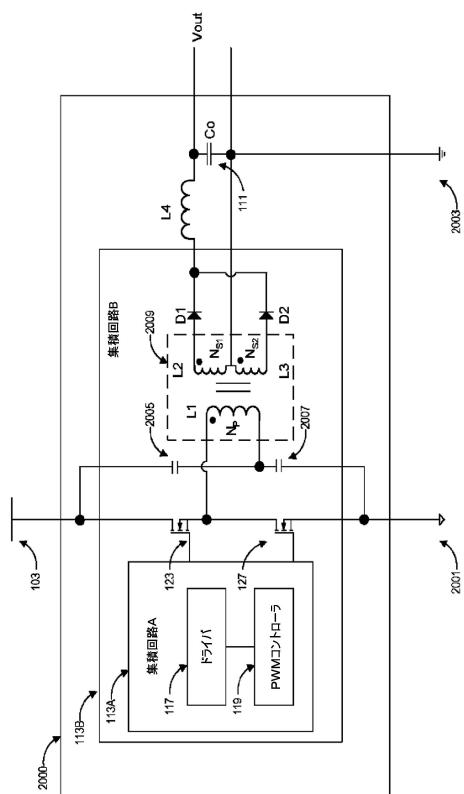

【図 20】図 20 は、絶縁型トポロジを有するチップ埋め込み型 DC - DC 変換器パッケージの例示的回路レベルの回路図を示す。

【図 21 A】図 21 A は、パッケージにおける無線通信システムを有する例示的 DC - DC 変換器を示す。

【図 21 B】図 21 B は、パッケージにおける無線通信システムを有する例示的 DC - DC 変換器を示す。

【図 21 C】図 21 C は、無線通信システムと 2 つの DC - DC 変換器とを備える例示的パッケージを示す。 50

【図21D】図21Dは、外部無線装置と通信するように構成された例示的な無線利用可能な電源を示す。

【図21E】図21Eは、パッケージにおける無線通信システムを有する例示的DC-D C変換器を示す。

【図22】図22は、例示的インターネット・オブ・シングス(IoT)装置を示す。

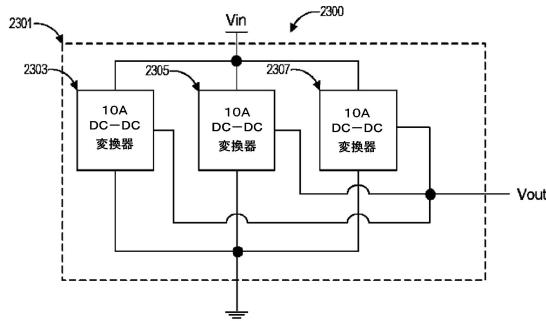

【図23A】図23Aは、多重DC-D C変換器を含む例示的DC-D C変換器システムを示す。

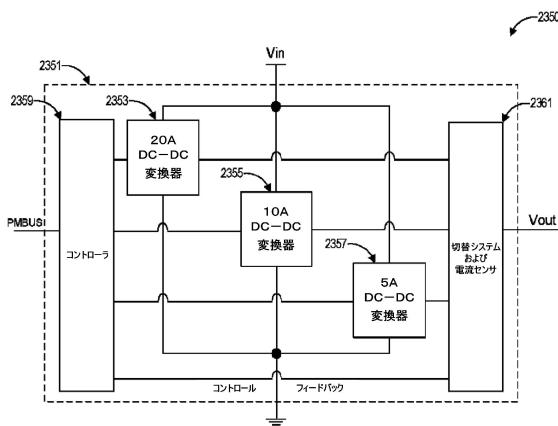

【図23B】図23Bは、多重DC-D C変換器を含む例示的DC-D C変換器システムを示す。

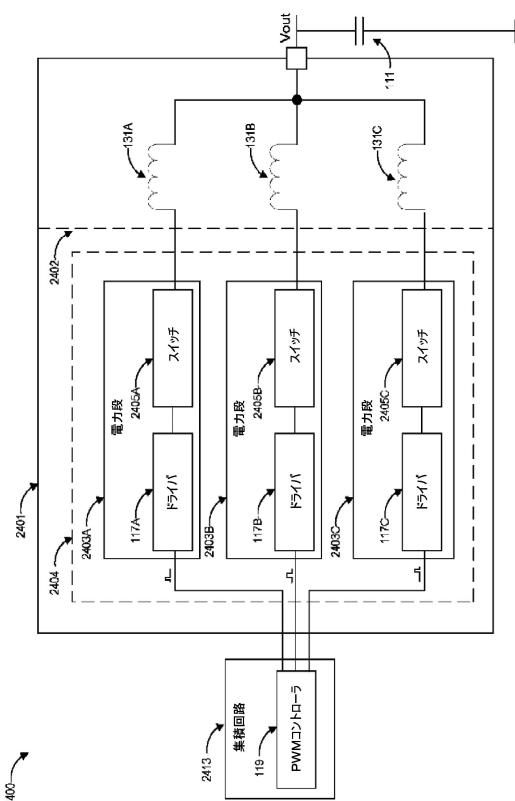

【図24A】図24Aは、多重電力段を有するDC-D C変換器を示す。

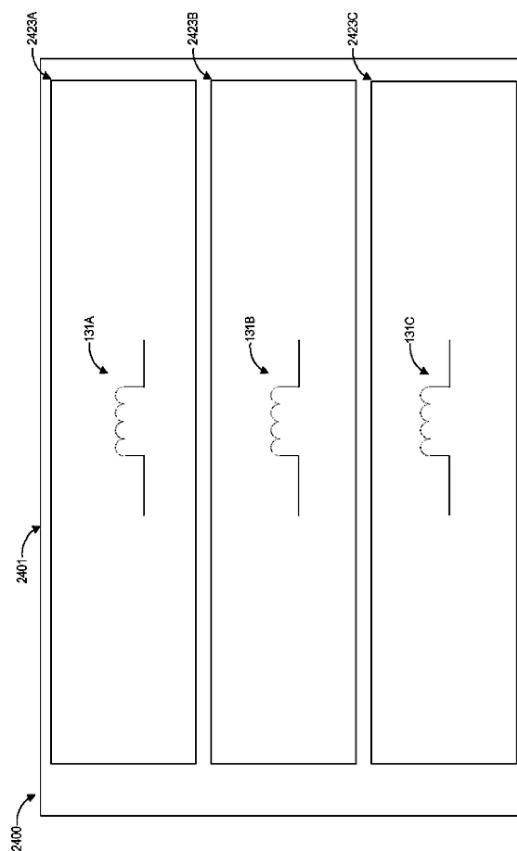

【図24B】図24Bは、DC-D C変換器におけるインダクタの例示的レイアウトを示す。

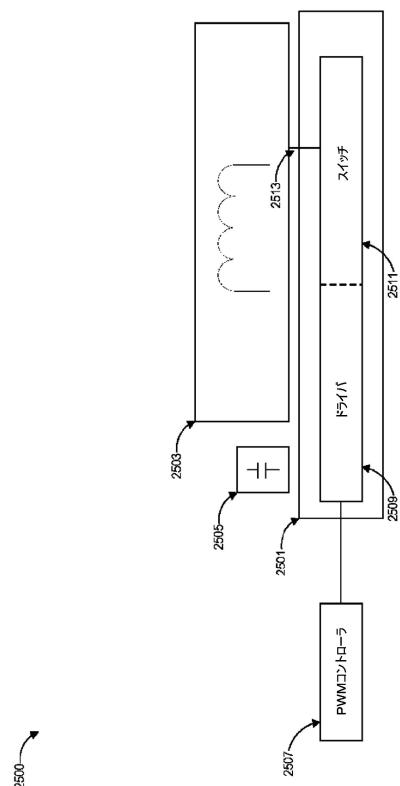

【図25】図25は、DC-D C変換器の例示的側面図を示す。

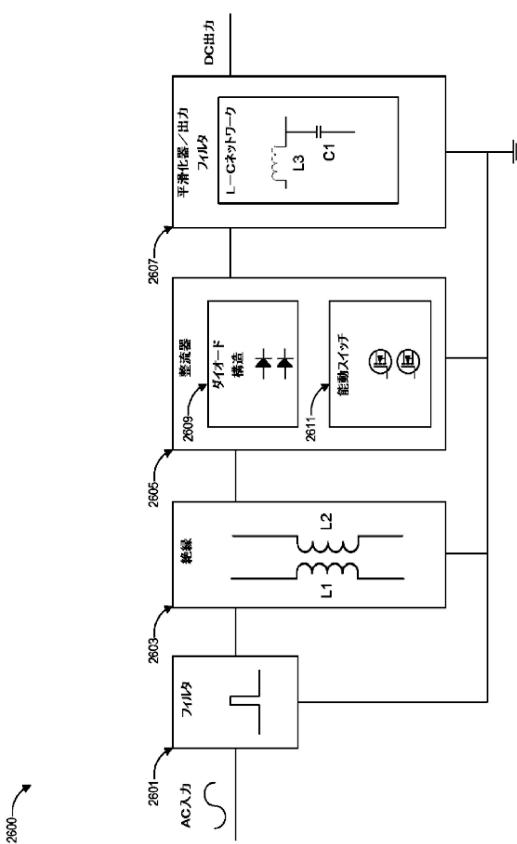

【図26A】図26Aは、AC-D C変換器の例示的ブロック図を示す。

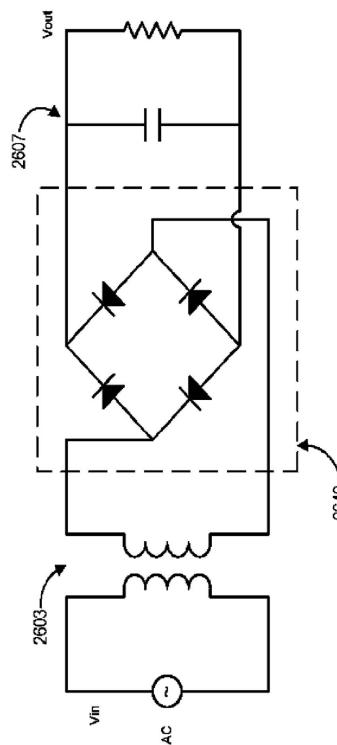

【図26B】図26Bは、例示的AC-D C変換器を示す。

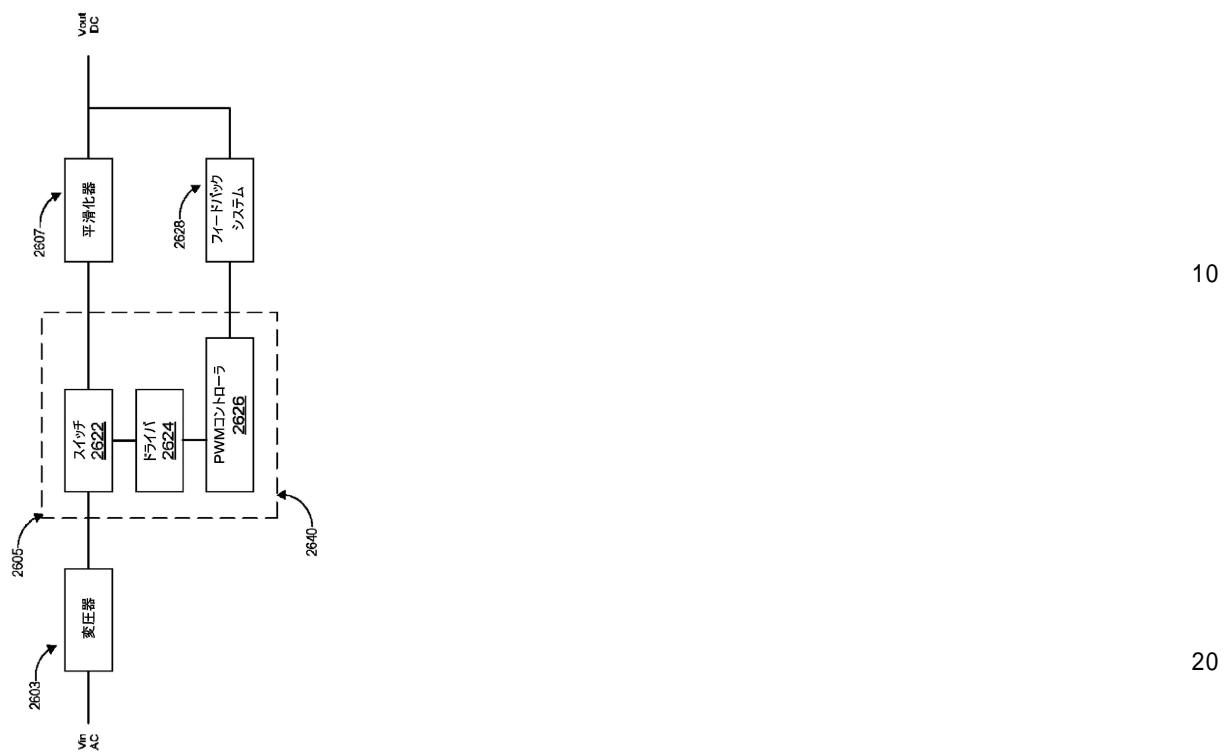

【図26C】図26Cは、例示的AC-D C変換器を示す。

【発明を実施するための形態】

【0028】

#### 序論

直流(DC)-直流(DC-D C)変換器は、電子回路の一種である。DC-D C変換器は、第1電圧の入力電力を受信することができ、かつ、第2電圧の出力電力を提供することができる。DC-D C変換器としては、例えば、ブーストコンバータ(入力電圧よりも高い出力電圧を有することができる)、バックコンバータ(入力電圧よりも低い出力電圧を有することができる)、バック-ブーストコンバータ、および種々のその他のトポロジが挙げられる。

【0029】

DC-D C変換器は、非理想的な構成要素特性により影響を受けるものもある。これらは、ワイヤボンドおよびクワッド・フラット・リード端子なし(QFN)パッケージ、パワークワッド・フラット・リード端子なし(PQFN)パッケージ、デュアルフラット・リードなし(DFN)パッケージ、マイクロリードフレーム(MLF)パッケージなどのリードフレームパッケージなどの構成要素により引き起こされる寄生インダクタンス、寄生容量、および/または寄生抵抗を含み得る。さらに、DC-D C変換器の内部構成要素間の、例えば、ドライバからスイッチへの相互接続も寄生効果に寄与し得る。これらの寄生効果は、DC-D C変換器の効率および/または切替速度を制限し得る。パッケージは、DC-D C変換器レベルパッケージのことであってもよい。パッケージは、DC-D C変換器に含まれる1つまたは複数のICを封止してもよい。パッケージは、DC-D C変換器における構成要素のための支持および保護を提供してもよく、パッケージは、DC-D C変換器に接続するための電気接触部を提供してもよい。種々の実施形態において、パッケージは、パッケージ内に備えられた、および/または、外部からパッケージと連結された1つまたは複数のインダクタおよび/またはキャパシタを備えていてもよい。

【0030】

この開示は、高集積ソリューションの例を含み、高集積ソリューションでは、DC-D C変換器は、より効率的に切替可能であり、比較的高い周波数で切替可能であり、および/または低減されたパッケージフットプリントを有する向上した性能を提供する。パルス幅変調器コントローラ、ドライバ、および/または1つまたは複数のエンハンストヒ化ガリウムスイッチ(エンハンスマントモードヒ化ガリウムスイッチおよびeGaN(登録商標)FETとしても知られている)などの多くのDC-D C構成要素を集積する集積回路チップがパッケージに含まれていてもよい。集積回路は、プリント基板に埋め込みされていてもよく、または、プリント基板間に埋め込みされていてもよい。パッケージは、パッケージフットプリントを低減するために垂直設計のインダクタおよび/またはキャパシタ

10

20

30

40

50

を含んでいてもよい。ある種の特徴は、比較的高い切替速度および／または比較的高い効率を達成することを阻止してしまう寄生効果を低減することができる。比較的高い切替速度を効率的に達成することにより、インダクタサイズは低減され得る。D C - D C 変換器は、比較的高い周波数で動作することができ、より良好な過渡性能を提供することができ、比較的低いリップルを有すことができ、より少数のキャパシタを使用することができ、および／または全体のフットプリントを低減することができる。

#### 【0031】

序論を提供するために、ある種の態様、利点、および新規の特徴を紹介した。必ずしも序論のこのような態様、利点、および新規の特徴の全てが任意の特定の実施形態に基づいて達成されるわけではないことが理解される。したがって、1つまたは複数の態様、利点、および新規の特徴は、ここに記載のその他の態様、利点、新規の特徴を必ずしも達成せずに達成されてもよい。全ての態様、利点、および新規の特徴が序論において開示されているわけではないことが分かる。

#### 【0032】

##### 例示的な概略図

図1は、チップ埋め込み型D C - D C 変換器パッケージ100の例示的回路レベルの回路図を示す。回路図は、電力入力ポート101と、電源103と、入力キャパシタ105と、アースポート106と、アース107と、電圧出力ポート109と、出力キャパシタ111と、集積回路(I C)チップ113Aと、代替I C113Bと、ドライバ117と、パルス幅変調器(PWM)コントローラ119と、第1電気経路121と、第1スイッチ(例えば、第1エンハンスト窒化ガリウム(eGaN)スイッチ)123と、第2電気経路125と、第2スイッチ(例えば、第2eGaNスイッチ)127と、第3電気経路129と、インダクタ131と、ACバイパスキャパシタ133とを示す。破線135は、スイッチ123、127の代替の別個のパッケージングを示す。スイッチ123、127は、電力スイッチ、スイッチングFET、および／またはスイッチングトランジスタとも称される。この回路図は、電流源137、比較器139、故障論理および／または過電流保護回路141も示す。

#### 【0033】

チップ埋め込み型D C - D C 変換器パッケージ100は、電力入力ポート101を介して電源103と連結されてもよく、かつ、入力キャパシタ105を介してアース107とも連結されてもよい。チップ埋め込み型D C - D C 変換器パッケージ100は、入力キャパシタ111を介してアース107と連結されてもよい電力入力ポート109も備えていてもよい。チップ埋め込み型D C - D C 変換器パッケージ100は、アース107と連結されたアース基準ポート106も備えていてもよい。

#### 【0034】

チップ埋め込み型D C - D C 変換器パッケージ100は、埋め込み型集積回路(I C)チップ113Aまたは113Bを含むプリント基板(PCB)を備えていてもよい。I Cは、ドライバ117および／またはパルス幅変調器(PWM)コントローラ119を備えていてもよい。例えば、第1電気経路121は、I Cを第1eGaNスイッチ123のゲートに連結する。第2電気経路125は、I Cを第2eGaNスイッチ127のゲートに連結する。第3電気経路129は、I Cを第1eGaNスイッチ123のソース、第2eGaNスイッチ127のドレイン、およびインダクタ131に連結する。インダクタ131は、電圧出力ポート109と連結されてもよい。ACバイパスキャパシタ133は、第1eGaNスイッチ123のドレインから第2eGaNスイッチ127のソースへ連結されてAC信号をアース107に短絡してもよい。

#### 【0035】

図1は、ドライバ117およびPWMコントローラ119を、I C113Aの一部として示すが、種々の実施形態において、I Cは、PWMコントローラ119またはドライバ117の一方を含んでいてもよく、一方、PWMコントローラ119およびドライバ117の他方は、個別にI C113Aに連結されている。いくつかの実施形態において、eG

10

20

30

40

50

a Nスイッチ123、127または一対のe G a Nスイッチ123、127の1つは、各電気経路121、125、および/または129と共にI C 113Aに集積されてもよい。I C 113Aは、半導体であってもよい。I C 113Aは、シリコン、ヒ化ガリウム、窒化ガリウム、e G a N、または他のI I I - V族半導体であってもよい。したがって、任意の集積された構成要素も、I C 113Aと同じまたは同様の材料で形成されていてもよい。スイッチ123、127、電気経路121、129、125、ドライバ、117、およびP W Mコントローラ119も、I C 113Aと同じまたは同様の材料で形成されていてもよい。

#### 【0036】

一対のスイッチ123、127は、モノリシックのe G a N電界効果トランジスタ(F E T)であってもよい。いくつかの実施形態において、一対のスイッチ123、127は、個別の装置であってもよく、2つの独立型e G a N F E Tを含む。いくつかの実施形態において、スイッチ123、127は、金属酸化物電界効果トランジスタ(M O S F E T)である。種々の他の複数のまたは種類のスイッチは、種々の他の実施形態において使用されてもよい。複数の実施形態はスイッチ123、127をe G a Nスイッチとして説明しているが、他の適切な材料を、e G a Nの代替としてまたはe G a Nに加えて使用してもよい。

10

#### 【0037】

いくつかの実施形態において、電気経路121、129、125は、銅ピラーなどのピア、配線、および/または低い寄生効果(例えば、低い寄生インダクタンス、低い寄生抵抗、および/または低い寄生容量)を有する他の電気経路によって実施されてもよい。ワイヤボンドは、比較的高い寄生効果(例えば、比較的高い寄生インダクタンス、比較的高い寄生抵抗、および/または比較的高い寄生容量)を有していてもよい。

20

#### 【0038】

電力入力ポート101、アースポート106、および電圧出力ポート109を含むポートは、低い寄生効果(例えば、低い寄生インダクタンス、低い寄生抵抗、および/または低い寄生容量)を有するパッド、ピン、または他の電気導体として実施されてもよい。ポートは、マザーボード、P C B、などの別の装置における配線と連結されるように設計されてもよい。

30

多くの変形例が可能である。いくつかの実施形態において、バイパスキャパシタ133は省略されてもよい。いくつかの実施形態は、異なるインダクタ、キャパシタ、磁石、および/または共振構造を特徴としてもよい。図1の例示的な回路図に示す種々の構成要素は、D C - D C変換器を形成するが、D C - D C変換器は、他の変形例を有していてもよい。ここに開示される教示は、他の変形例のD C - D C変換器に拡大し得ることが分かる。

#### 【0040】

例えば、D C - D C変換器110は、電力信号を電力入力ポート101を介して電源103から受信し得る。電力信号は、ノイズの在る交流電流(A C)信号構成要素をフィルタするために減結合キャパシタとして作用し得るシャント入力キャパシタ105を通してフィルタリングされ得る。電力信号は、一対のスイッチ123、127の第1スイッチ123のドレインに提供される。

40

#### 【0041】

ドライバ117は、電気経路121を介して第1制御信号を第1スイッチ(例えば、e G a Nスイッチ)123のゲートへ提供する。また、ドライバは、電気経路125を介して第2制御信号を第2スイッチ(例えば、e G a Nスイッチ)127のゲートへ提供する。制御信号を用いて、ドライバは、スイッチ123、127を交互にオンおよびオフすることができる。ドライバは、第1スイッチ123のオン/オフ状態は第2スイッチ127のオン/オフ状態の逆であるように信号を制御してもよい。制御信号のオン/オフデューティサイクルは、P W Mコントローラ119によって設定されてもよい。P W Mコントローラ119によって設定されてもよい。

50

ーラ 119 は、ドライバに提供される PWM 信号を介してパルス幅または周期を制御してもよい。

【 0042 】

スイッチ 123、127、I C 113A ( 例えば、PWM コントローラ 119 および / またはドライバ 117 を含む ) 、および、インダクタ 131 は、非絶縁同期電力変換器または電力段の一部を形成するように配置されてもよい。ドライバ 117 が第 1 スイッチ 123 を駆動してオンにし、第 2 スイッチ 127 を駆動してオフにする場合、電力は、電源 103 からインダクタ 131 および / またはキャパシタ 111 などのエネルギー蓄積回路に提供されてもよく、電圧出力ポート 109 における DC 出力電圧を上昇させる。ドライバ 117 が第 1 スイッチ 123 を駆動してオフし、第 2 スイッチ 127 を駆動してオンする一方で、エネルギー蓄積回路からの電力は、第 2 スイッチ 127 を通ってアース 107 へ流れてもよく、電圧出力ポート 109 における DC 出力電圧を低減させる。したがって、スイッチ 123、127 のペア 123 は、迅速に切り替えられて電圧出力ポート 109 における DC 出力電圧を制御する。インダクタ 131 およびキャパシタ 111 も、DC 電圧を制御することを補助する共振フィルタとして作用する。

10

【 0043 】

比較器 139 は、第 2 スイッチ 127 のドレインに連結された第 1 入力部を有する。比較器 139 は、第 2 スイッチ 127 のソースに連結された第 2 入力部を有する。したがって、比較器 139 は、第 2 スイッチ 127 の両端に連結されてもよい。いくつかの実施形態において、比較器 139 は、第 1 入力部としての反転端子を有していてもよい。比較器 139 の第 1 入力部は、電流源 137 とも連結されていてもよい。I 2 C および / または P M B U S ( 図 2 に関連してさらに説明される ) は、電流源 137 の出力電流をトリムおよび / または調節するために使用されてもよい。したがって、過電流限度は、設定および / または調節され得る。比較器 139 の出力は、故障論理および過電流保護 ( O C P ) 回路 141 に提供されてもよい。

20

【 0044 】

故障論理および C P 回路 141 と共に比較器 139 は、スイッチ 127 がオンである場合にドレインソース抵抗  $R_{ds}$  を検知するように構成されている。 $R_{ds}$  により引き起こされるスイッチ 127 の両端の電圧降下は、電流源 137 をトリムまたは調節することにより調節され得る基準値と比較される。比較器 139 の出力は、過電流条件が生じるとトリップする可能性がある。過電流保護回路 141 は、過電流条件が検出され故障モードになると、スイッチ 123、127 および / またはドライバをオフしてもよい。種々の実施形態において、C P 回路は、スイッチ 123、127 のゲートに直接連結されて、スイッチをオフしてもよく、1つまたは複数の代替のエネルギー経路 ( 図示せず ) を短絡してエネルギーを放出してもよく、過電流条件に応答して PWM コントローラ 119 の出力に影響を及ぼし、および / または、過電流条件に応答してドライバ 117 の出力に影響を及ぼしてもよい。故障モードにおいて、システムは、スイッチ 123、127 および / またはドライバを短期間オンにすることにより回復を周期的に試みてもよく、過電流条件の検出を試みてもよく、過電流条件が依然として継続するならば、スイッチ 123、127 および / またはドライバ 117 をオフし、回復を再び試みる前に一定の期間待機する。

30

【 0045 】

過電流条件は、インダクタ飽和の結果として起こり得る場合もある。インダクタ 131 などのインダクタは、長すぎる期間に多すぎる電流がインダクタへ提供されると、飽和し、その磁気特性を失う可能性がある。このような場合、インダクタのインダクタンスは、10%、30%、またはそれ以上低下する。完全に飽和したインダクタは、配線として効果的に作用することができ、回路において潜在的な短絡を作成する。飽和中にインダクタの実行抵抗は、降下する可能性があり、出力電流を仕様を上回って潜在的に危険なレベルまで上昇させる。回路の L C 共振は、インダクタがエネルギーを効果的に格納しなくなる場合も影響される可能性があり、そのため、過電圧および / または電圧条件が起こり得る。

40

【 0046 】

50

インダクタ 131 は、 A C リップルと同様に負荷電流 ( D C 出力電流 ) を許容するように選択されてもよい。したがって、インダクタ 131 の飽和電流限度は、特定の D C 出力電流プラス最大 A C リップルを超過するように選択されてもよい。例えば、チップ埋め込み型 D C - D C 変換器が 10 A の D C 電流と + / - 5 A のリップルとを生成する場合、最大合計電流は 15 A であり、インダクタ飽和限度は、 15 A を上回ることになる。比較的高いインダクタンスを有するインダクタは、比較的高い飽和限度を有していてもよく、サイズが比較的大きくてもよい。

#### 【 0047 】

いくつかの設計では、過電流保護限度の決定およびインダクタサイズの決定が互いに独立して行われることがあり、一方または他方がオーバースペックになっている可能性がある。これは、例えば、製造者により作成された D C - D C 変換器に対して、第 2 者がインダクタを選択し連結する場合に起こり得る。いくつかの場合には、第 2 者は、十分な注意の範囲外でインダクタをオーバースペックにしてしまうことがあり、例えば、 5 A の A C 電流、 10 A の D C 電流、および 100 % の D C 過電流を許容することで、このようなインダクタは、 25 A 以上の飽和限度を有するように選択される。いくつかの場合には、第 2 者は、 O C P 限度を知ら無いことがあり、そのため、インダクタが飽和しないように、インダクタンスおよびサイズを比較的大きくするためにインダクタをオーバースペックにすることに頼る場合がある。または、いくつかの場合には、第 2 ユーザーは、高すぎる過電流保護限度に比較的小さいインダクタを使用することがあり、そのため、最小サイズと必要以上に大きいインダクタンスとを有するインダクタを使用する。いくつかの場合には、製造者は高すぎるまたは低すぎる過電流限度を設定することがある。ここに開示された D C - D C 変換器のいくつかの実施形態は、調整可能な過電流限度を有していてもよい。ここに開示された D C - D C 変換器のいくつかの実施形態は、過電流保護回路とインダクタとの双方を含んでいてもよく、過電流限度は、インダクタの少なくともサイズに基づいて決定され、過電流限度は、インダクタの飽和限度と等しい、および / または、飽和限度よりも低いように設定されてもよい。ここに開示された D C - D C 変換器のいくつかの実施形態は、過電流保護回路とインダクタとの双方を含んでいてもよく、インダクタのサイズは、少なくとも一部は過電流限度に基づいて、インダクタの飽和限度が過電流限度に等しいか、または、過電流限度を、 50 % 以下、 40 % 以下、 30 % 以下、 20 % 以下、 10 % 以下、またはそれらの間の任意の値または、これらの値のいずれかにより規定される範囲等の狭い幅だけ上回るように選択される。ここに開示された D C - D C 変換器のいくつかの実施形態は、 90 % 以下の D C 過電流、 75 % 以下の D C 過電流、 50 % 以下の D C 過電流、 50 % 以下の D C 過電流、 40 % 以下の D C 過電流、 30 % 以下の D C 過電流、 20 % 以下の D C 過電流、 10 % 以下の D C 過電流、またはこれらの間の任意の値、または、これらの値の何れかにより規定される範囲など、予測される最大 A C 電流プラス予測される D C 電流の 2 倍よりも少ないように設定された過電流限度を有していてもよい。いくつかの実施形態において、単独の設計者が、構成要素を提供でき、インダクタおよびその飽和限度と同様に、 O C P 回路および限度の双方のために値を選択してもよい。したがって、いくつかの実施形態において、 D C - D C 変換器は、比較的低いフットプリント、比較的低いインダクタ直流抵抗、および上昇された効率を有しつつ、インダクタが飽和に達することなく動作し得る。

#### 【 0048 】

##### パッケージング

図 2 は、チップ埋め込み型 D C - D C 変換器パッケージ 100 の実施形態のパッケージレベルの回路図を示す。チップ埋め込み型 D C - D C 変換器パッケージは、入力ポート 101 、アースポート 106 、および出力ポート 109 を備えていてもよい。図 1 に関連して説明したように、電力入力ポート 101 は、電源 103 と、アースに連結された入力キャパシタ 105 などにより連結されていてもよい。電圧出力ポート 109 は、 D C 出力電圧をノード 201 に連結された負荷へ、アース 107 と連結された出力キャパシタ 111 などによって供給してもよい。イネーブルポート 205 は、信号を受信して D C - D C 変

10

20

30

40

50

換器をイネーブルするように構成されていてもよい。テストポート 203 は、装置の状態を確認するために使用されてもよい。いくつかの実施形態において、集積回路間 ( I2C ) および / または電源管理バス ( PMBUS ) は、チップ埋め込み型 DC - DC 変換器パッケージ 100 への通信経路を提供する。

#### 【 0049 】

パッケージ 100 のフットプリントは、DC - DC 変換器の全ての構成要素を含んでいてもよい。いくつかの実施形態において、パッケージ 100 のフットプリントは、I C 1 13A または 113B およびインダクタ 131 を、例えば、外部インダクタを追加せずにパッケージが DC - DC 変換器として動作し得るように備える。いくつかの実施形態において、例えば、外部キャパシタを追加せずにこのようなパッケージが DC - DC 変換器として動作し得るように、キャパシタ 105 、 111 、および / または 133 の少なくとも 1 つまたは複数もパッケージフットプリント内に含まれていてもよい。

#### 【 0050 】

いくつかの実施形態において、I2C および / または PMBUS は、I2C および / または PMBUS プロトコル通信を受信するために使用されて、チップ埋め込み型 DC - DC 変換器パッケージ 100 のオンまたはオフし、前記 DC - DC 電力変換器パッケージ 100 の低電力またはスリープモードの変更、前記 DC - DC 変換装置パッケージ 100 の電流設定についての情報の読み出し、前記 DC - DC 変換装置パッケージ 100 について診断および / または技術情報の読み出し、DC - DC 変換器パッケージ 100 により提供される出力電圧の（例えば、図 16 および図 17 に関連して説明されるデジタル - アナログコントローラ「 DAC 」へ提供されるデジタル信号を変更することによる）変更または設定、ランプ波発生器（例えば、図 17 のランプ波発生器）の振幅または周波数などの特性のトリム、1 つまたは複数の電流源（例えば、図 18 の電流源）のトリム、その他の機能、の 1 つまたは複数を行ってもよい。いくつかの実施形態において、PMBUS プロトコルは、I2C 実装品の上に配線層として実施されている。

#### 【 0051 】

##### 集積およびチップ埋め込み型設計

DC - DC 変換器は、比較的高く集積されていてもよく、比較的高い周波数で切り替わってもよく、他の DC - DC 変換器と比べて改善された性能を提供することができる。いくつかの設計では、寄生効果防止は、仮にあったとしても、DC - DC 変換器が比較的高い周波数（比較的高い切替速度）で効率的に動作することを防止することができる。DC - DC 変換器の複数の設計は、寄生効果が低下された追加の設計と共にここで開示されている。

#### 【 0052 】

いくつかの DC - DC 変換器パッケージは、ワイヤボンドおよび / またはリードフレームパッケージを備える。一例 1m11 、 1mm の長さのボンドワイヤは、0.7nH の寄生インダクタンス、0.08pF の寄生容量、および 140m の寄生抵抗を有していてもよい。同様のまたはより高い寄生抵抗は、ワイヤボンドおよびクワッド・フラット・リード端子なし ( QFN ) パッケージ、パワークワッド・フラット・リード端子なし ( PQFN ) パッケージ、デュアルフラット・リードなし ( DFN ) パッケージ、マイクロリードフレーム ( MLF ) パッケージなどのリードフレームパッケージから生じ得る。ここに開示される DC - DC 変換器のいくつかの実施形態は、寄生効果を低減するために、ワイヤボンドおよび / またはリードフレームの使用をまとめて制限または回避することができる。ビア、配線、バンプ、および / またはバンプパッドは、代替として、パッケージの内側に使用されてもよい。

#### 【 0053 】

いくつかの DC - DC 変換器パッケージは、インダクタもキャパシタも備えていない。このようなパッケージは、ユーザーにキャパシタおよびインダクタのための特定値の選択の柔軟性を提供し、これらの構成要素の品質を制御する。DC - DC 変換器パッケージ、インダクタ、およびキャパシタは、マザーボードまたは別個の PCB に表面実装されてい

10

20

30

40

50

てもよく、マザーボードまたは別個の P C B に亘るワイヤボンドまたは長い配線と一緒に（例えば、図 7 A に示すように）連結されている。しかしながら、D C - D C 変換器パッケージを外部インダクタまたはキャパシタと連結することは寄生効果を導入し得る。寄生効果は、インダクタと負荷との間に同様に導入される可能性がある。ここに開示される D C - D C 変換器のいくつかの実施形態は、インダクタまたはキャパシタを D C - D C 変換器の他の構成要素と同じパッケージに集積することにより、インダクタまたはキャパシタに対する連結の寄生効果を低減することができる。ここに開示されたいいくつかの実施形態において、インダクタまたはキャパシタを連結する電気経路は、ワイヤボンドの代わりにビアおよび／または配線と共に実施されてもよい。ここに開示されたいいくつかの実施形態において、1 つまたは複数のインダクタまたはキャパシタを連結する電気経路は、マザーボードまたは別個の P C B（例えば、図 3 および図 7 B に示すように）における配線を含む代わりに、D C - D C 変換器の P C B に位置するビアおよび／または配線を含んでいてもよい。ここに開示されたいいくつかの実施形態において、P W M コントローラ、ドライバ、1 つまたは複数のインダクタ、1 つまたは複数のキャパシタ、および／または 1 つまたは複数のスイッチの任意の組み合わせは、同じパッケージに含まれていてもよい。

#### 【 0 0 5 4 】

いくつかの設計では、寄生効果は、構成要素の相互接続の結果として生じ得る。例えば、図 1 に関して、1 つの集積回路 1 1 3 A におけるドライバ 1 1 7 は、スイッチ 1 2 3、1 2 7 を含む別個の構成要素電子 1 3 5 と連結し得る。集積回路 1 1 3 A および別個の構成要素電子 1 3 5 は、P C B に含まれていてもよい。ドライバとスイッチ 1 2 3、1 2 7 との間の電気経路 1 2 1、1 2 9、1 2 5 は、P C B 上の配線を用いて実施されてもよいが、P C B 上の配線は、集積回路内の電気経路よりも高い寄生効果を有し得る。ここに開示される D C - D C 変換器のいくつかの実施形態は、スイッチ 1 2 3、1 2 7、およびドライバ 1 1 7 をそれらの相互接続と共に同じ I C 1 1 3 B に集積することによって、ドライバとスイッチとの間の相互接続の寄生効果を低減し得る。ここに開示されたいいくつかの実施形態において、P W M コントローラ、ドライバ、およびスイッチは、同じ I C 1 1 3 B に全て含まれている。いくつかの実施形態において、1 つまたは複数のキャパシタも、同じ I C 1 1 3 B に含まれていてもよい。

#### 【 0 0 5 5 】

いくつかの設計では、M O S F E T スイッチを使用することができる。しかしながら、M O S F E T スイッチは、比較的高い切替速度ではあまり効率的でないこともある。ここに開示されたいいくつかの実施形態において、スイッチ 1 2 3、1 2 7 は、e G a N スイッチであってもよい。e G a N スイッチは、M O S F E T スイッチと比べてより効率的かつより高い速度で切替可能である。

#### 【 0 0 5 6 】

ここに記載の技術の相乗効果が考えられる。寄生容量および／またはインダクタンス効果は、D C - D C 変換器における最大切替速度を制限し得る。その理由は、寄生効果は、格納されることになる不都合なエネルギーを引き起こす可能性があり、エネルギーの充電および放電に影響し、それにより、D C 電圧規制に影響するためである。寄生効果は、スイッチをゆっくりとオンまたはオフにすることもあり得る。いくつかの実施形態において、ここに記載の技術の組み合わせは、D C - D C 変換器性能における十分な程度の改善により低減されることになる寄生効果を引き起こし得る。D C - D C 変換器の構造、サイズ、性能に関連する追加の相乗効果は、詳細な開示の後の部分においても検討される。

#### 【 0 0 5 7 】

いくつかの他の D C - D C 変換器と比べ、ここに開示されたいいくつかの実施形態は、約 4 0 本のボンドワイヤを除去し、このことは、約 2 0 m 分の寄生効果を低減することができ、1 0 n H 以上分のパッケージ漏れインダクタンス（寄生インダクタンス）も低減することができる。これらの寄生効果の除去は、高速切替（例えば、e G a N スイッチ）の利益を実現することを補助し得る。

#### 【 0 0 5 8 】

10

20

30

40

50

電力スイッチについての性能指数は、数式 1 に基づいて決定され得る。

【数 1】

$$FOM = R_{DS(ON)} \times Q_G \quad \text{数式 1}$$

ただし、FOM は性能指数、 $R_{DS(ON)}$  は、スイッチのオン抵抗、および  $Q_G$  はスイッチのゲート電荷である。ゲート電荷  $Q_G$  は、寄生インダクタンスによって影響され得る。寄生インダクタンスを低減することは、比較的低い FOM、通常は達成することが困難な設計改善という結果になり得る。

【0059】

全体の利点の全てではないがいくつかは、十分な寄生効果低減と構成要素選択の同時の組み合わせによってのみ実現され得ることがさらに分かる。例えば、寄生効果を低減することのいくつかの利点は、MOSFET を使用する場合、いくつかの条件下では実現されない場合もある。これは、切替速度をより高くできるように十分なレベルまで寄生効果を低減できるかもしれないが、MOSFET 設計がより高い速度での効率的な切替を許容しない場合もあるためである。同様に、DC - DC 変換器における eGaN スイッチ（または他のより高速かつ典型的にはより高コストのスイッチ）の完全な切替性能が寄生効果によって制限される可能性がある。完全な切替性能は、1 MHz 以上、3 MHz 以上、4 MHz 以上、5 MHz 以上、7 MHz 以上、10 MHz 以上などのメガヘルツ範囲における比較的高い周波数でより効率的に切り替えることを含んでいてもよい。いくつかの例では、15 MHz までの切替速度を達成でき、これらの特定された範囲外の切替速度は、いくつかの実施において使用され得る。

【0060】

したがって、寄生効果を低減するために限定された技術をテストするエンジニアは、インパクトのあるレベルへ寄生効果を低下させない可能性がある。寄生低減技術の組み合わせをテストするエンジニアは、切替速度が MOSFET により限定される場合、より顕著なゲインを達成しない場合がある。DC - DC 変換器における寄生効果に最初に気付かず、対処せずに eGaN スイッチをテストするエンジニアは、eGaN スイッチを使用する切替速度利点に気付かない場合があり、特に、eGaN スイッチは MOSFET スイッチよりもコストがかかるからである。さらに、切替速度を、他の変数に応じて、特に、1、2、3、5、7 または 10 MHz 以上に上昇することは、効率がより高い切替速度で低減する傾向があるという従来の知識に反する。

【0061】

詳細な開示の集積およびチップ埋め込み型設計の項目は、寄生効果を低減および / または比較的高速の切替速度の達成のための種々の実施形態を検討する。いくつかの実施形態は、特徴の組み合わせを含むが、全ての特徴よりも少ない特徴を有する実施形態は、それ自体の権利において理解される。

【0062】

#### 物理的構造図

図 3 は、例示的チップ埋め込み型 DC - DC 変換器の断面図 300 を示す。図 300 は、絶縁体 301、コンダクタ（例えば、金属）303、バンプまたはパッド 304、コンダクタマイクロビア 305、第 1 PCB 層 307、導電性メッキ 309、PCB コア 311、配線 313、埋め込み型 IC チップ 315、第 2 PCB 層 317、インダクタ 321、およびキャパシタ 323 を備える。

【0063】

埋め込み型 IC チップ 315 は、PCB コア 311 に埋め込みされていてもよい。種々の実施形態において、IC チップ 315 は PCB の一層、または、PCB の 2 以上の層の

10

20

30

40

50

間、または、下部 P C B と上部 P C B との間に埋め込みされていてもよい。埋め込み型 I C チップ 3 1 5 は、例えば図 1 に関連してここで検討したように、P W M コントローラ、ドライバ、および / または 1 つまたは複数のスイッチ（例えば、e G a N スイッチ）を備えていてもよい。埋め込み型 I C チップ 3 1 5 は、D C - D C 変換器構造において、複数のピア 3 0 5 および / または配線 3 1 3 を介してインダクタ 3 2 1 およびキャパシタ 3 2 3 と連結されていてもよい。

#### 【 0 0 6 4 】

絶縁体 3 0 1 は、例えば、半田マスク、モールド、アンダーフィルなどを備えていてもよい。P C B の層 3 0 7、3 1 7 は、P C B 基板、積層、樹脂、エポキシ、絶縁体などであってもよい。図 3 に示す図 3 0 0 において、P C B コア 3 1 1 はフィラー、積層、絶縁モールド化合物、または基板などであってもよい。導体（例えば、金属）3 0 3、ピア 3 0 5、および配線 3 1 3 は、銅、アルミニウム、金などの様々な種類の金属または導電性材料であってもよい。ピアは、メッキされたピアとして示されているが、いくつかの実施形態は、ピラーまたは他のピラーを使用してもよい。種々の実施形態は、金属の種類および層を増減して使用し得る。

10

#### 【 0 0 6 5 】

いくつかの実施形態において、I C チップ 3 1 5 は、フリップチップ実装されていてもよい。種々の実施形態において、I C チップ 3 1 5 は、I C チップ 3 1 5 上の接続がインダクタ 3 2 1 および / またはキャパシタ 3 2 3 に対向し得るように、または、インダクタ 3 2 1 および / またはキャパシタ 3 2 3 の反対側を向くように、フェイスアップまたはフェイスダウンであってもよい。I C チップ 3 1 5 上の接続が、インダクタ 3 2 1 および / またはキャパシタ 3 2 3 の反対側を向く場合、インダクタ 3 2 1 および / またはキャパシタ 3 2 3 は、ピア 3 0 5 および / または配線 3 1 3 によって I C チップ 3 1 5 の遠位端と連結されてもよい。

20

#### 【 0 0 6 6 】

図 3 は、ドライバおよびスイッチを含み得る单一のI C チップ 3 1 5 を示すが、いくつかの実施形態において、スイッチ（例えば、モノリシックのe G a N スイッチ）はI C チップ 3 1 5 とは別個のP C B にチップ埋め込まれたチップであってもよく、チップ埋め込み型 I C チップ 3 1 5 におけるドライバによって相互接続されていてもよい。ピア、パッド、および / または配線は、D C - D C 変換器の種々の構成要素を連結することができ、2つのダイはフェイスダウンまたはフェイスアップであってもよい。インダクタまたは他の磁気は、最上層内または最上層上に配置されてもよく、バックコンバータにおける完全なハーフブリッジ組み合わせ、または、ハーフブリッジ回路図を用いる任意の他の構成を作成してもよい。

30

#### 【 0 0 6 7 】

I C チップ 3 1 5 は、ピア 3 0 5 および配線 3 1 3 の双方によってインダクタ 3 2 1 と連結されたものを示したが、いくつかの実施形態において、I C チップ 3 1 5 は、ピア 3 0 5 または配線 3 1 3 のどちらかでインダクタ 3 2 1 および / またはキャパシタ 3 2 3 と連結されていてもよい。種々の実施形態において、P C B 組立品は、図 3 に示すよりも多くの、または、よりも少ないP C B 層を有していてもよく、I C チップ 3 1 5 は、単一層に、または、複数層のP C B 間に埋め込みされていてもよい。種々の実施形態において、層 3 0 7、3 1 7 は、1 つのP C B または別個の複数のP C B の複数の層であってもよい。P C B の底に露出した金属 3 0 3 は、入力電源、アース、および / または負荷と連結するための入力 / 出力パッドを提供し得る。

40

#### 【 0 0 6 8 】

インダクタ 3 2 1 および / またはキャパシタ 3 2 3 の一部は、I C チップ 3 1 5 に積層されていてもよい。いくつかの実施形態において、インダクタ 3 2 1 および / またはキャパシタ 3 2 3 は、I C チップ 3 1 5 に全体的に積層されていてもよい。インダクタ 3 2 1 および I C チップ 3 1 5 は、D C - D C 変換器パッケージにおいて大きい方の構成要素になる傾向がある。いくつかの実施形態において、インダクタ 3 2 1 または I C チップ 3 1

50

5の小さい方は、インダクタ321またはICチップ315の大きい方のフットプリント範囲内に積層されてもよい。スイッチおよびドライバの双方を含む单一のICチップ315が図3に示されているが、種々の実施形態において、インダクタ321および/またはキャパシタ323は、单一のICチップ315とは別個の構成要素に少なくとも部分的に重なってもよい。例えば、インダクタ321は、1つまたは複数のスイッチ、PWMコントローラ、および/またはドライバなどに重なっていてもよい。

#### 【0069】

インダクタ321の位置は、DC - DC変換器のより良好な熱性能に寄与し得る。インダクタ321を最上部に設けることにより、インダクタ321は、周囲空気により冷却され得る。最上部に実装されたインダクタ321により、インダクタ321について種々のサイズまたは形状も（例えば、インダクタ321がPCBの寸法により制約されないように）使用できるようになる。

10

#### 【0070】

図4Aは、積層型インダクタ321を有する例示的チップ埋め込み型DC - DC変換器の斜視図400を示す。インダクタ321は、PCBの層317、307間にコア311に埋め込まれたICチップ（不可視）上に積層されてもよい。インダクタ321は、少なくとも部分的に、金属接点401を介してPCBと連結されてもよい。いくつかの実施形態において、1つまたは複数のキャパシタ323（不可視）は、PBC層317と連結されていてもよい。

20

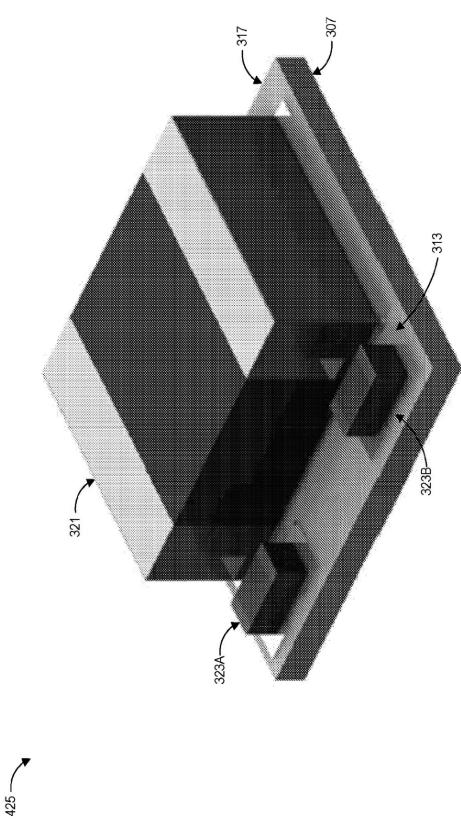

#### 【0071】

図4Bは、積層型インダクタ321を有する例示的なレンダリングされたチップ埋め込み型DC - DC変換器の逆斜視図425を示す。インダクタ321は、PCBの層317、307間に埋め込まれたICチップ（不可視）上に積層されてもよい。インダクタ321は、少なくとも部分的に、金属配線313を介してPCBと連結されてもよい。1つまたは複数のキャパシタ323A、323Bは、PBC層317と連結されていてもよい。1つまたは複数のキャパシタ323A、323Bは、配線313によってインダクタ321とも連結されていてもよい。

20

#### 【0072】

いくつかの実施形態において、切替周波数が上昇するにつれて、インダクタが小さくなり得る。さらに、いくつかの材料および薄膜技術などの技術は、インダクタのサイズも低減することができる。したがって、いくつかの実施形態において、インダクタは、例えばICの上方に、または、ICに並行してPCBに埋め込みされていてもよい。このような構造はさらなる集積を提供し、入力および出力キャパシタなどの他の周辺の構成要素のために、PCB実装表面上などの利用可能な空間量を増大させる。

30

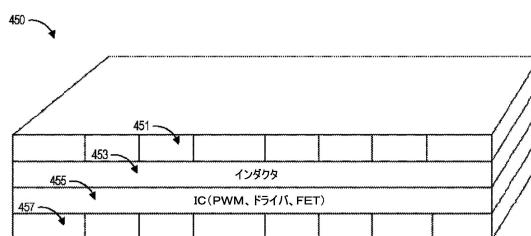

#### 【0073】

図4Cは、埋め込み積層型インダクタを有する例示的チップ埋め込み型DC - DC変換器の側面図450を示す。第1層451は、例えば、パッケージング層またはPCB層でもよい。第2層453は、第2層453内に埋め込まれたインダクタを備えるPCB層であってもよい。第3層455は、第3層内に埋め込まれた回路（例えば、IC）を含むPCB層であってもよい。回路（例えば、IC）は、PWMコントローラ、ドライバ、および/またはスイッチ（例えば、FET）を備えていてもよい。第4層457は、例えば、パッケージング層またはPCB層でもよい。図4Cにおいて、インダクタは、少なくとも一部が、回路（例えば、IC）に重なっていてもよくまたは、側方へずれていてもよい。インダクタは、ボンドワイヤを使用せずにビアおよび/または配線によりICと連結されてもよい。

40

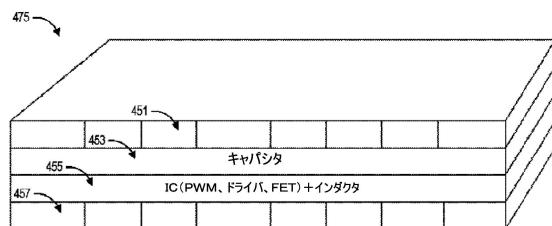

#### 【0074】

図4Dは、埋め込み型インダクタを有する例示的チップ埋め込み型DC - DC変換器の側面図475を示す。層451、453、455、および457は、図4Cについて説明されたものと同じまたは同様であってもよい。図4Dにおいて、層455は、回路（例えば、IC）、および他の回路（例えば、IC）の他にインダクタを含んでいてもよい。I

50

Cは、配線によってインダクタと連結されていてもよい。層453は、埋め込み型キャパシタを備えていてもよい。いくつかの実施形態において、1つまたは複数の埋め込み型キャパシタは、PCBに埋め込みされていてもよく、埋め込み型キャパシタは、1つまたは複数の埋め込み型キャパシタのフットプリントが回路（例えば、IC）および／またはインダクタのフットプリントに重なるように実装されていてもよい。いくつかの実施形態において、1つまたは複数の埋め込み型キャパシタは、埋め込み型回路（例えば、IC）および／または埋め込み型インダクタと共に、同じ層455に含まれていてもよい。いくつかの実施形態において、キャパシタは、層453に表面実装されていてもよい。いくつかの実施形態において、層453は省略されていてもよい。いくつかの実施形態において、キャパシタは、PCB（例えば、図3に示すキャパシタ323など）の外側に実装されてよい。多くの変形例が可能である。PWMコントローラ、ドライバ、および／またはスイッチの任意の組み合わせを含む回路（例えば、1つまたは複数のIC）は、1つまたは複数のインダクタおよび／または1つまたは複数のキャパシタのいずれかまたは双方と同じ層に在ってもよい。ICは、eGANICであってもよい。モノリシックのeGANICは、PWMコントローラ、ドライバ、および1つまたは複数のスイッチの任意の組み合わせを含んでいてもよい。いくつかの実施においては、1つまたは複数のキャパシタおよび／または1つまたは複数のインダクタは、1つまたは複数のPWMコントローラ、ドライバ、および／または1つまたは複数のスイッチと共にIC（例えば、eGANIC）に含まれていてもよい。1つまたは複数のインダクタ、1つまたは複数のキャパシタ、または両方は、回路（例えば、IC）の上方または下方などの、PCBに埋め込まれた別個の層に設けられていてもよい。いくつかの実施形態において、1つまたは複数のインダクタは、回路（例えば、IC）の第1面に在ってもよく、1つまたは複数のキャパシタは、回路（例えば、IC）の反対側の第2面に在ってもよい。いくつかの実施形態において、1つまたは複数のインダクタおよび1つまたは複数のキャパシタは、PCBの異なる層に埋め込みされていてもよいが、回路（例えば、IC）の同じ側に在ってもよい。1つまたは複数のキャパシタおよび／または1つまたは複数のインダクタのいずれかまたは両方は、（例えば、図3に示すように）PCBの外側に設けられていてもよい。いくつかの実施において、1つまたは複数のPWMコントローラ、ドライバ、および1つまたは複数のスイッチは、PCBに埋め込まれた異なる層に在ってもよい。いくつかの実施形態において、PWMコントローラおよびドライバは、別個のIC（例えば、eGANIC）に在ってもよい。PCBにおける異なる層に埋め込まれた構成要素は、少なくとも部分的にもしくは完全に重なるように、または、重ならないように配向されている。ここに開示された任意のeGAN実施形態は、代替として、デブレッショングループモードGAN、eGANおよび／またはこれらの任意の組み合わせを含んでいてもよいGAN実施形態として実施されてもよい。

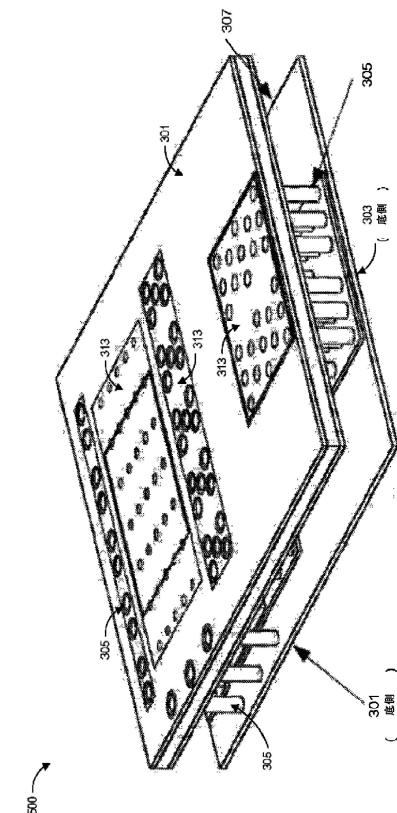

#### 【0075】

図5は、例示的チップ埋め込み型DC-DC変換器の透過斜視図500を示す。図5は、図4Aおよび図4Bに示すものと同じ例示的チップ埋め込み型DC-DC変換器を示すが、構成要素が不明瞭になるため、インダクタ321、キャパシタ323、またはコア311無しで示す。ビア305は、配線313および／またはパッド303を連結することができる。

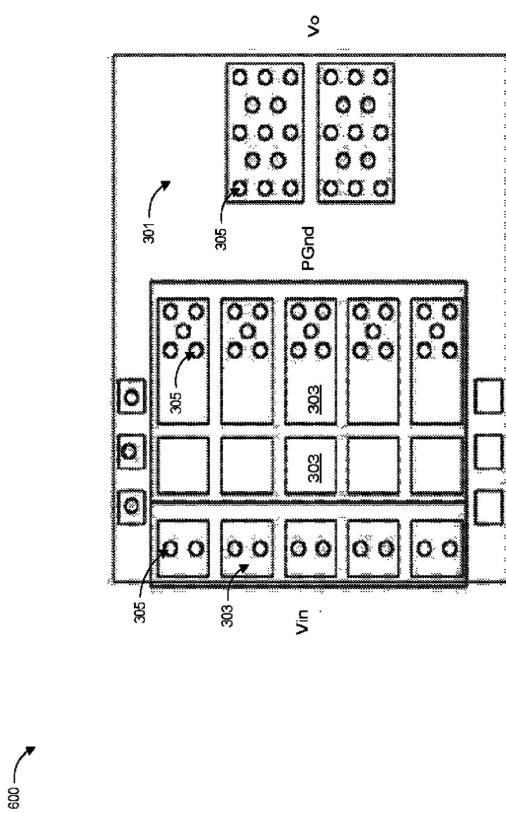

#### 【0076】

図6は、例示的チップ埋め込み型DC-DC変換器の底面図を600示す。図6は、図5に示すものと同じ例示的チップ埋め込み型DC-DC変換器を示す。絶縁体301のエリア間の露出された金属303のパッドは、供給電圧、アース、および／または電圧出力のための電気的な接点を提供する。ビア305を示す。しかしながら、いくつかの実施形態において、ビアは、露出された金属303に亘って可視的に延びていない。

#### 【0077】

##### 低減されたフットプリント

ここに記載の物理的構造および他の技術は、DC-DC変換器のフットプリントを低減

するために使用されてもよい。いくつかの実施形態において、フットプリントは、約 70 % 低減されてもよい。積層された構成要素、より高い切替速度を有するより小さいインダクタの使用、および構成要素の単一のパッケージは全て、低減されたフットプリントに寄与し得る。

#### 【 0 0 7 8 】

先述のように、いくつかの D C - D C 変換器パッケージは、インダクタもキャパシタも備えておらず、いくつかの D C - D C 変換器は、ドライバ、P W M コントローラ、および / または I C チップの傍らに実装されたインダクタを備えていてもよい。このようなパッケージは、ユーザーにキャパシタおよび / またはインダクタのための特定値の選択これらの構成要素の品質の制御の柔軟性を提供してもよい。しかしながら、構成要素を互いに並べる代わりに積層する構造に配置することで、D C - D C 変換器のフットプリントを低減することができる。ここに開示されたいいくつかの実施形態は、I C チップ上に全体または一部が垂直に積層されたインダクタを特徴とする。ここに開示されたいいくつかの実施形態は、I C チップ上に全体または一部が垂直に積層されたキャパシタを特徴とする。インダクタおよび / またはキャパシタを積層することで、D C - D C 変換器のフットプリントを低減することができる。積層された構成要素は、ビアを介して（例えば、I C チップと）電気的に連結されてもよく、これにより、上記のような寄生効果を低減することができる。ここに開示されたいいくつかの実施形態は、ユーザーによって個々の構成要素が選択され、配置され、実装される必要が無いように設計の簡単化を提供し得る。単一のパッケージ D C - D C 変換器は、外部キャパシタまたはインダクタを構成せずに使用され得る。さらに、いくつかの実施形態は、インダクタのサイズに妥協することなく、インダクタの性能に妥協することなく、および / または、カスタムメイドのインダクタを必要とすることなく、インダクタをパッケージに集積し得る。

#### 【 0 0 7 9 】

上述のように、寄生効果を低減することができ、D C - D C 変換器の切替速度を効率的に上昇させることができる。D C - D C 変換器のインダクタンスは、数式 2 に基づいて決定され得る。

#### 【 数 2 】

$$L = \frac{(V_{in} - V_o) \times V_o}{2 \Delta i L \times F_s \times V_{in}} \quad \text{数式 2}$$

ただし、L はインダクタンス、V<sub>in</sub> は入力電圧、V<sub>o</sub> は出力電圧、I<sub>L</sub> はインダクタリップル電流、F<sub>s</sub> は切替周波数である。なお、インダクタンスは、切替速度が上昇するにつれて上昇する。したがって、低減された寄生効果および比較的高速の 1 つまたは複数のスイッチ（例えば、e G a N スイッチ）により、D C - D C 変換器は、比較的小さいインダクタを使用することができる。D C - D C 変換器において、インダクタは、最大構成要素の 1 つであってもよい。前記インダクタのサイズを（例えば、その元のサイズの何分の 1 かに）低減することにより、フットプリントを実質的に低減することができる。

#### 【 0 0 8 0 】

いくつかの D C - D C 変換器は、複数のパッケージを備える。例えば、ドライバを含む第 1 パッケージ、スイッチ用の第 2 パッケージ、および、インダクタを含む第 3 パッケージがあつてもよい。ここに開示されたいいくつかの実施形態は、単一のパッケージを特徴とし、単一のパッケージは、P W M コントローラ、ドライバ、スイッチ（例えば、e G a N スイッチ）、1 つまたは複数のインダクタ、および 1 つまたは複数のキャパシタなどの、D C - D C 変換器の構成要素の全てを備える。ここに開示されたいいくつかの実施形態において、P W M コントローラ、ドライバ、および / またはスイッチ（例えば、e G a N スイッチ）などの多数の構成要素を単一の I C に集積することができる。

10

20

30

40

50

## 【0081】

したがって、比較的高い切替速度に関連する特徴は、DC - DC変換器のサイズを低減することができるよう、DC - DC変換器の物理的設計によって相乗作用を与えることができる。DC - DC変換器が小さいほど、種々のアプリケーションにおいて使用して、マイクロプロセッサ、フィールドプログラム可能なゲートアレイ、アプリケーション特有の集積プロセッサなどの最新の電子デバイスに動力供給するためにより高い電流密度を提供することができる。より小さいDC - DC変換器は、低減された製造コストで作成され得る。ここに記載の技術は、ボードおよびパッケージ寄生効果を低減することができる。より小さいDC - DC変換器は、より密接した接続を特徴とし得る。この接続は、インダクタ、ICチップ、および/または負荷間の寄生効果を低減し、DC - DC変換器は、より高い周波数で効率的に動作され得る。ここに記載の技術は、ノイズを低減することができ、比較的低いリップル効果および比較的低い電波障害を含む。

## 【0082】

一般的に、比較的大きいサイズのDC - DC変換器は、比較的大きい電流量を処理することができる。いくつかの実施形態において、ここに開示されるDC - DC変換器は、従来の方法に比べて、比較的小さいサイズのDC - DC変換器による電流の任意の量を処理することができる。例えば、ここに開示されるDC - DC変換器は、アンペア数当たり20mm<sup>2</sup>未満の電流、アンペア数当たり15mm<sup>2</sup>未満の電流、アンペア数当たり10mm<sup>2</sup>未満の電流、アンペア数当たり7mm<sup>2</sup>未満の電流、アンペア数当たり5mm<sup>2</sup>未満の電流、アンペア数当たり4mm<sup>2</sup>未満の電流、アンペア数当たり3mm<sup>2</sup>未満の電流、アンペア数当たり2mm<sup>2</sup>未満の電流、アンペア数当たり1.5mm<sup>2</sup>未満の電流、または、アンペア数当たり1mm<sup>2</sup>未満の電流のフットプリント領域を有し得る。DC - DC変換器は、ここで検討した範囲外の値をいくつかの実施において使用してもよいが、アンペア数当たり1.0mm<sup>2</sup>または0.5mm<sup>2</sup>という低い電流を有していてもよい。

## 【0083】

例示的アプリケーション

ここに開示されるDC - DC変換器は、電子デバイスに電力を提供するために使用されてもよい。例は、一次供給電圧を供給電圧によって電力供給される電子デバイスに適したDC電圧に変換するためにDC - DC変換器を使用することを含む。例えば、いくつかのアプリケーションにおいて、最新の電力管理ソリューションは、サイズ、入力/出力リップル、効率、および温度限度についての仕様を満たしつつ、40以上のチップ埋め込み型DC - DC変換器を使用して40以上の電子構成要素に給電することができる。ここに開示されるようなDC - DC変換器は、より小さく作成され、空間およびボードサイズが制限された最新のシステムにおいて使用されてもよい。ここに開示されるようなDC - DC変換器は、ストレージ、サーバー、ネットワーク構築、電気通信、インターネット・オブ・シングスなどの種々のマーケットセグメントにおける構成要素に給電するために使用され得る。他のアプリケーションは、ここに開示されるDC - DC変換器を使用して、ブレードサーバー、固体素子の構成要素などにおけるプロセッサのためなどのポイントオブロード装置のマイクロポイントに対して電力を提供することを含む。

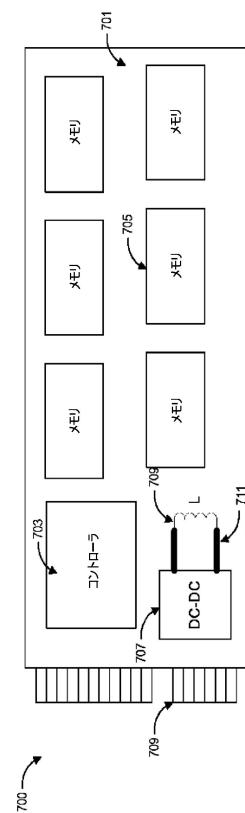

## 【0084】

図7Aは、記憶装置700において使用されるDC - DC変換器の一例を示す。記憶装置700は、例えば、固体素子であってもよい。記憶装置700は、コントローラ703と、PCB701を介して連結された複数のメモリチップ705とを備えていてもよい。DC - DC変換器707は、電力入力ピン709を介して供給電圧を受信し、メモリチップ705および/またはコントローラ703へDC電力を提供することができる。DC - DC変換器707は、PCB701を介してボンドワイヤまたは配線711によりインダクタ709に連結されていてもよい。PCB701は、DC - DC変換器707のパッケージからは別個のPCB701であってもよい。記憶装置700の容量は、図7Aの実施においては6個のメモリチップであるメモリチップ705の数によって制限される。

## 【0085】

10

20

30

40

50

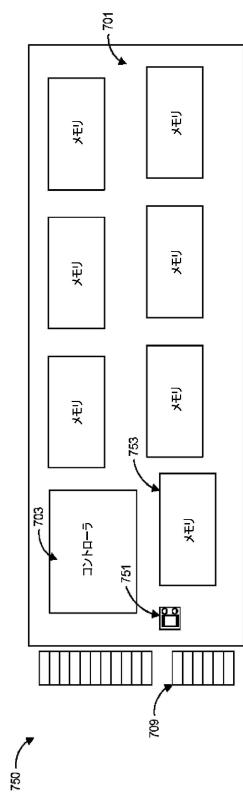

図 7 B は、記憶装置 750 に対するチップ埋め込み型 DC - DC 変換器の例示的適用を示す。チップ埋め込み型 DC - DC 変換器 751 は、電力入力ピン 709 を介して供給電圧を受信し、メモリチップ 705 および / またはコントローラ 703 へ DC 電力を提供する。比較的小さいインダクタは、チップ埋め込み型 DC - DC 変換器 751 のパッケージフットプリントに含まれていてもよい。チップ埋め込み型 DC - DC 変換器 751 は、図 7 A の DC - DC 変換器 707 よりも実質的に小さくてもよい。したがって、追加の PC B 空間を、追加のメモリチップ 753 のために使用して記憶装置 750 の記憶容量を向上することができる。

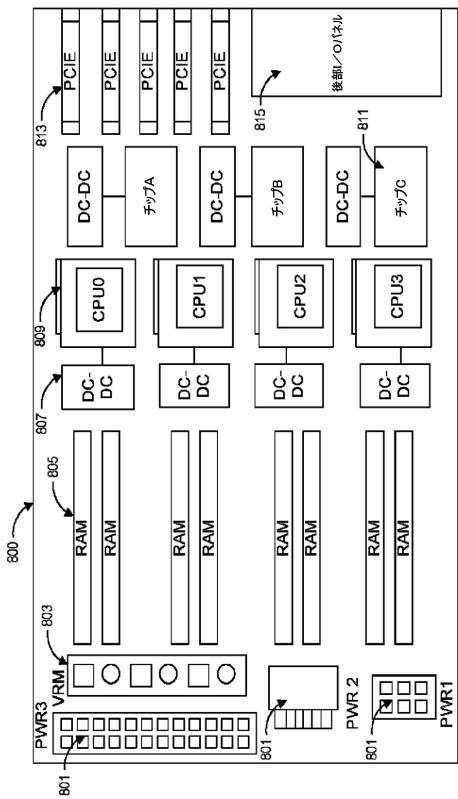

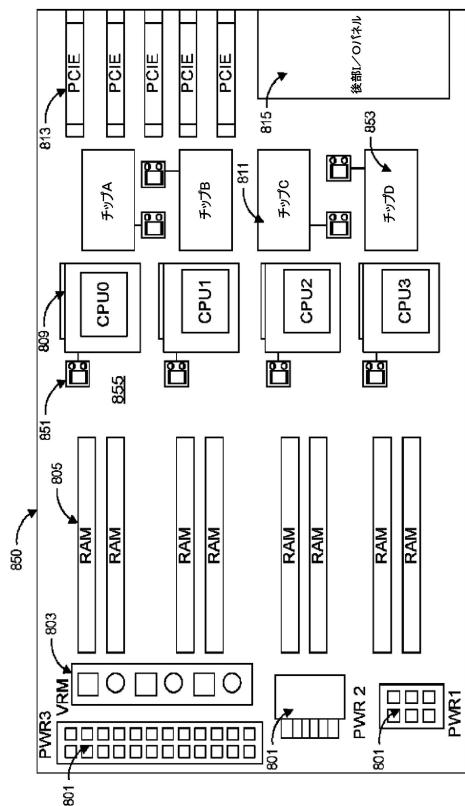

#### 【 0086 】

図 8 A は、回路基板 800 における DC - DC 変換器の例示的適用を示す。回路基板 800 は、例えば、複数の電源コネクタ 801 (PWR)、電圧レギュレータ管理 (VRM) 回路 803、複数のランダムアクセスメモリ (RAM) スロット 805、複数のペリフェラル・コンポーネント・インターフェクト・エクスプレス (PCIe) スロット 813、および後部入力 / 出力パネル 815 等を含むブレードサーバーまたはマザーボードであってもよい。回路基板 800 は、ポイントオブロードにおいて複数の DC - DC 変換器 807 も含む。DC - DC 変換器 807 は、中央処理装置 809 またはコンピュータチップ 811 にそれぞれ給電する。DC - DC 変換器 807 は、電源コネクタ 801 および / または VRM 回路 803 を介して供給される電力を受信し、供給された電力の電圧を CPU 809 またはコンピュータチップ 811 のそれぞれ DC 電力仕様に合った DC 電圧に変換することができる。

10

#### 【 0087 】

図 8 B は、回路基板 850 におけるチップ埋め込み型 DC - DC 変換器の例示的適用を示す。回路基板 850 は、複数のチップ埋め込み型 DC - DC 変換器 851 を (例えばポイントオブロードにおいて) 含む。チップ埋め込み型 DC - DC 変換器 851 は、例えば、中央処理装置 809 および / またはコンピュータチップ 811 に給電し得る。DC - DC 変換器 851 は、電源コネクタ 801 および / または VRM 回路 803 を介して供給される電力を受信し、供給された電力の電圧を CPU 809 および / またはコンピュータチップ 811 のそれぞれ DC 電力仕様に合った DC 電圧に変換することができる。チップ埋め込み型 DC - DC 変換器 851 は、図 8 A の DC - DC 変換器 807 よりも小さくてもよい。したがって、マザーボードは、追加のコンピュータチップ 853 のための空間を有し得る。DC - DC 変換器 807 によって事前に占拠されていたエリアは、この場合は、他の構成要素のために利用可能な開放エリア 855 であってもよく、または、気流を向上するために開放されたままであってもよい。

20

30

#### 【 0088 】

##### 追加の実施形態

いくつかの例示的実施形態において、1つまたは複数のスイッチ (例えば、eGAN スイッチ) (例えば、モノリシックのまたは独立型の) は、インダクタを有するチップ埋め込み型 DC - DC 同期バックコンバータにおいて使用されてもよく、埋め込み型 IC チップは、PWM コントローラおよびドライバを備える。DC - DC 同期バックコンバータを基礎とする MOSFET と比較して、チップ埋め込み型 DC - DC 変換器は、比較的低い切替損失で比較的高い速度で切り替えられ、高い切替速度 (例えば、約 5 MHz、または、ここに記載されたほかの速度) でより効果的に切り替わることができ、eGAN スイッチは、約 5 倍低い  $Q_G$  を有し得る。

40

#### 【 0089 】

いくつかの実施形態は、3 MHz などの同じ速度で切り替わる場合、代替設計と比較して約 30 % 低い電力損失の向上された効率ゲインを実現する。

#### 【 0090 】

チップ埋め込み型 DC - DC 変換器の一例示的実施形態は、約 3 mm × 3 mm × 1.5 mm のパッケージにパッケージングされ、約 1 MHz ~ 5 MHz の範囲で切り替わり、約 6 A の電流を供給してもよい。比較において、同様のアンペア数のための種々のワイヤボ

50

ンド D C - D C 変換器設計は、約 1 2 m m × 1 2 m m の面積であり、約 6 0 0 k H z で切り替わってもよい。

【 0 0 9 1 】

チップ埋め込み型 D C - D C 変換器の一例示的実施形態は、1 2 V 電源を受信することができ、約 1 . 2 V および約 1 0 A の D C 信号を出力することができる。チップ埋め込み型 D C - D C 変換器は、約 1 M H z で切り替わることができ、約 3 0 0 n H であるインダクタを有し得る。

【 0 0 9 2 】

チップ埋め込み型 D C - D C 変換器のいくつかの例示的実施形態は、約 6 m m × 6 m m または 7 m m × 7 m m であるパッケージにはめ込むことができる 2 5 A のバックコンバータを含むことができる。

10

【 0 0 9 3 】

チップ埋め込み型 D C - D C 変換器のいくつかの実施形態は e G a N スイッチを備える。スイッチは約 5 M H z で動作することができ、チップ埋め込み型 D C - D C 変換器は約 1 M H z で動作している D C - D C 変換器に基づく M O S F E T と同様の効率で動作し得る。その結果、パッケージサイズが比較的小さくなり、過渡負荷に対する比較的迅速な応答により全体的にシステム性能が比較的高くなる。

【 0 0 9 4 】

例示的方法

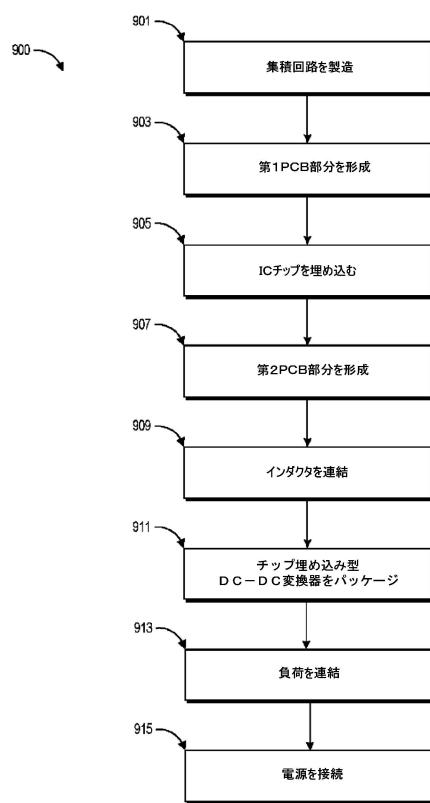

図 9 は、チップ埋め込み型 D C - D C 変換器を作成し使用するための例示的方法 9 0 0 のフローチャートを示す。

20

【 0 0 9 5 】

ブロック 9 0 1 において、集積回路は製造され得る。集積回路は、I C チップでもよく、この I C チップは、ドライバ、P W M コントローラ、および 1 つまたは複数の電力スイッチの少なくとも 1 つを備えていてもよい。I C チップは、D C - D C 変換器の他の構成要素のドライバ、P W M コントローラ、電力スイッチ、インダクタ、キャパシタ、または複数を備えていてもよい。いくつかの実施形態において、1 つまたは複数の電力スイッチは、e G a N スイッチ、ヒ化ガリウムスイッチ、または他の種類の高性能スイッチであってもよい。

【 0 0 9 6 】

ブロック 9 0 3 において、第 1 P C B 部分を形成することができる。第 1 P C B 部分を形成することは、P C B 層または絶縁体を提供すること、マスキング、エッティング、ビア掘削、ビア充填、導体配線およびパッドの配置、I 2 C および / または P M B U S のいくつかまたは全ての配置、などを含んでいてもよい。

30

【 0 0 9 7 】

ブロック 9 0 5 において、I C チップは、チップ埋め込み技術を用いて埋め込みされてもよい。いくつかの実施形態において、例えば、機械加工またはエッティング技術を用いて空洞が（例えば、P C B に）形成されてもよく、I C チップが空洞に配置されてもよい。I C チップは、第 1 P C B 部分と、P C B 内部へ、P C B 層上に、複数の P C B 層間に、複数の P C B の間などに連結されてもよい。I C チップは、フェイスアップまたはフェイスダウンでチップ埋め込みされてもよい。いくつかの実施形態において、I C は、フリップチップ技術を用いて埋め込みされていてもよい。I C チップまたはダイは、取付部またはボンディング材料と連結されていてもよい。いくつかの実施形態において、他の構成要素も P C B に埋め込みされていてもよい。例えば、1 つまたは複数のスイッチ（例えば、モノリシックの e G a N 電力スイッチ）が I C チップから分離されている実施形態において、1 つまたは複数のスイッチ（例えば、モノリシックの e G a N スイッチ）も P C B において埋め込みされていてもよい。

40

【 0 0 9 8 】

ブロック 9 0 7 において、P C B の第 2 部分のための導通経路および絶縁体が形成されてもよい。このことは、追加の P C B 層または絶縁体を提供すること、マスキング、エッ

50

チング、ビアの掘削または露出、ビア充填、導体配線およびパッドの配置、I 2 C および / または P M B U S のいくつかまたは全ての配置、などを含んでいてもよい。いくつかの実施形態において、ブロック 903、905、および 907 に関連して説明された作業はまとめられ、および / または重複してもよい。ブロック 903、905、および 907 において、導体（例えば、ビアおよび配線）は、（例えば、図 1 および図 3 に示すような）DC - DC 変換器構造における構成要素を連結するために形成され得る。

#### 【 0 0 9 9 】

ブロック 909 において、インダクタが連結され得る。インダクタは、PCB の最上部と連結されてもよい。インダクタは、IC チップなどの DC - DC 変換器の他の構成要素の 1 つまたは複数と共に少なくとも部分的に積層されてもよい。インダクタは、PWM コントローラ、ドライバ、スイッチなどの DC - DC 変換器の他の構成要素の 1 つまたは複数と共に少なくとも部分的に積層されてもよい。いくつかの実施形態において、キャパシタなどの他の表面構成要素も連結されていてもよい。したがって、チップ埋め込み型 DC - DC 変換器の構成要素も一緒に連結されていてもよい。いくつかの実施形態において、インダクタのインダクタンスは、少なくとも一部が、例えば、図 1 を参照して説明したような過電流限度に基づいて選択されてもよい。いくつかの実施形態において、過電流限度は、少なくとも一部がインダクタの飽和限度に基づいて決定され、調整され、および / またはトリムされてもよい。いくつかの実施形態において、インダクタおよび過電流限度値は、単一の人、設計者、設計チーム、および / または製造者によって決定および / または設計されていてもよい。

10

#### 【 0 1 0 0 】

ブロック 911 において、チップ埋め込み型 DC - DC 変換器はパッケージされていてもよい。このことは、単一の離散型の構成要素としてチップ埋め込み型 DC - DC 変換器をパッケージングすることを含んでいてもよい。パッケージは、DC - DC 変換器が外部インダクタまたはキャパシタ無しで動作できるように、インダクタおよびキャパシタを含んでいてもよい。

20

#### 【 0 1 0 1 】

ブロック 913 において、負荷が DC - DC 変換器に連結されていてもよい。このことは、例えば、パッケージされたチップ埋め込み型 DC - DC 変換器の出力を分離されたマザーボード上の配線を介して電子デバイスと連結することを含んでいてもよい。いくつかの実施形態において、DC - DC 変換器は、ポイントオブロードの付近に連結されて寄生効果を多少低減することができる。

30

#### 【 0 1 0 2 】

ブロック 915 において、パッケージされたチップ埋め込み型 DC - DC 変換器に電源が連結されていてもよい。したがって、チップ埋め込み型 DC - DC 変換器は、供給された電力を使用して DC 出力電圧を提供して電子デバイスに給電してもよい。

#### 【 0 1 0 3 】

ブロック 911、913 は、パッケージングすること、および、負荷装置の分離された PCB と共にパッケージングされたチップ埋め込み型 DC - DC 変換器を使用することを説明しているが、いくつかの実施形態において、ここに記載の技術は、端末装置の PCB に適用されてもよい。

40

#### 【 0 1 0 4 】

##### マルチインダクタチップ埋め込み型 DC - DC 変換器

ここに記載のチップ埋め込み型 DC - DC 変換器技術は、マルチインダクタ実装品に拡大されてもよい。このことは、2、3、4、5、6、8、16、または任意の数のインダクタと共に、例えば、デュアルバックコンバータ、デュアルブーストコンバータ、および電圧変換器を含んでいてもよい。複数インダクタは、並列に配置されていてもよい。複数インダクタの出力（例えば、並列配置において）は、キャパシタまたは LC 共振回路などのエネルギー蓄積回路と連結されていてもよい。各インダクタは、それぞれ一対のスイッチと連結されていてもよい。各一対のスイッチは、それぞれドライバにより駆動されても

50

よい。各ドライバは、他のドライバへ提供される PWM 信号とは位相がずれている PWM 信号によって駆動されてもよい。各 PWM 信号は、オン時間を有していてもよく、オン時間は、ドライバ信号の重畳された組み合わせが共通期間よりも短い実効期間を有するよう に十分に小さい割合の共通期間である。いくつかの実施形態において、マルチインダクタチップ埋め込み型 DC - DC 変換器は、ここで（例えば、図 1 に示す）開示する構成要素（例えば、スイッチ、インダクタ、集積回路の一部）の一部または全てを複製することにより形成され得る。

#### 【 0 1 0 5 】

ここに開示の種々の実施形態は、以下の特徴の 1 つ、いくつかの組み合わせ、または全てを有していてもよい。マルチインダクタチップ埋め込み型 DC - DC 変換器は、単一のインダクタチップ埋め込み型 DC - DC 変換器よりも高速かつ高効率で動作し得る。DC - DC 変換器を通る電流は、複数インダクタに沿って分割されていてもよい。熱は、複数インダクタに亘って分散されてもよい。より小さいサイズの個別インダクタを使用してもよい。電流密度は、上昇され得る。DC - DC 変換器の全体のサイズは低減されてもよい。スイッチは、より少ない回数切り替わってもよい。スイッチの平均寿命は、延長され得る。インダクタの平均寿命は、向上され得る。より少ないおよび / またはより少数の出力キャパシタが使用されてもよい。より速い過渡応答があってもよい。電流受容が変化する場合、出力電力におけるより低い変動があってもよい。DC - DC 変換器は、（例えば、数式 2 に基づき）より高い周波数で動作してもよく、および / または、より少ないインダクタを使用してもよい。DC - DC 変換器のサイズは低減されてもよい。各一対のスイッチは、効率的である最大周波数で動作してもよいが、全体的な周波数は、任意の一対のスイッチの個別周波数よりも大きくてよい。

10

#### 【 0 1 0 6 】

いくつかの実施形態において、電力損失を低減することができる。数式  $P = I^2 \times R$  を使用すると、電力損失が DC 電流 (I) と共に上昇し得ることが分かる。しかしながら、複数インダクタ間で電流を分割することにより、全体の電力損失は低減され得る。さらに、各インダクタの抵抗も低減する。例えば、2 つのインダクタ間で電流 (I<sub>o</sub>) を分割することにより、 $P = 2 \times [(I_o / 2)^2 \times R / 2] = [I_o^2 \times R] / 2$ 、電力損失を半分に低減することができる事が分かる。したがって、複数インダクタ間の分散電力搬送は、向上された効率を提供する。高い電流密度の DC - DC 変換器についての需要が増大するにつれて、マルチインダクタ、チップ埋め込み型 DC - DC 変換器は、より小さいサイズと高い電流密度とをより少ない電力損失で提供することができる。

20

#### 【 0 1 0 7 】

いくつかの実施形態において、マルチインダクタ、チップ埋め込み型 DC - DC 変換器における比較的小さいインダクタにより、要求される電流における変化に対するより迅速な過渡応答が可能になる。例えば、図 8 B に示すように、チップ埋め込み型 DC - DC 変換器は、DC 電力を C P U に提供してもよい。C P U は、重い計算負荷（例えば、すべてのコアの利用および / またはその切替周波数の上昇）を突然受けることがあり、パワーダウンにおける突然の増加を引き起こす（例えば、n s 範囲における 1 アンペアから 10 アンペアへの増大）。エネルギーは出力キャパシタ（例えば、図 1、図 2 の出力キャパシタ 111）から引き出されるため、出力キャパシタの両端電圧は、C P U により必要とされる DC 電力仕様（例えば、< 1 % の降圧）よりも早すぎるよう低下する可能性があり、停止エラーのリスクを冒す。したがって、フィードバックシステム（例えば、図 14、図 16、および図 17 に示すように）は、インダクタを介してキャパシタへ搬送される電力を増大し、電圧降下を防止するように構成されていてもよい。しかしながら、高いインダクタは、電力搬送において変化に抵抗する。マルチインダクタシステムは比較的小さいインダクタを使用するため、マルチインダクタの過渡フィードバック応答、チップ埋め込み型 DC - DC 変換器は、比較的少なく比較的大きいインダクタを有する DC - DC 変換器の過渡フィードバック応答よりも高速であってもよく、応答は、比較的小さい出力電圧降下を有する。比較的高い切替周波数を有するここに開示される DC - DC 変換器は、

30

40

50

比較的小さいインダクタを利用することができ、その結果、ここに記載の单一のインダクタ実施形態は、過渡負荷に対して向上した応答を有することができる。

【0108】

例示的デュアルバックコンバータ

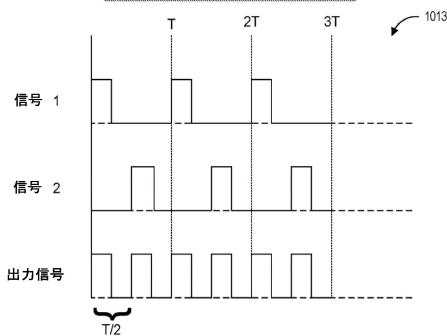

図10は、チップ埋め込み型DC - DC変換器を使用するデュアルバックコンバータ1000用の例示的デュアルインダクタ設計を示す。デュアルバックコンバータは、単一のインダクタの代わりに2つの並列のインダクタを使用することができる。

【0109】

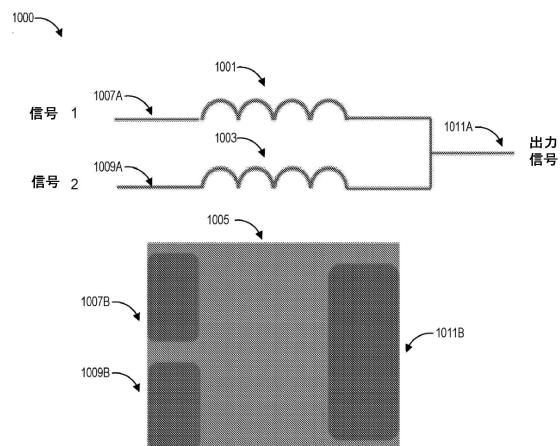

図10は、第1インダクタ1001と、第2インダクタ1003と、チップ埋め込み型ICおよび他の構成要素を有するPCB1005(図11A、11B、11Cおよび11Dに示し、図10においては不可視)を備える。第1インダクタ1001への第1入力ノード1007Aは、PCB1005における第1パッド1007Bに対応してもよい。第2インダクタ1003への第2入力ノード1009Aは、PCB1005における第2パッド1009Bに対応する。電圧出力ノード1011Aは、PCB1005上の電圧出力パッド1011Bに対応してもよい。グラフ1013は、信号1、信号2、および出力信号についての波形を示す。

10

【0110】

デュアルバックコンバータは、2つのインダクタ1001、1003を含むように構成されてもよい。2つのインダクタ1001、1003は、PCB1005上に表面実装されてもよい。種々の実施形態において、2つのインダクタ1001、1003は、並べて配置された2つの分離したインダクタであってもよく、上下に垂直に配置された2つの分離したインダクタ、または、2つのインダクタ巻き線を有する単一の磁気コアであってもよい。

20

【0111】

信号1は、第1入力ノード1007Aへ提供される。信号1は、Tの期間を有する。信号2は、第2入力ノード1009Aへ提供される。信号2も、Tの期間を有する。信号1および2は、互いに位相がずれており、期間Tの50%未満の「オン」時間有する。出力信号は、信号1および信号2の組み合わせにより形成される。各パルスについて、出力信号は、信号1および信号2と同じ「オン」時間有する。信号1および信号2の「オン」時間は同じであり、出力信号の有効期間は、半分に低減される(周波数は2倍になる)。

30

【0112】

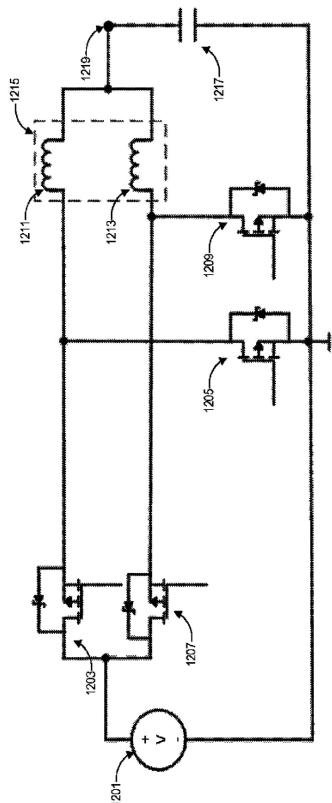

図12は、チップ埋め込み型DC - DC変換器を含むデュアルバックコンバータの例示的回路レベル回路図1200を示す。回路図は、電圧源1201、第1スイッチペアの第1スイッチ1203、第1スイッチペアの第2スイッチ1205、第2スイッチペアの第3スイッチ1207、第2スイッチペアの第4スイッチ1209、第1インダクタ1211、第2インダクタ1213、出力キャパシタ1217、および電圧出力ノード1219を備える。

30

【0113】

インダクタ1211、1213のペア1215は、PCBの外部と連結されてもよい。スイッチ1203、1205、1207、1209は、独立型チップとして、または、他の構成要素(例えば、ドライバ、PWMコントローラ、他のスイッチ)を含むICチップの一部としてPCBに埋め込みされてもよい。キャパシタ1217は、PCBの外側またはPCBの内側と連結されていてもよい。インダクタ1211および1213は、共用される共通コアを使用してもよく、または、分離されたコアを使用してもよい。

40

【0114】

電圧源1201は、第1スイッチ1203のドレインと連結されていてもよい。第1スイッチ1203のソースは、第1インダクタ1211の第1ノードと連結されていてもよい。前記第1スイッチ1203のソースは、第2スイッチ1205のドレインと連結されていてもよい。第1スイッチ1203および第2スイッチ1205のゲートは、ドライバ(図12には示さず)と連結されていてもよい。ドライバは、逆制御信号を第1スイッチ

50

1203および第2スイッチ1205へ駆動することができ、第1スイッチ1203および第2スイッチ1205の一方がオンであり他方がオフであるように第1スイッチ1203および第2スイッチ1205を交互にオンおよびオフする。第1スイッチ1203がオンであり、第2スイッチ1205がオフである間、エネルギーは、電圧源1201からインダクタ1211および/またはキャパシタ1217へ提供されてもよく、ただし、エネルギーは格納されてもよく、出力電圧を上昇させる。第1スイッチ1203がオフであり、第2スイッチ1205がオフである間、エネルギーは、インダクタ1211および/またはキャパシタ1217から放出されてもよく、出力電圧が低減する。

#### 【0115】

電圧源1201は、第3スイッチ1207のドレインと連結されていてもよい。第3スイッチ1207のソースは、第2インダクタ1213の第1ノードと連結されていてもよい。前記第3スイッチ1207のソースは、第4スイッチ1209のドレインと連結されていてもよい。第3スイッチ1207および第4スイッチ1209のゲートは、ドライバ(図12には示さず)と連結されていてもよい。したがって、ドライバは、逆制御信号を第3スイッチ1207および第4スイッチ1209へ駆動することができ、第3スイッチ1207および第4スイッチ1209の一方がオンであり他方がオフであるように第3スイッチ1207および第4スイッチ1209を交互にオンおよびオフしてもよい。第3スイッチ1207がオンであり、第4スイッチ1209がオフである間、エネルギーは、電圧源1201からインダクタ1213および/またはキャパシタ1217へ提供されてもよく、ここにエネルギーを格納することができ、出力電圧を上昇させる。第3スイッチ1207がオフであり、第4スイッチ1209がオンである間、エネルギーは、インダクタ1213および/またはキャパシタ1217から放出されてもよく、出力電圧が低減する。

10

#### 【0116】

第1インダクタ1211の第2ノードおよび第2インダクタ1213の第2ノードは、出力ノード1219と連結されていてもよく、平滑キャパシタとも称される出力キャパシタ1217とも連結されていてもよい。出力ノード1219における電圧は、キャパシタ1217において格納されたエネルギーによって影響を受ける可能性がある。キャパシタ1217に格納されたエネルギーは、キャパシタ1217から、第1インダクタ1211の第2ノード、または、第2インダクタ1213の第2ノードから電流が流れると上昇する可能性がある。したがって、小さい信号リップルは、スイッチがエネルギーを提供または放出するのに応じてキャパシタへ提供される。

20

#### 【0117】

第1ペアのスイッチ1203、1205は、第2ペアのスイッチ1207、1209から位相をずらして駆動されてもよい。第1ペアのスイッチ1203、1205は、第2ペアのスイッチ1207、1209と同じ周波数および同じ周期で駆動されてもよい。したがって、いくつかの実施形態において、上側スイッチ1203、1207の最大で1つが任意の時間にオンになる。4つのスイッチ1203、1205、1207、1209は、互いに全て位相がずれている4つの各信号で駆動されてもよい。第1ペアのスイッチ1203、1205および第1インダクタ1211は、第2ペアのスイッチ1207、1209および第2インダクタ1213と並列にDCバックニング機能を提供する。

30

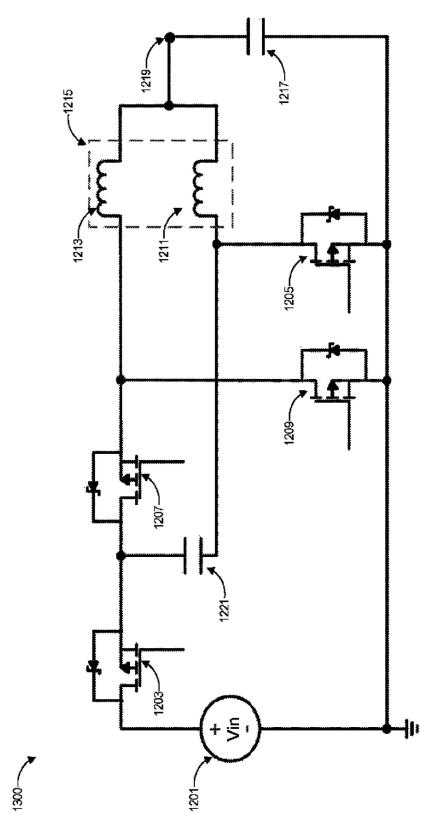

#### 【0118】

図13Aは、チップ埋め込み型DC-DC変換器を含むDC-DC変換器の例示的回路レベルの回路図1300を示す。図13Aの構成要素は、図12の構成要素と同じであるかまたは同様であってもよい。図13AのDC-DC変換器は、増設のキャパシタ1221を備えていてもよい。キャパシタ1221は、スイッチ1203がオンされた場合にエネルギーを格納することができる。いくつかの実施形態において、キャパシタ1221が電圧源1201の電圧の約半分まで充電するように、エネルギーが格納されてもよい。スイッチ1203がオンされる場合、スイッチ1207がオフされ、スイッチ1205がオフされ、過渡電流は、キャパシタ1221を介してインダクタ1211へ流れ得る。スイッチ1207がオンされ、スイッチ1209がオフされると、キャパシタ1221は、ス

40

50

イッチ1207に電力を提供し、インダクタ1213へ電流を流すことができる。キャパシタ1221も、スイッチ1207とスイッチ1205との間のAC連結キャパシタとして作用し得る。図13における構成要素も、図12のものに比べて変更されたレイアウトで配置されているが、図12およびズ13AのDC-DC変換器は、同様に機能し得る。インダクタ1211および1213は、共用される共通コアを使用してもよく、または、分離されたコアを使用してもよい。

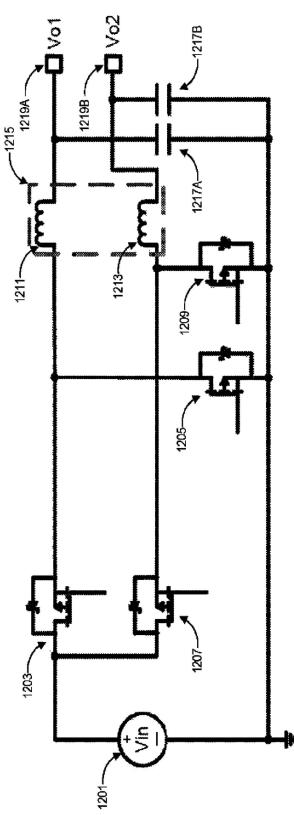

#### 【0119】

図13Bは、チップ埋め込み型DC-DC変換器を含むDC-DC変換器の例示的回路レベルの回路図1350を示す。図13の構成要素は、図12の構成要素と同じであるかまたは同様であってもよい。第1ペアのスイッチ1203、1205および第1インダクタ1211は、第1キャパシタ1217Aに連結され、第1出力ノード1219Aにおける第1出力電圧を提供するように構成されてもよい。第2ペアのスイッチ1207、1209および第2インダクタ1213は、第2キャパシタ1217Bに連結され、第2出力ノード1219Bにおける第2出力電圧を提供するように構成されてもよい。第1および第2出力ノード1219A、1219Bにおける出力電圧は、同じ電圧であってもよく、または、異なる電圧であってもよい。いくつかの実施形態において、ドライバ（例えば、図1に示し、図13Bには示さず）は、異なる電圧が異なるノード1219A、1219Bへ提供されるように、第1ペアのスイッチ1203、1205および第2ペアのスイッチ1207、1209を個別に駆動することができる。インダクタ1211および1213は、共用される共通コアを使用してもよく、または、分離されたコアを使用してもよい。

10

20

#### 【0120】

図13Aおよび13Bに示す実施形態は、1つまたは複数のICダイ上に実施されてもよい。例えば、図13Aにおいて、スイッチ1203、1205、1207、1209は、単一のIC（例えば、モノリシックのeGaNIC）において全てが含まれてもよい。いくつかの実施形態において、スイッチ1203、1205、1207、1209は、2つまたはそれ以上の別個の装置間で分割されていてもよい。図13Aおよび13Bに示す実施形態は、1つまたは複数のドライバおよび/またはPWMコントローラにより制御されてもよい。例えば、第1PWMコントローラは、第1ドライバと連結されていてもよく、第1ドライバは、スイッチ1203、1205、1207、1209のうち第1ペアのスイッチを駆動し、第2PWMコントローラは、第2ドライバと連結されていてもよく、第2ドライバは、スイッチ1203、1205、1207、1209うち第2ペアのスイッチを駆動する。

30

#### 【0121】

##### デュアルバックコンバータに埋め込まれたチップのための例示的設計

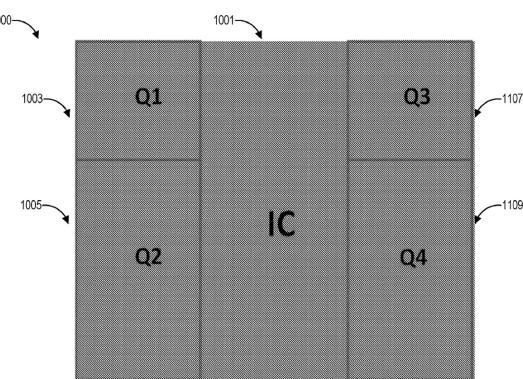

図11Aは、デュアルバックコンバータにおける埋め込み型チップ用の第1例示的レイアウト設計1100を示す。この設計は、IC部分1101、第1スイッチペアの第1電力スイッチ1103、第1スイッチペアの第2電力スイッチ1105、第2スイッチペアの第3電力スイッチ1107、および第2スイッチペアの第4電力スイッチ1109を備える。

40

#### 【0122】

図11Aの実施形態において、IC部分1101、第1電力スイッチ1103、第2電力スイッチ1105、第3電力スイッチ1107、および第4電力スイッチ1109は、全て同じICチップに含まれている。IC部分1101は、PWMコントローラおよびドライバを含んでいてもよい。ドライバは、第1スイッチペアを第2スイッチペアとは位相をずらして駆動するように構成されていてもよい。ドライバは、第1スイッチペアおよび第2スイッチペアを、同一周期および同一周波数で駆動するように構成されていてもよい。いくつかの実施形態において、IC部分1101は、第1スイッチペアを駆動するように構成された第1ドライバと、第2スイッチペアを駆動するように構成された第2ドライバとを備える。PWMコントローラは、第1PWM信号を第1ドライバへ提供し、

50

第2 PWM信号を第2ドライバへ提供し、第1および第2PWM信号は、互いに位相がずれてもよい。

【0123】

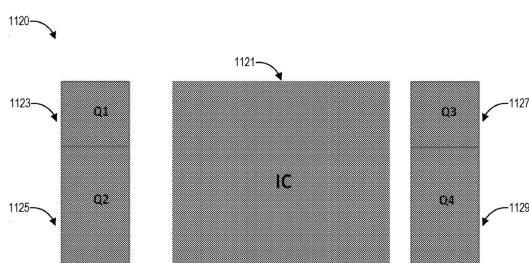

図11Bは、デュアルバックコンバータにおける埋め込み型チップ用第2例示的レイアウト設計1120を示す。この設計は、ICチップ1121、第1スイッチペアの第1電力スイッチ1123、第1スイッチペアの第2電力スイッチ1125、第2スイッチペアの第3電力スイッチ1127、および第2スイッチペアの第4電力スイッチ1129を備える。

【0124】

第1電力スイッチ1123および第2電力スイッチ1125は、モノリシックのeGANスイッチチップなどの第1モノリシックのスイッチチップの一部であってもよい。第3電力スイッチ1127および第4電力スイッチ1129は、第2モノリシックのスイッチチップの一部であってもよい。いくつかの実施形態において、第1モノリシックのスイッチペアおよび第2モノリシックのスイッチペアは、同じモノリシックのチップの一部であってもよい。いくつかの実施形態において、第1モノリシックのスイッチペアおよび第2モノリシックのスイッチペアは分離モノリシックのチップの一部であってもよい。ICチップ1121および分離モノリシックのチップは、PCBに埋め込みされていてもよい。IC部分1121は、PWMコントローラおよびドライバを含んでいてもよい。ドライバは、第1モノリシックスイッチ対を第2モノリシックスイッチ対とは位相をずらして駆動するように構成されていてもよい。ドライバは、第1モノリシックスイッチ対および第2モノリシックスイッチ対を、同一周期および同一周波数で駆動するように構成されていてもよい。ドライバは、各モノリシックスイッチペアにおけるスイッチを交互に駆動するように構成されていてもよい。いくつかの実施形態において、IC部分1121は、第1モノリシックスイッチ対を駆動するように構成された第1ドライバと、第2モノリシックスイッチ対を駆動するように構成された第2ドライバとを備える。PWMコントローラは、第1PWM信号を第1ドライバへ提供し、第2PWM信号を第2ドライバへ提供し、第1および第2PWM信号は、互いに位相がずれている。

10

20

30

【0125】

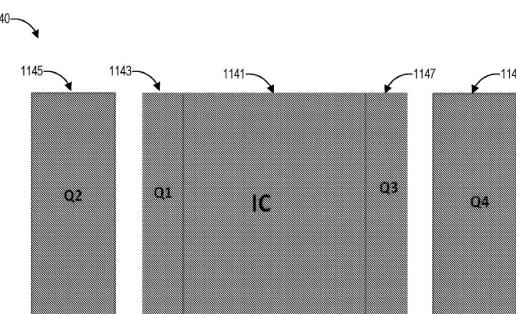

図11Cは、デュアルバックコンバータにおける埋め込み型チップ用第3例示的レイアウト設計1140を示す。この設計は、ICチップ部1141、第1スイッチペアの第1電力スイッチ1143、第1スイッチペアの第2電力スイッチ1145、第2スイッチペアの第3電力スイッチ1147、および第2スイッチペアの第4電力スイッチ1149を備える。

40

【0126】

ICチップ部1141、第1電力スイッチ1143および第3電力スイッチ1147は、第1ICチップの一部であってもよい。第2電力スイッチ1145および第4電力スイッチ1149は、第1ICチップからは分離されたモノリシックのeGANチップなどの分離チップであってもよい。いくつかの実施形態において、第2電力スイッチ1145および4つの電力スイッチ1149は、同じモノリシックのチップの一部であってもよい。チップの1つ、一部、または全ては、PCBに埋め込みされていてもよい。IC部分1141は、PWMコントローラおよびドライバを含んでいてもよい。ドライバは、第1スイッチペアを第2スイッチペアとは位相をずらして駆動するように構成されていてもよい。ドライバは、第1スイッチペアおよび第2スイッチペアを、同一周期および同一周波数で駆動するように構成されていてもよい。ドライバは、各スイッチペアにおけるスイッチを交互に駆動するように構成されていてもよい。いくつかの実施形態において、IC部分1141は、第1スイッチペアを駆動するように構成された第1ドライバと、第2スイッチペアを駆動するように構成された第2ドライバとを備える。PWMコントローラは、第1PWM信号を第1ドライバへ提供し、第2PWM信号を第2ドライバへ提供し、第1および第2PWM信号は、互いに位相がずれている。

【0127】

50

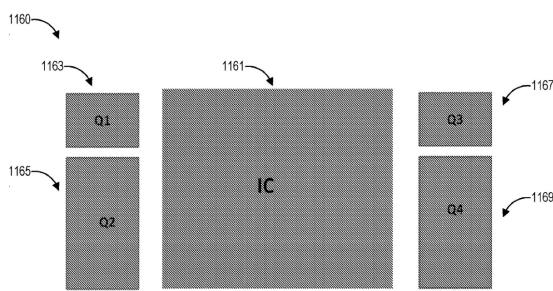

図11Dは、デュアルバックコンバータにおける埋め込み型チップ用第4例示的レイアウト設計1160を示す。この設計は、ICチップ部1161、第1スイッチペアの第1電力スイッチ1163、第1スイッチペアの第2電力スイッチ1165、第2スイッチペアの第3電力スイッチ1167、および第2スイッチペアの第4電力スイッチ1169を備える。

【0128】

ICチップ部1161、第1電力スイッチ1163、第2電力スイッチ1165、第3電力スイッチ1167、および第4電力スイッチ1169は、分離ICチップの一部であつてもよい。分離ICチップの1つ、一部、または全ては、PCBに埋め込みされていてもよい。IC部分1161は、PWMコントローラおよびドライバを含んでいてもよい。ドライバは、第1スイッチペアを第2スイッチペアとは位相をずらして駆動するように構成されていてもよい。ドライバは、第1スイッチペアおよび第2スイッチペアを、同一周期および同一周波数で駆動するように構成されていてもよい。ドライバは、各スイッチペアにおけるスイッチを交互に駆動するように構成されていてもよい。いくつかの実施形態において、IC部分1161は、第1スイッチペアを駆動するように構成された第1ドライバと、第2スイッチペアを駆動するように構成された第2ドライバとを備える。PWMコントローラは、第1PWM信号を第1ドライバへ提供し、第2PWM信号を第2ドライバへ提供し、第1および第2PWM信号は、互いに位相がずれている。

【0129】

構成要素1161、1163、1165、1167および1169の任意の組み合わせなど種々の追加の構造が可能であり、任意の数のICチップに組み合わせあつてもよい。いくつかの実施形態において、マルチインダクタDC-DC変換器は、個別またはマルチインダクタDC-DC変換器の個別パッケージを組み合わせることにより作成されてもよい。

【0130】

マルチインダクタチップ埋め込み型DC-DC変換器の追加の例示的な特徴

いくつかのチップ埋め込み型DC-DC変換器において、インダクタは、最大の物理的な構成要素である。マルチインダクタチップ埋め込み型DC-DC変換器は、並列に連結された複数の比較的小さいインダクタを代わりに使用してもよい。スイッチは、複数のインダクタが位相をずらしてエネルギーを充電および放電するように、位相をずらして駆動されてもよい。いくつかの実施形態において、複数のインダクタの出力は、複数のインダクタの出力リップルが任意の個別インダクタの出力リップルよりも高い周波数であるように並列に連結される。いくつかの実施形態において、複数のインダクタの出力は並列に連結され、複数のインダクタの出力リップルが任意の個別インダクタの出力リップルよりも高い周波数である

【0131】

いくつかの実施形態においては、複数インダクタDC-DC変換器の出力リップル周波数は、比較的高くてよく、1つまたは複数の出力キャパシタの数および/または容量は低減されてもよく、比較的小さい1つまたは複数の出力キャパシタを使用することができる。

【0132】

上述のように、複数インダクタシステムは、単一のインダクタシステムと比較して、比較的高い効率的切替速度を有していてもよい。いくつかの実施形態において、これは、スイッチの切替速度を上昇せずに行うことができ、代わりに、複数スイッチは、互いに位相がずれて動作し得る。したがって、個別スイッチを比較的高い非効率な切替速度に押すことなく、比較的高い効率的な切替速度が達成され得る。

【0133】

数式2によると、並列に配置された複数のインダクタの比較的高い効率的な切替速度により、複数のインダクタのインダクタンスを低減することができる。したがって、インダクタは、互いに並列に配置されて、インダクタンスを下げることができ、および/または

10

20

30

40

50

比較的小さいインダクタンスを有する比較的小さいインダクタを使用することができる。比較的小さいインダクタを使用することができるため、特に、1つまたは複数のインダクタが最大の構成要素である場合に、全体的なDC - DC変換器サイズを低減することができる。

#### 【0134】

いくつかの実施形態において、さらなる相乗効果は、比較的小さいインダクタを使用することから結果として生じる可能性があり、スイッチの切替速度が上昇する可能性があり、なぜなら、スイッチのインダクタンス負荷が低減される。このことは、比較的高い効率的な切替速度につながる可能性があり、数式2などに基づいてインダクタンスをさらに低減する。

10

#### 【0135】

いくつかの実施形態において、マルチインダクタチップ埋め込み型DC - DC変換器は、単一のインダクタDC - DC変換器における出力キャパシタよりも小さい出力キャパシタを使用することができる。

#### 【0136】

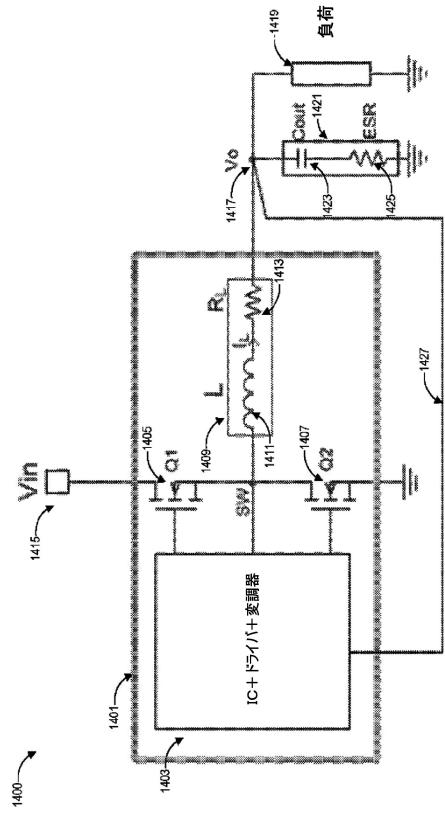

##### フィードバックを有するチップ埋め込み型DC - DC変換器の例

図14は、外部リップル電圧フィードバック回路を有する例示的チップ埋め込み型DC - DC変換器1400を示す。チップ埋め込み型DC - DC変換器1400は、ここで検討するように、ドライバおよび/または変調器を含み得る埋め込み型ICチップ1403を含んでいてもよい。ICチップは、PCB1401に埋め込みされていてもよい。チップ埋め込み型DC - DC変換器1400は、第1電力スイッチ1405、第2電力スイッチ1407、およびインダクタ1409をさらに含む。インダクタ1409は、そのインダクタンス構成要素1411およびその内部直流抵抗(DCR)構成要素1413を説明するために概略的に示す。

20

#### 【0137】

チップ埋め込み型DC - DC変換器1400は、電圧入力ノード1415において入力電圧を受信し、出力電圧ノード1417において出力電圧を提供する。出力キャパシタ1421は、出力ノード1417と連結され、出力キャパシタは、その容量性成分1423およびその等価直列抵抗(ESR)1425を示すために概略的に表される。フィードバック経路1427は、出力ノードから埋め込み型ICチップ1403へ連結されている。

30

#### 【0138】

チップ埋め込み型DC - DC変換器1400は、ここで先述のように、入力電圧を受信することができ、出力電圧を生成することができる。出力電圧は、スイッチがオンおよびオフする時に、小さい変動またはリップルを有し得る。リップル電圧( $V_{ESR}$ )は、インダクタ電流 $I_L$ にESRを乗じることにより計算されてもよい。フィードバック経路1427は、リップルおよび/またはDC出力電圧を検知する。リップルおよび/またはDC出力電圧のフィードバック指標は、埋め込み型ICチップ1403に提供されている。埋め込み型ICチップ1403における変調器は、スイッチ1405、1407を制御するためにフィードバックを使用して、出力電圧が高すぎる場合は出力電圧を低減し、出力電圧が低すぎる場合は出力電圧を上昇させることができる。

40

#### 【0139】

フィードバックシステムは、電流モード制御方式および電圧モード制御方式を使用して、デューティサイクルの広い範囲に亘ってDC - DC動作安定性を確保することができる。電流モード制御方式において、傾斜補償スキーマは、上昇したサイズおよびコストを追加する場合がある外部構成要素と共に使用され実施されてもよい。電流モード制御方式は、ループ安定性のためのタイプII補償を使用してもよく、比較的低いループ応答性を有していてもよい。電圧モード制御方式において、電圧エラーは、増幅され、フィードバックされ、補償されてもよい。

#### 【0140】

いくつかの実施形態において、変調器は、常時オン時間周波数変調方式、常時オフ時間

50

周波数変調方式、パルス幅変調方式、または他の方式を使用することができる。常時オン時間および常時オフ時間方式は、高性能を有するテーブル D C - D C 動作を提供することができる。いくつかの実施形態において、変調器にとっては、リップル電圧を検出してある程度の制御イベントをトリガすることが望ましい可能性がある。例えば、常時オン時間方式または常時オフ時間方式において、変調器は、一定のオンまたはオフ時間をそれぞれ有するオンまたはオフパルスを生成するために、A C リップルを検出することができ、これにより周波数を変調し、スイッチ 1 4 0 5、1 4 0 7 へ送信される制御信号の周期に影響する。例えば、常時オン時間方式においては、基準電圧との比較において低出力電圧の検出に応答しておよび / または十分な量のインダクタ電流リップルの検出に応答して、固定幅のオンパルスを提供して出力電圧を上昇することができる。したがって、常時オン時間方式について、各パルスは同じ継続期間をオン状態において有し、変調は、時間当たり多少のパルスを行うことにより達成される（例えば、パルス間のオフ時間は変化する可能性がある）。常時オフ時間方式は、パルス間のオフ時間が一定であることを除き、ここで説明する常時オン時間方式と同様であってもよく、変調は、オンパルスの幅によって達成され得る。別の例示的電圧モードシステムにおいて、周波数は固定されていてもよく、パルスのデューティサイクルは、変調されてもよい。変形例は、リーディングまたはトレイルエッジ変調方式を含んでいてもよい。任意の適切な変調方式を使用することができる。したがって、E S R 1 4 2 5 は、十分に大きいV E S R を変調器によって検出できるように、設計および / または選択されてもよい。

#### 【 0 1 4 1 】

ここに開示されたいくつかの実施形態は、複数の矛盾する設計課題に対する解決策を提供する。非遅延フィードバック経路は、出力電圧の変化に対して迅速な応答を提供することができる。フィードバック経路を常時オン時間または常時オフ時間方式などのいくつかの変調 / 制御方式において使用して、スイッチ 1 4 0 5、1 4 0 7 がいつオンまたはオフされるかを制御することができる。変調器によって確実に検出可能なフィードバック経路に沿って測定可能な程度に大きいV E S R 信号を提供するために、キャパシタ 1 4 2 1 のE S R 1 4 2 5 は、十分に大きいリップルが引き起こされるように設計および / または選択されていてもよい。同時に、リップル電圧を最小化することが望ましい可能性がある。D C - D C 変換器は、純粋なD C 電圧を理想的には生成できる。実際には、多くのアプリケーションは、D C - D C 変換器の出力における小さいリップルを許容するが、狭い範囲においてしか許容しない。D C 電源により給電されるいくつかの装置は、最大で 3 % のリップル、2 % リップル、1 % リップル、0 . 5 % リップル、0 . 1 % リップル、0 . 0 5 % リップル、1 0 m V リップル、5 m V リップル、3 m V リップル、1 m V リップル、0 . 5 m V リップル、より少量のリップル、または検出できない程少量のリップル、またはこれらの値のいずれかにより規定される任意の範囲を必要としてもよいが、いくつかの例ではこれらの範囲外の値を使用することもできる。例えば、いくつかのポイントオブロード装置は、D C 電源が 1 . 0 0 V のD C 出力を 1 . 0 0 V の値から 1 % ( 1 0 m V ) 未満のリップルで、または、変化で提供することを指定してもよい。非常に低いE S R キャパシタは、低リップル出力を達成するために使用されてもよい。しかしながら、リップルが低すぎると、変調器は、リップルフィードバックに基づいて動作しない場合（例えば、変調器は、ノイズからリップルを区別しない場合、不規則に動作する場合など）がある。

#### 【 0 1 4 2 】

本開示は、リップルによりトリガされる変調器、低E S R キャパシタを使用し、低リップルD C 出力を提供するD C - D C 変換器のいくつかの実施形態を含む。

#### 【 0 1 4 3 】

#### 例示的電流およびリップルグラフ

図 1 5 は、時間に対するインダクタ電流  $I_L$  および時間に対する等価直列抵抗電圧V E S R (リップル電圧とも称する) の例示的グラフ 1 5 0 0、1 5 5 0 を示す。線 1 5 0 1 は、図 1 4 のインダクタ 1 4 0 9 を通る電流  $I_L$  を示す。線 1 5 5 1 は、図 1 4 のノード 1 4 1 7 における出カリップル電圧V E S R を示す。

## 【0144】

インダクタ電流  $I_L$  は、スイッチ 1405 がオンされスイッチ 1407 がオフされる場合に増加する。  $I_L$  は、以下の数式に従って増加する。

## 【数3A】

$$I_{Lon} = \frac{V_{in} - V_{out}}{L} \times T_{on} + I_o \quad \text{数式3A}$$

10

数式3Aただし、  $V_{in}$  は、入力電圧であり、  $V_{out}$  は、出力電圧であり、  $L$  はインダクタンスであり、  $T_{on}$  はスイッチ 1405 がオンされる時間であり、  $I_o$  は初期電流である。

## 【0145】

インダクタ電流  $I_L$  は、スイッチ 1405 がオフされスイッチ 1407 がオンされる場合に低下する。  $I_L$  は、以下の数式に従って低下する。

## 【数4A】

$$I_{loff} = \frac{-V_{out}}{L} \times T_{off} + I_o \quad \text{数式4A}$$

20

ただし、  $V_{out}$  は、出力電圧であり、  $L$  はインダクタンスであり、  $T_{off}$  はスイッチ 1405 がオフされる時間であり、  $I_o$  は初期電流である。数式3および4は、一般方程式の応用版であり、  $V$  はインダクタの両端電圧であり、  $dI/dt$  は、時間に対する電流の変化率である。

## 【0146】

数式3Aおよび4Aに基づき、電流の変化率は、時間の微分係数により、以下のように決定されてもよい。すなわち、

30

## 【数3B】

$$\frac{d}{dt} I_{Lon} = \frac{V_{in} - V_{out}}{L} \quad \text{数式3B}$$

## 【数4B】

$$\frac{d}{dt} I_{loff} = \frac{-V_{out}}{L} \quad \text{数式4B}$$

40

## 【0147】

$V_{ESR}$  は、インダクタ電流  $I_L$  と共に上下に変動する。しかしながら、  $V_{ESR}$  および  $I_L$  は、異なるスルーレート（例えば、異なる傾斜）で増加および低減する。率の差は、キャパシタ 1421 の ESR により影響される。電圧は、数式  $V = I \times R_{ESR}$  にしたがって ESR をインダクタ電流  $I_L$  に乘じることによって決定されてもよい。したがって、

## 【数3C】

50

$$\frac{d}{dt} V_{on} = \frac{V_{in} - V_{out}}{L} \times R_{ESR} \quad \text{数式 3 C}$$

【数 4 C】

$$\frac{d}{dt} V_{off} = \frac{-V_{out}}{L} \times R_{ESR} \quad \text{数式 4 C}$$

10

【0148】

グラフ 1500、1550 に示すように、電流  $I_L$  が上昇および低下するにつれて、 $V_{ESR}$  も同時に、しかしながら、異なるスルーレートで（異なる傾斜で）上昇および低下する。 $V_{ESR}$  のスルーレートは、数式  $V_{ESR} = I_L \times ESR$  によると  $ESR$  に比例し、 $ESR$  に影響を受ける。したがって、低  $ESR$  値のためには、 $V_{ESR}$  は、たとえ  $I_L$  が大きくても小さい振幅を有していてもよい。例えば、インダクタ電流  $I_L$  は 3.0 A の振幅で 1.5 A から 4.5 A へ変動するように、50% リップルで 3.0 A である。低い  $ESR$  が 1 m であれば、 $V_{ESR}$  は、-1.5 mV から 1.5 mV の間で変動する場合があるが、これは、いくつかの変調器にとっては小さすぎて信頼性のある使用ができない、および/または、信頼性のある使用が困難である。また、 $V_{ESR}$  は、正と負との間で変化し、一方、電流は正のままである。

20

【0149】

例示的低  $ESR$ 、低リップル、チップ埋め込み型 DC - DC 変換器

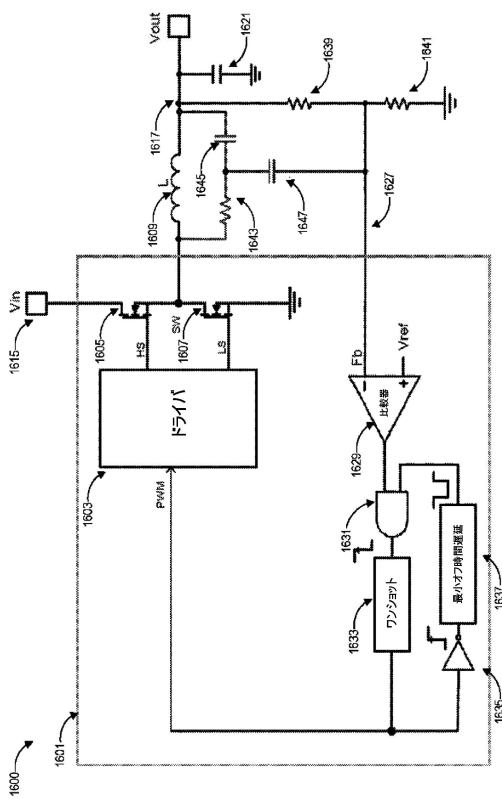

図 16 は、外部リップル電圧フィードバック回路 1600 を有する例示的チップ埋め込み型 DC - DC 変換器を示す。図 16 の実施形態は、PCB 1601、ドライバ 1603、第 1 電力スイッチ 1605（eGaN スイッチなど）、第 2 電力スイッチ 1607（eGaN スイッチなど）、インダクタ 1609、出力キャパシタ 1621、および出力ノード 1617 を含んでいてもよい。図 16 は抵抗器 1643、キャパシタ 1645、AC バイパスキャパシタ 1647、フィードバック経路 1627、比較器 1629、AND ゲート 1631、ワンショット回路 1633、インバーター 1635、最小時間遅延カウンタ 1637、抵抗器 1639、および抵抗器 1641 をさらに備える。

30

【0150】

出力キャパシタ 1621 は、1つまたは複数の低  $ESR$  キャパシタであってもよい。低  $ESR$  効果は、有効な並列  $ESR$  が低減されるように複数のキャパシタを並列に連結することにより達成されてもよい。例えば、各キャパシタは、m 範囲（例えば、1 m、10 m、100 m）における、または、より低い  $\mu$  範囲（例えば 10  $\mu$ 、100  $\mu$ ）において  $ESR$  を有していてもよく、並列なキャパシタの構造は、有効な並列  $ESR$  をより一層低減してもよい。低  $ESR$  の結果として、ノード 1617 におけるリップル電圧はフィードバックのための信頼性のある使用には小さすぎる可能性があるが、低いリップル DC 出力がノード 1617 に提供される。例えば、インダクタを通る 1.5 A リップルは、1 m  $ESR$  キャパシタが使用される場合、1.5 mV のリップルしか引き起こさない場合がある。1つまたは複数の出力キャパシタ 1621 は、合計  $ESR$  が 1000 m、100 m、10 m、1 m、100  $\mu$ 、これらの間の任意の値、これらの値のいずれかにより規定される任意の範囲、またはより低い  $ESR$  を有していてもよいが、いくつかの例においてはこれらの範囲外の値が使用されてもよい。いくつかの実施形態において、DC - DC 変換器の出力電圧は、3% 以下、2%、以下、1% 以下、0.5% 以下、0.1% 以下、0.05% 以下、10 mV 以下、5 mV 以下、3 mV 以下、1 mV 以下

40

50

、0.5 mV以下のAC電圧リップル、より低い値のリップル、確実に検出できないリップル、検出できないほど低い量のリップル、またはこれらの値のいずれかにより規定される任意の範囲を有していてもよいが、いくつかの例においては、これらの範囲外の値が使用されてもよい。ここで検討される低いESRおよび低いリップル値は、図17の実施形態に対するのと同様に他の実施形態にも関連していてもよい。

#### 【0151】

リップルを検知しフィードバック電圧を提供するために、抵抗器1643は、キャパシタ1645と直列に連結されてもよく、抵抗器1643およびキャパシタ1645の直列組み合わせはインダクタ1609の両端に並列に連結されてもよい。キャパシタ1645はDC信号をブロックする。リップルなどのAC信号は、依然として検知され得る。キャパシタ1645および抵抗器1643は、AC信号のための分圧器を形成し、検知されたリップルは、ACバイパスキャパシタ1647を介してフィードバック経路1627へ通ることができる。抵抗器1643およびキャパシタ1645の値は、数式5を満たすように設定されてもよい。

#### 【数5】

$$\frac{L}{DCR_L} = Rx \times Cx \quad \text{数式5}$$

10

20

ただし、Lはインダクタ1609のインダクタンスの値であり、DCRLは、インダクタ1609の直流抵抗（「DCR」）であり、Rxは、抵抗器1643の抵抗であり、Cxはキャパシタ1645の容量である。したがって、回路は、ESR値とは独立してインダクタ電流リップルを測定可能に、かつ、確実に検知するように提供されてもよい。

#### 【0152】

抵抗器1639および1641は、出力ノード1617に連結された分圧器を形成してもよい。分圧器は、出力ノード1617における電圧出力を分割してもよい。いくつかの実施において、出力ノード1617におけるリップルは、ノイズ閾値の範囲内において小さく、検出することが困難である可能性があり、または、それ以外の場合は、出力キャパシタ1621のESRが低いため、変調目的のためには信頼性がない。したがって、分圧器は、DC分圧器として主として作用してもよい。

30

#### 【0153】

フィードバック経路1627は分圧器に連結されてDC電圧を受信し、ACバイパスキャパシタ1647にも連結されてリップル電圧を検知する。フィードバック経路は、比較器1629とも連結され、基準電圧と比較される。基準電圧は、バンドギャップ発生器、水晶素子、デジタルアナログ変換器（「DAC」）、電池、などの基準電圧発生器（図示せず）により提供されてもよい。いくつかの実施形態において、DACは、基準電圧を提供するために使用され、デジタル信号は、DACへ提供されて所望の基準電圧を設定することができる。

40

#### 【0154】

比較器1629は、フィードバック信号および基準電圧の比較に基づいて比較器出力信号を生成してもよい。例示的常時オン時間変調器について、比較器1629は、フィードバック信号が基準電圧を下回ると、高い出力信号を生成する場合がある。

#### 【0155】

比較器1629の出力は、ドライバ1603に供給されてもよい常時オン時間PWM信号を生成するワンショット回路1633に提供されてもよい。ワンショット回路1633の出力は、インバーター1635、最小オフ時間遅延回路1637、およびANDゲート1631にも提供されて、PWM信号が高いままであることを防止することができる。

#### 【0156】

50

抵抗器 1643、キャパシタ 1645、および AC バイパスキャパシタ 1647 の構成により、顕著な、測定可能なリップルが検出されることを可能にし、低 ESR キャパシタ 1621 にもかかわらず、そして、低出力リップルにもかかわらず、フィードバック経路 1627 へ注入されることを可能にする。したがって、検出されたリップルは、出力リップルよりも大きいことがある。フィードバック経路 1627 に注入される AC リップルは、以下により表される。すなわち、

【数 6】

$$V_{cx} = \frac{I_L \times L}{(R_x \times C_x)} \quad \text{数式 6}$$

10

ただし、 $V_{cx}$  はキャパシタ 1645 におけるリップル電圧、 $I_L$  はインダクタのピーク・トゥ・ピーク電流リップルであり、 $R_x$  は、抵抗器 1643 の抵抗であり、 $C_x$  はキャパシタ 1645 の容量である。

【0157】

いくつかの実施形態において、PCB 1601 およびその内部構成要素は、パッケージされてもよく、ユーザーは、インダクタ 1609、抵抗器 1643、キャパシタ 1645、キャパシタ 1621、キャパシタ 1645、AC バイパスキャパシタ 1647、抵抗器 1639、および抵抗器 1641 を含む回路を提供および/または構成してもよい。このような実施形態において、インダクタ 1609、抵抗器 1643、および/またはキャパシタの値は、数式 6 にしたがって選択され調整されてもよい。例えば、インダクタ 1609 がアプリケーションのために（例えば、異なるインダクタンスおよび/または DCR を有するように）変更される場合、ユーザーは、数式 6 を解き、その後、抵抗器 1643 および/またはキャパシタ 1645 をインダクタ 1609 の新規の L および DCR L 値に対応するように選択し、調達し、変更することができる。

20

【0158】

いくつかの実施形態において、図 16 に示す一部または全ての構成要素が单一のパッケージに含まれていてもよい。抵抗器 1643、キャパシタ 1645、およびインダクタ 1609 のいくつかであって全てを 1 つのパッケージに含んでいないいくつかの実施形態において、数式 6 にしたがって回路を調整する能力を制限する可能性がある。例えば、抵抗器 1643 およびキャパシタ 1645 がパッケージに含まれているがインダクタ 1609 はエンドユーザーによって選択される場合、エンドユーザーは数式 6 を満たすために特定の L および DCR L 値を有する特定のインダクタを使用するように制限され得る。このようなシステムおよび何らかの不適切に調整されたシステムにおいて、不適切に選択されたインダクタ 1609 は、システム不安定性および/または不具合を引き起こす可能性があり、このことは、DC - DC 変換器から電力を受ける構成要素を損傷する場合がある。いくつかの例においては、DC - DC 変換器にとっては、適切に調整され、エンドユーザーによる修正を必要としない単一のパッケージされた装置として提供されることが望ましいことがある。ここに開示されたいいくつかの実施形態は、単一のパッケージとしてのインダクタ 1609、抵抗器 1643、およびキャパシタ 1645 を含んでいてもよい。

30

40

【0159】

例示的低 ESR、低リップル、DC - DC 変換器

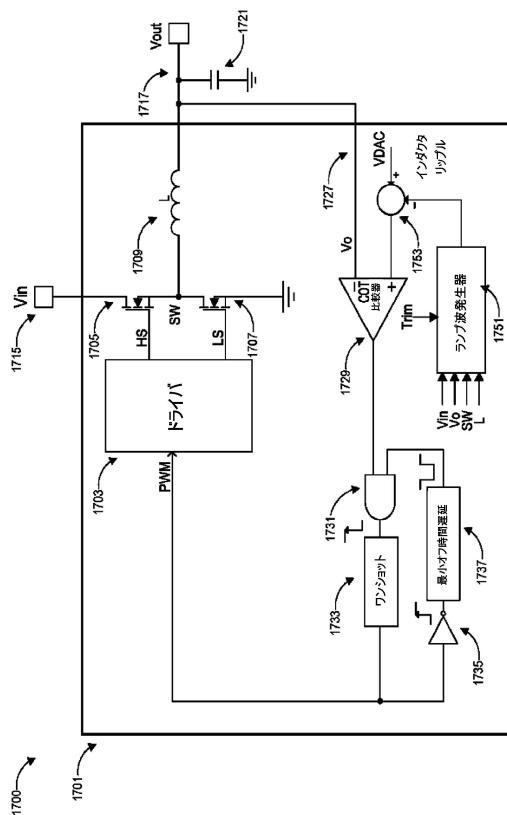

図 17 は、内部リップル電圧フィードバック回路を有する（いくつかの実施形態においてはチップ埋め込み型 DC - DC 変換器でもよい）例示的 DC - DC 変換器 1700 を示す。チップ埋め込み型 DC - DC 変換器 1700 は、ここで説明した他の実施形態と同様であってもよいパッケージ 1701、ドライバ 1703、第 1 電力スイッチ 1705、第 2 電力スイッチ 1707、およびインダクタ 1709 を備える。DC - DC 変換器 170

50

0は、電圧入力ノード1715において入力電圧を受信し、出力電圧ノード1717において出力電圧を提供することができる。出力キャパシタ1721（例えば、低ESR出力キャパシタまたは低並列ESRを有する複数の並列キャパシタ）は、出力ノード1717と連結されてもよい。フィードバック経路1727は、出力ノードから比較器1729へ連結されている。比較器出力部は、ANDゲート1731およびワンショット回路1733に連結されてPWM信号をドライバ1703へ提供されてもよい。ランプ波発生器1751は、インダクタリップル電流をエミュレートすることができ（例えば、図15における電流1501をエミュレートし）、リップル電流（例えば、図15における1551）の電圧表示を出力する。いくつかの実施形態において、ランプ波発生器1751の出力は信号結合器1753における基準電圧と組み合わせられ（例えば、加算または減算）されてもよい。いくつかの実施形態において、ランプ波発生器によって出力されたインダクタリップル信号は、基準電圧から減算される代わりにフィードバック信号に可算されてもよい。比較器1729は、ランプ波発生器1751により出力されるリップル信号および基準電圧を含む比較を実施してもよい。比較の結果はシステム（例えば、スイッチ1705および/または1707）を分割するためのフィードバックループにおいて使用されてもよい。

#### 【0160】

インダクタ1709は、図1、図3、図4A、および図4Bにおいて示したような、チップ埋め込み型DC-DC変換器パッケージに含まれていてもよい。低ESR出力キャパシタ1721は、出力ノード1717と連結されてもよい。少なくとも1つの出力キャパシタ1721は、低ESR（例えば、図16の実施形態に関してここで検討した値および範囲と同様）を有していてもよい。例えば、ESRは、m範囲（例えば、1m、10m、100m）における、または、より低いμ範囲（例えば10μ、100μ）におけるESRであってもよく、並列なキャパシタの構造は、有効並列ESRをより一層低減してもよい。出力電圧は、DC-DC変換器がいくつかの装置において必要とされる低リップル出力仕様に合うように、低いACリップルを有しているかまたは有していないてもよい（例えば、図16に関してここで検討した値および範囲と同様）。しかしながら、同じ低ACリップルは、小さい、検出することが困難である、ノイズ閾値内にある、存在しない、または、（例えば、出力キャパシタ1721のESRが低いため）変調目的では信頼性が無い場合があり、変調目的でそのACリップルを使用することは困難な場合がある。DC出力電圧は、（例えば、任意の小さな（しかしながら確実には測定できない）ACリップルと共に、または、ACリップル無しで）フィードバック経路1727上のフィードバック経路1727を介して提供される。

#### 【0161】