### (19) World Intellectual Property Organization International Bureau

#### (43) International Publication Date 14 February 2002 (14.02.2002)

#### PCT

## (10) International Publication Number WO 02/13153 A1

(51) International Patent Classification<sup>7</sup>: G07F 7/10

English

(21) International Application Number: PCT/US00/31421

(22) International Filing Date:

15 November 2000 (15.11.2000)

(25) Filing Language:

(26) Publication Language: English

(30) Priority Data:

60/223,467 7 August 2000 (07.08.2000) US 09/644,031 22 August 2000 (22.08.2000) US

- (71) Applicant: DALLAS SEMICONDUCTOR COR-PORATION [US/US]; 4401 South Beltwood Parkway, Dallas, TX 75244-3292 (US).

- (72) Inventors: CUSEY, James, P.; 3401 Canyon View Court, McKinney, TX 75070 (US). KURKOWSKI, Hal; 4316 Joshua Drive, Dallas, TX 75287 (US).

- (74) Agents: DWORK, Stuart, D. et al.; Jenkens & Gilchrist, P.C., 3200 Fountain Place, 1445 Ross Avenue, Dallas, TX 75202-2799 (US).

- (81) Designated States (national): AE, AG, AL, AM, AT, AT (utility model), AU, AZ, BA, BB, BG, BR, BY, BZ, CA, CH, CN, CR, CU, CZ, CZ (utility model), DE, DE (utility model), DK, DK (utility model), DM, DZ, EE, EE (utility model), ES, FI, FI (utility model), GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KR (utility model), KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NO, NZ, PL, PT, RO, RU, SD, SE, SG, SI, SK, SK (utility model), SL, TJ, TM, TR, TT, TZ, UA, UG, UZ, VN, YU, ZA, ZW.

- (84) Designated States (regional): ARIPO patent (GH, GM, KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZW), Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BE, CH, CY, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE, TR), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, GW, ML, MR, NE, SN, TD, TG).

#### Published:

with international search report

[Continued on next page]

(54) Title: SECURITY DEVICE AND METHOD

(57) Abstract: A security device is disclosed. In one embodiment, the security device includes a memory device comprising having a first memory portion configured to store a device ID; and a second memory portion configured to store a device secret. The security device further includes a processor connected to the memory device wherein the processor is configured to read the stored device ID from the first memory portion and the stored device secret from the second memory portion and perform a nonreversible computation using the stored device ID, the stored device secret, and a challenge as seeds. Additionally, the security device includes a communication circuit connected to the processor, the communication circuit configured to receive the challenge from a host device and to communicate a result of the nonreversible computation performed by the processor.

VO 02/13153 A

### WO 02/13153 A1

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

#### SECURITY DEVICE AND METHOD

#### FIELD OF THE INVENTION

5

The present invention relates to automatic information systems and methods and in particular, but not by way of limitation, to systems and methods for positively identifying a device/user and verifying the integrity of relevant data associated with the device/user.

#### RELATED APPLICATIONS/PATENTS

The following commonly owned and assigned United States patents are incorporated by reference:

| 10 | 5,306,961 | Low-power integrated circuit with selectable battery modes                                                                                                       |

|----|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | 5,679,944 | Potable electronic module having EPROM memory, systems and processes                                                                                             |

|    | 5,764,888 | Electronic micro identification circuit that is inherently bonded to someone or something                                                                        |

| 15 | 5,831,827 | Token shaped module for housing an electronic circuit                                                                                                            |

|    | 5,832,207 | Secure module with microprocessor and co-processor                                                                                                               |

|    | 5,940,510 | Transfer of valuable information between a secure module and another module                                                                                      |

| 20 | 5,949,880 | Transfer of valuable information between a secure module and another module                                                                                      |

|    | 5,978,927 | Method and system for measuring a maximum and minimum response time of a plurality of devices on a data bus and adapting the timing of read and write time slots |

|    | 5,994,770 | Portable electronic data carrier                                                                                                                                 |

| 25 | 5,998,858 | Microcircuit with memory that is protected by both hardware and software                                                                                         |

|    | 6,016,255 | Portable data carrier mounting system                                                                                                                            |

#### **BACKGROUND OF THE INVENTION**

5

10

15

20

25

With the public's ever increasing reliance upon electronic data, the integrity of that data is becoming extremely critical. Many present day systems attempt to guarantee the integrity of such data through encryption and complicated monitoring means. Although these systems are generally effective, they are often expensive and unnecessary in that they consume too much energy and/or use too many processor cycles. Additionally, those systems that include encryption technology often face export restrictions that delay or prevent the widespread proliferation of a developed technology.

For many applications, the secrecy of the data may not be as important as the integrity of the data or may not be important at all. That is, in some situations the data can be known to the public but should not be alterable by the public. For example, the fact that \$10 is stored on a transit card is not important. The public can know this fact without any harm. However, significant harm will occur if the transit card is fraudulently changed to show a value of \$100 dollars rather than \$10.

Accordingly, a device and method are needed that store electronic data, guarantee the integrity of that electronic data, and guarantee the integrity of any changes to that electronic data in an efficient manner. Additionally, a device and method are needed for overcoming the other problems presently associated with securely storing and transmitting electronic data.

#### BRIEF DESCRIPTION OF THE DRAWINGS

Various objects and advantages and a more complete understanding of the present invention are apparent and more readily appreciated by reference to the following Detailed Description and to the appended claims when taken in conjunction with the accompanying Drawings wherein:

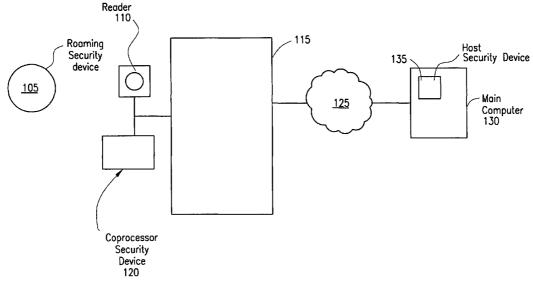

FIGURE 1 illustrates one implementation of the present invention that utilizes a roaming security device;

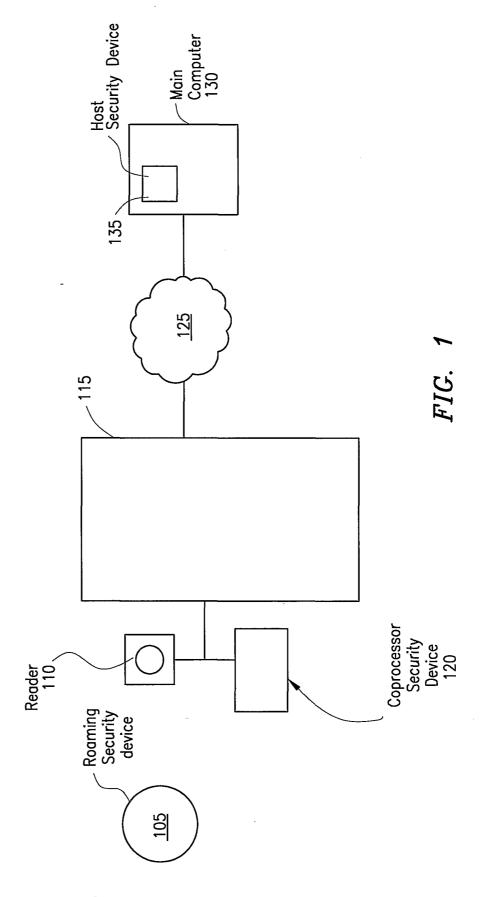

FIGURES 2A and 2B illustrate two different form factors into which a security device can be incorporated;

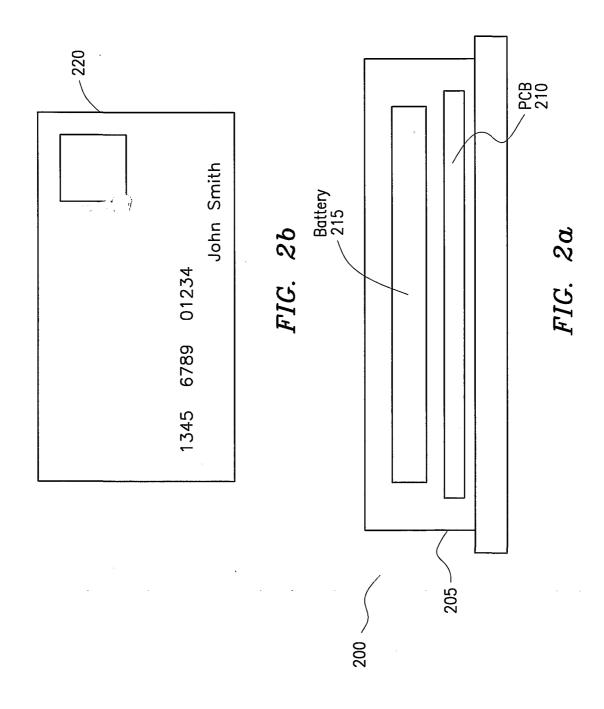

FIGURE 3A is a schematic of the components of a roaming security device;

FIGURE 3B illustrates one embodiment of the memory component of the roaming security device shown in FIGURE 3A;

FIGURE 3C illustrates one embodiment of the data page portion of the memory component shown in FIGURE 3B;

FIGURE 3D illustrates one embodiment of the device secrets portion of the memory component shown in FIGURE 3B;

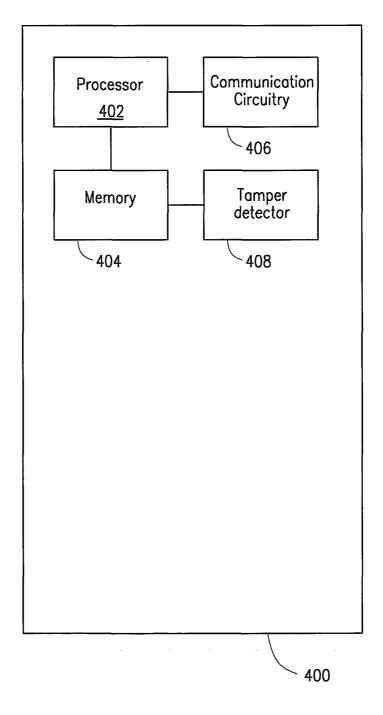

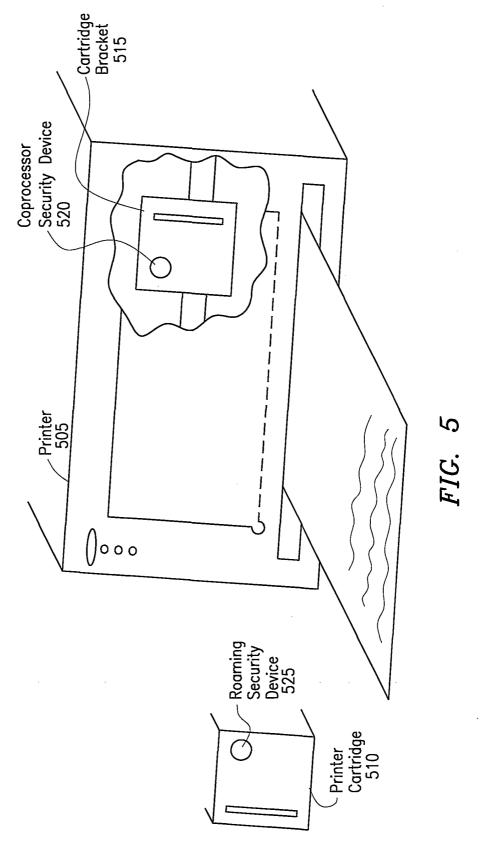

FIGURE 4 is a schematic of the components of a coprocessor security device; FIGURE 5 illustrates a roaming security device and a coprocessor security device incorporated into a printer and printer cartridge;

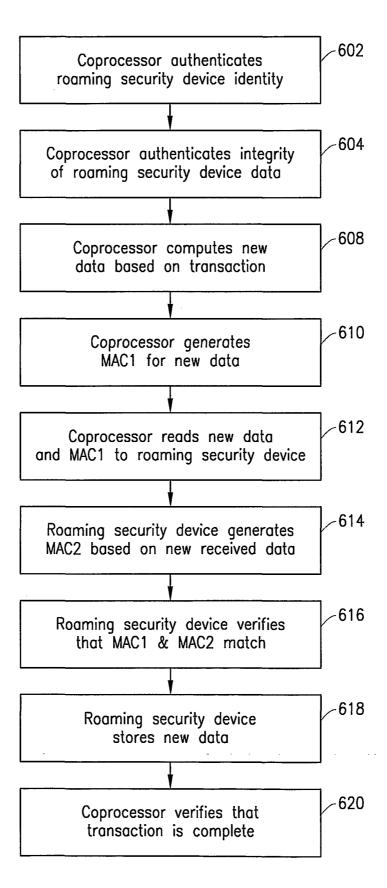

FIGURE 6A is a flowchart demonstrating a transaction between a roaming security device and a coprocessor security device;

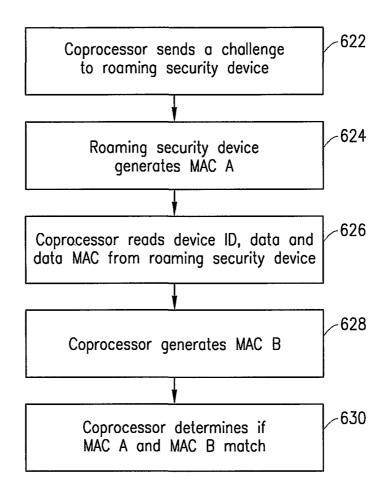

FIGURE 6B is a flowchart demonstrating in more detail the method of security device authentication shown in FIGURE 6A;

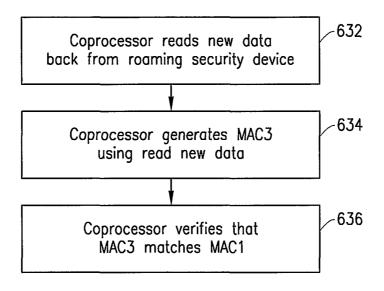

FIGURE 6C is a flowchart demonstrating in more detail the method of verifying the completion of the transaction illustrated in FIGURE 6A;

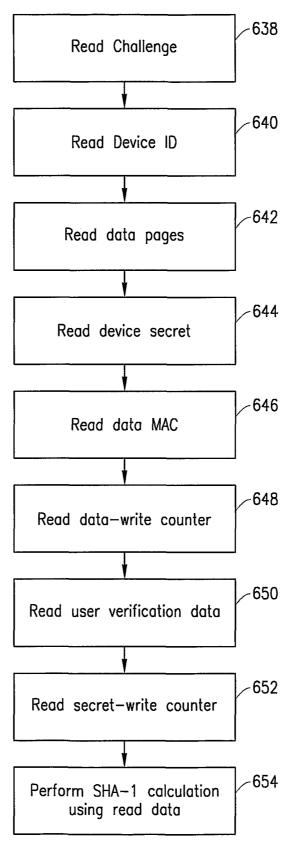

FIGURE 6D is a flowchart demonstrating a method of generating a hash result used, for example, in the transaction illustrated in FIGURE 6A;

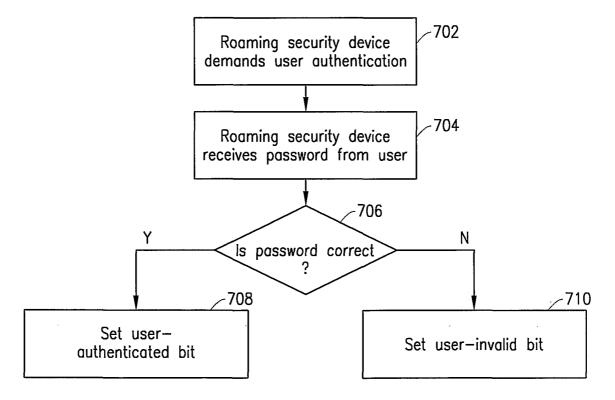

FIGURE 7 is a flowchart demonstrating a method of verifying the identity of a user to a security device; and

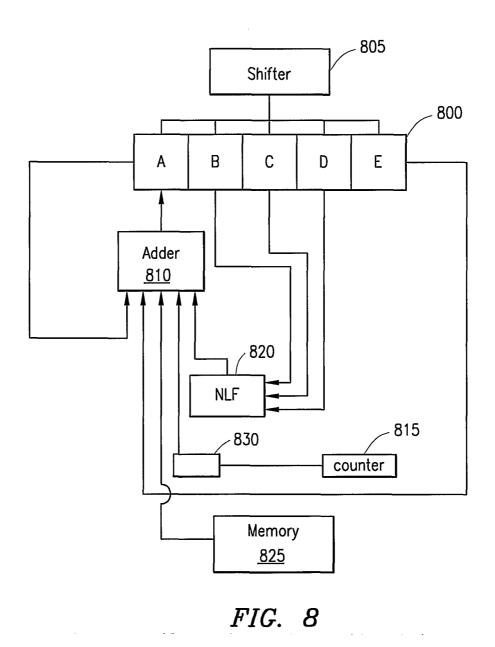

FIGURE 8 is a block diagram of a device for computing a SHA-1 computation.

#### **DETAILED DESCRIPTION**

5

10

15

20

25

30

Although the present invention is open to various modifications and alternative constructions, a preferred exemplary embodiment that is shown in the drawings is described herein in detail. It is to be understood, however, that there is no intention to limit the invention to the particular forms and/or step sequences disclosed. One skilled in the art can recognize that there are numerous modifications, equivalences and alternative constructions that fall within the spirit and scope of the invention as expressed in the claims.

Referring now to FIGURE 1, there is illustrated an overview of one implementation of the present invention that utilizes a roaming security device 105. The roaming security device 105 can be associated with a person (e.g., key chain, ID card,

5

10

15

20

25

30

jewelry, etc.) or a device (e.g., furniture, printer, printer cartridge, etc.) and can be configured to securely store data. Additionally, the roaming security device can be configured to securely interface with a reader 110, which can be for example, at or in a host device 115 such as a vending machine, toll booth, printer, computer system, security door, etc.

Because the roaming security device 105 can carry valuable data such as monetary value, it is important that any data transferred between the roaming security device 105 and the host device 115 be protected against alterations. In one embodiment, the data is encrypted prior to transfer between the roaming security device 105 and the host device 115. In the preferred embodiment, however, the data is used (along with secret data known only to the roaming security device 105 and the coprocessor security device 120) to seed a nonreversible algorithm, such as the SHA-1 algorithm. (In this context, a nonreversible algorithm is intended to refer to an algorithm that produces a result, wherein the input to the algorithm is extremely difficult or impossible to determine from the result.) The result of this algorithm is sent along with the associated data--but not the secret--from the roaming security device 105 to the coprocessor security device 120. The coprocessor security device 120, which may or may not be the same type of device as the remote security device 105, can then perform the same hashing algorithm using the received data and the locally stored secret. If the result computed by the coprocessor security device 120 matches the result computed by the roaming security device 105, then the roaming security device 105 is likely legitimate and the data contained therein valid.

As can be appreciated by those skilled in the art, the host device 115 can take the form of most any device both portable and stationary. Additionally, the reader within the host device 115 can operate in a variety of ways to read data from the roaming security device 105 including, but not limited to, direct contact transfer, proximity transfer, and single wire protocol transfers.

Furthermore, in one embodiment, the host device 115 is connected through a network 125, or otherwise, to a main computer 130. This main computer 130 can collect transaction information or monitor the host device 115. To guarantee the integrity of data transferred between the host device 115 and the main computer 130, a security device 135 can be incorporated into the main computer 130. The coprocessor security

5

10

15

20

25

30

device 120, in this embodiment, acts like a roaming security device in its interaction with the host computer's security device 135.

Referring now to FIGURES 2A and 2B, there are illustrated two of the different form factors into which a security device can be incorporated. FIGURE 2A, for example, illustrates a token form factor 200 for a security device. This form factor consists of a sealed metal housing 205 that encases a printed circuit board (PCB) 210 and a battery 215. (This form factor is based upon Dallas Semiconductor's I-button and is described in, for example, U.S. Patent 5,994,770 titled *Portable Electronic Data Carrier.*) Any attempt to access the circuitry on the PCB 210 will likely result in the destruction of any data stored thereon. FIGURE 2B, on the other hand, illustrates a security device incorporated into a card 220 such as a credit/ATM card. One skilled in the art, however, can readily recognize that the security device can be incorporated into other form factors and, moreover, that a single system can utilize more than one form factor. For example, the roaming security device 105 shown in FIGURE 1 could be in a card form factor, and the coprocessor security device 120 could be in a token form factor. Further, a simple mounting of the device as a circuit board can be done in lower risk situations.

Referring now to FIGURE 3A, there is illustrated a schematic of the components of a roaming security device 300 such as roaming security device 105 shown in FIGURE 1. In this embodiment, the roaming security device 300 includes a processor 302 connected both to a memory component 304 and to communication circuitry 306. The processor 302 is configured to perform a variety of transactions including hash and/or encryption computations. Additionally, the memory component is configured to store transaction data, device ID numbers, device secrets, and other information and to provide at least part of that data to the processor 302 for any computations. In one embodiment, the memory also is connected to tamper detector circuitry 308 that can destroy the contents of the memory component 304 if it is probed or otherwise accessed in an unauthorized way. Moreover, in the preferred embodiment, the memory component 304 is a nonvolatile, unalterable memory component, such as a lasered memory.

Referring now to FIGURE 3B, there is illustrated one embodiment of the memory component 304 shown in FIGURE 3A. The memory component 304 can consist of volatile and/or nonvolatile portions. The nonvolatile portions, which can be lasered for example, can store a device ID 310 including at least one of a unique serial number, a

5

10

15

20

25

30

device type identifier, a device model, etc. Other portions of the memory component can be divided to store data pages, device secrets, write counters, passwords, and/or a scratchpad.

The data page portion 312 of the memory, for example, can be configured as a single data page or as multiple data pages (shown in FIGURE 3C as data pages 0-6). These data pages can store a variety of information including monetary balances, copy counts, expiration data, trip data, security clearances, access information, inventory IDs, etc. Additionally, if the memory is divided into multiple data pages, each data page can be associated with a different service provider. That is, company A can use a first data page and company B can use a second data page.

Similarly, the device secret portion 314 of the memory component 304 can be divided to store one or more secrets for each service provider such that the various service providers are not forced to share their secrets with each other. For example, FIGURE 3D illustrates the device secret portion 314 of the memory component 304 wherein it is configured to store seven different secrets. Each secret can correspond to a particular data page (shown in FIGURE 3C) and to a particular service provider. Further, the device secrets stored in the various secret portions can be complete or partial. When partial secrets are used, each piece of the secret can be loaded by a different person at a different time so that the entire secret is never known by any one person and is never known outside the security device. After the first partial secret is loaded, each subsequent partial secret is combined, through, for example, a SHA-1 computation, with the previously computed secret to thereby form a new secret. For example, assume that two partial secrets are used in a roaming security device. The first secret would be loaded and stored at a location such as Secret 3 shown in FIGURE 3D. Next, the second partial secret could be loaded. The second partial secret and the first partial secret are used to seed a non-reversible algorithm. The result of this algorithm is stored in location Secret 3 as the master secret. This result can then be used in combination with a unique device identifier to seed a nonreversible algorithm -- the output of which is the device secret and is stored in the location Secret 3.

Referring again to the memory component 304 illustrated in FIGURE 3B, it can also include write counters 316. These write counters 316 are tamper proof counters that are incremented each time that a data page is altered or each time that a device secret is

5

10

15

20

25

30

changed. In one embodiment, individual counters are associated with each data page and each secret. Similarly, individual passwords 318 can be stored for each service provider (i.e., passwords can be associated with each data page). These passwords can be preloaded and stored in nonvolatile memory or alternately loaded by the user and stored in either nonvolatile or volatile memory.

Still referring to FIGURE 3B, the memory component 304 also can include a scratchpad memory 320. One scratchpad memory 320 that could be used is described in commonly owned U.S. Patent No. 5,306,961, *Low-power integrated circuit with selectable battery modes*, which is incorporated herein by reference. Briefly, however, the scratchpad memory 320 is used to guarantee that transactions between security devices are performed in an atomic fashion, thereby preventing incomplete transactions from being recorded.

Referring now to FIGURE 4, there is illustrated a schematic of the components of a coprocessor security device 400 such as coprocessor security device 120. This embodiment of the security device is very similar to the roaming security device shown in FIGURE 3. By designing the coprocessor security device and the roaming security device similarly, substantial cost savings can be realized. For example, the coprocessor security device 400 includes a processor 402, a memory 404, communication circuitry 406, and a tamper detector 408. One skilled in the art, however, can understand that the coprocessor security device 400 can take on various forms and could include more or less components than are illustrated and described herein while still performing substantially the same.

Referring now to FIGURE 5, there is illustrated a roaming security device and a coprocessor security device as they could be incorporated into a printer 505 and a printer cartridge 510. By incorporating the security devices into both the printer 505 and the printer cartridge 510, the printer 505 can verify that the printer cartridge 510 being used in the printer 505 is of the proper type, brand, age, etc. For example, the printer cartridge 510 can be secured to the cartridge bracket 515 so that the cartridge security device 525 contacts the printer security device 520. The printer security device 520 can periodically check to see if the cartridge security device 525 knows the proper secret. That is, the printer security device 520 can verify that the printer cartridge 510 is of the proper specifications. If the printer security device 520 determines that the printer

5

10

15

20

25

30

cartridge 510 is not of the proper specifications, then the printer 505 may be disabled until a proper printer cartridge having the proper authentication is installed.

In one embodiment, the printer security device 520 increments a counter in the cartridge security device 525 each time that the printer prints a page (or other measurement). Alternatively, the printer security device 520 writes a page count to the cartridge security device 525 every time that a page is printed. The cartridge security device 525 may also store a maximum page count (i.e., the maximum number of pages that the print cartridge 510 can print). Once the page count counter in the cartridge security device equals or exceeds the maximum page count, the printer 505 can be disabled until a new properly authenticated printer cartridge is installed.

Referring now to FIGURE 6A, there is illustrated a flowchart demonstrating a transaction between a roaming security device (e.g., the cartridge security device 525) and a coprocessor security device (e.g., the printer security device 520). In this embodiment, the coprocessor security device initially authenticates the roaming security device's identity (step 602). Next (although sequence is not necessarily important), the coprocessor security device--although not always necessary--can authenticate the integrity of the data stored in the roaming security device (step 604). In some embodiments, the roaming security device can also authenticate the coprocessor security device before allowing the coprocessor security device to write data to the roaming security device.

Next, the coprocessor security device computes new data based upon the transaction (step 608). For example, the coprocessor security device may deduct the fee for a snack from the monetary amount stored on the roaming security device. (This computation alternatively can be done in the roaming security device.) The coprocessor security device then generates a Message Authentication Code (MAC) (this particular MAC is referred to as MAC1) using the new data (step 610). MAC1 and the new data are transmitted to the roaming security device (step 612) where the new data is used to generate a second MAC (MAC2) (step 614). The roaming security device then compares MAC1 with MAC2 (step 616). If they match, then the data is stored in the roaming security device (step 618). Otherwise, the transactions can be voided and reexecuted. Assuming that the MACs match the coprocessor verifies that the data was properly written to and stored in the roaming security device (step 620).

5

10

15

20

25

30

Referring now to FIGURE 6B, it is a flowchart demonstrating in more detail the method of security device authentication shown in FIGURE 6A as step 602. Initially, the coprocessor security device generates and sends a challenge (e.g., a random number) to the roaming security device (step 622). The roaming security device generates a MAC (MAC A) using at least one of the challenge, the roaming security device ID, the device secret associated with the relevant service provider, a counter value, and other relevant data stored locally (step 624). MAC A is then transmitted to the coprocessor security device. At roughly the same time, the coprocessor security device reads the roaming security device ID and the other data from the roaming security device (step 626). This data, in combination with the device secret stored in the coprocessor security device, is used to generate a MAC (MAC B) (step 628). (Note that the device secret is not transferred directly between the security devices and thus never exposed). The coprocessor security device then compares MAC A with MAC B (step 630). If MAC A and MACB match, then the identity of the roaming device is authenticated. As can be appreciated, however, the method shown in FIGURE 6B, can easily be adapted so that the roaming security device can authenticate the coprocessor security device instead of the coprocessor security device authenticating the roaming security device.

Referring now to FIGURE 6C, it is a flowchart demonstrating in more detail step 620 shown in FIGURE 6A in which the completion of the transaction is verified. In this embodiment, after the coprocessor security device has written the new data to the roaming security device, the coprocessor security device reads back the new data to verify the integrity of the data (step 632). (The roaming security device can also send MAC2 along with the new data to the coprocessor security device. The coprocessor security device can use the MAC2 to detect tampering.) Although the coprocessor security device can read back the data without any security measures, in the preferred embodiment, the coprocessor security device reads back the data and generates a new MAC (MAC3) using the read-back data (step 634). If MAC3 matches the previously generated MAC1, then the data in the roaming security device was properly recorded (step 636). Otherwise, the data may be corrupt, thereby requiring the roaming security device to be deactivated or the transaction to be reexecuted.

In other embodiments, additional data is transferred between the roaming security device and the coprocessor security device. For example, at the completion of a

transaction, a write counter in the roaming security device (shown in FIGURE 3B) can be incremented and the coprocessor security device can verify that the write counter holds the proper transaction count. Additionally, an identifier associated with the coprocessor security device can be stored at the roaming security device. That is, the roaming security device can store not only the transaction results but also an identifier (e.g., device ID) for the coprocessor security device that conducted the transaction.

5

10

15

20

25

30

In yet another embodiment, the roaming security device can store access information, such as which buildings were accessed using the roaming security device. Alternatively, the coprocessor security device can store information such as who accessed a building. As can be understood by those of skill in the art, both the coprocessor security device and the roaming security device can be configured to store any type of information that would be useful.

Referring now to FIGURE 6D, it is a flowchart demonstrating a method of generating a hash result such as MAC A used in the transaction of FIGURE 6A. Initially, the coprocessor security device generates and sends a challenge (e.g., a random number) to the roaming security device (step 638). The roaming security device reads at least one of its unique device ID (step 640), the appropriate data page (step 642), secret (step 644), data MAC (step 646), data write counter (step 648), user verification data (step 650), and secret write counter (step 652). This data is then used to seed a nonreversible hashing algorithm such as the SHA-1 algorithm (step 654).

Referring now to FIGURE 7, it is a flowchart demonstrating a method of user verification. User verification further increases the security provided by the roaming/coprocessor security devices by requiring that the user as well as the security device be authenticated. In one embodiment, the roaming security device demands that the user authenticate himself by entering a password (step 702). The roaming security device can be prompted to make this demand by a coprocessor security device or any other device.

In response to the demand, the user should enter a password (step 704). Once entered, the password (possibly in an encrypted form or with a MAC) is sent to the roaming security device and verified (step 706). If the password is correct, a bit in the user verification data can be flipped (step 708). If the password is incorrect, another bit can be set to indicate an invalid user (step 710). The roaming security device can

incorporate these bits into any generated MAC so that the coprocessor security device can be properly informed of the user's status.

Now referring to FIGURE 8, it is a block diagram of a device for computing a SHA-1 computation. This embodiment includes five 32-bit registers 800, (labeled A-E); a barrel shifter 805; a 5-way 32-bit parallel adder 810; a counter 815; a 32-bit-wide logic function generator 820, (referred to as NLF); 16 32-bit memory elements 825, and a input number generator 830.

5

10

15

20

In operation, registers A-E are initialized and the memory 825 is loaded with the seed. The SHA-1 computation is computed with 80 cycles of shifts and additions. In a typical cycle, for example, the value of register A is shifted to register B, the value of register B is shifted to register C, the value of register C is shifted to register D, the value of register D is shifted to register E, and the output of adder 810 is loaded into register A.

To load a new value into register A every cycle, the adder 810 adds, in parallel, the value of register A, the value of register E, an input from the memory element 825, an input from the input number generator 830, and an input from the NLF 820. (The NLF receives the values of registers B, C, and D and performs a non-linear function thereon to generate the output.)

In conclusion, those skilled in the art can readily recognize that numerous variations and substitutions may be made in the invention, its use and its configuration to achieve substantially the same results as achieved by the embodiments described herein. Accordingly, there is no intention to limit the invention to the disclosed exemplary forms. Many variations, modifications and alternative constructions fall within the scope and spirit of the disclosed invention as expressed in the claims.

#### WHAT IS CLAIMED IS:

A security device comprising:

a memory device comprising:

a first memory portion configured to store a device ID; and

a second memory portion configured to store a device secret;

5

10

15

20

a processor connected to the memory device, the processor configured to read the stored device ID from the first memory portion and the stored device secret from the second memory portion and perform a nonreversible computation using the stored device ID, the stored device secret, and a challenge as seeds; and

a communication circuit connected to the processor, the communication circuit configured to receive the challenge from a host device and to communicate a result of the nonreversible computation performed by the processor.

- 2. The security device of claim 1, wherein the memory device further comprises: a third memory portion configured to store a service provider data item; wherein the stored service provider data item is also used to seed the nonreversible computation.

- 3. The security device of claim 2, wherein the memory device further comprises: a fourth memory portion configured to store a counter value that is incremented responsive to the service provider data item being changed;

wherein the stored counter value is also used to seed the nonreversible computation.

- 4. The security device of claim 1, wherein the first memory portion comprises a nonvolatile and unalterable memory device.

- 5. The security device of claim 4, wherein the second memory portion comprises an unalterable memory portion.

- 25 6. The security device of claim 1, wherein the communication circuit operates according to a one-wire protocol.

7. The security device of claim 1, wherein the security device is incorporated into a smart card.

- 8. The security device of claim 1, wherein the security device is attached to a printer cartridge.

- 5 9. The security device of claim 1, wherein the security device is incorporated into a host device.

- 10. The security device of claim 1, wherein the nonreversible computation is a SHA-1 computation.

- 11. The security device of claim 10, wherein the processor is configured to perform the SHA-1 computation serially.

- 12. The security device of claim 10, wherein the processor is configured to perform the SHA-1 computation in parallel.

- 13. A method of device authentication comprising the steps of: receiving a challenge from a device; generating a nonreversible computation result; and

outputting a response to the challenge, wherein the outputted response includes the nonreversible computation result;

wherein the nonreversible computation result is computed by seeding an algorithm with the received challenge, a device secret, and a unique device identifier.

20 14. The method of claim 13, further comprising the steps of: generating a challenge; transmitting the challenge to the device;

receiving a response from the device, the response including the result of the nonreversible computation, which is seeded with at least the challenge; and

25 authenticating the response from the device.

15

15. The method of claim 13, wherein the step of receiving comprises the step of: receiving a challenge from a remote security device.

16. The method of claim 13, further comprising the steps of: receiving the outputted response at the device; and authenticating the received response.

5

15

- 17. The method of claim 15, further comprising the step of:

enabling an electronic device responsive to a positive authentication of the received response.

- 10 18. The method of claim 15, further comprising the step of:

disabling an electronic device responsive to a failure to authenticate the received response.

- 19. A system for device authentication, the system comprising:

a coprocessor security device configured to store a service provider data item and

a device secret; and

- a host device connected to the coprocessor security device, the host device configured to communicate with the coprocessor security device and a roaming security device;

wherein the roaming security device can be authenticated to thereby enable the host device.

- The system of claim 19, further comprising:a printer, wherein the coprocessor security device is attached to the printer.

- 21. The system of claim 19, further comprising a means for attaching the roaming security device to a printer cartridge.

- 25 22. The system of claim 19, further comprising: a means for attaching the roaming security device to a printer.

23. The system of claim 20, wherein the printer cartridge is disabled responsive to the roaming security device being removed from the printer cartridge.

24. A method of device authentication, the method comprising the steps of: receiving, at a roaming device, a challenge from a host device;

5

25

generating, at the roaming device, a nonreversible computation result, wherein the nonreversible computation result is computed by seeding a nonreversible algorithm with at least the challenge and a device secret; and

outputting to the host device a response to the challenge, wherein the outputted response includes the nonreversible computation result.

- 25. The method of claim 23, further comprising the steps of:

generating a challenge at the roaming device;

transmitting the challenge from the roaming device to the host device;

receiving a response from the host device, the response including the result of the

nonreversible algorithm seeded with at least the challenge; and

authenticating, at the roaming device, the response from the host device.

- 26. The method of claim 23, further comprising the steps of: receiving the outputted response at the host device; and authenticating the received response at the host device.

- 27. The method of claim 24, further comprising the step of:

enabling an electronic device responsive to a positive authentication of the received response.

- 28. The method of claim 24, further comprising the step of:

disabling an electronic device responsive to a failure to authenticate the received response.

- 29. The method of claim 24, wherein the nonreversible computation result is computed by further seeding the nonreversible algorithm with a unique device identifier.

30. A security device comprising:

5

15

a memory device comprising a first memory portion configured to store a device secret;

a processor connected to the memory device, the processor configured to read the stored device secret from the first memory portion and to perform a hash computation using at least the stored device secret and a challenge as seeds; and

a communication circuit connected to the processor, the communication circuit configured to receive the challenge from a host device and to communicate a result of the hash computation performed by the processor.

- The security device of claim 30, wherein the memory device is configured to store a partial secret.

- 32. The security device of claim 31, wherein the processor is configured to compute the device secret using the partial secret.

- 33. The security device of claim 30, wherein the memory device further comprises:

- a second memory portion configured to store a printed page count; and

- a third memory portion configured to store a maximum page count;

wherein the processor is configured to generate a signal responsive to the stored printed page count being equal to or exceeding the stored maximum page count.

SUBSTITUTE SHEET (RULE 26)

# **SUBSTITUTE SHEET (RULE 26)**

FIG. 3a

4/13

Device ID 304 <u>310</u> Data Pages <u>312</u> Device Secrets <u>314</u> Write Counters <u>316</u> Passwords <u>318</u> Scratch Pad <u>320</u>

FIG. 36

SUBSTITUTE SHEET (RULE 26)

5/13

| Data Page 0 |

|-------------|

| Data Page 1 |

| Data Page 2 |

| Data Page 3 |

| Data Page 4 |

| Data Page 5 |

| Data Page 6 |

FIG. 3c

6/13

| Secret 0 |

|----------|

| Secret 1 |

| Secret 2 |

| Secret 3 |

| Secret 4 |

| Secret 5 |

| Secret 6 |

FIG. 3d

FIG. 4

SUBSTITUTE SHEET (RULE 26)

FIG. 6a SUBSTITUTE SHEET (RULE 26)

FIG. 6b

FIG. 6c

FIG. 7

# SUBSTITUTE SHEET (RULE 26)

FIG. 6d

# **SUBSTITUTE SHEET (RULE 26)**

**SUBSTITUTE SHEET (RULE 26)**

#### INTERNATIONAL SEARCH REPORT

ional Application No PCT/US 00/31421

A. CLASSIFICATION OF SUBJECT MATTER IPC 7 G07F7/10

According to International Patent Classification (IPC) or to both national classification and IPC

#### B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols) IPC 7 607F B41J

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

| C. DOCUME  | ENTS CONSIDERED TO BE RELEVANT                                                     |                             |

|------------|------------------------------------------------------------------------------------|-----------------------------|

| Category ° | Citation of document, with indication, where appropriate, of the relevant passages | Relevant to claim No.       |

| Х          | EP 0 028 965 A (CII-HB)<br>20 May 1981 (1981-05-20)                                | 1,7,<br>13-18,              |

| A          | abstract; claims; figure 1                                                         | 24,26-29<br>4,5,9,<br>19,30 |

|            | page 3, line 20 -page 5, line 11                                                   |                             |

| Υ          | WO 97 22091 A (KONINKLIJKE PTT NEDERLAND) 19 June 1997 (1997-06-19)                | 1-7,9,<br>10,<br>13-19,     |

|            | the whole document                                                                 | 24,26-30                    |

| Υ          | EP 0 621 570 A (FRANCE TELECOM)<br>26 October 1994 (1994-10-26)                    | 1-7,9,<br>10,<br>13-19,     |

|            | the whole document                                                                 | 24,26-30                    |

|            | -/                                                                                 |                             |

| X Further documents are listed in the continuation of box C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | χ Patent family members are listed in annex.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Special categories of cited documents:      A* document defining the general state of the art which is not considered to be of particular relevance      E* earlier document but published on or after the international filing date      L* document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)      O* document referring to an oral disclosure, use, exhibition or other means      document published prior to the international filing date but later than the priority date claimed | <ul> <li>"T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention</li> <li>"X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone</li> <li>"Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.</li> <li>"&amp;" document member of the same patent family</li> </ul> |  |  |

| Date of the actual completion of the international search  29 May 2001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Date of mailing of the international search report  07/06/2001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| Name and mailing address of the ISA  European Patent Office, P.B. 5818 Patentlaan 2  NL – 2280 HV Rijswijk  Tel. (+31–70) 340–2040, Tx. 31 651 epo nl,  Fax: (+31–70) 340–3016                                                                                                                                                                                                                                                                                                                                                                                                                            | Authorized officer  David, J                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

#### INTERNATIONAL SEARCH REPORT

Ir tional Application No PCT/US 00/31421

|            | ation) DOCUMENTS CONSIDERED TO BE RELEVANT                                                                               |                                |

|------------|--------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| Category ° | Citation of document, with indication, where appropriate, of the relevant passages                                       | Relevant to claim No.          |

| A          | EP 0 427 465 A (AMERICAN TELEPHONE AND TELEGRAPH) 15 May 1991 (1991-05-15)  abstract; claims; figures 1,5,6              | 1,5-7,9,<br>13-19,<br>24,26-30 |

| A          | US 4 549 075 A (C. SAADA)<br>22 October 1985 (1985-10-22)                                                                | 1,4-7,9,<br>13-19,             |

|            | abstract; claims; figure                                                                                                 | 24-30                          |

| A          | WO 90 00974 A (SIEMENS)<br>8 February 1990 (1990-02-08)<br>abstract; claims; figures<br>page 6, line 16 -page 7, line 10 | 1,8,<br>19-23                  |

| A          | DE 195 23 466 C (INFORMATIKZENTRUM DER<br>SPARKASSENORGANIZATION)<br>3 April 1997 (1997-04-03)                           |                                |

| Α          | DE 41 38 861 A (SIEMENS NIXDORF<br>INFORMATIONSSYSTEME)<br>1 October 1992 (1992-10-01)                                   |                                |

| A          | <br>WO 97 22093 A (LANDIS & GYR TECHNOLOGY<br>INNOVATION) 19 June 1997 (1997-06-19)                                      |                                |

|            |                                                                                                                          |                                |

|            |                                                                                                                          |                                |

|            |                                                                                                                          |                                |

|            |                                                                                                                          |                                |

|            |                                                                                                                          |                                |

|            |                                                                                                                          |                                |

|            |                                                                                                                          |                                |

|            |                                                                                                                          |                                |

|            |                                                                                                                          |                                |

|            |                                                                                                                          |                                |

|            |                                                                                                                          |                                |

|            |                                                                                                                          |                                |

|            |                                                                                                                          |                                |

#### INTERNATIONAL SEARCH REPORT

formation on patent family members

In ional Application No

PCT/US 00/31421

|                                        |          |                  |                                                                                              | PC1/US                                                                                                                                                                                                                | 00/31421                                                                                                                                                                                                                     |

|----------------------------------------|----------|------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Patent document cited in search report |          | Publication date |                                                                                              | atent family<br>nember(s)                                                                                                                                                                                             | Publication<br>date                                                                                                                                                                                                          |

| EP 0028965                             | A        | 20-05-1981       | FR<br>DE<br>US                                                                               | 2469760 A<br>3068240 D<br>4471216 A                                                                                                                                                                                   | 22-05-1981<br>19-07-1984<br>11-09-1984                                                                                                                                                                                       |

| WO 9722091                             | A        | 19-06-1997       | NL<br>AU<br>AU<br>BG<br>BR<br>CA<br>CN<br>CZ<br>DE<br>DE<br>EP<br>ES<br>NO<br>NZ<br>PL<br>US | 1001863 C<br>190420 T<br>703985 B<br>7625496 A<br>102607 A<br>9611975 A<br>2239875 A<br>1203681 A<br>9801758 A<br>69607041 D<br>69607041 T<br>0883866 A<br>2143790 T<br>982527 A<br>322489 A<br>327192 A<br>5991412 A | 10-06-1997<br>15-03-2000<br>01-04-1999<br>03-07-1997<br>29-01-1999<br>17-02-1999<br>19-06-1997<br>30-12-1998<br>13-01-1999<br>13-04-2000<br>13-07-2000<br>16-12-1998<br>16-05-2000<br>03-06-1998<br>28-10-1998<br>23-11-1999 |

| EP 0621570                             | A        | 26-10-1994       | FR<br>DE<br>DE<br>JP<br>US                                                                   | 2704081 A<br>69407647 D<br>69407647 T<br>7110876 A<br>5495098 A                                                                                                                                                       | 21-10-1994<br>12-02-1998<br>09-07-1998<br>25-04-1995<br>27-02-1996                                                                                                                                                           |

| EP 0427465                             | A        | 15-05-1991       | US<br>CA<br>DE<br>DE<br>JP<br>JP<br>JP                                                       | 5120939 A<br>2023872 A,C<br>69016589 D<br>69016589 T<br>1921556 C<br>3158955 A<br>6052518 B                                                                                                                           | 09-06-1992<br>10-05-1991<br>16-03-1995<br>07-09-1995<br>07-04-1995<br>08-07-1991<br>06-07-1994                                                                                                                               |

| US 4549075                             | A        | 22-10-1985       | FR<br>DE<br>EP<br>JP<br>JP<br>JP                                                             | 2530053 A<br>3374039 D<br>0100260 A<br>1733117 C<br>4018497 B<br>59062241 A                                                                                                                                           | 13-01-1984<br>12-11-1987<br>08-02-1984<br>17-02-1993<br>27-03-1992<br>09-04-1984                                                                                                                                             |

| WO 9000974                             | <b>A</b> | 08-02-1990       | DE<br>EP<br>JP<br>JP<br>US                                                                   | 3880694 D<br>0433280 A<br>2752402 B<br>4500482 T<br>5365312 A                                                                                                                                                         | 03-06-1993<br>26-06-1991<br>18-05-1998<br>30-01-1992<br>15-11-1994                                                                                                                                                           |

| DE 19523466                            | С        | 03-04-1997       | NONE                                                                                         |                                                                                                                                                                                                                       |                                                                                                                                                                                                                              |

| DE 4138861                             | Α        | 01-10-1992       | NONE                                                                                         |                                                                                                                                                                                                                       |                                                                                                                                                                                                                              |

| WO 9722093                             | A        | 19-06-1997       | CH<br>AU<br>AU<br>EP                                                                         | 690530 A<br>704773 B<br>1140497 A<br>0870286 A                                                                                                                                                                        | 29-09-2000<br>06-05-1999<br>03-07-1997<br>14-10-1998                                                                                                                                                                         |