(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3825257号

(P3825257)

(45) 発行日 平成18年9月27日(2006.9.27)

(24) 登録日 平成18年7月7日(2006.7.7)

(51) Int.C1.

F 1

|            |           |            |      |

|------------|-----------|------------|------|

| HO1L 27/00 | (2006.01) | HO1L 27/00 | 301C |

| G11C 13/00 | (2006.01) | G11C 13/00 | Z    |

| HO1L 27/10 | (2006.01) | HO1L 27/10 | 301  |

請求項の数 20 (全 16 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2000-590213 (P2000-590213)  |

| (86) (22) 出願日 | 平成11年12月3日 (1999.12.3)        |

| (65) 公表番号     | 特表2002-533928 (P2002-533928A) |

| (43) 公表日      | 平成14年10月8日 (2002.10.8)        |

| (86) 國際出願番号   | PCT/N01999/000365             |

| (87) 國際公開番号   | W02000/038234                 |

| (87) 國際公開日    | 平成12年6月29日 (2000.6.29)        |

| 審査請求日         | 平成13年6月4日 (2001.6.4)          |

| (31) 優先権主張番号  | 19985707                      |

| (32) 優先日      | 平成10年12月4日 (1998.12.4)        |

| (33) 優先権主張国   | ノルウェー (NO)                    |

|           |                                                                                 |

|-----------|---------------------------------------------------------------------------------|

| (73) 特許権者 | 500034413<br>シン・ファイルム エレクトロニクス エイ<br>エスエイ<br>ノルウェー国、オスロ、バイカ、ビー、<br>オー、ボックス 1872 |

| (74) 代理人  | 100066692<br>弁理士 浅村 皓                                                           |

| (74) 代理人  | 100072040<br>弁理士 浅村 肇                                                           |

| (74) 代理人  | 100087217<br>弁理士 吉田 裕                                                           |

| (74) 代理人  | 100080263<br>弁理士 岩本 行夫                                                          |

最終頁に続く

(54) 【発明の名称】容量増大化可能なデータ処理装置

## (57) 【特許請求の範囲】

## 【請求項 1】

1つ以上の薄膜デバイス(1)を含む容量増大化可能なデータ処理装置、具体的にはデータ記憶装置であって、

各薄膜デバイス(1)が、同一の拡がりをもって重ね合わされた薄膜材料から成る複数の副層(S)によって作られた平坦層であり、

前記各薄膜デバイス(1)の複数の副層(S)が、電気絶縁性および/または導電性および/または半導電性の構造体と、副層(S)における薄膜材料で実現された情報記憶能力を有する構造体とを含み、

前記構造体が、前記薄膜デバイスにおける能動および受動電子回路素子または論理セルを実現するために、前記薄膜デバイス(1)を形成する、スタッカにおける隣接する複数の副層における同種の他の構造体と電気的に整合または接触しており、

前記薄膜デバイス(1)の前記能動および受動回路素子が、3次元構造によって実現され、該薄膜デバイス(1)の隣り合う2つ以上の副層(S)を貫通して延在し、前記能動および受動回路素子が、1つ以上の副層(S)における水平方向の導電性構造体と、1つ以上の前記副層(S)を貫通して延在する垂直方向の導電性構造体とによって電気的に接続され、さらに

2つ以上の薄膜デバイス(1)が重合して配設されている前記データ処理装置において、各薄膜デバイス(1)が、1つ以上のマトリックス・アドレス指定可能メモリ(3')

10

20

を形成する1つ以上のメモリ領域(3)を含み、それぞれが、ストライプ状の並列導電性構造形態(7)または電極構造形態の第1組の電極と、該第1組の電極における電極構造体(7)と概ね直交するように配向された対応する電極構造形態の第2組の電極(8)とに接触した、副層(5)にあるメモリ媒体(6)を含み、

前記各組の電極が、前記メモリ媒体を有する前記副層の両側にそれぞれ隣接する別の副層(5)に設けられ、もって前記第1および第2組の電極における前記電極構造体(7、8)の間の交差点で、前記メモリ媒体(6)にアドレス指定可能なメモリ・セルが作られており、

各薄膜デバイス(1)が、1つ以上のメモリ(3')内で前記メモリ・セルを制御し、駆動し、かつアドレス指定するための電子薄膜回路を形成する回路領域(2)をさらに含み、

前記電子薄膜回路が、電流経路を介して、メモリ(3')の前記第1および第2組の電極の各々における電極構造体(7、8)と接続されており、前記電流経路は、前記第1および第2組の電極が設けられた同じ副層内で導電性構造体として形成されており、

各薄膜デバイス(1)が、前記データ処理装置の全ての別の薄膜デバイスに対してインターフェースを有し、前記インターフェースが、通信・信号回線、および、該通信・信号回線を処理するためのサポート回路によって実現されており、

前記通信・信号回線と前記サポート回路が、それぞれ前記薄膜デバイス(1)における専用インターフェース領域(4)に設けられていることを特徴とする容量増大可能なデータ処理装置。

#### 【請求項2】

1つ以上のメモリにおけるメモリ媒体(6)が、モノマー、オリゴマー、またはポリマー形態の分子材料のうちから選択された材料、無機または有機形態の炭素含有材料、あるいはこうした材料の並列体または混合体を含むことを特徴とする請求項1に記載された容量増大可能なデータ処理装置。

#### 【請求項3】

メモリ媒体(6)が、メモリ・セル内で非線形電流/電圧特性を与えるメモリ材料を含み、前記非線形電流/電圧特性が、無機または有機ダイオードあるいは閾値切換え可能材料によって生じることを特徴とする請求項2に記載された容量増大可能なデータ処理装置。

#### 【請求項4】

メモリ媒体(6)が切換え可能材料を含み、前記切換え可能材料がそれぞれ強誘電性材料または電荷移動有機錯体として選択された不揮発性材料であることを特徴とする請求項1に記載された容量増大可能なデータ処理装置。

#### 【請求項5】

メモリ媒体(6)が切換え可能であって非線形電流/電圧特性を有することを特徴とする請求項1に記載された容量増大可能なデータ処理装置。

#### 【請求項6】

電子回路が無機および/または有機の半導電性材料を含むことを特徴とする請求項1に記載された容量増大可能なデータ処理装置。

#### 【請求項7】

1つ又は2つ以上の薄膜デバイス(1)におけるインターフェース領域(4)が、前記薄膜デバイスの縁部分で一体化され、薄膜デバイス(1)が2つ以上の場合における前記縁部分が相互に整合していることを特徴とする請求項1に記載された容量増大可能なデータ処理装置。

#### 【請求項8】

縁部分のインターフェース領域(4)がさらに、各薄膜デバイス(1)用または任意選択でデータ処理装置全体用のI/Oインターフェース(12)を含み、外部デバイスおよび/または周辺デバイスとデータおよび信号通信を行うための機能を実行することを特徴とする請求項7に記載された容量増大可能なデータ処理装置。

10

20

30

40

50

## 【請求項 9】

薄膜デバイス(1)または該薄膜デバイスのスタックが基板(13)上に設けられ、該基板が、装置内で追加の制御、駆動、および通信機能を実行するための能動電子回路(14)を含み、各薄膜デバイス(1)が、それぞれの場合に、当該の薄膜デバイスと基板(13)との間に配置された薄膜デバイスを通って垂直方向に延在する別々のインターフェース領域(4)を介して、回路(14)に接続されることを特徴とする請求項1に記載された容量増大可能なデータ処理装置。

## 【請求項 10】

基板(13)がインターフェース部分(15)を含み、該インターフェース部分(15)が、基板内で水平方向に、かつその上に設けた薄膜デバイスに並列または隣接して延在し、基板(13)上に設けた1以上の薄膜デバイス(1)におけるインターフェース部分(4)と電気的に接続されていることを特徴とする請求項9に記載された容量増大可能なデータ処理装置。

10

## 【請求項 11】

インターフェース部分(13)が、データ処理装置全体用のI/Oインターフェース(12)をさらに含み、前記I/Oインターフェース(12)が、外部デバイスおよび/または周辺デバイスとデータおよび信号通信を行うための機能を実行することを特徴とする請求項10に記載された容量増大可能なデータ処理装置。

## 【請求項 12】

基板(13)が、半導電性材料、具体的には無機単結晶半導電性材料、とりわけシリコンから成る単結晶半導電性材料のような材料で形成されていることを特徴とする請求項11に記載された容量増大可能なデータ処理装置。

20

## 【請求項 13】

基板(13)における電子回路(14)がCMOS技術で実現されたものであることを特徴とする請求項12に記載された容量増大可能なデータ処理装置。

## 【請求項 14】

基板(13)における電子回路とそのインターフェース部分(15)との電気接続、またはこのインターフェース部分(15)を介して上にある薄膜デバイス(1)のインターフェース領域(4)への電気接続が、CMOS互換の金属相互接続として実現されたものであることを特徴とする請求項10または請求項13に記載された容量増大可能なデータ処理装置。

30

## 【請求項 15】

装置が2つ以上の薄膜デバイス(1)を含み、薄膜デバイス(1)が同一の拡がりをもち、スタックにおいて相互に整合して設けられていることを特徴とする請求項1に記載された容量増大可能なデータ処理装置。

## 【請求項 16】

1つ以上の分離層(16)が、隣接する薄膜デバイス(1)間に薄片状に設けられ、単独で、または選択された組み合わせで、それぞれが、電気、温度、光、または機械的な絶縁機能または平面化機能を実行し、それぞれの場合に、各膜デバイス(1)の前記インターフェース領域が、それぞれの分離層(16)にある経路を介して電気的に接続されていることを特徴とする請求項15に記載された容量増大可能なデータ処理装置。

40

## 【請求項 17】

装置が2つ以上の薄膜デバイス(1)を備え、薄膜デバイス(1)がそのスタックにおいて相互にずらして配置されていることを特徴とする請求項1に記載された容量増大可能なデータ処理装置。

## 【請求項 18】

薄膜デバイス(1)間および/または薄膜デバイス(1)と任意選択の基板(13)との間の電気的接続(4')が、ずらして配置されたスタックの段上に水平方向および垂直方向に延在して設けられていることを特徴とする請求項17に記載された容量増大可能なデータ処理装置。

50

## 【請求項 19】

1つ以上の分離層(16)が、隣接する薄膜デバイス(1)間に薄片状に設けられ、単独で、または選択された組み合わせで、それぞれが、電気、温度、光、または機械的な絶縁機能または平面化機能を実行することと、

分離層(16)だけが、隣接する2つの薄膜デバイスの重なり合った部分に設けられ、薄膜デバイス(1)間の分離層(16)が、個々の薄膜デバイス(1)間の電気接続(4')のための経路の無い非破壊層を形成するように、各薄膜デバイス(1)のインターフェース部分(4)が、ずらして配置された領域内の薄膜デバイス(1)の露出表面部分上に設けられていることを特徴とする請求項17に記載された容量増大化可能なデータ処理装置。

10

## 【請求項 20】

前記データ処理装置が、箔状の材料またはシリコンなどの硬質材料で形成されたキャリア基板上に設けられ、それぞれの場合の前記キャリア基板が、スタックのうちの最下部の薄膜デバイスまたは任意選択で設けた電子回路(14)を備える基板(13)に隣接して設けられていることを特徴とする請求項1に記載された容量増大化可能なデータ処理装置。

## 【発明の詳細な説明】

## 【0001】

本発明は、1つ以上の薄膜デバイスを含む容量増大化可能なデータ処理装置、具体的にはデータ記憶装置に係り、各薄膜デバイスが、同一の拡がりをもって重ね合わされた薄膜材料から成る複数の副層によって作られた平坦層であり、各薄膜デバイスの複数の副層が、電気的絶縁性および/または導電性および/または半導電性の構造体、および副層の薄膜材料において情報記憶機能を実現した構造体を含み、この構造体が、薄膜デバイスにおける能動および受動電子回路素子または論理セルを実現するために、スタックを形成する薄膜デバイスの隣接する副層における同種の他の構造体と電気的に整合または接触しており、この薄膜デバイスの能動および受動回路素子が、3次元構造によって実現され、該薄膜デバイスの隣り合う2つ以上の副層を貫通して延在し、この能動および受動回路素子が、1つ以上の副層における水平方向の導電性構造体、および1つ以上の副層を貫通して延在する垂直方向の導電性構造体によって電気的に接続され、2つ以上の薄膜デバイスが重合して配設される。

20

## 【0002】

当該技術分野では、スタック構造(積み重ね構造)の薄膜回路形態でメモリ・デバイスを作成することが知られており、さらにメモリ・デバイスは、メモリを制御、駆動、およびアドレス指定するためにプロセッサと組み合わせてもよいが、その後、単結晶硬質基板の形態で、および/または二酸化珪素の膜として形成される場合は確実に非常に薄くできるキャリア基板上に設けられる薄膜の形態で、無機半導電性材料で実現される後者と組み合わせてもよい。処理回路を備えた完全なメモリ・デバイスは、並列に並べられた層により、さらにしばしば特別な方法による薄膜回路の転送を使用して作成される。層間の相互接続を行なうために、複数層に亘る貫通穴を用いて蒸着金属で結合して必要な電流路を作る。さらに、本出願人によるPCT/N099/00180(その記載内容を本明細書に援用する)に記載された大容量メモリおよびプロセッサとメモリ・モジュールとの組み合わせを有する完全なコンピュータを形成する、周知の容量増大化可能な集積データ処理デバイスがあり、別体プロセッサ層または別体メモリ層あるいは結合されたプロセッサおよびメモリ層のいずれかで、コンピュータのCPU機能を実現するか、またはコンピュータ内で制御および通信機能を実現する、いわゆるインテリジェント・ランダム・アクセス・メモリ(IRMAM)およびプロセッサが設けられる。短い電流経路を提供するために、3次元の電気構造体を使用して、別体層にある構成要素間、および層相互間の、相互接続がなされる。データ処理デバイス全体が基板上に設けられ、これがさらに従来の技法では無機半導電性材料で実現されている制御および通信目的の高速処理回路を含み、そうでない場合はプロセッサかまたはメモリに関するデータ処理デバイスの異なる層が全体的に薄膜

30

40

50

技術で実現される。

【0003】

関連する従来技術の例についていくつか述べる。米国特許第5714768号(Ovshinsky等)では、プロセッサおよび、デバイスの最上部でプロセッサの上に取り付けられた薄膜技術の特定のメモリ・アレイを備えたコンピュータ・デバイスについて開示し、別々のメモリ・セルへの選択された電気的入力信号に応答して、異なる電気的抵抗値を達成することができる、様々な無機材料に基づいたメモリ媒体の使用法について開示している。具体的に言えば、Ovshinsky等は、電気的な位相の変化に基づき、スイッチとして無機カルコゲニド化合物で形成された、いわゆるovionicメモリ形態の特別なメモリ要素について開示している。各メモリ要素は單一ユニットと考えられ、カプセル化され、さらにたとえばSiO<sub>2</sub>またはSi<sub>3</sub>N<sub>4</sub>などの絶縁材料で相互に分離される。メモリ要素は平面アレイ構造に配置され、この構造は両側が電極構造体の上になるグリッドに接触し、各グリッド内の電極構造体が他のグリッド内の電極構造体に対して垂直方向となる。この種の2次元メモリ・アレイは、適切な相互絶縁により、電子回路を含む論理処理デバイスであってよい基板上に提供される、垂直に集積されたメモリ構造体を形成するようにスタッツクすることができる。Ovshinsky等の特許では、薄膜材料からなる同延の薄膜副層で形成された薄膜デバイスをスタッツクするため、あるいは、薄膜デバイスが、目的に従った機能特性を有する薄膜材料の副層を提供することによって実現される、能動回路を備えた回路領域とメモリ・モジュールを備えたメモリ領域の両方を備えるためのヒントまたは提案が与えられていない。受動電極マトリックス内の2次元メモリ・セル・アレイが容量測定メモリ・デバイスを形成するためにスタッツクされた、強誘電性のメモリ・デバイスについては、たとえば米国特許第5329485号(Isono等)および米国特許第5375085号(Gnade等)から、当該技術分野ではさらによく知られている。消去可能メモリ用の強誘電性ポリマー材料の使用法、具体的に言えば、ポリ塩化ビニリデンまたはポリビニリデン-トリフルオロエチレンの共重合体の使用法に基づいた実施形態も、たとえば、IBM Technical Disclosure Bulletin 37:421~424、No. 11(1994年)で提案されている。これらのポリマーは、非常に薄い膜として得ることが可能であり、メモリ媒体は、両側に堆積され、相互に直交するように配向された並列導電性電極のセットを備えた、薄膜材料の連続する層として提供される。こうした2次元の受動強誘電性アレイを、3次元構造体を形成するようにスタッツクすることができる。ただし、前述の公開で、薄膜デバイスに集積された能動回路と受動メモリ・モジュールの両方を実現することができる機能特性を備えた副層を含む薄膜デバイスについて開示しているものはない。

【0004】

最後に、転写された薄膜回路に基づく3次元のメモリ・プロセッサ構造体について、国際公開出願WO95/09438(Zavracky等)および同一発明者による米国特許第5656548号で開示されており、いざれの刊行物も、1993年9月30日付米国特許出願第130033号を基礎とするが、現在は権利放棄されている。具体的に言えば、これらの刊行物では、3次元構造体を形成するように積み重ねられたメモリおよびプロセッサ回路の層について開示しており、従来の平面回路技術を使用して薄膜材料をパターン化すること、および、たとえば構造体を通じて延在する金属導通部により垂直に相互接続することによって、回路の別々の機能素子が製造される。

【0005】

薄膜技術の使用に基づいてデータを処理および記憶するための従来技術のデバイスには、速度および機能性についていくつかの利点があるが、純粋に記憶目的の場合はかなり高価であることが多く、具体的には生産するのが複雑な場合がある。効率的なメモリ管理をするには、かなりの処理容量が必要であり、制御、通信、およびアドレス指定の場合には、こうした目的専用の回路が大規模なメモリまたは大規模な記憶容量を有するいくつかの別々のメモリに割り当てられることが多い。

【0006】

10

20

30

40

50

本発明の主な目的は、容量増大化可能なデータ処理装置を提供することであって、具体的に言えば、相対的に作成が単純かつ安価であり、原理上はメモリの管理および動作を複雑にすることなくデータの記憶容量をほぼ無制限に増大化することが可能な、データ記憶装置を提供することである。

【0007】

本発明の他の目的は、容量増大化可能なデータ処理装置を実現することであって、具体的に言えば、薄膜技術で実現されるメモリの制御およびアドレス指定のためのサポート機能を実行できるデータ記憶装置を、実質上薄膜技術で実現し、前述の目的の電子回路を薄膜デバイス内でメモリと一体化させることである。

【0008】

最終的に本発明の一目的は、大規模な記憶密度、高速のデータ・アクセス、および高速のデータ転送速度を備え、選択的に、データ・メモリに対するデータの並列入力と高速の並列データ読出しと組み合わされる、容量データ記憶デバイスを実現することでもある。

【0009】

前記目的およびその他の特徴と利点は、容量増大化可能なデータ処理装置、具体的にはデータ記憶装置を使用する本発明に従って達成され、各薄膜デバイスが、1つ以上のマトリックス・アドレス指定可能メモリを形成する1以上のメモリ領域を含み、それぞれが、ストライプ状の並列導電性構造形態または電極構造形態の第1組の電極と、第1組の電極における電極構造体と概ね直交するように配向された対応する電極構造形態の第2組の電極に接触した、副層にあるメモリ媒体を含み、各組の電極が、前記メモリ媒体を有する前記副層の両側にそれぞれ隣接する別の副層に設けられ、もって第1および第2組の電極における電極構造体の間の交差点で、メモリ媒体にアドレス指定可能なメモリ・セルが作られており、各薄膜デバイスが、1つ以上のメモリ内でメモリ・セルを制御し、駆動し、かつアドレス指定するための電子薄膜回路を形成する回路領域をさらに含み、前記電子回路が、電流経路を介してメモリの第1組および第2組の電極における電極構造体と、接続されており、前記電流経路は、前記第1および第2組の電極が設けられた同じ副層内で導電性構造体として形成されており、各薄膜デバイスが、前記データ処理装置の全ての別の薄膜デバイスに対してインターフェースを有し、前記インターフェースが、通信・信号回線、および、該通信・信号回線を処理するためのサポート回路によって実現され、前記通信・信号回線と前記サポート回路が、それぞれ薄膜デバイスにおける専用のインターフェース領域に設けられていることを特徴とする。

【0010】

本発明による装置の有利な実施形態では、1つ以上のメモリにおけるメモリ媒体が、モノマー、オリゴマー、またはポリマー形態の分子材料のうちで選択された材料、無機または有機形態の炭素含有材料、あるいはこうした材料の並列または混合を含む。この点について、メモリ媒体が、メモリ・セル内で非線形電流／電圧特性を与えるメモリ材料を含み、前記非線形電流／電圧特性が、無機または有機ダイオードあるいはしきい値切換え可能材料によって生成されることが好ましい。

【0011】

本発明による装置の他の有利な実施形態では、メモリ媒体が切換え可能材料(a switchable material)を含み、前記切換え可能材料がそれぞれ強誘電性材料または電荷移動有機錯体として選択された不揮発性材料であるか、あるいはメモリ媒体が切換え可能であつて非線形電流／電圧特性を有することができる。

【0012】

本発明により、電子回路が無機および／または有機の半導電性材料を含むので有利である。

【0013】

本発明による装置の有利な実施形態では、1つまたは2つ以上の薄膜デバイスにあるインターフェース領域は、薄膜デバイスの縁部分(側辺寄りの部分)に一体化され、後者の場合には前記縁部分が相互に整合する。この点について、縁部分のインターフェース領域

10

20

30

40

50

が、さらに、それぞれの薄膜デバイス用または任意選択で装置全体用の I / O インターフェースを含み、外部デバイスおよび / または周辺デバイスとデータおよび信号通信を行うための機能を実行することが好ましい。

【 0 0 1 4 】

本発明による装置では、薄膜デバイス、または、スタック構造の斯かるデバイスが、基板上に設けられ、これが、装置内で追加の制御、駆動、および通信機能を実行するための能動電子回路を含み、各薄膜デバイスが、それぞれの場合に当該薄膜デバイスと基板との間に配置された薄膜デバイスを通って垂直方向に延在する別々のインターフェース領域を介して回路に接続されることが可能なので有利である。この点について、基板内でほぼ水平に、およびその上に提供された薄膜デバイスに並列または隣接して延在し、基板上に提供された 1 以上の薄膜デバイスにあるインターフェース部分と電気的に接続されたインターフェース部分を基板が含むことが好ましく、さらに具体的に言えば、インターフェース部分が、装置全体用の I / O インターフェースをさらに含むインターフェース部分であり、前記 I / O インターフェースが、外部デバイスおよび / または周辺デバイスとデータおよび信号通信を行うための機能を実行することが好ましい。

【 0 0 1 5 】

次いで基板が、半導電性材料、具体的には無機単結晶半導電性材料、特にシリコンから成る単結晶半導電性材料のような材料で形成されるので有利であり、具体的に言えば、この点について、基板内における電子回路が CMOS 技術で実現されることが好ましい。さらにこの点について、基板内における電子回路とそのインターフェース部分との電気接続、またはこのインターフェース部分を介して上にある薄膜デバイスのインターフェース領域までの電気接続が、CMOS 互換の金属相互接続として実現されることが好ましい。

【 0 0 1 6 】

装置が 2 またはそれ以上の薄膜デバイスを備える、本発明による装置の有利な実施形態では、薄膜デバイスは同一の拡がりをもっており、そのスタッ�で相互に整合して設けられる。この点について、1 以上の分離層が、隣接する薄膜デバイス間に薄片状に設けられ、単独で、または選択された組み合わせそれぞれで、電気、温度、光、または機械的な絶縁機能または平面化機能を実行し、それぞれの場合に、それぞれの薄膜デバイスの前記インターフェース領域が、それぞれの分離層にある導通部（バイア）を介して電気的に接続されることが好ましい。

【 0 0 1 7 】

装置が 2 つ以上の薄膜デバイスを備える、本発明による装置の他の有利な実施形態では、薄膜デバイスが相互に位置ずれした重なり構造で配置される。

【 0 0 1 8 】

次いで薄膜デバイス間および / または任意選択の基板との間での電気接続は、ずらして配置されたスタッ�の段上に水平方向および垂直方向に延在して提供されることが好ましい。

【 0 0 1 9 】

次いで、1 つ以上の分離層が、隣接する薄膜デバイス間でインターリープ（薄片状に間挿）され、単独で、または選択された組み合わせで、それぞれが、電気、温度、光、または機械的な絶縁機能または平面化機能を実行すること、および分離層だけが隣接する 2 の薄膜デバイスの重なり合った部分に提供されることが好ましく、薄膜デバイス間の分離層が、別々の薄膜デバイス間の電気接続用の経路なしで非破壊層を形成するように、それぞれの薄膜デバイスのインターフェース部分が、そのずらして配置された領域内の薄膜デバイスの露出表面部分上に提供されることも好ましい。

【 0 0 2 0 】

最終的に、本発明による装置は、箔状の材料またはシリコンなどの硬質材料で形成されたキャリア基板上に設けることが可能なため有利であり、それぞれの場合に前記キャリア基板は、スタッ�構造で最下部の薄膜デバイスまたは任意選択で提供された電子回路を備えた基板に隣接して設けられる。

10

20

30

40

50

## 【0021】

次に、本発明による容量増大化可能なデータ処理装置、具体的にはデータ記憶装置について、例示的な実施形態および添付の図面を参照しながら、以下で、より詳細に説明する。

## 【0022】

本発明の主な目的は、データ記憶デバイスを提供することであり、したがって以下の本発明による装置は、メモリ・デバイスを実現して「装置」と呼ばれるものにすることに関する。本発明の基礎は、装置が相互に隣接しほぼ平行にスタックされた層の形態で実現可能であり、これらのスタック層がそれぞれ薄膜デバイスとして形成され、これが特有の機能および異なる機能を備え、異なる材料で形成することが可能な複数の薄膜副層から成ることである。

10

## 【0023】

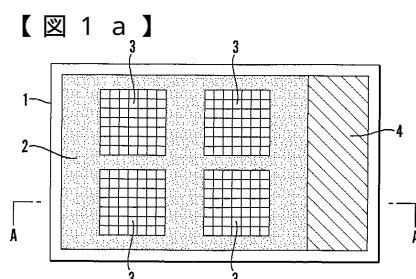

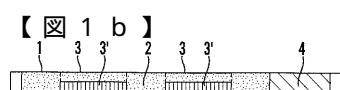

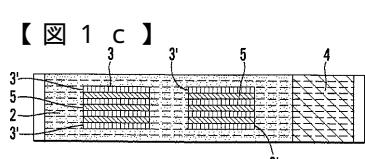

本発明で使用される薄膜デバイス1が、図1aの平面図に示される。薄膜デバイス1は、それぞれ回路領域2、メモリ領域3、およびインターフェース領域4で編成される。図1bでは、図1cの薄膜デバイスで線A-Aに沿う断面図が示される。本明細書で、薄膜技術で実現されるメモリ3'を含むメモリ領域3が、メモリに制御、通信、およびアドレス指定機能を実現するための電子回路を基にした薄膜を含む回路領域2の内部に設けられることが示される。アドレス指定機能は、メモリのタイプに応じて、たとえばメモリにおける書き込み、読み取り、および消去、ならびにインターフェース領域4を介したメモリとの間の通信を含むことになる。図1cは、図1aの薄膜デバイスで、これも線A-Aに沿う断面図であるが、ここでは実施形態が図1bとは異なり、メモリ領域3が、回路領域2内で垂直にスタックされているが相互に電気的絶縁層5によって分離された薄膜メモリ3'を有する。この点について、独立メモリ3'は、以下でより詳細に論じるように、勿論それぞれ多数の分離層によって構成され、さらに、具体的には示されていないが、インターフェース領域4を介した回路領域2の電子回路は、分離薄膜デバイスにおけるメモリを制御し、かつ、アドレス指定すために使用されるだけでなく、対応する回路および隣接して提供された薄膜デバイス1におけるその他のメモリとの通信も行うことを理解すべきである。

20

## 【0024】

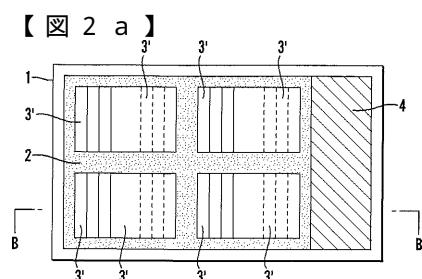

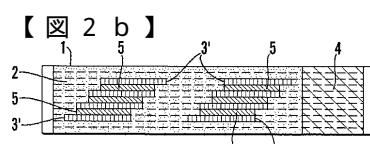

各独立薄膜デバイス1が多数の副層、典型的にはたとえば数十の副層からなると同時に、独立メモリ3'が4~5個よりも多くの副層からなる必要がない環境では、幾つかのメモリを、図1cに示されるように垂直方向に、または図2aの平面図、および、図2aの線B-Bに沿う断面図2bに見られるその他の有利な形態で、重ねることができる。ここでもまた、薄膜デバイス1の独立メモリ3'が重ねられるが、相互に位置をずらして配置される。図2aおよび図2bでは、電気的絶縁層5によって相互に絶縁された4つのメモリ3'を備えた4つのメモリ・スタックが示されている。各スタックでそれぞれ最下部および最上部のメモリだけが、参照番号3'で示されている。

30

## 【0025】

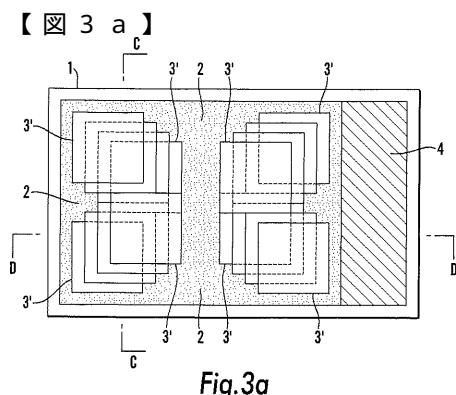

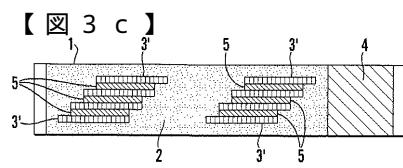

本発明で使用される薄膜デバイス1の他の実施形態が図3aに示されており、これは図2aの実施形態にほぼ対応し、位置ずれ配置されたメモリで作成されたメモリ・スタックを備えているが、ここでは図3aの平面図に示されるように、図3aの線C-Cに沿う断面図3bおよび図3aの線D-Dに沿う断面図3cで、こうしたスタックが対角線に沿って現れる。それぞれ図2aおよび図3aに示されるようなスタックのメモリ配置は、回路領域2の表面積を効率よく活用することに関して有利であると同時に、位置ずれ配置によって、メモリと回路領域2における電子回路との間の相互接続を簡略化することができる。もちろん、回路領域2内のメモリ領域3におけるメモリ3'の相互配置は、本質的になんらかの特定の幾何图形的配列に限定されるものではないが、実施形態および薄膜デバイス1の形態要素によって与えられる境界内で変えることができる。

40

## 【0026】

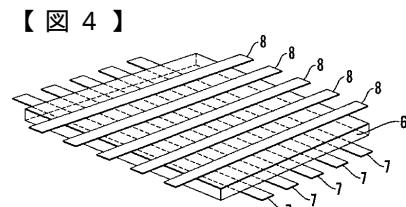

図4は、本質的に受動のマトリックス・アドレス可能メモリ3'の実施形態を概略的に

50

示す。この種のメモリは、たとえば、本出願人による PCT/NO98/00185 (その記載内容を本明細書に援用する) に開示されている。図4では、メモリ媒体6が、平行なストライプ状電極7からなる下になる電極セットと、平行なストライプ状電極8からなる上になる電極セットとで、それぞれサンドイッチされた状態で設けられる。下になる電極7および上になる電極8にそれぞれ電圧をかけることにより、メモリ媒体6における電極間の交差点に、たとえばメモリ媒体におけるインピーダンスの変化で表すことのできる、状態の変化が得られる。メモリ媒体6それ自体は、分子材料あるいは炭素質の無機材料または有機材料で形成されることが好ましい。通常は、メモリ媒体が非線形インピーダンス特性を有することが望ましく、下になる電極7と上になる電極8との間の交差点に形成される図示していないメモリ・セルをアドレス指定することにより、メモリ・マトリックスにおける他のメモリ・セルへのいわゆるスニーケ電流 (sneak currents: 予期せぬ電流) の発生を防ぐことが望ましい。これは、メモリ媒体に整流特性を与えることによって、好ましくはダイオード接合を形成する層の組込みによって、またはメモリ媒体6それ自体が自然発生的に電極材料とのダイオード接合を形成することによって達成できるので有利である。

#### 【0027】

メモリ材料6がポリマーである場合、その情報記憶能力は、電流または電圧が印加されたときのそのインピーダンス値の変化と、電流または電圧の印加を停止した後においても該変化したインピーダンス値の変化を維持することによって定まる。このメモリは、スイッチング可能材料 (この材料は、たとえば、ポリマー形態の強誘電性材料であり、その分極状態が特定の論理状態を表す)、または、M(TCNQ)等の電荷移動金属有機錯体であってよい。一般に、当該技術分野で知られた、マトリックス・アドレス指定可能メモリで使用可能な多数の異なるメモリ材料があり、この点について、たとえば前述の公開PCT/NO98/00185で言及されている。図4では、メモリはサンドイッチされた状態で設けられるが、ただし、他の電極構成、たとえば本出願に属するPCT/NO98/00212に開示されたようなブリッジ構成を使用することは無条件かつ全面的に可能であって、下になる電極7および上になる電極8が交差点で相互に絶縁されることになる場合、もちろんその一部が、このような場合でもメモリ材料がその情報記憶能力を保証する特性を持たなければならないことを必要とする電極を介して、メモリ材料6が設けられる。典型的には、この場合、メモリ材料は共役ポリマーであってよい。

#### 【0028】

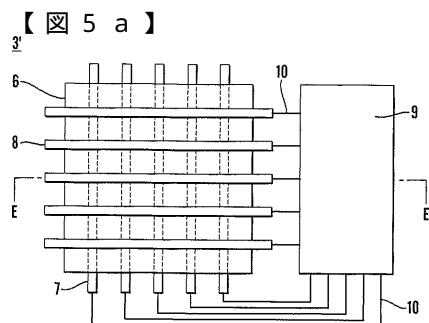

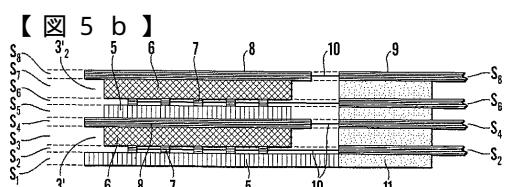

メモリ3' と回路領域2内における回路9との間の相互接続が、図5aの概略平面図に示される。マトリックスの電極6、および7はそれぞれ、ワード線およびビット線10を介して回路9に接続される。図5aの線E-Eに沿う断面図では、薄膜デバイス1における副層s<sub>1</sub>~s<sub>8</sub>として形成された図5aの配置が、図5bに示すように表され、全体として薄膜技術で実現される2つのスタック・メモリ3'1、3'2、および回路9が示される。具体的に言えば、メモリ3'の電流経路および導体経路、すなわち下になる電極7および上になる電極8、ならびに電極を回路9に接続する線10は、ほぼすべてが同じ副層内、ここでは、たとえばs<sub>2</sub>、s<sub>4</sub>、s<sub>6</sub>、0g s<sub>8</sub>に提供され、その一部が目的に従って、1つおよび同じ副層にある導電性構造体形態で、このような電流経路および導体経路をより一層生成しやすくする。

#### 【0029】

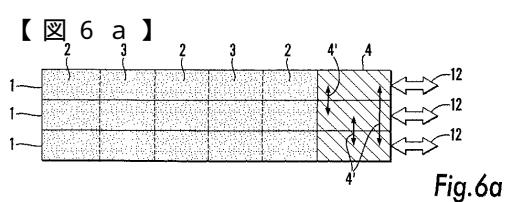

図6aは、幾つかの(この場合は3つの)薄膜デバイス1が接合されてスタック構造になされる態様を示している。前述のように、回路領域は2で表され、メモリ領域は3で表され、図では、これらが互いに正確に整合して示されているが、これは無条件である。インターフェース領域4が回路領域の側部に設けられ、対応して整合しており、薄膜デバイス1間の電気的な接続は矢印4'で概略的に示され、インターフェース領域4を通って垂直に延在している。さらに、インターフェース領域4は、データの入力および出力のために図示されていない外部デバイスまたは周辺デバイスと薄膜デバイス1を接続するI/Oインターフェース12で形成することができる。

10

20

30

40

50

## 【0030】

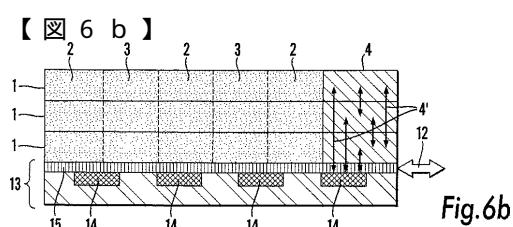

図6bもスタック構造の薄膜デバイス1を示すが、ここでは、能動電子回路14を有する基板13上に設けられる。この基板は、無機半導電性材料、たとえばシリコンまたはシリコン変性材でより良く実現することが可能であり、能動電子回路は、たとえばCMOS技術で実現される。基板13における能動電子回路14は、薄膜デバイスにおけるメモリの管理における制御タスクおよび通信タスクを意図するものであって、薄膜デバイス1の回路領域2で、薄膜回路と協働するように適合される。この場合、回路領域2における薄膜回路を、効率の良いメモリの制御および駆動を維持するために必要なものに制約できるので、メモリ目的で薄膜デバイス1により多くの空きを残すことになると同時に、たとえばメモリへのデータの並列入出力に関して、誤り訂正、メモリの再マッピングなどのための処理タスクは、基板における能動電子回路14によって実施されるデバイスの処理によって対処することができる。スタックされた薄膜デバイスにおけるインターフェース領域4にある垂直相互接続4'は、基板13上のインターフェース部分15と通信し、このインターフェース部分を介した、回路14と垂直相互接続4'との間の電気的接続は、たとえばインターフェース部分15に形成される金属経路によって行なうことができるが、これはCMOS回路を基板内に設ける場合には、CMOS互換プロセスで実行されなければならない。スタックされた薄膜デバイスにおけるインターフェース領域4にI/Oインターフェース12を作成する代わりに、ここでは基板のインターフェース15に関してこのI/Oインターフェース12を提供することができる。

## 【0031】

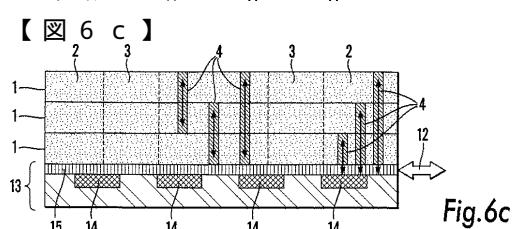

本発明による装置の他の実施形態が、図6cに示される。ここでも前述のように、薄膜デバイスは基板13上のスタック構造体内に設けられるが、薄膜デバイス1のインターフェース領域4はその縁部分に提供する代わりに、薄膜デバイス1の間およびこれらと基板13におけるインターフェース15との間に垂直の相互接続を作成するために、独立したインターフェース領域4が設けられる。これは、独立薄膜デバイスにおける回路領域を位相的(topologically:トポロジカル)に考えられた有利なレイアウトにすることに寄与し、その中の水平な電流経路の必要性を減少させることができる。

## 【0032】

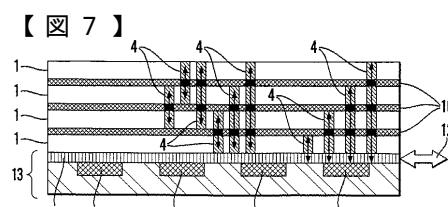

図6cの実施形態の変形で、装置を図7に示されるように実現することができる。ここでは各薄膜デバイス1の間に分離層16が設けられている。これらの層については、例えば、本出願人によるノルウェー特許出願第980781号(その記載内容を本明細書に援用する)に記載されている。これらの分離層は、単独でまたは選択された組み合わせのいずれかで、たとえば電気、温度、光、または機械的に分離した機能を実施することができる。スタックされた構成では、平面化層としても使用することができる。薄膜デバイス1におけるインターフェース領域4が図7に示されるように設けられるときには、これらが分離層16を貫通することを前提としており、たとえば分離層における経路(vias:バイア)により相互接続を行わなければならず、その中には、分離機能に関して有害であり、さらに製造過程のコスト増加をもたらす可能性のあるものもある。これを避ける方法の1つが、前述のように薄膜デバイス1をスタック構造内に設けることであって、ここでは相互に位置をずらして配置することである。

## 【0033】

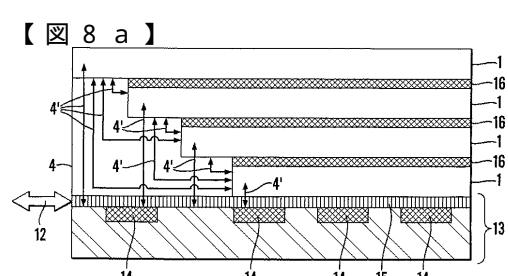

この一実施形態が図8aに示されており、ここでは再度薄膜デバイスが基板13上に設けられ、分離層16によって相互に分離されるが、ここでインターフェース領域4は、基板13におけるインターフェース15とその上にある薄膜デバイス側面の露出した薄膜デバイスの段状部との間に設けられる。薄膜デバイス1相互間またはこれらと基板15との間の相互接続は、それぞれ水平および垂直の相互接続4'によって概略的に示されている。

## 【0034】

図8aの実施形態では、スタックされた構成の反対側に、さらに図示されていないキャリア基板を薄膜デバイス1に隣接して提供することができる。製造の際には、薄膜デバイ

10

20

30

40

50

ス1の配置構成を、図示されていないキャリア基板から上方に向かって実行していくことが可能であり、その後能動電子回路14を備えた基板13が、製造プロセスの最終ステップとしてスタックされた構成の上部に設けられる。これは、インターフェース領域4を介したインターフェース部分15への相互接続が、先行する製造ステップで薄膜デバイス1を配置した後に実現されることを示唆しており、場合によっては、コスト面と相互接続の作成が簡略化される面の両方で有利となる可能性がある。

【0035】

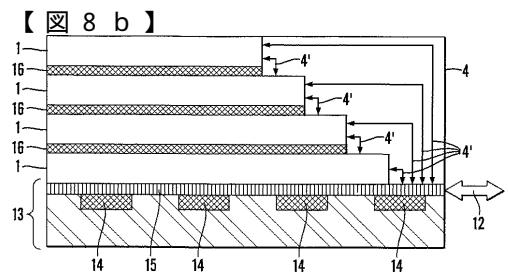

図8bは、図8aの実施形態にほぼ対応する実施形態を示す図であり、薄膜デバイス1が分離層16によって相互に分離された状態で設けられ、さらにここでもスタック構造体内で位置をずらして配置されるため、基板13に最も近い薄膜デバイス1はこれを完全に覆っておらず、基板の表面に向かって降りていく段を形成する。次いでここでも、スタック構造における段状部分の上にインターフェース領域4が設けられ、薄膜デバイス1相互間またはこれらと基板13のインターフェース15との間の相互接続4'は、スタック構造における段状部を覆って水平および垂直に延在する。

【0036】

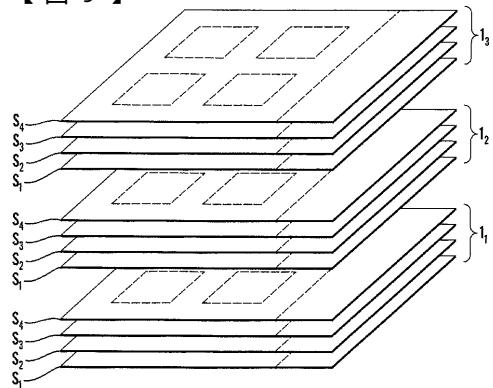

図9は、各独立薄膜デバイス1<sub>1</sub>、1<sub>2</sub>、1<sub>3</sub>が、4つの層S<sub>1</sub>～S<sub>4</sub>として示される多数の副層によってどのように構成されるかを、かなり概略的に示す図である。水平方向の電気的相互接続は、この副層内の薄膜材料を変化させることによって、副層Sの一体化部分として作成することが可能であり、それに対応して、垂直方向の導電性相互接続は、薄膜における導電性材料部分を整合させることによって、複数の副層Sを貫通して作成することができる。特定条件下では、斯かる導電性または半導電性構造体を、すでに形成された薄膜スタックにその状態で形成することが可能であるか、または、各独立副層Sに個別に形成することが可能であり、その後、これを積層するか、または他の方法で薄膜デバイス1を形成するスタックに接合する。本出願人によるPCT/NO99/00023（その記載ないようを本明細書に援用する）では、たとえば光放射または粒子放射などの放射によって、スタックされた薄膜デバイス内に3次元の導電性および半導電性の構造体を作成するために、水平および垂直の導電性構造物を元の位置に生成する方法について論じている。ただし、こうした構造体の生成は、特別な発生器/変調器デバイスを使用し、電界を独立副層Sをパターン化するために空間的に変調して印加することによっても実行することが可能であり、こうしたことについては、本出願人によるPCT/NO99/00022（その記載ないようを本明細書に援用する）で論じられている。

【0037】

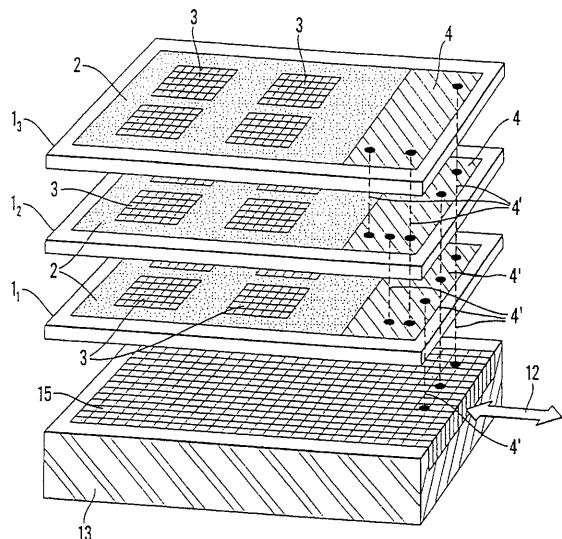

本発明による装置は、図10に、その主要構成要素内で分解して示されており、3つの薄膜デバイス1<sub>1</sub>、1<sub>2</sub>、1<sub>3</sub>および薄膜デバイスの縁部分（側辺寄りの部分）に設けられたインターフェース領域4が備えられている。図10の装置は、図示されていない能動電子回路およびインターフェース15を備え、装置全体に対するI/Oインターフェース12も形成している基板13を使用して図示されている。この種の基板13を本発明による装置に使用することは無条件であるが、薄膜デバイス1をスタックした構成も全く同様に、たとえば箔状の材料またはシリコンなどの硬質材料で形成された受動キャリア基板上のみに提供することが可能である。

【0038】

図10の実施形態は、前述の国際特許出願PCT/NO98/00185に示された、対応する実施形態と同様の特徴を有する。この特許出願では、本発明による装置で使用するのに好適な、より詳細なマトリックス・アドレス指定可能メモリ手段が開示されており、スタックされた薄膜層内に3次元位相によって回路を実現する方法も開示されている。これにより、薄膜技術で、例えば当該のダイオード、トランジスタ、相補型トランジスタ回路、および論理ゲートを実現することが可能であるが、それらについては本明細書で詳細に論じない。独立薄膜デバイス内では、メモリを多数のメモリ・タイプ、すなわちRAM、ROM、WORM、ERASABLE、またはREWITABLE、あるいはこうしたメモリを組み合わせたもののうちの、1以上として構成することができることも理

10

20

30

40

50

解されよう。これについても、前述の特許出願で詳細に開示されているため、本明細書ではこれ以上説明しないものとする。

#### 【0039】

本明細書による装置における各薄膜デバイス1は、スタッツ構造体にするための接合を実行する前に、専用分離層16上に設けることができる。薄膜デバイス1における独立副層の厚さは、 $1 \mu m$ よりもかなり下、たとえば $0.1 \mu m$ まで薄くすることが可能であるが、これはすなわち、キャリア基板または基板上に設けられる、分離層16に容易に対応できる薄膜デバイス1と合わせて、たとえば厚さ $20 \mu m$ の構成要素を構成する場合、100を超える副層を含むことが可能であって、薄膜技術で比較的複雑な電子回路を実現するのに十分であり、同時に各メモリ領域3に何十もの独立メモリ3'を積み重ねできることを示唆している。大きさが $1 \mu m^2$ のメモリ・セルを使用すると、たとえば $1 cm^2$ の単一のメモリは、この種のメモリ・セルを $10^8$ 個含むことが可能であり、したがって、少なくとも $10^8$ ビットを格納することができる。たとえばクレジット・カード・サイズの薄膜デバイスであれば、こうした独立メモリを40個含むことになり、したがって0.5Gバイトを格納する。たとえばP C M C I Aのような厚さ3mmのカードとして提供可能な装置の場合、100個のスタッツされた薄膜デバイスを含むことが可能であり、この装置には、形態要因によって与えられる条件の範囲内で、50Gバイトを格納できることがわかる。各薄膜デバイスの表面積をより効率よく活用する、すなわちメモリ領域3の面積を大きくすることによって、また個々のメモリ・セルの大きさは小さくすることによって、少なくとも $0.25 \mu m \times 0.25 \mu m$ サイズまで小さくすることは現実的であると思われる。さらに大きな記憶容量を得ることができる。この場合、单刀直入に言えば、記憶容量は800Gバイトまで上げることが可能であり、したがってこのように本発明により実現される装置は、現在ほとんどのパーソナル・コンピュータまたはワークステーションで使用可能な大容量記憶デバイスまたはハードディスクに代わるものとなる可能性がある。 20

#### 【0040】

所与のデータ記憶密度に従った条件の下では、装置の形態要因、面積、および厚さによって合計のデータ記憶密度が与えられることになる。基本的および実際的に、設計記憶容量の増大化は、十分な数の薄膜デバイスを使用することによって実施される。たとえば、本発明による装置をP C M C I Aカード・タイプ3に一体化した場合、このカードの従来のハードディスク・メモリに代わるものとなることができる。所与の標準が寸法に関する制約を設けていない場合、本発明による装置は、たとえばパーソナル・コンピュータにおける既存のハードディスク・ソリューションに代わるものとなることが可能であり、好適に増大化してTバイト範囲の大規模記憶容量を提供することができる。 30

#### 【0041】

最終的に、本発明による装置が平面的なスタッツ構造で実現された場合であっても、そのスタッツ構造体が逸脱した幾何图形的配列によって形成されていることも考えられる点に注目されたい。薄膜が柔軟性材料によって形成され、能動回路を備えた無機半導体に基づいた基板は使用されていないが、たとえば箔状材料形態の柔軟なキャリア基板のみが使用されている場合、用途によって有利であれば、たとえば装置全体を円筒形または管状の構成に巻き上げられることが考えられる。どのような場合でも、柔軟性材料によって実現された本発明による装置は、平面性または剛性に関する要件を避けることのできる他の物体に組み込むことが可能であり、したがって、従来のコンピュータ技術の範囲とは全く異なる環境で応用例を実施する場合に使用可能であることが明白である。 40

#### 【図面の簡単な説明】

【図1a】 本発明による装置で使用される薄膜デバイスの平面図である。

【図1b】 図1aに示す第1実施形態である薄膜デバイスの第1の実施形態で、線A-Aに沿う断面図である。

【図1c】 図1aに示す第2実施形態である薄膜デバイスの第2の実施形態で、線A-Aに沿う断面図である。 50

【図 2 a】 本発明による装置で使用される、第 3 実施形態である薄膜デバイスの第 3 の実施形態の平面図である。

【図 2 b】 図 2 a に示す薄膜デバイスの線 B - B に沿う断面図である。

【図 3 a】 本発明による装置で使用される、第 4 実施形態である薄膜デバイスの第 4 の実施形態を示す図である。

【図 3 b】 図 3 a に示す薄膜デバイスの線 C - C に沿う断面図である。

【図 3 c】 図 3 a に示す薄膜デバイスの線 D - D に沿う別他の断面図である。

【図 4】 図 1 ~ 図 3 のうちの 1 つの薄膜デバイスに使用される、マトリックス・アドレス指定可能メモリの例の模式的概略斜視図である。

【図 5 a】 図 1 ~ 図 3 のうちの 1 つに示されるような薄膜デバイスの能動電子回路に接続された、図 4 のマトリックス・アドレス指定可能メモリの平面図である。 10

【図 5 b】 図 5 a に示すのメモリで線 E - E に沿う概略断面図である。

【図 6 a】 本発明による装置の第 1 の実施形態を示す図である。

【図 6 b】 本発明による装置の第 2 の実施形態を示す図である。

【図 6 c】 本発明による装置の第 3 の実施形態を示す図である。

【図 7】 本発明による装置の第 4 の実施形態を示す図である。

【図 8 a】 本発明による装置の第 5 の実施形態の変形を示す図である。

【図 8 b】 本発明による装置の第 5 の実施形態の変形を示す図である。

【図 9】 薄膜技術で副層を接合して、本発明で使用される薄膜デバイスにすること、および幾つかの斯かる薄膜デバイスを接合して本発明による装置にする様子を示す模式図である。 20

【図 10】 本発明による装置の好適例を、その主要構成要素に分解した模式図である。

Fig.1a

Fig.1b

Fig.1c

Fig.2a

Fig.2b

Fig.3a

Fig.3b

Fig.3c

Fig.4

Fig.5a

Fig.5b

Fig.6a

Fig. 6b

Fig. 6c

Fig. 7

Fig. 8a

Fig. 8b

【図9】

Fig.9

【図10】

---

フロントページの続き

(72)発明者 グデセン、ハンス、グデ

ベルギー国 ブリュッセル、リュ フルトン 17

(72)発明者 ノルダル、ペル - エリク

ノルウェー国 アスケル、バスタドリイゲン 19

(72)発明者 レイスタド、ゲイル、アイ

ノルウェー国 サンドビカ、ヨングスツッベン 19

(72)発明者 ベルグレン、ロルフ、マグヌス

スウェーデン国 フレタクロステル、ベルグバドスベーゲン 14

(72)発明者 カールソン、ヨハン、ロジャー、アクセル

スウェーデン国 リンケピング、ステンホグスベーゲン 168

(72)発明者 ゲスタフソン、ベングト、ゴーラン

スウェーデン国 リンケピング、トルムスラガレガタン 33

審査官 河口 雅英

(56)参考文献 特開平09-045871(JP,A)

特開平03-137896(JP,A)

特開昭62-181464(JP,A)

特表平09-503622(JP,A)

米国特許第05714768(US,A)

(58)調査した分野(Int.Cl., DB名)

H01L 27/00

H01L 27/10

G11C 13/00