【公報種別】特許法第17条の2の規定による補正の掲載

【部門区分】第7部門第2区分

【発行日】平成25年12月5日(2013.12.5)

【公表番号】特表2013-509720(P2013-509720A)

【公表日】平成25年3月14日(2013.3.14)

【年通号数】公開・登録公報2013-013

【出願番号】特願2012-537084(P2012-537084)

【国際特許分類】

H 01 L 29/78 (2006.01)

【F I】

H 01 L 29/78 6 5 2 H

H 01 L 29/78 6 5 2 K

H 01 L 29/78 6 5 3 C

【手続補正書】

【提出日】平成25年10月18日(2013.10.18)

【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

【補正の内容】

【特許請求の範囲】

【請求項1】

トレンチ金属酸化物半導体電界効果トランジスタ(TMOSFET)であって、

ドレイン領域と、

複数のメサであって、前記複数のメサはそれぞれ、ドリフト領域および本体領域を含み、

複数のゲート領域間に配置される、複数のメサと、

前記ゲート領域と、前記本体領域、前記ドリフト領域、および前記ドレイン領域との間に

配置された複数のゲート絶縁体領域であって、前記メサの幅は、前記ゲート絶縁体領域と

前記本体領域との間の界面における量子井戸寸法のオーダーであり、かつ、前記ゲート領域と

前記ドレイン領域との間の前記ゲート絶縁体領域の厚さに起因して、オフ状態において

ゲートトウードレイン電界が発生し、前記ゲートトウードレイン電界は、前記ドリフト

領域内において実質的に横方向である、複数のゲート絶縁体領域と、

を含む、トレンチ金属酸化物半導体電界効果トランジスタ(TMOSFET)。

【請求項2】

前記ゲート絶縁体領域は酸化物を含む、請求項1のトレンチ金属酸化物半導体電界効果ト

ランジスタ(TMOSFET)。

【請求項3】

前記ドレイン領域は高nドープ半導体を含み、

前記ドリフト領域は低nドープ半導体を含み、

前記本体領域は中程度のpドープ半導体を含む、

請求項2のトレンチ金属酸化物半導体電界効果トランジスタ(TMOSFET)。

【請求項4】

前記ドリフト領域は、前記ドレイン領域から前記複数の本体領域に向かって低減する段階

的なドーピングプロファイルを含む、請求項1のトレンチ金属酸化物半導体電界効果ト

ランジスタ(TMOSFET)。

【請求項5】

前記ドリフト領域のドーピング濃度は、立方センチメートあたりおよそ5.00E+14

~8.00E+17である、請求項1のトレンチ金属酸化物半導体電界効果トランジスタ

(T M O S F E T)。

【請求項 6】

前記メサの幅は、およそ 0.03 ~ 2.0 ミクロン (μm) である、請求項 1 のトレンチ金属酸化物半導体電界効果トランジスタ (T M O S F E T)。

【請求項 7】

前記ゲート領域と前記ドレイン領域との間の前記ゲート絶縁体領域の厚さは、およそ 0.1 ~ 4.0 ミクロン (μm) である、請求項 1 のトレンチ金属酸化物半導体電界効果トランジスタ (T M O S F E T)。

【請求項 8】

降伏電圧はおよそ 15V ~ 55V である、請求項 1 のトレンチ金属酸化物半導体電界効果トランジスタ (T M O S F E T)。

【請求項 9】

ON 状態抵抗は、平方ミリメートルあたりおよそ 2 ~ 9 ミリオーム (mohm · mm<sup>2</sup>) である、請求項 1 のトレンチ金属酸化物半導体電界効果トランジスタ (T M O S F E T)。

。

【請求項 10】

前記メサの幅は、およそ 0.03 ~ 2.0 ミクロン (μm) であり、かつ、前記ゲート領域と前記ドレイン領域との間の前記ゲート絶縁体領域の厚さは、およそ 0.1 ~ 4.0 ミクロン (μm) である、請求項 1 のトレンチ金属酸化物半導体電界効果トランジスタ (T M O S F E T)。

【請求項 11】

前記記ドリフト領域は、段階的なドーピングプロファイルを含み、前記段階的なドーピングプロファイルは、前記複数のメサのそれぞれの縁部から前記複数のメサのそれぞれの中心へ向かって横方向に変化する、請求項 1 のトレンチ金属酸化物半導体電界効果トランジスタ (T M O S F E T)。

【請求項 12】

オフ状態における前記ゲート領域と前記ドレイン領域との間の漏れ磁場により、前記メサ内のドリフト領域電荷の空乏が支援され、これにより、実質的に一定な降伏電圧のための前記ドリフト領域内により高いドーピングが得られる、請求項 1 のトレンチ金属酸化物半導体電界効果トランジスタ (T M O S F E T)。

【請求項 13】

前記ゲート領域と前記ドレイン領域との間の前記ゲート絶縁体領域の厚さにより、ドリフト領域ドーピング濃度が上昇した場合でも、さらなるゲート電荷上昇無く、実質的に一定の降伏電圧が得られる、請求項 1 のトレンチ金属酸化物半導体電界効果トランジスタ (T M O S F E T)。

【手続補正 2】

【補正対象書類名】明細書

【補正対象項目名】全文

【補正方法】変更

【補正の内容】

【発明の詳細な説明】

【発明の名称】トレンチ金属酸化物半導体電界効果トランジスタ

【背景】

【0001】

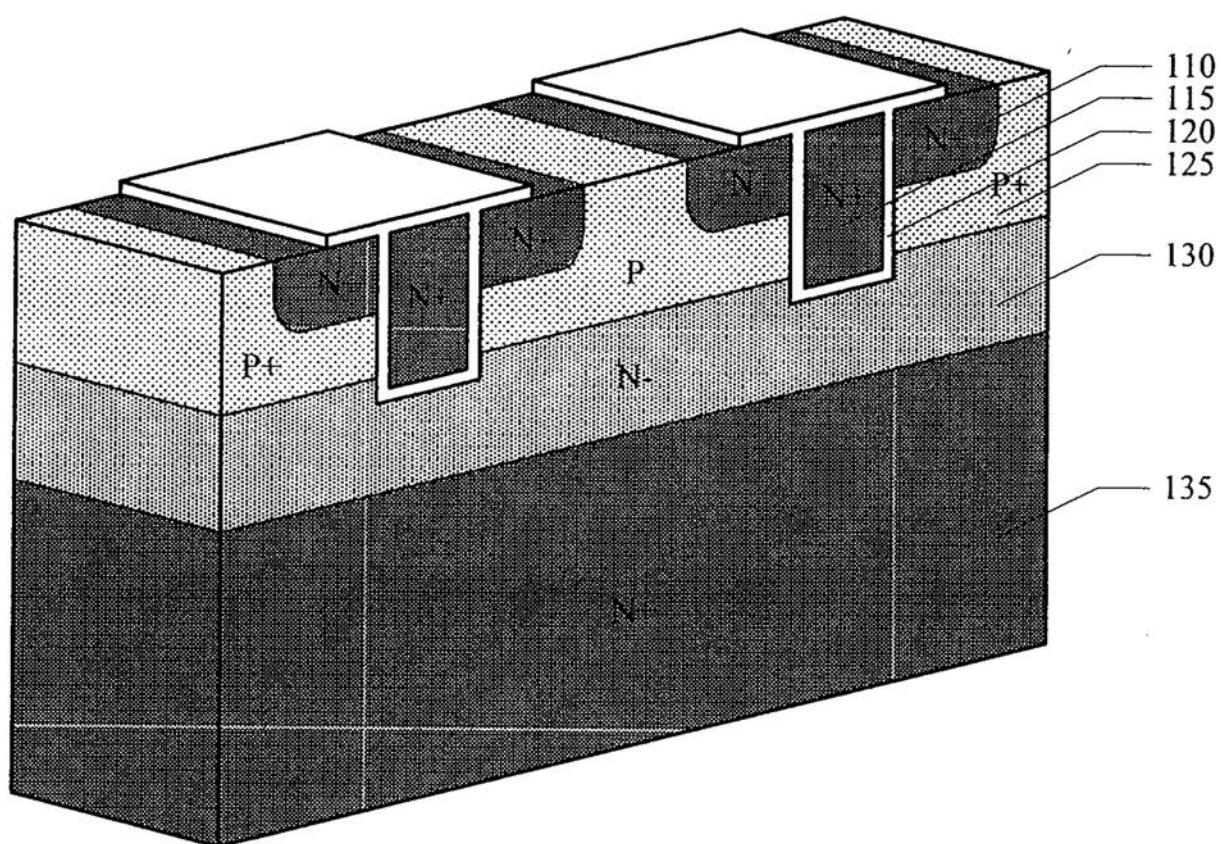

図 1 を参照して、従来技術によるトレンチ金属酸化物半導体電界効果トランジスタ (T M O S F E T) 100 の断面斜視図が図示されている。T M O S F E T 100 は、複数のソース領域 110 と、複数のゲート領域 115 と、複数のゲート絶縁体領域 120 と、複数の本体領域 (body region) 125 と、ドリフト領域 130 と、ドレイン領域 135 とを含むがこれらに限定されない。

## 【0002】

ドリフト領域130は、ドレイン領域135と、本体領域125との間に配置される。ソース領域110、ゲート領域115およびゲート絶縁体領域120は、本体領域125内に配置される。ゲート領域115およびゲート絶縁体領域120は、縞状または閉鎖状のセル構造として形成され得る。ゲート絶縁体領域120は、ゲート領域115を包囲する。よって、ゲート領域115は、ゲート絶縁体領域120によって周囲の領域から電気的に絶縁される。ゲート領域115は、装置100の共通ゲートを形成するように、連結される。ソース領域110は、ゲート絶縁体領域120の周囲に沿って形成され得る。ソース領域110は、装置100の共通ゲートを形成するように、連結される。ソース領域110はまた、典型的にはソース／本体コンタクト（図示せず）によって本体領域125へと連結される。

## 【0003】

1つの実行様態において、ソース領域110およびドレイン領域135は、高nドープ（N+）半導体（例えば、リンまたはヒ素でドープされたシリコン）であり得る。ドリフト領域130は、低nドープ（N-）半導体（例えば、リンまたはヒ素でドープされたシリコン）であり得る。本体領域125は、pドープ（P）半導体（例えば、ホウ素でドープされたシリコン）であり得る。ゲート領域115は、高nドープ（N+）半導体（例えば、リンでドープされたポリシリコン）であり得る。ゲート絶縁体領域120は、絶縁体（例えば、二酸化珪素）であり得る。

## 【0004】

ソース領域110に対するゲート領域115の電位が装置100の閾電圧を上回った場合、ゲート絶縁体領域120の周辺に沿って、伝導チャネルが本体領域125内に誘導される。その後、T M O S F E T 1 0 0 は、ドレイン領域135とソース領域110との間において電流を伝導させる。その結果、前記装置はON状態となる。

## 【0005】

ゲート領域115の電位が前記閾電圧を下回った場合、前記チャネルによる誘導が停止する。その結果、ドレイン領域135とソース領域110との間に付加された電位に起因する電流は、両者間に流れなくなる。そのため、装置100はオフ状態となり、本体領域125およびドレイン領域135によって形成された接合により、前記ソースおよびドレインに亘って付加された電圧が支持される。

## 【0006】

低nドープ（N-）ドリフト領域130に起因して発生した空乏領域は、本体領域125およびドレイン領域130の双方内に延びて、これによりパンチスルーエフェクトを低下させる。このように、低nドープ（N-）ドリフト領域130は、T M O S F E T 1 0 0 の降伏電圧を増加させるように機能する。

## 【0007】

T M O S F E T 1 0 0 のチャネル幅は、ゲート絶縁体領域120の周辺に沿った複数の前記ソース領域110の長さの関数である。装置100のチャネル長さは、ゲート絶縁体領域120の周辺に沿ったソース領域110とドリフト領域130との間の本体領域125の関数である。よって、装置100のチャネル幅と長さとの間の比が大きくなる。よって、パワーM O S F E T用（例えば、パルス幅変調（P W M）電圧レギュレータ内のスイッチング素子）においてT M O S F E T装置100を有利に用いることが可能となる。

## 【要旨】

## 【0008】

本文書は、フィールドブースト型(field boosted)金属酸化物半導体電界効果トランジスタの分野に関する。本技術の実施形態は好適には、フィールドブースト型電界効果トランジスタの分野に向けられる。本技術は、以下の記載および添付図面を参照すれば、最良に理解され得る。以下の記載および添付図面は、本技術の実施形態を例示するためのものである。一実施形態において、トレンチ金属

酸化物半導体電界効果トランジスタ (T M O S F E T ) は好適には、ドレイン領域と、複数のゲート領域と、複数のドリフト領域と、複数の本体領域 (body region) と、複数のソース領域と、複数のゲート絶縁体領域とを含む。前記ゲート領域は、前記ドレイン領域の上方に配置される。前記ドリフト領域は好適には、前記ゲート領域間のメサ内で前記ドレイン領域の上方に配置される。前記本体領域は好適には、前記メサ内において前記ドリフト領域の上方において前記ゲート領域に隣接して配置される。前記ソース領域は好適には、前記メサ内において前記本体領域の上方に配置される。前記ゲート絶縁体領域は好適には、前記ゲート領域と、前記ソース、本体、ドリフトおよびドレイン領域との間に配置される。前記メサの幅は好適には、およそ  $0.03 \sim 1.0$  ミクロン ( $\mu m$ ) である。前記ゲート領域と前記ドレイン領域との間の前記ゲート絶縁体領域の厚さは好適には、およそ  $0.1 \sim 4.0 \mu m$  である。より詳細には、本文書は、以下の好適な観点を開示する。トレンチ金属酸化物半導体電界効果トランジスタ (T M O S F E T ) は、複数のゲート領域間に配置された複数のメサを含む。各メサは、ドリフト領域および本体領域を含む。前記メサの幅は、前記ゲート絶縁体領域と前記本体領域との間の界面において量子井戸寸法のオーダーである。前記 T M O S F E T はまた、前記ゲート領域と、前記本体領域、前記ドリフト領域および前記ドレイン領域との間に配置された複数のゲート絶縁体領域を含む。前記ゲート領域と前記ドレイン領域との間の前記ゲート絶縁体領域の厚さに起因して、オフ状態においてゲートトウードレイン電界は実質的に横方向において発生し、これにより、前記ドリフト領域内の電荷の空乏化が支援される。

【図面の簡単な説明】

【0009】

本技術の実施形態を、制限目的ではなく例示目的のために添付図面中に示す。図面中、類似の参照符号は、類似の要素を指す。

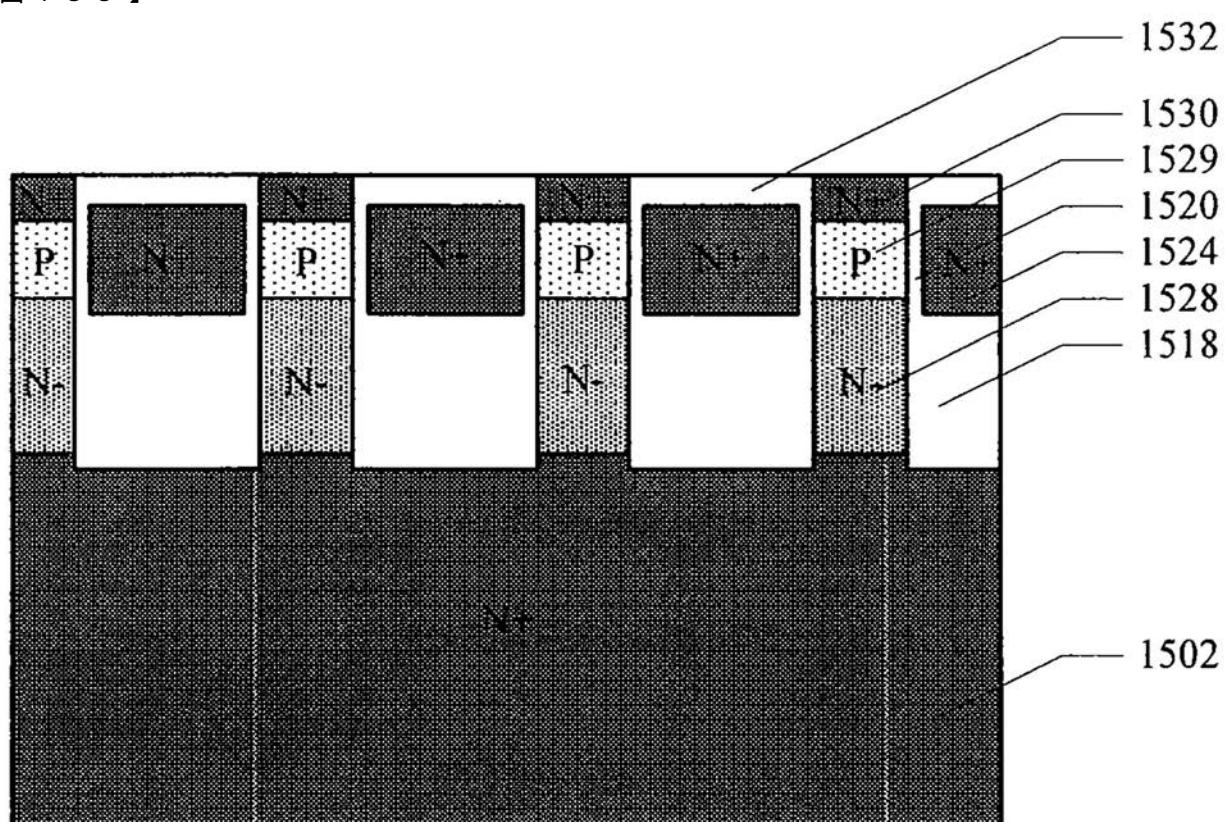

【図1】図1は、従来技術によるトレンチ金属酸化物半導体電界効果トランジスタ (T M O S F E T ) の断面斜視図である。

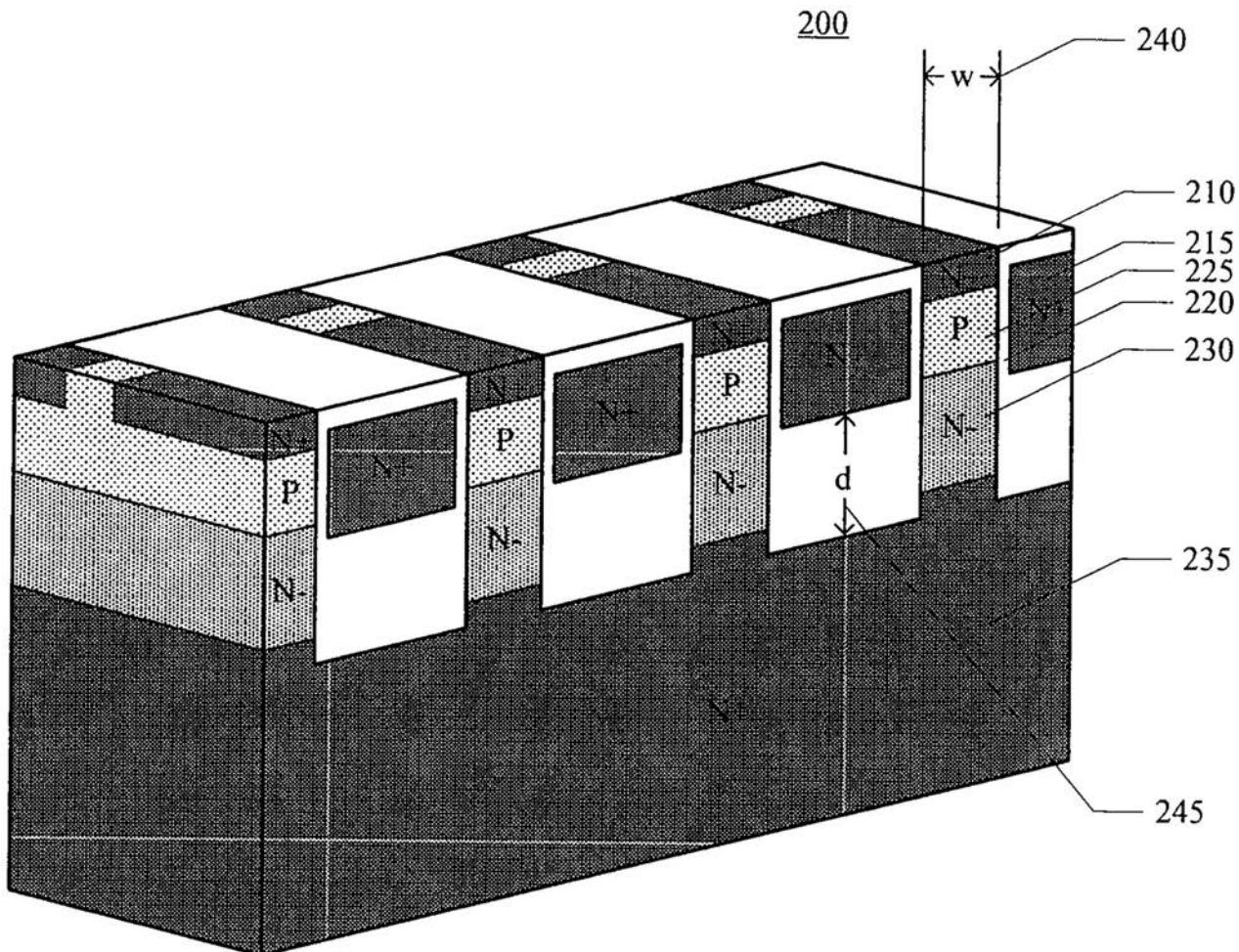

【図2】図2は、本技術の一実施形態によるT M O S F E T の断面斜視図である。

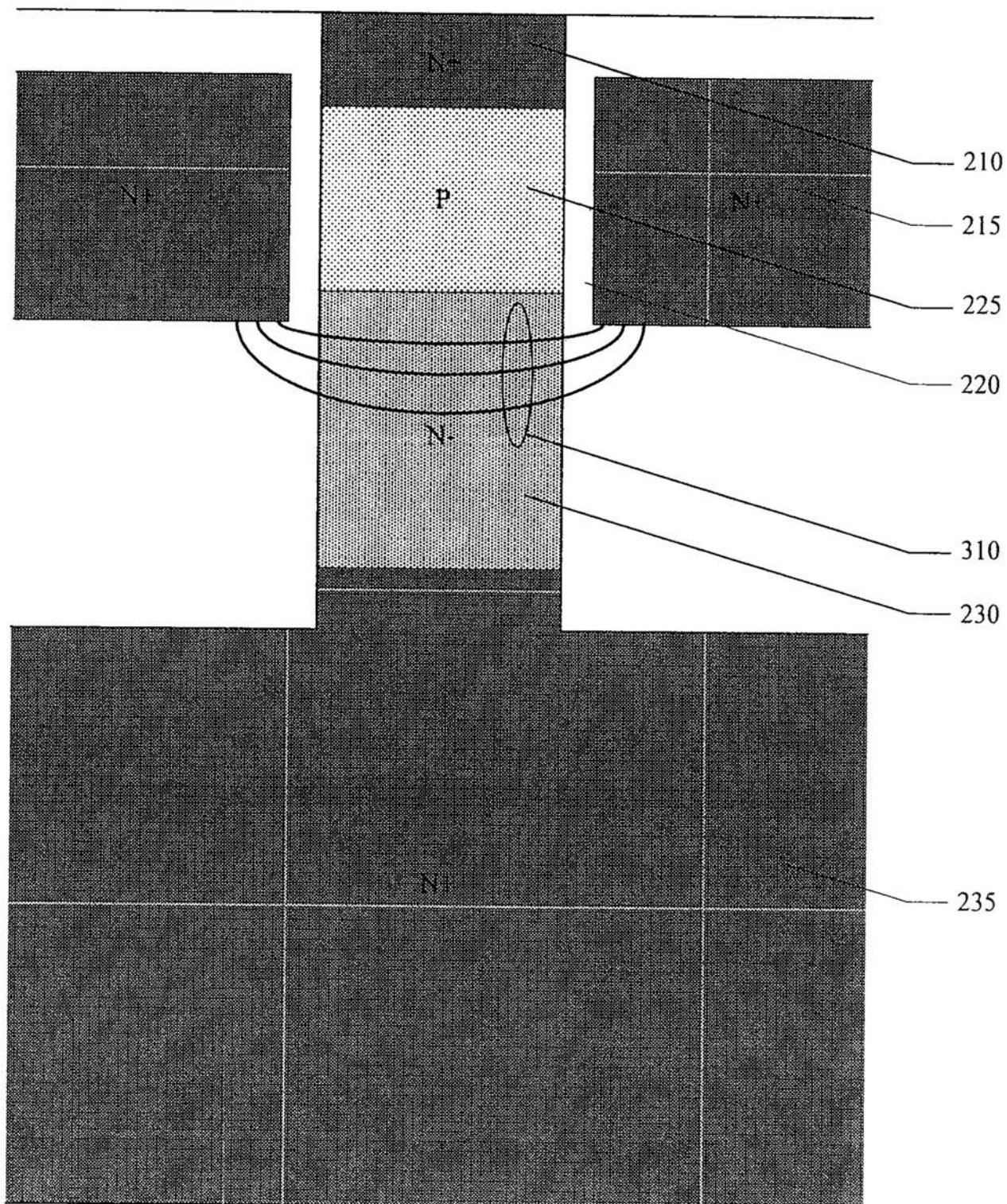

【図3】図3は、本技術の一実施形態によるT M O S F E T の拡大断面図である。

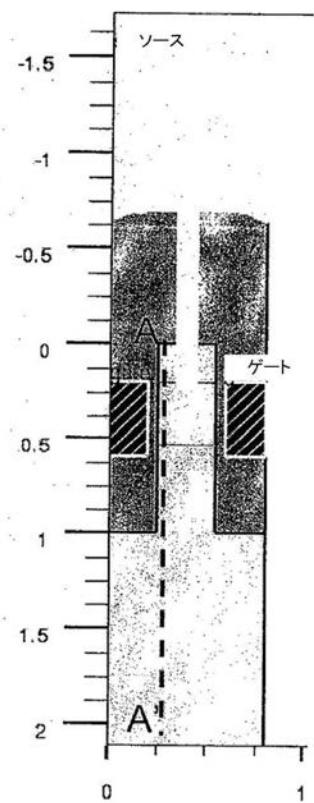

【図4】図4は、本技術の一実施形態による例示的T M O S F E T の断面図である。前記T M O S F E T のメサ幅は  $0.3 \mu m$  であり、厚さが  $0.4 \mu m$  のゲート絶縁体がゲート領域とドレイン領域との間に設けられている。

【図5】図5は、従来技術による従来のT M O S F E T の断面図である。前記T M O S F E T のメサ幅は  $0.3 \mu m$  であり、厚さが  $0.05 \mu m$  のゲート絶縁体がゲート領域とドレイン領域との間に設けられている。

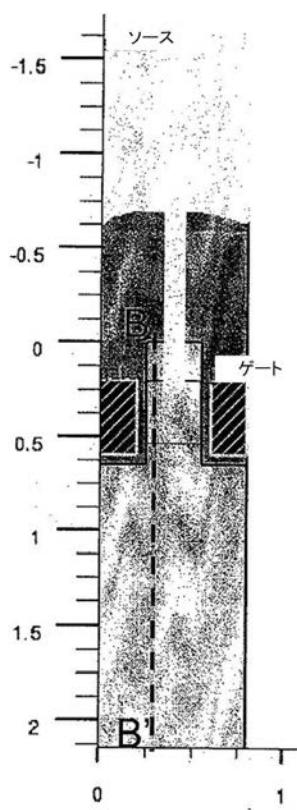

【図6】図6は、図4中に示す例示的T M O S F E T の線A A' に沿ったネットドーピングプロファイルと、図5中に示す従来のT M O S F E T の線B B' に沿ったドーピングプロファイルとを示す。

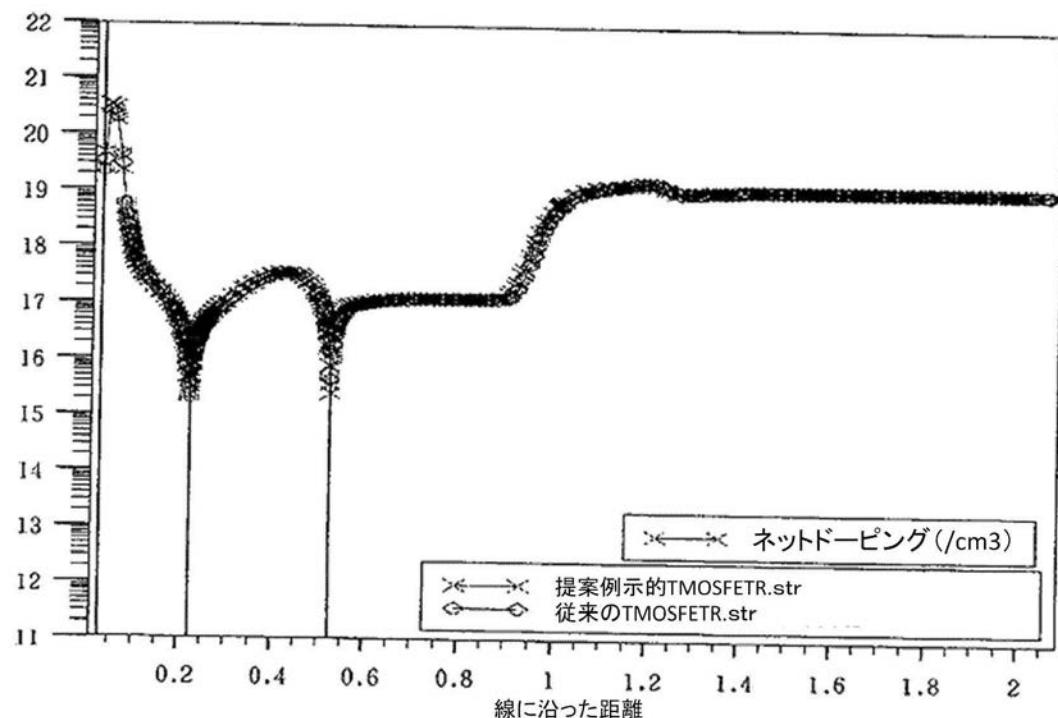

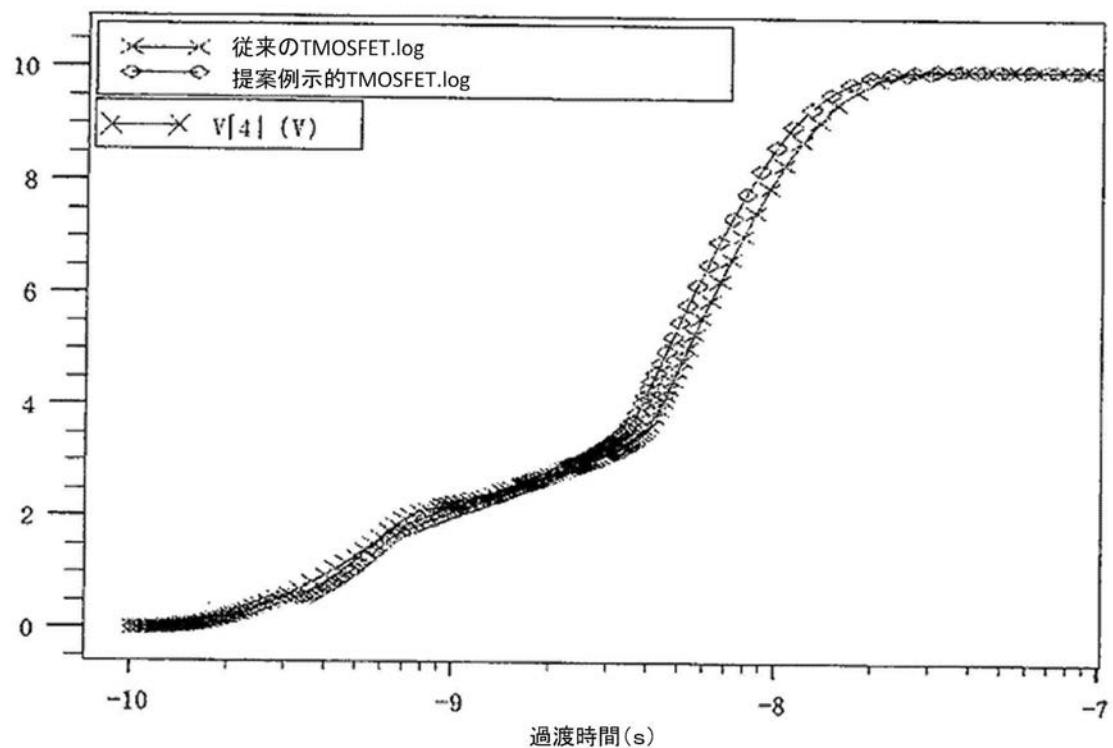

【図7】図7は、図4中に示す例示的T M O S F E T および図5中に示す従来のT M O S F E T それぞれの線A A' および線B B' に沿った電子濃度を示す。これらのT M O S F E T はどちらともON状態であり、 $V_{D S} = 0.1 V$  および  $V_{G S} = 10 V$  は閾電圧よりも高い。

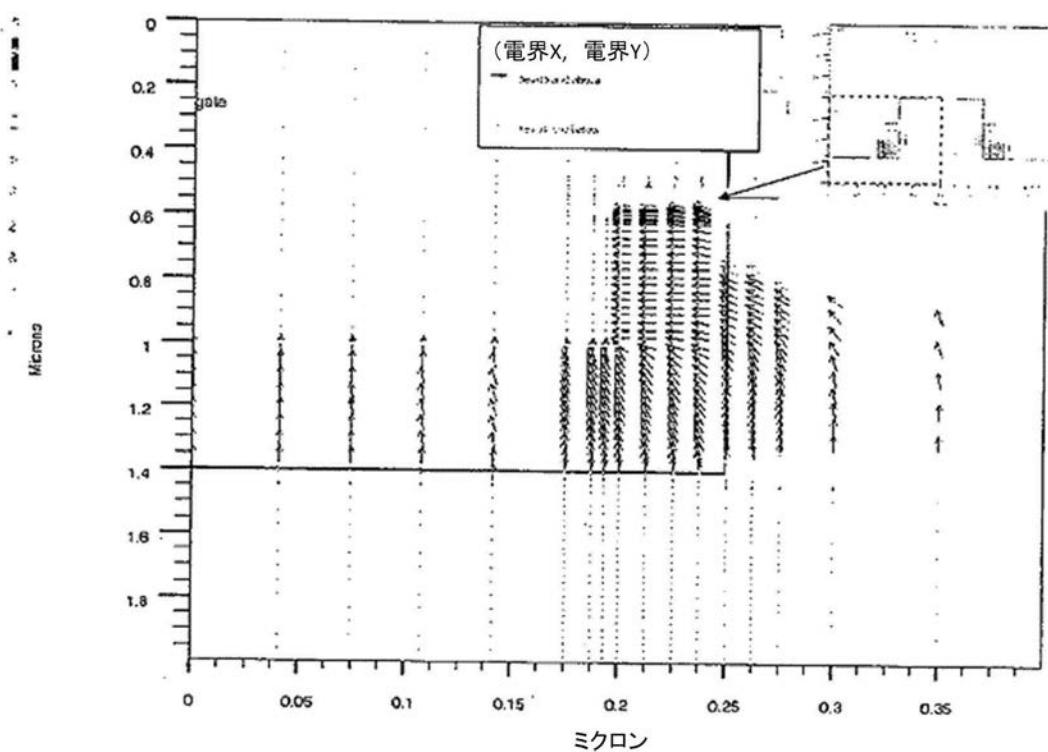

【図8】図8は、前記例示的T M O S F E T の降伏電圧条件下における電界ベクトル合計を示す。ゲート領域からドレイン領域への漏れ磁場により、ドリフト領域電荷の空乏が支援される。

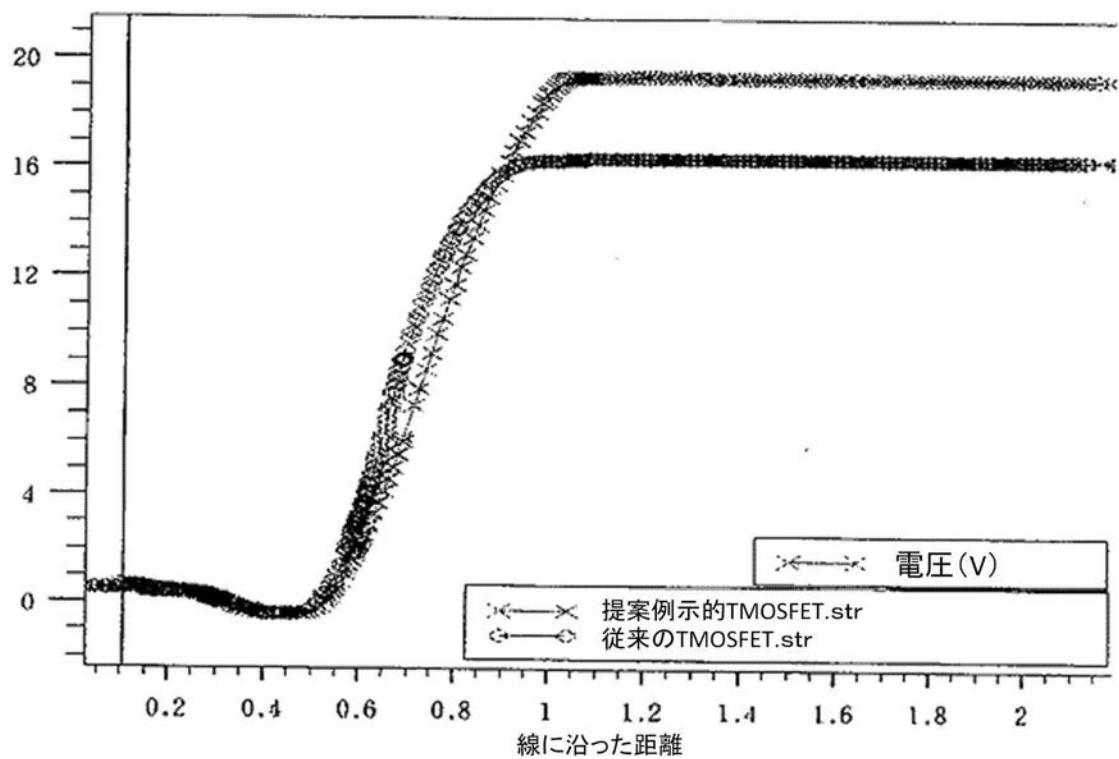

【図9】図9は、例示的T M O S F E T (図4) および従来のT M O S F E T (図5) それぞれの線A A' および線B B' に沿った電圧降下を示す。両者どちらにおいても、阻止電圧が降伏電圧よりも高い。

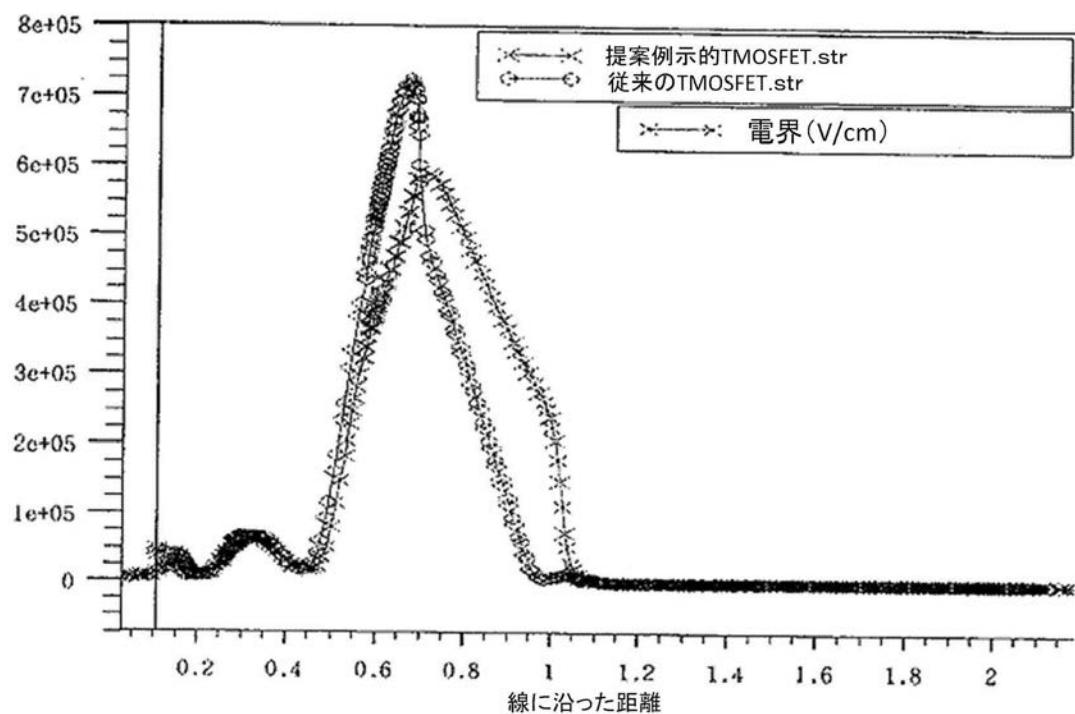

【図10】図10は、例示的T M O S F E T (図4) および従来のT M O S F E T (図5) それぞれの線A A' および線B B' に沿った全電界を示す。両者どちらにおいても、阻止電圧が降伏電圧よりも高い。

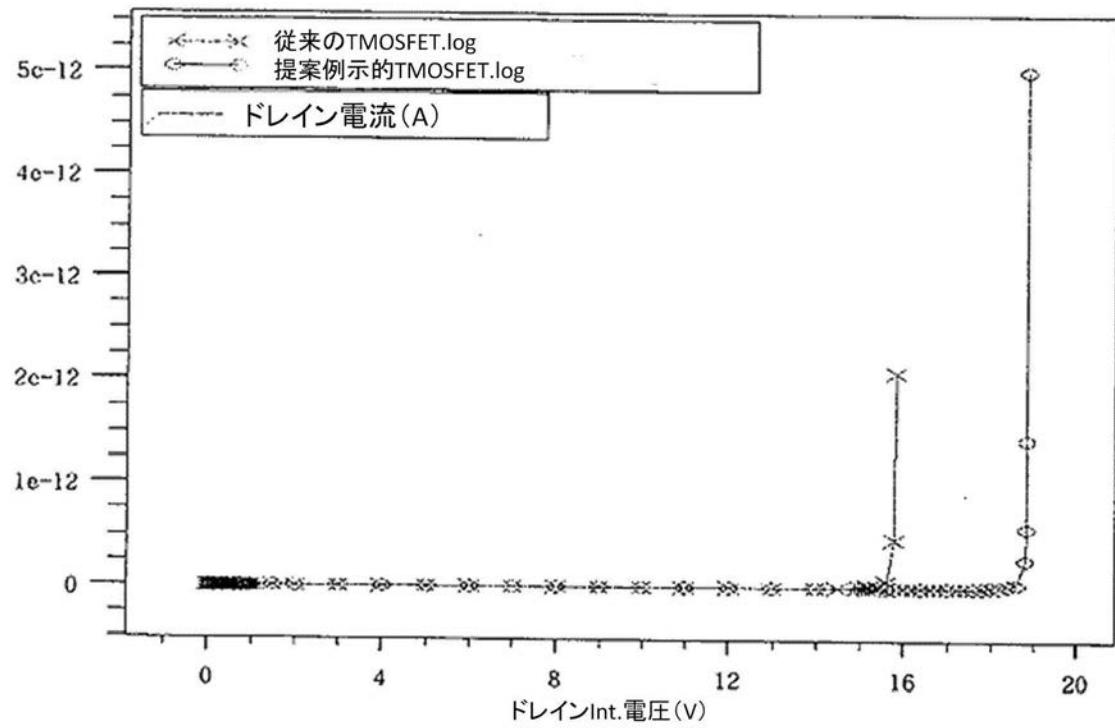

【図11】図11は、例示的T M O S F E T (図4)および従来のT M O S F E T (図5)それぞれについての、オフ状態のドレイン-ソース電圧V D Sおよび電流I D Sの曲線AおよびBを示す。

【図12】図12は、例示的T M O S F E T (図4)および従来のT M O S F E T (図5)それぞれについてのゲート電荷波形を示す。

【図13】図13は、例示的T M O S F E T (図4)および従来技術によるT M O S F E T (図5)についてのドリフト領域ドーピング、降伏電圧および特定のON状態抵抗の比較を示す。

【図14A】～

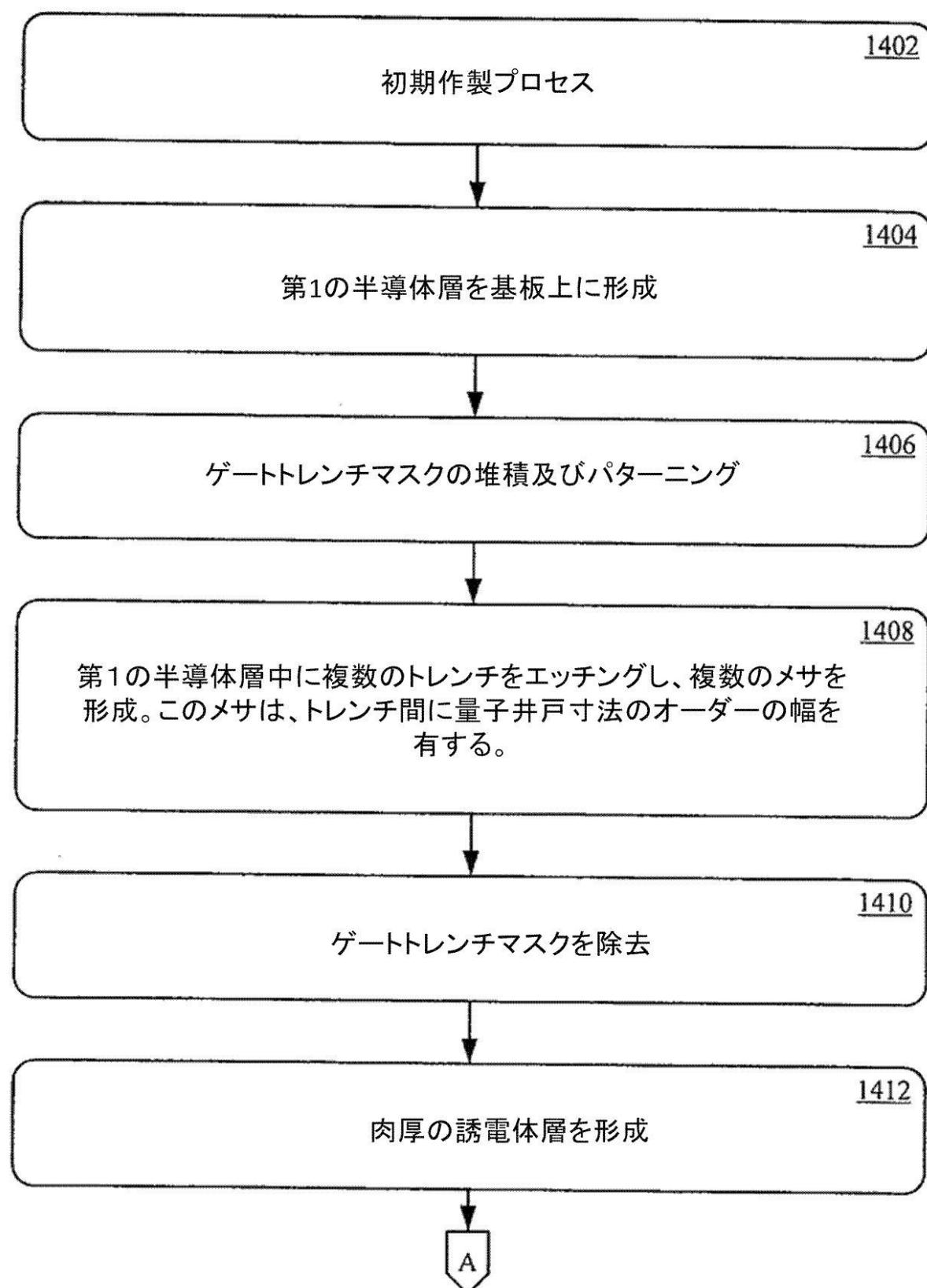

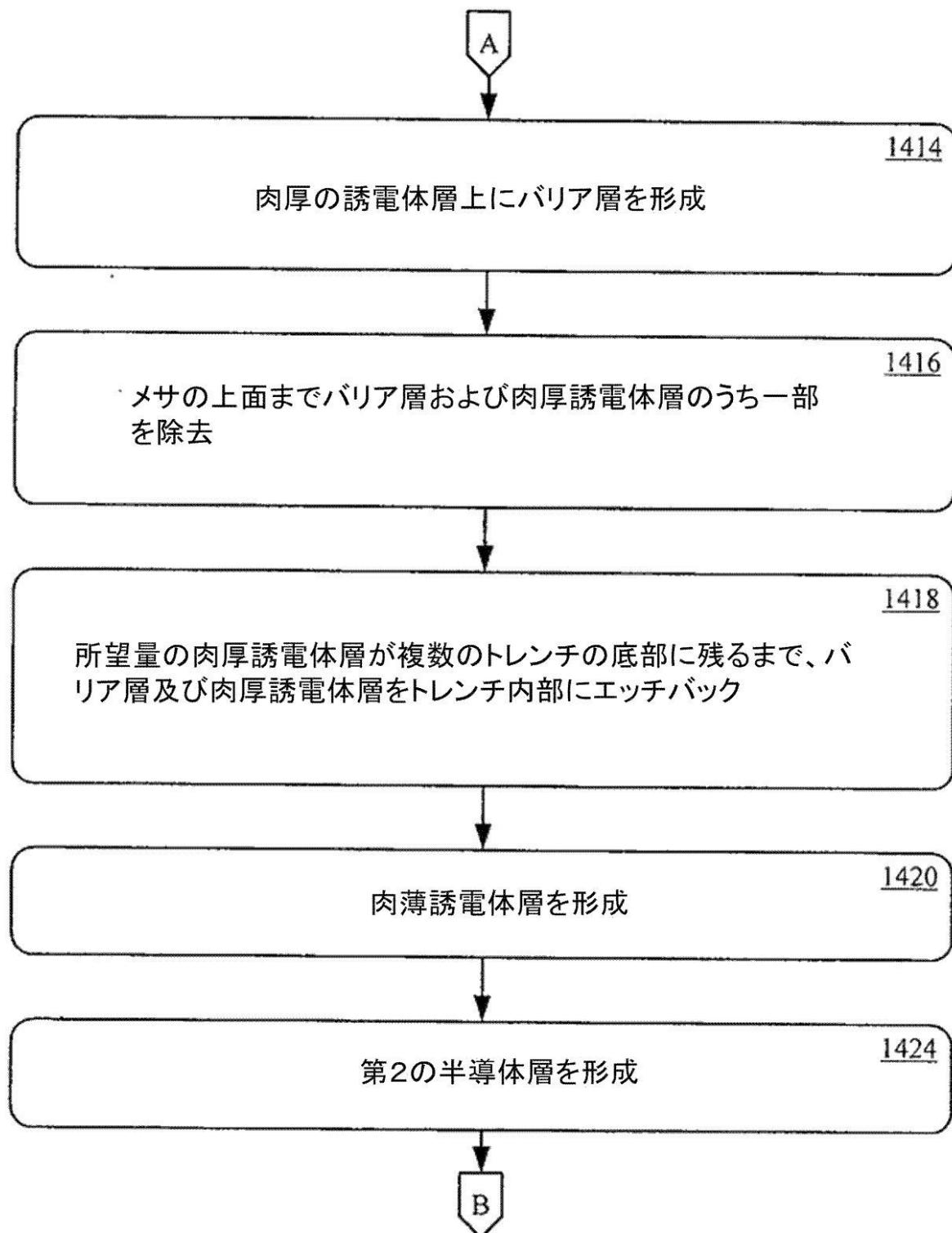

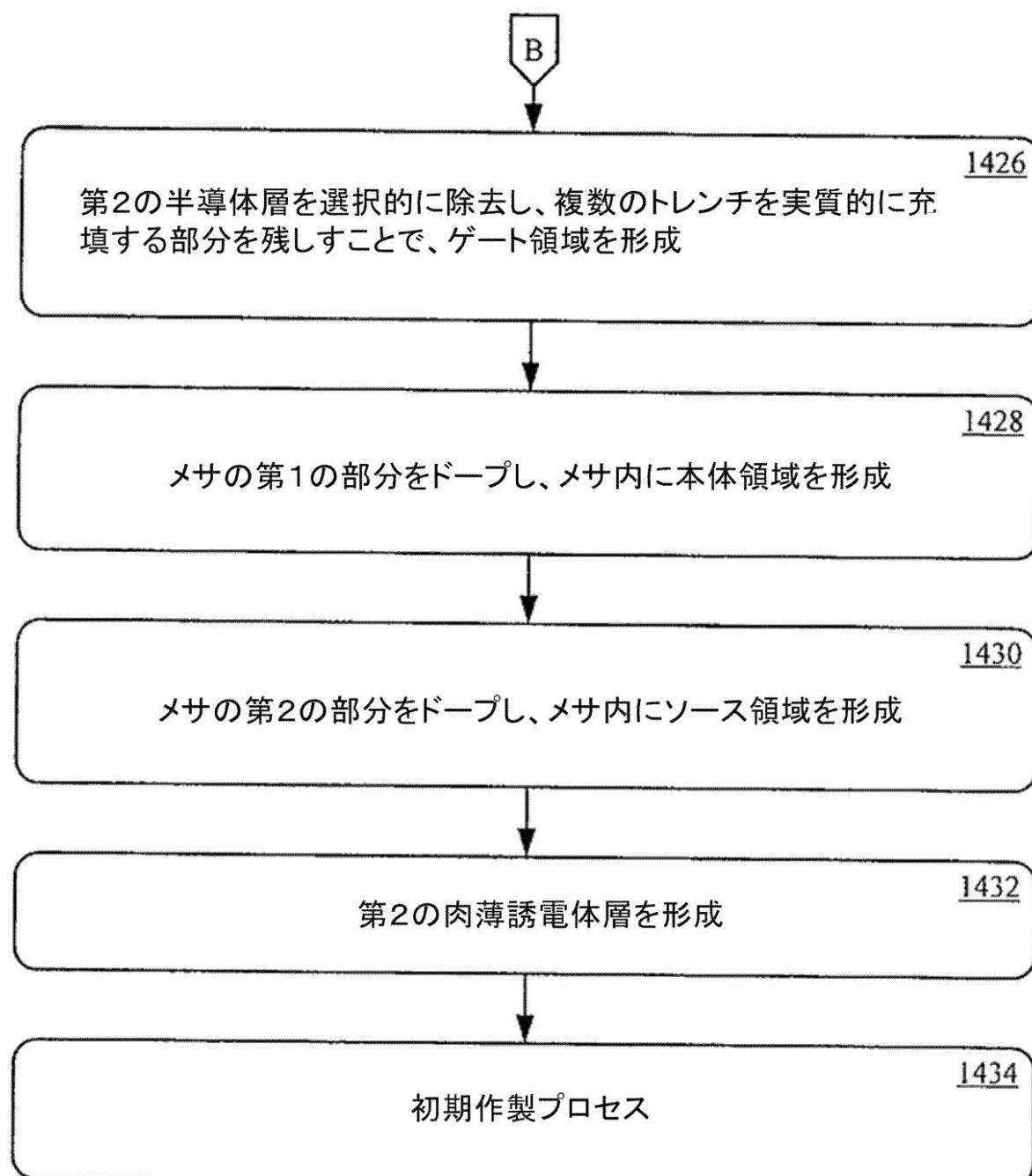

【図14C】図14A～図14Cは、本技術の一実施形態によるT M O S F E Tを作製する方法のフロー図を示す。

【図15A】～

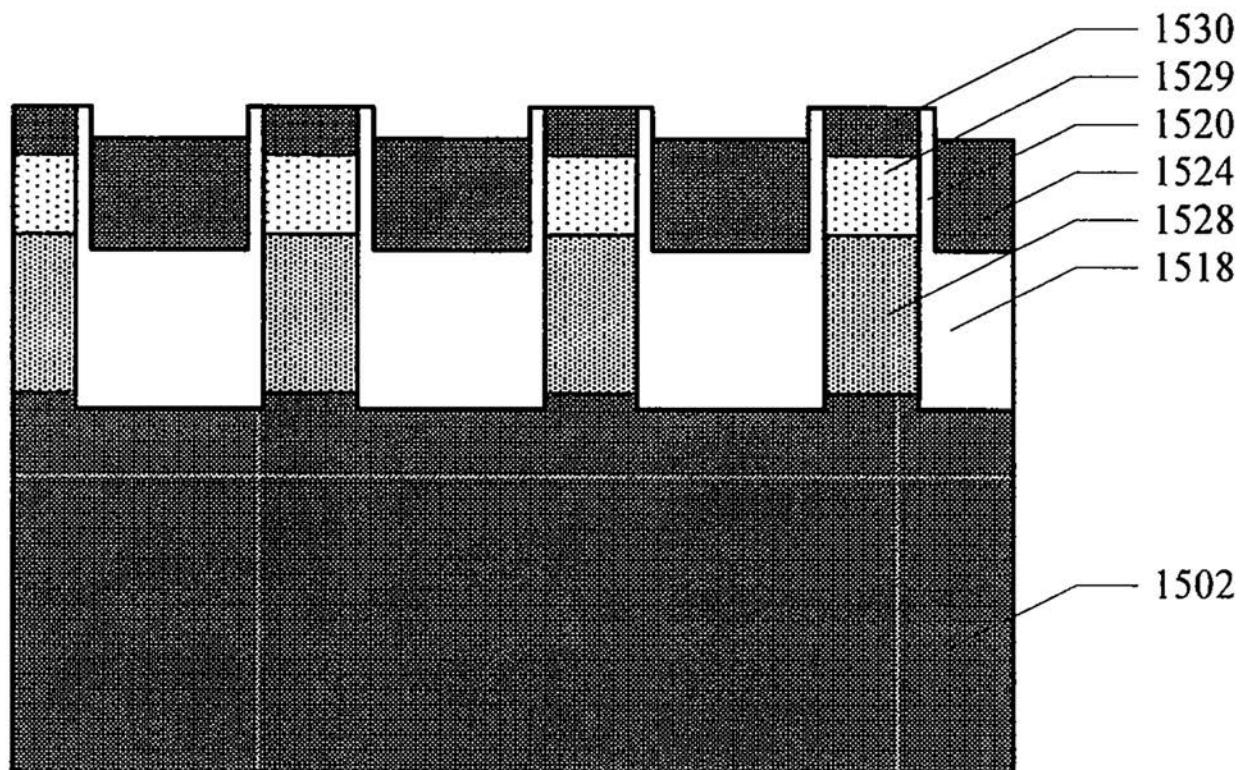

【図15J】図15A～図15Jは、本技術の一実施形態によるT M O S F E Tを作製する方法のブロック図を示す。

【詳細な説明】

【0010】

以下、本技術の実施形態を詳述する。本技術の実施形態の例を添付図面中に示す。本技術についてこれらの実施形態と関連付けて説明していくが、本発明はこれらの実施形態に限定されないことが意図されることが理解される。すなわち、本発明は、添付の特許請求の範囲中に規定されるような本発明の範囲内に含まれ得る代替物、改変物および均等物を含むものとして意図される。さらに、以下の本技術の詳細な説明において、本技術の深い理解のために、多数の特定の詳細について説明する。しかし、これらの特定の詳細が無くても、本技術が実施可能であることが理解される。他の場合において、本技術の観点を必要に曖昧にしないために、周知の方法、手順、構成要素および回路についての詳細な説明はなされていない。

【0011】

図2を参照して、本技術の一実施形態によるトレンチ金属酸化物半導体電界効果トランジスタ(T M O S F E T)200の断面斜視図が図示されている。T M O S F E T 200は、複数のソース領域210と、複数のゲート領域215と、複数のゲート絶縁体領域220と、複数の本体領域225と、複数のドリフト領域230と、ドレイン領域235とを含むがこれらに限定されない。

【0012】

ドリフト領域230は、ドレイン領域235と、本体領域225との間に配置される。本体領域224は、ドリフト領域230と、ソース領域210との間に配置される。ゲート領域215およびゲート絶縁体領域220は、ゲート/ゲート絶縁体構造として形成され得る。ゲート絶縁体領域220は、ゲート領域215を包囲し、ゲート領域215を周囲の領域から電気的に絶縁する。ソース領域210、本体領域220およびドリフト領域230は、ゲート/ゲート絶縁体構造215および220間のメサ内に配置される。本体領域225のうちソース領域210とドリフト領域230との間に配置されかつゲート/ゲート絶縁体構造215および220の近隣の部分は、前記T M O S F E Tのチャネル領域を形成する。

【0013】

1つの実行様態において、ドレイン領域235は、図2に示すように、ゲート/ゲート絶縁体構造215および220間のメサ内まで延び得る。別の実行様態において、ドリフト領域230は、ゲート/ゲート絶縁体構造215および220間のメサを越えて延び得る。

【0014】

ゲート領域215が連結されて、装置200の共通ゲートが形成される。ソース領域210が連結されて、装置200の共通ソースが形成される。本体領域225も、ソース領域210へと連結される。1つの実行様態において、本体領域225は、ソース領域21

0 の長さに沿って周期的にメサの表面まで延び得る。ソース領域 210 および本体領域 225 は、ソース / 本体コンタクト（図示せず）によって共に連結され得る。

#### 【0015】

ゲート / ゲート絶縁体構造 215 および 220 間のメサの幅 240 は、ON 状態の装置（例えば、閾電圧を越えた VGS）内に形成された本体領域 225 とゲート絶縁体領域 220 との間の界面（例えば、Si - SiO<sub>2</sub> 界面）における量子井戸幅の実質的に 1/10 倍 ~ 100 倍の範囲内である。本明細書中、以下、このことを「量子井戸寸法のオーダーである」と呼ぶ。1 つの実行様態において、前記メサの幅 240 は、本体領域 225 とゲート絶縁体領域 220 との間の界面（例えば、Si - SiO<sub>2</sub> 界面）において形成された量子井戸幅の約 2 倍である。1 つの実行様態において、前記メサの幅 240 は、およそ 0.03 ~ 1.0 μm である。ゲート絶縁体領域 220 は、ゲート領域 215 およびドリフト領域 230 間ならびにゲート領域 215 およびドレイン領域 235 間において、肉厚部位を含む。ゲート絶縁体領域 220 はまた、ゲート領域 215 および本体領域 225 間において、肉薄部位を含む。絶縁体領域 220 の肉厚部位の深さは、図 3 に示すようにオフ状態の装置内のゲートトウードレイン電界が本体領域 225 の近隣のドリフト領域 230 内において実質的に横方向となるように、選択される。オフ状態における本体領域 225 の近隣のドリフト領域 230 中の実質的に横方向の電界により、ドリフト領域 230 内の電荷が実質的に空乏化される。1 つの実行様態において、ゲート絶縁体領域 220 の肉厚部位の深さ 245 は、実質的に 0.1 ~ 4.0 μm の範囲内である。

#### 【0016】

ソース領域 210 およびドレイン領域 235 は、高 n ドープ (N+) 半導体（例えば、リンまたはヒ素でドープされたシリコン）であり得る。ドリフト領域 230 は、低 n ドープ (N-) 半導体（例えば、リンまたはヒ素でドープされたシリコン）であり得る。1 つの実行様態において、前記ドリフト領域内に含まれる段階的なドーピングプロファイルは、前記ドレイン領域から前記複数の本体領域へと垂直方向に低減し、かつ / または前記メサの縁部から前記メサの中心へと横方向に変化する。別の実行様態においては、前記ドリフト領域は、実質的に一定のドーピングプロファイルを有する。例示的な実行様態において、前記ドーピングプロファイルは、立方センチメートあたりにおいて実質的に 1.00 E + 14 ~ 8.00 E + 17 の範囲内である。本体領域 225 は、低程度または中程度の p ドープ (P-、P) 半導体（例えば、ホウ素でドープされたシリコン）であり得る。ゲート領域 215 は、高 n ドープ (N+) 半導体（例えば、リンでドープされたポリシリコン）であり得る。ゲート絶縁体領域 220 は、二酸化珪素 (SiO<sub>2</sub>) であり得る。

#### 【0017】

図 4 は、例示的 T M O S F E T の断面図である。T M O S F E T において、メサ幅が 0.3 μm ありかつ厚さが 0.4 μm のゲート絶縁体がゲート領域とドレイン領域との間に設けられている。同様に、図 5 は、従来技術による例示的 T M O S F E T の断面図である。この T M O S F E T において、メサ幅が 0.3 μm ありかつ厚さが 0.05 μm のゲート絶縁体がゲート領域とドレイン領域との間に設けられている。さらに、図 4 中において線 A A' に沿って切断されたドーピングプロファイルと、図 5 中において線 B B' に沿って切断されたドーピングプロファイルとを比較した様子を図 6 中に示す。

#### 【0018】

ゲート領域 215 のソース / 本体領域 210 / 225 に対する電位が装置 200 の閾電圧を上回った場合、伝導チャネルがゲート絶縁体領域 220 の周辺に沿って本体領域 225 内に誘導される。その後、T M S O F E T 200 は、ドレイン領域 235 とソース領域 210 との間で電流を伝導させる。その結果、前記装置は ON 状態となる。

#### 【0019】

前記本体領域のメサ幅が量子井戸寸法のオーダーになると、ON 状態においてシリコン界面が逆転しているため、メサ中の本体領域内において相当の移動度を有する高密度の電子（~ 1 e 18 cm<sup>-3</sup> から 1 e 20 cm<sup>-3</sup>）が溢れる。本体領域内における ON 状態時において二次元電子ガス (2 D E G) の形成が発生し、ゲートドレイン領域の漏れ電界

## (fringing

electric field)に起因して、肉薄メサ構造内のエピタキシャル層内において蓄積層の形成が発生する。前記本体領域はより低濃度でドープすることが可能であるため、ON状態時におけるこの領域内のキャリア移動度に対するイオン化不純物散乱による影響が低下する。ON状態時において、前記肉薄メサ内の本体領域のSi-SiO<sub>2</sub>界面に形成された三角形の量子井戸によって、本体領域が高密度の電子で溢れる。図7に、図4中の切断線AA'に沿ったON状態の電子濃度(VGS=10V)と、図5中の切断線BB'に沿ったON状態の電子濃度(VGS=10V)との比較を示す。

## 【0020】

ゲート領域215の電位が閾電圧を下回った場合、チャネルの誘導が停止する。その結果、ドレイン領域235とソース領域210との間に電界が付加されても、装置200内には大きな電流は全く流れなくなる。そのため、装置200はオフ状態となり、ゲートドレイン電界による支援を伴って本体領域225およびドレイン領域235によって形成された接合により、ソースおよびドレインに亘って付加された電圧が支持される。

## 【0021】

オフ状態においては、ゲートおよびドレイン領域間の電圧の存在に起因して、ゲート領域とドレイン領域との間のゲート絶縁体の肉厚部位に沿って垂直電界が発生する。この垂直電界は、特定の横方向距離「L」内で実質的に低い値へと低下して、ゲート領域の横方向縁部を越える。ゲート縁部からの横方向距離「L」内の電界低下値は、当該領域内に存在する材料によって異なる。所与の装置200について、ゲート領域215、ドリフト領域230およびドレイン領域235の配置および寸法は、メサドリフト領域230内のゲートおよびドレイン間の電圧に起因する垂直電界の値が大きくなるように、選択される。前記メサ領域内のゲートドレイン電界の横方向成分により、当該領域内に存在する電荷の空乏化が支援され、これにより、図8中の例示的TMOSET(図4)の絶縁破壊条件下の全電界ベクトルによって示すように、前記メサ内の有効電荷の電場誘起低下(field induced reduction)が可能となる。このようにして、狭幅のメサ内においてゲートドレイン電界によって誘起された有効電荷低下が発生することにより、所与の降伏電圧に対するドリフト領域内のドーピング濃度が増加する。電界が横方向において有意に低下していない領域内においてメサが量子井戸寸法のオーダーでありかつゲートドレインキャパシタ縁部に十分近接している限り、ゲートドレイン垂直電界が横方向に有効にシリコン内へと移動する。

## 【0022】

ここで図9を参照して、図4中の切断線AA'および図5中の切断線BB'に沿った絶縁破壊条件下の電圧降下を比較する。メサ幅が0.3μmである例示的TMOSETの降伏電圧はおよそ19Vであり、同一のドーピングプロファイルを有する従来のTMOSETの降伏電圧はより低くおよそ16Vである。図10中に、切断線AA'(図4)およびBB'(図5)に沿った装置深さ(ミクロン)の関数として電界を示す。図10から分かるように、前記電圧のうち大部分がドリフト領域全域において支持される。この構造内において、本体領域によって支持される電圧は極めて低いかまたはほとんどゼロである点に留意されたい。図9および図10に示すように、前記電圧のうちほとんどが前記ドリフト領域によって支持され得、ピーク電界のうちより大部分が肉厚酸化物の底部に向かう面にある。図11は、例示的TMOSET(図4)および従来のTMOSET(図5)それぞれについての、オフ状態のドレイン-ソース電圧VDSおよび電流IDS曲線AおよびBを示す。図12は、例示的TMOSET(図4)および従来のTMOSET(図5)それぞれについてのゲート電荷波形を示す。図13において、例示的TMOSET(図4)および従来技術のTMOSET(図5)について、ドリフト領域ドーピング、降伏電圧および特定のON状態抵抗を比較する

## 【0023】

ここで図14A～図14C、を参照して、本技術の一実施形態によるトレンチ金属酸化物半導体電界効果トランジスタ(TMOSET)を作製する方法が図示されている。本

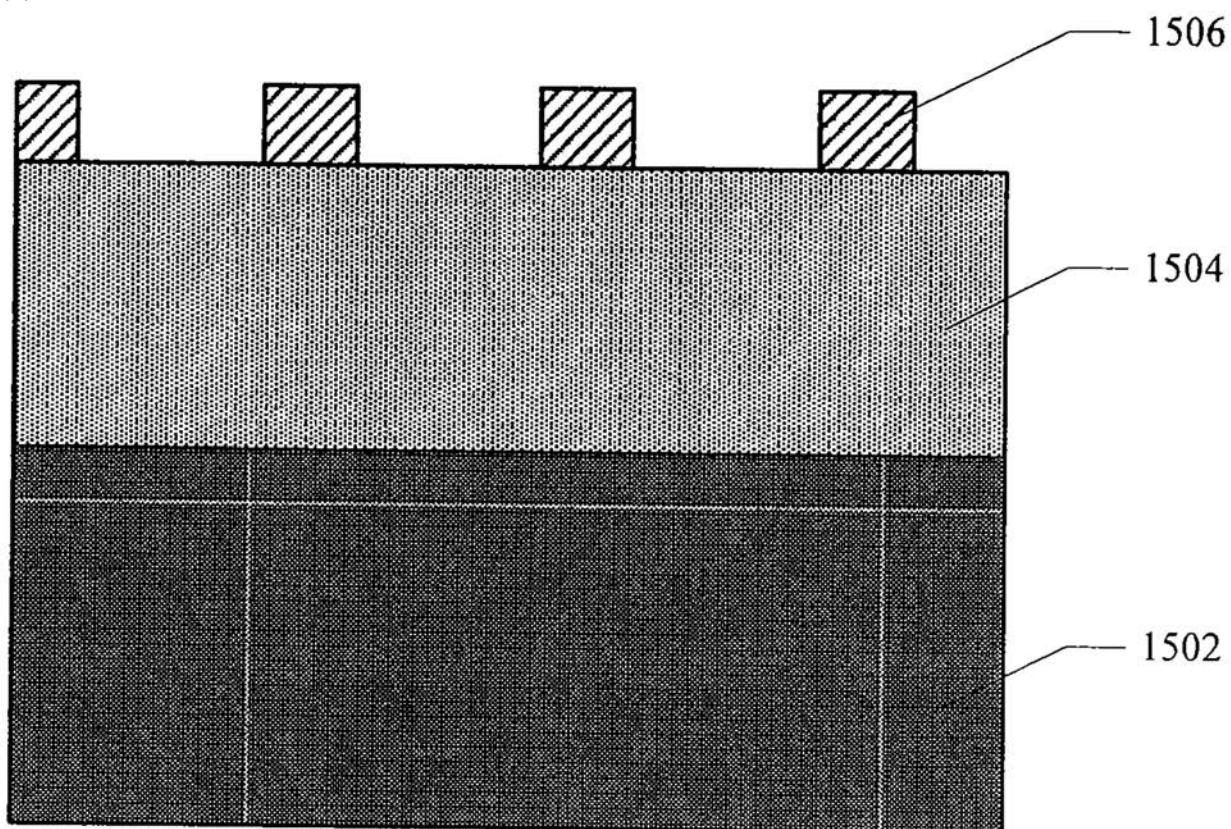

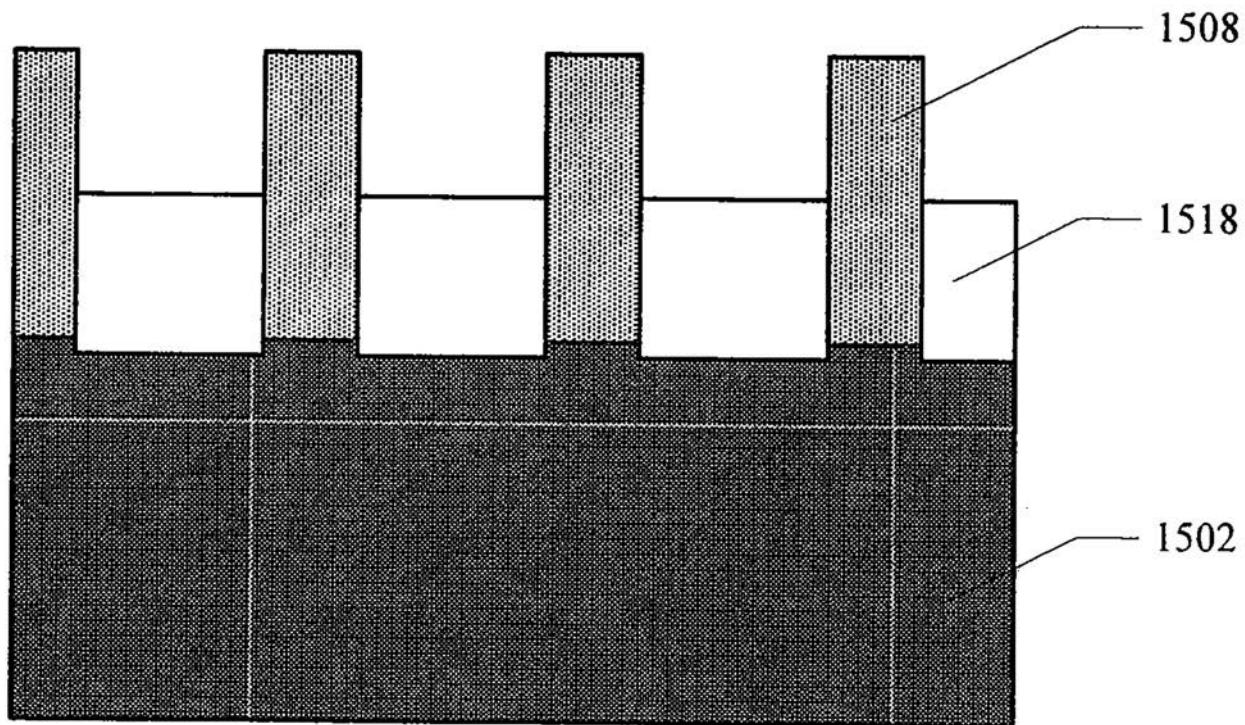

技術の一実施形態によるT M O S F E Tの作製方法を図15A～図15Jに示す。図14Aおよび15Aに示すように、このプロセスは1402において開始し、半導体ウエハ基板1502に対して多様な初期プロセス（例えば、洗浄、堆積、ドーピング、エッチングおよび／または類似のプロセス）が行われる。前記基板は、第1のドーパント型で比較的高ドープされた半導体である。前記半導体基板は、ドレイン領域を形成する。1つの実行様態において、前記ドレイン領域は、リン（N+）で高ドープされたシリコンであり得る。

#### 【0024】

1404において、第1の半導体層1504をウエハ基板1502上に形成する。1つの実行様態において、前記半導体層は、前記基板上にエピタキシャル堆積される。1つの実行様態において、前記エピタキシャル堆積された第1の半導体層は、リン（-）で低ドープされたシリコンを含む。前記エピタキシャル堆積されたシリコンは、所望の不純物（例えば、リン）を反応チャンバ内に導入することにより、ドープされ得る。1つの実行様態において、前記エピタキシャル層は、段階的なドーピングプロファイルを有するように堆積される。この段階的なドーピングプロファイルにおいて、ドーピング濃度は、前記ウエハ基板からエピタキシャル層表面に向かって低下する。

#### 【0025】

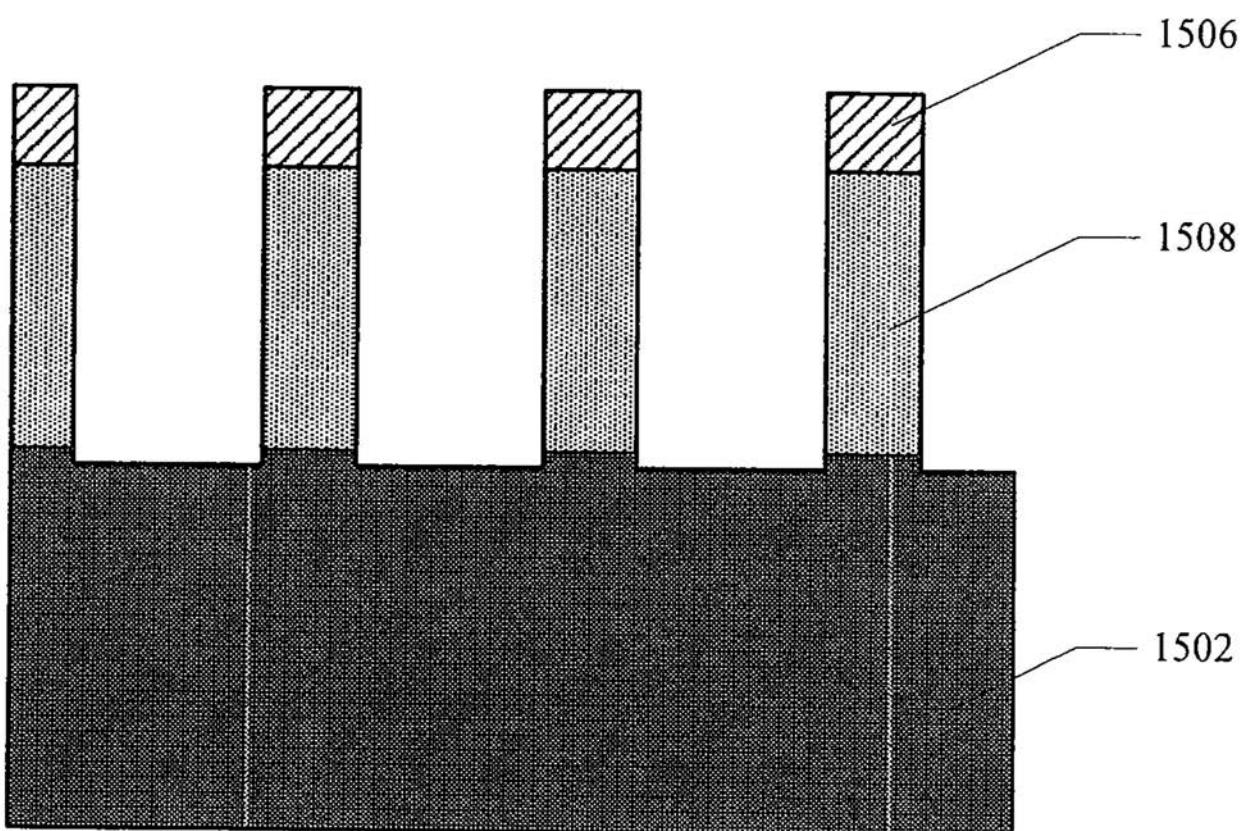

1406において、任意の周知のリソグラフィープロセスによりフォトレジストを堆積させ、パターニング（1506）を行って、ゲートトレンチマスクを形成する。ここで図15Bを参照して、第1の半導体層の露出部位に対して任意の周知の等方性エッチング方法によってエッチングを行う（1408）。1つの実行様態において、イオンエッチャントが、パターニングされたレジスト層によって露出されたバリア層、犠牲酸化物層および第1の半導体層と相互作用する。トレンチ間に配置された複数のメサ1508を有する複数のトレンチが形成され、前記メサの幅は、ゲート絶縁体領域と後続プロセスにおいて形成されたメサとの間の界面における量子井戸寸法のオーダーである。1つの実行様態において、前記メサの幅は、およそ0.03～1.0μmである。1410において、適切なレジストストリッパーまたはレジストアッシングプロセスを用いてゲートトレンチマスクを除去する。

#### 【0026】

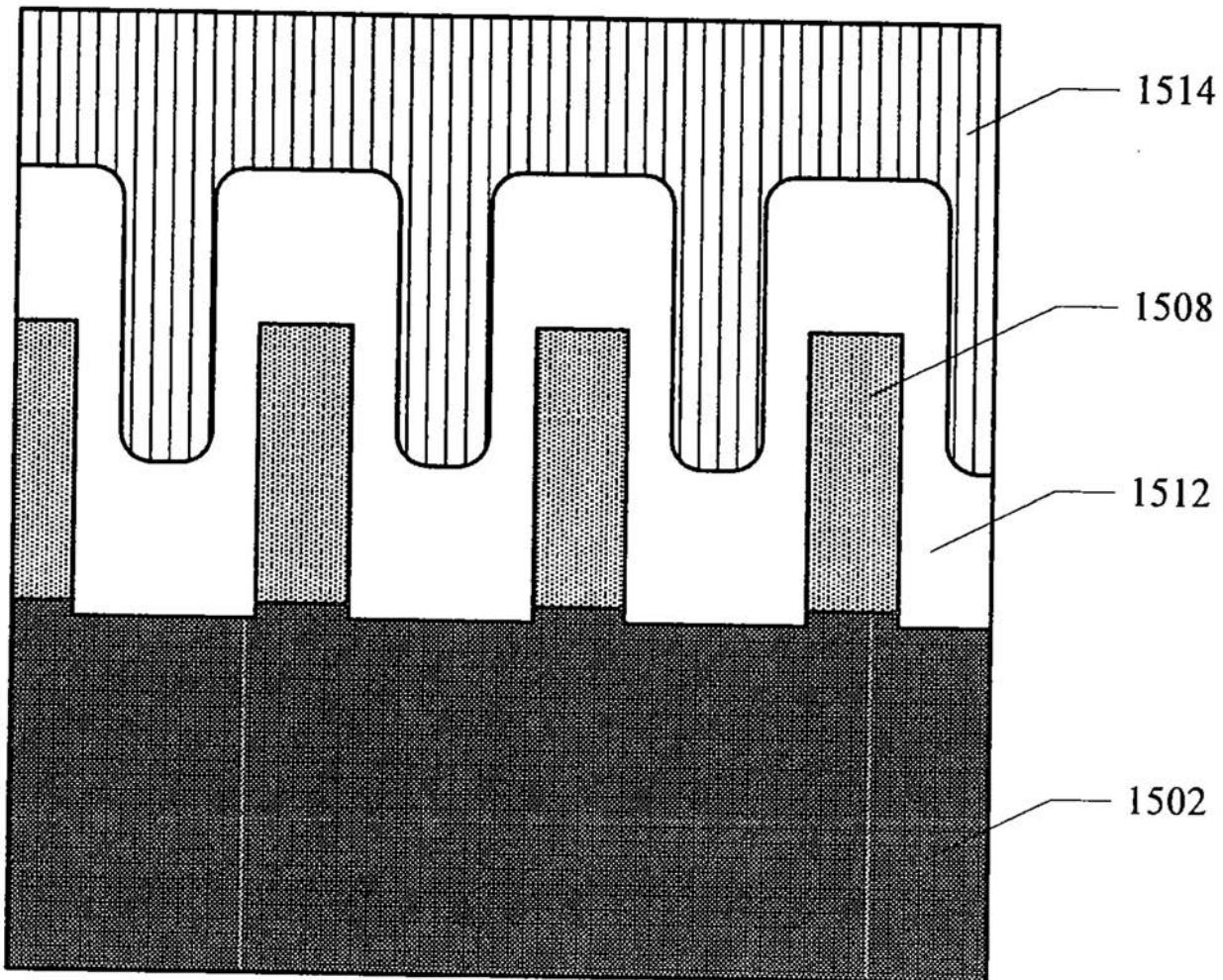

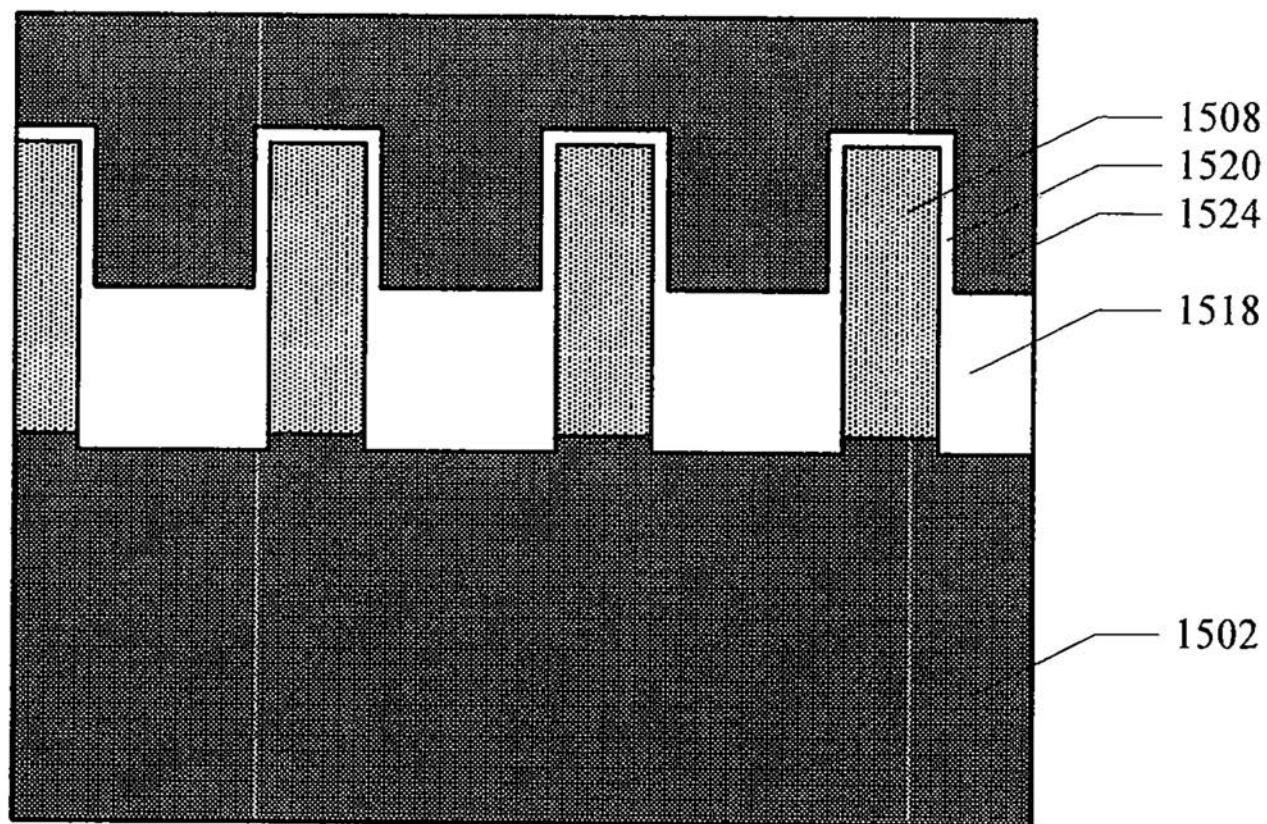

ここで図15Cを参照して、1412において肉厚の誘電体層1512を形成する。1つの実行様態において、任意の周知の方法（例えば、化学気相成長（CVD））により、コンフォーマルな二酸化珪素層を堆積させる。0.1～4.0μmの厚さの誘電体層を堆積させる。

#### 【0027】

ここで図15Cを参照して、バリア層1514を前記肉厚の誘電体層上に形成し、1414において前記トレンチを充填する。ここで図15Dを参照して、1416において化学機械研磨（CMP）または任意の公知の平坦化方法を用いて平坦化を行うことにより、メサ1508の上面までバリア層1514および肉厚誘電体層1512のうち一部を除去する。ここで15Eを参照して、1418において、所望量の肉厚誘電体層が前記トレンチの底部に残るまで、前記肉厚誘電体層の残り部分を前記トレンチ内にエッチバックする。一実施形態において、約0.14～4.0μmが前記トレンチの底部に残るまで、前記肉厚誘電体層を前記トレンチ内にエッチバックする。

#### 【0028】

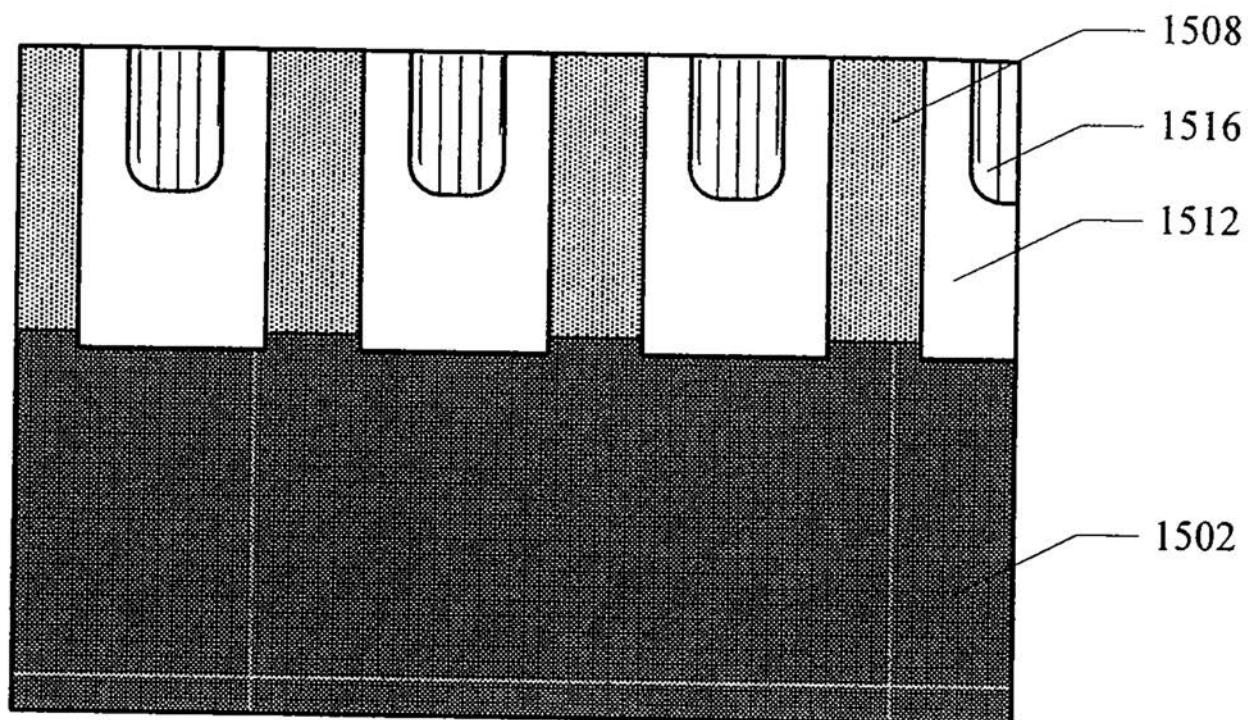

ここで図15Fを参照して、1420において第1の肉薄誘電体層1520を前記メサ上に形成する。1つの実行様態において、第1の半導体層のメサ表面を酸化させて二酸化珪素層を形成することにより、前記肉薄誘電体層を形成する。

#### 【0029】

1424において、第2の半導体層1524を形成する。1つの実行様態において、前記トレンチを充填ながらウエハ上にポリシリコン層をコンフォーマルに形成する。この形成は、シランの分解（S1H4）のような方法により行われる。1つの実行様態において

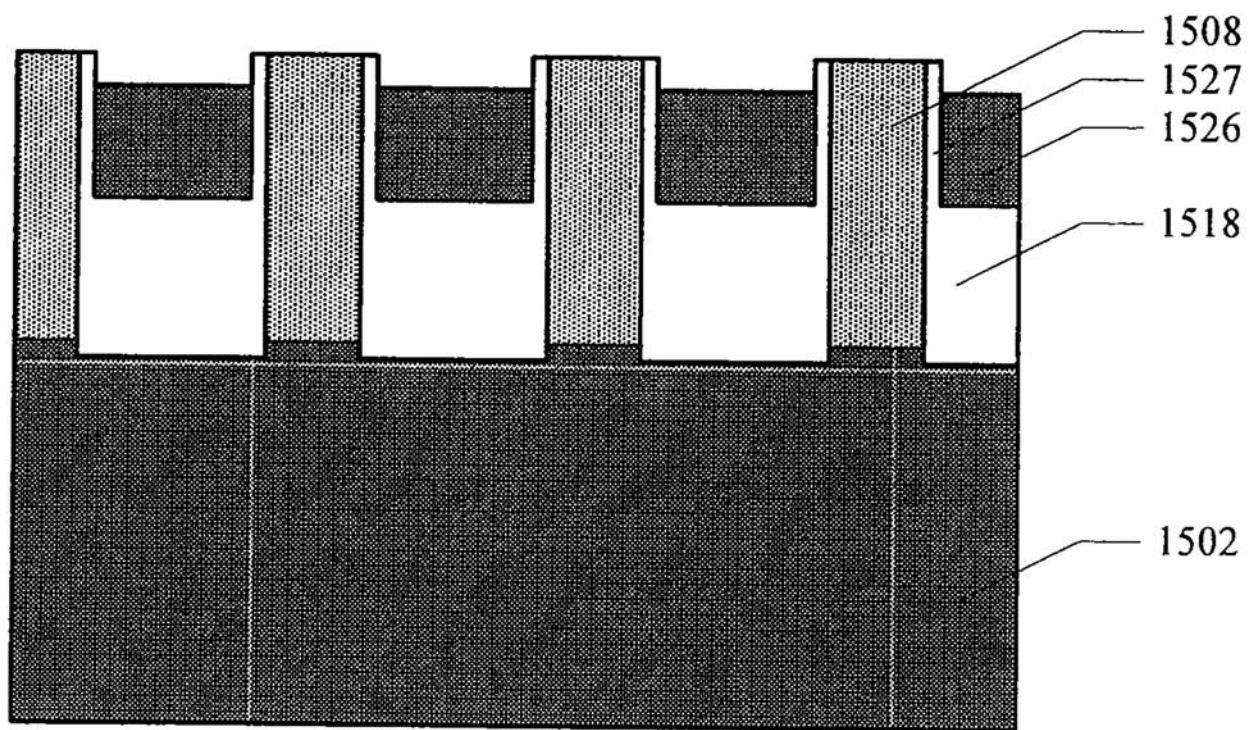

、前記ポリシリコンは、n型不純物（例えば、リンまたはヒ素）によってドープされる。1つの実行様態において、前記ポリシリコンのドープは、前記堆積プロセス時において不純物を導入することにより、行われる。ここで図14Cおよび図15Gを参照して、1426において、エッチバックプロセスを行って、ウエハ表面上の余分な第2の半導体層および肉薄誘電体層を除去する。このようにしてウエハ表面上の余分な第2の半導体層および肉薄誘電体層を除去することにより、ゲート領域1526と、ゲート領域およびメサ間のゲート絶縁体領域の肉薄部位1527とが形成される。1つの実行様態において、余分な第2の半導体および肉薄誘電体層は、ウェットエッチプロセスなどによって選択的に除去される。1つの実行様態において、メサ1508の上部上の肉薄誘電体層の部分を第1のエッチングプロセス時においてハードマスクとして用いることで、第2の半導体層をトレンチ内に部分的にエッチバックすることが可能となる。その後、第2のエッチングプロセスにより、メサ上部上の肉薄誘電体層を除去することができる。

#### 【0030】

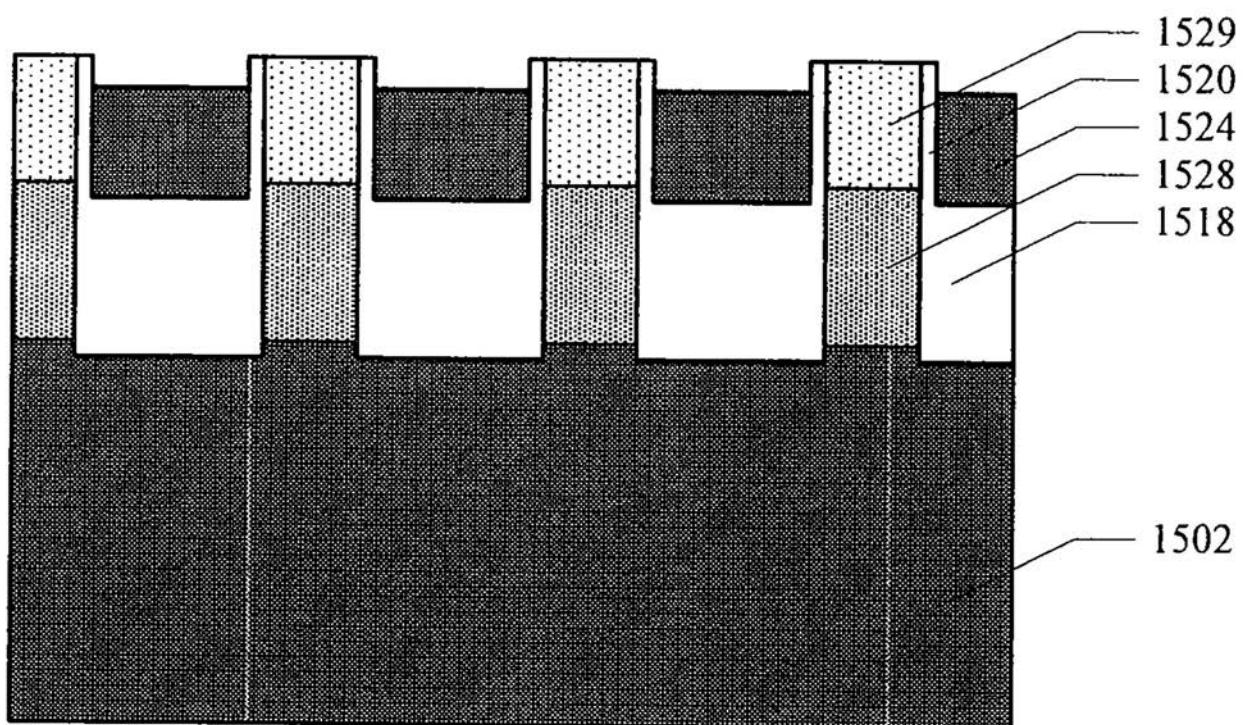

ここで図15Hを参照して、1428において、メサ1508およびゲート領域1526の第1の部分を第2のドーパント型によって比較的中程度または低程度のドーピング濃度で第1の深さまでドープする。エピタキシャル堆積半導体層のうち露出部分をドープして、複数のメサ内に本体領域1529をゲート領域と実質的に同一の深さで形成する。1つの実行様態において、前記ドーピングプロセスにより、p型不純物（例えば、ホウ素）を前記メサ中に注入する。高温熱サイクルを用いて、本体領域内におけるドーピングを促進することができる。その結果、エピタキシャル堆積半導体層1528の下部により、低程度ドープドリフト領域がドレイン領域1502と本体領域1529との間に形成される。ゲート領域1524のドーピングは、第1のドーパント型により実質的に中程度～高程度にドープされた状態で保持される点にも留意されたい。

#### 【0031】

ここで図15Iを参照して、1430において、メサ1508およびゲート領域の第2の部分を第2の深さまで比較的高ドーピング濃度で第1のドーパント型によりドープして、ソース領域1530を形成する。第2のドーピング深さは、第1のドーピング深さよりも浅い。1つの実行様態において、前記ドーピングプロセスは、n型不純物（例えば、リンまたはヒ素）を複数のメサ中に高濃度注入する工程を含む。高温熱サイクルを用いて、ソース領域ドーピングにおける活性化および／または促進が可能となる。ここで図15Jを参照して、1432において第2の肉薄誘電体層1532を形成する。1つの実行様態において、前記肉薄誘電体層は、メサおよびゲート領域の表面を酸化させることにより行われ、これにより二酸化珪素層が形成される。

#### 【0032】

1436において、他の多様なプロセスと共に作製が継続する。前記多様なプロセスの典型例を挙げると、エッチング、堆積(deposition)、ドーピング、洗浄、アニーリング、パッシベーション、劈開(cleaving)および／または類似のプロセスがある。例えば、さらなるプロセスにより、ソース／本体コンタクト開口部、ソース／本体コンタクト、ゲートコンタクト開口部、ゲートコンタクト、ドレインコンタクト、パッシベーション層、ビア、配線、終端構造、周辺構造および／または類似のものが形成される。

#### 【0033】

本技術の実施形態は、漏れゲートドレイン電界(fringing gate-drain electric field)を有利に用いることにより、低オン状態抵抗を有利に達成する。メサ内のドリフト領域のドーピング濃度を有利に増加させることができ、p-n接合降伏電圧の低下も、平面p-n接合理論によって予測される場合よりも低くなる。メサ幅により、前記メサ内のp-n接合の降伏電圧と前記メサ内のドーピングとの間の関係が有利に制御される。加えて、オフ状態におけるゲートとドレインとの間の漏れ磁場によりメサ内のドリフト領域電荷の空乏化が支援され、これにより、所与の降伏電圧におけるドリフト領域のドーピングをより高濃度とすることができます。さらに、ゲートとドレインとの間のゲート絶縁体の厚さにより、ドリフト領域ドーピング濃度が上昇した場合でも

、さらなるゲート電荷上昇無く、実質的に一定の降伏電圧が得られる。その結果、低オン抵抗ゲート電荷生成が可能となる。

#### 【0034】

特定の本発明の実施形態についての上記記載は、例示および説明の目的のためのものであり、網羅的なものを意図しておらずまた本発明を開示の形態そのものに限定することも意図していない。よって、上記教示内容を鑑みれば、多くの改変例および変更例が可能である。実施形態は、本発明の原理およびその実際的用途を説明するために選択および記載されたものであり、これにより、当業者が本発明および多様な実施形態を最も利用することが可能となり、特定の用途に適した多様な改変例が企図される。本発明の範囲は、本明細書に添付される特許請求の範囲およびその均等物によって規定されることが意図される。本明細書中記載される全ての要素、部品および工程が、好適に含まれる。当業者であれば理解するように、これらの要素、部品および工程のうち任意のものを他の要素、部品および工程と置換することも可能であるし、あるいは、これらの要素、部品および工程を削除することも可能であることが理解される。

#### 【コンセプト】

##### 【0035】

本文書は、少なくとも以下のコンセプトを開示する。

コンセプト1. トレンチ金属酸化物半導体電界効果トランジスタ（T M O S F E T）であって、

ドレイン領域と、

前記ドレイン領域の上方に配置された複数のゲート領域と、

前記複数のゲート領域の間および前記ドレイン領域の上方においてメサ内に配置された複数のドリフト領域と、

前記メサ内において前記ドリフト領域の上方において前記ゲート領域に隣接して配置された複数の本体領域と、

前記メサ内において前記本体領域の上方に配置された複数のソース領域と、

前記ゲート領域と、前記ソース領域、前記本体領域、前記ドリフト領域および前記ドレイン領域との間に配置された複数のゲート絶縁体領域と、

を含み、

前記メサの幅は、およそ0.03～1.0ミクロン（ $\mu$ m）であり、

前記ゲート領域と前記ドレイン領域との間の前記ゲート絶縁体領域の厚さは、およそ0.1～4.0ミクロン（ $\mu$ m）である、

トレンチ金属酸化物半導体電界効果トランジスタ（T M O S F E T）。

コンセプト2. 前記ドリフト領域は、段階的なドーピングプロファイルを含み、前記段階的なドーピングプロファイルは、前記ドレイン領域から前記複数の本体領域に向かって垂直方向に低減するかまたは前記メサの縁部から前記メサの中心へ向かって横方向に変化する、コンセプト1のトレンチ金属酸化物半導体電界効果トランジスタ（T M O S F E T）。

コンセプト3. 前記ドレイン領域を用いて前記メサ内にp-n接合が形成される、コンセプト1のトレンチ金属酸化物半導体電界効果トランジスタ（T M O S F E T）。

コンセプト4. 前記ソース領域および前記本体領域は実質的に同一の電位において連結される、コンセプト1のトレンチ金属酸化物半導体電界効果トランジスタ（T M O S F E T）。

コンセプト5. 平面p-n接合理論によって予測される場合よりも低いp-n接合降伏電圧の低下により、前記ドリフト領域のドーピングを増加させることができる、コンセプト1のトレンチ金属酸化物半導体電界効果トランジスタ(TMOSFET)。

コンセプト6. 前記メサ内のp-n接合の降伏電圧と、前記メサ内のドーピングとの間の関係は、前記メサの幅によって制御される、コンセプト1のトレンチ金属酸化物半導体電界効果トランジスタ(TMOSFET)。

コンセプト7. オフ状態における前記ゲート領域と前記ドレイン領域との間の漏れ磁場により、前記メサ内のドリフト領域電荷の空乏が支援され、これにより、実質的に一定な降伏電圧のための前記ドリフト領域内のより高いドーピングが得られる、コンセプト1のトレンチ金属酸化物半導体電界効果トランジスタ(TMOSFET)。

コンセプト8. 前記ゲート領域と前記ドレイン領域との間の前記ゲート絶縁体領域の厚さにより、ドリフト領域ドーピング濃度が上昇した場合でも、さらなるゲート電荷上昇無く、実質的に一定の降伏電圧が得られ、その結果、低オン抵抗ゲート電荷生成が可能となる、コンセプト1のトレンチ金属酸化物半導体電界効果トランジスタ(TMOSFET)。

コンセプト9.

前記ドレイン領域は高nドープ半導体を含み、

前記ゲート領域はnドープ半導体を含み、

前記ドリフト領域は低nドープ半導体を含み、

前記本体領域は、中程度のpドープ半導体を含み、

前記複数のソース領域は、高nドープ半導体を含む、

コンセプト1のトレンチ金属酸化物半導体電界効果トランジスタ(TMOSFET)。

コンセプト10.

前記ドレイン領域は、高nドープ半導体を含み、

前記ゲート領域は、n-ドープ半導体を含み、

前記ドリフト領域は、前記本体領域と前記ドレイン領域との間において、低程度～中程度のnドープ半導体を含み、

前記本体領域は、中程度のpドープ半導体を含み、

前記複数のソース領域は、高nドープ半導体を含む、

コンセプト1のトレンチ金属酸化物半導体電界効果トランジスタ(TMOSFET)。

コンセプト11. 前記ゲート絶縁体領域は酸化物を含む、コンセプト1のトレンチ金属酸化物半導体電界効果トランジスタ(TMOSFET)。

コンセプト12. トレンチ金属酸化物半導体電界効果トランジスタ(TMOSFET)であって、

ドレイン領域と、

複数のメサであって、前記複数のメサはそれぞれ、ドリフト領域および本体領域を含み、複数のゲート領域間に配置され、前記メサの幅は、前記ゲート絶縁体領域と前記本体領域との間の界面における量子井戸寸法のオーダーである、複数のメサと、

前記ゲート領域と、前記本体領域、前記ドリフト領域、および前記ドレイン領域との間に配置された複数のゲート絶縁体領域であって、前記ゲート領域と前記ドレイン領域との間の前記ゲート絶縁体領域の厚さに起因して、オフ状態においてゲートトウードレイン電界が発生し、前記ゲートトウードレイン電界は、前記ドリフト領域内において実質的に横方向である、複数のゲート絶縁体領域と、

を含む、トレンチ金属酸化物半導体電界効果トランジスタ(TMOSFET)。

コンセプト 1 3 . 前記ゲート絶縁体領域は酸化物を含む、コンセプト 1 2 のトレンチ金属酸化物半導体電界効果トランジスタ ( T M O S F E T ) 。

コンセプト 1 4 .

前記ドレイン領域は、リンまたはヒ素で高ドープされたシリコンを含み、

前記ドリフト領域は、リンまたはヒ素で低程度または中程度にドープされたシリコンを含み、

前記本体領域は、ホウ素で低程度または中程度にドープされたシリコンを含む、コンセプト 1 2 のトレンチ金属酸化物半導体電界効果トランジスタ ( T M O S F E T ) 。

コンセプト 1 5 .

前記ドリフト領域は、前記ドレイン領域から前記複数の本体領域に向かって低減する段階的なドーピングプロファイルを含む、コンセプト 1 3 のトレンチ金属酸化物半導体電界効果トランジスタ ( T M O S F E T ) 。

コンセプト 1 6 . 前記ドリフト領域のドーピング濃度は、立方センチメートあたりおよそ  $5 \cdot 0 \cdot 0 \cdot E + 1 \cdot 4 \sim 8 \cdot 0 \cdot 0 \cdot E + 1 \cdot 7$  である、コンセプト 1 4 のトレンチ金属酸化物半導体電界効果トランジスタ ( T M O S F E T ) 。

コンセプト 1 7 . 前記メサの幅は、およそ  $0 \cdot 0 \cdot 3 \sim 2 \cdot 0$  ミクロン (  $\mu m$  ) である、コンセプト 1 6 のトレンチ金属酸化物半導体電界効果トランジスタ ( T M O S F E T ) 。

コンセプト 1 8 . 前記ゲート領域と前記ドレイン領域との間の前記ゲート絶縁体領域の厚さは、およそ  $0 \cdot 1 \sim 4 \cdot 0$  ミクロン (  $\mu m$  ) である、コンセプト 1 7 のトレンチ金属酸化物半導体電界効果トランジスタ ( T M O S F E T ) 。

コンセプト 1 9 . 降伏電圧はおよそ  $1 \cdot 5 V \sim 5 \cdot 5 V$  である、コンセプト 1 8 のトレンチ金属酸化物半導体電界効果トランジスタ ( T M O S F E T ) 。

コンセプト 2 0 . ON 状態抵抗は、平方ミリメートルあたりおよそ  $2 \sim 9$  ミリオーム (  $m \cdot \Omega \cdot mm^2$  ) である、コンセプト 1 8 のトレンチ金属酸化物半導体電界効果トランジスタ ( T M O S F E T ) 。

【手続補正 3】

【補正対象書類名】図面

【補正対象項目名】全図

【補正方法】変更

【補正の内容】

【図1】

【図2】

【図3】

【図4】

【図5】

【図 6】

【図 7】

【図8】

【図9】

【図 1 0】

【図 1 1】

【図12】

【図13】

| 装置                      | ドリフト領域<br>ドーピング,/cm <sup>3</sup> | BV, V | R <sub>sp</sub> (V <sub>gs</sub> =10V),<br>mohm.mm <sup>2</sup> | Q <sub>g,sp</sub><br>(V <sub>gs</sub> =10V),<br>nC/cm <sup>2</sup> | R <sub>on,Qg</sub> ,<br>mohm.nc |

|-------------------------|----------------------------------|-------|-----------------------------------------------------------------|--------------------------------------------------------------------|---------------------------------|

| 図5の従来の<br>TMOSFET       | 1.3E+17                          | 15.8  | 3.4                                                             | 1522                                                               | 51.74                           |

| 図4の提案<br>例示的<br>TMOSFET | 1.3E+17                          | 19.2  | 3.54                                                            | 1177                                                               | 41.66                           |

【図 14 A】

【図 14 B】

【図 14C】

【図 15 A】

【図 15 B】

【図 15 C】

【図 15 D】

【図 15 E】

【図 15 F】

【図 15 G】

【図 15 H】

【図 15 I】

【図 15 J】