(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2018년06월27일

(11) 등록번호 10-1871866

(24) 등록일자 2018년06월21일

- (51) 국제특허분류(Int. Cl.)

*H01L 23/12* (2006.01) *H01L 23/48* (2006.01)

- (21) 출원번호 10-2013-7017239

- (22) 출원일자(국제) 2011년12월02일

심사청구일자 2016년11월25일

- (85) 번역문제출일자 2013년07월01일

- (65) 공개번호 10-2013-0122959

- (43) 공개일자 2013년11월11일

- (86) 국제출원번호 PCT/US2011/063025

- (87) 국제공개번호 WO 2012/075371

국제공개일자 2012년06월07일

- (30) 우선권주장

12/958,866 2010년12월02일 미국(US)

- (56) 선행기술조사문현

KR1020060105797 A\*

KR1020010067231 A\*

US20100230795 A1\*

US20100117242 A1\*

\*는 심사관에 의하여 인용된 문현

전체 청구항 수 : 총 26 항

심사관 : 김진우

(54) 발명의 명칭 액티브 칩을 연결하는 인터포저를 갖는 적층형 마이크로 전자 어셈블리

**(57) 요 약**

마이크로 전자 어셈블리(100)는, 제1 및 제2 마이크로 전자 요소(102, 112)의 전면(104, 114)에 인접한 액티브 반도체 장치를 각각 구현하는 제1 및 제2 마이크로 전자 요소와, 10ppm/°C 미만의 CTE를 갖는 재료의 인퍼포저(120)를 포함할 수 있다. 각각의 마이크로 전자 요소(102, 112)는 각각의 전면(104, 114)에서 노출되는 도전성

(뒷면에 계속)

**대 표 도** - 도1

패드(106, 116)를 가질 수 있다. 인터포저(120)는, 인터포저의 개구부(222) 내에서 연장하고 인터포저의 제1 표면 및 제2 표면(227, 229)에서 노출되는 제2 도전성 요소(118)를 가질 수 있다. 제1 및 제2 표면(227, 229)은 각각의 제1 및 제2 마이크로 전자 요소(102, 112)의 전면(104, 114)을 향할 수 있다. 각각의 마이크로 전자 요소(102, 112)는 각각의 마이크로 전자 요소의 후면(237, 239)으로부터 전면(104, 114) 쪽으로 연장하는 개구부(206, 216) 내에 연장하는 제1 도전성 요소(236, 238)를 포함할 수 있다. 제1 도전성 요소(236, 238) 중의 하나 이상이 각각의 제1 또는 제2 마이크로 전자 요소(102, 112)의 도전성 패드(204, 214)를 통해 연장할 수 있다.

(72) 발명자

모하메드 일야스

미국 95134 캘리포니아주 샌 호세 오처드 파크웨이

3025 테세라, 인코포레이티드

사발리아 피유시

미국 95134 캘리포니아주 샌 호세 오처드 파크웨이

3025 테세라, 인코포레이티드

미셸 크레이그

미국 95134 캘리포니아주 샌 호세 오처드 파크웨이

3025 테세라, 인코포레이티드

## 명세서

### 청구범위

#### 청구항 1

마이크로 전자 어셈블리에 있어서,

제1 마이크로 전자 요소 및 제2 마이크로 전자 요소로서, 상기 제1 마이크로 전자 요소 및 상기 제2 마이크로 전자 요소의 각각이 상기 제1 마이크로 전자 요소 및 상기 제2 마이크로 전자 요소의 전면에 인접한 액티브 반도체 장치를 구현하고, 상기 제1 마이크로 전자 요소 및 상기 제2 마이크로 전자 요소의 각각이 상기 전면에서 떨어져 있는 후면을 가지며, 상기 제1 마이크로 전자 요소 및 상기 제2 마이크로 전자 요소의 각각이 각각의 상기 전면에서 노출되어 있는 전기 도전성 패드를 갖는, 상기 제1 마이크로 전자 요소 및 상기 제2 마이크로 전자 요소; 및

10ppm(parts per million)/°C 미만의 열팽창 계수(coefficient of thermal expansion, CTE)를 갖는 재료의 인터포저(interposer)로서, 상기 인터포저가, 서로 반대쪽으로 향하고 있는 제1 표면 및 제2 표면과, 상기 인터포저의 개구부 내에 연장하고 상기 제1 표면 및 상기 제2 표면에서 노출되어 있는 제2 도전성 요소를 가지며, 상기 제1 표면이 상기 제1 마이크로 전자 요소의 전면을 향하고 있고, 상기 제2 표면이 상기 제2 마이크로 전자 요소의 전면을 향하고 있는, 상기 인터포저

를 포함하며,

상기 제1 마이크로 전자 요소 및 상기 제2 마이크로 전자 요소의 각각은 각각의 상기 마이크로 전자 요소의 후면으로부터 각각의 상기 마이크로 전자 요소의 전면쪽으로 연장하는 개구부 내에 연장하는 제1 도전성 요소를 더 포함하며, 상기 제1 도전성 요소 중의 하나 이상이 각각의 상기 제1 마이크로 전자 요소 또는 상기 제2 마이크로 전자 요소의 상기 전기 도전성 패드를 통해 연장하며, 상기 제1 도전성 요소가 상기 제2 도전성 요소와 전기 접속되고,

상기 제2 도전성 요소는 상기 제1 표면 및 상기 제2 표면에서 노출되는 제2 전기 도전성 패드를 포함하며, 상기 제1 마이크로 전자 요소 및 상기 제2 마이크로 전자 요소의 상기 전기 도전성 패드가 제1 패드이며, 상기 제1 패드가 상기 제2 전기 도전성 패드와 병치(juxtapose)되고, 상기 제1 도전성 요소가 상기 제1 패드와 상기 제2 전기 도전성 패드의 병치 표면들과 접촉하는,

마이크로 전자 어셈블리.

#### 청구항 2

제1항에 있어서,

상기 제2 도전성 요소가 통과하여 연장하고 있는 개구부는, 상기 제1 마이크로 전자 요소 및 상기 제2 마이크로 전자 요소를 통해 연장하는 개구부 중의 하나 이상과 교차하는, 마이크로 전자 어셈블리.

#### 청구항 3

제1항에 있어서,

상기 제2 도전성 요소가 통과하여 연장하고 있는 개구부는, 상기 제1 마이크로 전자 요소 및 상기 제2 마이크로 전자 요소를 통해 연장하는 각각의 개구부와 교차하는, 마이크로 전자 어셈블리.

#### 청구항 4

제1항에 있어서,

상기 제2 도전성 요소가 통과하여 연장하고 있는 개구부는, 상기 제1 마이크로 전자 요소 및 상기 제2 마이크로 전자 요소를 통해 연장하는 어느 개구부와도 교차하지 않는, 마이크로 전자 어셈블리.

#### 청구항 5

제1항에 있어서,

상기 인터포저는 기본적으로 유전체 재료를 포함하는, 마이크로 전자 어셈블리.

#### 청구항 6

제1항에 있어서,

상기 인터포저는 기본적으로 금속 또는 반도체 재료를 포함하며, 상기 인터포저의 개구부는 절연체로 라이닝 (lining)되는, 마이크로 전자 어셈블리.

#### 청구항 7

제1항에 있어서,

각각의 상기 마이크로 전자 요소의 상기 제1 도전성 요소는 각각의 도전성 패드를 통해 연장하는, 마이크로 전자 어셈블리.

#### 청구항 8

삭제

#### 청구항 9

제1항에 있어서,

상기 제2 도전성 요소가 통과하여 연장하고 있는 상기 인터포저의 개구부는 상기 인터포저의 상기 제1 표면 및 상기 제2 표면에 관련하여 수직 각도(normal angle)로 연장하는 내부 벽부를 갖는, 마이크로 전자 어셈블리.

#### 청구항 10

제1항에 있어서,

상기 제2 도전성 요소가 통과하여 연장하고 있는 상기 인터포저의 개구부는 상기 인터포저의 상기 제1 표면과 상기 제2 표면 사이의 방향으로 테이퍼되는, 마이크로 전자 어셈블리.

#### 청구항 11

제9항에 있어서,

상기 제1 마이크로 전자 요소의 개구부는 상기 제1 마이크로 전자 요소의 후면으로부터 상기 제1 마이크로 전자 요소의 전면을 향하는 방향으로 테이퍼되는, 마이크로 전자 어셈블리.

#### 청구항 12

제10항에 있어서,

상기 제1 마이크로 전자 요소의 개구부는 상기 제1 마이크로 전자 요소의 후면으로부터 상기 제1 마이크로 전자 요소의 전면을 향하는 방향으로 테이퍼되는, 마이크로 전자 어셈블리.

#### 청구항 13

제9항에 있어서,

상기 제1 마이크로 전자 요소의 개구부의 내부 표면은 상기 제1 마이크로 전자 요소의 전면에 대해 수직 각도로 연장하는, 마이크로 전자 어셈블리.

#### 청구항 14

제10항에 있어서,

상기 제1 마이크로 전자 요소의 개구부의 내부 표면은 상기 제1 마이크로 전자 요소의 전면에 대해 수직 각도로 연장하는, 마이크로 전자 어셈블리.

**청구항 15**

제1항에 있어서,

상기 제2 도전성 요소는 상기 인터포저의 개구부의 내부 표면의 윤곽을 따르는, 마이크로 전자 어셈블리.

**청구항 16**

제1항에 있어서,

상기 제2 도전성 요소는 상기 인터포저의 개구부의 내부 표면의 윤곽을 따르지 않는, 마이크로 전자 어셈블리.

**청구항 17**

제1항에 있어서,

상기 인터포저의 개구부와 상기 제1 마이크로 전자 요소 또는 상기 제2 마이크로 전자 요소의 하나 이상의 마이크로 전자 요소의 개구부가 테이퍼되어, 서로 반대 방향으로 더 작게 되는, 마이크로 전자 어셈블리.

**청구항 18**

제1항에 있어서,

상기 인터포저는 상기 제1 마이크로 전자 요소 또는 상기 제2 마이크로 전자 요소 중의 하나 이상과 전기 접속되는 하나 이상의 패시브 부품을 더 포함하는, 마이크로 전자 어셈블리.

**청구항 19**

청구항 1에 따른 마이크로 전자 어셈블리 및 상기 마이크로 전자 어셈블리에 전기 접속된 하나 이상의 기타 전자 부품을 포함하는 시스템.

**청구항 20**

제19항에 있어서,

상기 마이크로 전자 어셈블리 및 상기 기타 전자 부품이 탑재되는 하우징을 더 포함하는, 시스템.

**청구항 21**

마이크로 전자 어셈블리를 제조하는 제조 방법에 있어서,

제1 마이크로 전자 요소와 제2 마이크로 전자 요소를 그 사이에 인터포저(interposer)를 두고 어셈블하는 단계로서, 상기 제1 마이크로 전자 요소 및 상기 제2 마이크로 전자 요소의 각각이 상기 제1 마이크로 전자 요소 및 상기 제2 마이크로 전자 요소의 전면에 인접한 액티브 반도체 장치를 구현하고, 상기 제1 마이크로 전자 요소 및 상기 제2 마이크로 전자 요소의 각각이, 상기 전면에서 떨어져 있는 후면과, 상기 전면에서 노출되어 있는 전기 도전성 패드를 가지며,

상기 인터포저가 기본적으로 반도체 또는 무기 유전체 재료 중의 하나 이상을 포함하며, 상기 인터포저가, 서로 반대쪽으로 향하고 있는 제1 표면 및 제2 표면과, 상기 인터포저를 통해 연장하고 상기 제1 표면 및 상기 제2 표면에서 노출되어 있는 제2 도전성 요소를 가지며, 상기 제1 표면이 상기 제1 마이크로 전자 요소의 전면을 향하고 있고, 상기 제2 표면이 상기 제2 마이크로 전자 요소의 전면을 향하도록 되어 있는, 상기 제1 마이크로 전자 요소 및 상기 제2 마이크로 전자 요소를 어셈블하는 단계; 및

상기 마이크로 전자 요소의 후면으로부터 각각의 상기 전면 쪽으로 연장하는 개구부 내에 연장하는 제1 도전성 요소를 형성하는 단계로서, 하나 이상의 상기 제1 도전성 요소가 하나 이상의 상기 마이크로 전자 요소의 각각의 상기 전기 도전성 패드를 통해 연장하며, 상기 제1 도전성 요소가 상기 제2 도전성 요소와 전기 접속되며, 상기 마이크로 전자 요소의 개구부의 내부 표면이 실질적인 각도를 형성하도록 각각의 상기 마이크로 전자 요소의 각각의 전면에 관련하여 제1 방향 및 제2 방향으로 연장하는, 상기 제1 도전성 요소를 형성하는 단계

를 포함하고,

상기 제2 도전성 요소는 상기 제1 표면 및 상기 제2 표면에서 노출되어 있는 제2 전기 도전성 패드를 포함하며,

상기 제1 마이크로 전자 요소 및 상기 제2 마이크로 전자 요소의 상기 전기 도전성 패드가 제1 패드이며, 상기 제1 패드는 상기 제2 전기 도전성 패드와 병치되며, 상기 제1 도전성 요소가 상기 제1 패드와 상기 제2 전기 도전성 패드의 병치 표면들과 접촉하는,

마이크로 전자 어셈블리의 제조 방법.

### 청구항 22

제21항에 있어서,

각각의 상기 마이크로 전자 요소의 상기 제1 도전성 요소는 각각의 상기 도전성 패드를 통해 연장하는, 마이크로 전자 어셈블리의 제조 방법.

### 청구항 23

삭제

### 청구항 24

제21항에 있어서,

상기 제2 도전성 요소가 통과하여 연장하고 있는 상기 인터포저의 개구부는 상기 인터포저의 상기 제1 표면 및 상기 제2 표면에 관련하여 수직 각도로 연장하는 내부 벽부를 갖는, 마이크로 전자 어셈블리의 제조 방법.

### 청구항 25

제21항에 있어서,

상기 제2 도전성 요소가 통과하여 연장하고 있는 상기 인터포저의 개구부는 상기 인터포저의 상기 제1 표면과 상기 제2 표면 사이의 방향으로 테이퍼되는, 마이크로 전자 어셈블리의 제조 방법.

### 청구항 26

제21항에 있어서,

상기 제2 도전성 요소는 상기 인터포저의 개구부의 내부 표면의 윤곽을 따르는, 마이크로 전자 어셈블리의 제조 방법.

### 청구항 27

제21항에 있어서,

상기 제2 도전성 요소는 상기 인터포저의 개구부의 내부 표면의 윤곽을 따르지 않는, 마이크로 전자 어셈블리의 제조 방법.

### 청구항 28

제27항에 있어서,

상기 인터포저의 개구부와 상기 제2 도전성 요소는 반대 방향으로 테이퍼되는, 마이크로 전자 어셈블리의 제조 방법.

## 발명의 설명

### 기술 분야

[0001] 관련 출원의 상호 참조

[0002] 본 출원은 2010년 12월 2일자로 출원된 미국 특허 출원 번호 12/958,866의 계속 출원이며, 상기 특허 출원은 그 개시 내용이 참조에 의해 본 명세서에 원용된다.

[0003] 발명의 분야

[0004] 본 발명은 마이크로 전자 장치의 패키징에 관한 것으로, 보다 구체적으로는 반도체 장치의 패키징에 관한 것이

다.

## 배경기술

[0005] 마이크로 전자 장치는 일반적으로 흔히 다이 또는 반도체칩으로 지칭되는 실리콘 또는 갈륨 아세나이드와 같은 반도체 재료의 얇은 슬랩(slab)을 포함한다. 반도체칩은 대개는 개별적인 사전 패키징된 유닛으로서 제공된다. 일부 유닛 설계에서, 반도체칩은 기판 또는 칩 캐리어에 탑재되며, 이 기판 또는 칩 캐리어가 그 후 인쇄회로 기판과 같은 회로 패널 상에 탑재된다.

[0006] 반도체칩의 제1 면(예컨대, 전면)에는 액티브 회로가 제조된다. 액티브 회로에 대한 전기 접속을 용이하게 하기 위해, 칩은 동일한 면 상에 본드 패드가 제공된다. 본드 패드는 통상적으로 다이의 에지 주변 또는 다수의 메모리 장치에 대해서는 다이 센터 중의 하나에 규칙적인 어레이로 배치된다. 본드 패드는 일반적으로 대략  $0.5\mu\text{m}$  두께의 구리 또는 알루미늄과 같은 도전성 금속으로 이루어진다. 본드 패드는 금속의 단일층 또는 복수 층을 포함할 수 있다. 본드 패드의 크기는 장치 타입에 따라 변화될 수 있지만, 통상적으로 한 변이 수십 내지 수백 마이크로미터의 치수로 된다.

[0007] 관통 실리콘 비아(through-silicon via, TSV)는 본드 패드가 배치되는 반도체칩의 전면과 전면 반대쪽의 반도체 칩의 후면 간의 전기 접속을 제공하기 위해 사용될 수 있다. 종래의 TSV 홀은 액티브 회로를 포함하기 위해 사용될 수 있는 제1 면의 부분을 감소시킬 수 있다. 액티브 회로용으로 사용될 수 있는 제1 면 상의 이용 가능한 공간의 이러한 감소는 각각의 반도체칩을 생산하기 위해 요구되는 실리콘의 양을 증가시킬 수 있으며, 이에 의해 각각의 칩의 비용을 증가시킬 가능성이 있다.

[0008] 크기는 칩의 임의의 물리적 배열에서 중요한 고려사항이다. 칩의 더욱 컴팩트한 물리적 배열에 대한 요구는 휴대 가능한 전자 장치의 급속한 진보로 더욱 커지게 되었다. 단지 일례로서, "스마트폰"으로서 흔히 지칭되는 장치는 셀룰러 전화의 기능에 강력한 데이터 프로세서와, 메모리와, 위치 확인 시스템(GPS) 수신기, 전자 카메라, 근거리 통신망 접속, 고해상도 디스플레이 및 관련 이미지 처리 칩과 같은 보조 장치를 통합하고 있다. 이러한 장치는 폴 인터넷 접속성, 폴해상도 비디오를 포함하는 엔터테인먼트, 내비게이션, 전자 뱅킹(electronic banking) 등과 같은 성능을 포켓-사이즈 장치에 모두 제공할 수 있다. 더욱이, 칩 중의 몇몇은 흔히 I/O로 지칭되는 다수의 입력 및 출력 접속부를 갖는다. 이를 I/O는 다른 칩의 I/O와 상호접속되어야 한다. 상호접속부는 신호 전파 지연을 최소화하기 위해 짧아야만 하고 낮은 임피던스를 가져야 한다. 상호접속부를 형성하는 부품은 어셈블리의 크기를 크게 증가시키지 않아야 한다. 예컨대 인터넷 검색 엔진에서 이용되는 것과 같은 데이터 서버에서와 같이 기타 애플리케이션에서 유사한 요구가 발생하고 있다. 예컨대, 복잡한 칩들 간의 다수의 짧은 저임피던스 상호접속부를 제공하는 구조는 검색 엔진의 대역폭을 증가시킬 수 있고, 전력 소모를 감소시킬 수 있다.

## 발명의 내용

### 해결하려는 과제

[0009] 반도체 비아 형성 및 상호접속부에서 이루어진 진전에도 불구하고, 칩 전면과 칩 후면 간에 상호접속을 이루기 위한 프로세스를 향상시키고 이러한 프로세스에 의해 발생할 수 있는 구조에 대한 추가의 개선이 이루어질 수 있다.

### 과제의 해결 수단

[0010] 본 발명의 양태에 따라, 마이크로 전자 어셈블리는, 제1 마이크로 전자 요소 및 제2 마이크로 전자 요소의 각각이 상기 제1 마이크로 전자 요소 및 상기 제2 마이크로 전자 요소의 전면에 인접한 액티브 반도체 장치를 구현하는 상기 제1 마이크로 전자 요소 및 상기 제2 마이크로 전자 요소와, 10ppm(parts per million)/°C 미만의 열팽창 계수(coefficient of thermal expansion, CTE)를 갖는 재료의 인터포저(interposer)를 포함할 수 있다. 각각의 상기 마이크로 전자 요소는, 각각의 상기 전면에서 떨어져 있는 후면과, 각각의 상기 전면에서 노출되어 있는 전기 도전성 패드를 가질 수 있다. 상기 인터포저는, 서로 반대쪽으로 향하고 있는 제1 표면 및 제2 표면과, 상기 인터포저의 개구부 내에 연장하는 제2 도전성 요소를 가질 수 있다. 상기 제2 도전성 요소는 상기 인터포저의 상기 제1 표면 및 상기 제2 표면에서 노출될 수 있다.

[0011] 상기 인터포저의 상기 제1 표면이 상기 제1 마이크로 전자 요소의 전면을 향하고 있고, 상기 제2 표면이 상기 제2 마이크로 전자 요소의 전면을 향할 수 있다. 상기 제1 마이크로 전자 요소 및 상기 제2 마이크로 전자 요

소의 각각은 각각의 상기 마이크로 전자 요소의 후면으로부터 각각의 상기 마이크로 전자 요소의 전면쪽으로 연장하는 개구부 내에 연장하는 제1 도전성 요소를 더 포함할 수 있다. 상기 제1 도전성 요소 중의 하나 이상이 각각의 상기 제1 마이크로 전자 요소 또는 상기 제2 마이크로 전자 요소의 상기 전기 도전성 패드를 통해 연장할 수 있다. 상기 제1 도전성 요소가 상기 제2 도전성 요소와 전기 접속될 수 있다.

[0012] 특정 실시예에서, 상기 제2 도전성 요소가 통과하여 연장하고 있는 개구부는, 상기 제1 마이크로 전자 요소 및 상기 제2 마이크로 전자 요소를 통해 연장하는 개구부 중의 하나 이상과 교차할 수 있다. 일실시예에서, 상기 제2 도전성 요소가 통과하여 연장하고 있는 개구부는, 상기 제1 마이크로 전자 요소 및 상기 제2 마이크로 전자 요소를 통해 연장하는 각각의 개구부와 교차할 수 있다. 일례의 실시예에서, 상기 제2 도전성 요소가 통과하여 연장하고 있는 개구부는, 상기 제1 마이크로 전자 요소 및 상기 제2 마이크로 전자 요소를 통해 연장하는 어느 개구부와도 교차하지 않을 수 있다. 특정 실시예에서, 상기 인터포저는 기본적으로 유전체 재료를 포함할 수 있다. 일실시예에서, 상기 인터포저는 기본적으로 금속 또는 반도체 재료를 포함할 수 있다. 상기 인터포저의 개구부는 절연체로 라이닝(lining)될 수 있다.

[0013] 일례의 실시예에서, 각각의 상기 마이크로 전자 요소의 상기 제1 도전성 요소는 각각의 도전성 패드를 통해 연장할 수 있다. 특정 실시예에서, 상기 제2 도전성 요소는 상기 제1 표면 및 상기 제2 표면에서 노출되는 제2 전기 도전성 패드를 포함할 수 있다. 상기 제1 마이크로 전자 요소 및 상기 제2 마이크로 전자 요소의 상기 전기 도전성 패드가 제1 패드이며, 상기 제1 패드가 상기 제2 전기 도전성 패드와 병치(juxtapose)될 수 있다. 상기 제1 도전성 요소가 상기 제1 패드와 상기 제2 도전성 패드의 병치 표면들과 접촉할 수 있다. 일실시예에서, 상기 제2 도전성 요소가 통과하여 연장하고 있는 상기 인터포저의 개구부는 상기 인터포저의 상기 제1 표면 및 상기 제2 표면에 관련하여 수직 각도(normal angle)로 연장하는 내부 벽부를 가질 수 있다. 일례의 실시예에서, 상기 제2 도전성 요소가 통과하여 연장하고 있는 상기 인터포저의 개구부는 상기 인터포저의 상기 제1 표면과 상기 제2 표면 사이의 방향으로 테이퍼될 수 있다.

[0014] 일실시예에서, 상기 제1 마이크로 전자 요소의 개구부는 상기 제1 마이크로 전자 요소의 후면으로부터 상기 제1 마이크로 전자 요소의 전면을 향하는 방향으로 테이퍼될 수 있다. 특정 실시예에서, 상기 제1 마이크로 전자 요소의 개구부의 내부 표면은 상기 제1 마이크로 전자 요소의 전면에 대해 수직 각도로 연장할 수 있다. 일례의 실시예에서, 상기 제2 도전성 요소는 상기 인터포저의 개구부의 내부 표면의 윤곽을 따를 수 있다. 일실시예에서, 상기 제2 도전성 요소는 상기 인터포저의 개구부의 내부 표면의 윤곽을 따르지 않을 수도 있다.

[0015] 특정 실시예에서, 상기 인터포저의 개구부와 상기 제1 마이크로 전자 요소 또는 상기 제2 마이크로 전자 요소의 하나 이상의 마이크로 전자 요소의 개구부가 테이퍼되어, 서로 반대 방향으로 더 작게 될 수 있다. 일례의 실시예에서, 상기 인터포저는 상기 제1 마이크로 전자 요소 또는 상기 제2 마이크로 전자 요소 중의 하나 이상과 전기 접속되는 하나 이상의 패시브 부품을 포함할 수 있다. 일실시예에서, 본 발명의 양태에 따른 시스템은 전술한 마이크로 전자 어셈블리 및 상기 마이크로 전자 어셈블리에 전기 접속된 하나 이상의 기타 전자 부품을 포함할 수 있다. 특정 실시예에서, 상기 시스템은 상기 마이크로 전자 어셈블리 및 상기 기타 전자 부품이 탑재되는 하우징을 더 포함할 수 있다.

[0016] 본 발명의 또 다른 양태에 따라, 마이크로 전자 어셈블리를 제조하는 제조 방법은, 제1 마이크로 전자 요소와 제2 마이크로 전자 요소를 그 사이에 인터포저(interposer)를 두고 어셈블하는 단계로서, 상기 제1 마이크로 전자 요소 및 상기 제2 마이크로 전자 요소의 각각이 상기 제1 마이크로 전자 요소 및 상기 제2 마이크로 전자 요소의 전면에 인접한 액티브 반도체 장치를 구현하는, 상기 제1 마이크로 전자 요소 및 상기 제2 마이크로 전자 요소를 어셈블하는 단계와, 상기 마이크로 전자 요소의 후면으로부터 각각의 상기 전면 쪽으로 연장하는 개구부 내에 연장하는 제1 도전성 요소를 형성하는 단계를 포함할 수 있다. 상기 제1 마이크로 전자 요소 및 상기 제2 마이크로 전자 요소의 각각이, 상기 전면에서 떨어져 있는 후면과, 상기 전면에서 노출되어 있는 전기 도전성 패드를 가질 수 있다.

[0017] 상기 인터포저는 기본적으로 반도체 또는 무기 유전체 재료 중의 하나 이상을 포함할 수 있다. 상기 인터포저는, 서로 반대쪽으로 향하고 있는 제1 표면 및 제2 표면과, 상기 인터포저를 통해 연장하고 상기 제1 표면 및 상기 제2 표면에서 노출되어 있는 제2 도전성 요소를 가질 수 있다. 상기 인터포저의 상기 제1 표면이 상기 제1 마이크로 전자 요소의 전면을 향하고 있고, 상기 인터포저의 상기 제2 표면이 상기 제2 마이크로 전자 요소의 전면을 향하도록 될 수 있다. 하나 이상의 상기 제1 도전성 요소가 하나 이상의 상기 마이크로 전자 요소의 각각의 상기 전기 도전성 패드를 통해 연장할 수 있다. 상기 제1 도전성 요소가 상기 제2 도전성 요소와 전기 접속될 수 있다. 상기 마이크로 전자 요소의 개구부의 내부 표면은 실질적인 각도를 형성하도록 각각의 상기 마

이크로 전자 요소의 각각의 전면에 관련하여 제1 방향 및 제2 방향으로 연장할 수 있다.

[0018] 일례의 실시예에서, 각각의 상기 마이크로 전자 요소의 상기 제1 도전성 요소는 각각의 상기 도전성 패드를 통해 연장할 수 있다. 일실시예에서, 상기 제2 도전성 요소는 상기 제1 표면 및 상기 제2 표면에서 노출되어 있는 제2 전기 도전성 패드를 포함할 수 있다. 각각의 상기 마이크로 전자 요소의 상기 제1 도전성 패드는 상기 제2 패드 중의 하나와 병치될 수 있다. 상기 제1 도전성 요소는 상기 제1 패드 및 상기 제2 패드의 병치된 표면들과 접촉할 수 있다. 특정 실시예에서, 상기 제2 도전성 요소가 통과하여 연장하고 있는 상기 인터포조의 개구부는 상기 인터포저의 상기 제1 표면 및 상기 제2 표면에 관련하여 수직 각도로 연장하는 내부 벽부를 가질 수 있다.

[0019] 일실시예에서, 상기 제2 도전성 요소가 통과하여 연장하고 있는 상기 인터포저의 개구부는 상기 인터포저의 상기 제1 표면과 상기 제2 표면 사이의 방향으로 테이퍼될 수 있다. 일례의 실시예에서, 상기 제2 도전성 요소는 상기 인터포저의 개구부의 내부 표면의 윤곽을 따를 수 있다. 특정 실시예에서, 상기 제2 도전성 요소는 상기 인터포저의 개구부의 내부 표면의 윤곽을 따르지 않을 수 있다. 일실시예에서, 상기 인터포저의 개구부와 상기 제2 도전성 요소는 반대 방향으로 테이퍼될 수 있다.

### 도면의 간단한 설명

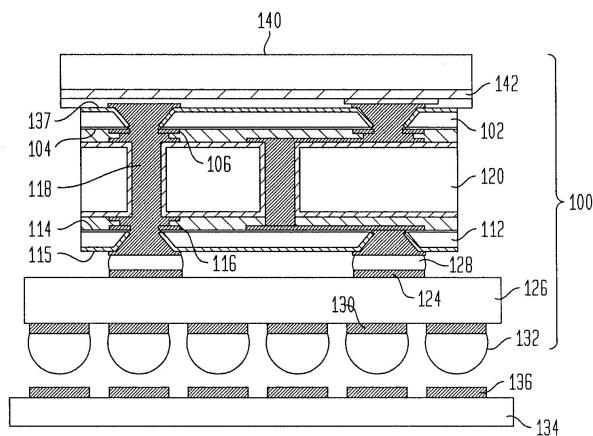

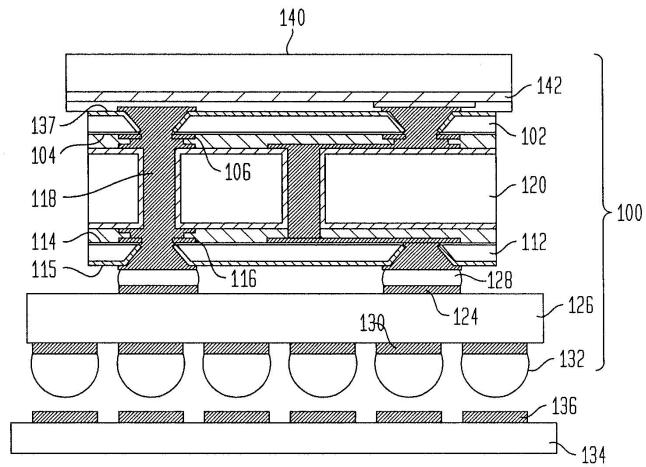

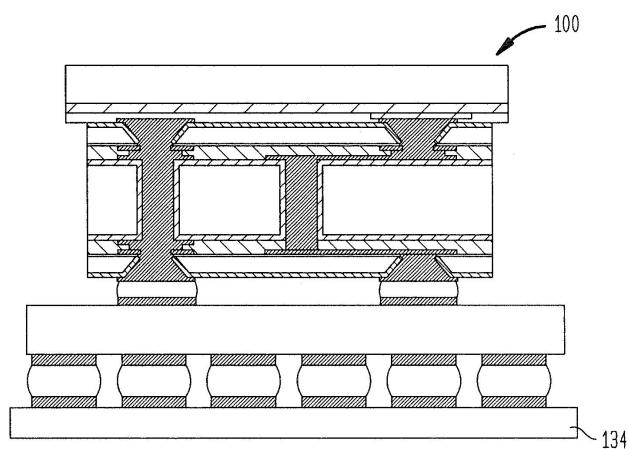

[0020] 도 1은 회로 패널과의 부착을 위해 위치된 본 발명의 실시예에 따른 마이크로 전자 어셈블리를 예시하는 단면도이다.

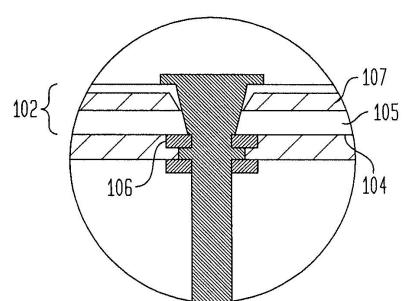

도 1a는 본 발명의 실시예에 따른 마이크로 전자 어셈블리를 상세하게 예시하는 부분 단면도이다.

도 2는 회로 패널에 탑재된 바와 같은 본 발명의 실시예에 따른 마이크로 전자 어셈블리를 예시하는 단면도이다.

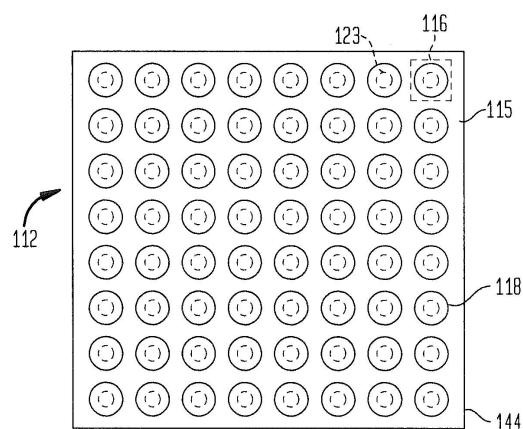

도 3은 본 발명의 실시예에 따른 마이크로 전자 어셈블리를 예시하는 평면도이다.

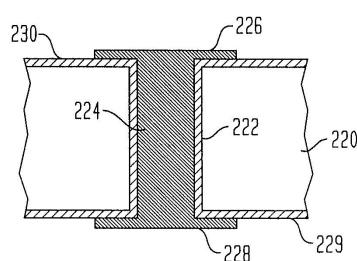

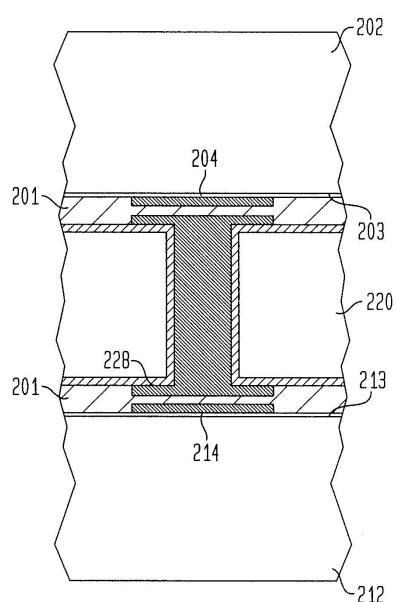

도 4 내지 도 11은 본 발명의 실시예의 변형예에 따른 마이크로 전자 어셈블리를 제조하는 방법에서의 단계를 예시하는 부분 단면도이다.

도 12 내지 도 14는 도 4 내지 도 11에 도시된 본 발명의 실시예의 변형예에 따른 마이크로 전자 어셈블리를 제조하는 방법의 단계를 예시하는 부분 단면도이다.

도 15 및 도 16은 도 12 내지 도 14에 도시된 본 발명의 실시예의 변형예에 따른 마이크로 전자 어셈블리를 제조하는 방법의 단계를 예시하는 부분 단면도이다.

도 17은 도 16에 도시된 본 발명의 실시예의 변형예에 따른 마이크로 전자 어셈블리를 예시하는 부분 단면도이다.

도 18은 도 10에 도시된 본 발명의 실시예의 다른 변형예에 따른 마이크로 전자 어셈블리를 예시하는 부분 단면도이다.

도 19는 본 발명의 일실시예에 따른 시스템의 개요도이다.

### 발명을 실시하기 위한 구체적인 내용

[0021] 도 1은 본 발명의 실시예에 따른 마이크로 전자 어셈블리(100)를 예시하고 있다. 마이크로 전자 패키지는 제1 및 제2 마이크로 전자 요소(102, 112)를 포함하며, 이를 마이크로 전자 요소의 각각의 마이크로 전자 요소 사이에 배치된 인터포저(120) 쪽으로 바라보는 컨택-포함 전면(contact-bearing front surface)(104, 114)을 갖는다. 각각의 마이크로 전자 요소는 실리콘, 실리콘의 합금, 또는 III-V족 반도체 재료 또는 II-VI족 반도체 재료와 같은 기타 반도체 재료를 포함할 수 있는 예컨대 반도체칩으로 구현되는 집적회로이어도 된다. 도 1a의 확대도에서 보여지는 바와 같이, 칩(102)은, 컨택-포함 면으로도 지칭되고 칩의 주요 표면인 전면(104)을 가지며, 이 전면에 칩의 제1 영역(105)이 있다. 제2 칩(112)은 칩 102와 동일한 구조를 가질 수 있다. 제1 영역(105)은 통상적으로 배선층 사이 및 배선층 주위에 유전체층이 배치된 복수의 배선층을 포함하는 유전체 영역을 포함한다. 특정 실시예에서, 유전체 영역은 저유전상수를 갖는 유전체 재료의 하나 이상의 층, 즉 "로우-k" 유전체층을 포함할 수 있다. 로우-k 유전체 재료는 다른 것들 중에서도 다공성의 이산화규소, 탄소-도핑된 이산화규소, 중합성 유전체, 및 다공성의 중합성 유전체를 포함한다. 다공성 로우-k 유전체층에서, 유전체층은 동일 재료의 비다공성 층에 비하여 유전체 재료의 유전 상수를 감소시키는 상당한 다공성을 가질 수 있다. 유전

체 재료는 통상적으로 1.0을 크게 초과하는 유전 상수를 갖지만, 다공성 유전체 재료 내의 개방 공간을 점유하는 공기는 약 1.0의 유전 상수를 갖는다. 이로써, 일부 유전체 재료는 상당한 다공성을 가짐으로써 유전 상수의 감소를 달성할 수 있다.

[0022] 그러나, 중합성 유전체 재료 및 다공성 유전체 재료와 같은 일부 로우-k 유전체 재료는 전통적인 유전체 재료보다 훨씬 적은 기계적 응력을 견뎌낸다. 마이크로 전자 요소가 테스트될 수 있는 특정 타입의 작동 환경 및 방식은 로우-k 유전체 재료가 견뎌낼 수 있는 한계점의 응력 또는 한계점 부근의 응력을 제공할 수 있다. 여기에서 설명된 마이크로 전자 어셈블리는 마이크로 전자 요소에 응력이 가해지는 지점을 영역 105 내의 로우-k 유전체층으로부터 멀어지도록 이동시킴으로써 마이크로 전자 요소의 로우-k 유전체층에 대한 향상된 보호를 제공한다. 이러한 방식으로, 제조, 작동 및 테스팅은 로우-k 유전체층에 훨씬 감소된 응력을 가하게 되어, 로우-k 유전체층을 보호한다.

[0023] 층(105)은 또한 액티브 반도체 장치(예컨대, 트랜지스터, 다이오드 또는 기타 액티브 장치)를 포함하며, 이들 반도체 장치는 배선층에 의해 궁극적으로는 전면에 있는 전기 도전성 패드(106)와 접속된다. 칩이 SOI(silicon-on-insulator) 타입 칩인 때에, 제1 영역(105)은 또한 액티브 반도체 장치 아래에 놓여 있는 매립된 유전체층을 포함할 수 있다. 제1 영역(105)은 칩의 제2 영역(107)을 전면(104)으로부터 분리시킬 수 있다. 제1 영역은 통상적으로 0.1 $\mu$ m 내지 5 $\mu$ m의 두께를 가지며, 통상적으로 박막화될 수 없다. 제2 영역(107)은 통상적으로는 기본적으로 반도체 재료(통상적으로 단결정 또는 다결정 중의 어느 하나)를 포함하며, 통상적으로 20  $\mu$ m 미만의 두께를 가지며, 이 두께는 통상적으로 초기 반도체 웨이퍼가 가공 동안 박막화되는 정도에 의해 결정된다. 일실시예에서, 칩은 제1 영역(105)만을 가질 수도 있고, 제2 영역(107)이 제공되지 않을 수도 있다. 그러므로, 마이크로 전자 요소(102, 112)가 탑재되는 구조상의 인터포저(120)는 마이크로 전자 요소를 구조적으로 지지하여, 마이크로 전자 요소(102, 112)의 두께를 예외적인 정도로 감소시킬 수 있다. 또한, 유전체 영역(105)으로도, 인터포저를 바라보는 각각의 마이크로 전자 요소가 지지된다.

[0024] 도 1에 도시된 바와 같이, 마이크로 전자 요소는 접착제(101) 등에 의해 인터포저(120)와 함께 접합될 수 있다. 다른 가능한 접합 재료는, 특정 실시예에서는 도핑될 수 있고 500°C 아래의 글래스 전이 온도(glass transition temperature)를 가질 수 있는 글래스를 포함할 수 있다. 통상적으로, 마이크로 전자 요소(112)는 기본적으로 다른 마이크로 전자 요소(102)와 동일한 반도체 재료를 포함한다. 도 1에 도시된 바와 같이, 마이크로 전자 요소(110)는 도전성 패드(106, 116)와의 전기 도전성 접속을 제공하기 위해 마이크로 전자 요소에서의 개구부를 통해 연장하는 복수의 도전성 비아 요소를 가질 수 있다.

[0025] 마이크로 전자 요소(102, 112)는 도전성 패드(106, 116)와 이 도전성 패드들 사이의 인터포저(120)를 통해 연장하는 전기 도전성 요소(118)를 통해 함께 전기 접속될 수 있다. 일례에서, 도전성 요소(118)는 도전성 패드(106, 116)의 노출 표면과 접촉하여 금속을 침적시킴으로써 형성되는 금속 특징부를 포함할 수 있다. 본 명세서에서 추가로 상세하게 설명되는 바와 같이 도전성 요소를 형성하기 위해 다양한 금속 침적 단계가 이용될 수 있다.

[0026] 도 1에 도시된 바와 같이, 도전성 요소(118)는, 플립-칩(flip-chip) 방식과 유사하게, 예컨대 솔더(solder), 주석, 인듐 또는 이들의 조합과 같은 접합 금속의 매스(mass)(128)를 통해서와 같이 유전체 요소(126)의 표면에 노출된 컨택(124)에 도전 가능하게 접합될 수 있다. 그 다음으로, 유전체 요소는 패키지(100)를 예컨대 유전체 요소(126)로부터 멀어지도록 들출하는 솔더 볼과 같은 도전성 매스(132)를 통해서와 같이 회로 패널(134)의 대응하는 컨택(136)에 추가로 전기 접속하기 위한 복수의 단자(130)를 가질 수 있다. 도 1은 회로 패널(134)을 패키지(100)에 연결하기 전의 패키지(100)를 도시하고 있다. 도 2는 패키지(100) 및 이 패키지에 연결된 회로 패널(134)을 포함하는 마이크로 전자 어셈블리를 도시하고 있다.

[0027] 열 분산기(heat spreader)(140)가 예컨대 열전도성 그리스, 열전도성 접착제, 또는 솔더, 주석, 인듐, 금, 또는 기타 재료와 같은 비교적 낮은 용융 온도를 갖는 연결 금속과 같은 열전도성 재료(142)를 통해서와 같이 마이크로 전자 요소(102)의 후면(137)에 열적으로 결합될 수 있다. 열전도성 재료(142)가 또한 금속 또는 금속의 도전성 화합물과 같이 전기 도전성을 나타낼 때에, 유전체층(도시하지 않음)이 마이크로 전자 요소(102)의 후면(137)을 이러한 열전도성 및 전기 전도성 재료(142)로부터 분리시킬 수 있다. 전술한 바와 같이, 마이크로 전자 어셈블리 또는 패키지(100)는 마이크로 전자 요소(102, 112)의 두께가 예외적인 정도로 감소될 수 있도록 한다. 이로써, 각각의 마이크로 전자 요소(102 또는 112)의 두께는 단지 제1 영역(105)(도 1a)의 두께가 되거나 또는 이러한 두께에 제2 영역(107)의 작은 두께를 더한 두께가 될 수 있다. 감소된 두께는 현저하게 효과적이고 고른 열전달이 열 분산기(140)로 달성될 수 있도록 할 수 있다.

- [0028] 도 3은 패키지의 마이크로 전자 요소(112)의 후면(115) 쪽으로 본 도면으로, 후면에 노출된 영역 어레이로 배열된 것으로 도시된 도전성 요소(118)를 예시하고 있다. 도 3에 또한 도시된 바와 같이, 도전성 요소(118)는 제2 개구부(123) 내에서 연장하고 있고, 마이크로 전자 요소(110)의 전면(103)(도 1)에 노출된 역시 영역 어레이로 배열될 수 있는 도전성 패드(116)에 접속된다. 이와 달리, 마이크로 전자 요소의 도전성 패드(116)가 상이한 배열을 가져서, 예컨대 주변 에지(144)에 인접하게 배열되거나, 또는 전면에 대해 중앙에 배열될 수 있을 때에, 도전성 요소(118)는 통상적으로 그에 부합하는 패턴을 갖는다.

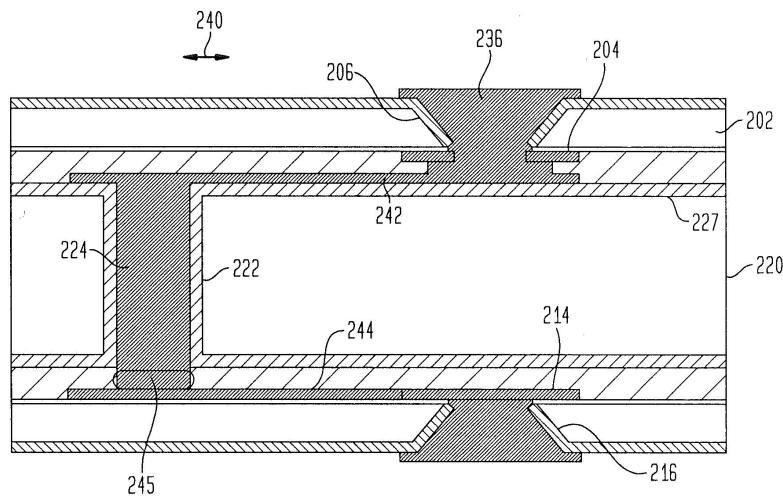

- [0029] 도 4를 참조하여, 본 발명의 또 다른 실시예에 따른 마이크로 전자 어셈블리의 제조 방법을 설명한다. 도 4는 관통 홀(222)을 갖는 인터포저(220)를 도시하는 부분 단면도이며, 이 관통 홀을 통해 도전성 비아(224)가 연장하고 있다. 비아(224)는 인터포저의 제1 및 제2 주요 표면(227, 229)에 각각 노출된 제1 및 제2 도전성 패드(226, 228)로 종료될 수 있다.

- [0030] 인터포저는 섭씨 온도당 약 10ppm(parts per million) 미만, 즉 "10ppm/°C 미만"인 선형 열팽창 계수(linear coefficient of thermal expansion)(CTE- $\alpha$ )를 가질 수 있다. 다른 것들 중에서도 실리콘, 이산화규소, 일부 세라믹 재료, 및 일부 금속의 CTE- $\alpha$ 는 이 범위 내에 있다. 인터포저가 금속 또는 반도체 재료로 이루어질 때, 유전체층(230)은 제1 및 제2 주요 표면 위에 놓여질 수 있고, 비아(224) 및 패드(226, 228)를 인터포저(220)의 몸체로부터 절연하기 위해 관통 홀(222)을 라이닝(lining)할 수 있다. 그리고나서, 도 5에 예시된 바와 같이, 웨이퍼의 전면(203, 213)이 각각 제1 및 제2 인터포저 표면(227, 229)을 바라보는 상태로 제1 웨이퍼(202) 및 제2 웨이퍼(212)가 인터포저에 부착된다. 접착제 또는 기타 유전체 재료(201), 예컨대 글래스가 인터포저와 웨이퍼를 부착하기 위해 이용될 수 있다. 통상적으로, 웨이퍼는 각각의 웨이퍼의 도전성 패드가 인터포저의 패드와 병치(juxtapose)되도록 인터포저에 부착된다. 예컨대, 제1 웨이퍼(202)의 도전성 패드(204)는 인터포저 패드(226)와 병치되고, 제2 웨이퍼(212)의 도전성 패드(214)는 인터포저 패드(228)와 병치된다.

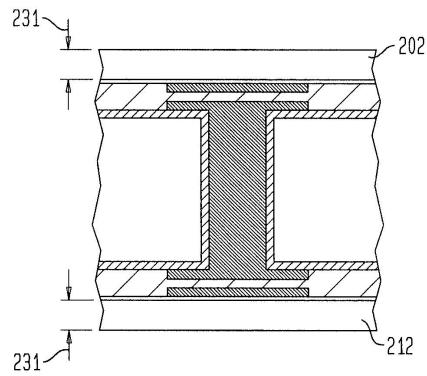

- [0031] 다음으로, 도 6에 도시된 바와 같이, 웨이퍼의 두께가 전술한 바와 같이 그라인딩, 랩핑 또는 폴리싱 등에 의해 감소된다. 이 단계를 완료한 후, 각각의 웨이퍼(202, 212)는 전술한 바와 같이 박막화 가능하지 않은 영역(105)(도 1a)의 두께에 대응하는 두께(231)를 가질 수 있거나, 또는 박막화 가능하지 않은 영역 아래에 있는 영역(107)(도 1a)의 일부 재료를 포함할 수 있는 더 큰 두께를 가질 수 있다. 일실시예에서, 웨이퍼(202, 212) 중의 하나 또는 둘 다의 웨이퍼의 영역(107)은 20 $\mu$ m까지의 두께를 가질 수 있다.

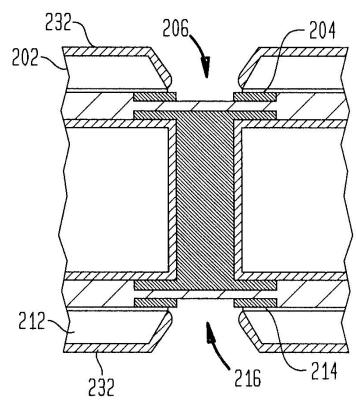

- [0032] 도 7은 각각의 웨이퍼 및 이들 웨이퍼의 도전성 패드(204, 214)를 포함한 두께를 통해 연장하는 제1 및 제2 개구부(206, 216)가 형성되는 후속 가공 단계를 도시하고 있다. 이러한 개구부는 예컨대 각각의 웨이퍼의 반도체 재료에 가해지는 에칭, 레이저 패터닝, 샌드블래스팅, 기계식 밀링, 또는 기타 기술에 의해 이루어질 수 있다. 웨이퍼 두께를 통해 연장하는 개구부를 형성한 후, 개구부의 내부 벽부 상에 유전체층(232)이 형성될 수 있으며, 그 후 개구부가 각각의 패드(204, 214)를 통해 연장될 수 있다. 개구부(206, 216) 및 유전체층(232)을 형성하는 공정은 미국 특허 공개 번호 20080246136A1 또는 모두 2010년 7월 23일자로 출원된 미국 특허 출원 번호 12/842,717, 12/842,612, 12/842,669, 12/842,692, 12/842,587 중의 어느 하나 또는 전부에 일반적으로 개시된 바와 같이 이루어질 수 있으며, 이 공개 특허 및 특허 출원의 개시 내용이 참조에 의해 본 명세서에 원용된다. 일실시예에서, 유전체층(232)은 전기영동 또는 전해 침적(electrophoretic or electrolytic deposition)에 의해 개구부(206, 216) 내의 노출된 반도전성 또는 도전성 표면 상에 및 마이크로 전자 요소의 노출된 면 상에 선택적으로 형성될 수 있다.

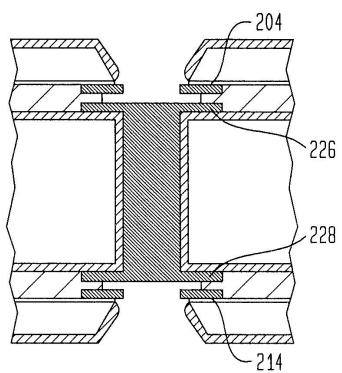

- [0033] 도 8은 각각 웨이퍼 패드(204, 214)와 인터포저 패드(226, 228)의 병치된 표면들 사이의 유전체 또는 본딩 재료의 일부분을 제거하는 선택적 단계를 예시하고 있다.

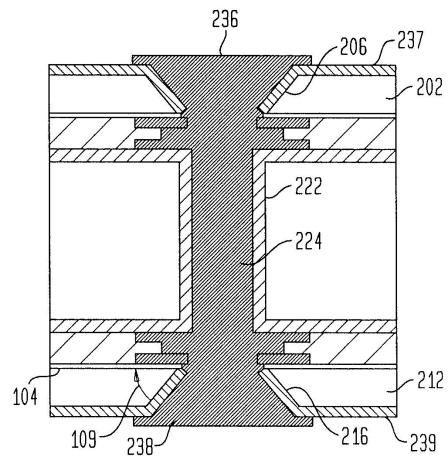

- [0034] 그리고나서, 도 9에 도시된 바와 같이, 마이크로 전자 어셈블리의 각각의 외측으로 향하는 표면(237, 239)에서 노출되는 도전성 요소(236, 238)를 형성하기 위해 개구부(206, 216) 내로 하나 이상의 금속층이 침적될 수 있다. 도전성 요소(236, 238)는 각각의 웨이퍼(202, 212)의 도전성 패드(204, 214)와 접속하고, 인터포저 패드(226, 228) 및 인터포저를 통해 연장하는 비아(224)를 통해 함께 전기 접속된다.

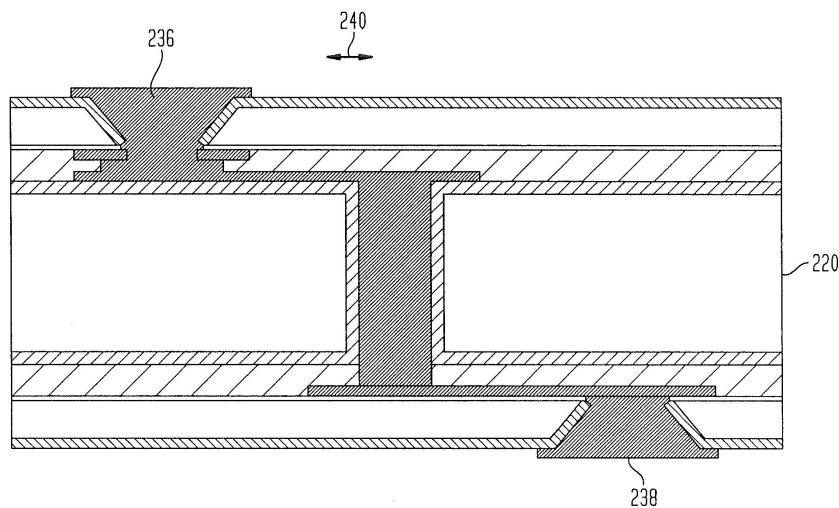

- [0035] 도 9에 도시된 실시예에서, 비아(224)가 관통하여 연장하고 있는 개구부(222)는 제1 및 제2 웨이퍼(202, 212)를 통해 연장하는 개구부(206, 216)를 교차한다. 그러나, 다른 구성도 가능하다. 예컨대, 도 10에 도시된 바와 같이, 웨이퍼(202, 212) 중의 하나 또는 둘 다의 웨이퍼에서의 도전성 요소는 비아(224)로부터 하나 이상의 측 방향(240)(인터포저 주표면(227)이 연장하는 방향)으로 변위될 수 있다. 도 10에 도시된 경우에서는, 도전성 요소(236, 238) 양자가 비아로부터 동일 방향으로 변위될 수 있으며, 도전성 요소가 안에 형성되는 개구부(206, 216) 중의 어느 것도, 비아(224)가 관통하여 연장하고 도전성 요소(236, 238)와 전기 접속하게 하는 대응하는

인터포저 개구부(222)를 교차하지 않는다. 도 9에 도시된 바와 같이, 반도체 요소(202, 212)에서의 개구부(216, 206)의 내부 표면은 실질적인 각도(109)를 형성하도록 각각의 반도체 요소의 각각의 제1 표면(104)에 관련하여 제1 및 제2 방향으로 연장할 수 있다.

[0036] 도 10에 도시된 바와 같이, 인터포저 비아(224)와 패드(204, 214) 간의 전기 접속은 하나 이상의 방식으로 제공될 수 있다. 예컨대, 마이크로 전자 요소(212)는 인터포저(220)를 향해 도전성 패드(214)로부터 떨어져 연장하는 트레이스(244)를 가질 수 있으며, 이 트레이스(244)는 열과 압력 하에서 솔더, 주석 또는 인듐과 같은 연결 금속(245)을 이용하거나, 확산 접합을 이용하거나, 또는 이와 달리 직접적인 금속 대 금속 연결 등에 의해 인터포저의 비아(224)에 도전 방식으로 접합될 수 있다. 또 다른 예에서, 인터포저(220)는 인터포저의 제1 주표면(227)이 연장하는 방향으로 비아(224)로부터 떨어지도록 연장하는 전기 도전성 트레이스(242)를 가질 수 있다. 이 경우, 도전성 요소(236)의 제조는 제1 웨이퍼의 패드(204)와 인터포저의 트레이스(242) 간의 전기 접속을 형성한다.

[0037] 도 11은 도전성 요소(236, 238)가 도면부호 240 방향으로 서로 변위되는 또 다른 예를 예시하고 있다.

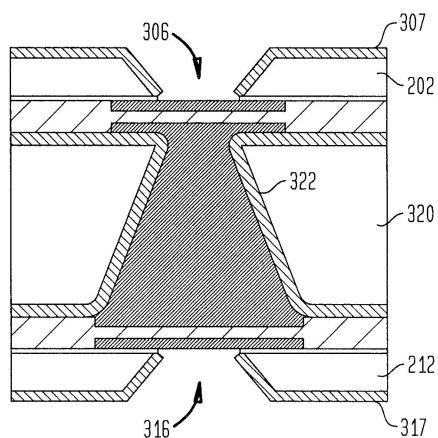

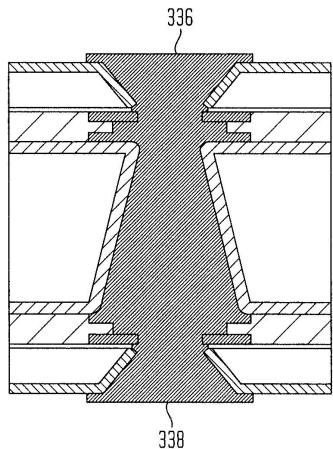

[0038] 도 12를 참조하면, 인터포저(320)의 개구부(322)가 그 폭이 하나의 마이크로 전자 요소(202)의 전면 쪽의 방향으로 더 작아지게 되도록 테이퍼되는 다른 변형예가 도시되어 있다. 마이크로 전자 요소(202, 212)에 개구부(306, 316)를 형성한 후, 개구부의 벽부 및 제1 표면 상에 유전체층(307, 317)이 형성될 수 있다. 그 후, 도 13에서 알 수 있는 바와 같이, 도전성 패드(304, 314)의 병치 표면들과 인터포저 비아의 대응하는 본딩 표면(326, 328) 사이의 예컨대 접착제와 같은 유전체 재료의 일부분이 제거될 수 있다. 도 14는 도전성 요소(336, 338)가 인터포저 비아의 대응하는 표면들과 접촉하는 상태로 형성된 후의 마이크로 전자 어셈블리를 예시하며, 이 도면에서는 예컨대 침적된 금속과 같은 침적된 도전성 재료가 도전성 패드(304, 314)의 표면과 이 표면과 병치되어 있는 인터포저 비아의 대응하는 표면(326, 328) 사이의 공간을 채운다.

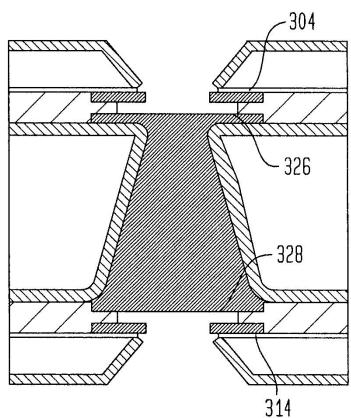

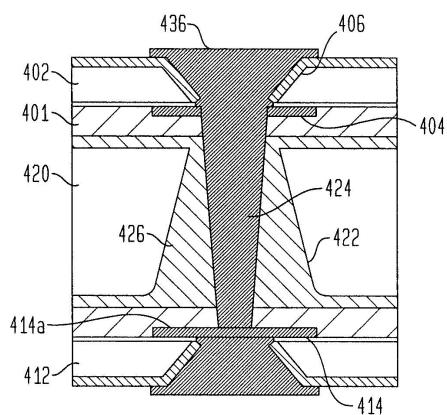

[0039] 도 15는, 인터포저 개구부를 통해 연장하는 도전성 요소(424)가, 인터포저 개구부(422)의 내부 표면의 윤곽을 따르지 않는 예컨대 원뿔대 형상(frusto-conical shape)과 같은 형상을 갖는, 다른 변형예를 예시하고 있다. 도 15에 도시된 구조의 제조 방법 또한 전술한 방법(도 4 내지 도 14)으로부터 변경될 수 있다. 이 경우, 인터포저(420)가 마이크로 전자 요소(402, 412)와 연결될 때, 인터포저는 유전체 재료(426)로 채워지는 제1 주요 표면과 제2 주요 표면 사이에 연장하는 개구부(422)를 가질 수 있다. 마이크로 전자 요소(402) 및 그 위의 도전성 패드(404)에 개구부(406)가 형성될 때, 도전성 패드(414)의 상부 표면(414a)이 개구부(406) 내에서 노출될 때까지, 접착제 또는 접합층(401)을 통과하여 그리고 유전체 재료(426)의 영역을 통과하여 재료 제거 공정이 지속된다. 그 후, 개구부(406)를 금속 또는 도전성 금속 화합물의 하나 이상의 층으로 채워, 마이크로 전자 요소(402) 및 인터포저(420)를 통해 연장하는 도전성 요소(436)를 형성할 수 있다.

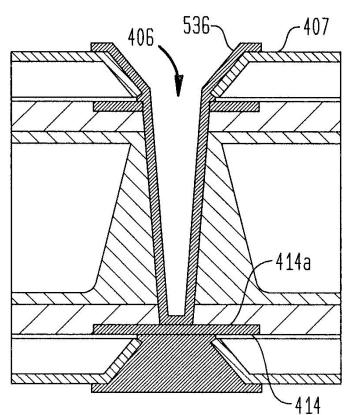

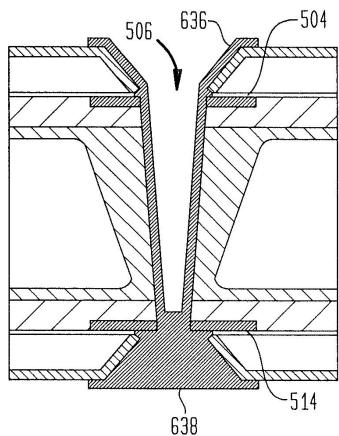

[0040] 도 16은 도 15에 도시된 구조의 변형예를 예시하며, 이 도면에서는 도전성 요소(536)가 개구부(406) 내의 유전체층(407)의 내부 표면을 라이닝하지만 개구부를 채우고 있지는 않은 공동 구조(hollow structure)로서 형성되어 있다. 도전성 요소(536)는 개구부(406) 내에 노출된 도전성 패드(414)의 상부 표면(414a)과 접촉한다. 도 17은 도전성 요소(636, 638)를 형성할 때에 도전성 요소가 서로 직접 접촉할 수 있도록 개구부(506)가 도전성 패드(504, 514) 양자의 두께를 관통하여 연장하는 또 다른 변형예를 예시하고 있다.

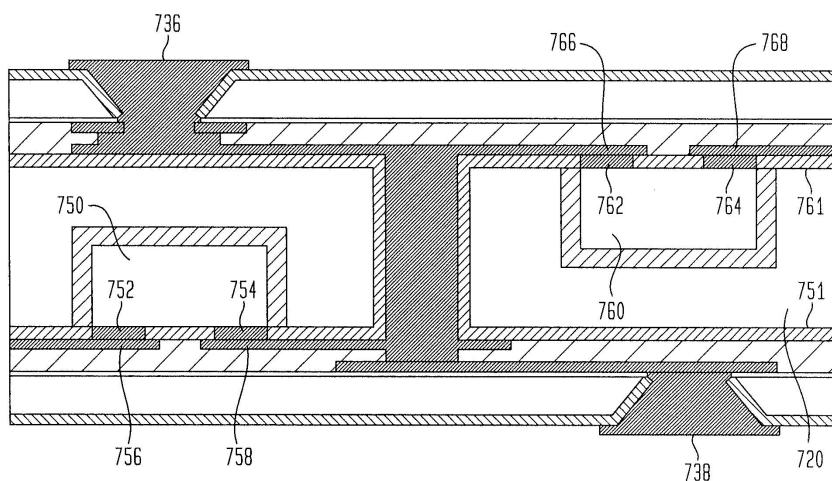

[0041] 도 18은 인터포저(720)가 하나 이상의 패시브 회로 요소를 구현하는 전술한 실시예(도 11)의 변형예를 예시한다. 예컨대, 인터포저는 인터포저(720)의 주요 표면(751)을 따라 연장하는 각각의 트레이스(756, 758)와 전기 접속되는 전극(752, 754)을 갖는 제1 커패시터(750)를 구현할 수 있다. 유사하게, 인터포저는 인터포저(720)의 주요 표면(761)을 따라 연장하는 각각의 트레이스(766, 768)와 전기 접속되는 전극(762, 764)을 갖는 제2 커패시터(760)를 구현할 수 있다. 몇몇 트레이스(758, 766)는, 추가의 도전성 요소(736, 738)를 통해, 어셈블리의 동작 시에 시간에 따라 변화하는 신호(time-varying signal)를 운반하는 도전성 패드에 접속될 수 있는 한편, 다른 트레이스(756, 768)는 어셈블리의 동작 시에 그라운드 또는 전원 공급 전압과 같은 기준 전위를 운반하는 하나 이상의 도전성 패드(도시하지 않음)에 접속될 수 있다.

[0042] 도 18에 도시된 실시예의 다른 변형예에서는, 패시브 회로 요소가 도 18에 도시된 바와 같이 배치되고 예컨대 도 18에 도시된 바와 같이 전기적 상호접속 배열을 갖는 인덕터, 저항기, 또는 기타 패시브 회로 요소 중의 하나 이상을 포함할 수 있다.

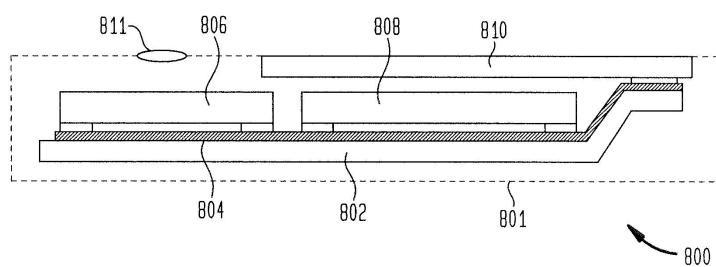

[0043] 마이크로 전자 어셈블리의 구조 및 제조와 이들을 하이-레벨 어셈블리에 통합하는 것은, 다음과 같은 동일자로 출원된 Oganesian 등의 공동 소유의 공동 계류 출원인 "STACKED MICROELECTRONIC ASSEMBLY WITH TSVS FORMED

IN STAGES AND CARRIER ABOVE CHIP"(미국 가특허 출원 번호 61/419,033; 대리인 문서 No. Tessera 3.8-619) 및 "STACKED MICROELECTRONIC ASSEMBLY WITH TSVS FORMED IN STAGES WITH PLURAL ACTIVE CHIPS"(미국 가특허 출원 번호 61/419,037; 대리인 문서 No. Tessera 3.8-632)과, 각각 2010년 7월 23일자로 출원된 이하의 미국 특허 출원 번호 12/842,717, 12/842,651, 12/842,612, 12/842,669, 12/842,692 및 12/842,587 중의 하나 이상에 기술된 구조 및 제조 단계를 포함할 수 있으며, 이러한 특허 출원 모두의 개시 내용은 참조에 의해 본 명세서에 원용된다. 전술한 구조는 우수한 3차원 상호접속 성능을 제공한다. 이들 성능은 어떠한 타입의 칩과도 이용될 수 있다. 단지 예로서, 전술한 바와 같은 구조에 이하의 조합의 칩이 포함될 수 있다: (i) 프로세서 및 프로세서와 함께 이용되는 메모리, (ii) 동일한 타입의 복수의 메모리칩, (iii) DRAM 및 SRAM과 같은 다양한 타입의 복수의 메모리칩, (iv) 이미지 센서 및 이 센서로부터의 이미지를 처리하기 위해 이용되는 이미지 프로세서, (v) ASIC(application-specific integrated circuit) 및 메모리. 전술한 구조는 다양한 전자 시스템의 구성에 활용될 수 있다. 예컨대, 본 발명의 추가의 실시예에 따른 시스템(800)은 전술한 바와 같은 구조물(806)과 함께 다른 전자 부품(808, 810)을 포함한다. 도시된 예에서, 부품 808은 반도체칩인 반면, 부품 810은 디스플레이 화면이지만, 다른 부품이 이용될 수 있다. 물론, 예시를 명확하게 하기 위해 도 19에는 단지 2개의 추가 부품만이 도시되어 있지만, 시스템은 이러한 부품의 어떠한 개수도 포함할 수 있다. 전술한 구조물(806)은 예컨대 도 1, 도 9, 도 10, 도 14, 도 15, 도 16 및 도 18과 관련하여 전술한 바와 같은 마이크로 전자 어셈블리(100)이어도 된다. 다른 변형에서는, 양자 모두가 제공될 수 있으며, 이러한 구조물이 어떠한 개수로도 이용될 수 있다. 구조물(806) 및 부품(808, 810)은 점선으로 개략적으로 나타낸 공통 하우징(801)에 탑재되며, 요구된 회로를 형성하기 위해 필요한 경우에는 서로 전기적으로 상호접속된다. 도시된 일례의 시스템에서, 시스템은 가요성 인쇄회로 기판과 같은 회로 패널(802)을 포함하며, 회로 패널은 부품들과 서로 상호접속하는 다수의 도전체(804)를 포함하며, 도 19에는 도전체 중의 하나만이 도시되어 있다. 그러나, 이것은 단지 예시를 위한 것이며, 전기 접속을 구성하기 위한 어떠한 적합한 구조도 이용될 수 있다. 하우징(801)은 예컨대 셀룰러 전화 또는 PDA(personal digital assistant)에 이용할 수 있는 타입의 휴대 가능한 하우징으로서 도시되어 있으며, 화면(810)은 하우징의 표면에 노출되어 있다. 구조물(806)이 이미징 칩과 같은 감광성 요소를 포함하는 경우에는, 구조물에 대해 광을 경로 배정하기 위해 렌즈(811) 또는 기타 광학 장치가 제공될 수 있다. 또한, 도 19에 도시된 간략화된 시스템은 단지 예시를 위한 것이며, 데스크탑 컴퓨터, 라우터 등과 같은 흔히 고정된 구조물로서 간주되는 시스템을 포함한 다른 시스템이 전술한 구조를 이용하여 구성될 수 있다.

[0044]

전술한 특징부의 이러한 변형 및 기타 변형과 조합을 본 발명으로부터 벗어나지 않고서도 활용할 수 있으므로, 바람직한 실시예에 대한 전술한 설명은 청구범위에 의해 정해지는 바와 같은 본 발명에 대한 한정으로서가 아니라 예시로서 간주되어야 한다.

[0045]

본 발명은 마이크로 전자 어셈블리 및 마이크로 전자 어셈블리의 제조 방법을 포함한 넓은 산업상 이용가능성을 갖지만, 이러한 것으로 한정되지는 않는다.

도면

도면1

도면1a

도면2

도면3

도면4

도면5

도면6

도면7

도면8

도면9

도면10

도면11

도면12

도면13

도면14

도면15

도면16

도면17

도면18

도면19