(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6076268号

(P6076268)

(45) 発行日 平成29年2月8日(2017.2.8)

(24) 登録日 平成29年1月20日(2017.1.20)

(51) Int.Cl.

H03M 1/10 (2006.01)

H03M 1/14 (2006.01)

F 1

H03M 1/10

H03M 1/14A

A

請求項の数 19 (全 15 頁)

(21) 出願番号 特願2013-555511 (P2013-555511)

(86) (22) 出願日 平成24年2月22日 (2012.2.22)

(65) 公表番号 特表2014-506773 (P2014-506773A)

(43) 公表日 平成26年3月17日 (2014.3.17)

(86) 國際出願番号 PCT/US2012/026022

(87) 國際公開番号 WO2012/116006

(87) 國際公開日 平成24年8月30日 (2012.8.30)

審査請求日 平成27年2月3日 (2015.2.3)

(31) 優先権主張番号 13/032,457

(32) 優先日 平成23年2月22日 (2011.2.22)

(33) 優先権主張国 米国(US)

(73) 特許権者 390020248

日本テキサス・インスツルメンツ株式会社

東京都新宿区西新宿六丁目24番1号

(73) 特許権者 507107291

テキサス インスツルメンツ インコーポ

レイテッド

アメリカ合衆国 テキサス州 75265

-5474 ダラス メイル ステイショ

ン 3999 ピーオーボックス 655

474

(74) 上記1名の代理人 100098497

弁理士 片寄 恒三

最終頁に続く

(54) 【発明の名称】パイプラインADC内部ステージ誤差キャリブレーション

## (57) 【特許請求の範囲】

## 【請求項1】

装置であって、

複数のパイプラインアナログデジタルコンバータ(ADC)であって、各パイプラインADCがアナログ入力信号を受け取るように適合され、各パイプラインADCが調節可能な伝達関数を有し、各パイプラインADCが、補償器と、シーケンスに互いに結合される複数のステージと、前記シーケンスの最終ステージに結合されるバックエンドサブADCとを含む、前記複数のパイプラインADCと、

各パイプラインADCに結合される調節回路であって、推定曖昧性を概してなくすように各パイプラインADCに対して前記伝達関数を調節し、デジタルアナログコンバータ(DAC)利得誤差を含む内部ステージ誤差を推定し、前記内部ステージ誤差を補償するため各パイプラインADCに対して前記補償器を調節する、前記調節回路と、

を含む、装置。

## 【請求項2】

請求項1に記載の装置であって、

各補償器が、

そのパイプラインADCの前記シーケンスの各ステージに結合されるデジタル加算器と、

前記バックエンドサブADCと前記デジタル加算器との間に結合され、前記調節回路に結合されるデジタル乗算器と、

10

20

を更に含み、

前記調節回路が、前記内部ステージ誤差を補償するように前記デジタル乗算器に対して利得を調節する、装置。

**【請求項 3】**

請求項 2 に記載の装置であって、

各パイプライン A D C のための各ステージが、

入力端子と、

前記入力端子に結合されるサブ A D C と、

前記サブ A D C に結合される D A C と、

前記入力端子と前記 D A C とに結合される相殺器と、

前記相殺器に結合される残存増幅器と、

を更に含む、装置。

**【請求項 4】**

請求項 3 に記載の装置であって、

各サブ A D C が、そのパイプライン A D C の前記伝達関数を調節するように、シフトされるように適合される複数のコンパレータを更に含む、装置。

**【請求項 5】**

請求項 4 に記載の装置であって、

前記調節回路が、前記パイプライン A D C の少なくとも 1 つの前記第 1 のステージの前記サブ A D C を最下位ビット ( L S B ) の 4 分の 1 シフトする、装置。

**【請求項 6】**

請求項 3 に記載の装置であって、

前記パイプライン A D C のための各ステージが、前記入力端子と前記サブ A D C との間に結合されるアナログ乗算器を更に含み、前記アナログ乗算器の利得が前記調節回路により調節される、装置。

**【請求項 7】**

第 1 のパイプライン A D C と第 2 のパイプライン A D C とを有する A D C をキャリブレーションするための方法であって、前記方法が、

前記第 1 のパイプライン A D C 内のステージの第 1 のセットの第 1 のステージの第 1 のサブ A D C のコンパレータの第 1 のセットを、前記第 1 のパイプライン A D C の第 1 の伝達関数を調節するために第 1 の量シフトする工程と、

前記第 2 のパイプライン A D C 内のステージの第 2 のセットの第 1 のステージの第 1 のサブ A D C のコンパレータの第 2 のセットを、前記第 2 のパイプライン A D C の第 2 の伝達関数を調節するために第 2 の量シフトする工程と、

コンパレータの前記第 1 のセットとコンパレータの前記第 2 のセットとがシフトされると前記 A D C に対する内部ステージ誤差を推定する工程であって、前記内部ステージ誤差が、内部ステージ誤差と D A C 利得誤差とのうちの少なくとも 1 つを含む、前記推定する工程と、

前記内部ステージ誤差を補償するために前記第 1 のパイプライン A D C の第 1 の補償器と前記第 2 のパイプライン A D C の第 2 の補償器とを調節する工程であって、前記第 1 の補償器が前記ステージの第 1 のセット内のステージの各々に結合され、前記第 2 の補償器が前記ステージの第 2 のセット内のステージの各々に結合される、前記調節する工程と、を含む、方法。

**【請求項 8】**

請求項 7 に記載の方法であって、

前記調節する工程が、

前記第 1 のパイプライン A D C の第 1 のデジタル乗算器の第 1 の利得を調節することと、

前記第 1 のパイプライン A D C の第 1 のバックエンドサブ A D C からのデジタル出力を前記第 1 の利得で乗算することと、

10

20

30

40

50

前記第2のパイプラインA D Cの各ステージに対する及び前記第1のデジタル乗算器に対するデジタル出力を共に加算することと、

前記第2のパイプラインA D Cの第2のデジタル乗算器の第2の利得を調節することと、

前記第2のパイプラインA D Cの第2のバックエンドサブA D Cからのデジタル出力を前記第2の利得で乗算することと、

前記第2のパイプラインA D Cの各ステージに対する及び前記第2のデジタル乗算器に対するデジタル出力を共に加算することと、

を更に含む、方法。

#### 【請求項9】

10

請求項8に記載の方法であって、

前記方法が、

前記第1及び第2のパイプラインA D C間の利得ミスマッチを推定することと、

前記第1及び第2のパイプラインA D C間のオフセットミスマッチを推定することと、

前記利得及びオフセットミスマッチを補償することと、

を更に含む、方法。

#### 【請求項10】

請求項9に記載の方法であって、

前記第1及び第2の量がL S Bの4分の1である、方法。

#### 【請求項11】

20

装置であって、

第1の伝達関数を有する第1のパイプラインA D Cであって、

アナログ入力信号を受け取るように適合される第1のトラックアンドホールド(T/H)回路と、

第1のシーケンスに互いに結合されるステージの第1のセットであって、前記第1のシーケンスの第1のステージが前記第1のT/H回路に結合され、前記ステージの第1のセットからの前記ステージの少なくとも1つが第1の伝達関数を調節するように調節可能である、前記ステージの第1のセットと、

前記第1のシーケンスの最終ステージに結合される第1のバックエンドサブA D Cと、

前記ステージの第1のセットから各ステージと前記第1のバックエンドサブA D Cとに結合される第1の補償器と、

を有する、前記第1のパイプラインA D Cと、

第2の伝達関数を有する第2のパイプラインA D Cであって、

前記アナログ入力信号を受け取るように適合される第2のT/H回路と、

第2のシーケンスに互いに結合されるステージの第2のセットであって、前記第2のシーケンスの第1のステージが前記第2のT/H回路に結合され、前記ステージの第2のセットからの前記ステージの少なくとも1つが、第2の伝達関数を調節するように調節可能である、前記ステージの第2のセットと、

前記第2のシーケンスの最終ステージに結合される第2のバックエンドサブA D Cと、

前記ステージの第2のセットから各ステージと前記第2のバックエンドサブA D Cとに結合される第2の補償器と、

を有する、前記第2のパイプラインA D Cと、

前記第1及び第2の伝達関数を調節するように前記第1及び第2のパイプラインA D Cに結合され、且つ、前記第1及び第2の補償器に結合される調節回路であって、内部ステージ利得誤差とD A C利得誤差とのうちの少なくとも1つを含む内部ステージ誤差を推定し、前記内部ステージ誤差を補償するように前記第1及び第2の補償器を調節する、前記調節回路と、

を含む、装置。

#### 【請求項12】

請求項11に記載の装置であって、

50

前記第1の補償器が、

前記ステージの第1のセットから各ステージに結合される第1のデジタル加算器と、

前記第1のバックエンドサブA D Cと前記第1のデジタル加算器との間に結合され、前

記調節回路に結合される、第1のデジタル乗算器と、

を更に含む、装置。

## 【請求項13】

請求項12に記載の装置であって、

前記第2の補償器が、

前記ステージの第2のセットから各ステージに結合される第2のデジタル加算器と、

前記第2のバックエンドサブA D Cと前記第2のデジタル加算器との間に結合され、前 10

記調節回路に結合される、第2のデジタル乗算器と、

を更に含む、装置。

## 【請求項14】

請求項13に記載の装置であって、

前記ステージの第1及び第2のセットからの各ステージが、

入力端子と、

前記入力端子に結合されるサブA D Cと、

前記サブA D Cに結合されるD A Cと、

前記入力端子と前記D A Cとに結合される相殺器と、

前記相殺器に結合される残存增幅器と、 20

を更に含む。

## 【請求項15】

請求項14に記載の装置であって、

各サブA D Cが複数のコンパレータを有するフラッシュA D Cを更に含み、前記コンパ

レータの各々がシフトされるように適合される、装置。

## 【請求項16】

請求項15に記載の装置であって、

前記調節回路が、前記パイプラインA D Cの少なくとも1つの前記第1のステージの前

記サブA D CをL S Bの4分の1シフトする、装置。

## 【請求項17】

請求項16に記載の装置であって、

前記第1及び第2のデジタル加算器に結合される出力回路を更に含む、装置。

## 【請求項18】

請求項17に記載の装置であって、

前記第1のパイプラインA D Cが、前記第1のT / H回路と前記ステージの第1のセッ

トの前記第1のステージとの間に結合される第1のミスマッチ補償器を更に含み、

前記第2のパイプラインA D Cが、前記第2のT / H回路と前記ステージの第2のセッ

トの前記第1のステージとの間に結合される第2のミスマッチ補償器を更に含み、

前記調節回路が、前記第1及び第2のパイプラインA D C間の利得及びオフセットのミ

スマッチを推定し、前記第1及び第2のミスマッチ補償器を調節する、装置。 40

## 【請求項19】

請求項18に記載の装置であって、

前記調節回路が、最小二乗平均(L M S)を用いて、前記内部ステージ誤差と前記利得

ミスマッチと前記オフセットミスマッチとを推定する、装置。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本願は、概してパイプラインアナログデジタルコンバータ(A D C)に関し、更に特定

して言えば、各ステージにおいて内部ステージ(inter-stage)利得誤差又はデジタルア 50

ナログコンバータ（D A C）利得誤差を補償するため分割（split）A D Cアーキテクチャを用いるパイプラインA D Cに関連する。

#### 【背景技術】

##### 【0 0 0 2】

パイプラインA D Cは、（例えば）高性能デジタル通信システム、波形取得、及び計測において幅広く用いられてきている。最新のパイプラインA D Cの速度は1 0 0 M S P Sを超えるが、解像度は概して、回路非理想値（即ち、キャパシタミスマッチ及び有限演算増幅器（オペアンプ）利得など）に起因する内部ステージ利得誤差及び／又はD A C利得誤差により制限される。そのため、1 2 ビットより高い解像度の大抵のパイプラインA D Cは通常、何らかの線形性向上手法を必要とする。

10

##### 【0 0 0 3】

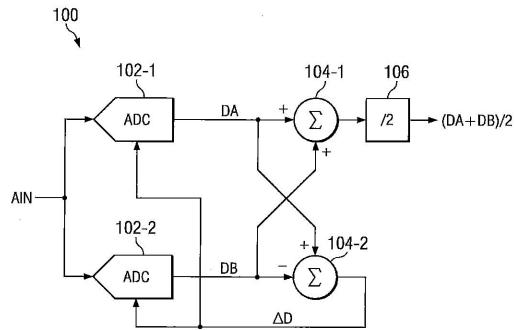

バックグラウンドキャリブレーションを実行するために用いることができる、分割A D Cアーキテクチャとして知られているアーキテクチャもあり、図1に移ると、分割A D Cアーキテクチャを用いる従来のA D C 1 0 0の一例を見ることができる。このA D C 1 0 0は、チャネル又はA D C 1 0 2 - 1 及び1 0 2 - 2、加算器1 0 4 - 1 及び1 0 4 - 2、及び分周器1 0 6を概して含む。典型的に、A D C 1 0 2 - 1 及び1 0 2 - 2は、同じ全般的構造を有し、オペレーションにおいて、ほぼ同時にデータ変換を実行するように（それぞれ、デジタル出力信号D A及びD Bを生成する）同じアナログ入力信号A I Nを受け取る。加算器1 0 4 - 2（これは相殺器として動作する）により生成される、これらの出力信号D A及びD B間の差Dは、A D C 1 0 2 - 1 及び1 0 2 - 2をキャリブレーションするために用いることができ、一方、出力信号D A及びD Bの平均（加算器1 0 4 - 1 及び分周器1 0 6により生成される）は、A D C 1 0 0のデジタル出力に対応し得る。しかし、A D C 1 0 2 - 1 及び1 0 2 - 2がパイプラインA D Cであるとき、内部ステージ利得誤差及び／又はD A C利得誤差を補償することが困難である。

20

##### 【0 0 0 4】

従って、パイプラインA D Cにおいて内部ステージ利得誤差及び／又はD A C利得誤差を補償する方法及び／又は装置が求められている。

##### 【0 0 0 5】

従来の回路の幾つかの例は下記文献に記載されている。

【非特許文献1】Park et al, "A 10-b 100MS/s CMOS pipelined ADC with 1.8V power supply," Proc. ISSCC Digest Technical Papers, pp. 130-131, Feb. 2001

30

【非特許文献2】McNeill et al, "Split ADC Architecture for Deterministic Digital Background Calibration of a 16-bit 1-MS/s ADC," IEEE Journal of Solid State Circuits, vol. 40, pp. 2437-2445, Dec. 2005

【非特許文献3】Li et al, "Background calibration techniques for multistage pipelined ADCs with digital redundancy," IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process., vol. 50, no. 9, pp. 531-538, Sep. 2003

##### 【特許文献1】米国特許番号第6,081,215号

##### 【特許文献2】米国特許番号第6,445,317号

##### 【特許文献3】米国特許番号第6,452,518号

40

##### 【特許文献4】米国特許番号第7,312,734号

##### 【特許文献5】米国特許公開番号2006/0176197

#### 【発明の概要】

##### 【0 0 0 6】

従って、例示の一実施例は或る装置を提供する。この装置は、複数のパイプラインアナログデジタルコンバータ（A D C）であって、各パイプラインA D Cがアナログ入力信号を受け取るように適合され、各パイプラインA D Cが調節可能な伝達関数を有し、各パイプラインA D Cが補償器を含む、複数のパイプラインA D C、及び各パイプラインA D Cに結合される調節回路を含む。調節回路は、推定曖昧性を概してなくすように各パイプラインA D Cに対し伝達関数を調節する。調節回路は、少なくとも一つの内部ステージ利得

50

誤差及びデジタルアナログコンバータ（D A C）利得誤差を含む内部ステージ誤差を推定し、内部ステージ誤差を補償するため各パイプラインA D Cに対し補償器を調節する。

#### 【0007】

例示の一実施例において、各パイプラインA D Cが、シーケンスに亘りに結合される複数のステージ、及びシーケンスの最終ステージに結合されるバックエンドサブA D Cを更に含む。

#### 【0008】

例示の一実施例において、各補償器が、そのパイプラインA D Cのシーケンスの各ステージに結合されるデジタル加算器、及びバックエンドサブA D Cとデジタル加算器との間に結合され、且つ、調節回路に結合されるデジタル乗算器を更に含む。調節回路は、内部ステージ誤差を補償するようにデジタル乗算器に対し利得を調節する。

10

#### 【0009】

例示の一実施例において、各パイプラインA D Cのための各ステージが、入力端子、入力端子に結合されるサブA D C、サブA D Cに結合されるD A C、入力端子及びD A Cに結合される相殺器、及び相殺器に結合される残存増幅器を更に含む。

#### 【0010】

例示の一実施例において、各サブA D Cが、そのパイプラインA D Cの伝達関数を調節するようにシフトされるように適合される複数のコンパレータを更に含む。

#### 【0011】

例示の一実施例において、調節回路は、パイプラインA D Cの少なくとも1つの第1のステージのサブA D Cを最下位ビット（L S B）の4分の1シフトする。

20

#### 【0012】

例示の一実施例において、パイプラインA D Cのための各ステージが、入力端子とサブA D Cとの間に結合されるアナログ乗算器を更に含み、アナログ乗算器の利得が調節回路により調節される。

#### 【0013】

例示の一実施例において、第1のパイプラインA D C及び第2のパイプラインA D Cを有するA D Cをキャリブレーションするための方法が提供される。この方法は、第1のパイプラインA D Cの第1のステージの第1のサブA D Cのコンパレータの第1のセットを、第1のパイプラインA D Cの第1の伝達関数を調節するため第1の量シフトする工程、第2のパイプラインA D Cの第1のステージ第1のサブA D Cのコンパレータの第2のセットを、第2のパイプラインA D Cの第2の伝達関数を調節するため第2の量シフトする工程、コンパレータの第1のセット及びコンパレータの第2のセットがシフトされるとA D Cに対する内部ステージ誤差を推定する工程であって、内部ステージ誤差が、内部ステージ誤差及びD A C利得誤差のうち少なくとも一つを含むこと、及び内部ステージ誤差を補償するため第1のパイプラインA D Cの第1の補償器及び第2のパイプラインA D Cの第2の補償器を調節する工程を含む。

30

#### 【0014】

例示の一実施例において、調節する工程は、第1のパイプラインA D Cの第1のデジタル乗算器の第1の利得を調節すること、第1のパイプラインA D Cの第1のバックエンドサブA D Cからのデジタル出力を第1の利得で乗算すること、第2のパイプラインA D Cの各ステージに対する及び第1のデジタル乗算器に対するデジタル出力を共に加算すること、第2のパイプラインA D Cの第2のデジタル乗算器の第2の利得を調節すること、第2のパイプラインA D Cの第2のバックエンドサブA D Cからのデジタル出力を第2の利得で乗算すること、及び第2のパイプラインA D Cの各ステージに対する及び第2のデジタル乗算器に対するデジタル出力を共に加算することを更に含む。

40

#### 【0015】

例示の一実施例において、この方法は、第1及び第2のパイプラインA D C間の利得ミスマッチを推定すること、第1及び第2のパイプラインA D C間のオフセットミスマッチを推定すること、及び利得及びオフセットミスマッチを補償することを更に含む。

50

**【0016】**

例示の一実施例において、第1及び第2の量が LSB の4分の1である。

**【0017】**

例示の一実施例において或る装置が提供される。この装置は、第1の伝達関数を有する第1のパイプラインADC、第2の伝達関数を有する第2のパイプラインADC、並びに、第1及び第2の伝達関数を調節するように第1及び第2のパイプラインADCに結合され、且つ、第1及び第2の補償器に結合される調節回路を含む。第1のパイプラインADCは、アナログ入力信号を受け取るように適合される第1のトラックアンドホールド(T/H)回路と、第1のシーケンスに互いに結合されるステージの第1のセットであって、第1のシーケンスの第1のステージが第1のT/H回路に結合され、ステージの第1のセットからのステージの少なくとも1つが第1の伝達関数を調節するように調節可能である、ステージの第1のセットと、第1のシーケンスの最終ステージに結合される第1のバックエンドサブADCと、ステージの第1のセット及び第1のバックエンドサブADCから各ステージに結合される第1の補償器とを有する。第2のパイプラインADCは、アナログ入力信号を受け取るように適合される第2のT/H回路と、第2のシーケンスに互いに結合されるステージの第2のセットであって、第2のシーケンスの第1のステージが第2のT/H回路に結合され、ステージの第2のセットからのステージの少なくとも1つが、第2の伝達関数を調節するように調節可能である、ステージの第2のセットと、第2のシーケンスの最終ステージに結合される第2のバックエンドサブADCと、ステージの第2のセット及び第2のバックエンドサブADCから各ステージに結合される第2の補償器とを有する。調節回路は、内部ステージ利得誤差及びDAC利得誤差のうち少なくとも一つを含む内部ステージ誤差を推定し、内部ステージ誤差を補償するように第1及び第2の補償器を調節する。

10

**【0018】**

例示の一実施例において、第1の補償器は、ステージの第1のセットから各ステージに結合される第1のデジタル加算器、及び第1のバックエンドサブADCと第1のデジタル加算器との間に結合され、且つ、調節回路に結合される第1のデジタル乗算器を更に含む。

**【0019】**

例示の一実施例において、第1の補償器は、ステージの第2のセットから各ステージに結合される第2のデジタル加算器、及び第2のバックエンドサブADCと第2のデジタル加算器との間に結合され、且つ、調節回路に結合される第1のデジタル乗算器を更に含む。

30

**【0020】**

例示の一実施例において、ステージの第1及び第2のセットからの各ステージが、入力端子、入力端子に結合されるサブADC、サブADCに結合されるDAC、入力端子及びDACに結合される相殺器、及び相殺器に結合される残存増幅器を更に含む。

**【0021】**

例示の一実施例において、各サブADCが、複数のコンパレータを有するフラッシュADCを更に含み、コンパレータの各々がシフトされるように適合される。

40

**【0022】**

例示の一実施例において、調節回路は、パイプラインADCの少なくとも1つの第1のステージのサブADCを最下位ビット(LSB)の4分の1シフトする。

**【0023】**

例示の一実施例に従って、この装置は、第1及び第2のデジタル加算器に結合される出力回路を更に含む。

**【0024】**

例示の一実施例において、第1のパイプラインADCは、第1のT/H回路とステージの第1のセットの第1のステージとの間に結合される第1のミスマッチ補償器を更に含み、第2のパイプラインADCは、第2のT/H回路とステージの第2のセットの第1のス

50

ステージとの間に結合される第2のミスマッチ補償器を更に含み、調節回路は、第1及び第2のパイプラインADC間の利得及びオフセットミスマッチを推定し、第1及び第2のミスマッチ回路を調節する。

**【0025】**

例示の一実施例において、調節回路は、最小二乗平均( LMS )アルゴリズムを用いて、内部ステージ誤差、利得ミスマッチ、及びオフセットミスマッチを推定する。

**【図面の簡単な説明】**

**【0026】**

【図1】図1は従来のADCの例を示す。

**【0027】**

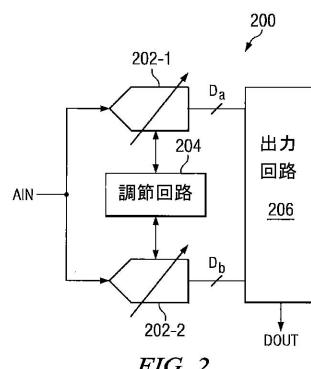

【図2】図2は、例示の一実施例に従ったADCの例を示す。

**【0028】**

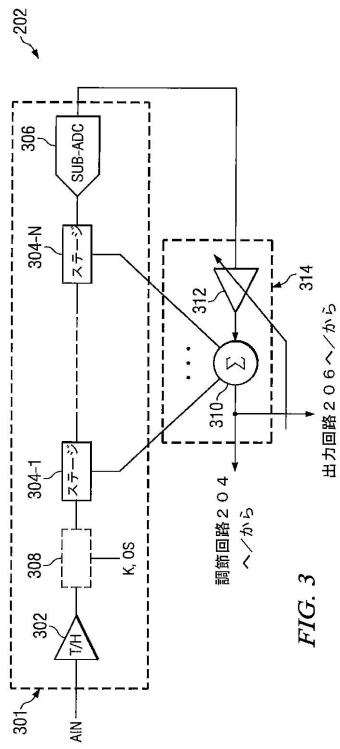

【図3】図3は、図2のパイプラインADCの例を示す。

**【0029】**

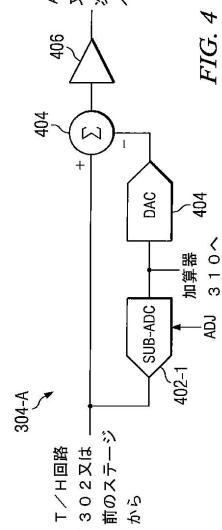

【図4】図4は、図3のステージの例を示す。

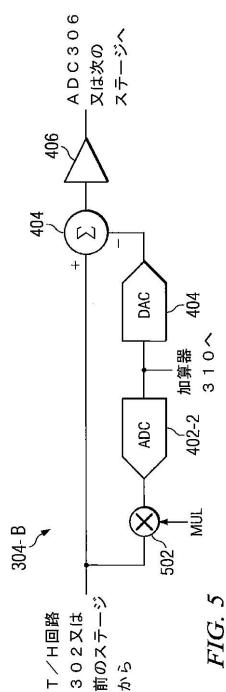

【図5】図5は、図3のステージの例を示す。

**【0030】**

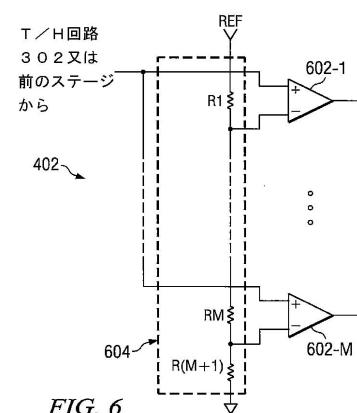

【図6】図6は、図4及び図5のサブADCの例を示す。

**【0031】**

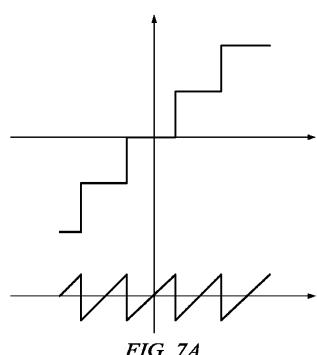

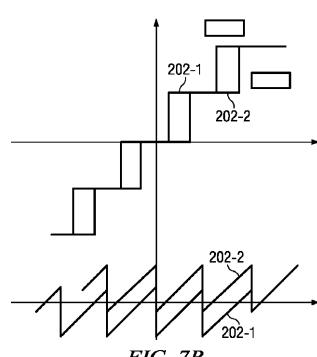

【図7A】図7Aは、図2のパイプラインADCの伝達関数に対する調節を示す。

10

【図7B】図7Bは、図2のパイプラインADCの伝達関数に対する調節を示す。

**【0032】**

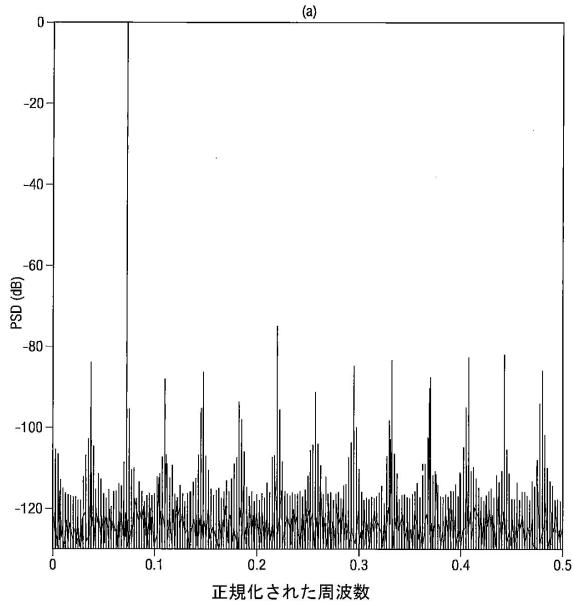

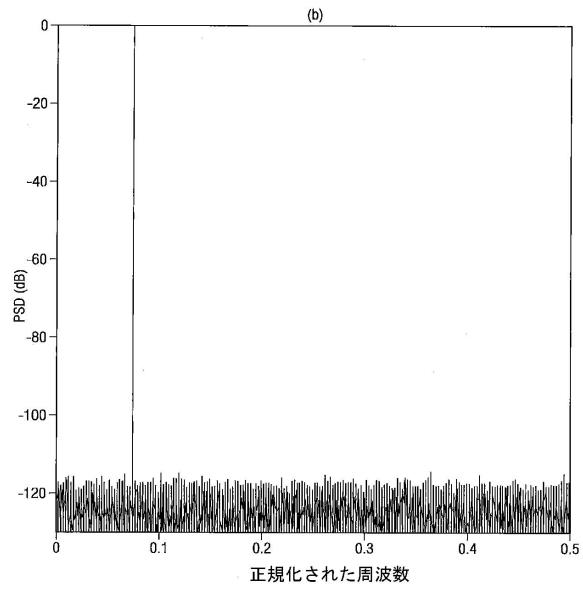

【図8A】図8Aは、キャリブレーション有りの図2のADCのスプリアスフリーダイナミックレンジ(SFDR)を示す。

20

【図8B】図8Bは、キャリブレーションなしの図2のADCのスプリアスフリーダイナミックレンジ(SFDR)を示す。

**【0033】**

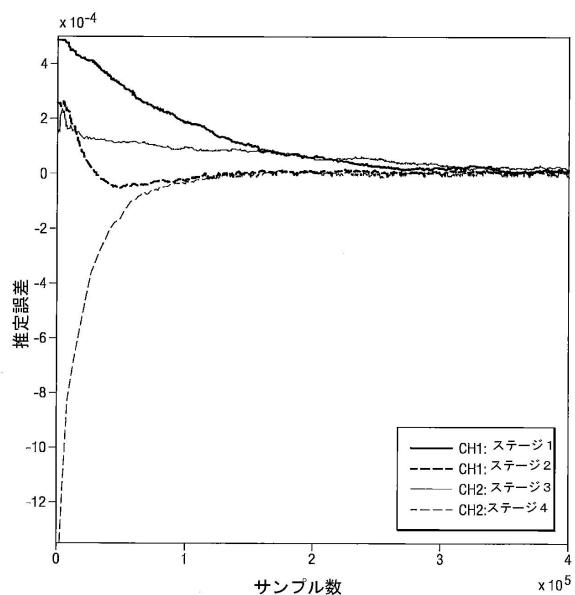

【図9】図9は、図2ADCにより用いられるキャリブレーション方法の収束を示す。

**【発明を実施するための形態】**

**【0034】**

30

図2は、パイプラインADC202-1及び202-2、調節回路204、及び出力回路206を概して含むADC200の例を図示する。ここでは、簡潔にするため2つのパイプラインADCが示されているが、付加的なパイプラインADC又はADCツリーが用いられてもよい。オペレーションにおいて、ADC202-1及び202-2の各々は、概して同じ構造を有し、アナログ入力信号AINを受け取り、出力回路206(これはこれらの信号を平均化し得、デジタル補正を実行することができる)に対し出力信号Da及びDbを生成する。調節回路204は、内部ステージ利得誤差及び/又はDAC利得誤差(ADC202-1及び202-2内)及び利得/オフセットミスマッチ(ADC202-1及び202-2間)を補償するように、ADC202-1及び202-2に調節を提供する。

40

**【0035】**

図3において、各パイプラインADC202-1及び202-2(後述では、図3の202)を更に詳細に見ることができる。図示するように、パイプラインADC202は、補償器314(これは概してデジタル乗算器又はデジタル利得ブロック312及び加算器又は結合器(combiner)310を含む)及びパイプライン301(これはトラックアンドホールド(T/H)回路302、ミスマッチ補償器308、シーケンスに共に結合されるステージ304-1~304-Nのセット、及びバックエンドサブADC306を含む)を概して含む。オペレーションにおいて、調節回路206は、加算器310(これはステージ304-1~304-N及びバックエンドサブADC306からのデジタル出力を組み合わせる)からの出力を受け取り、デジタル乗算器312(これは、加算器310とバ

50

ックエンドサブADC306との間に結合される)に対して調節を実行すること(即ち、利得を調節すること)により内部ステージ利得誤差及び/又はDAC利得誤差を補償することができる。しかし、これらの状況下では、概して正確な推定を妨げる推定曇昧性が存在する。

#### 【0036】

簡潔にするため、1つのステージ(即ち、304-1)及びバックエンドサブADC(即ち、306)があると仮定することができる。出力信号Da及びDbは下記となり得る。

$$(1) \quad D_a = D_{1,a} + g_a D_{2,a}$$

$$(2) \quad D_b = D_{1,b} + g_b D_{2,b}$$

ここで、 $D_{1,a}$ 及び $D_{1,b}$ はステージ(即ち304-1)からの出力であり、 $D_{2,a}$ 及び $D_{2,b}$ はバックエンドサブADC(即ち、306)からの出力であり、 $g_a$ 及び $g_b$ はデジタル乗算器(即ち、312)の利得である。ステージ(即ち、304-1)からの出力 $D_{1,a}$ 及び $D_{1,b}$ は同じであるべきであり、そのため、差Dは下記となり得る。

(3)  $D = D_a - D_b = g_a D_{2,a} - g_b D_{2,b}$

デジタル乗算器(即ち、306)に対する最適な解は次の通りである。

#### 【数1】

$$(4) \quad g_a^{opt} = \frac{1}{G_{1a}}$$

$$(5) \quad g_b^{opt} = \frac{1}{G_{1b}}$$

ここで、 $G_{1,a}$ 及び $G_{1,b}$ は内部ステージ利得及び/又はDAC利得誤差を示し、そのため、差が最小二乗平均(LMS)アルゴリズムを用いて最小化されるとき、変数の数がシステムの式の数を超えるため推定曇昧性がある。即ち、推定曇昧性は下記の通りである。

#### 【数2】

$$(6) \quad \hat{g}_a = \alpha g_a^{opt}$$

$$(7) \quad \hat{g}_b = \alpha g_b^{opt}$$

この推定曇昧性に対処するため、調節回路204は、パイプラインADC(即ち、図2の204-1及び204-2)の各々の伝達関数を調節することができ、これらの伝達関数を調節するための方式が幾つかある。

#### 【0037】

図4及び図5は、調節回路204により調節され得るステージ304-1~304-N(これ以降では、それぞれ、図4及び図5で304-A及び304-B)の一つの例を図示する。ステージ304-Aは、サブADC402-1、DAC404、加算器408(これは相殺器として動作する)、及び残存増幅器406を概して含み、ステージ304-Bは、サブADC402-2、及びアナログ乗算器502を含む。典型的に、(T/H回

10

20

30

40

50

路 3 0 2 又は前のステージのいずれかからの ) アナログ信号は、サブ A D C 4 0 2 - 1 ( 又は 4 0 2 - 2 ) によってデジタル信号に変換される。このデジタル信号は加算器 3 1 0 及び D A C 4 0 4 に提供される。D A C 4 0 4 はこの信号をアナログ信号に変換し、D A C 4 0 4 ( これは D A C 利得を導入し得る ) からのアナログ信号は、加算器 4 0 8 により T / H 回路 3 0 2 又は前のステージからのアナログ信号から減算されて、残存信号を生成する。この残存信号は残存增幅器 4 0 6 ( これは内部ステージ利得を導入し得る ) により増幅される。

#### 【 0 0 3 8 】

図 6 に示すように、サブ A D C 4 0 2 - 1 又は 4 0 2 - 2 ( 後述では、4 0 2 ) は、種々のタイプの A D C の一つであってよいが、典型的には、( 図示するような ) フラッシュ A D C である。このフラッシュ A D C 4 0 2 は、分圧器 6 0 4 ( これは概して、互いに直列に結合されるレジスタ R 1 ~ R ( M + 1 ) を含む ) 及びコンパレータ 6 0 2 - 1 ~ 6 0 2 - M を概して含む。概して、各コンパレータ 6 0 2 - 1 ~ 6 0 2 - M は、分圧器 6 0 4 に結合され、デジタル出力信号を生成するためアナログ入力信号を受け取る。

#### 【 0 0 3 9 】

図 4 に戻ると、伝達関数に対する調節は、サブ A D C 4 0 2 - 1 に対し直に調節することにより達成され得る。好ましくは、伝達関数に対する調節は、コンパレータ 6 0 2 - 1 ~ 6 0 2 - M をサブ A D C 4 0 2 - 1 内で調節信号 A D J でシフトさせること ( 即ち、基準電圧 R E F をシフトすること ) により実行され得る。通常、パイプライン A D C 2 0 2 - 1 及び 2 0 2 - 2 の各々に対する伝達関数は、( 図 7 A に図示するように ) 合致すると考えられるが、上述の推定曖昧性を解決するため、パイプライン A D C の各々の 1 つ又は複数のステージに対するコンパレータ 6 0 2 - 1 ~ 6 0 2 - M は、所定の量シフトされ得る。例えば、図 7 B に示すように、パイプライン A D C 2 0 2 - 1 に対する第 1 のステージ ( 即ち、3 0 4 - 1 ) のためのコンパレータ 6 0 2 - 1 ~ 6 0 2 - M は、最下位ビット ( L S B ) の + 4 分の 1 シフトされ得、一方、パイプライン A D C 2 0 2 - 2 に対する第 1 のステージ ( 即ち、3 0 4 - 1 ) のためのコンパレータ 6 0 2 - 1 ~ 6 0 2 - M は、L S B の - 4 分の 1 シフトされ得る。しかしながら、これを行うことにより、デジタル冗長性における解像度が幾らか失われる。

#### 【 0 0 4 0 】

代替として、図 5 に示すように、T / H 回路 3 0 2 から又は前のステージからのアナログ信号は、変換される前に修正され得る。図示するように、乗算器 5 0 2 が信号経路に含まれ得る。調節回路 2 0 6 は、上述の A D C 4 0 2 - 1 を直接的に調節するのと実質的に同一の目的を達成するため、利得 M U L ( 又は代替として信号 ) を提供することができる。

#### 【 0 0 4 1 】

マルチパイプライン A D C ( 即ち、A D C 2 0 0 ) では、チャネル間の利得及びオフセットミスマッチがあることにも注意されたい。これらのミスマッチは、乗算器 ( 即ち、3 1 2 ) が実質的に最適であるように調節されるとき、概してゼロとならない。そのため、推定は、利得及びオフセットミスマッチを考慮すべきである。ここでも、( 説明を簡潔にするため ) 各々 2 つのステージを有する ( 図 2 に図示するような ) 2 つのパイプライン A D C があり、ここで、K<sub>a</sub> 及び K<sub>b</sub> が ( それぞれ ) パイプライン A D C 2 0 2 - 1 及び 2 0 2 - 2 に対する全体的な利得を示し、O S<sub>a</sub> 及び O S<sub>b</sub> が ( それぞれ ) パイプライン A D C 2 0 2 - 1 及び 2 0 2 - 2 に対するオフセットを示し、D<sub>0</sub> が理想的な出力であると仮定する。内部ステージ利得及び D A C 利得誤差を無視すると、出力信号 D<sub>a</sub> 及び D<sub>b</sub> は下記となり得る。

$$( 8 ) \quad D_a = K_a D_0 + O S_a$$

$$( 9 ) \quad D_b = K_b D_0 + O S_b$$

重み付された差 D は、上記式 ( 8 ) 及び ( 9 ) を用いて次のように定義することができる。

$$( 10 ) \quad D = K D_a - D_b + O S = ( K K_a - K_b ) D_0 + ( O S + O S_a - O S_b )$$

10

20

30

40

50

<sup>b</sup>)

ここで、K 及び OS はミスマッチ補償器 308 に対する利得及びオフセット調節である。その結果のコスト関数 J は下記となり得る。

$$(11) \quad J = D^2$$

ミスマッチ補償器に対する利得調節 K 及びオフセット調節 OS は、下記のように収束する。

$$(12) \quad K = K_b / K_a$$

$$(13) \quad OS = OS_b - OS_a$$

コスト関数 J の最小化はゼロとなり得、利得及びオフセットミスマッチが補償され得ることを示す。このコスト関数を適応性推定（これは内部ステージ利得誤差及び / 又は DAC 利得誤差に対する推定を含む）に展開すると、出力信号  $D_a$  及び  $D_b$  は下記となる。

$$(14) \quad D_a = K_a (D_{1,a} + g_a D_{2,a}) + OS_a$$

$$(15) \quad D_b = K_b (D_{1,b} + g_a D_{2,b}) + OS_b$$

その後、LMS アルゴリズムが（式（14）及び（15）の出力信号  $D_a$  及び  $D_b$  を用いる上記式（11）の）コスト関数 J に適用され得、下記式となる。

【数 3】

$$(16) \quad \hat{g}_a(k+1) = \hat{g}_a(k) - \mu_a \nabla J_{g_a}$$

10

$$(17) \quad \hat{g}_b(k+1) = \hat{g}_b(k) - \mu_b \nabla J_{g_b}$$

20

$$(18) \quad \hat{K}(k+1) = \hat{K}(k) - \mu_K \nabla J_K$$

$$(19) \quad \hat{OS}(k+1) = \hat{OS}(k) - \mu_{OS} \nabla J_{OS}$$

30

そのため、上記式（16）～（19）を用いて、調節回路 204 は、ほぼ同時に内部ステージ利得誤差、DAC 利得誤差及び利得 / オフセットミスマッチを推定（及び補償）することができる。

【0042】

図 8A～図 9 は、幾つかの例示シミュレーションの結果を示す。この例では、パイプライン ADC 202-1 及び 202-2 の各々が、4 つのステージを有する 16 ビットパイプライン ADC である。この例のパイプラインにおける 4 つのステージの各々は、それぞれ、各ステージに対し、4、5、5、及び 5 ビットを有する。これに対応して、最適な内部ステージ利得は、第 1 及び第 2 のステージでは 8 及び 16 である。この例では、両方のパイプラインが最初の 2 ステージにおいて利得誤差を有すると仮定し、パイプライン ADC 202-1 及び 202-2 に対して実装される利得を下記表 1 に示す。

【表 1】

Table 1

|        | パイプライン ADC 202-1 | パイプライン ADC 202-2 |

|--------|------------------|------------------|

| ステージ 1 | 8.0092           | 7.9077           |

| ステージ 2 | 16.1278          | 16.0653          |

40

50

チャネルミスマッチをモデル化するため、0.05%利得ミスマッチ及び10 LSBオフセットミスマッチが導入された。図8A及び図8Bにおいて、キャリブレーション前後のS F D Rが示されており、S F D Rは74 dBから113 dBまで改善されることが分かる。また、パイプラインADC 202-1及び202-2の各々に対するデジタル乗算器（即ち、312）の収束曲線を図9において見ることができ、4分の1 LSBシフト（これは一層長い収束時間となる）の代わりに1/10 LSBシフトを用いるときの約40,000個のサンプルでの収束を示し、これは、任意の他の既知のアプローチより約100倍速く、（幾つかのエネルギーフリーアプローチとは異なり）制約がない。

## 【0043】

本発明に関連する技術に習熟した者であれば、本発明の特許請求の範囲内で、説明した例示の実施例に変形が成され得ること、及び他の実施例を実装し得ることが分かるであろう。

10

【図7A】

FIG. 7A

【図7B】

FIG. 7B

【図1】

FIG. 1

(従来技術)

【図2】

FIG. 2

【図3】

【図4】

【図5】

【図6】

【図 8 A】

FIG. 8A

【図 8 B】

FIG. 8B

【図 9】

FIG. 9

---

フロントページの続き

(72)発明者 クン シー

アメリカ合衆国 75081 テキサス州 リチャードソン, エイピーティ 1030, バッキンガム ロード 540

(72)発明者 チャールズ セストック

アメリカ合衆国 75251 テキサス州 ダラス, エイピーティ 11-205, チャーチル ウェイ 7900

(72)発明者 パトリック サターザデー

アメリカ合衆国 75001 テキサス州 アディソン, エイピーティ 2402 スペクトラム ドライブ 15695

(72)発明者 アーサー ジェイ レドファーン

アメリカ合衆国 75025 テキサス州 プラノ, グランド メサ ドライブ 3448

審査官 栗栖 正和

(56)参考文献 特開2010-035140 (JP, A)

米国特許出願公開第2006/0176197 (US, A1)

特開2002-368618 (JP, A)

特開2001-313566 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H03M 1/00 - 1/88