(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4389325号

(P4389325)

(45) 発行日 平成21年12月24日(2009.12.24)

(24) 登録日 平成21年10月16日(2009.10.16)

(51) Int.Cl.

H01C 7/00 (2006.01)

F 1

H01C 7/00

B

請求項の数 1 (全 9 頁)

(21) 出願番号 特願2000-68321 (P2000-68321)

(22) 出願日 平成12年3月13日 (2000.3.13)

(65) 公開番号 特開2001-257102 (P2001-257102A)

(43) 公開日 平成13年9月21日 (2001.9.21)

審査請求日 平成19年1月24日 (2007.1.24)

(73) 特許権者 000005821

パナソニック株式会社

大阪府門真市大字門真1006番地

(74) 代理人 100097445

弁理士 岩橋 文雄

(74) 代理人 100109667

弁理士 内藤 浩樹

(74) 代理人 100109151

弁理士 永野 大介

(72) 発明者 渋谷 直樹

大阪府門真市大字門真1006番地 松下

電器産業株式会社内

(72) 発明者 中谷 光成

大阪府門真市大字門真1006番地 松下

電器産業株式会社内

最終頁に続く

(54) 【発明の名称】薄膜多連チップ抵抗器

## (57) 【特許請求の範囲】

## 【請求項 1】

絶縁基板と、前記絶縁基板の上面における対向する側辺に沿って互いに対向するように形成された4対の上面電極と、前記互いに対向する4対の上面電極間を電気的に接続する4素子の薄膜抵抗体と、この4素子の薄膜抵抗体を覆う保護膜とを備え、前記4素子の薄膜抵抗体は、材料、膜厚を等しくし、かつ占有面積とパターン形状を異ならせることにより抵抗値を変えるとともに、前記4素子の薄膜抵抗体のパターン形状を、前記絶縁基板の対向する側辺と直交する前記絶縁基板の中心線に対して線対称に構成し、かつ前記4素子の薄膜抵抗体の抵抗値比が前記絶縁基板の両側のどちらからも同じになるように構成した薄膜多連チップ抵抗器。

## 【発明の詳細な説明】

## 【0001】

## 【発明の属する技術分野】

本発明は各種電子機器に用いられる薄膜多連チップ抵抗器に関するものである。

## 【0002】

## 【従来の技術】

従来のこの種の薄膜多連チップ抵抗器としては、特開平7-74002号公報に開示されたものが知られている。

## 【0003】

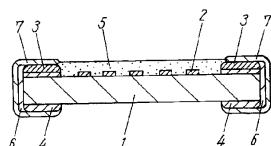

図7は従来の薄膜多連チップ抵抗器における抵抗体形成後の上面図、図8は同薄膜多連

チップ抵抗器の完成後の上面図、図9は図8のA-A線断面図である。

**【0004】**

図7～図9において、1はアルミナ等からなる絶縁基板で、この絶縁基板1の上面にはNiCrからなる同一の占有面積、同一のパターン形状を有する薄膜抵抗体2を複数設けている。3は複数の薄膜抵抗体2毎にその両端部近傍にそれぞれ重畳するように設けられたCr/Ni/Cuの積層構造からなる複数対の上面電極である。4は前記絶縁基板1の下面において前記複数対の上面電極3と略対応する位置に設けられたCr/Ni/Cuの積層構造からなる複数対の下面電極である。5は少なくとも前記複数の薄膜抵抗体2を覆うように設けられたエポキシ樹脂等からなる保護膜である。6は前記絶縁基板1の両端面に位置して上面電極3と下面電極4を電気的に接続するように設けられたCr/Ni/Cuの積層構造からなる複数対の端面電極である。7は前記複数対の上面電極3、複数対の端面電極6および複数対の下面電極4を覆うように設けられたNi/はんだの積層構造からなる複数対の外部電極である。

**【0005】**

上記のように構成された従来の薄膜多連チップ抵抗器について、次にその製造方法を図面を参照しながら説明する。

**【0006】**

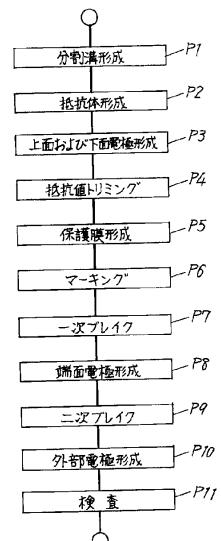

図10は従来の薄膜多連チップ抵抗器の製造方法を示す製造工程図である。

**【0007】**

まず、図10に示す工程P1で、チップ状の絶縁基板1が多数個取れるように略長方形のシート状の絶縁基板の一方の面にレーザ加工により分割溝を形成する。

**【0008】**

次に工程P2で、シート状の絶縁基板の上面にスパッタリング等により所定の膜厚のNiCrからなる薄膜金属層を形成した後、フォトリソグラフィ法、エッチングにより薄膜金属層の不要部分を除去して図7に示すような同一の占有面積、同一のパターン形状を有する薄膜抵抗体2を複数形成する。

**【0009】**

次に工程P3で、複数の薄膜抵抗体2の両端部に薄膜形成技術によりCr/Ni/Cuの積層構造からなる複数対の上面電極を形成する。続いて、この上面電極と同じ工法により、シート状の絶縁基板の下面において複数対の上面電極と略対応する位置に複数対の下面電極を形成する。

**【0010】**

次に工程P4で、必要に応じて抵抗値トリミングを行う。

**【0011】**

次に工程P5で、少なくとも複数の薄膜抵抗体2を覆うように図8および図9に示すような保護膜5を形成する。

**【0012】**

次に工程P6で、各保護膜5上に抵抗値のマーキングを形成する。

**【0013】**

次に工程P7で、シート状の絶縁基板を分割溝に沿って一次ブレイクすることにより、短冊状に分割する。

**【0014】**

次に工程P8で、短冊状に分割された絶縁基板の分割面に、複数対の上面電極と複数対の下面電極を電気的に接続するようにCr/Ni/Cuの積層構造からなる複数対の端面電極を形成する。

**【0015】**

次に工程P9で、短冊状に分割された絶縁基板を分割溝に沿って二次ブレイクすることにより、個片状に分割する。

**【0016】**

次に工程P10で、前記複数対の上面電極、複数対の端面電極および複数対の下面電極

10

20

30

40

50

を覆うようにNiめっきおよびはんだめっきを施すことによりNi／はんだの積層構造からなる複数対の外部電極を形成する。

#### 【0017】

次に工程P11で、検査を行うことにより、薄膜多連チップ抵抗器が完成するものである。

#### 【0018】

##### 【発明が解決しようとする課題】

しかしながら、上記した従来の薄膜多連チップ抵抗器においては、各薄膜抵抗体2の占有面積、パターン形状が同一であるため、例えば異種抵抗値、特に複数の薄膜抵抗体の最小抵抗値と最大抵抗値の比が1：2以上のもので、さらに高抵抗値領域までを得ようとした場合、非常に困難であるという課題を有していた。10

#### 【0019】

すなわち、任意の抵抗値を得る場合、薄膜抵抗体材料の導電率およびパターン形状、つまり薄膜抵抗体の長さと幅、薄膜抵抗体の膜厚により抵抗値は決定されるもので、概ね抵抗値は下記の式により決定される。

#### 【0020】

$$\text{抵抗値} = \text{薄膜抵抗体材料の導電率} \div \text{薄膜抵抗体の膜厚} \times (\text{薄膜抵抗体の長さ} \div \text{幅})$$

したがって、上記した異種抵抗値を得ようとした場合、上記式の定数を変える必要がある。

#### 【0021】

例えば、薄膜抵抗体材料あるいは薄膜抵抗体の膜厚を変えて異種抵抗値を得る場合は、薄膜抵抗体形成工程を異種抵抗値の種類だけ別個に設ける必要があるため、生産効率が悪くなつて高コストになるという問題点を有していた。また、薄膜抵抗体のパターン形状、すなわち薄膜抵抗体の長さと幅を変える場合は、高抵抗値を得ようとすると、薄膜抵抗体のパターン形状として長さを長くし、かつ幅を細くする必要があり、特に薄膜多連チップ抵抗器の小型化が進む中では、上記のように薄膜抵抗体のパターン形状として長さを長くし、かつ幅を細くした場合、薄膜抵抗体の占有面積が小さくなるため、高抵抗値領域までの品揃えが困難であるという課題を有していた。20

#### 【0022】

本発明は上記従来の課題を解決するもので、生産効率が高く、低コストで得られ、しかも高抵抗値領域までの品揃えを可能とした薄膜多連チップ抵抗器を提供することを目的とするものである。30

#### 【0023】

##### 【課題を解決するための手段】

上記目的を達成するために本発明の薄膜多連チップ抵抗器は、絶縁基板と、前記絶縁基板の上面における対向する側辺に沿って互いに対向するように形成された4対の上面電極と、前記互いに対向する4対の上面電極間を電気的に接続する4素子の薄膜抵抗体と、この4素子の薄膜抵抗体を覆う保護膜とを備え、前記4素子の薄膜抵抗体は、材料、膜厚を等しくし、かつ占有面積とパターン形状を異ならせることにより抵抗値を変えるとともに、前記4素子の薄膜抵抗体のパターン形状を、前記絶縁基板の対向する側辺と直交する前記絶縁基板の中心線に対して線対称に構成し、かつ前記4素子の薄膜抵抗体の抵抗値比が前記絶縁基板の両側のどちらからも同じになるように構成したもので、この構成によれば、生産効率が高く、低コストで得られ、しかも高抵抗値領域までの品揃えを可能にした薄膜多連チップ抵抗器を提供することができるものである。40

#### 【0024】

##### 【発明の実施の形態】

本発明の請求項1に記載の発明は、絶縁基板と、前記絶縁基板の上面における対向する側辺に沿って互いに対向するように形成された4対の上面電極と、前記互いに対向する4対の上面電極間を電気的に接続する4素子の薄膜抵抗体と、この4素子の薄膜抵抗体を覆う保護膜とを備え、前記4素子の薄膜抵抗体は、材料、膜厚を等しくし、かつ占有面積と50

パターン形状を異ならせることにより抵抗値を変えるとともに、前記4素子の薄膜抵抗体のパターン形状を、前記絶縁基板の対向する側辺と直交する前記絶縁基板の中心線に対して線対称に構成し、かつ前記4素子の薄膜抵抗体の抵抗値比が前記絶縁基板の両側のどちらからも同じになるように構成したもので、この構成によれば、4素子の薄膜抵抗体の抵抗値を変える場合、薄膜抵抗体の材料と膜厚を等しくして、薄膜抵抗体の占有面積とパターン形状を異ならせることにより抵抗値を変えるようにしているため、薄膜抵抗体の材料あるいは薄膜抵抗体の膜厚を変えるもののように、薄膜抵抗体形成工程を異種抵抗値の種類だけ別個に設けるという必要はなく、薄膜抵抗体形成工程を一括で行うことができ、これにより、生産効率が高く、低コストで得られ、しかも高抵抗値領域までの品揃えにおいても、薄膜抵抗体の占有面積とパターン形状を自由に変えることができるため、容易に製造することができる。また、前記4素子の薄膜抵抗体のパターン形状を、前記絶縁基板の対向する側辺と直交する前記絶縁基板の中心線に対して線対称に構成し、かつ前記4素子の薄膜抵抗体の抵抗値比が前記絶縁基板の両側のどちらからも同じになるように構成しているため、薄膜多連チップ抵抗器の方向性をなくすることができるという作用を有するものである。

#### 【0025】

以下、本発明の一実施の形態における薄膜多連チップ抵抗器について、図面を参照しながら説明する。

#### 【0026】

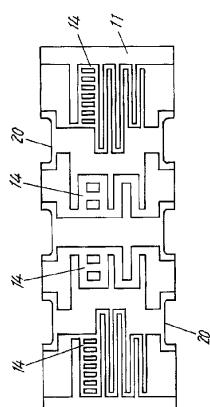

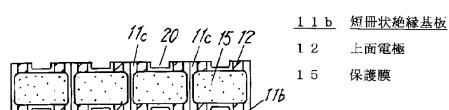

図1は本発明の一実施の形態における薄膜多連チップ抵抗器の抵抗体形成後の上面図、図2は同薄膜多連チップ抵抗器の完成後の断面図である。

#### 【0027】

図1および図2において、11はアルミナ等からなる絶縁基板で、この絶縁基板11の上面には対向する側辺に沿って互いに対向するように複数対の上面電極12を形成している。そしてこの上面電極12はAu, Ag, Ni, Cr, Cu等の单一金属もしくはその合金で構成されているものである。13は前記絶縁基板11の下面において前記複数対の上面電極12と略対応する位置に設けられた複数対の下面電極で、この下面電極13は前記上面電極12と同じ材料で構成されているものである。14は前記互いに対向する複数対の上面電極12間を電気的に接続するように絶縁基板11の上面に設けられた複数の薄膜抵抗体で、この薄膜抵抗体14はNiCr, CrSi, CrSiO, 窒化タンタル等からなり、そして図1に示すように、各素子毎に、材料、膜厚を等しくし、かつ占有面積とパターン形状を異ならせた薄膜抵抗体14を複数形成することにより異種抵抗値を得るよう正在しているものである。15は前記複数の薄膜抵抗体14を覆うように設けられたエポキシ樹脂等からなる保護膜である。16は前記絶縁基板11の両端面に位置して上面電極12と下面電極13を電気的に接続するように設けられたAg, Ni等の導電性樹脂からなる複数対の端面電極である。17は前記複数対の上面電極12、複数対の端面電極16および複数対の下面電極13を覆うように設けられたNi／はんだの積層構造からなる複数対の外部電極である。

#### 【0028】

上記のように構成された本発明の一実施の形態における薄膜多連チップ抵抗器について、次にその製造方法を図面を参照しながら説明する。

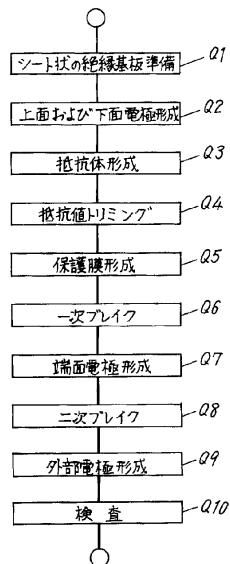

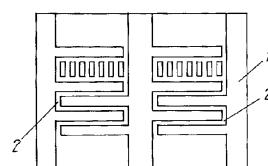

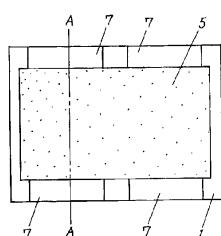

#### 【0029】

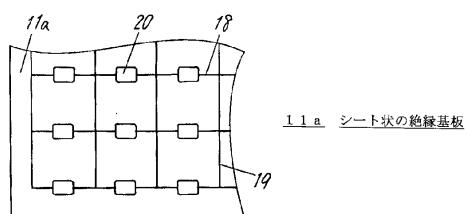

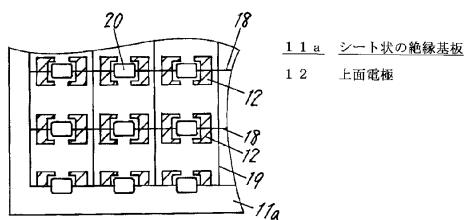

図3は本発明の一実施の形態における薄膜多連チップ抵抗器の製造方法を示す製造工程図である。図4～図6は各工程での一例を示したもので、図4はシート状の絶縁基板の一例を示す上面図、図5は同シート状の絶縁基板に複数対の上面電極を形成した後の上面図、図6は同シート状の絶縁基板を横方向の分割溝に沿って一次ブレイクした後の短冊状絶縁基板の上面図である。

#### 【0030】

まず、図3に示す工程Q1で、図4に一例を示すような一方の面に横方向の分割溝18、縦方向の分割溝19、スルーホール20が多数形成された所定製造単位の大きさを有す

10

20

30

40

50

るアルミナ等からなるシート状の絶縁基板 11a を準備する。

#### 【0031】

次に工程 Q 2 で、図 5 に一例を示すように、シート状の絶縁基板 11a の上面に位置して横方向の分割溝 18 を跨いで縦方向の分割溝 19 を跨がないように複数対の上面電極 12 を形成する。続いて、シート状の絶縁基板 11a の下面において複数対の上面電極 12 と略対応する位置に複数対の下面電極 13 を形成する。なお、上面電極 12 は Au, Ag, Ni 系の金属有機物ペーストをスクリーン印刷し、かつ焼成することにより形成する方が、コスト的にも安価で、特性上良好なため、望ましい。しかし、これに限定されるものではなく、Cr, Ni, Cu, Ti 等の材料を用いて薄膜形成技術により上面電極 12 を形成しても良いものである。この薄膜形成技術で上面電極 12 を形成する場合は、薄膜抵抗体 14 の形成後に上面電極 12 を形成しても良い。また、下面電極 13 については、上面電極 12 と同様の方法で形成しても良く、あるいは Ag 系の低温硬化型のペーストで形成しても良いものである。10

#### 【0032】

次に工程 Q 3 で、図 1 に示すように 1 個の部品領域毎に 4 素子の薄膜抵抗体 14 を形成する。すなわち、複数対の上面電極 12 間を電気的に接続するようにシート状の絶縁基板 11a の上面に、例えばスパッタリング等により、所定の厚さの NiCr の薄膜金属層を着膜した後、フォトレジストをロールコートにより塗布し、そしてフォトリソグラフィによりレジストをパターニングし、かつ薄膜金属層をエッチングした後、レジストを除去することにより、図 1 に示すようなパターン形状を有する 4 素子の薄膜抵抗体 14 を形成する。この 4 素子の薄膜抵抗体 14 は各素子毎に、材料、膜厚を等しくし、かつ占有面積とパターン形状を異ならせることにより異種抵抗値を得るとともに、前記 4 素子の薄膜抵抗体のパターン形状を線対称に構成し、かつ前記 4 素子の薄膜抵抗体の抵抗値比が絶縁基板 11 の両側のどちらからも同じになるように構成したところに特徴を有するものである。20

なお、この薄膜抵抗体 14 の材料は NiCr に限定されるものではなく、CrSi, CrSiO, 窒化タンタルなども使用できるものである。

#### 【0033】

次に工程 Q 4 で、必要に応じて YAG レーザにより抵抗値修正を行い、所望の抵抗値を得る。なお、薄膜抵抗体 14 を窒化タンタルにより形成した場合は、陽極酸化法により抵抗値を修正する。30

#### 【0034】

次に工程 Q 5 で、図 2 に示すように、複数対の上面電極 12 間を電気的に接続するように設けられた複数の薄膜抵抗体 14 を覆うようにスクリーン印刷等により保護膜 15 を形成する。この保護膜 15 の材料としては、エポキシ樹脂、ポリイミド樹脂等が用いられる。

#### 【0035】

次に工程 Q 6 で、シート状の絶縁基板 11a を横方向の分割溝 18 に沿って一次ブレイクすることにより、短冊状に分割して図 6 に示すような短冊状絶縁基板 11b を得る。

#### 【0036】

次に工程 Q 7 で、短冊状に分割された短冊状絶縁基板 11b の分割面における凸部 11c に、図 2 に示すような複数対の上面電極 12 と複数対の下面電極 13 を電気的に接続する端面電極 16 を塗布、乾燥により形成する。この場合、端面電極 16 の材料としては、Ag, Ni 等の導電性樹脂が用いられる。なお、シート状の絶縁基板 11a として、横方向の分割溝 18、縦方向の分割溝 19 が形成されているのみで、スルーホール 20 を有していないものを用いる場合は、短冊状絶縁基板 11b の分割面全面に端面電極 16 を形成し、そして各素子の上面電極 12 間の端面電極 16 と下面電極 13 間の端面電極 16 を YAG レーザ、ダイシング等で除去するようにしても良い。この場合の端面電極 16 はスパッタ等による薄膜形成技術によって形成しても良いものである。40

#### 【0037】

次に工程 Q 8 で、短冊状に分割された短冊状絶縁基板 11b を縦方向の分割溝 19 に沿50

つて二次ブレイクすることにより、4素子の薄膜抵抗体14を有する個片状の絶縁基板に分割する。

**【0038】**

次に工程Q9で、前記4対の上面電極12、4素子の薄膜抵抗体14の電極部（保護膜15で被覆されていない部分）、4対の端面電極16および4対の下面電極13を覆うように、Niによる下地めっきとはんだめっきを施すことにより、Ni／はんだの積層構造からなる4対の外部電極17を形成する。

**【0039】**

最後に工程Q10で、検査を行うことにより、抵抗値を異ならせた薄膜多連チップ抵抗器が完成するものである。

10

**【0040】**

上記した本発明の一実施の形態においては、4素子の薄膜抵抗体14の材料、膜厚を等しくし、かつ占有面積とパターン形状を異ならすことにより異種抵抗値を得る、すなわち抵抗値を変えるようにしているため、薄膜抵抗体の材料あるいは薄膜抵抗体の膜厚を変えるもののように、薄膜抵抗体形成工程を異種抵抗値の種類だけ別個に設けるという必要はなく、薄膜抵抗体形成工程を一括で行うことができ、これにより、生産効率が高く、低コストの薄膜多連チップ抵抗器が得られる。また高抵抗値領域までの品揃えにおいても、薄膜抵抗体の占有面積、パターン形状を自由に変えることができるため、容易に製造できるという効果を有するものである。

**【0041】**

20

また上記本発明の一実施の形態においては、4素子の薄膜抵抗体14の最小抵抗値と最大抵抗値の比を1：2以上としているものである。

**【0042】**

そしてまた上記本発明の一実施の形態においては、4素子の薄膜抵抗体14のパターン形状を線対称に構成し、かつ前記4素子の薄膜抵抗体14の抵抗値比が絶縁基板11の両側のどちらからも同じになるように構成しているため、薄膜多連チップ抵抗器の方向性をなくすることができるという効果を有するものである。

**【0043】**

さらに上記本発明の一実施の形態における4素子の薄膜抵抗体14は、一定の抵抗値を有する抗体を基準にしてその相対値に応じた抵抗値修正を行うことにより抵抗値を変えるようにしているため、抵抗値の相対値比を高精度に制御することができるという効果を有するものである。

30

**【0044】**

さらにまた4素子の薄膜抵抗体14の各素子毎に電力が異なる場合にも、大電力が必要な素子部の占有面積を大きくすることが可能であるため、薄膜多連チップ抵抗器の信頼性向上を図ることができるものである。

**【0045】**

**【発明の効果】**

以上のように本発明の薄膜多連チップ抵抗器は、絶縁基板と、前記絶縁基板の上面における対向する側辺に沿って互いに対向するように形成された4対の上面電極と、前記互いに対向する4対の上面電極間を電気的に接続する4素子の薄膜抵抗体と、この4素子の薄膜抵抗体を覆う保護膜とを備え、前記4素子の薄膜抵抗体は、材料、膜厚を等しくし、かつ占有面積とパターン形状を異ならせることにより抵抗値を変えるとともに、前記4素子の薄膜抵抗体のパターン形状を、前記絶縁基板の対向する側辺と直交する前記絶縁基板の中心線に対して線対称に構成し、かつ前記4素子の薄膜抵抗体の抵抗値比が前記絶縁基板の両側のどちらからも同じになるように構成したもので、この構成によれば、4素子の薄膜抵抗体の抵抗値を変える場合、薄膜抵抗体の材料、膜厚は等しくて、占有面積とパターン形状を異ならせることにより抵抗値を変えるようにしているため、薄膜抵抗体の材料あるいは薄膜抵抗体の膜厚を変えるもののように、薄膜抵抗体形成工程を異種抵抗値の種類だけ別個に設けるという必要はなく、薄膜抵抗体形成工程を一括で行うことができ、これ

40

50

により、生産効率が高く、低コストで得られ、しかも高抵抗値領域までの品揃えにおいても、薄膜抵抗体の占有面積、パターン形状を自由に変えることができるため、容易に製造することができるという効果を有するものである。

**【図面の簡単な説明】**

**【図 1】** 本発明の一実施の形態における薄膜多連チップ抵抗器の薄膜抵抗体形成後の上面図

**【図 2】** 同薄膜多連チップ抵抗器の完成後の断面図

**【図 3】** 同薄膜多連チップ抵抗器の製造方法を示す製造工程図

**【図 4】** 同製造方法におけるシート状の絶縁基板の一例を示す上面図

**【図 5】** 同シート状の絶縁基板の上面電極形成後の上面図

10

**【図 6】** 同シート状の絶縁基板を一次ブレイクした後の短冊状絶縁基板の上面図

**【図 7】** 従来の薄膜多連チップ抵抗器における薄膜抵抗体形成後の上面図

**【図 8】** 同薄膜多連チップ抵抗器の完成後の上面図

**【図 9】** 図 8 の A - A 線断面図

**【図 10】** 同薄膜多連チップ抵抗器の製造方法を示す製造工程図

**【符号の説明】**

1 1 絶縁基板

1 1 a シート状の絶縁基板

1 1 b 短冊状絶縁基板

1 2 上面電極

20

1 4 薄膜抵抗体

1 5 保護膜

**【図 1】**

1 1 絶縁基板

1 4 薄膜抵抗体

**【図 2】**

1 1 絶縁基板

1 2 上面電極

1 4 薄膜抵抗体

1 5 保護膜

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図10】

【図9】

---

フロントページの続き

審査官 田中 純一

(56)参考文献 特開平07-074002(JP,A)

特開平06-045101(JP,A)

特開平11-186008(JP,A)

実開昭57-097903(JP,U)

(58)調査した分野(Int.Cl., DB名)

H01C 1/00 - 1/16

H01C 7/00

H01C 11/00 - 13/02