(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3889311号

(P3889311)

(45) 発行日 平成19年3月7日(2007.3.7)

(24) 登録日 平成18年12月8日(2006.12.8)

(51) Int.C1.

F 1

|             |              |                  |      |       |      |

|-------------|--------------|------------------|------|-------|------|

| <b>H05K</b> | <b>1/02</b>  | <b>(2006.01)</b> | H05K | 1/02  | E    |

| <b>H01L</b> | <b>23/12</b> | <b>(2006.01)</b> | H01L | 23/12 | 501Z |

| <b>H05K</b> | <b>1/18</b>  | <b>(2006.01)</b> | H05K | 1/18  | L    |

| <b>H05K</b> | <b>3/24</b>  | <b>(2006.01)</b> | H05K | 3/24  | B    |

| <b>H05K</b> | <b>3/28</b>  | <b>(2006.01)</b> | H05K | 3/24  | D    |

請求項の数 3 (全 7 頁) 最終頁に続く

(21) 出願番号

特願2002-143609 (P2002-143609)

(22) 出願日

平成14年5月17日 (2002.5.17)

(65) 公開番号

特開2003-338666 (P2003-338666A)

(43) 公開日

平成15年11月28日 (2003.11.28)

審査請求日

平成17年1月25日 (2005.1.25)

(73) 特許権者 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

(74) 代理人 100066474

弁理士 田澤 博昭

(74) 代理人 100088605

弁理士 加藤 公延

(72) 発明者 羽立 剛

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

(72) 発明者 長嶺 高宏

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

審査官 長屋 陽二郎

最終頁に続く

(54) 【発明の名称】プリント配線板

## (57) 【特許請求の範囲】

## 【請求項1】

半導体チップ搭載パッケージが配置され、半田付けランドが配置されない中央部の絶縁基板上に形成されたベタパターンと、

上記ベタパターンを被覆すると共に、上部が開口されたソルダレジストと、

上記開口されたソルダレジストのベタパターン上に施されたニッケル／金メッキとを備えたプリント配線板。

## 【請求項2】

ニッケル／金メッキ上に施されたクリーム半田を備えたことを特徴とするプリント配線板。

10

## 【請求項3】

半導体チップ搭載パッケージが配置され、半田付けランドが配置されない中央部の絶縁基板上に形成されたベタパターンと、

上記ベタパターンを被覆すると共に、上部が開口されたソルダレジストと、

上記開口されたソルダレジストのベタパターン上に施された半田コートとを備えたプリント配線板。

## 【発明の詳細な説明】

## 【0001】

## 【発明の属する技術分野】

この発明は、半導体チップ搭載パッケージ、特に小型多ピン化を図った構造のCSP(C

20

hip Scale Package) を搭載するプリント配線板に関するものである。

【0002】

【従来の技術】

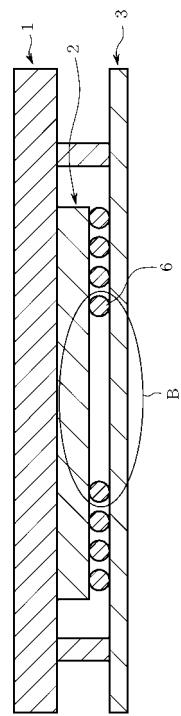

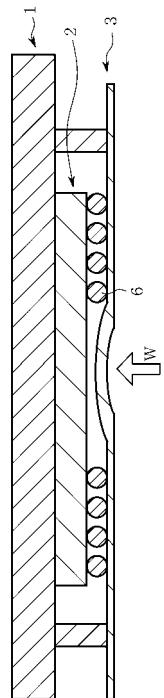

図5は従来のパッケージ実装後のプリント配線板を示す断面図、図6はパッケージ実装後のプリント配線板のB部詳細を示す断面図であり、図において、1はケース、2は半導体チップが搭載されたパッケージ、3はプリント配線板となるマザー基板である。4はマザー基板側ランド、5はパッケージ側ランド、6はマザー基板側ランド4およびパッケージ側ランド5を接合する半田ボール、7はマザー基板3上に形成されたベタパターン、8はベタパターン7を被覆するソルダレジストである。

【0003】

10

次に動作について説明する。

図5および図6において、半導体チップが搭載されたパッケージ2は、半田ボール6によりマザー基板側ランド4およびパッケージ側ランド5を接合することによってマザー基板3上に配置される。

また、マザー基板3上において、パッケージ側ランド5が配置されない中央部は、信号配線領域として使用されるか、または、グランド領域として使用される。グランド領域として使用される場合には、マザー基板3上にベタパターン7が形成され、表面をソルダレジスト8によって被覆することが一般的である。また、マザー基板3の剛性向上を目的として、ベタパターン7を形成する場合も同様にソルダレジスト8によって被覆することが一般的である。

20

【0004】

【発明が解決しようとする課題】

従来のプリント配線板は以上のように構成されているので、マザー基板3の剛性向上を目的として、マザー基板3上のパッケージ側ランド5が配置されない中央部にベタパターン7を形成する場合においてもソルダレジスト8によって被覆される。

図7はマザー基板の裏面から外力が加わった状態を示す説明図であり、従来のプリント配線板では、この図7に示すように、マザー基板3の裏面から外力Wが加わった場合、パッケージ2は、ケース1との間に挟まれて、マザー基板3が変形することになる。この変形を繰り返し受けることにより、最内周に設けられる半田ボール6に応力疲労が発生し、マザー基板側ランド4およびパッケージ側ランド5の接合部が破断してしまう課題があった。

30

なお、この接合部の破断を解決するために、マザー基板3を厚板化したり、マザー基板3およびパッケージ2間に樹脂を注入する等の手段も考えられたが、工程が多くなってしまう等、製造コストが増大してしまう課題があった。

【0005】

この発明は上記のような課題を解決するためになされたもので、曲げ剛性を向上したプリント配線板を得ることを目的とする。

【0006】

【課題を解決するための手段】

この発明に係るプリント配線板は、開口されたソルダレジストのベタパターン上に施されたニッケル／金メッキを備えたものである。

40

【0007】

この発明に係るプリント配線板は、ニッケル／金メッキ上に施されたクリーム半田を備えたものである。

【0008】

この発明に係るプリント配線板は、開口されたソルダレジストのベタパターン上に施された半田コートを備えたものである。

【0009】

【発明の実施の形態】

以下、この発明の実施の一形態を説明する。

50

### 実施の形態 1 .

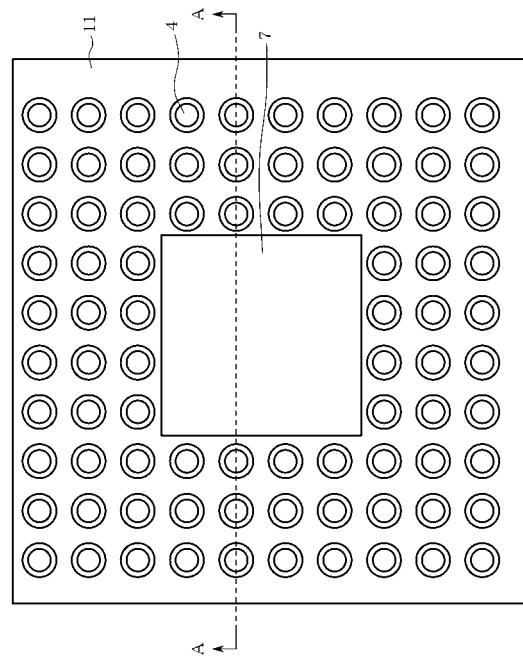

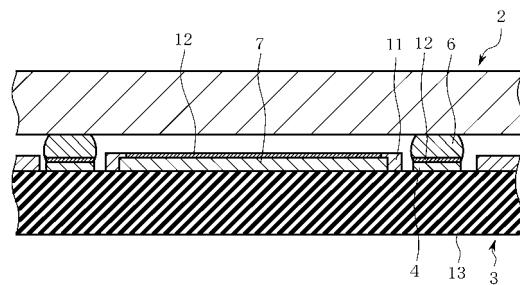

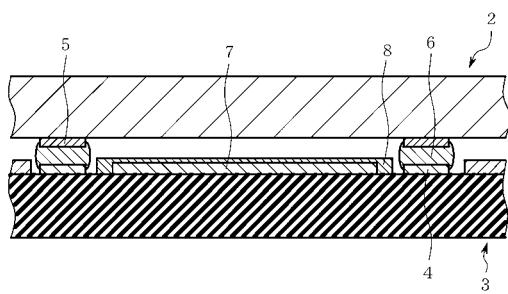

図 1 はこの発明の実施の形態 1 によるプリント配線板を示す平面図、図 2 はパッケージ実装後のプリント配線板の A A 矢視部詳細を示す断面図であり、図において、2 は半導体チップが搭載されたパッケージ（半導体チップ搭載パッケージ）、3 はプリント配線板となるマザー基板である。4 はマザー基板側ランド（半田付けランド）、6 はマザー基板側ランド 4 およびパッケージ 2 側を接合する半田ボール、7 はマザー基板側ランド 4 が配置されないマザー基板 3 上に形成されたベタパターン、11 はベタパターン 7 を被覆すると共に、上部が開口されたソルダレジスト、12 は開口されたソルダレジスト 11 のベタパターン 7 に施された Ni / Au メッキ（ニッケル / 金メッキ）である。13 は絶縁基板である。

10

#### 【 0 0 1 0 】

次に動作について説明する。

図 1 において、マザー基板側ランド 4 は、パターン形成した導体パターンを、ソルダレジスト 11 の開口によって表面に露出させる。絶縁基板 13 としては、ガラスエポキシ等の樹脂基板を用いる。ソルダレジスト 11 としては、液体ソルダレジストまたは熱硬化型等を用いる。マザー基板側ランド 4 は、銅箔の祖面化表面のアンカー効果によって絶縁基板 13 に接着している。

マザー基板側ランド 4 は、表面の酸化腐食防止および半田付けの媒体として、Ni / Au メッキ 12 の処理、またはフラックス塗布が施される。

#### 【 0 0 1 1 】

半導体チップが搭載されたパッケージ 2 のマザー基板 3 上への実装は、図 2 に示すように、マザー基板側ランド 4 上に、例えば、クリーム半田を塗布した後、半田ボール 6 が接触するようにパッケージ 2 を載置する。次いで、これを加熱溶融炉に入れてクリーム半田と半田ボール 6 とを溶融する。これにより、マザー基板側ランド 4 上に、半田ボール 6 が接合される。

20

また、マザー基板 3 上において、パッケージ 2 の接続端子が存在せず、マザー基板側ランド 4 が配置されない中央部に、ベタパターン 7 をマザー基板側ランド 4 と同一形成にて設ける。また、ソルダレジスト 11 によって、ベタパターン 7 を被覆すると共に、上部を開口し、開口されたソルダレジスト 11 のベタパターン 7 に Ni / Au メッキ 12 を施す。

#### 【 0 0 1 2 】

以上のように、この実施の形態 1 によれば、ソルダレジスト 11 に比較して硬度の高い Ni（ニッケル）がベタパターン 7 上に施されるので、マザー基板 3 の曲げ剛性を向上させることができる。これにより、マザー基板 3 の裏面からの外力に対してマザー基板 3 の曲がり量が抑制され、パッケージ 2 の最内周に設けられる半田ボール 6 の発生応力を低減することができ、半田ボール 6 による接合信頼性を向上させることができる。

30

また、絶縁基板 13 上に、ベタパターン 7 とマザー基板側ランド 4 とを同一形成にて設け、次いでソルダレジスト 11 を設け、さらにベタパターン 7 およびマザー基板側ランド 4 上に Ni / Au メッキ 12 を一括して施すことにより、製造工程が増えることなく、製造コストの増大を抑えることができる。

なお、ソルダレジスト 11 から露出したベタパターン 7 の表面処理として、Ni / Au メッキ 12 とフラックス塗布とを選択的に施す場合においても例外ではない。

40

#### 【 0 0 1 3 】

実施の形態 2 .

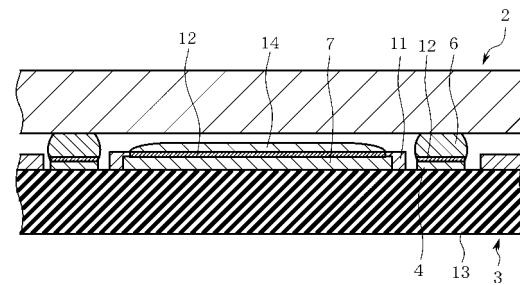

図 3 はこの発明の実施の形態 2 によるパッケージ実装後のプリント配線板の詳細を示す断面図であり、図において、14 はパッケージ 2 の実装時に、マザー基板側ランド 4 上および Ni / Au メッキ 12 上に施されたクリーム半田である。

その他の構成については、図 2 と同一である。

#### 【 0 0 1 4 】

次に動作について説明する。

上記実施の形態 1 では、ベタパターン 7 の表面処理として、Ni / Au メッキ 12 を施し

50

たものを示したが、この実施の形態2では、パッケージ2の実装時に、マザー基板側ランド4上にクリーム半田を供給すると共に、Ni/Auメッキ12上にクリーム半田を供給し、溶融させるものである。

【0015】

以上のように、この実施の形態2によれば、ベタパターン7上にNi/Auメッキ12を施し、さらに、クリーム半田を溶融させることにより、さらなる剛性の向上を図ることができる。

また、このクリーム半田の供給および溶融は、マザー基板側ランド4上と一括して処理できるので、製造工程が増えることなく、製造コストの増大を抑えることができる。

【0016】

実施の形態3。

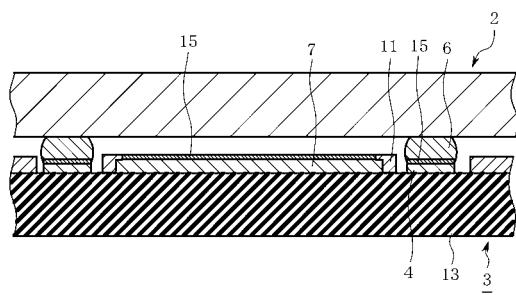

図4はこの発明の実施の形態3によるパッケージ実装後のプリント配線板の詳細を示す断面図であり、図において、15は開口されたソルダレジスト11のベタパターン7上およびマザー基板側ランド4上に施された半田コートである。

その他の構成については、図2と同一である。

【0017】

次に動作について説明する。

上記実施の形態1では、ベタパターン7およびマザー基板側ランド4上に、Ni/Auメッキ12を施したものを見たが、この実施の形態3では、そのNi/Auメッキ12の代わりに半田コート15を施したものである。

【0018】

以上のように、この実施の形態3によれば、ソルダレジスト11に比較して硬度の高い半田コート15がベタパターン7上に施されるので、マザー基板3の曲げ剛性を向上させることができる。これにより、マザー基板3の裏面からの外力に対してマザー基板3の曲がり量が抑制され、パッケージ2の最内周に設けられる半田ボール6の発生応力を低減することができ、半田ボール6による接合信頼性を向上させることができる。

また、絶縁基板13上に、ベタパターン7とマザー基板側ランド4とを同一形成にて設け、次いでソルダレジスト11を設け、さらにベタパターン7およびマザー基板側ランド4上に半田コート15を一括して施すことにより、製造工程が増えることなく、製造コストの増大を抑えることができる。

【0019】

【発明の効果】

以上のように、この発明によれば、開口されたソルダレジストのベタパターン上に施されたニッケル/金メッキを備えるように構成したので、ニッケル/金メッキを施すことにより、ソルダレジストと比較して硬質のニッケルが表面に存在することになり、曲げ剛性を得ることができる。したがって、半導体チップ搭載パッケージを半田ボールでプリント配線板に接続する場合において、プリント配線板側の半田付けランドが配置されない中央部にこの構造を適用することで、この部分へのプリント配線板の裏面からの外力に対して曲げ剛性が上昇し、近傍の接合部への応力緩和を実現することができる効果がある。

【0020】

この発明によれば、ニッケル/金メッキ上に施されたクリーム半田を備えるように構成したので、ニッケル/金メッキ上にクリーム半田を施すことで、外力に対してさらに曲げ剛性が上昇し、近傍の接合部へのさらなる応力緩和を実現することができる。

また、クリーム半田のニッケル/金メッキ上への供給は、半田付けランドへの供給時に行われるので、製造工程が増えることなく、したがって、製造コストの増大を抑えることができる効果がある。

【0021】

この発明によれば、開口されたソルダレジストのベタパターン上に施された半田コートを備えるように構成したので、半田コートを施すことにより、ソルダレジストと比較して硬質の半田コートが表面に存在することになり、曲げ剛性を得ることができる。したがって

10

20

30

40

50

、半導体チップ搭載パッケージを半田ボールでプリント配線板に接続する場合において、プリント配線板側の半田付けランドが配置されない中央部にこの構造を適用することで、この部分へのプリント配線板の裏面からの外力に対して曲げ剛性が上昇し、近傍の接合部への応力緩和を実現することができる効果がある。

【図面の簡単な説明】

【図 1】 この発明の実施の形態 1 によるプリント配線板を示す平面図である。

【図 2】 パッケージ実装後のプリント配線板の A A 矢視部詳細を示す断面図である。

【図 3】 この発明の実施の形態 2 によるパッケージ実装後のプリント配線板の詳細を示す断面図である。

【図 4】 この発明の実施の形態 3 によるパッケージ実装後のプリント配線板の詳細を示す断面図である。 10

【図 5】 従来のパッケージ実装後のプリント配線板を示す断面図である。

【図 6】 パッケージ実装後のプリント配線板の B 部詳細を示す断面図である。

【図 7】 マザー基板の裏面から外力が加わった状態を示す説明図である。

【符号の説明】

2 パッケージ (半導体チップ搭載パッケージ)、3 マザー基板 (プリント配線板)、

4 マザー基板側ランド (半田付けランド)、6 半田ボール、7 ベタパターン、11

ソルダレジスト、12 Ni / Au メッキ (ニッケル / 金メッキ)、13 絶縁基板、

14 クリーム半田、15 半田コート。

【図 1】

【図 2】

【図 3】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

(51)Int.CI. F I

**H 0 5 K 3/34 (2006.01)** H 0 5 K 3/28 B

H 0 5 K 3/34 5 0 1 E

(56)参考文献 特開平09-082557(JP, A)

特開2001-015638(JP, A)

(58)調査した分野(Int.CI., DB名)

H05K 1/02

H01L 23/12

H05K 1/18

H05K 3/24

H05K 3/28

H05K 3/34