(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7161317号

(P7161317)

(45)発行日 令和4年10月26日(2022.10.26)

(24)登録日 令和4年10月18日(2022.10.18)

(51)国際特許分類

|         |                 |         |       |       |

|---------|-----------------|---------|-------|-------|

| H 0 4 N | 5/369(2011.01)  | H 0 4 N | 5/369 | 6 0 0 |

| H 0 4 N | 5/353(2011.01)  | H 0 4 N | 5/353 | 5 0 0 |

| H 0 4 N | 5/355(2011.01)  | H 0 4 N | 5/355 | 9 0 0 |

| G 0 3 B | 13/36 (2021.01) | G 0 3 B | 13/36 |       |

| G 0 2 B | 7/34 (2021.01)  | G 0 2 B | 7/34  |       |

請求項の数 14 (全23頁) 最終頁に続く

(21)出願番号 特願2018-113789(P2018-113789)

(22)出願日 平成30年6月14日(2018.6.14)

(65)公開番号 特開2019-216394(P2019-216394)

A)

(43)公開日 令和1年12月19日(2019.12.19)

審査請求日 令和3年6月10日(2021.6.10)

(73)特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74)代理人 100094112

弁理士 岡部 讓

(74)代理人 100101498

弁理士 越智 隆夫

(74)代理人 100106183

弁理士 吉澤 弘司

(74)代理人 100136799

弁理士 本田 亜希

(72)発明者 小林 昌弘

東京都大田区下丸子3丁目30番2号

キヤノン株式会社内

審査官 西谷 憲人

最終頁に続く

(54)【発明の名称】 撮像装置、撮像システム及び移動体

## (57)【特許請求の範囲】

## 【請求項1】

入射光のうちの瞳分割された一部の光が入射される第1の光電変換部と、前記入射光のうちの瞳分割された他の一部の光が入射される第2の光電変換部と、入力ノードを有し、前記入力ノードに転送された電荷に基づく信号を出力する増幅部と、制御信号に応じて前記入力ノードの容量値を変化させる容量制御部と、を各々が含むとともに、複数の行及び複数の列にわたって配された複数の画素と、

前記複数の画素から出力される信号を、前記複数の画素の列ごとに読み出す読み出し回路と、

を有し、

前記複数の画素の各々は、一のフレーム期間において、前記第1の光電変換部で生成された電荷に基づく第1の信号と、前記第2の光電変換部で生成された電荷に少なくとも基づく第2の信号とを出力可能であり、

前記複数の画素は、同一の行の互いに異なる列に配された第1の画素及び第2の画素を含み、

前記一のフレーム期間において、前記第1の画素の前記第1の信号及び前記第2の信号の一方を得るために電荷を蓄積している蓄積時間と、前記第2の画素の前記第1の信号及び前記第2の信号の対応する一方を得るために電荷を蓄積している蓄積時間とは互いに異なり、

前記第1の画素の前記容量制御部に第1の制御信号を供給する第1の制御信号線と、

前記第2の画素の前記容量制御部に、前記第1の制御信号線により供給される前記第1の制御信号とは異なる第2の制御信号を供給する第2の制御信号線と、を有し、

前記一のフレーム期間において、前記第1の画素の前記入力ノードの容量値と、前記第2の画素の前記入力ノードの容量値とは、互いに異なる値に制御されることを特徴とする撮像装置。

【請求項2】

前記一のフレーム期間において、前記第1の画素の前記第1の信号及び前記第2の信号の一方を得るための電荷の蓄積が開始される時刻は、前記第2の画素の前記第1の信号及び前記第2の信号の対応する一方を得るための電荷の蓄積が開始される時刻と異なることを特徴とする請求項1に記載の撮像装置。

10

【請求項3】

前記一のフレーム期間において、前記第1の画素の前記第1の信号を得るための電荷の蓄積が終了する時刻は、前記第2の画素の前記第1の信号を得るための電荷の蓄積が終了する時刻と同一である

ことを特徴とする請求項1又は2に記載の撮像装置。

【請求項4】

前記一のフレーム期間において、前記第1の画素の前記第1の信号を得るための電荷の蓄積が終了する時刻は、前記第2の画素の前記第1の信号を得るための電荷の蓄積が終了する時刻と同一であり、

前記一のフレーム期間において、前記第1の画素の前記第2の信号を得るための電荷の蓄積が終了する時刻は、前記第2の画素の前記第2の信号を得るための電荷の蓄積が終了する時刻と同一である

20

ことを特徴とする請求項1又は2に記載の撮像装置。

【請求項5】

入射光のうちの瞳分割された一部の光が入射される第1の光電変換部と、前記入射光のうちの瞳分割された他の一部の光が入射される第2の光電変換部と、入力ノードを有し、前記入力ノードに転送された電荷に基づく信号を出力する増幅部と、制御信号に応じて前記入力ノードの容量値を変化させる容量制御部と、を各々が含むとともに、複数の行及び複数の列にわたって配された複数の画素と、

前記複数の画素から出力される信号を、前記複数の画素の列ごとに読み出す読み出し回路と、

30

を有し、

前記複数の画素の各々は、一のフレーム期間において、前記第1の光電変換部で生成された電荷に基づく第1の信号と、前記第1の光電変換部で生成された電荷及び前記第2の光電変換部で生成された電荷に基づく第2の信号とを出力可能であり、

前記複数の画素は、同一の行の互いに異なる列に配された第1の画素及び第2の画素を含み、

前記一のフレーム期間において、前記第1の画素は、前記第1の信号及び前記第2の信号を個別に出力し、

前記一のフレーム期間において、前記第2の画素は、前記第1の画素に供給される制御信号とは異なる制御信号に応じて、前記第1の信号を出力せず、前記第2の信号を出力し、前記第1の画素の前記容量制御部に第1の制御信号を供給する第1の制御信号線と、前記第2の画素の前記容量制御部に、前記第1の制御信号線により供給される前記第1の制御信号とは異なる第2の制御信号を供給する第2の制御信号線と、を有し、前記一のフレーム期間において、前記第1の画素の前記入力ノードの容量値と、前記第2の画素の前記入力ノードの容量値とは、互いに異なる値に制御される

40

ことを特徴とする撮像装置。

【請求項6】

前記一のフレーム期間において、前記第1の画素の前記第1の信号及び前記第2の信号の一方を得るために電荷を蓄積している蓄積時間と、前記第2の画素の前記第1の信号及

50

び前記第2の信号の対応する一方を得るために電荷を蓄積している蓄積時間とは同一であることを特徴とする請求項5に記載の撮像装置。

**【請求項7】**

前記一のフレーム期間において、前記第2の画素の前記第1の信号又は前記第2の信号を得るために電荷の蓄積が開始する時刻は、前記第1の画素の前記第1の信号を得るために電荷の蓄積が開始する時刻と、前記第1の画素の前記第2の信号を得るために電荷の蓄積が開始する時刻の中間の時刻である

ことを特徴とする請求項5又は6に記載の撮像装置。

**【請求項8】**

前記一のフレーム期間において、前記第2の画素の前記第1の信号又は前記第2の信号を得るために電荷の蓄積が終了する時刻は、前記第1の画素の前記第1の信号を得るために電荷の蓄積が終了する時刻と、前記第1の画素の前記第2の信号を得るために電荷の蓄積が終了する時刻の中間の時刻である

ことを特徴とする請求項5乃至7のいずれか1項に記載の撮像装置。

**【請求項9】**

前記一のフレーム期間において、前記第1の画素の前記第1の信号及び前記第2の信号の一方を得るために電荷を蓄積している蓄積時間と、前記第2の画素の前記第1の信号及び前記第2の信号の対応する一方を得るために電荷を蓄積している蓄積時間とは互いに異なる

ことを特徴とする請求項5に記載の撮像装置。

10

**【請求項10】**

前記第1の画素及び前記第2の画素の各々は、互いに同一の分光特性を有するカラーフィルタを更に含む

ことを特徴とする請求項1乃至9のいずれか1項に記載の撮像装置。

**【請求項11】**

前記第2の信号は、前記第1の光電変換部で生成された電荷及び前記第2の光電変換部で生成された電荷の両方に基づく

ことを特徴とする請求項1乃至10のいずれか1項に記載の撮像装置。

**【請求項12】**

前記第1の制御信号線は、前記第2の画素の前記容量制御部には前記第1の制御信号を供給しておらず、

20

前記第2の制御信号線は、前記第1の画素の前記容量制御部には前記第2の制御信号を供給していない

ことを特徴とする請求項1乃至4のいずれか1項に記載の撮像装置。

**【請求項13】**

請求項1乃至12のいずれか1項に記載の撮像装置と、

前記撮像装置から出力される信号を処理する信号処理部と

を有することを特徴とする撮像システム。

**【請求項14】**

移動体であって、

40

請求項1乃至12のいずれか1項に記載の撮像装置と、

前記撮像装置からの信号に基づく視差画像から、対象物までの距離情報を取得する距離情報取得手段と、

前記距離情報に基づいて前記移動体を制御する制御手段と

を有することを特徴とする移動体。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、撮像装置、撮像システム及び移動体に関する。

**【背景技術】**

50

**【 0 0 0 2 】**

特許文献1は、1つの画素に複数の光電変換部を設けることにより、撮像及び位相差検出方式の焦点検出を行うことが可能な撮像装置を開示している。特許文献1の撮像装置は、複数の光電変換部のうちの一部のみの光電変換部に基づく信号を出力する個数を少なくすることにより、信号の取得を高速化する構成を備えている。

**【先行技術文献】****【特許文献】****【 0 0 0 3 】**

【文献】特開2013-211833号公報

10

**【発明の概要】****【発明が解決しようとする課題】****【 0 0 0 4 】**

特許文献1に記載されているような撮像装置において、更なる高機能化が求められている。そこで、本発明は、他の構成により更なる高機能化を実現し得る撮像装置を提供することを目的とする。

**【課題を解決するための手段】****【 0 0 0 5 】**

本発明の一観点によれば、入射光のうちの瞳分割された一部の光が入射される第1の光電変換部と、前記入射光のうちの瞳分割された他の一部の光が入射される第2の光電変換部と、入力ノードを有し、前記入力ノードに転送された電荷に基づく信号を出力する増幅部と、制御信号に応じて前記入力ノードの容量値を変化させる容量制御部と、を各々が含むとともに、複数の行及び複数の列にわたって配された複数の画素と、前記複数の画素から出力される信号を、前記複数の画素の列ごとに読み出す読み出し回路と、を有し、前記複数の画素の各々は、一のフレーム期間において、前記第1の光電変換部で生成された電荷に基づく第1の信号と、前記第2の光電変換部で生成された電荷に少なくとも基づく第2の信号とを出力可能であり、前記複数の画素は、同一の行の互いに異なる列に配された第1の画素及び第2の画素を含み、前記一のフレーム期間において、前記第1の画素の前記第1の信号及び前記第2の信号の一方を得るために電荷を蓄積している蓄積時間と、前記第2の画素の前記第1の信号及び前記第2の信号の対応する一方を得るために電荷を蓄積している蓄積時間とは互いに異なり、前記第1の画素の前記容量制御部に第1の制御信号を供給する第1の制御信号線と、前記第2の画素の前記容量制御部に、前記第1の制御信号線により供給される前記第1の制御信号とは異なる第2の制御信号を供給する第2の制御信号線と、を有し、前記一のフレーム期間において、前記第1の画素の前記入力ノードの容量値と、前記第2の画素の前記入力ノードの容量値とは、互いに異なる値に制御されることを特徴とする撮像装置が提供される。

20

**【 0 0 0 6 】**

本発明の他の一観点によれば、入射光のうちの瞳分割された一部の光が入射される第1の光電変換部と、前記入射光のうちの瞳分割された他の一部の光が入射される第2の光電変換部と、入力ノードを有し、前記入力ノードに転送された電荷に基づく信号を出力する増幅部と、制御信号に応じて前記入力ノードの容量値を変化させる容量制御部と、を各々が含むとともに、複数の行及び複数の列にわたって配された複数の画素と、前記複数の画素から出力される信号を、前記複数の画素の列ごとに読み出す読み出し回路と、を有し、前記複数の画素の各々は、一のフレーム期間において、前記第1の光電変換部で生成された電荷に基づく第1の信号と、前記第1の光電変換部で生成された電荷及び前記第2の光電変換部で生成された電荷に基づく第2の信号とを出力可能であり、前記複数の画素は、同一の行の互いに異なる列に配された第1の画素及び第2の画素を含み、前記一のフレーム期間において、前記第1の画素は、前記第1の信号及び前記第2の信号を個別に出力し、前記一のフレーム期間において、前記第2の画素は、前記第1の画素に供給される制御信号とは異なる制御信号に応じて、前記第1の信号を出力せず、前記第2の信号を出力し、前記第1の画素の前記容量制御部に第1の制御信号を供給する第1の制御信号線と、前

30

40

50

記第2の画素の前記容量制御部に、前記第1の制御信号線により供給される前記第1の制御信号とは異なる第2の制御信号を供給する第2の制御信号線と、を有し、前記一のフレーム期間において、前記第1の画素の前記入力ノードの容量値と、前記第2の画素の前記入力ノードの容量値とは、互いに異なる値に制御されることを特徴とする撮像装置が提供される。

【0007】

本発明の他の観点によれば、上述のいずれかの撮像装置を有する撮像システム及び移動体が提供される。

【発明の効果】

【0008】

本発明によれば、更なる高機能化を実現し得る撮像装置を提供することができる。

10

【図面の簡単な説明】

【0009】

【図1】本発明の第1実施形態に係る撮像装置の概略構成を示すブロック図である。

【図2】本発明の第1実施形態に係る画素アレイの構成を示す回路図である。

【図3】本発明の第1実施形態に係る画素アレイの断面模式図である。

【図4】本発明の第1実施形態及び第2実施形態に係る撮像装置の駆動方法を示すタイミング図である。

【図5】本発明の第3実施形態に係る画素アレイの構成を示す回路図である。

20

【図6】本発明の第3実施形態に係るカラーフィルタの配列図である。

【図7】本発明の第4実施形態に係る画素アレイの構成を示す回路図である。

【図8】本発明の第5実施形態に係る画素アレイの構成を示す回路図である。

【図9】本発明の第6実施形態に係る画素アレイの構成を示す回路図である。

【図10】本発明の第6実施形態に係る撮像装置の駆動方法を示すタイミング図である。

【図11】本発明の第7実施形態に係る撮像システムの概略構成を示すブロック図である。

【図12】本発明の第8実施形態による撮像システム及び移動体の構成例を示す図である。

【発明を実施するための形態】

【0010】

以下に、本発明の好ましい実施形態を、添付の図面を参照しつつ説明する。複数の図面にわたって対応する要素には共通の符号を付し、その説明を省略又は簡略化することがある。

30

【0011】

[第1実施形態]

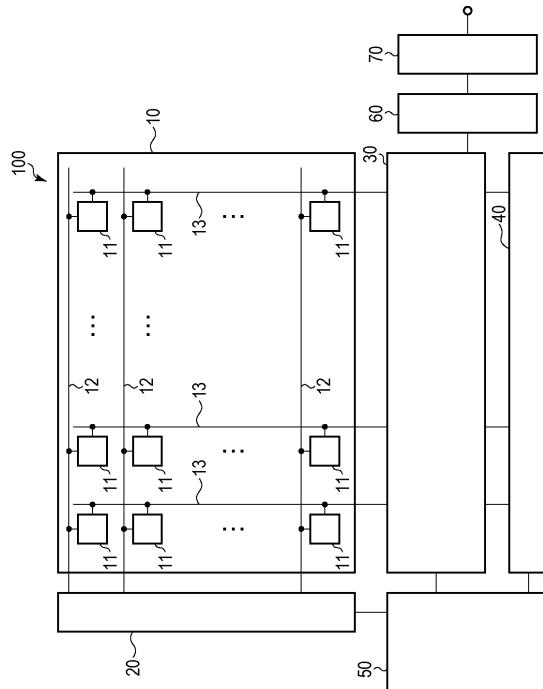

図1は、本発明の第1実施形態に係る撮像装置100の概略構成を示すブロック図である。撮像装置100は、画素アレイ10、垂直走査回路20、読み出し回路30、水平走査回路40、タイミングジェネレータ(以下、TGと呼称する)50、デジタルシグナルプロセッサ(以下、DSPと呼称する)60及び出力回路70を有する。

【0012】

画素アレイ10は、複数の行及び複数の列にわたって配された複数の画素11を有する。複数の画素11の各々は、入射される光に応じた電荷を生成する光電変換部を複数個有する。

40

【0013】

垂直走査回路20は、複数の画素11の各々から信号を出力させるための複数の制御信号を出力する回路である。複数の制御信号は、画素アレイ10の行ごとに設けられた制御信号線群12を介して画素11に供給される。なお、図1において、各行に対応する制御信号線群12は1本のみにより図示されているが、実際には制御信号線群12は複数本の制御信号線により構成される。

【0014】

画素11から出力される信号は、画素アレイ10の列ごとに設けられた垂直出力線13を介して、読み出し回路30に入力される。読み出し回路30は、画素11から出力され

50

た信号を列ごとに読み出して、増幅、A/D変換、相関二重サンプリング等の処理を行う回路である。

【0015】

水平走査回路40は、読み出し回路30において処理された信号を列ごとに順次DSP60に転送させるための制御信号を読み出し回路30に供給する回路である。DSP60は、入力された信号に対し、所定のデジタル信号処理を行い、出力回路70に出力する。出力回路70は、DSP60から入力された信号を撮像装置100の外部に出力する。

【0016】

TG50は、垂直走査回路20、読み出し回路30及び水平走査回路40に対し、動作タイミングの制御等のための制御信号を供給する回路である。図1では、垂直走査回路20、読み出し回路30及び水平走査回路40を制御する制御信号はTG50から供給されるように図示されているが、当該制御信号の一部又は全部は撮像装置100の外部から供給されてもよい。

10

【0017】

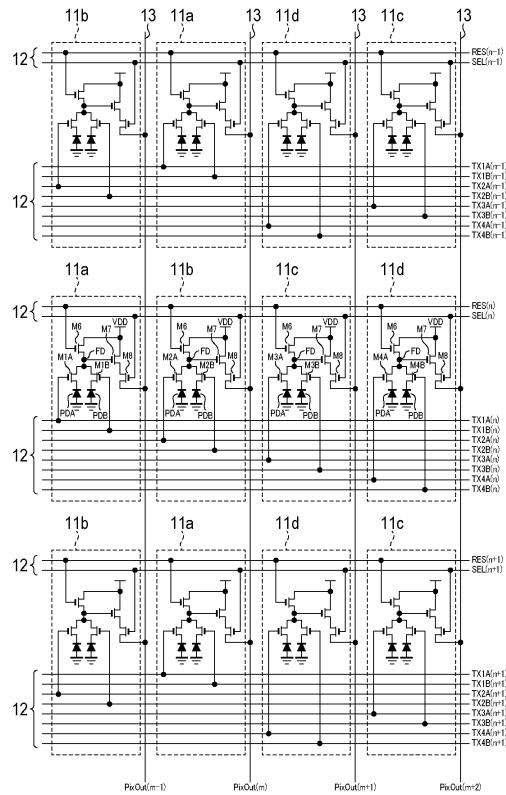

図2は、本実施形態に係る画素アレイ10の構成を示す回路図である。図2には、画素アレイ10のうちの3行×4列に配された12個の画素11a、11bが図示されているが、一般的には画素アレイ10は、更に多くの画素11a、11bを含み得る。以下の説明では、図2に示されている3行は、画素アレイ10の中のn-1行目、n行目及びn+1行目であるものとし、図2に示されている4列は、画素アレイ10の中のm-1列目、m列目、m+1列目及びm+2列目であるものとする。

20

【0018】

ここで、図2における画素11a、11bは、図1における画素11に対応するものであり、画素11aと画素11bとの相違点は、制御信号線群12に対する接続関係である。図2に示されているように、同一の列において、画素11aと画素11bは交互に配されている。また、同一の行においても、画素11aと画素11bは交互に配されている。

【0019】

n行m-1列目に配された画素11a（第1の画素）と、n行m列目に配された画素11b（第2の画素）の構成について説明する。他の画素11a、11bは同様の構成であるため、説明を省略する。

30

【0020】

まず、画素11aの構成について説明する。画素11aは、光電変換部PDA、PDB、転送トランジスタM1A、M1B、リセットトランジスタM6、増幅トランジスタM7、選択トランジスタM8を有する。

【0021】

光電変換部PDA（第1の光電変換部）、光電変換部PDB（第2の光電変換部）は、例えばフォトダイオードにより構成される。光電変換部PDA、PDBのアノードは、接地電圧線に接続されている。光電変換部PDAのカソードは、転送トランジスタM1Aのソースに接続され、光電変換部PDBのカソードは、転送トランジスタM1Bのソースに接続されている。光電変換部PDAと光電変換部PDBには撮像光学系の射出瞳の異なる領域を通過した光が入射される。言い換えると、光電変換部PDAには、入射光のうちの瞳分割された一部の光が入射され光電変換部PDBには、入射光のうちの瞳分割された他の一部の光が入射される。

40

【0022】

転送トランジスタM1A、M1Bのドレインは、リセットトランジスタM6のソース及び増幅トランジスタM7のゲートに接続されている。転送トランジスタM1A、M1Bのドレイン、リセットトランジスタM6のソース及び増幅トランジスタM7のゲートが相互に接続されているノードは、浮遊拡散領域FDである。浮遊拡散領域FDは、転送トランジスタM1A、M1Bにより転送された電荷を保持する機能を有する。

【0023】

リセットトランジスタM6のドレイン及び増幅トランジスタM7のドレインは、電源電

50

圧線 V D D に接続されている。増幅トランジスタ M 7 のソースは、選択トランジスタ M 8 のドレインに接続されている。選択トランジスタ M 8 のソースは、垂直出力線 1 3 に接続されている。

#### 【 0 0 2 4 】

次に、画素 1 1 a の構成について説明する。画素 1 1 b は、画素 1 1 a に隣接して配されている画素である。例えば、同一の n 行目において、画素 1 1 b は、画素 1 1 a が配されている m - 1 列目の隣の列である m 列目に配されている。画素 1 1 b は、光電変換部 P D A、P D B、転送トランジスタ M 2 A、M 2 B、リセットトランジスタ M 6、増幅トランジスタ M 7、選択トランジスタ M 8 を有する。転送トランジスタ M 2 A、M 2 B と制御信号線群 1 2 との接続関係を除き、画素 1 1 b 内の素子の接続関係は画素 1 1 a と同様であるため説明を省略する。

10

#### 【 0 0 2 5 】

画素アレイ 1 0 の各行には、行方向（図 2 において横方向）に延在する制御信号線群 1 2 が配されている。各行の制御信号線群 1 2 は、制御信号線 TX 1 A、TX 1 B、TX 2 A、TX 2 B、RES、SEL を含む。

#### 【 0 0 2 6 】

制御信号線 TX 1 A は、同一行に並ぶ画素 1 1 a の転送トランジスタ M 1 A のゲートにそれぞれ接続され、これらの画素 1 1 a に共通の信号線をなしている。制御信号線 TX 1 B は、行方向に並ぶ画素 1 1 a の転送トランジスタ M 1 B のゲートにそれぞれ接続され、これらの画素 1 1 a に共通の信号線をなしている。

20

#### 【 0 0 2 7 】

制御信号線 TX 2 A は、同一行に並ぶ画素 1 1 b の転送トランジスタ M 2 A のゲートにそれぞれ接続され、これらの画素 1 1 b に共通の信号線をなしている。制御信号線 TX 2 B は、行方向に並ぶ画素 1 1 b の転送トランジスタ M 2 B のゲートにそれぞれ接続され、これらの画素 1 1 b に共通の信号線をなしている。

#### 【 0 0 2 8 】

制御信号線 RES は、行方向に並ぶ画素 1 1 a、1 1 b のリセットトランジスタ M 6 のゲートにそれぞれ接続され、これらの画素 1 1 a、1 1 b に共通の信号線をなしている。制御信号線 SEL は、行方向に並ぶ画素 1 1 a、1 1 b の選択トランジスタ M 8 のゲートにそれぞれ接続され、これらの画素 1 1 a、1 1 b に共通の信号線をなしている。

30

#### 【 0 0 2 9 】

なお、図 2 においては、各制御信号線の名称に、対応する行番号をそれぞれ付すことにより（例えば、TX 1 A (m)、TX 1 A (m + 1)）、各行の制御信号線を区別している。この表記方法は、図 3 以降においても同様に適用される。

#### 【 0 0 3 0 】

制御信号線 TX 1 A、TX 1 B、TX 2 A、TX 2 B、RES、SEL は、垂直走査回路 2 0 に接続されている。制御信号線 TX 1 A には、垂直走査回路 2 0 から、転送トランジスタ M 1 A を制御するための制御信号 p TX 1 A が出力される。制御信号線 TX 1 B には、垂直走査回路 2 0 から、転送トランジスタ M 1 B を制御するための制御信号 p TX 1 B が出力される。制御信号線 TX 2 A には、垂直走査回路 2 0 から、転送トランジスタ M 2 A を制御するための制御信号 p TX 2 A が出力される。制御信号線 TX 2 B には、垂直走査回路 2 0 から、転送トランジスタ M 2 B を制御するための制御信号 p TX 2 B が出力される。制御信号線 RES には、垂直走査回路 2 0 から、リセットトランジスタ M 6 を制御するための制御信号 p RES が出力される。制御信号線 SEL には、垂直走査回路 2 0 から、選択トランジスタ M 8 を制御するための制御信号 p SEL が出力される。

40

#### 【 0 0 3 1 】

典型例では、垂直走査回路 2 0 からハイレベルの制御信号が出力されると対応するトランジスタがオンとなり、垂直走査回路 2 0 からローレベルの制御信号が出力されると対応するトランジスタがオフとなる。垂直走査回路 2 0 は、TG 5 0 から出力された所定のタイミング信号に応じて、これらの制御信号を供給する。垂直走査回路 2 0 には、シフトレ

50

ジスタ、アドレスデコーダ等の論理回路が用いられる。

【0032】

画素アレイ10の各列には、列方向(図2において縦方向)に延在する垂直出力線13が配されている。垂直出力線13は、列方向に並ぶ画素11a、11bの選択トランジスタM8のソースにそれぞれ接続され、これらの画素11a、11bに共通の信号線をなしている。なお、画素11a、11bの選択トランジスタM8は、省略されていてもよい。この場合、垂直出力線13は、増幅トランジスタM7のソースに接続される。垂直出力線13の各々には、不図示の電流源が接続されている。

【0033】

光電変換部PDA、PDBは、光電変換により入射光に応じた電荷を生成するとともに、生成された電荷を蓄積する。転送トランジスタM1A、M2Aは、光電変換部PDAに蓄積された電荷を浮遊拡散領域FDに転送する。転送トランジスタM1B、M2Bは、光電変換部PDBに蓄積された電荷を浮遊拡散領域FDに転送する。

10

【0034】

リセットトランジスタM6は、浮遊拡散領域FD及び光電変換部PDA、PDBの電位をリセットする。選択トランジスタM8は、垂直出力線13に信号を出力する画素11a、11bを選択する。増幅トランジスタM7は、ドレインに電源電圧が供給され、ソースに選択トランジスタM8を介して電流源からバイアス電流が供給される構成となっている。これにより、増幅トランジスタM7は、浮遊拡散領域FDに接続されたゲートを入力ノードとする増幅部(ソースフォロワ回路)を構成する。このようにして、増幅トランジスタM7は、入射光によって生じた電荷に基づく出力信号PixOutを、垂直出力線13に出力する。なお、図2においては、出力信号PixOutに、対応する列番号をそれぞれ付すことにより(例えば、PixOut(m-1), PixOut(m))、各列の出力信号を区別している。この表記方法は、図3以降においても同様に適用される。

20

【0035】

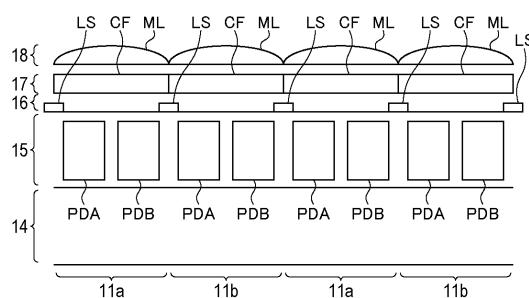

図3は、本実施形態に係る画素アレイ10の断面模式図である。図3に示される断面図には、配線層14、光電変換層15、遮光部形成層16、カラーフィルタ形成層17及びマイクロレンズ形成層18が図示されている。光電変換層15は、シリコン基板等の半導体基板により構成されている。光電変換層15内には、フォトダイオード等の光電変換部PDA、PDBが形成されている。

30

【0036】

図3に示されるように光電変換層15の下方(基板の表側)には配線層14が形成されている。また、光電変換層15の上方(基板の裏側)には遮光部形成層16、カラーフィルタ形成層17及びマイクロレンズ形成層18がこの順に形成されている。

【0037】

配線層14は、制御信号線群12、垂直出力線13等の配線が形成される層である。遮光部形成層16は、複数の遮光部LSが形成される層である。カラーフィルタ形成層17は、複数のカラーフィルタCFが形成される層である。マイクロレンズ形成層18は複数のマイクロレンズMLが形成される層である。なお、各層の間には不図示の平坦化層が更に形成されていてもよい。

40

【0038】

遮光部LSは、平面視において画素間に対応する位置に配されており、入射光が隣の画素に入射されにくくする機能を有する。これにより、混色の影響により画質劣化が軽減される。カラーフィルタCFは、画素11a、11bの各々に対応して配されており、入射光に対して所定の分光特性を有する。これにより、カラーフィルタCFは、入射光のうちの特定の波長の光を透過させる機能を有する。マイクロレンズMLは、画素11a、11bの各々に対応して配されており、入射光を光電変換部PDA、PDBに集光させることにより感度を向上させる機能を有する。

【0039】

上述の構成により、画素11a、11bは、マイクロレンズ形成層18側から入射され

50

た光を受光して電気信号を出力する。すなわち、本実施形態の撮像装置 100 は、配線層 14 が設けられている面と反対側の面に照射された光を検出可能な、いわゆる裏面照射型のイメージセンサである。裏面照射型では、入射光が通過する側とは反対側に配線を形成することができるため、配線の設計自由度が高い。本実施形態の撮像装置 100 は、制御信号線の本数が多くなりやすいため、配線設計の容易性及び素子面積低減の観点から裏面照射型を採用することが望ましい。しかしながら、撮像装置 100 の構成は、裏面照射型に限られるものではなく、配線層 14 が設けられている面から照射された光を検出可能な表面照射型であってもよい。

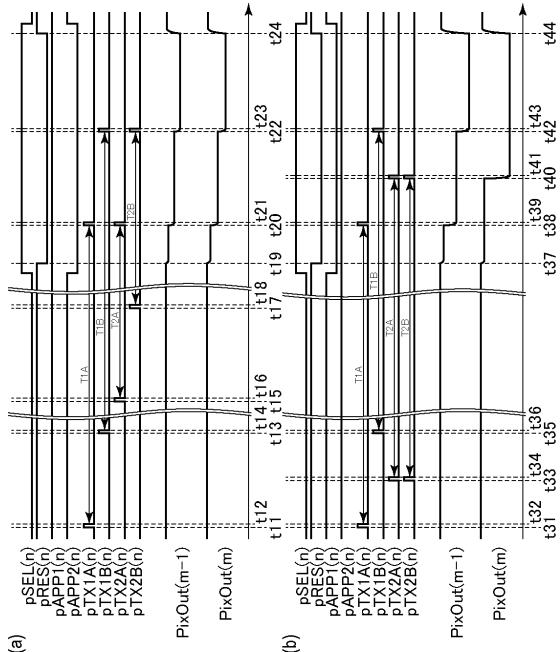

#### 【0040】

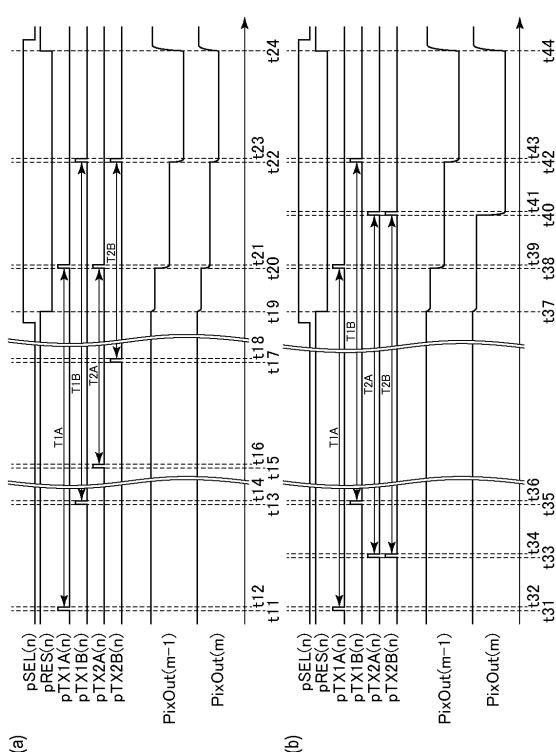

図 4 (a) は、本実施形態に係る撮像装置 100 の駆動方法を示すタイミング図である。図 4 (a) は、撮像装置 100 の 1 フレーム期間における n 行目の画素 11a、11b に関する制御信号及び出力信号が示されている。より具体的には、図 4 (a) には、n 行目の画素 11a、11b に供給される制御信号 p SEL (n)、p RES (n)、p TX 1A (n)、p TX 1B (n)、p TX 2A (n)、p TX 2B (n) が示されている。また、図 4 (a) には、m - 1 行目の垂直出力線 13 から出力される出力信号 Pi x Out (m - 1) と、m 行目の垂直出力線 13 から出力される Pi x Out (m) とが示されている。図 4 (a) を参照しつつ、撮像装置 100 の動作を説明する。

10

#### 【0041】

時刻 t 11 よりも前の期間において、制御信号 p SEL (n) はローレベルであり、選択トランジスタ M8 はオフになっており、n 行目の画素 11a、11b は非選択状態である。また、同期間ににおいて、制御信号 p RES (n) はハイレベルであり、リセットトランジスタ M6 はオンになっており、浮遊拡散領域 FD はリセット状態の電位になっている。また、制御信号 p TX 1A (n)、p TX 1B (n)、p TX 2A (n)、p TX 2B (n) はいずれもローレベルである。

20

#### 【0042】

時刻 t 11 において、制御信号 p TX 1A (n) がハイレベルになり、転送トランジスタ M1A がオンになる。その後時刻 t 12 において、制御信号 p TX 1A (n) がローレベルになり、転送トランジスタ M1A がオフになる。この動作により、画素 11a の光電変換部 PDA がリセットされる。そして、画素 11a の光電変換部 PDA は、時刻 t 12 から入射光に基づく電荷の蓄積を開始する。

30

#### 【0043】

時刻 t 13 において、制御信号 p TX 1B (n) がハイレベルになり、転送トランジスタ M1B がオンになる。その後時刻 t 14 において、制御信号 p TX 1B (n) がローレベルになり、転送トランジスタ M1B がオフになる。この動作により、画素 11a の光電変換部 PDB がリセットされる。そして、画素 11a の光電変換部 PDB は、時刻 t 14 から入射光に基づく電荷の蓄積を開始する。

30

#### 【0044】

時刻 t 15 において、制御信号 p TX 2A (n) がハイレベルになり、転送トランジスタ M2A がオンになる。その後時刻 t 16 において、制御信号 p TX 2A (n) がローレベルになり、転送トランジスタ M2A がオフになる。この動作により、画素 11b の光電変換部 PDA がリセットされる。そして、画素 11b の光電変換部 PDA は、時刻 t 16 から入射光に基づく電荷の蓄積を開始する。

40

#### 【0045】

時刻 t 17 において、制御信号 p TX 2B (n) がハイレベルになり、転送トランジスタ M2B がオンになる。その後時刻 t 18 において、制御信号 p TX 2B (n) がローレベルになり、転送トランジスタ M2B がオフになる。この動作により、画素 11b の光電変換部 PDB がリセットされる。そして、画素 11b の光電変換部 PDB は、時刻 t 18 から入射光に基づく電荷の蓄積を開始する。

#### 【0046】

時刻 t 18 の後、制御信号 p SEL (n) がハイレベルになり、選択トランジスタ M8

50

がオンになる。これにより、 $n$ 行目の画素 $11a$ 、 $11b$ が選択された状態となる。その後の時刻 $t_{19}$ において、制御信号 $pRES(n)$ がローレベルになり、リセットトランジスタ $M6$ がオフになる。

#### 【0047】

この動作に伴って浮遊拡散領域 $FD$ の電位が微小変動するため、出力信号 $PixOut(m-1)$ 、 $PixOut(m)$ もわずかに変化する。この電位の変化量はリセットを行うごとにばらつくため、ノイズとなり得る。そこで、時刻 $t_{19}$ と時刻 $t_{20}$ の間の期間において、読み出し回路 $30$ は、出力信号 $PixOut(m-1)$ 、 $PixOut(m)$ をノイズ信号として読み出す。入射光に基づく光信号とノイズ信号との差分を取得する相関二重サンプリングを行うことにより、リセットレベルのばらつきに起因するノイズが除去され得る。

10

#### 【0048】

時刻 $t_{20}$ において、制御信号 $pTX1A(n)$ 、 $pTX2A(n)$ がハイレベルになり、転送トランジスタ $M1A$ 、 $M2A$ がオンになる。その後時刻 $t_{21}$ において、制御信号 $pTX1A(n)$ 、 $pTX2A(n)$ がローレベルになり、転送トランジスタ $M1A$ 、 $M2A$ がオフになる。この動作により、画素 $11a$ の光電変換部 $PDA$ に蓄積された電荷が画素 $11a$ の浮遊拡散領域 $FD$ に転送される。また、画素 $11b$ の光電変換部 $PDA$ に蓄積された電荷も画素 $11b$ の浮遊拡散領域 $FD$ に転送される。ここで、画素 $11a$ の光電変換部 $PDA$ における電荷の蓄積時間は、時刻 $t_{12}$ から時刻 $t_{20}$ の間の期間 $T1A$ の長さに相当する。また、画素 $11b$ の光電変換部 $PDA$ における電荷の蓄積時間は、時刻 $t_{16}$ から時刻 $t_{20}$ の間の期間 $T2A$ の長さに相当する。

20

#### 【0049】

この電荷の転送に伴って、画素 $11a$ 及び画素 $11b$ の浮遊拡散領域 $FD$ の電位は変動し、出力信号 $PixOut(m-1)$ 、 $PixOut(m)$ も変化する。時刻 $t_{21}$ と時刻 $t_{22}$ の間の期間において、読み出し回路 $30$ は、出力信号 $PixOut(m-1)$ 、 $PixOut(m)$ を入射光に基づく光信号（ $A$ 信号又は第1の信号）として読み出す。同一行に配された画素 $11a$ 、 $11b$ からの電荷の転送が同時に行われているため、読み出し回路 $30$ は、 $TG50$ からの制御信号に応じて、複数の列の信号の読み出しを同時に実行する。

#### 【0050】

30

これにより、画素 $11a$ の光電変換部 $PDA$ において期間 $T1A$ に生成された電荷に基づく $A$ 信号と、画素 $11b$ の光電変換部 $PDA$ において期間 $T2A$ に生成された電荷に基づく $A$ 信号とが取得される。

#### 【0051】

時刻 $t_{22}$ において、制御信号 $pTX1B(n)$ 、 $pTX2B(n)$ がハイレベルになり、転送トランジスタ $M1B$ 、 $M2B$ がオンになる。その後時刻 $t_{23}$ において、制御信号 $pTX1B(n)$ 、 $pTX2B(n)$ がローレベルになり、転送トランジスタ $M1B$ 、 $M2B$ がオフになる。この動作により、画素 $11a$ の光電変換部 $PDB$ に蓄積された電荷が画素 $11a$ の浮遊拡散領域 $FD$ に転送される。また、画素 $11b$ の光電変換部 $PDB$ に蓄積された電荷も画素 $11b$ の浮遊拡散領域 $FD$ に転送される。ここで、画素 $11a$ の光電変換部 $PDB$ における電荷の蓄積時間は、時刻 $t_{14}$ から時刻 $t_{22}$ の間の期間 $T1B$ の長さに相当する。また、画素 $11b$ の光電変換部 $PDB$ における電荷の蓄積時間は、時刻 $t_{18}$ から時刻 $t_{22}$ の間の期間 $T2B$ の長さに相当する。

40

#### 【0052】

この電荷の転送に伴って、画素 $11a$ 及び画素 $11b$ の浮遊拡散領域 $FD$ の電位は変動し、出力信号 $PixOut(m-1)$ 、 $PixOut(m)$ も変化する。時刻 $t_{23}$ と時刻 $t_{24}$ の間の期間において、読み出し回路 $30$ は、出力信号 $PixOut(m-1)$ 、 $PixOut(m)$ を入射光に基づく光信号（ $A+B$ 信号又は第2の信号）として読み出す。この処理においても、同一行に配された画素 $11a$ 、 $11b$ からの電荷の転送が同時に行われているため、読み出し回路 $30$ は、 $TG50$ からの制御信号に応じて、複数の列

50

の信号の読み出しを同時に行い得る。なお、読み出される光信号は、光電変換部 P D A で蓄積された電荷と光電変換部 P D B で蓄積された電荷を加算したものに相当する信号である。

【 0 0 5 3 】

これにより、画素 1 1 a の光電変換部 P D A において期間 T 1 A に生成された電荷と、画素 1 1 a の光電変換部 P D B において期間 T 1 B に生成された電荷との両方に基づく A + B 信号が取得される。また、画素 1 1 b の光電変換部 P D A において期間 T 2 A に生成された電荷と、画素 1 1 b の光電変換部 P D B において期間 T 2 B に生成された電荷との両方に基づく A + B 信号が取得される。

【 0 0 5 4 】

時刻  $t_{24}$  において、制御信号  $p_{RES}(n)$  がハイレベルになり、リセットトランジスタ M 6 がオンになる。これにより、浮遊拡散領域 F D はリセット状態に戻り、n 行目の画素 1 1 a、1 1 b からの読み出しの処理が終了する。

【 0 0 5 5 】

撮像装置 1 0 0 の外部の信号処理回路等により A + B 信号と A 信号の差分を取得することにより、B 信号が取得される。A 信号と B 信号は、撮像光学系の異なる瞳領域を通過した光（すなわち瞳分割された光）により生じた電荷に基づく信号であるため、位相差焦点検出に用いられる焦点検出信号である。また、A + B 信号は、画像の生成に用いられる撮像信号である。このようにして、本実施形態の撮像装置 1 0 0 は、一のフレーム期間内に焦点検出信号と撮像信号を並行して取得可能である。

【 0 0 5 6 】

また、本実施形態の撮像装置 1 0 0 において、画素 1 1 a における電荷の蓄積時間（期間 T 1 A、T 1 B の長さ）は、画素 1 1 b における電荷の蓄積時間（期間 T 2 A、T 2 B の長さ）よりも大きい。これにより、焦点検出信号及び撮像信号のそれぞれを 2 種類の蓄積時間により生成することができる。焦点検出及び撮像におけるダイナミックレンジは、飽和電荷量等による制限が存在するが、2 種類の蓄積時間で信号を取得し、輝度に応じてこれらを適宜使い分ける処理を行うことによりダイナミックレンジを拡大することができる。

【 0 0 5 7 】

以上のように、本実施形態によれば、画素 1 1 a と画素 1 1 b とで蓄積時間が異なる信号を出力させることにより、ダイナミックレンジの拡大に適した焦点検出信号及び撮像信号を取得することができる。したがって、更なる高機能化を実現し得る撮像装置 1 0 0 が提供される。

【 0 0 5 8 】

図 2 において、画素 1 1 a と画素 1 1 b は、同一行内において交互に配列されている。また、画素 1 1 a と画素 1 1 b は、同一列内においても交互に配列されている。このような配置とすることにより、同一行内又は同一行列内に画素 1 1 a と画素 1 1 b を画素アレイ 1 0 内に均一な密度で配置することができる。しかしながら、画素 1 1 a と画素 1 1 b の配列方法は図 2 に示すものに限られるものではなく、例えば、2 行ごと又は 2 列ごとに画素 1 1 a と画素 1 1 b が入れ替わるようなパターンであってもよい。

【 0 0 5 9 】

また、上記の読み出し方法の変形例として、A 信号の読み出しと B 信号の読み出しとの間に、リセット動作を行ってもよい。このような駆動によれば、A 信号と B 信号とを独立に得ることができる。そして、撮像装置 1 0 0 の外部の信号処理回路等により A 信号と B 信号の和を取得することにより、A + B 信号が取得される。

【 0 0 6 0 】

[ 第 2 実施形態 ]

図 4 ( b ) を参照して、本発明の第 2 実施形態を説明する。第 2 実施形態において、第 1 実施形態と異なる点は、各制御信号が供給されるタイミングである。画素 1 1 a、1 1 b の回路構成、撮像装置 1 0 0 のブロック等、各制御信号の供給タイミング以外の点につ

10

20

30

40

50

いては第1実施形態と同様であるため説明を省略する。図4(b)は、本実施形態に係る撮像装置100の駆動方法を示すタイミング図である。図4(b)を参照しつつ、撮像装置100の動作を説明する。

#### 【0061】

時刻t33以前の動作は、第1実施形態の時刻t13以前の動作と同様であるため説明を省略する。時刻t33において、制御信号pTX2A(n)、pTX2B(n)がハイレベルになり、転送トランジスタM2A、M2Bがオンになる。その後時刻t34において、制御信号pTX2A(n)、pTX2B(n)がローレベルになり、転送トランジスタM2A、M2Bがオフになる。この動作により、画素11bの光電変換部PDA、PDBが同時にリセットされる。そして、画素11bの光電変換部PDA、PDBは、時刻t34から入射光に基づく電荷の蓄積を開始する。

10

#### 【0062】

時刻t35、t36の動作は、第1実施形態の時刻t13、t14の動作と同様であるため説明を省略する。また、時刻t37の前後の制御信号pSEL(n)、pRES(n)の駆動及びノイズ信号の読み出しについても、第1実施形態の時刻t19の前後のこれらの動作と同様であるため説明を省略する。

#### 【0063】

時刻t38において、制御信号pTX1A(n)がハイレベルになり、転送トランジスタM1Aがオンになる。その後時刻t39において、制御信号pTX1A(n)がローレベルになり、転送トランジスタM1Aがオフになる。この動作により、画素11aの光電変換部PDAに蓄積された電荷が画素11aの浮遊拡散領域FDに転送される。ここで、画素11aの光電変換部PDAにおける電荷の蓄積時間は、時刻t32から時刻t38の間の期間T1Aの長さに相当する。

20

#### 【0064】

この電荷の転送に伴って、画素11aの浮遊拡散領域FDの電位は変動し、出力信号PixOut(m-1)も変化する。時刻t39と時刻t40の間の期間において、読み出し回路30は、出力信号PixOut(m-1)を入射光に基づく光信号(A信号)として読み出す。これにより、画素11aの光電変換部PDAにおいて期間T1Aに生成された電荷に基づくA信号が取得される。

30

#### 【0065】

時刻t40において、制御信号pTX2A(n)、pTX2B(n)がハイレベルになり、転送トランジスタM2A、M2Bがオンになる。その後時刻t41において、制御信号pTX2A(n)、pTX2B(n)がローレベルになり、転送トランジスタM2A、M2Bがオフになる。この動作により、画素11bの光電変換部PDA、PDBに蓄積された電荷が画素11bの浮遊拡散領域FDに転送される。ここで、画素11bの光電変換部PDA、PDBにおける電荷の蓄積時間は、それぞれ、時刻t34から時刻t40の間の期間T2A、T2Bの長さに相当する。本実施形態においては、転送トランジスタM2A、M2Bによる転送は同時に行われる所以、期間T2Aと期間T2Bは同一である。

#### 【0066】

この電荷の転送に伴って、画素11bの浮遊拡散領域FDの電位は変動し、出力信号PixOut(m)も変化する。時刻t41と時刻t42の間の期間において、読み出し回路30は、出力信号PixOut(m)を入射光に基づく光信号(A+B信号)として読み出す。この光信号は、光電変換部PDAで蓄積された電荷と光電変換部PDBで蓄積された電荷を加算したものに相当する信号である。

40

#### 【0067】

時刻t42において、制御信号pTX1B(n)がハイレベルになり、転送トランジスタM1Bがオンになる。その後時刻t43において、制御信号pTX1B(n)がローレベルになり、転送トランジスタM1Bがオフになる。この動作により、画素11aの光電変換部PDBに蓄積された電荷が画素11aの浮遊拡散領域FDに転送される。ここで、画素11aの光電変換部PDBにおける電荷の蓄積時間は、時刻t36から時刻t42の

50

間の期間  $T_{1B}$  の長さに相当する。

【0068】

この電荷の転送に伴って、画素 11a の浮遊拡散領域 FD の電位は変動し、出力信号  $P_{i \times Out}(m-1)$  も変化する。時刻  $t_{43}$  と時刻  $t_{44}$  の間の期間において、読み出し回路 30 は、出力信号  $P_{i \times Out}(m-1)$  を入射光に基づく光信号 (A + B 信号) として読み出す。この光信号は、光電変換部 PDA で蓄積された電荷と光電変換部 PDB で蓄積された電荷を加算したものに相当する信号である。時刻  $t_{44}$  の動作は、第 1 実施形態の時刻  $t_{24}$  の動作と同様であるため説明を省略する。

【0069】

以上のように本実施形態においては、同一行の画素 11a、11b に対し制御信号  $p_{TX1A}(n)$ 、 $p_{TX1B}(n)$ 、 $p_{TX2A}(n)$ 、 $p_{TX2B}(n)$  の 4 種の制御信号により電荷の転送が制御される。この制御により、画素 11a は、A 信号と A + B 信号を個別に出力し、画素 11b は、A + B 信号のみを出力する。画素 11a から出力された信号に対しては、撮像装置 100 の外部の信号処理回路等により A + B 信号と A 信号の差分を取得することにより、B 信号が取得可能である。第 1 実施形態の場合と同様に、A 信号と B 信号は、焦点検出信号として用いられ、A + B 信号は撮像信号として用いられる。したがって、本実施形態の撮像装置 100 も、第 1 実施形態の場合と同様に、1 フレーム期間内に焦点検出信号と撮像信号を並行して取得可能である。

【0070】

また、本実施形態の撮像装置 100 は、画素 11b が A + B 信号のみを出力する構成であるため、読み出しの回数を削減することができる。これにより、信号処理時間の低減及び信号処理による消費電力の低減の効果が得られる。

【0071】

本実施形態では、焦点検出信号を出力可能な画素の個数が少なくなるが、信号処理時間の低減及び消費電力低減の効果が得られるため、焦点検出の精度がさほど要求されない場合に好適である。

【0072】

なお、図 4 (b)において、時刻  $t_{34}$  は、時刻  $t_{32}$  と時刻  $t_{36}$  の中間の時刻に設定されており、時刻  $t_{41}$  は、時刻  $t_{39}$  と時刻  $t_{43}$  の中間の時刻に設定されている。これにより、画素 11a と画素 11b の蓄積期間のずれ (撮影時刻のずれ) による画質への影響を低減することができる。しかしながら、この構成は必須ではなく、例えば、時刻  $t_{34}$  を時刻  $t_{32}$  又は時刻  $t_{36}$  と揃えてもよく、時刻  $t_{41}$  を時刻  $t_{39}$  又は時刻  $t_{43}$  と揃えてもよい。また、第 1 実施形態のように、画素 11a の蓄積期間の長さと画素 11b の蓄積期間の長さを異ならせてよい。この場合、第 1 実施形態と同様にダイナミックレンジを拡大する効果が得られる。

【0073】

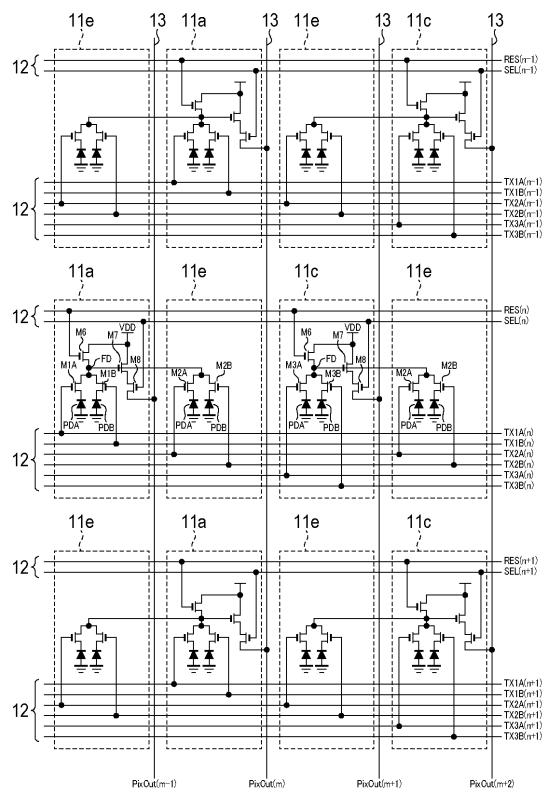

[第 3 実施形態]

図 5 を参照して、本発明の第 3 実施形態を説明する。第 3 実施形態において、第 1 又は第 2 実施形態と異なる点は、制御信号線の構成である。それ以外の点については第 1 又は第 2 実施形態と同様であるため説明を省略する。図 5 は、本実施形態に係る画素アレイ 10 の構成を示す回路図である。

【0074】

本実施形態では、制御信号線群 12 は、第 1 実施形態で述べたものに加えて、制御信号線  $TX3A$ 、 $TX3B$ 、 $TX4A$ 、 $TX4B$  を更に含む。また、画素アレイ 10 の  $n$  行目において、 $n+1$  列目には、画素 11c が配されており、 $n+2$  列目には、画素 11d が配されている。画素 11c は、制御信号線  $TX3A$  から制御信号が供給される転送トランジスタ  $M3A$  と、制御信号線  $TX3B$  から制御信号が供給される転送トランジスタ  $M3B$  とを有する。画素 11d は、制御信号線  $TX4A$  から制御信号が供給される転送トランジスタ  $M4A$  と、制御信号線  $TX4B$  から制御信号が供給される転送トランジスタ  $M4B$  とを有する。

10

20

30

40

50

## 【0075】

このように、本実施形態では、転送トランジスタ用の制御信号線が1行ごとに第1実施形態又は第2実施形態の2倍の8本設けられている。これにより、同一の行に配された4つの画素11a、11b、11c、11dに対して異なるタイミングで転送トランジスタM1A、M1B、M2A、M2B、M3A、M3B、M4A、M4Bの制御を行うことができる。

## 【0076】

本実施形態の構成は、同一行に複数の異なる色のカラーフィルタCFを有する配列においてより好適に用いられる。そのようなカラーフィルタCFの配列の例を説明する。図6は、本実施形態に係るカラーフィルタCFの配列図であり、画素アレイ10内におけるカラーフィルタCFの色の配列を模式的に示している。図中の「R」は、主として赤色の光を透過する分光特性を有するカラーフィルタCFが配置されている画素（R画素）を示している。図中の「G」は、主として緑色の光を透過する分光特性を有するカラーフィルタCFが配置されている画素（G画素）を示している。図中の「B」は、主として青色の光を透過する分光特性を有するカラーフィルタCFが配置されている画素（B画素）を示している。これにより、赤色、緑色、青色の各色によるカラー画像の撮像が可能となる。図6に示されている配列はベイヤー（Bayer）配列と呼ばれる配列であるが、これは一例であり、これ以外のパターンの配列が採用されてもよい。また、補色フィルタ等、上述以外の色のカラーフィルタCFが用いられる配列であってもよい。

10

## 【0077】

図6のようなベイヤー配列によるカラーフィルタCFを有する撮像装置100においては、同一行内に2色の画素が存在する。第1実施形態又は第2実施形態の構成では、転送トランジスタ用の制御信号線の本数が1行ごとに4本であるため、各色に対して異なるタイミングで図4（a）又は図4（b）のような駆動を行うことはできない。一方、本実施形態では、1行につき、転送トランジスタ用の制御信号線が第1実施形態又は第2実施形態の2倍の8本設けられているため、第1実施形態又は第2実施形態の駆動方法を画素の色ごとに異なるタイミングで実行することができる。

20

## 【0078】

以上のように、本実施形態によれば、第1実施形態又は第2実施形態と同様の駆動を行うことにより同様の効果が得られることに加え、画素の色ごとに異なるタイミングで転送トランジスタの駆動を行うことができるため、駆動方法の自由度が向上する。したがって、更なる高機能化を実現し得る撮像装置100が提供される。

30

## 【0079】

なお、上述の例では、画素の色ごとに異なるタイミングで転送させるために転送トランジスタ用の制御信号線の本数を第1実施形態又は第2実施形態よりも多くしているが、増加した制御信号線は他の目的で用いられてもよい。例えば、図4（a）の駆動方法を変形して、蓄積時間の種類を2種類から4種類に増加させることで、蓄積時間が異なる4種類の撮像信号及び焦点検出信号を出力させてもよい。これにより、ダイナミックレンジの拡大処理をより効果的に行うことができる。例えば、ダイナミックレンジを拡大した画像を生成するために画像を合成する処理を行う場合には、蓄積時間の種類が異なる画像の数が多いほど蓄積時間差に起因する合成後画像の不自然さが軽減される。

40

## 【0080】

## [第4実施形態]

図7を参照して、本発明の第4実施形態を説明する。第4実施形態において、第3実施形態と異なる点は、2つの画素が浮遊拡散領域FDを共有している点である。それ以外の点については第3実施形態と同様であるため説明を省略する。図7は、本実施形態に係る画素アレイ10の構成を示す回路図である。

## 【0081】

図7において、n行目の画素11a、11eに着目すると、画素11eの転送トランジスタM2A、M2Bのドレインが画素11eに隣接する画素11aの浮遊拡散領域FDに

50

接続されている。また、 $n$ 行目の画素  $11c$ 、 $11f$  に着目すると、画素  $11f$  の転送トランジスタ  $M4A$ 、 $M4B$  のドレインが画素  $11f$  に隣接する画素  $11c$  の浮遊拡散領域  $FD$  に接続されている。また、画素  $11e$ 、 $11f$  においては、リセットトランジスタ  $M6$ 、増幅トランジスタ  $M7$ 、選択トランジスタ  $M8$  等が省略されている。

#### 【0082】

本実施形態の構成においては、第1乃至第3実施形態と同様の駆動が可能であるとともに、画素  $11e$ 、 $11f$  内に設けられるトランジスタ等の回路部品の数を削減することができる。これにより、回路部品の占有面積を削減することができる。また、回路部品の削減により得られた面積を光電変換部  $PDA$ 、 $PDB$  等の面積に割り当てることで、飽和電荷量を増大させることができ、撮像装置  $100$  により撮像される画像の画質を向上することができる。したがって、更なる高機能化を実現し得る撮像装置  $100$  が提供される。

10

#### 【0083】

なお、削減された回路部品の占有面積は他の用途に割り当ててもよい。例えば、後述の第6実施形態で述べる容量付加トランジスタ、容量等の浮遊拡散領域  $FD$  の容量を増加させるための素子を追加してもよい。

#### 【0084】

また、図7では横方向に並ぶ2画素の浮遊拡散領域  $FD$  が共有されているが、これに限られない。例えば、縦方向に並ぶ2画素の浮遊拡散領域  $FD$  が共有されていてもよく、縦方向に2画素分、横方向に2画素分の合計4画素の浮遊拡散領域  $FD$  が共有されていてもよい。

20

#### 【0085】

##### [第5実施形態]

図8を参照して、本発明の第5実施形態を説明する。第5実施形態において、第4実施形態と異なる点は、制御信号線の構成である。それ以外の点については第4実施形態と同様であるため説明を省略する。図8は、本実施形態に係る画素アレイ  $10$  の構成を示す回路図である。

#### 【0086】

本実施形態では、第4実施形態で述べたものに対して、制御信号線群  $12$  から制御信号線  $TX4A$ 、 $TX4B$  が省略されている。また、画素アレイ  $10$  の  $n$  行目において、 $m$  列目及び  $m+2$  列目には、いずれも画素  $11e$  が配されている。画素  $11e$  の転送トランジスタ  $M2A$  には、共通の制御信号線  $TX2A$  から制御信号が供給される。また、画素  $11e$  の転送トランジスタ  $M2B$  には、共通の制御信号線  $TX2B$  から制御信号が供給される。このように本実施形態では、同一の行に含まれる4画素のうちの2つの転送トランジスタに対し共通の制御信号が供給される。

30

#### 【0087】

本実施形態においても第3及び第4実施形態と同様に駆動方法の自由度が向上する効果が得られる。転送トランジスタ用の制御信号線の本数が第3実施形態及び第4実施形態よりも少ないため、自由度向上の効果は劣るもの、第3実施形態及び第4実施形態に比べて制御信号線の本数を少なくすることができる。したがって、更なる高機能化を実現し得る撮像装置  $100$  が提供される。

40

#### 【0088】

本実施形態の構成では、例えば、ペイヤー配列中の同一行のR画素に対して異なる転送トランジスタ用の制御信号線を割り当てることができる。この場合、第2実施形態の駆動方法を適用すれば、同一行のR画素のうちの一部から焦点検出信号と撮像信号を出力させ、他の一部から撮像信号のみを出力させる駆動が可能となる。なお、本例におけるR画素は、G画素又はB画素に置き換えられてもよい。

#### 【0089】

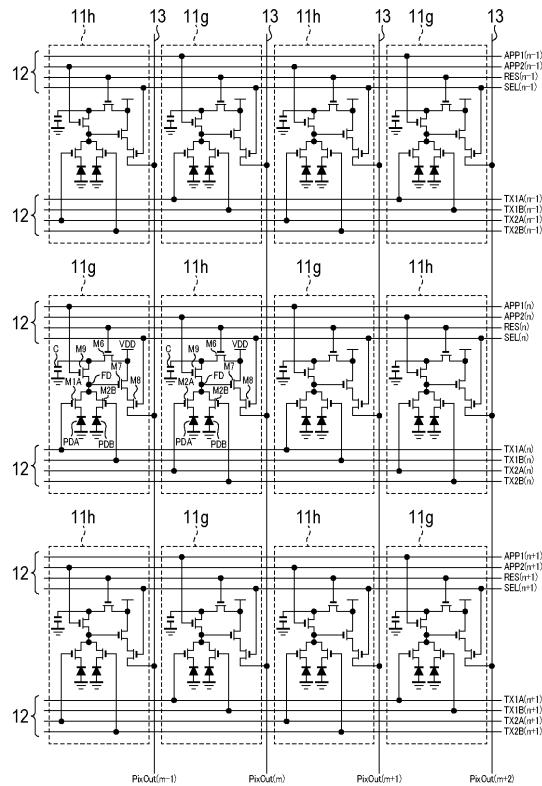

##### [第6実施形態]

図9、図10(a)及び図10(b)を参照して、本発明の第6実施形態を説明する。第6実施形態において、第1及び第2実施形態と異なる点は、容量付加トランジスタ  $M9$

50

(容量制御部)と容量Cが画素11h、11gの各々に設けられている点である。それ以外の点については第1及び第2実施形態と同様であるため説明を省略する。図9は、本実施形態に係る画素アレイ10の構成を示す回路図である。

#### 【0090】

画素11h、11gの各々において、浮遊拡散領域FDと、リセットトランジスタM6の間のノードには、容量付加トランジスタM9と容量Cが設けられている。容量付加トランジスタM9のソースは、浮遊拡散領域FDに接続されており、ドレンは、容量Cの一端及びリセットトランジスタM6のソースに接続されている。容量Cの他端は、接地電圧線に接続されている。

#### 【0091】

各行の制御信号線群12は、制御信号線APP1(第1の制御信号線)と制御信号線APP2(第2の制御信号線)を更に含む。制御信号線APP1は、同一行に並ぶ画素11gの容量付加トランジスタM9のゲートにそれぞれ接続され、これらの画素11gに共通の信号線をなしている。制御信号線APP2は、同一行に並ぶ画素11hの容量付加トランジスタM9のゲートにそれぞれ接続され、これらの画素11hに共通の信号線をなしている。

#### 【0092】

制御信号線APP1、APP2は、垂直走査回路20に接続されている。制御信号線APP1、APP2には、垂直走査回路20から、容量付加トランジスタM9を制御するための制御信号pAPP1、pAPP2がそれぞれ出力される。

#### 【0093】

図10(a)及び図10(b)を参照して、容量付加トランジスタM9の動作を説明する。図10(a)は、第1実施形態の図4(a)に対応する動作を示すタイミング図であり、図10(b)は、第2実施形態の図4(b)に対応する動作を示すタイミング図である。制御信号pAPP1、pAPP2以外の制御信号については第1実施形態又は第2実施形態と同一であるため、重複する説明を省略する。

#### 【0094】

図10(a)の時刻t18以前の期間において、制御信号pRES(n)、pAPP1(n)、pAPP2(n)は、いずれもハイレベルであり、画素11h、11gのリセットトランジスタM6、容量付加トランジスタM9は、オンになっている。これにより、時刻t18以前の期間においては、浮遊拡散領域FD、容量Cがリセットされている。

#### 【0095】

図10(a)の時刻t19以後の期間において、制御信号pRES(n)、pAPP2(n)はローレベルであり、制御信号pAPP1(n)はハイレベルである。そのため、画素11h、11gのリセットトランジスタM6はオフになっており、画素11gの容量付加トランジスタM9はオンになっており、画素11hの容量付加トランジスタM9はオフになっている。したがって、時刻t19以後の期間において、画素11gの浮遊拡散領域FDは容量Cが接続されている状態であるが、画素11hの浮遊拡散領域FDは容量Cが接続されていない状態である。すなわち、画素11gの浮遊拡散領域FDは容量値が増大されるが、画素11hの浮遊拡散領域FDは容量値が増大されない。

#### 【0096】

このように、本実施形態の図10(a)の駆動方法では、第1実施形態と同様に同一列の画素ごとに蓄積時間を変えることに加え、浮遊拡散領域FDの容量値の増大の有無を変えるような駆動が実現される。これにより、ダイナミックレンジの拡大をより効果的に実現することができる。なお、本例の駆動方法は、図10(a)とは逆に、時刻t19以後の期間において、画素11gの容量付加トランジスタM9はオフになり、画素11hの容量付加トランジスタM9はオンになるものであってもよい。

#### 【0097】

図10(b)は、図10(a)と同様の制御信号pRES(n)、pAPP1(n)、pAPP2(n)による駆動を第2実施形態の駆動方法に組み合わせたものである。この

10

20

30

40

50

構成においては、例えば、浮遊拡散領域 F D の容量値を増加させることで飽和電荷量を大きくすることができるため、高輝度な被写体に対する撮影又は焦点検出を行う際の信号の飽和が生じにくくなる効果が得られる。したがって、本実施形態によれば、更なる高機能化を実現し得る撮像装置 100 が提供される。

#### 【 0098 】

図 10 ( a ) 及び図 10 ( b ) においては、制御信号 p A P P 1 ( n )、p A P P 2 ( n ) のレベルは、基本的にハイレベルとなっており、ローレベルにする必要があるときにローレベルに変化させる駆動方法となっている。しかしながら、制御信号 p A P P 1 ( n )、p A P P 2 ( n ) のレベルを、基本的にローレベルとし、ハイレベルにする必要があるときにハイレベルに変化させる駆動方法であってもよい。

10

#### 【 0099 】

また、本実施形態においては、画素 11g と画素 11h の蓄積時間を揃えてもよい。一方で、画素 11g の容量付加トランジスタ M9 がオンであり、画素 11h の容量付加トランジスタ M9 がオフであるように制御する。このような制御により、蓄積時間を変えることなく、色に応じて異なるゲインの焦点検出信号又は撮像信号を得ることができる。

#### 【 0100 】

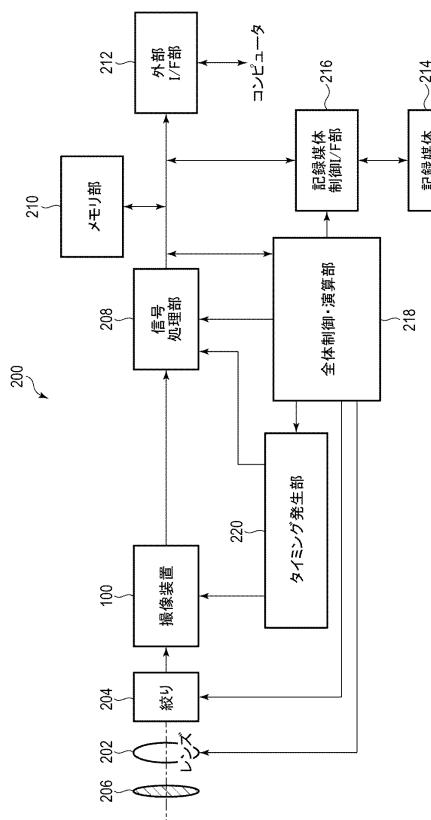

##### 〔 第 7 実施形態 〕

本発明の第 7 実施形態による撮像システムについて、図 11 を用いて説明する。第 1 乃至第 6 実施形態による撮像装置 100 と同様の構成要素には同一の符号を付し説明を省略しあるいは簡潔にする。図 11 は、本実施形態による撮像システムの概略構成を示すプロック図である。

20

#### 【 0101 】

上述の第 1 乃至第 6 実施形態で述べた撮像装置 100 は、種々の撮像システムに適用可能である。適用可能な撮像システムの例としては、デジタルスチルカメラ、デジタルカムコーダ、監視カメラ、複写機、ファックス、携帯電話、車載カメラ、観測衛星などが挙げられる。また、レンズなどの光学系と撮像装置とを備えるカメラモジュールも、撮像システムに含まれる。図 11 には、これらのうちの一例として、デジタルスチルカメラのプロック図を例示している。

#### 【 0102 】

図 11 に例示した撮像システム 200 は、撮像装置 100、被写体の光学像を撮像装置 100 に結像させるレンズ 202、レンズ 202 を通過する光量を可変にするための絞り 204、レンズ 202 の保護のためのバリア 206 を有する。レンズ 202 及び絞り 204 は、撮像装置 100 に光を集光する光学系である。撮像装置 100 は、第 1 乃至第 6 実施形態で説明した撮像装置 100 であって、レンズ 202 により結像された光学像を画像データに変換する。

30

#### 【 0103 】

撮像システム 200 は、また、撮像装置 100 より出力される出力信号の処理を行う信号処理部 208 を有する。信号処理部 208 は、必要に応じて各種の補正、圧縮を行って画像データを出力する動作を行う。信号処理部 208 は、撮像装置 100 が設けられた半導体基板に形成されていてもよいし、撮像装置 100 とは別の半導体基板に形成されていてもよい。

40

#### 【 0104 】

撮像システム 200 は、更に、画像データを一時的に記憶するためのメモリ部 210、外部コンピュータ等と通信するための外部インターフェース部 (外部 I / F 部) 212 を有する。更に撮像システム 200 は、撮像データの記録又は読み出しを行うための半導体メモリ等の記録媒体 214、記録媒体 214 に記録又は読み出しを行うための記録媒体制御インターフェース部 (記録媒体制御 I / F 部) 216 を有する。なお、記録媒体 214 は、撮像システム 200 に内蔵されていてもよく、着脱可能であってもよい。

#### 【 0105 】

更に撮像システム 200 は、各種演算とデジタルスチルカメラ全体を制御する全体制御

50

・演算部 218、撮像装置 100 と信号処理部 208 に各種タイミング信号を出力するタイミング発生部 220 を有する。ここで、タイミング信号等は外部から入力されてもよく、撮像システム 200 は少なくとも撮像装置 100 と、撮像装置 100 から出力された出力信号を処理する信号処理部 208 とを有すればよい。

【0106】

撮像装置 100 は、撮像信号を信号処理部 208 に出力する。信号処理部 208 は、撮像装置 100 から出力される撮像信号に対して所定の信号処理を実施し、画像データを出力する。信号処理部 208 は、撮像信号を用いて、画像を生成する。また、信号処理部 208 は焦点検出信号に対する信号処理を更に行ってもよい。

【0107】

第 1 乃至第 6 実施形態による撮像装置 100 を適用することにより、良質な画像を取得しうる撮像システム 200 を実現することができる。

【0108】

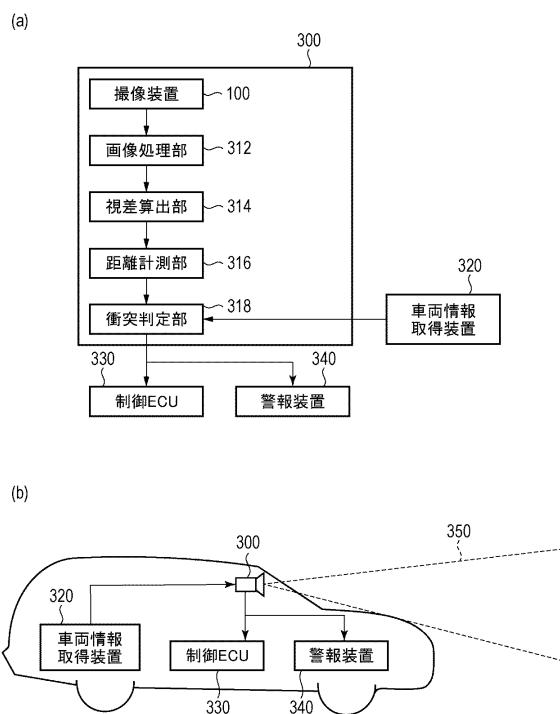

[第 8 実施形態]

本発明の第 8 実施形態による撮像システム及び移動体について、図 12 (a) 及び図 12 (b) を用いて説明する。図 12 (a) 及び図 12 (b) は、本実施形態による撮像システム 300 及び移動体の構成を示す図である。

【0109】

図 12 (a) は、車載カメラに関する撮像システム 300 の一例を示したものである。撮像システム 300 は、撮像装置 100 を有する。本実施形態の撮像装置 100 は、上述の第 1 乃至第 6 実施形態のいずれかに記載の撮像装置 100 である。撮像システム 300 は、撮像装置 100 により取得された複数の画像データに対し、画像処理を行う画像処理部 312 と、撮像システム 300 により取得された複数の画像データから視差（視差画像の位相差）の算出を行う視差算出部 314 を有する。また、撮像システム 300 は、算出された視差に基づいて対象物までの距離を算出する距離計測部 316 と、算出された距離に基づいて衝突可能性があるか否かを判定する衝突判定部 318 と、を有する。ここで、視差算出部 314 や距離計測部 316 は、対象物までの距離情報を取得する距離情報取得手段の一例である。すなわち、距離情報とは、視差、デフォーカス量、対象物までの距離等に関する情報である。衝突判定部 318 はこれらの距離情報のいずれかを用いて、衝突可能性を判定してもよい。距離情報取得手段は、専用に設計されたハードウェアによって実現されてもよいし、ソフトウェアモジュールによって実現されてもよい。また、FPGA (Field Programmable Gate Array) や ASIC (Application Specific Integrated Circuit) 等によって実現されてもよいし、これらの組合せによって実現されてもよい。

【0110】

撮像システム 300 は車両情報取得装置 320 と接続されており、車速、ヨーレート、舵角などの車両情報を取得することができる。また、撮像システム 300 は、衝突判定部 318 での判定結果に基づいて、車両に対して制動力を発生させる制御信号を出力する制御装置である制御 ECU 330 が接続されている。また、撮像システム 300 は、衝突判定部 318 での判定結果に基づいて、ドライバーへ警報を発する警報装置 340 とも接続されている。例えば、衝突判定部 318 の判定結果として衝突可能性が高い場合、制御 ECU 330 はブレーキをかける、アクセルを戻す、エンジン出力を抑制するなどして衝突を回避、被害を軽減する車両制御を行う。警報装置 340 は音等の警報を鳴らす、カーナビゲーションシステムなどの画面に警報情報を表示する、シートベルトやステアリングに振動を与えるなどしてユーザに警告を行う。

【0111】

本実施形態では、車両の周囲、例えば前方又は後方を撮像システム 300 で撮像する。図 12 (b) に、車両前方（撮像範囲 350）を撮像する場合の撮像システムを示した。車両情報取得装置 320 が、所定の動作を行うように撮像システム 300 又は撮像装置 100 に指示を送る。このような構成により、測距の精度をより向上させることができる。

【0112】

10

20

30

40

50

他の車両と衝突しないように制御する例を説明したが、他の車両に追従して自動運転する制御や、車線からはみ出さないように自動運転する制御などにも適用可能である。更に、撮像システムは、自車両等の車両に限らず、例えば、船舶、航空機あるいは産業用ロボットなどの移動体（移動装置）に適用することができる。加えて、移動体に限らず、高度道路交通システム（ITS）等、広く物体認識を利用する機器に適用することができる。

【0113】

【変形実施形態】

本発明は、上述の実施形態に限らず種々の変形が可能である。例えば、いずれかの実施形態の一部の構成を他の実施形態に追加した例や、他の実施形態の一部の構成と置換した例も、本発明の実施形態である。

10

【0114】

また、第7及び第8実施形態に示した装置又はシステムは、本発明の撮像装置100を適用し得る装置又はシステムの構成例を示したものであり、本発明の撮像装置100を適用可能な装置又はシステムは図11又は図12に示した構成に限定されない。

【0115】

また、上述に実施形態に開示されている撮像装置100において、画素から出力される信号を処理するDSP60等の信号処理回路は、画素が形成される基板と同一の半導体基板に形成されていてもよく、別の半導体基板に形成されていてもよい。言い換えると、撮像装置100は1つの半導体基板により構成されていてもよく、複数の半導体基板により構成されていてもよい。

20

【0116】

本発明は、上述の実施形態の1以上の機能を実現するプログラムを、ネットワーク又は記憶媒体を介してシステム又は装置に供給し、そのシステム又は装置のコンピュータにおける1つ以上のプロセッサがプログラムを読み出し実行する処理でも実現可能である。また、1以上の機能を実現する回路（例えば、ASIC）によっても実現可能である。

【0117】

なお、上述の実施形態は、いずれも本発明を実施するにあたっての具体化の例を示したものに過ぎず、これらによって本発明の技術的範囲が限定的に解釈されてはならないものである。すなわち、本発明はその技術思想、又はその主要な特徴から逸脱することなく、様々な形で実施することができる。

30

【符号の説明】

【0118】

|         |        |

|---------|--------|

| 11      | 画素     |

| 30      | 読み出し回路 |

| 100     | 撮像装置   |

| PDA、PDB | 光電変換部  |

40

50

【図面】

【図 1】

【図 2】

10

20

30

40

【図 3】

【図 4】

50

【図5】

【図6】

|   |   |   |   |

|---|---|---|---|

| R | G | R | G |

| G | B | G | B |

| R | G | R | G |

| G | B | G | B |

CF

10

20

30

40

50

【図7】

【図8】

【図 9】

【図 10】

10

20

30

40

【図 11】

【図 12】

50

## フロントページの続き

## (51)国際特許分類

|        |                | F I    |       |       |

|--------|----------------|--------|-------|-------|

| H 04 N | 5/225(2006.01) | H 04 N | 5/225 | 3 0 0 |

| H 04 N | 5/235(2006.01) | H 04 N | 5/235 | 6 0 0 |

| H 04 N | 5/232(2006.01) | H 04 N | 5/232 | 2 9 0 |

## (56)参考文献

特開2013-211833 (JP, A)

特開2001-088609 (JP, A)

特開2015-046761 (JP, A)

特開2015-212794 (JP, A)

特開2013-068759 (JP, A)

特開2017-220749 (JP, A)

## (58)調査した分野 (Int.Cl., DB名)

H 04 N 5 / 3 6 9

H 04 N 5 / 3 5 3

H 04 N 5 / 3 5 5

G 03 B 1 3 / 3 6

G 02 B 7 / 3 4

H 04 N 5 / 2 2 5

H 04 N 5 / 2 3 5

H 04 N 5 / 2 3 2