(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-9425

(P2008-9425A)

(43) 公開日 平成20年1月17日(2008.1.17)

(51) Int.CI.

F 1

テーマコード(参考)

G02F 1/1368 (2006.01)

G02F 1/1368

2H092

G02F 1/1343 (2006.01)

G02F 1/1343

審査請求 未請求 請求項の数 8 O L (全 112 頁)

(21) 出願番号 特願2007-147258 (P2007-147258)

(22) 出願日 平成19年6月1日 (2007.6.1)

(31) 優先権主張番号 特願2006-155471 (P2006-155471)

(32) 優先日 平成18年6月2日 (2006.6.2)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 木村 肇

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

F ターム(参考) 2H092 GA14 JA25 JA28 JA34 JA37

JA41 JA46 JA47 JB08 JB14

JB22 JB31 JB52 JB57 JB58

KA18 KB22 KB24 KB25 MA05

MA07 MA13 MA17 MA27 NA01

NA27 NA29 PA02 PA03 PA06

PA08 PA09 PA11 PA12

(54) 【発明の名称】 液晶表示装置及び電子機器

## (57) 【要約】

【課題】画素電極又は共通電極を透光性を有する導電膜とするため、画素電極又は共通電極をITOで形成していた。このため、製造工程数やマスク数が多くなり、製造コストが高くなっていた。そこで、広い視野角を有しており、かつ従来と比べて製造工程数やマスク数が少なく、製造コストが低い半導体装置及び液晶表示装置並びに電子機器を提供することを課題とする。

【解決手段】トランジスタの半導体層と、液晶素子の画素電極又は共通電極とは同一工程により形成する。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

第1の基板と、第2の基板と、液晶層と、を有し、

絶縁膜と前記第1の基板の間に第1の電極と、第2の電極と、トランジスタと、が形成され、

前記絶縁膜と前記第2の基板との間に液晶層を含み、

前記第1の電極及び前記第2の電極は前記トランジスタの半導体層と同層の膜であり、

前記第1の電極と前記第2の電極との電位差に依存して液晶層の液晶分子の分子配列が変化することを特徴とする液晶表示装置。

**【請求項 2】**

10

第1の基板と、第2の基板と、液晶層と、を有し、

前記第1の基板上に第1の絶縁膜が形成され、

前記第1の絶縁膜上に接して第1の電極と、第2の電極と、トランジスタの半導体層と、

が形成され、

前記第1の電極、前記第2の電極、及び前記トランジスタの半導体層上に第2の絶縁膜が

形成され、

前記第2の絶縁膜上に前記トランジスタの半導体層と重なってゲート電極が形成され、

前記ゲート電極上に第3の絶縁膜が形成され、

前記第3の絶縁膜と前記第2の基板との間に液晶層を含み、

前記第1の電極と前記第2の電極との電位差に依存して液晶層の液晶分子の分子配列が変化することを特徴とする液晶表示装置。

**【請求項 3】**

第1の基板と、第2の基板と、液晶層と、を有し、

前記第1の基板上にゲート電極が形成され、

前記ゲート電極上に第1の絶縁膜が形成され、

前記第1の絶縁膜上に接して、第1の電極と、第2の電極と、ゲート電極と重なってトランジスタの半導体層と、が形成され、

前記第1の電極、前記第2の電極、及び前記トランジスタの半導体層上に第2の絶縁膜が

形成され、

前記第2の絶縁膜と前記第2の基板との間に液晶層を含み、

前記第1の電極と前記第2の電極との電位差に依存して液晶層の液晶分子の分子配列が変化することを特徴とする液晶表示装置。

**【請求項 4】**

請求項1乃至3のいずれか一項において、前記第1の電極及び前記第2の電極は、櫛歯型電極であることを特徴とする液晶表示装置。

**【請求項 5】**

第1の基板と、第2の基板と、液晶層と、を有し、

絶縁膜と前記第1の基板の間に第1の電極と、第2の電極と、第3の電極と、トランジスタと、が形成され、

前記絶縁膜と前記第2の基板との間に液晶層を含み、

前記第1の電極及び前記第2の電極は前記トランジスタの半導体層と同層の膜であり、

前記第1の電極と前記第2の電極との電位差により生じる電界と、前記第1の電極と前記第3の電極との電位差により生じる電界と、によって液晶層の液晶分子の分子配列が変化することを特徴とする液晶表示装置。

**【請求項 6】**

請求項5において、前記第1の電極及び前記第2の電極は櫛歯型電極であり、前記第3の電極はプレート状の電極であることを特徴とする液晶表示装置。

**【請求項 7】**

請求項6において、前記第3の電極上には反射性の膜を有することを特徴とする液晶表示装置。

10

20

30

40

50

**【請求項 8】**

請求項 1 乃至 7 のいずれか一項に記載の液晶表示装置を表示部に有することを特徴とする電子機器。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、半導体装置及び液晶表示装置並びに電子機器に関する。特に、基板に平行な電界を生じさせて、液晶分子の分子配列を制御する半導体装置及び液晶表示装置並びに電子機器に関する。

**【背景技術】****【0002】**

液晶表示装置には、基板に対して垂直な方向の電界を液晶に印加する縦電界方式と、基板に対して横方向の電界を液晶に印加する横電界方式がある。横電界方式の液晶表示装置は、縦電界方式の液晶表示装置に比べて視野角特性に優れている。

**【0003】**

このように、基板に平行な電界（横方向の電界）を生じさせて、基板と平行な面内で液晶分子を動かして、階調を制御する方式として、IPS (In-Plane Switching) モードとFFS (Fringe-Field Switching) モードとがある。

**【0004】**

IPS 方式の液晶表示装置では、一対の基板の片側の基板に、櫛状の電極（櫛歯型電極や櫛型電極ともいう）を二つ配置する。そして、これらの電極（櫛状の電極の一方が画素電極で他方が共通電極）間の電位差により発生する横方向の電界により、基板と平行な面内で液晶分子を動かしている。

**【0005】**

FFS 方式の液晶表示装置では、一対の基板の片側の基板上に第 2 の電極、第 2 の電極上に第 1 の電極を配置する。第 1 の電極にはスリット（開口パターン）を有し、第 2 の電極はプレート状（第 1 の電極の多くのスリットを覆うような面状）の電極である。そして、これらの電極（第 1 の電極及び第 2 の電極のうち一方が画素電極、他方が共通電極）間の電位差により発生する横方向の電界により、基板と平行な面内で液晶分子を動かしている。

**【0006】**

つまり、IPS 方式や FFS 方式の液晶表示装置は、基板と平行に配向している液晶分子（いわゆるホモジニアス配向）を、基板と平行な方向で制御できるため、視野角が広くなる。

**【0007】**

従来は、画素電極又は共通電極を透光性を有する導電膜とするため、画素電極又は共通電極をITO（インジウム錫酸化物）で形成していた（例えば特許文献 1 参照）

**【特許文献 1】特開 2000-89255 号公報****【発明の開示】****【発明が解決しようとする課題】****【0008】**

上記したように、画素電極又は共通電極を透光性を有する導電膜とするため、画素電極又は共通電極をITOで形成していた。このため、製造工程数やマスク数が多くなり、製造コストが高くなっていた。

**【0009】**

そこで、本発明は、広い視野角を有しており、かつ従来と比べて製造工程数やマスク数が少なく、製造コストが低い半導体装置及び液晶表示装置並びに電子機器を提供することを課題とする。

**【課題を解決するための手段】**

10

20

30

40

50

**【 0 0 1 0 】**

本発明の液晶表示装置は、基板と、基板上に形成されたトランジスタ及び液晶素子、と、を有する。そして、トランジスタの半導体層と、液晶素子の画素電極又は共通電極と、は同一工程により形成された膜である。

**【 0 0 1 1 】**

なお、液晶素子は画素電極と、画素部の複数の画素に渡って接続された共通電極と、の電位差により生ずる横方向の電界により、光量を制御する液晶分子の分子配列を基板に対して概ね水平方向に回転させることができればよい。

**【 0 0 1 2 】**

本発明の液晶表示装置の一構成は、第1の電極及び第2の電極を備える液晶素子と、トランジスタと、を基板上に有し、該第1の電極には該トランジスタの半導体層と同層の膜が含まれる。10

**【 0 0 1 3 】**

本発明の液晶表示装置の他の構成は、第1の電極と、第2の電極と、トランジスタと、を基板上に有し、前記第1の電極には前記トランジスタの半導体層と同層の膜が含まれ、前記第1の電極と前記第2の電極との電位差に依存して液晶層の液晶分子の分子配列が変化する。

**【 0 0 1 4 】**

本発明の液晶表示装置の他の構成は、上記構成において、前記第1の電極は櫛歯型電極であり、前記第2の電極はプレート状の電極である。20

**【 0 0 1 5 】**

本発明の液晶表示装置の他の構成は、第1の電極、第2の電極及び第3の電極を備える液晶素子と、トランジスタと、を基板上に有し、前記第1の電極又は前記第2の電極には前記トランジスタの半導体層と同層の膜が含まれ、前記第2の電極と前記第3の電極とが電気的に接続されている。

**【 0 0 1 6 】**

本発明の液晶表示装置の他の構成は、第1の電極及び第2の電極を備える液晶素子と、トランジスタと、を基板上に有し、前記第1の電極及び前記第2の電極には前記トランジスタの半導体層と同層の膜が含まれる。

**【 0 0 1 7 】**

本発明の液晶表示装置の他の構成は、第1の電極と、第2の電極と、トランジスタと、を基板上に有し、前記第1の電極及び前記第2の電極には前記トランジスタの半導体層と同層の膜が含まれ、前記第1の電極と前記第2の電極との電位差に依存して液晶層の液晶分子の分子配列が変化する。30

**【 0 0 1 8 】**

本発明の液晶表示装置の他の構成は、第1の電極と、第2の電極と、第3の電極と、トランジスタと、を基板上に有し、前記第1の電極には前記トランジスタの半導体層と同層の膜が含まれ、前記第1の電極と前記第2の電極との電位差により生じる電界と、前記第1の電極と前記第3の電極との電位差により生じる電界と、によって液晶層の液晶分子の分子配列が変化する。40

**【 0 0 1 9 】**

本発明の液晶表示装置の他の構成は、上記構成において、前記第1の電極及び前記第2の電極は、櫛歯型電極である。

**【 0 0 2 0 】**

本発明の液晶表示装置の他の構成は、上記構成において、前記第1の電極及び前記第2の電極は櫛歯型電極であり、前記第3の電極はプレート状の電極である。

**【 0 0 2 1 】**

本発明の電子機器は上記構成の液晶表示装置を表示部に有する。

**【 0 0 2 2 】**

なお、本発明に示すスイッチは、様々な形態のものを用いることができ、一例として、電50

気的スイッチや機械的なスイッチなどがある。つまり、電流の流れを制御できるものであればよく、特定のものに限定されず、様々なものを用いることができる。例えば、トランジスタでもよいし、ダイオード（例えば、P N ダイオード、P I N ダイオード、ショットキーダイオード、ダイオード接続のトランジスタなど）でもよいし、サイリスタでもよいし、それらを組み合わせた論理回路でもよい。よって、スイッチとしてトランジスタを用いる場合、そのトランジスタは、単なるスイッチとしての機能を果たすため、トランジスタの極性（導電型）は特に限定されない。ただし、オフ電流が少ない方が望ましい場合、オフ電流が少ない方の極性のトランジスタを用いることが望ましい。オフ電流が少ないトランジスタとしては、L D D 領域を設けているものやマルチゲート構造にしているもの等がある。また、スイッチとしての機能を果たすトランジスタのソース端子の電位が、低電位側電源（V<sub>S S</sub>、G N D、0 Vなど）に近い状態で動作する場合はNチャネル型を、反対に、ソース端子の電位が、高電位側電源（V<sub>D D</sub>など）に近い状態で動作する場合はPチャネル型を用いることが望ましい。なぜなら、ゲートソース間電圧の絶対値を大きくできるため、トランジスタがスイッチとしての機能を果たし易くなるからである。

#### 【0023】

なお、Nチャネル型とPチャネル型の両方を用いて、C M O S型のスイッチにしてもよい。C M O S型のスイッチにすると、Pチャネル型及びNチャネル型のいずれか一方のスイッチが導通すれば電流を流すことができるため、スイッチとして機能しやすくなる。例えば、スイッチへの入力信号の電圧が高い場合でも、低い場合でも、適切に電圧を出力させることが出来る。また、スイッチをオン・オフさせるための信号の電圧振幅値を小さくすることが出来るので、消費電力を小さくすることも出来る。

なお、スイッチとしてトランジスタを用いる場合は、入力端子（ソース端子またはドレイン端子の一方）と、出力端子（ソース端子またはドレイン端子の他方）と、導通を制御する端子（ゲート端子）とを有している。一方、スイッチとしてダイオードを用いる場合は、導通を制御する端子を有していない場合がある。そのため、端子を制御するための配線を少なくすることが出来る。

#### 【0024】

なお、本発明において、接続されているとは、電気的に接続されている場合と機能的に接続されている場合と直接接続されている場合とを含むものとする。したがって、本発明が開示する構成において、所定の接続関係以外のものも含むものとする。例えば、ある部分とある部分との間に、電気的な接続を可能とする素子（例えば、スイッチやトランジスタや容量素子やインダクタや抵抗素子やダイオードなど）が1個以上配置されていてもよい。また、機能的な接続を可能とする回路（例えば、論理回路（インバータやN A N D 回路やN O R 回路など）や信号変換回路（D A 変換回路やA D 変換回路やガンマ補正回路など）や電位レベル変換回路（昇圧回路や降圧回路などの電源回路やH信号やL信号の電位レベルを変えるレベルシフト回路など）や電圧源や電流源や切り替え回路や増幅回路（オペアンプや差動増幅回路やソースフォロワ回路やバッファ回路など、信号振幅や電流量などを大きく出来る回路など）や信号生成回路や記憶回路や制御回路など）が間に1個以上配置されていてもよい。あるいは、間に他の素子や他の回路を挟まずに、直接接続されて、配置されていてもよい。なお、素子や回路を間に介さずに接続されている場合のみを含む場合は、直接接続されている、と記載するものとする。また、電気的に接続されている、と記載する場合は、電気的に接続されている場合（つまり、間に別の素子を挟んで接続されている場合）と機能的に接続されている場合（つまり、間に別の回路を挟んで接続されている場合）と直接接続されている場合（つまり、間に別の素子や別の回路を挟まずに接続されている場合）とを含むものとする。

#### 【0025】

なお、表示素子は、液晶素子の他に様々な形態を用いることが出来る。例えば、E L 素子（有機E L 素子、無機E L 素子又は有機物材料び無機材料を含むE L 素子）、電子放出素子、電子インク、光回折素子、放電素子、微小鏡面素子（D M D : D i g i t a l M i c r o m i r r o r D e v i c e）、圧電素子、カーボンナノチューブなど、電気磁気

的作作用によりコントラストが変化する表示媒体を適用することができる。なお、EL素子を用いたELパネル方式の表示装置としてはELディスプレイ、電子放出素子を用いた表示装置としてはフィールドエミッショニディスプレイ(FED: Field Emission Display)やSED方式平面型ディスプレイ(SED: Surface-conduction Electron-emitter Display)など、電子インクを用いたデジタルペーパー方式の表示装置としては電子ペーパー、光回折素子を用いた表示装置としてはグレーティングライトバルブ(GLV)方式のディスプレイ、放電素子を用いたPDP(Plasma Display Panel)方式のディスプレイとしてはプラズマディスプレイ、微小鏡面素子を用いたDMDパネル方式の表示装置としてはデジタル・ライト・プロセッシング(DLP)方式の表示装置、圧電素子を用いた表示装置としては圧電セラミックディスプレイ、カーボンナノチューブを用いた表示装置としてはナノ放射ディスプレイ(NED: Nano Emissive Display)、などがある。

10

20

30

40

#### 【0026】

なお、本発明において、トランジスタは、様々な形態のトランジスタを適用させることが出来る。よって、適用可能なトランジスタの種類に限定はない。したがって、例えば、非晶質シリコンや多結晶シリコンに代表される非単結晶半導体膜を有する薄膜トランジスタ(TFT)などを適用することが出来る。これらにより、製造温度が高くなくても製造でき、低コストで製造でき、大型基板上に製造でき、又は透光性基板上に製造することにより光を透過させることが可能なトランジスタを製造することが出来る。また、半導体基板やSOI基板を用いて形成されるトランジスタ、MOS型トランジスタ、接合型トランジスタ、バイポーラトランジスタなどを適用することが出来る。これらにより、バラツキの少ないトランジスタを製造でき、電流供給能力の高いトランジスタを製造でき、サイズの小さいトランジスタを製造でき、又は消費電力の少ない回路を構成することが出来る。また、ZnO、a-InGaZnO、SiGe、GaAsなどの化合物半導体を有するトランジスタや、さらに、それらを薄膜化した薄膜トランジスタなどを適用することが出来る。これらにより、製造温度が高くなくても製造でき、室温で製造でき、耐熱性の低い基板、例えばプラスチック基板やフィルム基板に直接トランジスタを形成することが出来る。また、インクジェットや印刷法を用いて作成したトランジスタなどを適用することが出来る。これらにより、室温で製造し、真空度の低い状態で製造し、又は大型基板で製造することができる。また、マスク(レチクル)を用いなくても製造することが可能となるため、トランジスタのレイアウトを容易に変更することが出来る。また、有機半導体やカーボンナノチューブを有するトランジスタ、その他のトランジスタを適用することができる。これらにより、曲げることが可能な基板上にトランジスタを形成することが出来る。なお、非単結晶半導体膜には水素またはハロゲンが含まれていてもよい。また、トランジスタが配置されている基板の種類は、様々なものを用いることができ、特定のものに限定されることはない。従って例えば、単結晶基板、SOI基板、ガラス基板、石英基板、プラスチック基板、紙基板、セロファン基板、石材基板、ステンレス・スチル基板、ステンレス・スチル・ホイルを有する基板などに配置することが出来る。また、ある基板でトランジスタを形成し、その後、別の基板にトランジスタを移動させて、別の基板上に配置するようにしてもよい。これらの基板を用いることにより、特性のよいトランジスタを形成し、消費電力の小さいトランジスタを形成し、壊れにくい装置にし、又は耐熱性を持たせることが出来る。

#### 【0027】

なお、トランジスタの構成は、様々な形態をとることができる。特定の構成に限定されない。例えば、ゲート電極が2個以上になっているマルチゲート構造を用いてもよい。マルチゲート構造にすると、チャネル領域が直列に接続されるような構成となるため、複数のトランジスタが直列に接続されたような構成となる。マルチゲート構造にすることにより、オフ電流を低減し、トランジスタの耐圧を向上させて信頼性を良くし、又は飽和領域で動作する時に、ドレイン・ソース間電圧が変化しても、ドレイン・ソース間電流があまり

50

変化せず、フラットな特性にすることなどができる。また、チャネルの上下にゲート電極が配置されている構造でもよい。チャネルの上下にゲート電極が配置されている構造により、チャネル領域が増えるため、電流値を大きくし、又は空乏層ができやすくなってS値を小さくすることができる。チャネルの上下にゲート電極が配置されると、複数のトランジスタが並列に接続されたような構成となる。

#### 【0028】

また、チャネルの上にゲート電極が配置されている構造でもよいし、チャネルの下にゲート電極が配置されている構造でもよいし、正スタガ構造であってもよいし、逆スタガ構造でもよいし、チャネル領域が複数の領域に分かれてもよいし、並列に接続されていてもよいし、直列に接続されていてもよい。また、チャネル（もしくはその一部）にソース電極やドレイン電極が重なっていてもよい。チャネル（もしくはその一部）にソース電極やドレイン電極が重なっている構造により、チャネルの一部に電荷がたまつて、動作が不安定になることを防ぐことができる。また、LDD領域があってもよい。LDD領域を設けることにより、オフ電流を低減し、トランジスタの耐圧を向上させて信頼性を良くし、又は飽和領域で動作する時に、ドレイン・ソース間電圧が変化しても、ドレイン・ソース間電流があまり変化せず、フラットな特性にすることができる。

#### 【0029】

なお、本発明においては、一画素とは画像の最小単位を示すものとする。よって、R（赤）G（緑）B（青）の色要素からなるフルカラー表示装置の場合には、一画素とはRの色要素のドットとGの色要素のドットとBの色要素のドットとから構成されるものとする。なお、色要素は、三色に限定されず、それ以上の数を用いても良いし、RGB以外の色を用いても良い。例えば、白色を加えて、RGBW（Wは白）としてもよい。また、RGBに、例えば、イエロー、シアン、マゼンタ、エメラルドグリーン、朱色などを一色以上追加したものでもよい。また、例えばRGBの中の少なくとも一色について、類似した色を追加してもよい。例えば、R、G、B1、B2としてもよい。B1とB2とは、どちらも青色であるが、少し周波数が異なっている。このような色要素を用いることにより、より実物に近い表示を行うことができ、又は消費電力を低減することができる。なお、一画素に、ある色の色要素のドットが複数あってもよい。そのとき、その複数の色要素は、各々、表示に寄与する領域の大きさが異なっていても良い。また、複数ある、ある色の色要素のドットを各々制御することによって、階調を表現してもよい。これを、面積階調方式と呼ぶ。あるいは、複数ある、ある色の色要素のドットを用いて、各々のドットに供給する信号を僅かに異ならせるようにして、視野角を広げるようにしてもよい。

#### 【0030】

なお、本発明において、画素は、マトリクス状に配置（配列）されている場合を含んでいる。ここで、画素がマトリクスに配置（配列）されているとは、縦方向もしくは横方向において、直線上に並んで配置されている場合や、ギザギザな線上に並んでいる場合を含んでいる。よって、例えば三色の色要素（例えばRGB）でフルカラー表示を行う場合に、ストライプ配置されている場合や、三つの色要素のドットがいわゆるデルタ配置されている場合も含むものとする。さらに、ペイヤー配置されている場合も含んでいる。なお、色要素は、三色に限定されず、それ以上でもよく、例えば、RGBW（Wは白）や、RGBに、イエロー、シアン、マゼンタなどを一色以上追加したものなどがある。また、色要素のドット毎にその表示領域の大きさが異なっていてもよい。これにより、消費電力を低下させる、又は表示素子の寿命を延ばすことが出来る。

#### 【0031】

なお、トランジスタとは、それぞれ、ゲートと、ドレインと、ソースとを含む少なくとも三つの端子を有する素子であり、ドレイン領域とソース領域の間にチャネル領域を有しており、ドレイン領域とチャネル領域とソース領域とを介して電流を流すことが出来る。ここで、ソースとドレインとは、トランジスタの構造や動作条件等によって変わるために、いずれがソースまたはドレインであるかを限定することが困難である。そこで、本発明においては、ソース及びドレインとして機能する領域を、ソースもしくはドレインと呼ばない

10

20

30

40

50

場合がある。その場合、一例としては、それぞれを第1端子、第2端子と表記する場合がある。なお、トランジスタは、ベースとエミッタとコレクタとを含む少なくとも三つの端子を有する素子であってもよい。この場合も同様に、エミッタとコレクタとを、第1端子、第2端子と表記する場合がある。

#### 【0032】

ゲート配線（走査線、ゲート線またはゲート信号線等とも言う）とは、各画素のゲート電極の間を接続するためや、又はゲート電極と別の配線とを接続するための配線のことを言う。

#### 【0033】

ただし、ゲート電極としても機能し、ゲート配線としても機能するような部分も存在する。そのような領域は、ゲート電極と呼んでも良いし、ゲート配線と呼んでも良い。つまり、ゲート電極とゲート配線とが、明確に区別できないような領域も存在する。例えば、延伸して配置されているゲート配線とオーバーラップしてチャネル領域がある場合、その領域はゲート配線として機能しているが、ゲート電極としても機能することになる。よって、そのような領域は、ゲート電極と呼んでも良いし、ゲート配線と呼んでも良い。

#### 【0034】

また、ゲート電極と同じ材料で形成され、ゲート電極とつながっている領域も、ゲート電極と呼んでも良い。同様に、ゲート配線と同じ材料で形成され、ゲート配線とつながっている領域も、ゲート配線と呼んでも良い。このような領域は、厳密な意味では、チャネル領域とオーバーラップしていない、又は別のゲート電極と接続させる機能を有していない場合がある。しかし、製造コスト、工程の削減、レイアウトの簡略化などの関係で、ゲート電極やゲート配線と同じ材料で形成され、ゲート電極やゲート配線とつながっている領域がある。よって、そのような領域もゲート電極やゲート配線と呼んでも良い。

#### 【0035】

また、例えば、マルチゲートのトランジスタにおいて、1つのトランジスタのゲート電極と、別のトランジスタのゲート電極とは、ゲート電極と同じ材料で形成された導電膜で接続される場合が多い。そのような領域は、ゲート電極とゲート電極とを接続させるための領域であるため、ゲート配線と呼んでも良いが、マルチゲートのトランジスタを1つのトランジスタであると見なすことも出来るため、ゲート電極と呼んでも良い。つまり、ゲート電極やゲート配線と同じ材料で形成され、それらとつながって配置されているものは、ゲート電極やゲート配線と呼んでも良い。また、例えば、ゲート電極とゲート配線とを接続してさせている部分の導電膜も、ゲート電極と呼んでも良いし、ゲート配線と呼んでも良い。

#### 【0036】

なお、ゲート端子とは、ゲート電極の領域や、ゲート電極と電気的に接続されている領域について、その一部分のことを言う。

#### 【0037】

なお、ソースとは、ソース領域とソース電極とソース配線（信号線、ソース線またはソース信号線等とも言う）とを含んだ全体、もしくは、それらの一部のことを言う。ソース領域とは、P型不純物（ボロンやガリウムなど）やN型不純物（リンやヒ素など）が多く含まれる半導体領域のことを言う。従って、少しだけP型不純物やN型不純物が含まれる領域、いわゆる、LDD（Lightly Doped Drain）領域は、ソース領域には含まれない。ソース電極とは、ソース領域とは別の材料で形成され、ソース領域と電気的に接続されて配置されている部分の導電層のことを言う。ただし、ソース電極は、ソース領域も含んでソース電極と呼ぶこともある。ソース配線とは、各画素のソース電極の間を接続する、又はソース電極と別の配線とを接続するための配線のことを言う。

#### 【0038】

しかしながら、ソース電極としても機能し、ソース配線としても機能するような部分も存在する。そのような領域は、ソース電極と呼んでも良いし、ソース配線と呼んでも良い。つまり、ソース電極とソース配線とが、明確に区別できないような領域も存在する。例え

10

20

30

40

50

ば、延伸して配置されているソース配線とオーバーラップしてソース領域がある場合、その領域はソース配線として機能しているが、ソース電極としても機能することになる。よって、そのような領域は、ソース電極と呼んでも良いし、ソース配線と呼んでも良い。

#### 【0039】

また、ソース電極と同じ材料で形成され、ソース電極とつながっている領域や、ソース電極とソース電極とを接続する部分も、ソース電極と呼んでも良い。また、ソース領域とオーバーラップしている部分も、ソース電極と呼んでも良い。同様に、ソース配線と同じ材料で形成され、ソース配線とつながっている領域も、ソース配線と呼んでも良い。このような領域は、厳密な意味では、別のソース電極と接続させる機能を有していたりすることがない場合がある。しかし、製造コスト、工程の削減、又はレイアウトの簡略化などの関係で、ソース電極やソース配線と同じ材料で形成され、ソース電極やソース配線とつながっている領域がある。よって、そのような領域もソース電極やソース配線と呼んでも良い。

10

#### 【0040】

また、例えば、ソース電極とソース配線とを接続してさせている部分の導電膜も、ソース電極と呼んでも良いし、ソース配線と呼んでも良い。

#### 【0041】

なお、ソース端子とは、ソース領域の領域や、ソース電極や、ソース電極と電気的に接続されている領域について、その一部分のことを言う。

20

#### 【0042】

なお、ドレインについては、ソースと同様である。

#### 【0043】

なお、本発明において、半導体装置とは半導体素子（トランジスタやダイオードなど）を含む回路を有する装置をいう。また、半導体特性を利用することで機能しうる装置全般でもよい。

30

#### 【0044】

また、表示装置とは、表示素子（液晶素子や発光素子など）を有する装置のことを言う。なお、液晶素子やEL素子などの表示素子を含む複数の画素やそれらの画素を駆動させる周辺駆動回路が同一基板上に形成された表示パネル本体のことでもよい。また、ワイヤボンディングやバンプなどによって基板上に配置された周辺駆動回路、いわゆるチップオングラス（COG）を含んでいても良い。さらに、フレキシブルプリントサーキット（FPC）やプリント配線基盤（PWB）が取り付けられたもの（ICや抵抗素子や容量素子やインダクタやトランジスタなど）も含んでもよい。さらに、偏光板や位相差板などの光学シートを含んでいても良い。さらに、バックライトユニット（導光板やブリズムシートや拡散シートや反射シートや光源（LEDや冷陰極管など）を含んでいても良い）を含んでいても良い。

#### 【0045】

また、発光装置とは、特にEL素子やFEDで用いる素子などの自発光型の表示素子を有している表示装置をいう。液晶表示装置とは、液晶素子を有している表示装置をいう。

40

#### 【0046】

なお、本発明において、ある物の上に形成されている、あるいは、～上に形成されている、というように、～の上に、あるいは、～上に、という記載については、ある物の上に直接接していることに限定されない。直接接してはいない場合、つまり、間に別のものが挟まっている場合も含むものとする。従って例えば、層Aの上に（もしくは層A上に）、層Bが形成されている、という場合は、層Aの上に直接接して層Bが形成されている場合と、層Aの上に直接接して別の層（例えば層Cや層Dなど）が形成されていて、その上に直接接して層Bが形成されている場合とを含むものとする。また、～の上方に、という記載についても同様であり、ある物の上に直接接していることに限定されず、間に別のものが挟まっている場合も含むものとする。従って例えば、層Aの上方に、層Bが形成されてい

50

る、という場合は、層Aの上に直接接して層Bが形成されている場合と、層Aの上に直接接して別の層（例えば層Cや層Dなど）が形成されていて、その上に直接接して層Bが形成されている場合とを含むものとする。なお、～の下に、あるいは、～の下方に、の場合についても、同様であり、直接接している場合と、接していない場合とを含むこととする。

### 【発明の効果】

#### 【0047】

従って、広い視野角を有しており、かつ従来と比べて製造コストが低い液晶表示装置を提供することができる。

#### 【発明を実施するための最良の形態】

10

#### 【0048】

以下、本発明の実施の形態について図面を参照しながら説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従つて本実施の形態の記載内容に限定して解釈されるものではない。

#### 【0049】

##### （実施の形態1）

まず、本発明の第1の実施の形態の表示パネルの構成について簡単に説明する。

#### 【0050】

本発明の第1の実施の形態の表示パネルには、第1の基板と第1の基板に対向して設けられた第2の基板とによって液晶層が挟持されている。

#### 【0051】

本発明の第1の実施の形態の表示パネルの画素部は第1の基板上に形成されている。画素部には、階調を表現するための信号（以下ビデオ信号という）が供給される配線（以下、信号線という）と、ビデオ信号の書き込みを行う画素を選択する配線（以下、走査線という）と、をそれぞれ複数有している。

#### 【0052】

そして、画素部には、複数の画素が走査線と信号線に対応してマトリクスに配置され、各画素は、それぞれ走査線のいずれか一と、信号線のいずれか一と、に接続されている。そして、各画素には、少なくとも一つのトランジスタと、画素電極とを有している。

30

#### 【0053】

走査線と信号線の交差する付近に各画素のトランジスタが設けられている。そして、トランジスタは、各画素の画素電極への電荷の充放電を制御している。

#### 【0054】

そして、各画素には、画素毎に独立して設けられた画素電極と、画素部の複数の画素に渡って接続された共通電極と、の電位差に依存して液晶層の液晶分子の分子配列が変化する液晶素子が含まれている。

#### 【0055】

液晶層としては、強誘電性液晶（FLC）、ネマティック液晶、スマートティック液晶、コレステリック液晶、ホモジニアス配向になるような液晶、ホメオトロピック配向になるような液晶などを用いることができる。

40

#### 【0056】

画素電極と共通電極との電位差により、電界を発生させる。この電界は、第1の基板に対して平行（つまり、画素電極及び共通電極に対して平行）な横方向の成分を多く含んでいる。そして、液晶分子の分子配列の変化とは、第1の基板に対して平行な面内（つまり、画素電極及び共通電極に対して平行な面内）で液晶分子の分子が回転することである。

#### 【0057】

なお、本明細書において「電極と平行な面内で回転」とは、人間の目で視認できない程度のズレを有していても良い程度に平行な回転も含む。言い換えると、面方向のベクトル成分を主とするが面方向のベクトル成分以外に法線方向のベクトル成分を僅かに有する回転

50

も「電極と平行な面内で回転」に含まれる。

【0058】

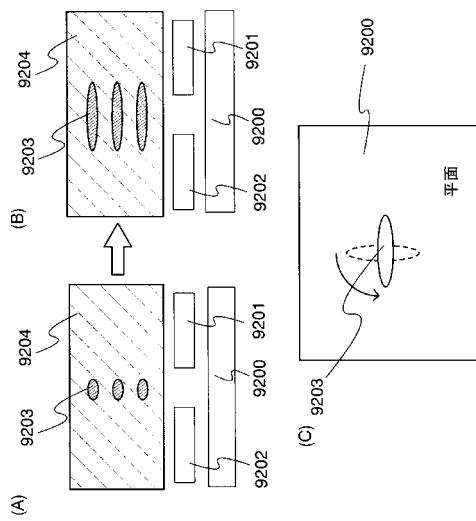

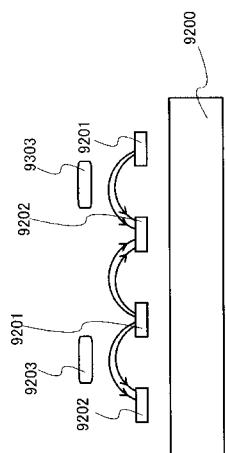

例えば、IPS方式の液晶表示装置は、図95に示すように基板9200上に画素電極9201と共に共通電極9202を有する。そして、画素電極9201と共に共通電極9202とに電位差が生ずると、図に示す矢印のような電界が発生する。すると画素電極9201及び共通電極9202上の液晶分子9203が回転する。つまり、図92(A)から図92(B)に示すように液晶層9204中の液晶分子9203の配列が変化する。さらに、上面から見ると図92(C)の矢印のように液晶分子9203が回転している。

【0059】

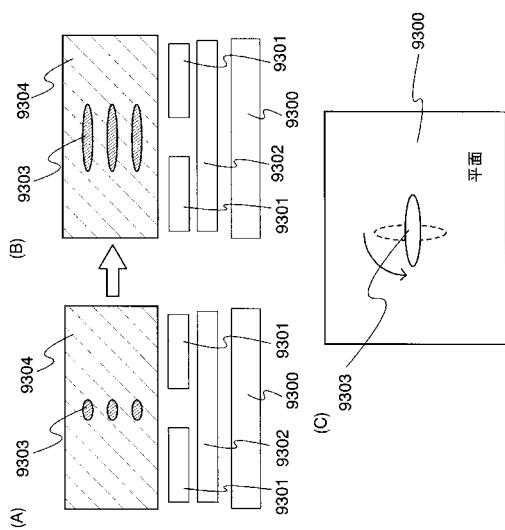

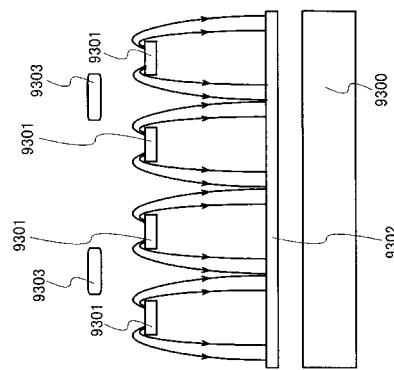

また、FFS方式の液晶表示装置は、図96に示すように基板9300上に共通電極9302を有し、さらに共通電極9302上に画素電極9301を有する。そして、画素電極9301と共に共通電極9302とに電位差が生ずると、図に示す矢印のような電界が発生する。すると画素電極9301上の液晶分子9303が回転する。つまり、図93(A)から図93(B)に示すように液晶層9304中の液晶分子9303の配列が変化する。さらに、上面から見ると図93(C)の矢印のように液晶分子9303が回転している。なお、画素電極と共に共通電極の配置は逆であっても構わない。

【0060】

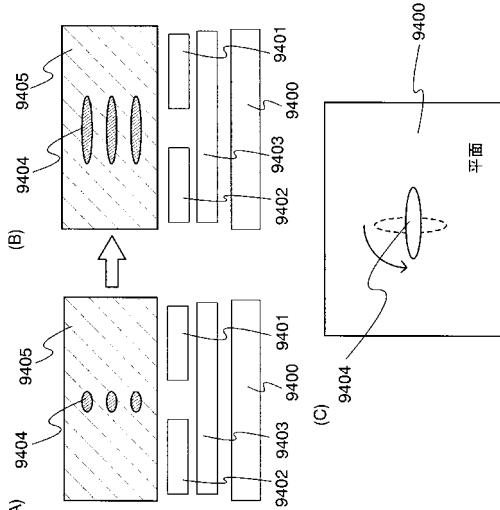

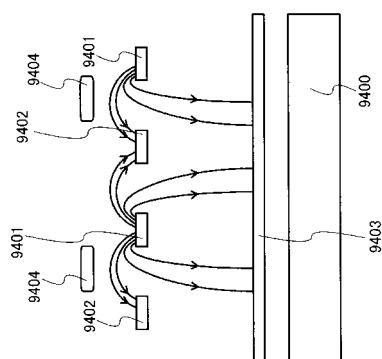

また、IPS方式とFFS方式とを組み合わせた液晶表示装置は、図97に示すように基板9400上に第2の共通電極9403を有し、さらに第2の共通電極9403上に画素電極9401及び第1の共通電極9402を有する。そして、画素電極9401と共に共通電極(第2の共通電極9403及び第1の共通電極9402)とに電位差が生ずると、図に示す矢印のような電界が発生する。すると画素電極9401及び第1の共通電極9402上の液晶分子9404が回転する。つまり、図94(A)から図94(B)に示すように液晶層9405中の液晶分子9404の配列が変化する。さらに、上面から見ると図94(C)の矢印のように液晶分子9404が回転している。画素電極として機能する電極の下方や横方向や斜め方向(斜め上方向や斜め下方向も含む)に、共通電極が存在することにより、基板に平行な電界成分が、より多く生じるようになる。その結果、視野角特性がさらに向上する。なお、画素電極と共に共通電極の配置は逆であっても構わない。

【0061】

このように、画素電極と共に共通電極との電位差により生ずる横方向の電界により、光量を制御する液晶分子の分子配列を基板に対して水平方向に回転させることができればよい。よって、画素電極及び共通電極には、様々な形状の電極を用いることができる。つまり、画素電極と共に共通電極との電位差により生ずる横方向の電界が生じたときに、液晶分子の傾く方向を電界方向にすることにより、液晶層を光が透過する(このような表示装置をノーマリーブラックモードの表示装置という)若しくは液晶層を光が透過しない(このような表示装置をノーマリーホワイトモードの表示装置という)ようにすればよい。

【0062】

例えば、基板上面から見たときの電極形状として、櫛状の電極(櫛歯型電極又は櫛型電極ともいう)、スリット(開口部)が設けられた電極又は一面を覆う形状の電極(プレート状電極ともいう)を画素電極及び共通電極に用いることができる。

【0063】

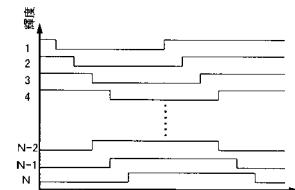

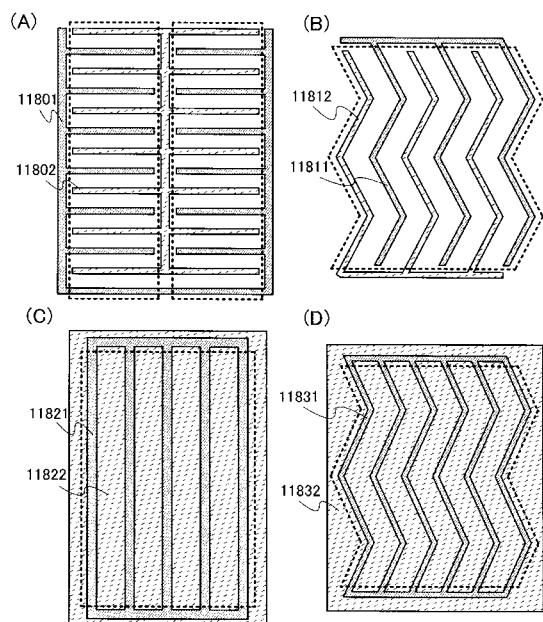

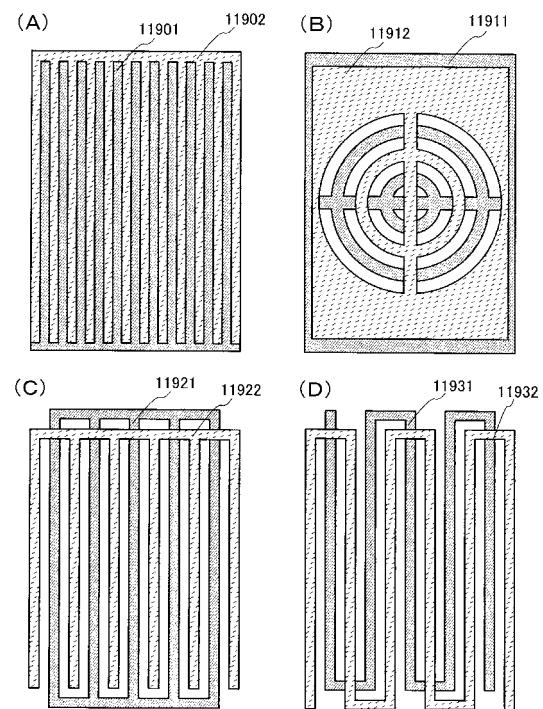

基板上面から見たときの電極形状の例を図118(A)~(D)、及び図119(A)~(D)に示す。

【0064】

図118(A)において、第1の電極11801及び第2の電極11802は櫛歯型電極である。第1の電極11801及び第2の電極11802の一方が画素電極で他方が共通電極である。そして、第1の電極11801及び第2の電極11802の点線で囲まれた領域がそれぞれの電極のプランチ部分である。つまり、第1の電極11801と第2の電極11802とに電位差が生じたときに発生する、電極面に対して水平方向の電界のうち、強い電界成分の発生に主に寄与する電極部分をプランチ部分という。なお、第1の電極

10

20

30

40

50

11801 及び第2の電極 11802 はいわゆる IPS 方式の液晶表示パネルの液晶素子の電極に適している。

【0065】

図 118 (B)において、第1の電極 11811 及び第2の電極 11812 は櫛歯型電極である。第1の電極 11811 及び第2の電極 11812 の一方が画素電極で他方が共通電極である。そして、第1の電極 11811 及び第2の電極 11812 の点線で囲まれた領域がそれぞれの電極のプランチ部分である。なお、第1の電極 11811 及び第2の電極 11812 のプランチ部分はジグザグ形状となっている。なお、第1の電極 11811 及び第2の電極 11812 はいわゆる IPS 方式の液晶表示パネルの液晶素子の電極に適している。

10

【0066】

図 118 (C)において、第1の電極 11821 はスリットの設けられた電極であり、第2の電極 11822 はプレート状の電極である。第1の電極 11821 及び第2の電極 11822 の一方が画素電極で他方が共通電極である。そして、第1の電極 11821 の点線で囲まれた領域が第1の電極 11821 のプランチ部分である。なお、第1の電極 11821 及び第2の電極 11822 はいわゆる FFS 方式の液晶表示パネルの液晶素子の電極に適している。

【0067】

図 118 (D)において、第1の電極 11831 はスリットの設けられた電極であり、第2の電極 11832 はプレート状の電極である。第1の電極 11831 及び第2の電極 11832 の一方が画素電極で他方が共通電極である。そして、第1の電極 11831 の点線で囲まれた領域が電極のプランチ部分である。なお、第1の電極 11831 のスリットはジグザグ形状となっている。なお、第1の電極 11831 及び第2の電極 11832 はいわゆる FFS 方式の液晶表示パネルの液晶素子の電極に適している。

20

【0068】

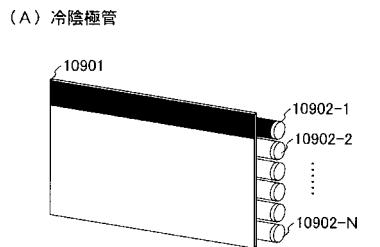

図 119 (A)において、第1の電極 11901 は櫛歯型電極であり、第2の電極 11902 はプレート状の電極である。第1の電極 11901 及び第2の電極 11902 の一方が画素電極で他方が共通電極である。なお、第1の電極 11901 及び第2の電極 11902 はいわゆる FFS 方式の液晶表示パネルの液晶素子の電極に適している。

30

【0069】

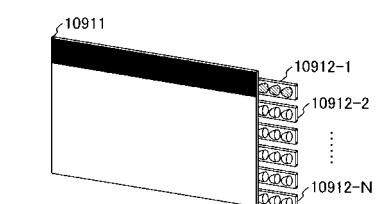

図 119 (B)において、第1の電極 11911 及び第2の電極 11912 はスリットの設けられた電極である。第1の電極 11911 及び第2の電極 11912 の一方が画素電極で他方が共通電極である。なお、第1の電極 11911 及び第2の電極 11912 はいわゆる IPS 方式の液晶表示パネルの液晶素子の電極に適している。

【0070】

図 119 (C)において、第1の電極 11921 はスリットの設けられた電極であり、第2の電極 11922 は櫛歯型電極である。第1の電極 11921 及び第2の電極 11922 の一方が画素電極で他方が共通電極である。なお、第1の電極 11921 及び第2の電極 11922 はいわゆる IPS 方式の液晶表示パネルの液晶素子の電極に適している。

40

【0071】

図 119 (D)において、第1の電極 11931 及び第2の電極 11932 は櫛歯型電極である。第1の電極 11931 及び第2の電極 11932 の一方が画素電極で他方が共通電極である。なお、第1の電極 11931 及び第2の電極 11932 はいわゆる IPS 方式の液晶表示パネルの液晶素子の電極に適している。

【0072】

なお、これらは電極形状の例であって本発明はこれらに限定されるものではない。

【0073】

このように、本明細書において、櫛歯形電極とは、電極のプランチ部分において、隣り合うプランチの一端がつながっており、他端がつながっていないような形状の電極を含む。スリットの設けられた電極とは、電極のプランチ部分において、隣り合うプランチの両端

50

がそれぞれつながっているような形状の電極を含む。プレート状の電極とは、他の電極の複数のブランチ間の領域にまたがって伸張しているような電極を含む。

#### 【0074】

また、例えば断面から見たときの形状として、画素電極及び共通電極は凸凹状、波状、平面状であってもよい。画素電極又は共通電極を反射型液晶表示パネル又は半透過型液晶表示パネルの反射膜として用いる場合、画素電極又は共通電極を断面から見たときに凸凹状、又は波状にすることで、画素電極又は共通電極で外光を乱反射することができるため、輝度を向上させることができると共に、反射による写り込みを防止することができる。なお、画素電極の形状と共通電極の形状とは様々な組み合わせを適用することができる。

#### 【0075】

なお、反射型液晶表示パネル又は半透過型液晶表示パネルにおいて、反射領域中の絶縁膜の表面を凹凸にする、又は絶縁膜中に光を散乱させるための粒子を添加することで絶縁膜を光散乱層として機能させてもよい。こうすれば、反射膜の表面は凹凸しなくとも、反射による写り込みを防止することができるため、画素電極又は共通電極を反射膜として用いる場合に液晶層へ所望な方向成分の電界の形成が容易となる。

#### 【0076】

また、半透過型液晶表示パネルにおいて、光を反射させて表示を行う部分（反射領域）とバックライト等からの光を透過させて表示を行う部分（透過領域）との液晶層の厚さ（いわゆるセルギャップ）を小さくするため、液晶層の厚さを調整する膜を配置してもよい。

#### 【0077】

なお、反射型液晶表示パネル又は、透過型液晶表示パネルの場合には液晶層の中を通る光の距離が、1画素内において場所によって大きく異なることはない。よって、液晶層の厚さ（セルギャップ）を調整するための絶縁膜を設けなくてもよい。

#### 【0078】

なお、画素電極と共通電極との電位差により生ずる横方向の電界が生じたときに液晶分子の傾く方向を、電界方向からずらすことで応答速度を高めた液晶表示パネルを提供することができる。また、液晶分子を高速で駆動する制御回路である、いわゆるオーバードライブ回路を備えることで中間階調間での応答速度を高めてよい。

#### 【0079】

なお、画素電極及び共通電極の形状を工夫することにより、いわゆるマルチドメイン化を図っても良い。つまり、画素電極と共通電極との電位差により液晶層に横方向の電界が生じたときに液晶分子の傾く方向を複数にする。こうして視野の角度による色調の変化を低減するようにしてもよい。その場合には、画素電極又は共通電極の形状をくの字型のスリット又はジグザグ形状のスリットが設けられた電極とする、又は電極のブランチ部分にくの字型やジグザグ形状を有するようにする。こうすることにより、視野の角度による色調の変化を極めて小さくでき、高色純度、高コントラスト比の液晶表示パネルを提供することができる。

#### 【0080】

そして、この画素電極、又は共通電極には、トランジスタの半導体層（チャネル、ソース若しくはドレインとして機能する半導体膜）に用いる膜の形成と同一工程により形成された膜を用いる。なお、画素電極や共通電極の少なくとも一部にトランジスタの半導体層に用いる膜と同一工程により形成された膜を用いていればよい。

#### 【0081】

トランジスタの半導体層としては、非晶質半導体（アモルファスシリコンともいう）や多結晶半導体（ポリシリコンともいう）に代表される非単結晶半導体膜（非晶質半導体膜及び多結晶半導体膜を含む）を適用することができる。また、ZnO、a-InGaZnOなどの化合物半導体膜を用いてもよい。非単結晶半導体膜には水素またはハロゲンが含まれていてもよい。つまり、画素電極及び共通電極の少なくとも一部にも非単結晶半導体膜や化合物半導体膜を用いる。

#### 【0082】

10

20

30

40

50

なお、トランジスタの半導体層の膜厚は光を透過する程度の厚さであることが望ましい。好ましくは、トランジスタの半導体層の膜厚は、10 nm以上100 nm以下、より好ましくは45 nm以上60 nmとする。また、画素電極及び共通電極の少なくとも一部にも、トランジスタの半導体層の膜厚と概略等しい厚さの非単結晶半導体膜や化合物半導体膜を用いていることが好ましい。

## 【0083】

トランジスタの半導体層に用いる膜と同一工程により形成された膜は透光性を有しているので、透過型液晶表示パネルの画素電極又は共通電極、並びに半透過型液晶表示パネルの画素電極又は共通電極の一部に用いることが好ましい。もちろん反射型液晶表示パネルの画素電極又は共通電極に用いてもよい。

10

## 【0084】

同一工程により形成された膜とは、一続きの膜を形成した後、一続きの膜を分離して形成された複数の膜をいう。また、同一工程により形成された膜のことを同層の膜ともいう。よって、一続きの膜上に並んで配置されている膜であっても、同一工程により形成されていないときには異なる層の膜となる。

## 【0085】

つまり、同層の膜は、化学気相成長法(CVD)、スパッタ法、真空蒸着法又はスピンドル法等により一続きの膜を形成し、その膜をパターニングして形成することができる。

## 【0086】

なお、パターニングとは、膜を形状加工することをいい、フォトリソグラフィー技術によって膜のパターンを形成すること（例えば、感光性アクリルにコンタクトホールを形成することや、感光性アクリルをスペーサとなるように形状加工することも含む）や、フォトリソグラフィー技術によってマスクパターンを形成し、当該マスクパターンを用いてエッチング加工を行うことなどをいう。つまり、パターニング工程では、膜の一部を選択的に除去する。

20

## 【0087】

そして、この同層の膜には、膜厚や成分が同一でないものも含まれる。

## 【0088】

例えば、同層の膜のパターニングにおいて、マスクパターンの膜厚を制御し、マスクパターンを等方性エッチングすることにより、同層の膜において膜厚を変化させることもできるし、同層の膜のうち一部の膜に不純物を添加して同層の膜のうち異なる成分の膜があつてもよい。

30

## 【0089】

また、同一工程により形成された膜は、それらの全ての膜が一続きの膜上に形成されてもよいし、それらの膜のうち異なる層の膜上に形成されている膜があつてもよい。

## 【0090】

つまり、同一工程により形成された第1の膜と第2の膜とは、接している下の膜は限定されない。

## 【0091】

なお、上記説明においては、本発明の第1の実施の形態に係る液晶表示パネルの主要な構成について説明したが、本発明はこれに限定されない。つまり、偏光板、位相差板、カラーフィルター、バックライト、走査線に信号を供給する走査線駆動回路、信号線に信号を供給する信号線駆動回路などを有していてもよい。

40

## 【0092】

バックライト用光源としては、蛍光ランプ（冷陰極蛍光管、熱陰極蛍光管）、発光ダイオード、CRT、EL（無機、有機）、白熱ランプなどを適宜用いることができる。また、導光板、反射鏡、光源、拡散シート、反射シートなど、とを組み合わせてバックライトとすることができる。

## 【0093】

つまり、本実施の形態に示す液晶表示装置の構成は、基板と、基板上に形成されたトラン

50

ジスタ及び液晶素子、と、を有する。そして、トランジスタの半導体層と、液晶素子の画素電極又は共通電極と、は同一工程により形成された膜である。

【0094】

なお、トランジスタの半導体層は、液晶素子の画素電極及び共通電極の一部であってもよい。つまり、液晶素子の画素電極及び共通電極は、トランジスタの半導体層と、さらに別の導電膜との積層であってもよい。

【0095】

なお、液晶素子は画素電極と、画素部の複数の画素に渡って接続された共通電極と、の電位差により生ずる横方向の電界により、光量を制御する液晶分子の分子配列を基板に対して概ね水平方向に回転させることができればよい。

10

【0096】

さらに本発明の第1実施の形態に係る液晶表示パネルについて詳しく説明する。

【0097】

第1の基板上にトランジスタと、液晶素子の画素電極となる第1電極及び液晶素子の共通電極となる第2の電極と、が形成されている。なお、本明細書において、第1の基板上にトランジスタと、第1の電極及び第2の電極とが形成された状態の基板を回路基板という。そして、液晶表示パネルは、回路基板と、回路基板と対向して設けられた第2の基板（対向基板）とが張り合わされ、その間には液晶層を有する。なお、対向基板にもトランジスタや液晶素子の画素電極となる第1の電極及び液晶素子の共通電極となる第2の電極とが形成されていても構わない。

20

【0098】

続いて、本発明の第1の実施の形態に係る液晶表示パネルに適用可能な回路基板の構成を以下に示す。

【0099】

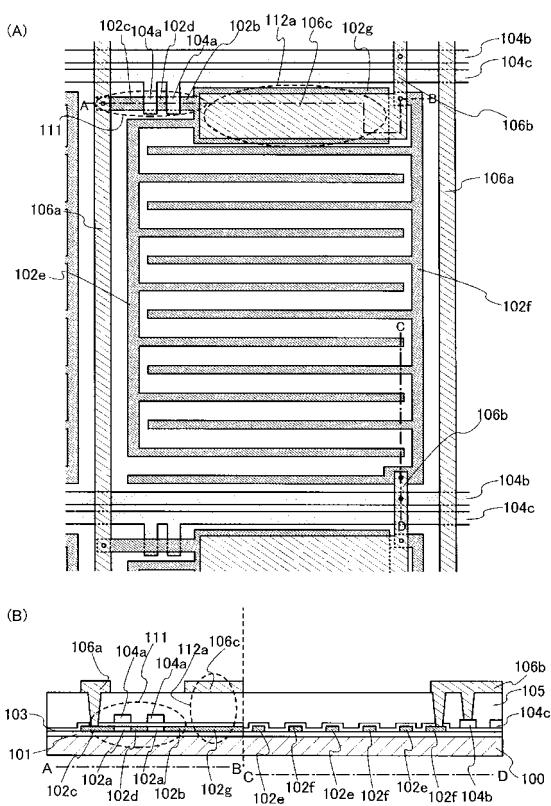

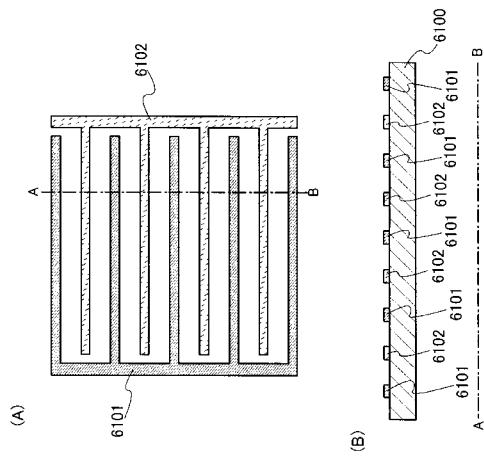

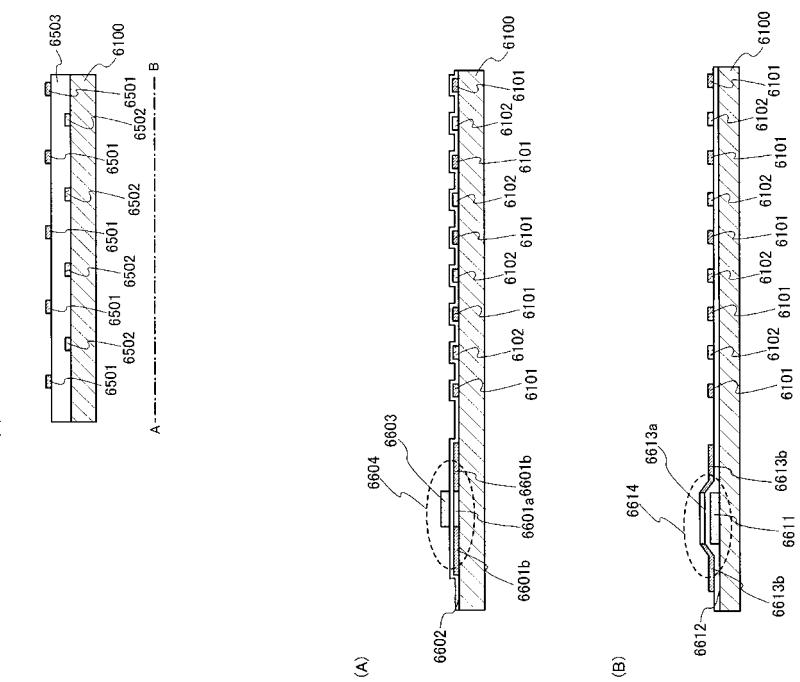

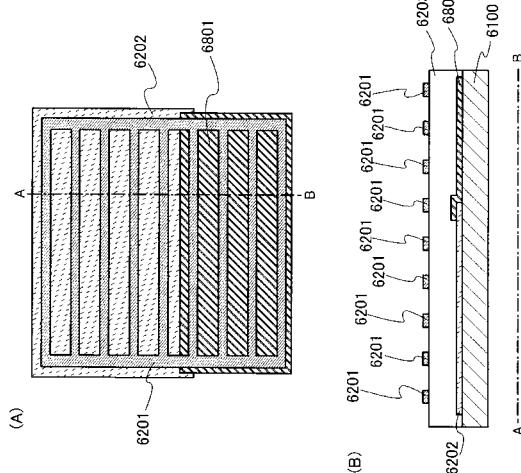

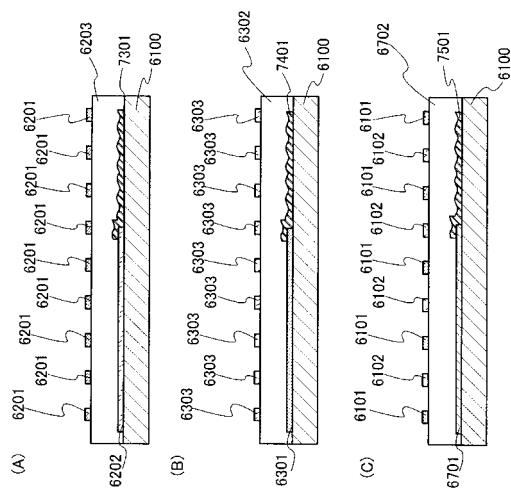

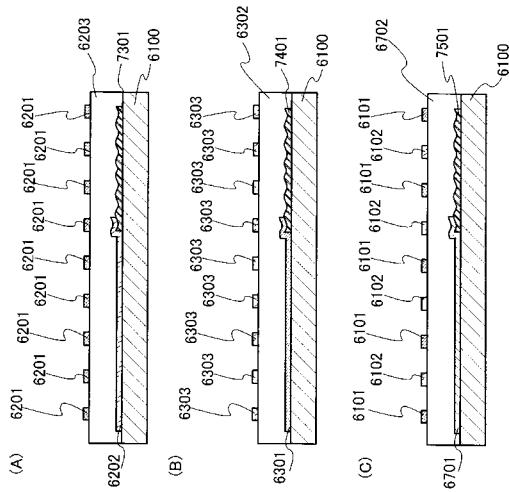

まず、本発明の第1の実施の形態に係る回路基板の第1の構成について説明する。第1の構成の上面図を図61(A)に示している。図61(A)の破線A-Bの断面図を図61(B)に示す。基板6100上に第1の電極6101と第2の電極6102を有する。第1の電極6101又は第2の電極6102の一方が画素電極で、他方が共通電極である。第1の電極6101はトランジスタの半導体層と同層の膜により形成されている。なお、第2の電極6102はトランジスタの半導体層と同層の膜でもいいし、別の膜であってもよい。

30

【0100】

なお、基板6100上にトランジスタを有する場合の回路基板の構成例を図66(A)、(B)に示す。図66(A)に示すトランジスタはいわゆるトップゲート構造のトランジスタであり、図66(B)に示すトランジスタはいわゆるボトムゲート構造のトランジスタである。

【0101】

図66(A)の回路基板は、トランジスタ6604、第1の電極6101及び第2の電極6102を有している。また、トランジスタ6604の半導体層はチャネル形成領域6601aと不純物領域6601bを有している。チャネル形成領域6601a上には絶縁膜6602を介してゲート電極6603を有している。第1の電極6101はトランジスタ6604の半導体層と同層の膜である。

40

【0102】

図66(B)の回路基板は、トランジスタ6614、第1の電極6101及び第2の電極6102を有している。また、トランジスタ6614の半導体層はチャネル形成領域6613aと不純物領域6613bを有している。チャネル形成領域6613a下には絶縁膜6612を介してゲート電極6611を有している。第1の電極6101はトランジスタ6614の半導体層と同層の膜である。

【0103】

第1の電極6101及び第2の電極6102は櫛歯型の形状を有しており、電極のプラン

50

チ部分が互い違いになるように配置されている。なお、図61(B)では、第1の電極6101と第2の電極6102とが基板6100上に直接接して設けられているが、本発明はそれに限定されない。第1の電極6101と第2の電極6102とは基板6100上に形成された異なる絶縁膜の上に形成されていてもよい。よって、断面から見たとき、第1の電極6101と第2の電極6102とは基板6100面と垂直方向にずれて配置されていてもよい。本構成の回路基板はいわゆるIPS方式の液晶表示パネルに用いるのに適している。

#### 【0104】

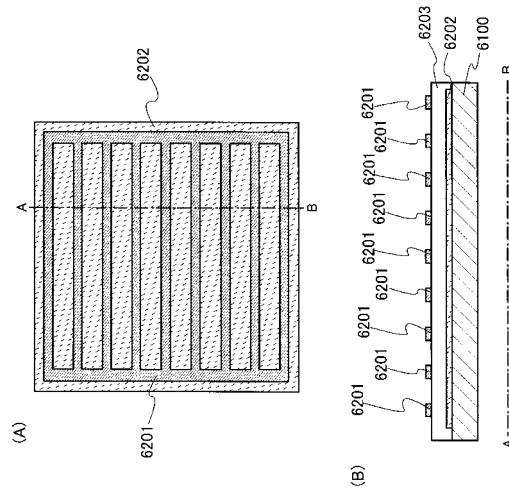

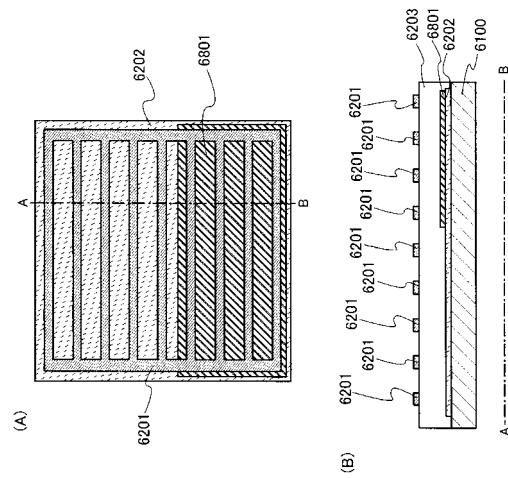

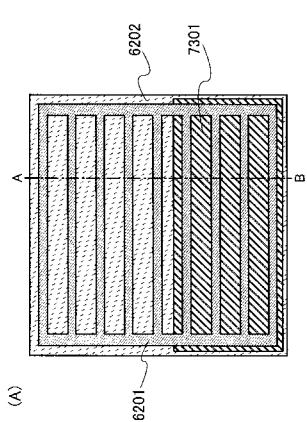

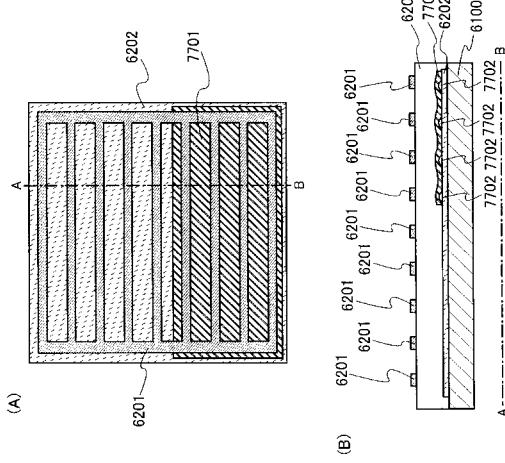

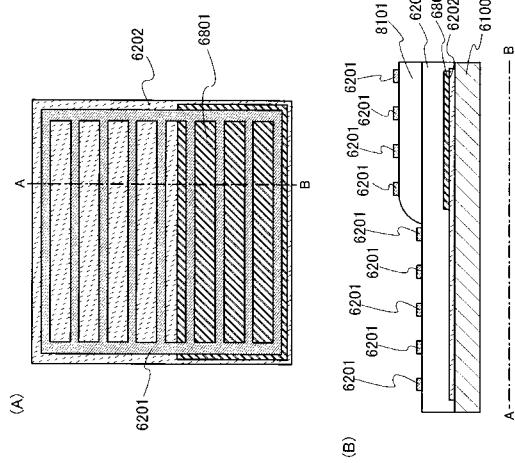

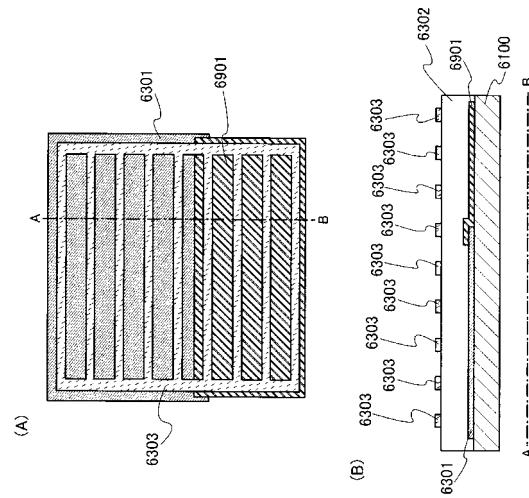

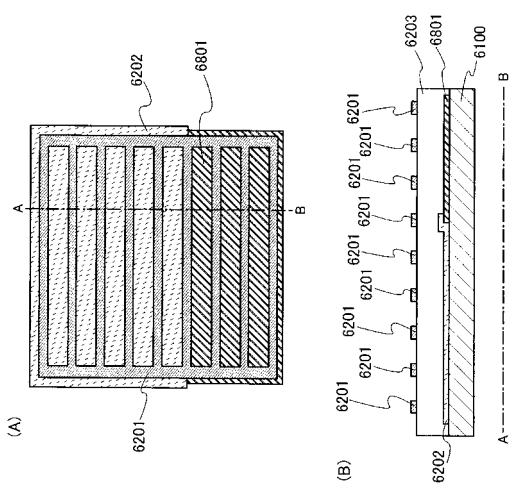

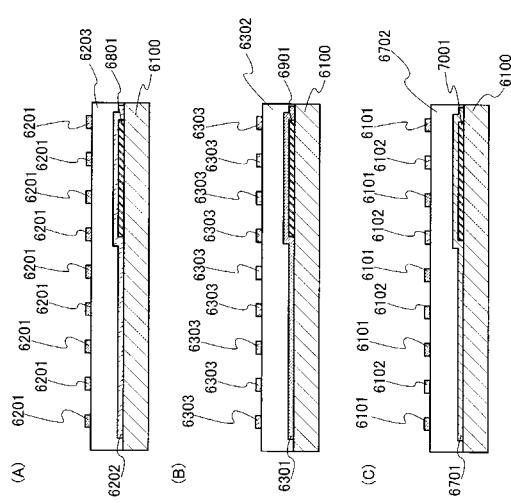

次に、本発明の第1の実施の形態に係る回路基板の第2の構成について説明する。第2の構成の上面図を図62(A)に示している。図62(A)の破線A-Bの断面図を図62(B)に示す。基板6100上に第2の電極6202を有し、第2の電極6202を覆うように絶縁膜6203を有し、絶縁膜6203上に第1の電極6201を有する。第1の電極6201又は第2の電極6202の一方が画素電極で、他方が共通電極である。第1の電極6201はトランジスタの半導体層と同層の膜により形成されている。第1の電極6201はスリットを有している。第2の電極6202はプレート状(一面を覆う形状)の電極である。なお、図62(A)では一例として矩形状のスリットを用いているが本発明は矩形状のスリットに限定されない。なお、図62(B)では、第2の電極6202が基板6100上に直接接して設けられているが、本発明はこれに限定されない。本構成の回路基板はいわゆるFFS方式の液晶表示パネルに用いるのに適している。

#### 【0105】

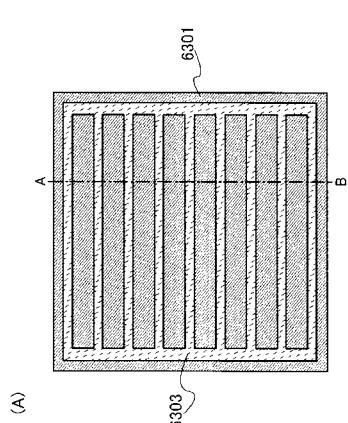

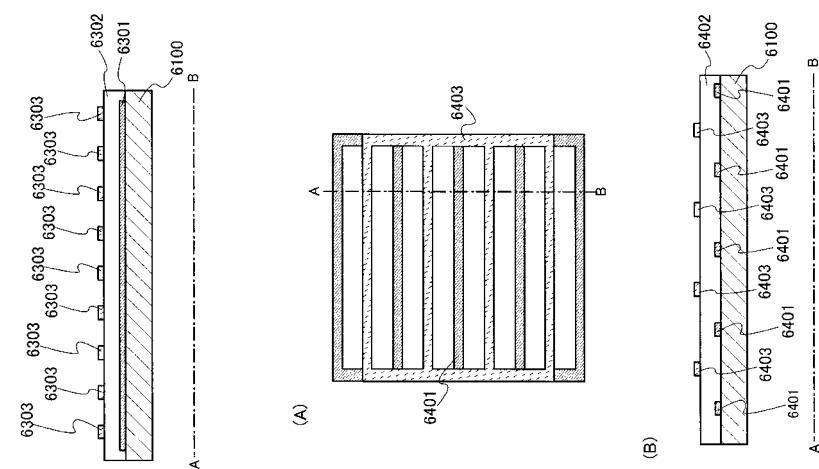

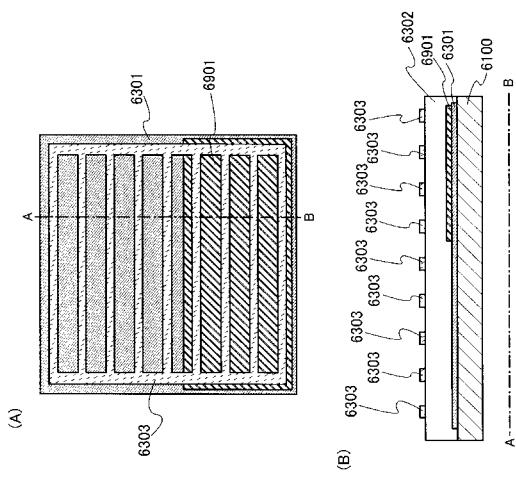

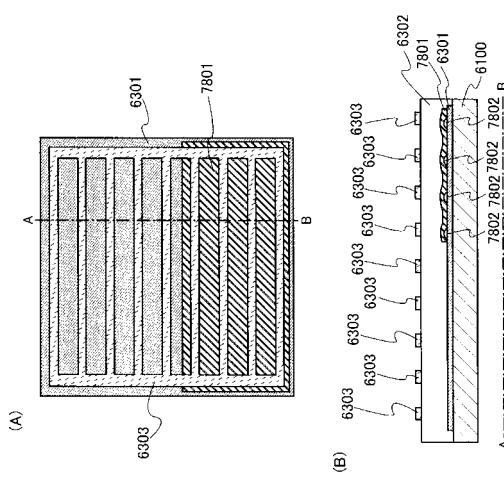

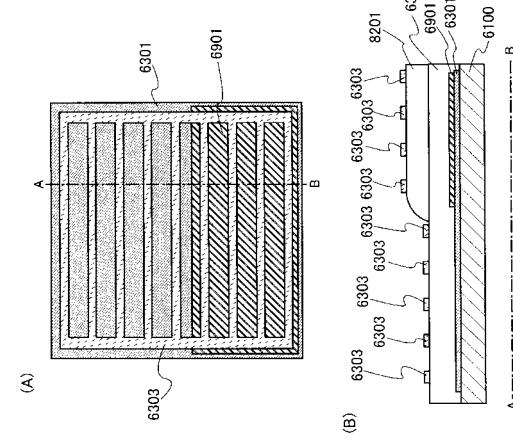

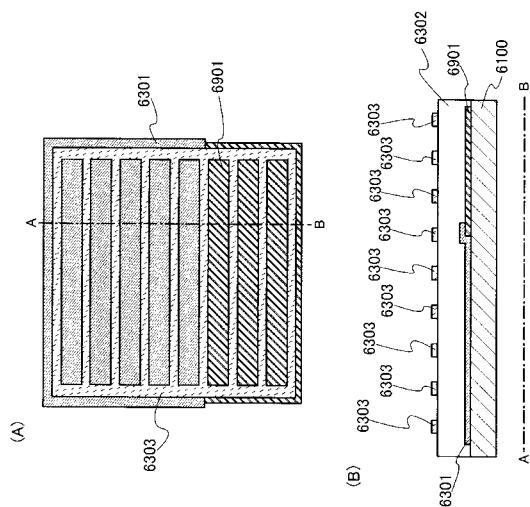

次に、本発明の第1の実施の形態に係る回路基板の第3の構成について説明する。第3の構成の上面図を図63(A)に示している。図63(A)の破線A-Bの断面図を図63(B)に示す。基板6100上に第1の電極6301を有し、第1の電極6301を覆うように絶縁膜6302を有し、絶縁膜6302上に第2の電極6303を有する。第1の電極6301又は第2の電極6303の一方が画素電極で、他方が共通電極である。第1の電極6301はトランジスタの半導体層と同層の膜により形成されている。第1の電極6301はプレート状(一面を覆う形状)の電極である。第2の電極6303はスリットを有している。なお、図63(A)では一例として矩形状のスリットを用いているが本発明はこれに限定されない。なお、図63(B)では、第1の電極6301が基板6100上に直接接して設けられているが、本発明はこれに限定されない。本構成の回路基板はいわゆるFFS方式の液晶表示パネルに用いるのに適している。

#### 【0106】

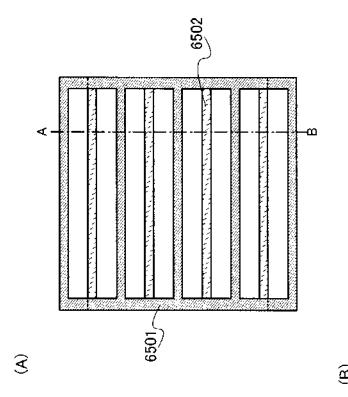

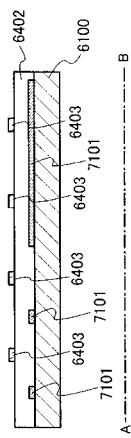

次に、本発明の第1の実施の形態に係る回路基板の第4の構成について説明する。第4の構成の上面図を図64(A)に示している。図64(A)の破線A-Bの断面図を図64(B)に示す。基板6100上に第1の電極6401を有し、第1の電極6401を覆うように絶縁膜6402を有し、絶縁膜6402上に第2の電極6403を有する。第1の電極6401又は第2の電極6403の一方が画素電極で、他方が共通電極である。第1の電極6401はトランジスタの半導体層と同層の膜により形成されている。第1の電極6401及び第2の電極6403はスリットを有している。なお、図64(A)では、一例として矩形状のスリットを用いているが、本発明はこれに限定されない。なお、図64(B)では、第1の電極6401が基板6100上に直接接して設けられているが、本発明はこれに限定されない。本構成の回路基板はいわゆるIPS方式の液晶表示パネルに用いるのに適している。

#### 【0107】

次に、本発明の第1の実施の形態に係る回路基板の第5の構成について説明する。第5の構成の上面図を図65(A)に示している。図65(A)の破線A-Bの断面図を図65(B)に示す。基板6100上に第2の電極6502を有し、第2の電極6502を覆うように絶縁膜6503を有し、絶縁膜6503上に第1の電極6501を有する。第1の電極6501又は第2の電極6502の一方が画素電極で、他方が共通電極である。第1の電極6501はトランジスタの半導体層と同層の膜により形成されている。第1の電極

10

20

30

40

50

6501及び第2の電極6502はスリットを有している。なお、図65(A)では、一例として矩形状のスリットを用いているが、本発明はこれに限定されない。なお、図65(B)では、第2の電極6502が基板6100上に直接接して設けられているが、本発明はこれに限定されない。本構成の回路基板はいわゆるIPS方式の液晶表示パネルに用いるのに適している。

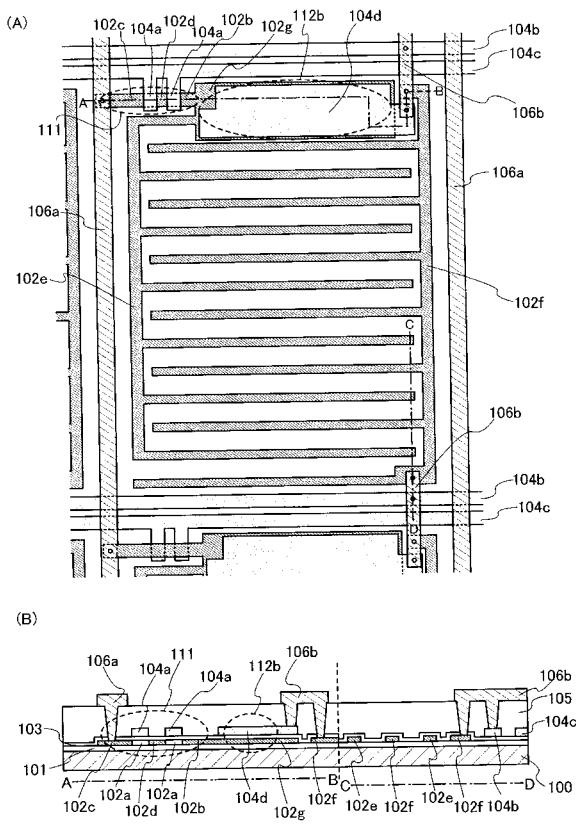

#### 【0108】

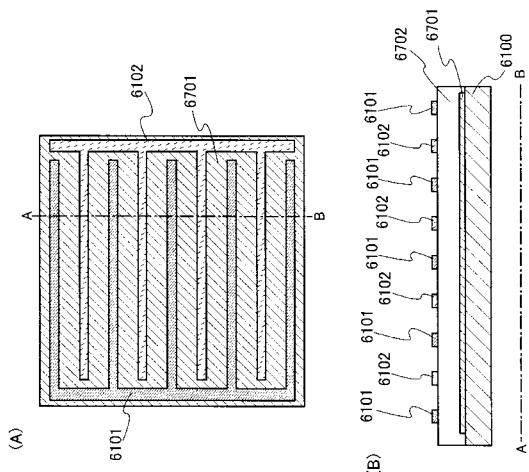

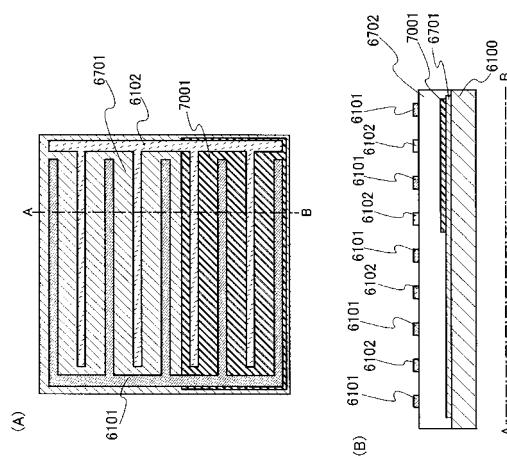

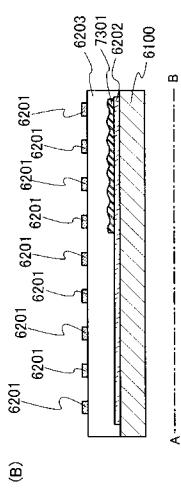

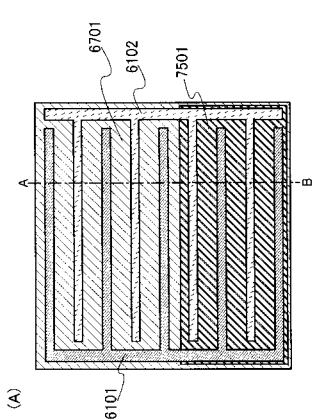

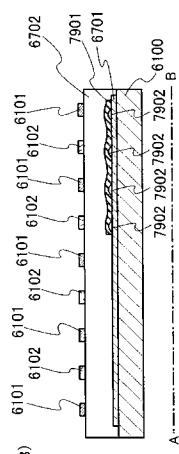

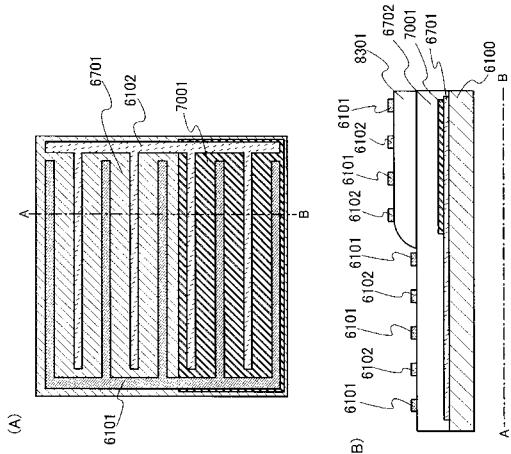

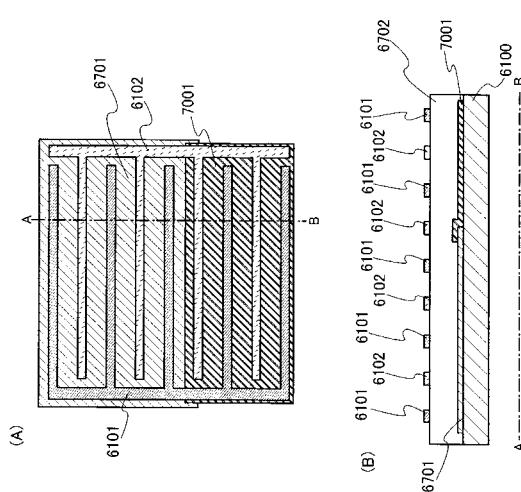

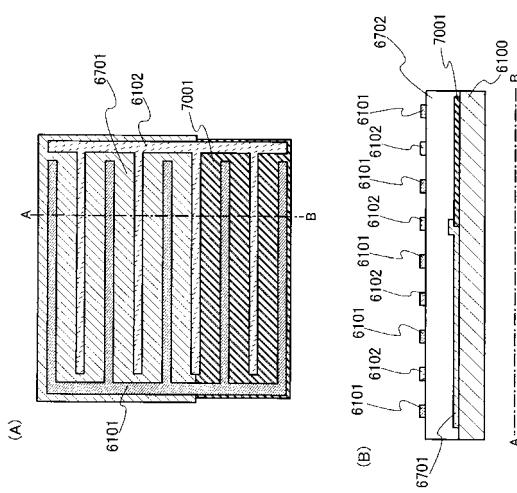

次に、本発明の第1の実施の形態に係る回路基板の第6の構成について説明する。第6の構成の上面図を図67(A)に示している。図67(A)の破線A-Bの断面図を図67(B)に示す。基板6100上に第3の電極6701を有し、第3の電極6701を覆うように絶縁膜6702を有し、絶縁膜6702上に第1の電極6101及び第2の電極6102を有する。第1の電極6101又は第2の電極6102の一方が画素電極で、他方が共通電極である。また、第3の電極6701も画素電極又は共通電極である。第1の電極6101はトランジスタの半導体層と同層の膜により形成されている。第1の電極6101及び第2の電極6102は櫛歯型の形状を有しており、電極のプランチ部分が互い違いになるように配置されている。なお、図67(B)では、第3の電極6701が基板6100上に直接接して設けられているが、本発明はこれに限定されない。本構成の回路基板はいわゆるIPS方式とFFS方式を組み合わせた液晶表示パネルに用いるのに適している。

#### 【0109】

次に、本発明の第1の実施の形態に係る回路基板の第7の構成について説明する。第7の構成の上面図を図68(A)に示している。図68(A)の破線A-Bの断面図を図68(B)に示す。図68(A)、(B)は、第2の電極6202上に反射性の導電膜6801を有した構成である。なお、図120(A)、(B)に示すように、基板6100上に反射性の導電膜6801を設け、反射性の導電膜6801の一部が第2の電極6202上に重なるように設けてもよい。第2の電極6202にITOを用いた場合に図120(A)、(B)の構成にすることで、膜切れを防止することができる。また、図123(A)、(B)に示すように、基板6100上に反射性の導電膜6801を設け、第2の電極6202の一部が反射性の導電膜6801上に重なるように設けてもよい。また、図126(A)に示すように、基板6100上に反射性を有する導電膜6801を設け、導電膜6801上に覆うように第2の電極6202を設けても良い。なお、このとき、導電膜6801を金属膜とし、第2の電極6202にITOを用いた場合、金属膜の酸化を防止することができ、反射率を高くすることができる。第2の電極6202が反射性を有する導電膜の場合には、本構成は反射型液晶表示パネルに適している。一方、第2の電極6202が透光性を有する場合には、本構成は半透過型液晶表示パネルに適している。

#### 【0110】

次に、本発明の第1の実施の形態に係る回路基板の第8の構成について説明する。第8の構成の上面図を図69(A)に示している。図69(A)の破線A-Bの断面図を図69(B)に示す。図69(A)、(B)は、第1の電極6301上に反射性の導電膜6901を有した構成である。なお、図121(A)、(B)に示すように、基板6100上に反射性の導電膜6901を設け、反射性の導電膜6901の一部が第1の電極6301上に重なるように設けてもよい。また、図124(A)、(B)に示すように、基板6100上に反射性の導電膜6901を設け、第1の電極6301の一部が反射性の導電膜6901上に重なるように設けてもよい。また、図126(B)に示すように、基板6100上に反射性を有する導電膜6901を設け、導電膜6901上に覆うように第1の電極6301を設けても良い。なお、このとき、導電膜6901を金属膜とした場合、金属膜の酸化を防止することができ、反射率を高くすることができる。第1の電極6301はトランジスタの半導体層と同層の膜であるため透光性を有する。よって、本構成は半透過型液晶表示パネルに適している。

#### 【0111】

次に、本発明の第1の実施の形態に係る回路基板の第9の構成について説明する。第9の

10

20

30

40

50

構成の上面図を図 70 (A) に示している。図 70 (A) の破線 A - B の断面図を図 70 (B) に示す。図 70 (A)、(B) は、第 3 の電極 6701 上に反射性の導電膜 7001 を有した構成である。なお、図 122 (A)、(B) に示すように、基板 6100 上に反射性の導電膜 7001 を設け、反射性の導電膜 7001 の一部が第 3 の電極 6701 上に重なるように設けてよい。第 3 の電極 6701 に ITO を用いた場合に図 122 (A)、(B) の構成にすることで、膜切れを防止することができる。また、図 125 (A)、(B) に示すように、基板 6100 上に反射性の導電膜 7001 を設け、第 3 の電極 6701 の一部が反射性の導電膜 7001 上に重なるように設けてよい。また、図 126 (C) に示すように、基板 6100 上に反射性を有する導電膜 7001 を設け、導電膜 7001 上に覆うように第 3 の電極 6701 を設けてよい。なお、このとき、導電膜 7001 を金属膜とし、第 3 の電極 6701 に ITO を用いた場合、金属膜の酸化を防止することができ、反射率を高くすることができる。第 3 の電極 6701 が反射性を有する導電膜の場合には、本構成は反射型液晶表示パネルに適している。一方、第 3 の電極 6701 が透光性を有する場合には、本構成は半透過型液晶表示パネルに適している。

10

20

30

40

50

#### 【 0112 】

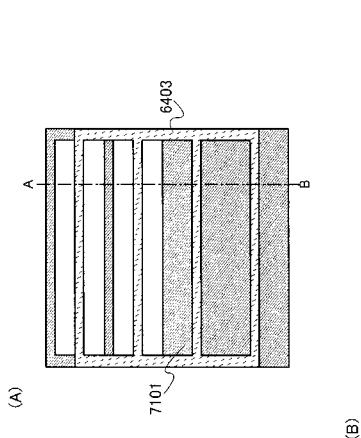

次に、本発明の第 1 の実施の形態に係る回路基板の第 10 の構成について説明する。第 10 の構成の上面図を図 71 (A) に示している。図 71 (A) の破線 A - B の断面図を図 71 (B) に示す。第 10 の構成は第 4 の構成において、第 1 の電極 6401 の代わりにプレート状の領域（一面を覆う形状の領域）と複数のスリットを有する領域とを含む第 1 の電極 7101 を用いた構成である。本構成の回路基板はいわゆる IPS 方式と FFS 方式とを組み合わせた液晶表示パネルに用いるのに適している。第 1 の電極 7101 はトランジスタの半導体層と同層の膜であるため透光性を有する。よって、本構成は半透過型液晶表示パネルに適している。

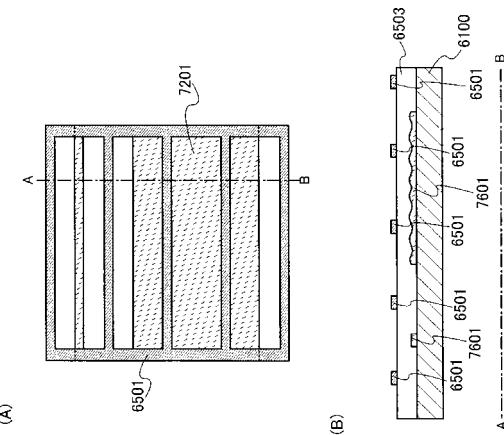

#### 【 0113 】

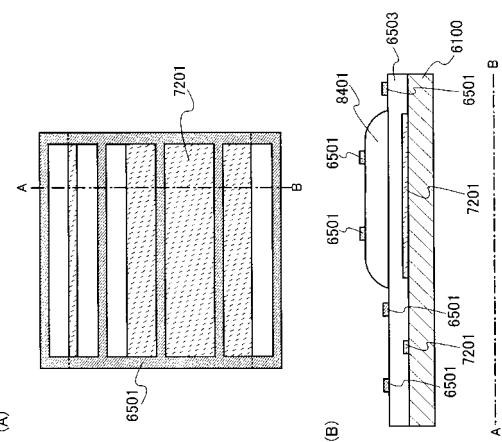

次に、本発明の第 1 の実施の形態に係る回路基板の第 11 の構成について説明する。第 11 の構成の上面図を図 72 (A) に示している。図 72 (A) の破線 A - B の断面図を図 72 (B) に示す。第 11 の構成は第 5 の構成において、第 2 の電極 6502 の代わりにプレート状（一面を覆う形状）の領域と複数のスリットを有する領域とを含む第 2 の電極 7201 を用いた構成である。本構成の回路基板はいわゆる IPS 方式と FFS 方式とを組み合わせた液晶表示パネルに用いるのに適している。第 2 の電極 7201 が反射性を有する導電膜の場合には、本構成は反射型液晶表示パネルに適している。一方、第 2 の電極 7201 が透光性を有する場合には、本構成は半透過型液晶表示パネルに適している。

#### 【 0114 】

次に、本発明の第 1 の実施の形態に係る回路基板の第 12 の構成について説明する。第 12 の構成の上面図を図 73 (A) に示している。図 73 (A) の破線 A - B の断面図を図 73 (B) に示す。第 12 の構成は第 7 の構成において、反射性の導電膜 6801 の代わりに凹凸の形成された反射性の導電膜 7301 を適用した構成である。また、図 120 (B)、図 123 (B)、図 126 (A) において、反射性の導電膜 6801 の代わりに凹凸の形成された反射性の導電膜 7301 を適用した構成を図 127 (A)、図 128 (A)、図 129 (A) に示す。図 129 (A) において、導電膜 7301 を金属膜とし、第 2 の電極 6202 に ITO を用いた場合、金属膜の酸化を防止することができ、反射率を高くすることができる。第 2 の電極 6202 が反射性を有する導電膜の場合には、本構成は反射型液晶表示パネルに適している。一方、第 2 の電極 6202 が透光性を有する場合には、本構成は半透過型液晶表示パネルに適している。

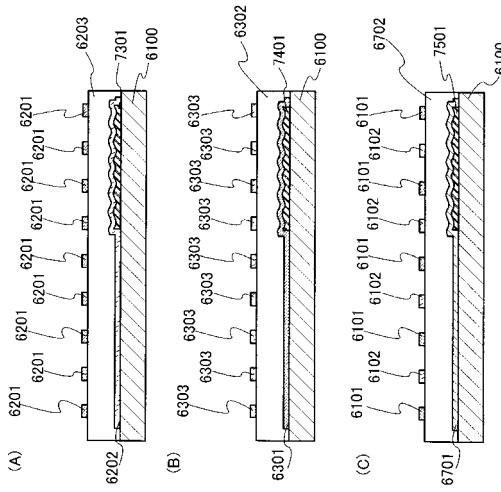

#### 【 0115 】

次に、本発明の第 1 の実施の形態に係る回路基板の第 13 の構成について説明する。第 13 の構成の上面図を図 74 (A) に示している。図 74 (A) の破線 A - B の断面図を図 74 (B) に示す。第 13 の構成は第 8 の構成において、反射性の導電膜 6901 の代わりに凹凸の形成された反射性の導電膜 7401 を適用した構成である。また、図 121 (B)、図 124 (B)、図 126 (B) において、反射性の導電膜 6901 の代わりに凹

凸の形成された反射性の導電膜 7401 を適用した構成を図 127 (B)、図 128 (B)、図 129 (B) に示す。図 129 (B)において、導電膜 7401 を金属膜とした場合、金属膜の酸化を防止することができ、反射率を高くすることができる。第 1 の電極 6301 はトランジスタの半導体層と同層の膜であるため透光性を有する。よって、本構成は半透過型液晶表示パネルに適している。

#### 【0116】

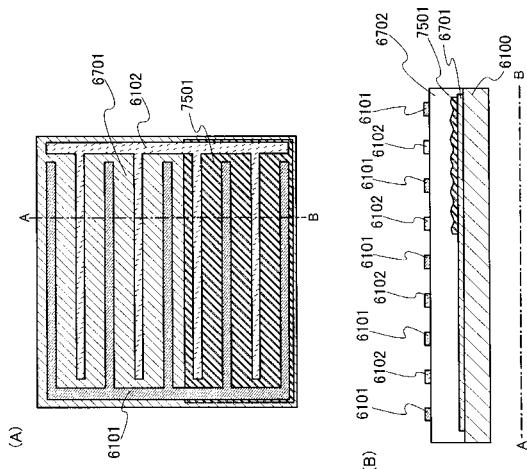

次に、本発明の第 1 の実施の形態に係る回路基板の第 14 の構成について説明する。第 14 の構成の上面図を図 75 (A) に示している。図 75 (A) の破線 A - B の断面図を図 75 (B) に示す。第 14 の構成は第 9 の構成において、反射性の導電膜 7001 の代わりに凹凸の形成された反射性の導電膜 7501 を適用した構成である。また、図 122 (B)、図 125 (B)、図 126 (C) において、反射性の導電膜 7001 の代わりに凹凸の形成された反射性の導電膜 7501 を適用した構成を図 127 (C)、図 128 (C)、図 129 (C) に示す。図 129 (C)において、導電膜 7501 を金属膜とし、第 3 の電極 6701 にITOを用いた場合、金属膜の酸化を防止することができ、反射率を高くすることができる。第 3 の電極 6701 が反射性を有する導電膜の場合には、本構成は反射型液晶表示パネルに適している。一方、第 3 の電極 6701 が透光性を有する場合には、本構成は半透過型液晶表示パネルに適している。

#### 【0117】

次に、本発明の第 1 の実施の形態に係る回路基板の第 15 の構成について説明する。第 15 の構成の上面図を図 76 (A) に示している。図 76 (A) の破線 A - B の断面図を図 76 (B) に示す。第 15 の構成は第 11 の構成において、第 2 の電極 7201 の代わりに凹凸の形成された第 2 の電極 7601 を適用した構成である。第 2 の電極 7201 が反射性を有する導電膜の場合には、本構成は反射型液晶表示パネルに適している。一方、第 2 の電極 7201 が透光性を有する場合には、本構成は半透過型液晶表示パネルに適している。

#### 【0118】

次に、本発明の第 1 の実施の形態に係る回路基板の第 16 の構成について説明する。第 16 の構成の上面図を図 77 (A) に示している。図 77 (A) の破線 A - B の断面図を図 77 (B) に示す。第 16 の構成は第 7 の構成において、第 2 の電極 6202 上に突起物 7702 を形成し、第 2 の電極 6202 及び突起物 7702 上に反射性の導電膜 7701 を形成することにより、反射性の導電膜 6801 の代わりに、凹凸を有する導電膜 7701 を適用した構成である。第 2 の電極 6202 が反射性を有する導電膜の場合には、本構成は反射型液晶表示パネルに適している。一方、第 2 の電極 6202 が透光性を有する場合には、本構成は半透過型液晶表示パネルに適している。

#### 【0119】

このような突起物 7702 の形状を反映して導電膜 7701 の表面に凹凸形状が形成される。このような突起物 7702 を用いることで大きな凹凸の段差や凹凸の数の調整が容易となる。

#### 【0120】

次に、本発明の第 1 の実施の形態に係る回路基板の第 17 の構成について説明する。第 17 の構成の上面図を図 78 (A) に示している。図 78 (A) の破線 A - B の断面図を図 78 (B) に示す。第 17 の構成は第 8 の構成において、第 1 の電極 6301 上に突起物 7802 を形成し、第 1 の電極 6301 及び突起物 7802 上に反射性の導電膜 7801 を形成することにより、反射性の導電膜 6901 の代わりに、凹凸を有する導電膜 7801 を適用した構成である。第 1 の電極 6301 はトランジスタの半導体層と同層の膜であるため透光性を有する。よって、本構成は半透過型液晶表示パネルに適している。

#### 【0121】

このような突起物 7802 の形状を反映して導電膜 7801 の表面に凹凸形状が形成される。このような突起物 7802 を用いることで大きな凹凸の段差や凹凸の数の調整が容易となる。

10

20

30

40

50

## 【0122】

次に、本発明の第1の実施の形態に係る回路基板の第18の構成について説明する。第18の構成の上面図を図79(A)に示している。図79(A)の破線A-Bの断面図を図79(B)に示す。第18の構成は第9の構成において、第3の電極6701上に突起物7902を形成し、第3の電極6701及び突起物7902上に反射性の導電膜7901を形成することにより、反射性の導電膜7901の代わりに、凹凸を有する導電膜7901を適用した構成である。第3の電極6701が反射性を有する導電膜の場合には、本構成は反射型液晶表示パネルに適している。一方、第3の電極6701が透光性を有する場合には、本構成は半透過型液晶表示パネルに適している。

## 【0123】

10 このような突起物7902の形状を反映して導電膜7901の表面に凹凸形状が形成される。このような突起物7902を用いることで大きな凹凸の段差や凹凸の数の調整が容易となる。

## 【0124】

次に、本発明の第1の実施の形態に係る回路基板の第19の構成について説明する。第19の構成の上面図を図80(A)に示している。図80(A)の破線A-Bの断面図を図80(B)に示す。第19の構成は第11の構成において、基板6100上に突起物8001を形成し、基板6100及び突起物8001上に反射性の第2の電極7201を形成することにより、第2の電極7201のプレート状(一面を覆う形状)の領域に凹凸を有する構成である。第2の電極7201が反射性を有する導電膜の場合には、本構成は反射型液晶表示パネルに適している。一方、第2の電極7201が透光性を有する場合には、本構成は半透過型液晶表示パネルに適している。

## 【0125】

20 このような突起物8001の形状を反映して第2の電極7201の表面に凹凸形状が形成される。このような突起物8001を用いることで大きな凹凸の段差や凹凸の数の調整が容易となる。

## 【0126】

次に、本発明の第1の実施の形態に係る回路基板の第20の構成について説明する。第20の構成の上面図を図81(A)に示している。図81(A)の破線A-Bの断面図を図81(B)に示す。第20の構成は第7の構成において、導電膜6801の形成された領域(反射領域)の上側であって絶縁膜6203上に絶縁膜8101を有している。そして、第2の電極6202が透光性を有し、本構成は半透過型液晶表示パネルである。つまり、第2の電極6202が形成され、導電膜6801が形成されていない、領域(透過領域)の上側であって絶縁膜6203上には絶縁膜8101は開口部が形成されている。よって、透過領域でのセルギャップを反射領域のセルギャップより厚くすることができる。

## 【0127】

次に、本発明の第1の実施の形態に係る回路基板の第21の構成について説明する。第21の構成の上面図を図82(A)に示している。図82(A)の破線A-Bの断面図を図82(B)に示す。第21の構成は第8の構成において、導電膜6901の形成された領域(反射領域)の上側であって絶縁膜6302上に絶縁膜8201を有している。そして、第1の電極6301が透光性を有し、本構成は半透過型液晶表示パネルである。つまり、第1の電極6301が形成され、導電膜6901が形成されていない、領域(透過領域)の上側であって絶縁膜6302上には絶縁膜8201は開口部が形成されている。よって、透過領域でのセルギャップを反射領域のセルギャップより厚くすることができる。

## 【0128】

次に、本発明の第1の実施の形態に係る回路基板の第22の構成について説明する。第22の構成の上面図を図83(A)に示している。図83(A)の破線A-Bの断面図を図83(B)に示す。第22の構成は第9の構成において、導電膜7001の形成された領域(反射領域)の上側であって絶縁膜6702上に絶縁膜8301を有している。そして、第3の電極6701が透光性を有し、本構成は半透過型液晶表示パネルである。つまり

10

20

30

40

50

、第3の電極6701が形成され、導電膜7001が形成されていない、領域(透過領域)の上側であって絶縁膜6702上には絶縁膜8301は開口部が形成されている。よって、透過領域でのセルギャップを反射領域のセルギャップより厚くすることができる。

### 【0129】

次に、本発明の第1の実施の形態に係る回路基板の第23の構成について説明する。第22の構成の上面図を図84(A)に示している。図84(A)の破線A-Bの断面図を図84(B)に示す。第23の構成は第11の構成において、第2の電極7201のプレート状の領域(反射領域)の上側であって絶縁膜6503上に絶縁膜8401を有している。そして、第2の電極7201が反射性を有し、本構成は半透過型液晶表示パネルである。つまり、第2の電極7201のスリットを有する領域(透過領域)の上側であって絶縁膜6503上には絶縁膜8401は開口部が形成されている。よって、透過領域でのセルギャップを反射領域のセルギャップより厚くすることができる。

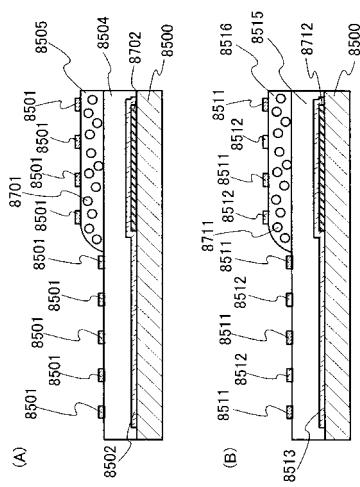

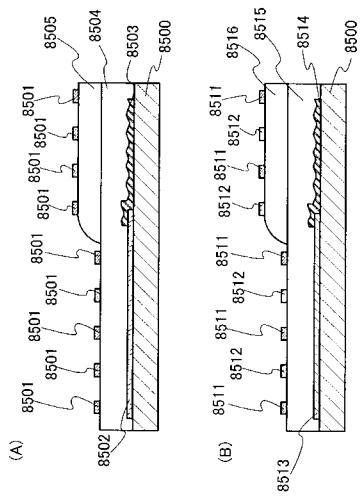

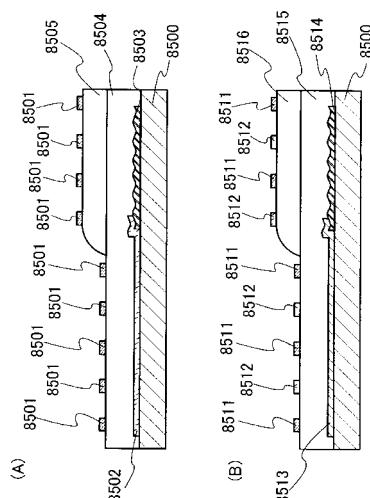

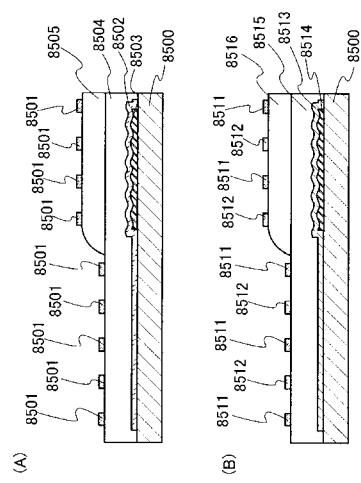

### 【0130】

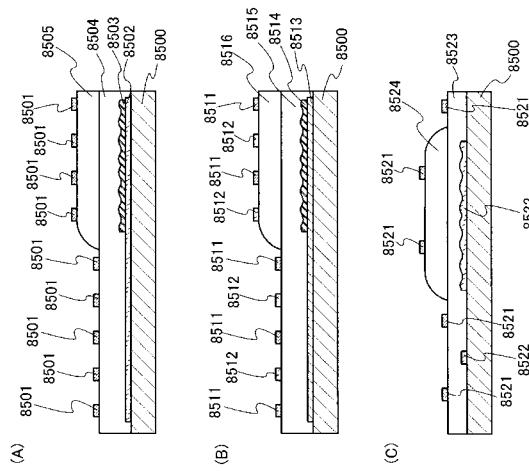

次に、本発明の第1の実施の形態に係る回路基板の第24の構成について説明する。第24の構成は回路基板の断面図85(A)を用いて説明する。基板8500上に第2の電極8502を有し、第2の電極8502上に第2の電極8502より面積が小さく、凹凸を有した反射性の導電膜8503を有する。そして、第2の電極8502が透光性を有し、本構成は半透過型液晶表示パネルである。第2の電極8502及び導電膜8503上に絶縁膜8504を有している。第2の電極8502が形成され、導電膜8503が形成されていない、領域(透過領域)の上側であって絶縁膜8504上に開口部を有する絶縁膜8505を有する。また、プランチの一部が絶縁膜8504上に直接接し、且つプランチの一部が絶縁膜8505上に直接接する第1の電極8501を有する。よって、透過領域でのセルギャップを反射領域(導電膜8503の上側の領域)のセルギャップより厚くすることができる。なお、図130(A)に示すように、基板8500上に反射性の導電膜8503を設け、反射性の導電膜8503の一部が第2の電極8502上に重なるように設けてもよい。第2の電極8502にITOを用いた場合に図130(A)の構成にすることで、膜切れを防止することができる。また、図131(A)に示すように、基板8500上に反射性の導電膜8503を設け、第2の電極8502の一部が反射性の導電膜8503上に重なるように設けてもよい。また、図132(A)に示すように、基板8500上に反射性を有する導電膜8503を設け、導電膜8503上に覆うように第2の電極8502を設けても良い。図132(A)において、導電膜8503を金属膜とし、第2の電極8502にITOを用いた場合、金属膜の酸化を防止することができ、反射率を高くすることができる。

### 【0131】

次に、本発明の第1の実施の形態に係る回路基板の第25の構成について説明する。第25の構成は回路基板の断面図85(B)を用いて説明する。基板8500上に第3の電極8513を有し、第3の電極8513上に第3の電極8513より面積が小さく、凹凸を有した反射性の導電膜8514を有する。そして、第3の電極8513が透光性を有し、本構成は半透過型液晶表示パネルである。第3の電極8513及び導電膜8514上に絶縁膜8515を有している。第3の電極8513が形成され、導電膜8514が形成されていない、領域(透過領域)の上側であって絶縁膜8515上に開口部を有する絶縁膜8516を有する。また、プランチの一部が絶縁膜8515上に直接接し、且つプランチの一部が絶縁膜8516上に直接接する第1の電極8511及び第2の電極8512を有する。よって、透過領域でのセルギャップを反射領域(導電膜8514の上側の領域)のセルギャップより厚くすることができる。なお、図130(B)に示すように、基板8500上に反射性の導電膜8514を設け、反射性の導電膜8514の一部が第3の電極8513上に重なるように設けてもよい。第3の電極8513にITOを用いた場合に図130(B)の構成にすることで、膜切れを防止することができる。また、図131(B)に示すように、基板8500上に反射性の導電膜8514を設け、第3の電極8513を設け、第3の電極8513の一部が反射性の導電膜8514上に重なるように設けてもよい。また、図132(B)に示すように、基板8500上に反射性の導電膜8514を設け、第3の電極8513の一部が反射性の導電膜8514上に重なるように設けてもよい。また、図132(B)に示すように、基板8500上に反射性の導電膜8514を設け、第3の電極8513の一部が反射性の導電膜8514上に重なるように設けてもよい。

10

20

30

40

50

すように、基板 8500 上に反射性を有する導電膜 8514 を設け、導電膜 8514 上に覆うように第 3 の電極 8513 を設けても良い。図 132 (A) において、導電膜 8514 を金属膜とし、第 3 の電極 8513 に ITO を用いた場合、金属膜の酸化を防止することができ、反射率を高くすることができる。

#### 【0132】

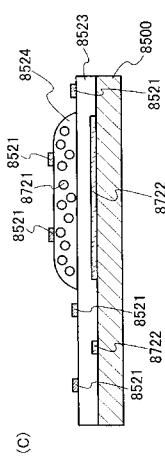

次に、本発明の第 1 の実施の形態に係る回路基板の第 26 の構成について説明する。第 26 の構成は回路基板の断面図 85 (C) を用いて説明する。基板 8500 上に第 2 の電極 8522 を有している。第 2 の電極 8522 は、スリットを有する領域と、プレート状の領域とを有し、プレート状の領域には凹凸を有する。そして、第 2 の電極 8522 が反射性を有し、本構成は半透過型液晶表示パネルである。また、第 2 の電極 8522 及び基板 8500 上に絶縁膜 8523 を有する。第 2 の電極 8522 のプレート状の領域（反射領域）の上側であって絶縁膜 8523 上に絶縁膜 8524 を有している。つまり、第 2 の電極 8522 のスリットを有する領域（透過領域）の上側であって絶縁膜 8523 上には絶縁膜 8524 は開口部が形成されている。また、プランチの一部が絶縁膜 8523 上に直接接し、且つプランチの一部が絶縁膜 8524 上に直接接する第 1 の電極 8521 を有する。よって、透過領域でのセルギャップを反射領域のセルギャップより厚くすることができる。

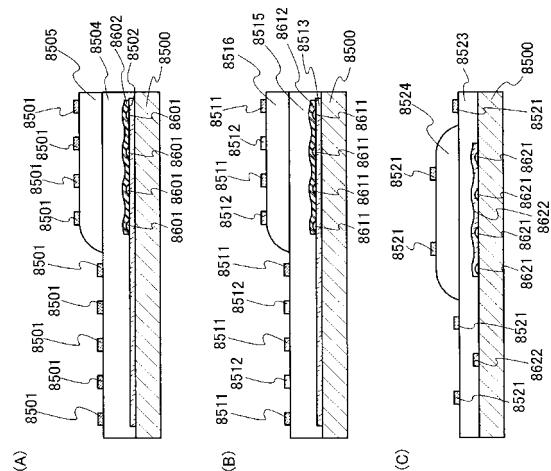

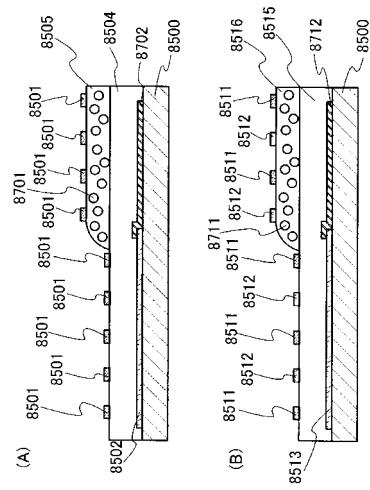

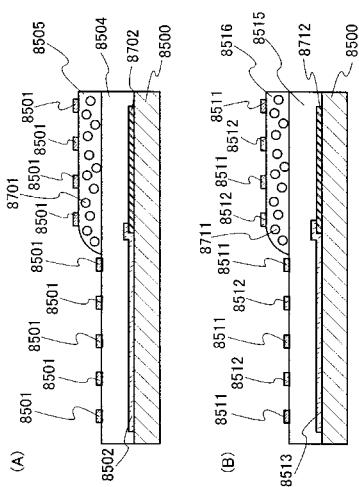

#### 【0133】

次に、本発明の第 1 の実施の形態に係る回路基板の第 27 の構成について説明する。第 27 の構成は回路基板の断面図 86 (A) を用いて説明する。第 27 の構成は第 24 の構成において、第 2 の電極 8502 上に突起物 8601 を形成し、第 2 の電極 8502 及び突起物 8601 上に反射性の導電膜 8602 を形成することにより、凹凸を有する導電膜 8503 の代わりに、突起物 8601 により形成される凹凸を有する導電膜 8602 を適用した構成である。そして、第 2 の電極 8502 が透光性を有し、本構成は半透過型液晶表示パネルである。

#### 【0134】

このように突起物 8601 の形状を反映して導電膜 8602 の表面に凹凸形状が形成される。このような突起物 8601 を用いることで大きな凹凸の段差や凹凸の数の調整が容易となる。

#### 【0135】

次に、本発明の第 1 の実施の形態に係る回路基板の第 28 の構成について説明する。第 28 の構成は回路基板の断面図 86 (B) を用いて説明する。第 28 の構成は第 25 の構成において、第 3 の電極 8513 上に突起物 8611 を形成し、第 3 の電極 8513 及び突起物 8611 上に反射性の導電膜 8612 を形成することにより、凹凸を有する導電膜 8514 の代わりに、突起物 8611 により形成される凹凸を有する導電膜 8612 を適用した構成である。そして、第 3 の電極 8513 が透光性を有し、本構成は半透過型液晶表示パネルである。

#### 【0136】

このように突起物 8611 の形状を反映して導電膜 8612 の表面に凹凸形状が形成される。このような突起物 8611 を用いることで大きな凹凸の段差や凹凸の数の調整が容易となる。

#### 【0137】

次に、本発明の第 1 の実施の形態に係る回路基板の第 29 の構成について説明する。第 29 の構成は回路基板の断面図 86 (C) を用いて説明する。第 29 の構成は第 26 の構成において、基板 8500 上に突起物 8621 を形成し、基板 8500 及び突起物 8621 上に反射性を有する第 2 の電極 8622 を形成することにより、凹凸を有する第 2 の電極 8522 の代わりに、突起物 8621 により形成される凹凸を有する第 2 の電極 8622 を適用した構成である。そして、第 2 の電極 8622 が反射性を有し、本構成は半透過型液晶表示パネルである。

#### 【0138】

10

20

30

40

50

このように突起物 8621 の形状を反映して第 2 の電極 8622 の表面に凹凸形状が形成される。このような突起物 8621 を用いることで大きな凹凸の段差や凹凸の数の調整が容易となる。

#### 【0139】

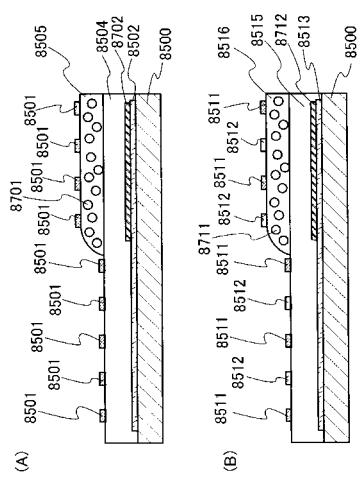

次に、本発明の第 1 の実施の形態に係る回路基板の第 30 の構成について説明する。第 30 の構成は回路基板の断面図 87(A)を用いて説明する。第 30 の構成は第 24 の構成において、凹凸を有する導電膜 8503 の代わりに、平坦な導電膜 8702 を適用し、絶縁膜 8505 には散乱材として機能する粒子 8701 が含まれている。なお、図 133(A)に示すように、基板 8500 上に反射性の導電膜 8702 を設け、反射性の導電膜 8702 の一部が第 2 の電極 8502 上に重なるように設けてもよい。第 2 の電極 8502 にITOを用いた場合に図 133(A)の構成にすることで、膜切れを防止することができる。また、図 134(A)に示すように、基板 8500 上に反射性の導電膜 8702 を設け、第 2 の電極 8502 の一部が反射性の導電膜 8702 上に重なるように設けてもよい。また、図 135(A)に示すように、基板 8500 上に反射性を有する導電膜 8702 を設け、導電膜 8702 上に覆うように第 2 の電極 8502 を設けても良い。図 135(A)において、導電膜 8702 を金属膜とし、第 2 の電極 8502 にITOを用いた場合、金属膜の酸化を防止することができ、反射率を高くすることができる。そして、第 2 の電極 8502 が透光性を有し、本構成は半透過型液晶表示パネルである。

#### 【0140】

次に、本発明の第 1 の実施の形態に係る回路基板の第 31 の構成について説明する。第 31 の構成は回路基板の断面図 87(B)を用いて説明する。第 31 の構成は第 25 の構成において、凹凸を有する導電膜 8514 の代わりに、平坦な導電膜 8712 を適用し、絶縁膜 8516 には散乱材として機能する粒子 8711 が含まれている。なお、図 133(B)に示すように、基板 8500 上に反射性の導電膜 8712 を設け、反射性の導電膜 8712 の一部が第 3 の電極 8513 上に重なるように設けてもよい。第 3 の電極 8513 にITOを用いた場合に図 133(B)の構成にすることで、膜切れを防止することができる。また、図 134(B)に示すように、基板 8500 上に反射性の導電膜 8712 を設け、第 3 の電極 8513 の一部が反射性の導電膜 8712 上に重なるように設けてもよい。また、図 135(B)に示すように、基板 8500 上に反射性を有する導電膜 8712 を設け、導電膜 8712 上に覆うように第 3 の電極 8513 を設けても良い。図 135(B)において、導電膜 8712 を金属膜とし、第 3 の電極 8513 にITOを用いた場合、金属膜の酸化を防止することができ、反射率を高くすることができる。そして、第 3 の電極 8513 が透光性を有し、本構成は半透過型液晶表示パネルである。

#### 【0141】

次に、本発明の第 1 の実施の形態に係る回路基板の第 32 の構成について説明する。第 32 の構成は回路基板の断面図 87(C)を用いて説明する。第 32 の構成は第 26 の構成において、凹凸を有する第 2 の電極 8522 の代わりに、平坦な第 2 の電極 8722 を適用し、絶縁膜 8524 には散乱材として機能する粒子 8721 が含まれている。そして、第 2 の電極 8722 が反射性を有し、本構成は半透過型液晶表示パネルである。

#### 【0142】

このように、本発明の第 1 の実施形態に係る液晶表示パネルには様々な構成の回路基板を適用することができる。

#### 【0143】

また、上述したような回路基板と対向基板とを貼り合わせた場合の液晶表示パネルの主要な構成を以下に示す。

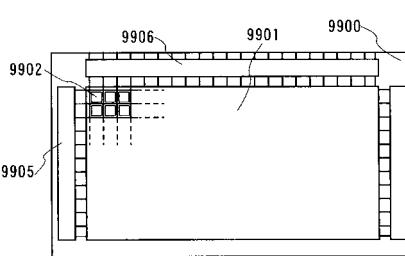

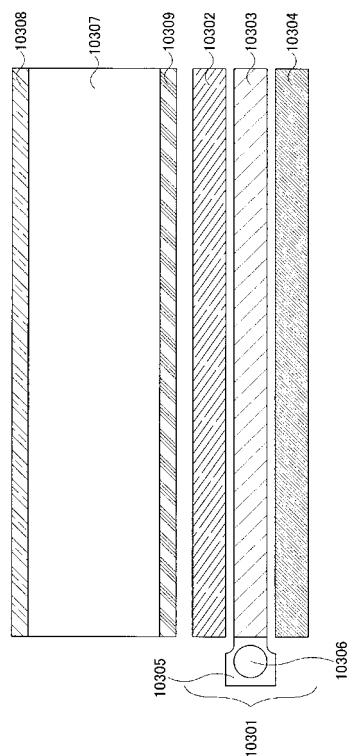

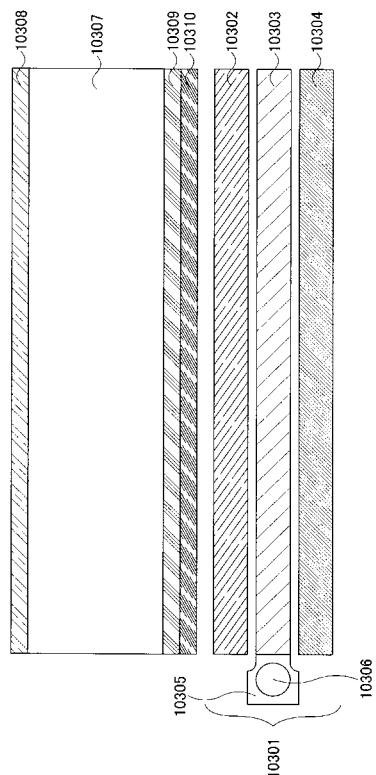

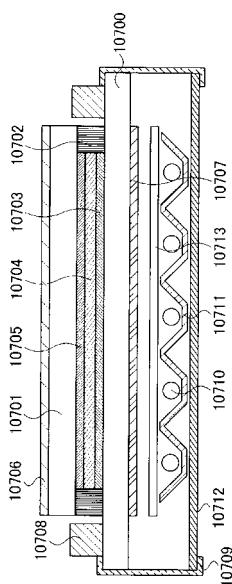

#### 【0144】

図 88 に示す液晶表示パネルの回路基板の構成について説明する。基板 8800 上に第 1 の電極 8801 及び第 2 の電極 8802 を有する。第 1 の電極 8801 及び第 2 の電極 8802 は一方が液晶素子の画素電極で他方が共通電極である。そして、第 1 電極 8801 又は第 2 の電極 8802 は基板 8800 上に形成されたトランジスタの半導体層と同一工

10

20

30

40

50

程により形成されている。

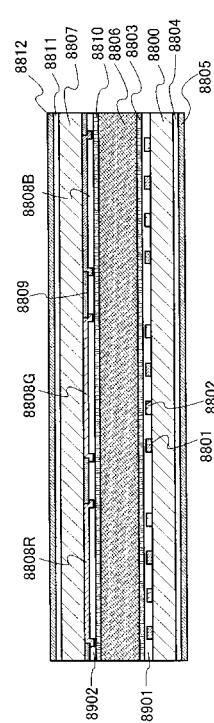

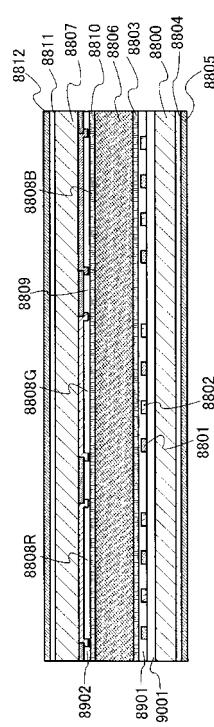

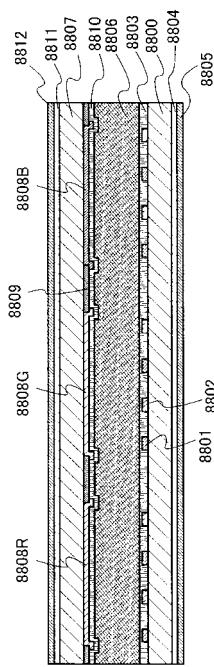

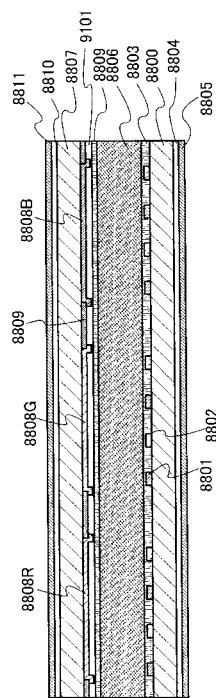

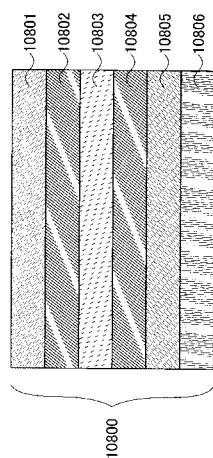

【0145】

第1の電極8801及び第2の電極8802上に配向膜8803が形成されている。そして、基板8800の第1電極8801及び第2の電極8802が形成されていない面には位相差板8804とさらに外側に偏光板が設けられている。

【0146】

次に図88に示す液晶表示パネルの対向基板の構成について説明する。基板8807の一方の面には、遮光膜8809及びカラーフィルター（赤のカラーフィルター8808R、緑のカラーフィルター8808G及び青のカラーフィルター8808B）が形成され、その外側に配向膜8810が設けられている。また、基板8807の他方の面には位相差板8811及び偏光板8812が設けられている。10

【0147】

なお、回路基板に形成された絶縁膜としてやその一部にカラーフィルター及び遮光層（ブラックマトリクス）又はこれらのいずれかが設けられていてもよい。回路基板にカラーフィルターや遮光層を設けることにより、対向基板との位置合わせのマージンが向上する。

【0148】

図88に示す液晶表示パネルは、回路基板の配向膜8803の形成された面と、対向基板の配向膜8810の形成された面とが内側として張り合わされ、その間には液晶層8806を有する。

【0149】

なお、図89に示す液晶表示パネルのように、図88の構成において、回路基板の第1の電極8801及び第2の電極8802上に平坦化膜として機能する絶縁膜8901を形成してもよい。また、対向基板の遮光膜8809及びカラーフィルターの外側に平坦化膜として機能する絶縁膜8902を設けてもよい。20

【0150】

また、第1の電極8801及び第2の電極8802はもちろん基板8800上に直接接して形成されなくててもよく、図90に示すように基板8800上に形成された絶縁膜9001上に第1の電極8801及び第2の電極8802が形成されていてもよい。

【0151】

また、図91に示すように、対向基板の遮光膜8809及びカラーフィルターの外側に透光性を有する導電膜9101を形成してもよい。こうすることにより、静電気防止や、残像除去を図ることができる。30

【0152】

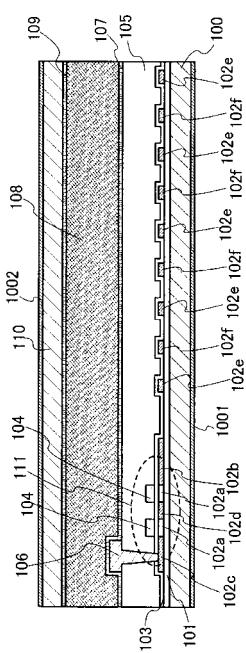

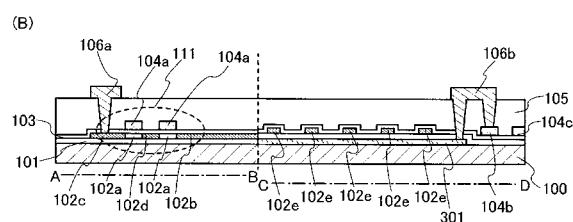

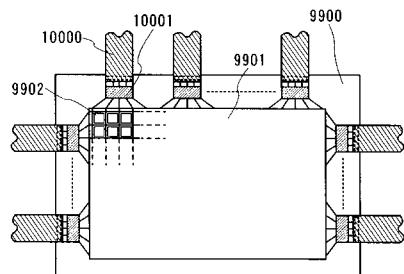

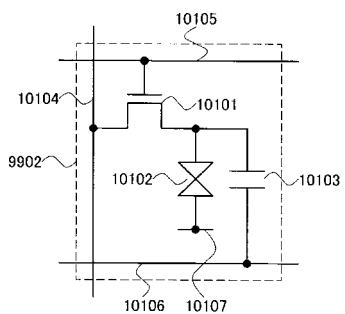

（実施の形態2）

本発明の第2の実施形態に係る液晶表示パネルの構成について説明する。

【0153】

本発明の第2の実施形態に係る液晶表示パネルは、第1の基板上に第1の絶縁膜を有し、第1の絶縁膜上にトランジスタの半導体層と、液晶素子の第1の電極及び第2の電極と、を有し、トランジスタの半導体層と、液晶素子の第1の電極及び第2の電極と、を覆うように第2の絶縁膜を有し、トランジスタの半導体層上に第2の絶縁膜を介してゲート電極を有し、ゲート電極及び第2の絶縁膜を覆うように第3の絶縁膜を有し、第3の絶縁膜及び第2の絶縁膜には孔（コンタクトホール）が設けられ、第3の絶縁膜上に形成された配線が孔を介してトランジスタの半導体層と接続されている。そして第1の基板は、トランジスタを有する面を内側にして、第2の基板と張り合わされている。第1の基板と、第2の基板との間には液晶層を有している。40

【0154】

なお、トランジスタの半導体層と、液晶素子の第1の電極及び液晶素子の第2の電極とは同層の膜である。

【0155】

また、液晶素子の第1の電極及び液晶素子の第2の電極はスリットを有する電極又は櫛形

10

20

30

40

50

電極である。

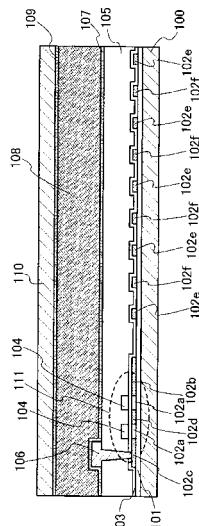

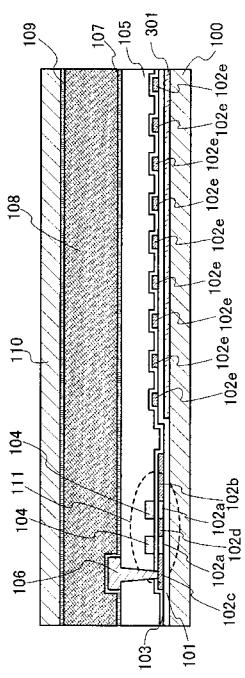

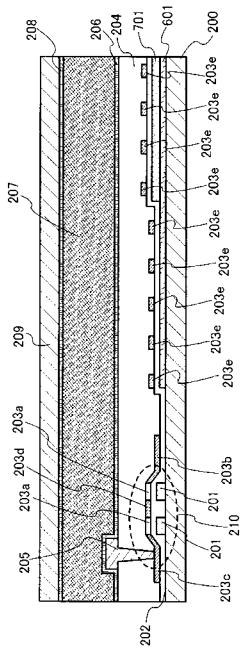

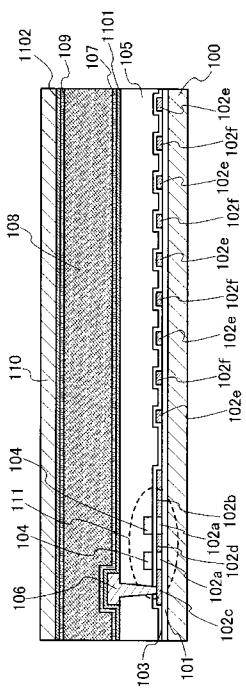

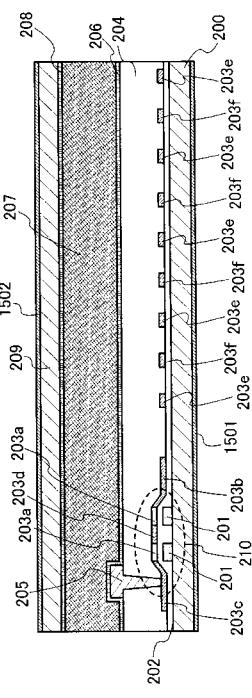

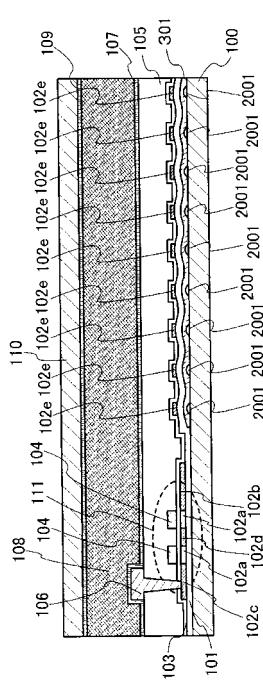

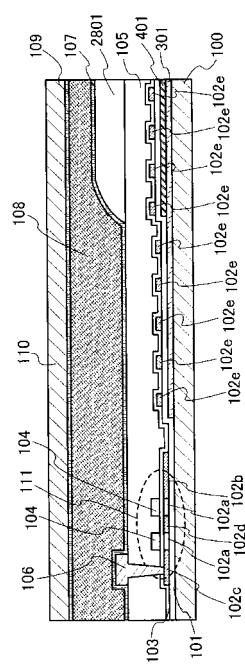

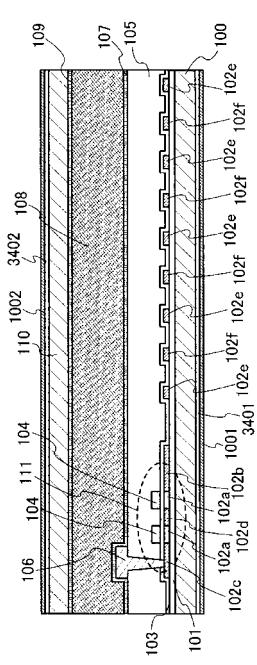

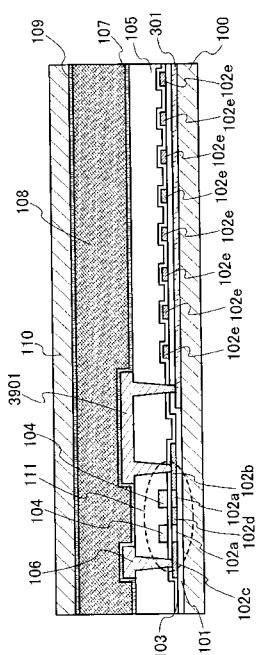

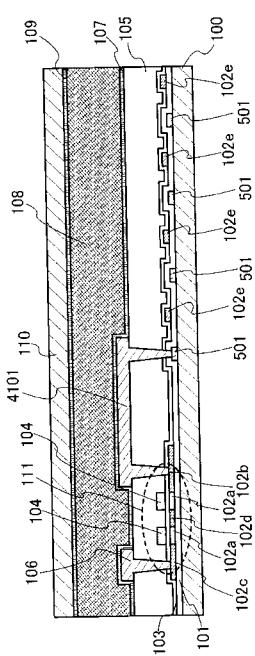

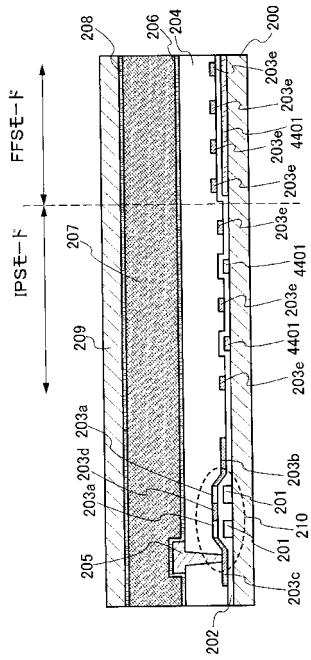

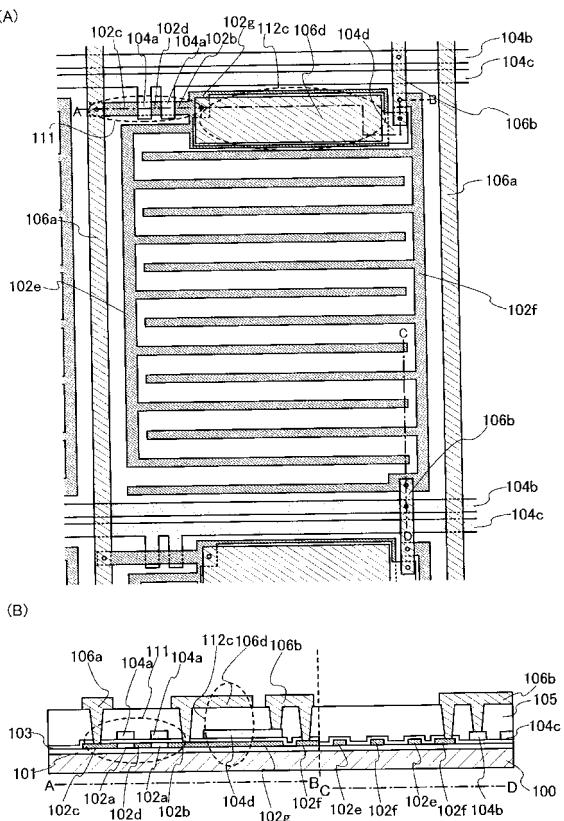

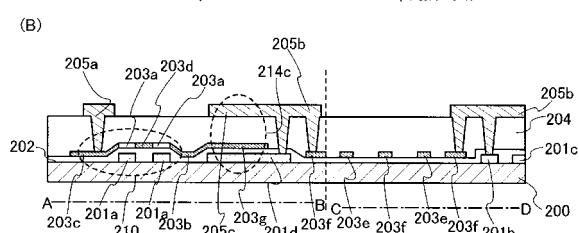

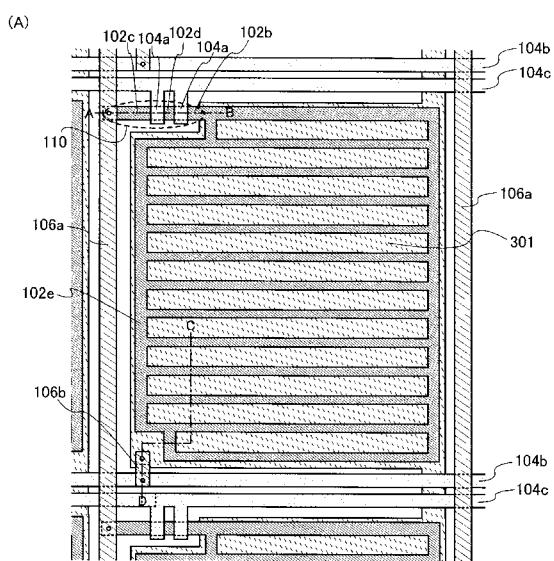

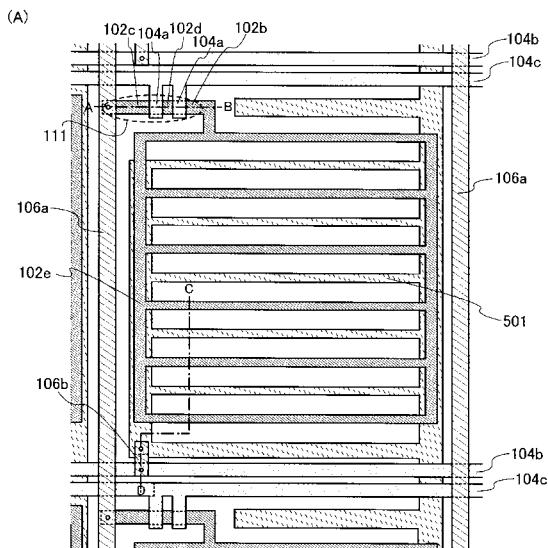

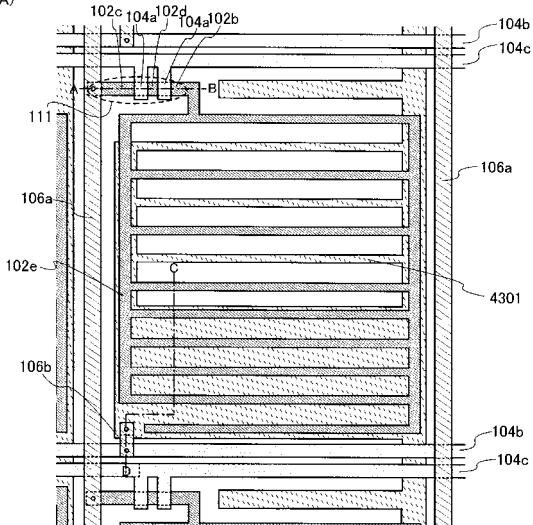

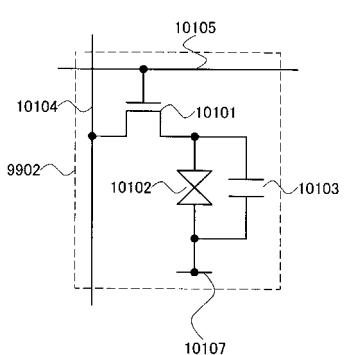

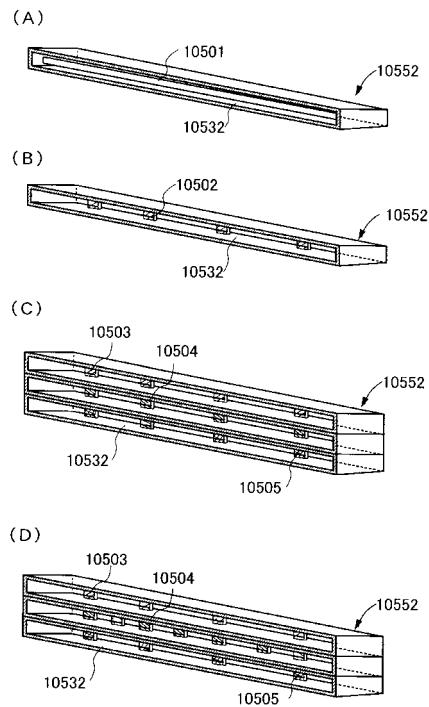

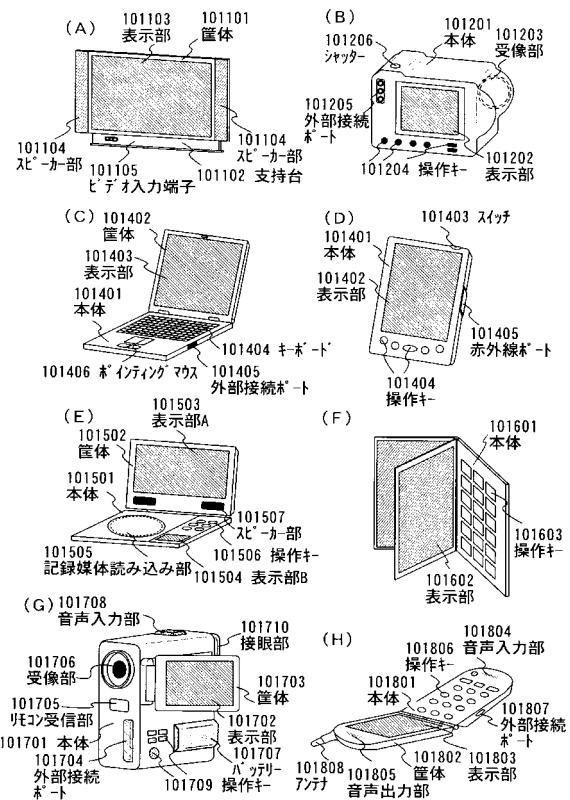

【0156】

図1は、本発明の第2の実施形態に係る液晶表示パネルの一構成例を説明する為の断面図である。

【0157】

図1は画素の断面を詳しく説明するため一画素の一部分を示している。

【0158】

基板100上には、基板100から不純物が拡散することを防止するために、下地絶縁膜(第1の絶縁膜101)が形成されている。基板100としてはガラス基板、石英基板、プラスチック基板、セラミックス基板等の絶縁性基板、金属基板、半導体基板等を用いることができる。第1の絶縁膜101はCVD法やスパッタ法により形成することができる。例えばSiH<sub>4</sub>、N<sub>2</sub>O、NH<sub>3</sub>を原料に用いたCVD法により形成した酸化珪素膜、窒化珪素膜、酸化窒化珪素膜等を適用することができる。また、これらの積層を用いても良い。なお、第1の絶縁膜101は基板100から不純物が半導体層に拡散することを防ぐために設けるものであり、基板100にガラス基板や石英基板を用いている場合には第1の絶縁膜101は設けなくてもよい。

【0159】

第1の絶縁膜101上には、トランジスタ111の半導体層(チャネル形成領域102a、不純物領域102b、不純物領域102c及び不純物領域102d)並びに液晶分子の分子配列を制御する画素電極(第1の電極102e)及び共通電極(第2の電極102f)が形成されている。チャネル形成領域102a、不純物領域102b、不純物領域102c、不純物領域102d、第1の電極102e及び第2の電極102fは、非単結晶半導体膜(例えばポリシリコン膜)であり、同一工程により形成される。

【0160】

トランジスタ111がn型のトランジスタの場合には、不純物領域102b、不純物領域102c及び102dには、リンやヒ素などの不純物元素が導入され、トランジスタ111がp型のトランジスタの場合には、不純物領域102b、不純物領域102c及び不純物領域102dには、ボロンなどの不純物元素が導入されている。

【0161】

また、第1の電極102e及び第2の電極102fにも不純物領域102b、不純物領域102c及び不純物領域102dに導入されている不純物元素が導入されていてもよい。第1の電極102e及び第2の電極102fは不純物が導入されることにより抵抗が下がり、電極として好ましい。

【0162】

第1の電極102e及び第2の電極102fは、膜厚が例えば45nm以上60nm以下であり、光の透過率は十分高い。ただし、光の透過率を更に下げる場合には、第1の電極102e及び第2の電極102fの膜厚を40nm以下にすることが望ましい。

【0163】

トランジスタ111の半導体層(チャネル形成領域102a、不純物領域102b、不純物領域102c及び不純物領域102d)並びに液晶分子の分子配列を制御する第1の電極102e及び第2の電極102fを同一工程により形成することにより、工程数を削減できるため、製造コストを低減することができる。また、不純物領域102b、不純物領域102c及び不純物領域102d並びに第1の電極102e及び第2の電極102fには、同じ種類の不純物元素が導入されることが望ましい。同じ種類の不純物元素を導入する場合、不純物領域102b、不純物領域102c及び不純物領域102d並びに第1の電極102e及び第2の電極102fを互いに近接して配置しても、問題なく不純物元素を導入することができるために、より密なレイアウトを構成することができる。p型又はn型どちらか一方のみの不純物元素を導入することにより、異なる種類の不純物元素を導入する場合と比較して低コストで製造できるため望ましい。

【0164】

10

20

30

40

50

トランジスタ 111 の半導体層、第 1 の電極 102e 及び第 2 の電極 102f 上には、ゲート絶縁膜（第 2 の絶縁膜 103）が形成されている。図 1 ではトランジスタ 111 の半導体層、第 1 の電極 102e 及び第 2 の電極 102f を覆うように第 2 の絶縁膜 103 が形成されているが、これに限定されず、トランジスタ 111 の半導体層上に第 2 の絶縁膜 103 が形成されればよい。第 2 の絶縁膜 103 としては CVD 法やスパッタ法により形成される酸化珪素膜、窒化珪素膜、酸化窒化珪素膜等を用いることができる。

#### 【0165】

トランジスタ 111 のチャネル形成領域 102a 上に第 2 の絶縁膜 103 を介して 2 本のゲート電極 104 が形成されている。ゲート電極 104 としてはアルミニウム（A1）膜、銅（Cu）膜、アルミニウム又は銅を主成分とする薄膜、クロム（Cr）膜、タンタル（Ta）膜、窒化タンタル膜、チタン（Ti）膜、タンゲステン（W）膜、モリブデン（Mo）膜等を用いることができる。

#### 【0166】

第 2 の絶縁膜 103 及びゲート電極 104 上には、層間絶縁膜（第 3 の絶縁膜 105）が形成されている。第 3 の絶縁膜 105 としては、積層構造が好ましい。例えば、保護膜及び平坦化膜がこの順に形成されているとよい。保護膜には、無機絶縁膜が適している。無機絶縁膜としては、窒化珪素膜、酸化珪素膜、酸化窒化珪素膜の単膜又はこれらを積層した膜を用いることができる。平坦化膜には、樹脂膜が適している。樹脂膜としては、ポリイミド、ポリアミド、アクリル、ポリイミドアミド、エポキシなどを用いることができる。

#### 【0167】

第 3 の絶縁膜 105 上には信号線（配線 106）が形成されている。配線 106 は第 3 の絶縁膜 105 に形成された孔（コンタクトホール）を介して不純物領域 102c と接続されている。配線 106 としては、チタン（Ti）膜、アルミニウム（A1）膜、銅（Cu）膜又は Ti を含むアルミニウム膜などを用いることができる。好ましくは、低抵抗な銅を用いるとよい。

#### 【0168】

配線 106 及び第 3 の絶縁膜 105 上には第 1 の配向膜 107 が形成されている。そして、第 1 の配向膜 107 上には液晶層 108、第 2 の配向膜 109 及び基板 110 が配置されている。つまり、第 1 の配向膜 107 と第 2 の配向膜 109 とで液晶層 108 が挟まれた構造となっている。つまり、第 2 の配向膜 109 は基板 110 に形成され、基板 110 は第 2 の配向膜 109 が形成された面を内側とし、基板 100 は第 1 の配向膜 107 が形成された面を内側とし、基板 100 と基板 110 が張り合わされている。そして、第 1 の配向膜 107 と第 2 の配向膜 109 との間に液晶層 108 が注入されている。

#### 【0169】

##### （実施の形態 3）

本発明の第 3 の実施形態に係る液晶表示パネルの構成について説明する。

#### 【0170】

本発明の第 3 の実施形態に係る液晶表示パネルは、第 1 の基板上に液晶素子の第 2 の電極を有し、液晶素子の第 2 の電極を覆うように第 1 の絶縁膜を有し、第 1 の絶縁膜上にトランジスタの半導体層と、液晶素子の第 1 の電極と、を有し、トランジスタの半導体層と、液晶素子の第 1 の電極と、を覆うように第 2 の絶縁膜を有し、トランジスタの半導体層上に第 2 の絶縁膜を介してゲート電極を有し、ゲート電極及び第 2 の絶縁膜を覆うように第 3 の絶縁膜を有し、第 3 の絶縁膜及び第 2 の絶縁膜には孔（コンタクトホール）が設けられ、第 3 の絶縁膜上に形成された配線が孔を介してトランジスタの半導体層と接続されている。そして第 1 の基板は、トランジスタを有する面を内側にして、第 2 の基板と張り合わされている。第 1 の基板と、第 2 の基板との間には液晶層を有している。

#### 【0171】

なお、トランジスタの半導体層と、液晶素子の第 1 の電極と、は同層の膜である。

#### 【0172】

10

20

30

40

50

また、液晶素子の第1の電極はスリットを有する電極又は櫛形電極であり、液晶素子の第2の電極はプレート状電極である。

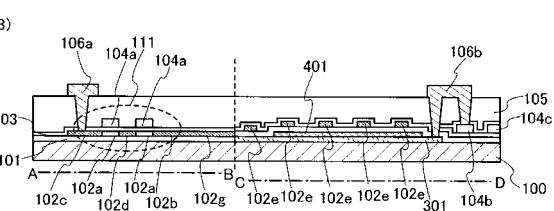

【0173】

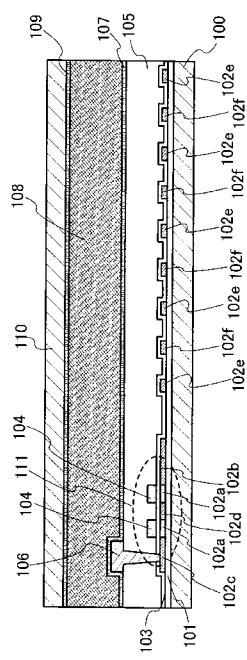

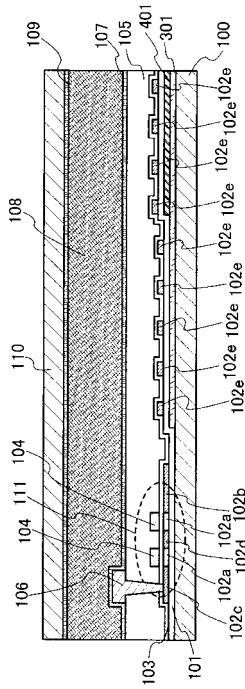

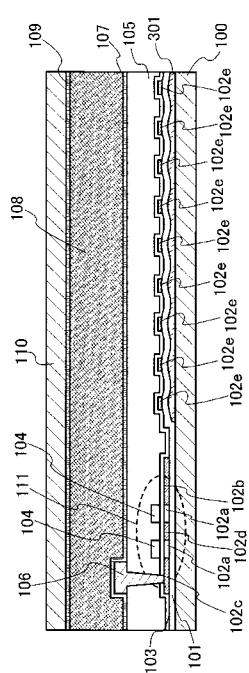

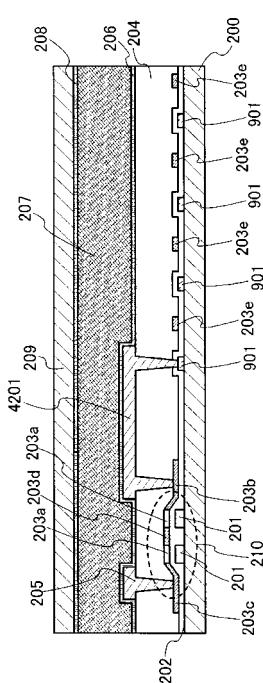

図3は、本発明の第3の実施形態に係る液晶表示パネルの一構成例を説明する為の断面図である。

【0174】

図3は画素構成を詳しく説明するため一画素の一部分を示している。なお、実施形態2で図1を用いて説明した液晶表示パネルの一構成と異なるところは、第2の電極102fの代わりに第2の電極301が設けられているところである。

【0175】

図1の共通電極(第2の電極102f)には画素電極(第1の電極102e)と同一工程により形成した膜を用いている。ところが、図3の共通電極(第2の電極301)は基板100上であって、第1の絶縁膜101下に形成されている。

【0176】

第2の電極301としては、反射性を有する導電膜でもいいし、透光性を有する導電膜でもよい。反射性を有する導電膜としては、アルミニウム(A1)膜、銅(Cu)膜、アルミニウム又は銅を主成分とする薄膜、クロム(Cr)膜、タンタル(Ta)膜、窒化タンタル膜、チタン(Ti)膜、タングステン(W)膜、モリブデン(Mo)膜等の金属膜が挙げられる。透光性を有する導電膜としては、インジウム錫酸化物(ITO)膜、インジウム亜鉛酸化物(IZO)膜、酸化珪素を含むインジウム錫酸化物(ITSO)膜、酸化亜鉛(ZnO)膜、酸化スズカドミウム(CTO)膜などの透明導電膜が挙げられる。本発明の第3の実施形態に係る液晶表示パネルは、第2の電極301が反射性を有する導電膜の場合には、反射型液晶表示パネルであり、第2の電極301が透光性を有する導電膜の場合には、透過型液晶表示パネルである。

【0177】

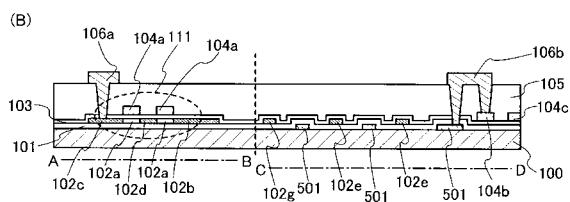

(実施の形態4)

本発明の第4の実施形態に係る液晶表示パネルの構成について説明する。

【0178】

本発明の第4の実施形態に係る液晶表示パネルは、第1の基板上に液晶素子の第2の電極を有し、液晶素子の第2の電極上に液晶素子の第2の電極よりも面積の小さい反射性の導電膜を有し、液晶素子の第2の電極及び導電膜を覆うように第1の絶縁膜を有し、第1の絶縁膜上にトランジスタの半導体層と、液晶素子の第1の電極と、を有し、トランジスタの半導体層と、液晶素子の第1の電極と、を覆うように第2の絶縁膜を有し、トランジスタの半導体層上に第2の絶縁膜を介してゲート電極を有し、ゲート電極及び第2の絶縁膜を覆うように第3の絶縁膜を有し、第3の絶縁膜及び第2の絶縁膜には孔(コンタクトホール)が設けられ、第3の絶縁膜上に形成された配線が孔を介してトランジスタの半導体層と接続されている。そして第1の基板は、トランジスタを有する面を内側にして、第2の基板と張り合わされている。第1の基板と、第2の基板との間には液晶層を有している。

【0179】

なお、トランジスタの半導体層と、液晶素子の第1の電極と、は同層の膜である。

【0180】

また、液晶素子の第1の電極はスリットを有する電極又は櫛形電極であり、液晶素子の第2の電極はプレート状電極である。

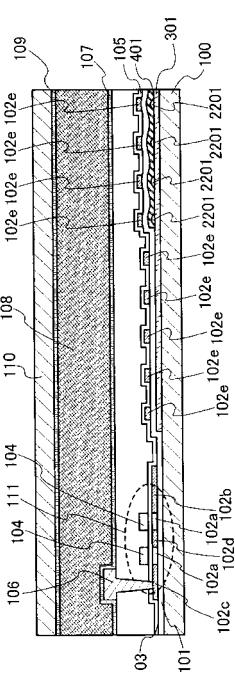

【0181】

図4は、本発明の第4の実施形態に係る液晶表示パネルの一構成例を説明する為の断面図である。

【0182】

図4は画素構成を詳しく説明するため一画素の一部分を示している。なお、実施形態3で図3を用いて説明した液晶表示パネルの一構成と異なるところは、第2の電極301上に

10

20

30

40

50

導電膜 401 が接して設けられているところである。本発明の第 4 の実施の形態に係る液晶表示パネルでは第 2 の電極 301 及び導電膜 401 が共通電極として機能する。

#### 【 0183 】

本発明の第 4 の実施形態に係る液晶表示パネルでは、第 2 の電極 301 は透光性を有する導電膜が好ましい。透光性を有する導電膜としては、インジウム錫酸化物 (ITO) 膜、インジウム亜鉛酸化物 (IZO) 膜、酸化珪素を含むインジウム錫酸化物 (ITSO) 膜、酸化亜鉛 (ZnO) 膜、酸化スズカドミウム (CTO) 膜などの透明導電膜が挙げられる。導電膜 401 は反射性を有する導電膜が好ましい。反射性を有する導電膜としては、アルミニウム (Al) 膜、銅 (Cu) 膜、アルミニウム又は銅を主成分とする薄膜、クロム (Cr) 膜、タンタル (Ta) 膜、窒化タンタル膜、チタン (Ti) 膜、タンゲステン (W) 膜、モリブデン (Mo) 膜等の金属膜が挙げられる。

#### 【 0184 】

本発明の第 4 の実施形態に係る液晶表示パネルは、半透過型液晶表示パネルに好適である。

#### 【 0185 】

##### ( 実施の形態 5 )

本発明の第 5 の実施形態に係る液晶表示パネルの構成について説明する。

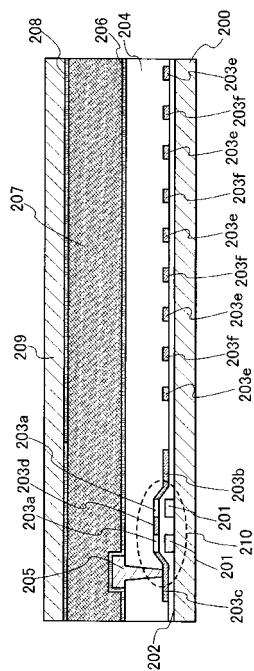

#### 【 0186 】

本発明の第 5 の実施形態に係る液晶表示パネルは、第 1 の基板上に液晶素子の第 2 の電極を有し、液晶素子の第 2 の電極を覆うように第 1 の絶縁膜を有し、第 1 の絶縁膜上にトランジスタの半導体層と、液晶素子の第 1 の電極と、を有し、トランジスタの半導体層と、液晶素子の第 1 の電極と、を覆うように第 2 の絶縁膜を有し、トランジスタの半導体層上に第 2 の絶縁膜を介してゲート電極を有し、ゲート電極及び第 2 の絶縁膜を覆うように第 3 の絶縁膜を有し、第 3 の絶縁膜及び第 2 の絶縁膜には孔 (コンタクトホール) が設けられ、第 3 の絶縁膜上に形成された配線が孔を介してトランジスタの半導体層と接続されている。そして第 1 の基板は、トランジスタを有する面を内側にして、第 2 の基板と張り合わされている。第 1 の基板と、第 2 の基板との間には液晶層を有している。

#### 【 0187 】

なお、トランジスタの半導体層と、液晶素子の第 1 の電極と、は同層の膜である。

#### 【 0188 】

また、液晶素子の第 1 の電極及び液晶素子の第 2 の電極は、スリットを有する電極又は櫛形電極であり、プランチ部分が互い違いに配置されている。

#### 【 0189 】

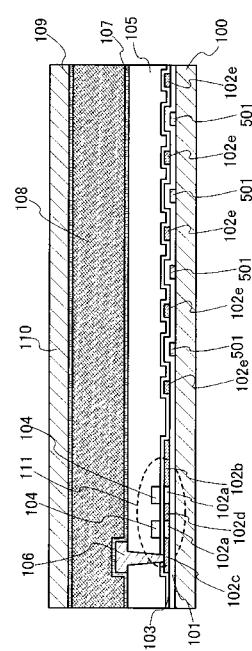

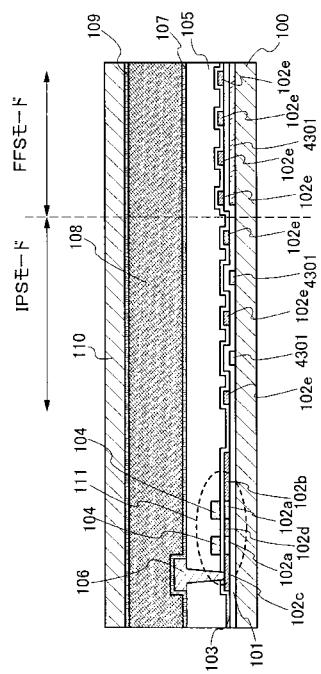

図 5 は、本発明の第 5 の実施形態に係る液晶表示パネルの一構成例を説明する為の断面図である。

#### 【 0190 】

図 5 は画素構成を詳しく説明するため一画素の一部分を示している。なお、実施形態 2 で図 1 を用いて説明した液晶表示パネルの一構成と異なるところは、第 2 の電極 102f の代わりに第 2 の電極 501 が設けられているところである。

#### 【 0191 】

図 1 の共通電極 (第 2 の電極 102f) には画素電極 (第 1 の電極 102e) と同一工程により形成した膜を用いている。ところが、図 5 の共通電極 (第 2 の電極 501) は基板 100 上であって、第 1 の絶縁膜 101 下に形成されている。

#### 【 0192 】

第 2 の電極 501 としては、反射性を有する導電膜でもいいし、透光性を有する導電膜でもよい。反射性を有する導電膜としては、アルミニウム (Al) 膜、銅 (Cu) 膜、アルミニウム又は銅を主成分とする薄膜、クロム (Cr) 膜、タンタル (Ta) 膜、窒化タンタル膜、チタン (Ti) 膜、タンゲステン (W) 膜、モリブデン (Mo) 膜等の金属膜が挙げられる。透光性を有する導電膜としては、インジウム錫酸化物 (ITO) 膜、インジウム亜鉛酸化物 (IZO) 膜、酸化珪素を含むインジウム錫酸化物 (ITSO) 膜、酸化

10

20

30

40

50

亜鉛 (ZnO) 膜、酸化スズカドミウム (CTO) 膜などの透明導電膜が挙げられる。本発明の第3の実施形態に係る液晶表示パネルは、反射型液晶表示パネルでも透過型液晶表示パネルでもよく、第2の電極301が反射性を有する導電膜の場合には、反射型液晶表示パネルが好適であり、第2の電極301が透光性を有する導電膜の場合には、透過型液晶表示パネルが好適である。

### 【0193】

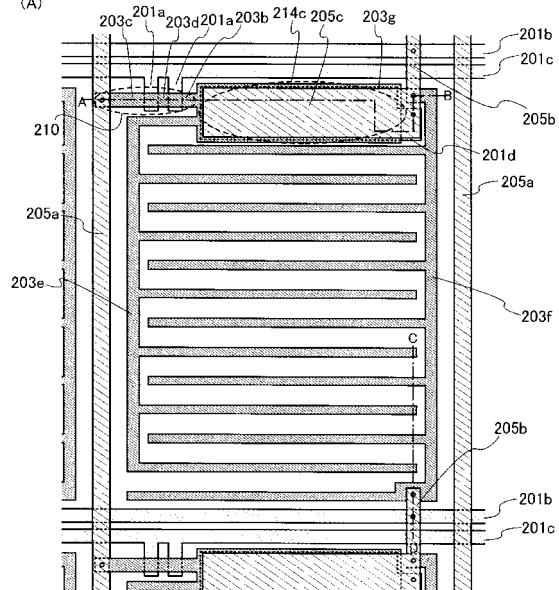

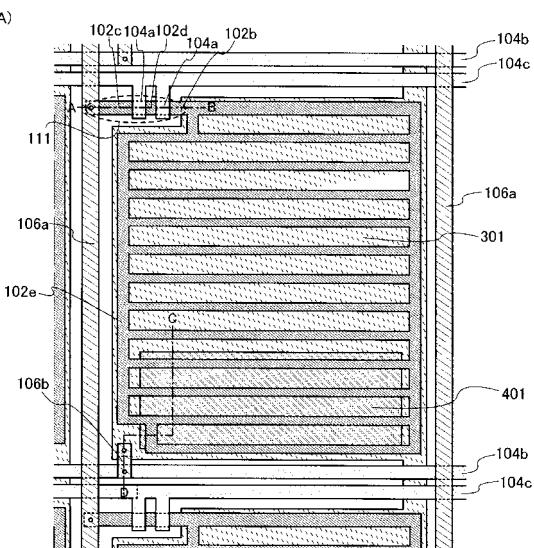

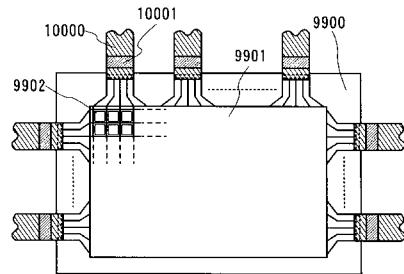

#### (実施の形態6)

実施の形態2乃至5では、基板上に形成されたトランジスタにおいて、トランジスタの半導体層上にゲート電極を有する、いわゆるトップゲート構造のトランジスタを有する液晶表示パネルの構成について示した。本実施の形態においては、基板上に形成されたトランジスタにおいて、トランジスタの半導体層下にゲート電極を有するいわゆるボトムゲート構造のトランジスタを有する液晶表示パネルの構成について示す。

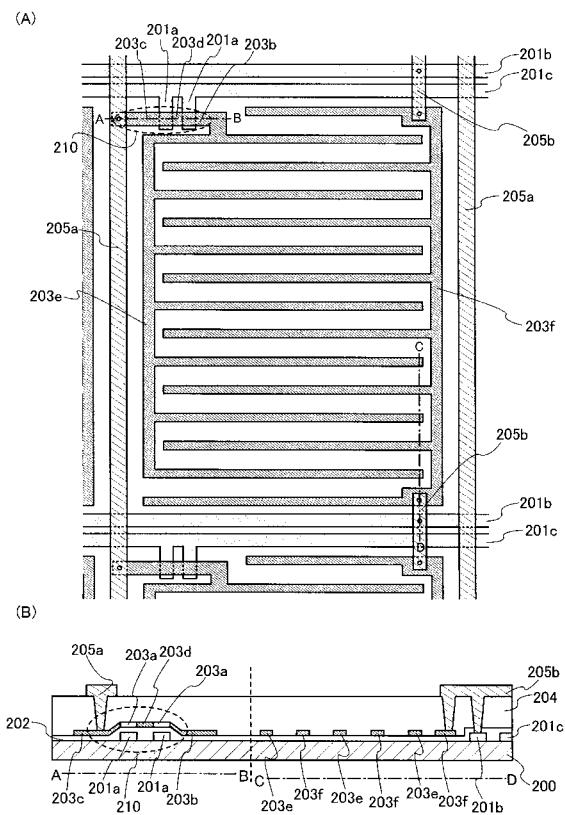

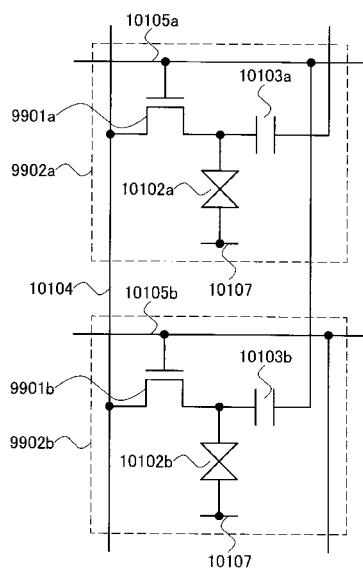

### 【0194】

本発明の第6の実施形態に係る液晶表示パネルは、第1の基板上にゲート電極を有し、ゲート電極を覆うように第1の絶縁膜を有し、ゲート電極上に第1の絶縁膜を介してトランジスタの半導体層と、基板上に第1の絶縁膜を介して液晶素子の第1の電極及び液晶素子の第2の電極と、を有し、トランジスタの半導体層と、液晶素子の第1の電極及び液晶素子の第2の電極と、を覆うように第2の絶縁膜を有し、第2の絶縁膜には孔（コンタクトホール）が設けられ、第2の絶縁膜上に形成された配線が孔を介してトランジスタの半導体層と接続されている。そして第1の基板は、トランジスタを有する面を内側にして、第2の基板と張り合わされている。第1の基板と、第2の基板との間には液晶層を有している。

### 【0195】

なお、トランジスタの半導体層と、液晶素子の第1の電極及び液晶素子の第2の電極とは同層の膜である。

### 【0196】

また、液晶素子の第1の電極及び液晶素子の第2の電極は、スリットを有する電極又は櫛形電極であり、ブランチ部分が互い違いに配置されている。

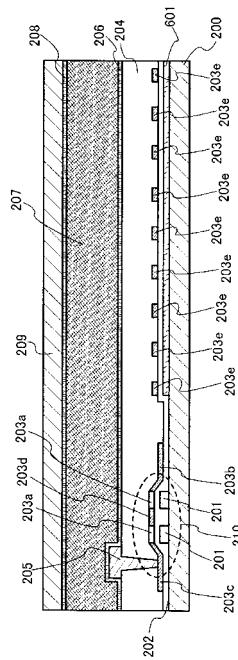

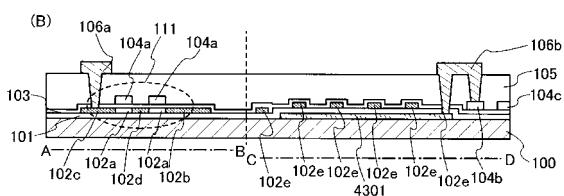

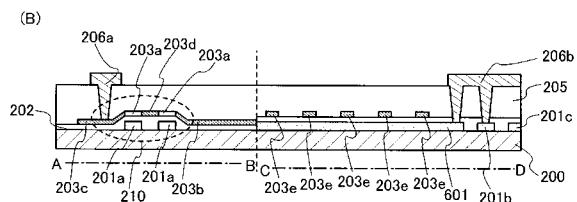

### 【0197】

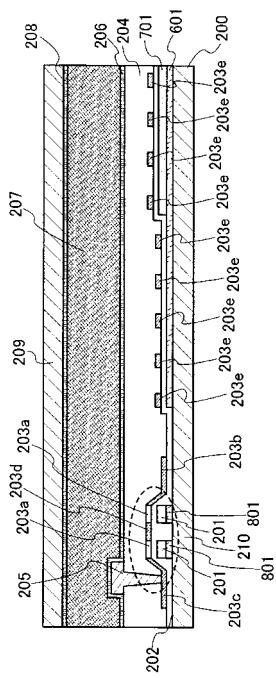

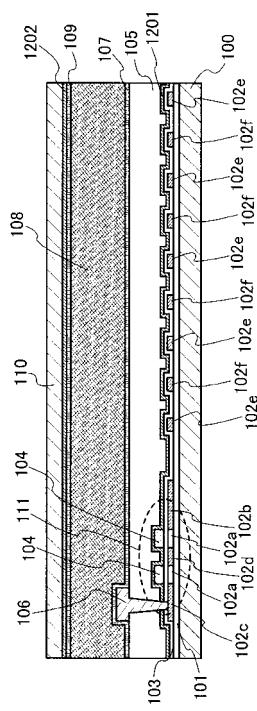

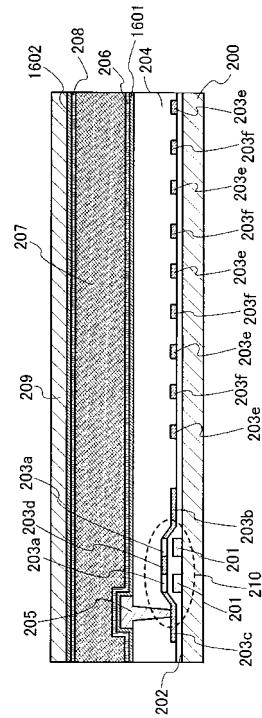

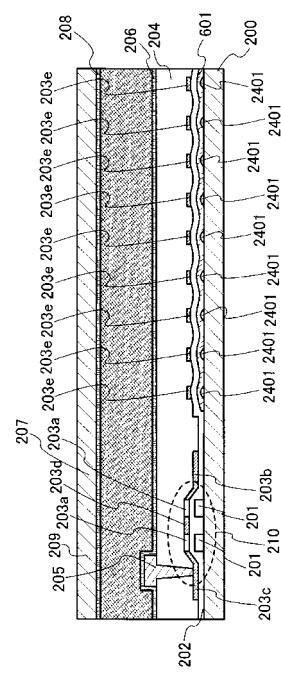

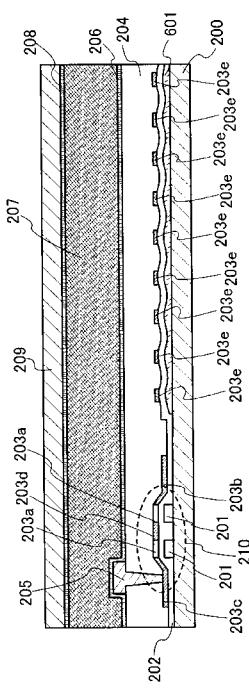

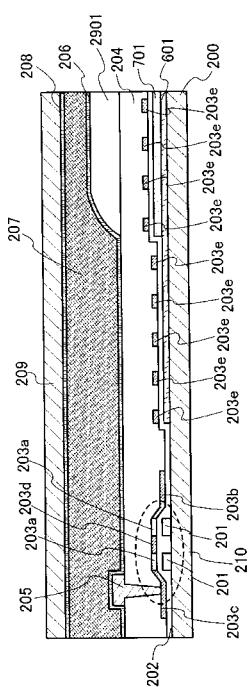

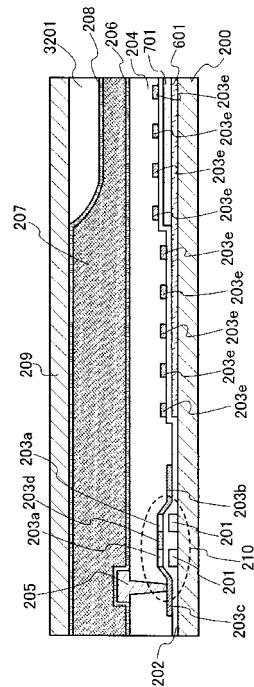

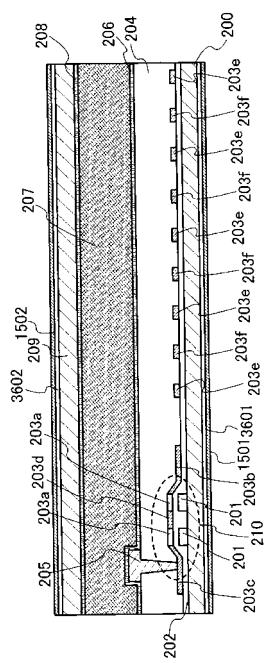

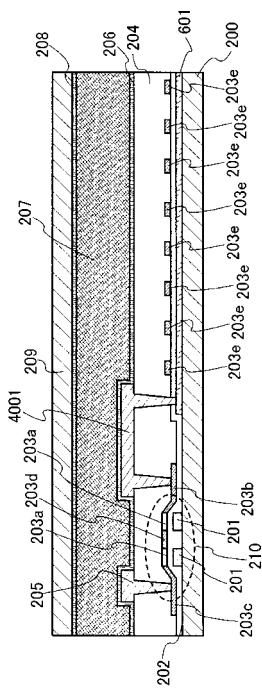

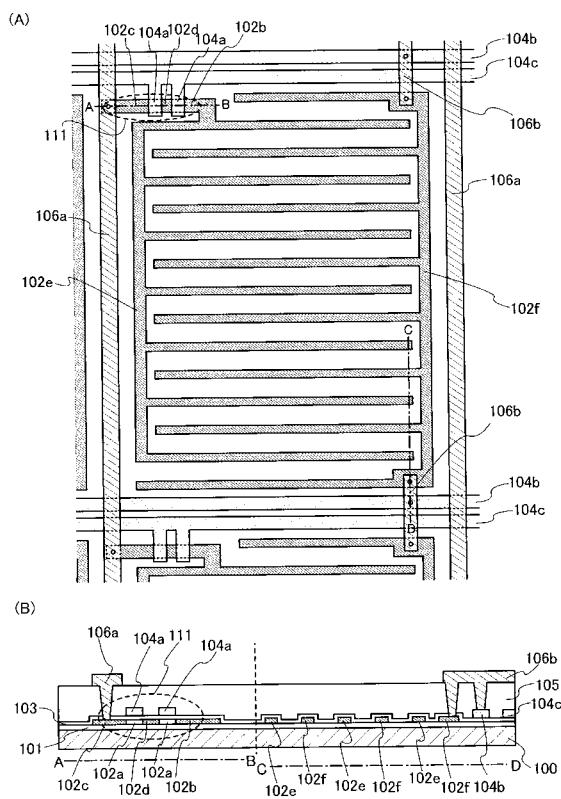

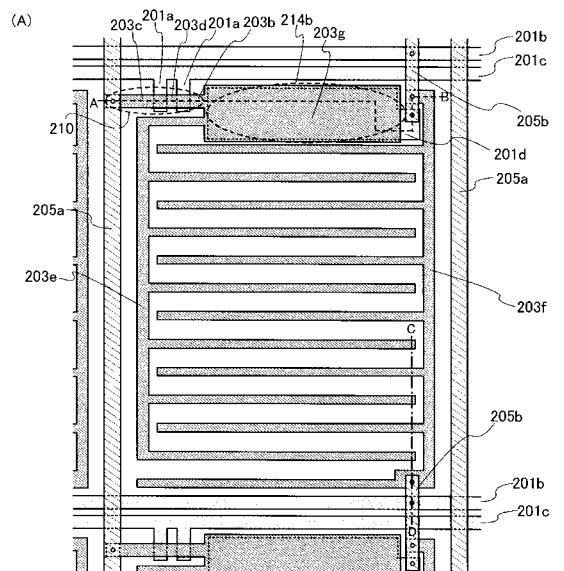

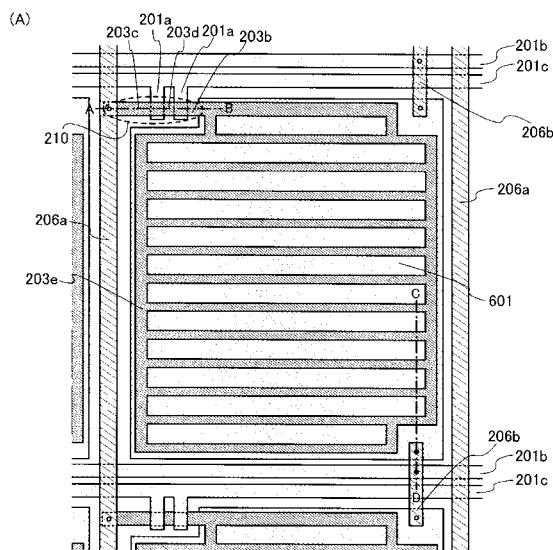

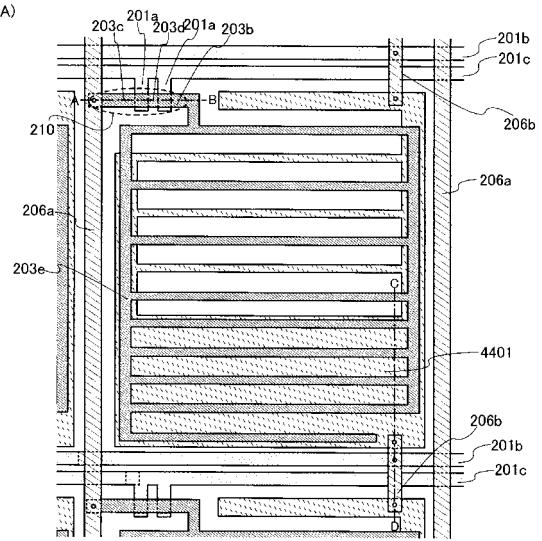

図2は、本発明の第3の実施形態に係る液晶表示パネルの一構成例を説明する為の断面図である。

### 【0198】

図2は画素構成を詳しく説明するため一画素の一部分を示している。

### 【0199】

基板200上には、2本のゲート電極201が形成されている。基板200としてはガラス基板、石英基板、プラスチック基板、セラミックス基板等の絶縁性基板、金属基板、半導体基板等を用いることができる。ゲート電極201としてはアルミニウム (Al) 膜、銅 (Cu) 膜、アルミニウム又は銅を主成分とする薄膜、クロム (Cr) 膜、タンタル (Ta) 膜、窒化タンタル膜、チタン (Ti) 膜、タンゲステン (W) 膜、モリブデン (Mo) 膜等を用いることができる。

### 【0200】

ゲート電極201を覆うようにゲート絶縁膜（第1の絶縁膜202）が形成されている。第1の絶縁膜202としてはCVD法やスパッタ法により形成される酸化珪素膜、窒化珪素膜、酸化窒化珪素膜等を用いることができる。

### 【0201】

第1の絶縁膜202上には、トランジスタ210の半導体層（チャネル形成領域203a、不純物領域203b、不純物領域203c及び不純物領域203d）並びに液晶分子の分子配列を制御する第1の電極203e及び第2の電極203fが形成されている。チャネル形成領域203a、不純物領域203b、不純物領域203c、不純物領域203d、第1の電極203e及び第2の電極203fは、非単結晶半導体膜（例えばポリシリコ

10

20

30

40

50

ン膜)であり、同一工程により形成される。

【0202】

トランジスタ210がn型のトランジスタの場合には、不純物領域203b、不純物領域203c及び不純物領域203dには、リンやヒ素などの不純物元素が導入され、トランジスタ210がp型のトランジスタの場合には、不純物領域203b、不純物領域203c及び不純物領域203dには、ボロンなどの不純物元素が導入されている。

【0203】

また、第1の電極203e及び第2の電極203fにも不純物領域203b、不純物領域203c及び不純物領域203dに導入されている不純物元素が導入されていてもよい。第1の電極203e及び第2の電極203fは不純物が導入されることにより抵抗が下がり、電極として好ましい。

【0204】

第1の電極203e及び第2の電極203fは、膜厚が例えば45nm以上60nm以下であり、光の透過率は十分高い。ただし、光の透過率を更に下げる場合には、第1の電極203e及び第2の電極203fの膜厚を40nm以下にすることが望ましい。

【0205】

トランジスタ210の半導体層(チャネル形成領域203a、不純物領域203b、不純物領域203c及び不純物領域203d)並びに液晶分子の分子配列を制御する第1の電極203e及び第2の電極203fを同一工程により形成することにより、工程数を削減できるため、製造コストを低減することができる。また、不純物領域203b、不純物領域203c及び不純物領域203d並びに第1の電極203e及び第2の電極203fには、同じ種類の不純物元素が導入されることが望ましい。同じ種類の不純物元素を導入する場合、不純物領域203b、不純物領域203c及び不純物領域203d並びに第1の電極203e及び第2の電極203fを互いに近接して配置しても、問題なく不純物元素を導入することができるので、より密なレイアウトを構成することができる。p型又はn型どちらか一方のみの不純物元素を導入することにより、異なる種類の不純物元素を導入する場合と比較して低コストで製造できるため望ましい。

【0206】

第1の絶縁膜202及びトランジスタ210の半導体層(チャネル形成領域203a、不純物領域203b、不純物領域203c及び不純物領域203d)並びに液晶分子の分子配列を制御する第1の電極203e及び第2の電極203f上には、層間絶縁膜(第2の絶縁膜204)が形成されている。第2の絶縁膜204としては、積層構造が好ましい。例えば、保護膜及び平坦化膜がこの順に形成されているとよい。保護膜には、無機絶縁膜が適している。無機絶縁膜としては、窒化珪素膜、酸化珪素膜、酸化窒化珪素膜の単膜又はこれらを積層した膜を用いることができる。平坦化膜には、樹脂膜が適している。樹脂膜としては、ポリイミド、ポリアミド、アクリル、ポリイミドアミド、エポキシなどを用いることができる。

【0207】

第2の絶縁膜204上には信号線(配線205)が形成されている。配線205は第2の絶縁膜204に形成された孔(コンタクトホール)を介して不純物領域203cと接続されている。配線205としては、チタン(Ti)膜、アルミニウム(A1)膜、銅(Cu)膜又はTiを含むアルミニウム膜などを用いることができる。好ましくは、低抵抗な銅を用いるとよい。

【0208】

配線205及び第2の絶縁膜204上には第1の配向膜206が形成されている。そして、第1の配向膜206上には液晶層207、第2の配向膜208及び基板209が配置されている。つまり、第1の配向膜206と第2の配向膜208とで液晶層207が挟まれた構造となっている。つまり、第2の配向膜208は基板209に形成され、基板209は第2の配向膜208が形成された面を内側とし、基板200は第1の配向膜206が形成された面を内側とし、基板200と基板209が張り合わされている。そして、第1

10

20

30

40

50

の配向膜 206 と第 2 の配向膜 208 との間に液晶層 207 が注入されている。

【0209】

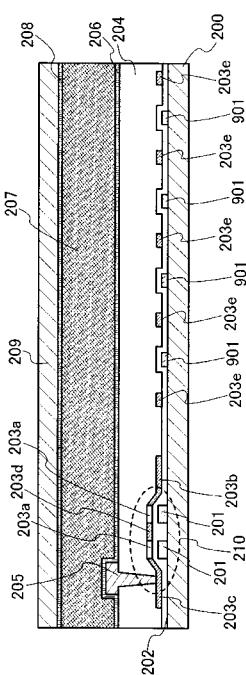

(実施の形態 7)

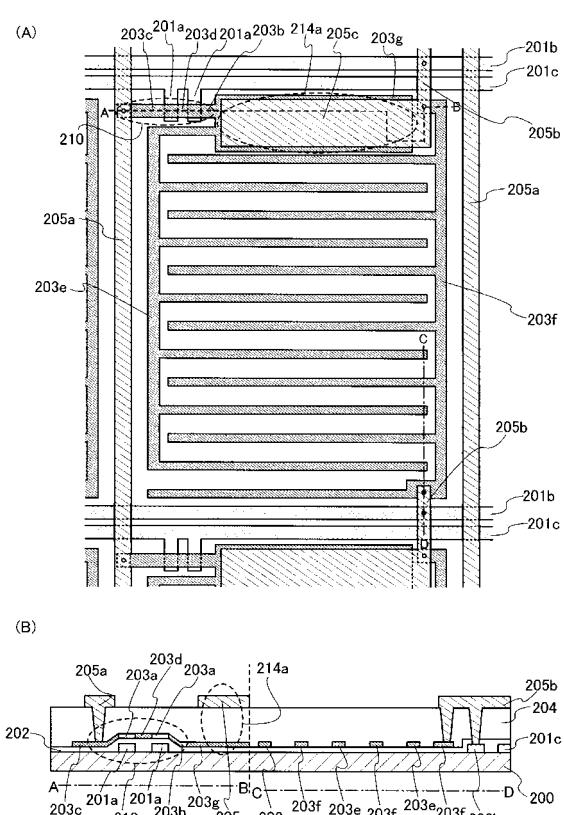

本発明の第 7 の実施形態に係る液晶表示パネルの構成について説明する。

【0210】

本発明の第 7 の実施形態に係る液晶表示パネルは、第 1 の基板上にゲート電極及び液晶素子の第 2 の電極を有し、ゲート電極及び液晶素子の第 2 の電極を覆うように第 1 の絶縁膜を有し、ゲート電極上に第 1 の絶縁膜を介してトランジスタの半導体層と、液晶素子の第 2 の電極上に第 1 の絶縁膜を介して液晶素子の第 1 の電極と、を有し、トランジスタの半導体層と、液晶素子の第 1 の電極と、を覆うように第 2 の絶縁膜を有し、第 2 の絶縁膜には孔（コンタクトホール）が設けられ、第 2 の絶縁膜上に形成された配線が孔を介してトランジスタの半導体層と接続されている。そして第 1 の基板は、トランジスタを有する面を内側にして、第 2 の基板と張り合わされている。第 1 の基板と、第 2 の基板との間には液晶層を有している。

10

【0211】

なお、トランジスタの半導体層と、液晶素子の第 1 の電極と、は同層の膜である。

【0212】

また、液晶素子の第 1 の電極はスリットを有する電極又は櫛形電極であり、液晶素子の第 2 の電極はプレート状電極である。

20

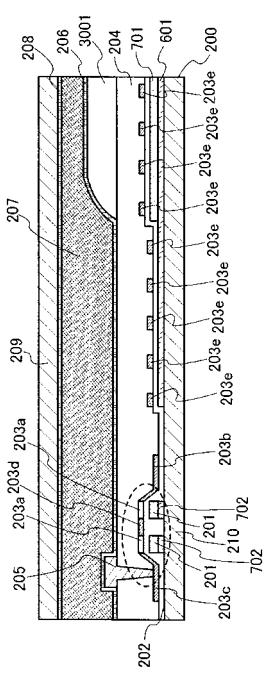

【0213】

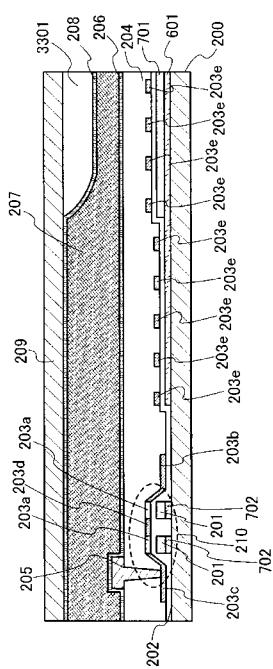

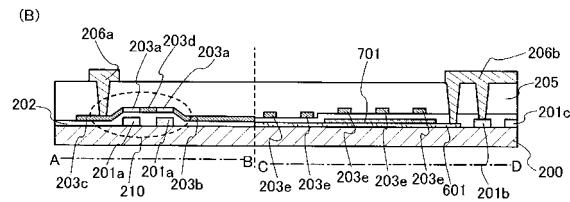

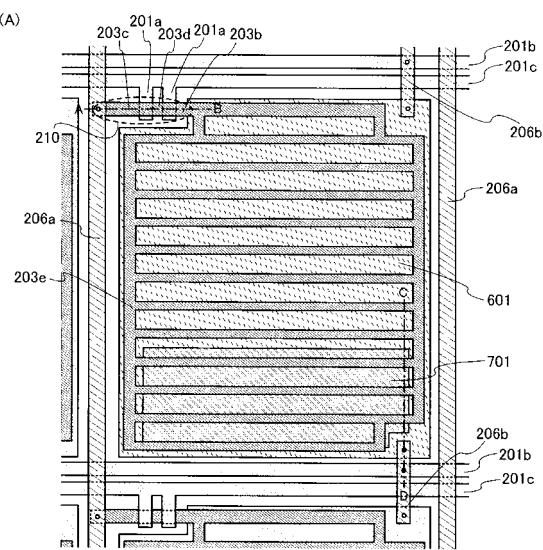

図 6 は、本発明の第 7 の実施形態に係る液晶表示パネルの一構成例を説明する為の断面図である。

【0214】

図 6 は画素構成を詳しく説明するため一画素の一部分を示している。なお、実施形態 6 で図 2 を用いて説明した液晶表示パネルの一構成と異なるところは、第 2 の電極 203f の代わりに第 2 の電極 601 が設けられているところである。

30

【0215】

図 2 の共通電極（第 2 の電極 203f）には画素電極（第 1 の電極 203e）と同一工程により形成した膜を用いている。ところが、図 6 の共通電極（第 2 の電極 601）は基板 200 上であって、第 1 の絶縁膜 202 下に形成されている。

30

【0216】

第 2 の電極 601 としては、反射性を有する導電膜でもいいし、透光性を有する導電膜でもよい。反射性を有する導電膜としては、アルミニウム（Al）膜、銅（Cu）膜、アルミニウム又は銅を主成分とする薄膜、クロム（Cr）膜、タンタル（Ta）膜、窒化タンタル膜、チタン（Ti）膜、タンゲステン（W）膜、モリブデン（Mo）膜等の金属膜が挙げられる。透光性を有する導電膜としては、インジウム錫酸化物（ITO）膜、インジウム亜鉛酸化物（IZO）膜、酸化珪素を含むインジウム錫酸化物（ITSO）膜、酸化亜鉛（ZnO）膜、酸化スズカドミウム（CTO）膜などの透明導電膜が挙げられる。本発明の第 7 の実施形態に係る液晶表示パネルは、第 2 の電極 601 が反射性を有する導電膜の場合には、反射型液晶表示パネルであり、第 2 の電極 601 が透光性を有する導電膜の場合には、透過型液晶表示パネルである。

40

【0217】

(実施の形態 8)

本発明の第 8 の実施形態に係る液晶表示パネルの構成について説明する。

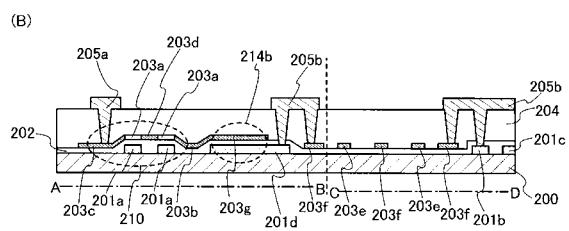

【0218】

本発明の第 8 の実施形態に係る液晶表示パネルは、第 1 の基板上にゲート電極及び液晶素子の第 2 の電極を有し、液晶素子の第 2 の電極上に液晶素子の第 2 の電極よりも面積の小さい反射性の導電膜を有し、ゲート電極及び液晶素子の第 2 の電極及び導電膜を覆うように第 1 の絶縁膜を有し、ゲート電極上に第 1 の絶縁膜を介してトランジスタの半導体層と、液晶素子の第 2 の電極上に第 1 の絶縁膜を介して液晶素子の第 1 の電極と、を有し、ト

50

ランジスタの半導体層と、液晶素子の第1の電極と、を覆うように第2の絶縁膜を有し、第2の絶縁膜には孔（コンタクトホール）が設けられ、第2の絶縁膜上に形成された配線が孔を介してトランジスタの半導体層と接続されている。そして第1の基板は、トランジスタを有する面を内側にして、第2の基板と張り合わされている。第1の基板と、第2の基板との間には液晶層を有している。

【0219】

なお、トランジスタの半導体層と、液晶素子の第1の電極と、は同層の膜である。

【0220】

また、液晶素子の第1の電極はスリットを有する電極又は櫛形電極であり、液晶素子の第2の電極はプレート状電極である。

10

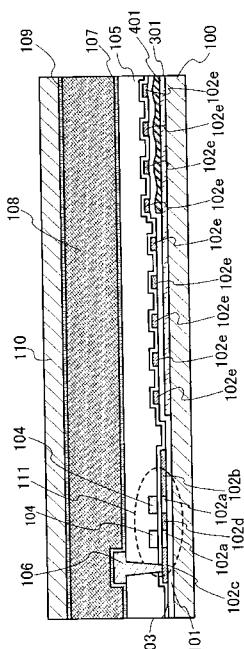

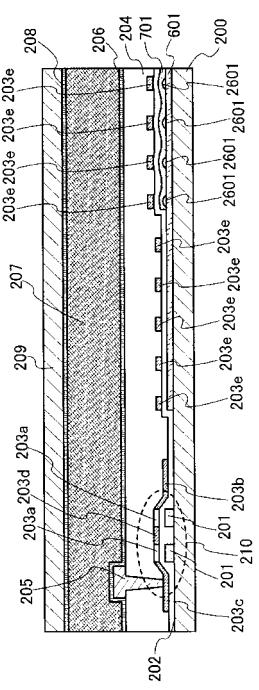

【0221】

図7は、本発明の第8の実施形態に係る液晶表示パネルの一構成例を説明する為の断面図である。

【0222】

図7は画素構成を詳しく説明するため一画素の一部分を示している。なお、実施形態7で図6を用いて説明した液晶表示パネルの一構成と異なるところは、第2の電極601上に導電膜701が接して設けられているところである。本発明の第8の実施の形態に係る液晶表示パネルでは第2の電極601及び導電膜701が共通電極として機能する。

20

【0223】

本発明の第8の実施形態に係る液晶表示パネルでは、第2の電極601は透光性を有する導電膜が好ましい。透光性を有する導電膜としては、インジウム錫酸化物（ITO）膜、インジウム亜鉛酸化物（IZO）膜、酸化珪素を含むインジウム錫酸化物（ITSO）膜、酸化亜鉛（ZnO）膜、酸化スズカドミウム（CTO）膜などの透明導電膜が挙げられる。導電膜701は反射性を有する導電膜が好ましい。反射性を有する導電膜としては、アルミニウム（Al）膜、銅（Cu）膜、アルミニウム又は銅を主成分とする薄膜、クロム（Cr）膜、タンタル（Ta）膜、窒化タンタル膜、チタン（Ti）膜、タングステン（W）膜、モリブデン（Mo）膜等の金属膜が挙げられる。

【0224】

本発明の第8の実施形態に係る液晶表示パネルは、半透過型液晶表示パネルに好適である。

30

【0225】

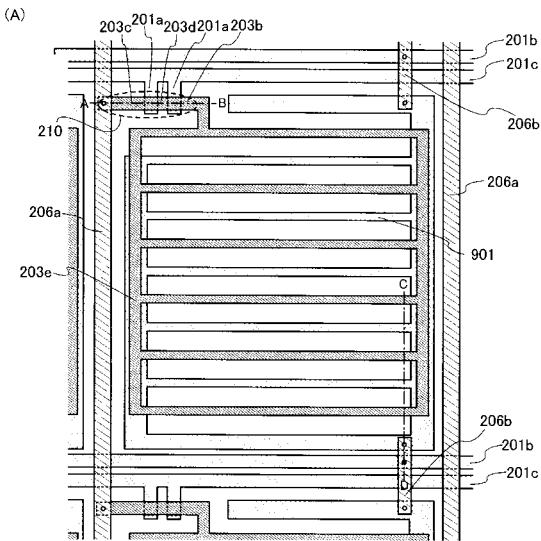

（実施の形態9）

本発明の第9の実施形態に係る液晶表示パネルの構成について説明する。

【0226】

本発明の第9の実施形態に係る液晶表示パネルでは、第2の電極601と導電膜701とを1枚のマスクにより形成した場合の構成である。つまり、ハーフトーンやグレートーンなどと呼ばれるレジストの厚さを領域によって変えたマスクを用いて第2の電極601と導電膜701とを形成する。その結果、製造工程を簡略化でき、マスク数（レチクル数）を減らすことができる。

40

【0227】

本発明の第9の実施形態に係る液晶表示パネルは、第1の基板上に第1の導電膜及び液晶素子の第2の電極を有し、第1の導電膜上にゲート電極を有し、液晶素子の第2の電極上に液晶素子の第2の電極よりも面積の小さい反射性の第2の導電膜を有し、ゲート電極及び液晶素子の第2の電極及び第2の導電膜を覆うように第1の絶縁膜を有し、ゲート電極上に第1の絶縁膜を介してトランジスタの半導体層と、液晶素子の第2の電極上に第1の絶縁膜を介して液晶素子の第1の電極と、を有し、トランジスタの半導体層と、液晶素子の第1の電極と、を覆うように第2の絶縁膜を有し、第2の絶縁膜には孔（コンタクトホール）が設けられ、第2の絶縁膜上に形成された配線が孔を介してトランジスタの半導体層と接続されている。そして第1の基板は、トランジスタを有する面を内側にして、第2の基板と張り合わされている。第1の基板と、第2の基板との間には液晶層を有している

50

。

【0228】

なお、トランジスタの半導体層と、液晶素子の第1の電極と、は同層の膜である。

【0229】

また、第1の導電膜と液晶素子の第2の電極と、は同層の膜であり、ゲート電極と第2の導電膜とは同層の膜である。

【0230】

また、液晶素子の第1の電極はスリットを有する電極又は櫛形電極であり、液晶素子の第2の電極はプレート状電極である。

【0231】

図8は、本発明の第9の実施形態に係る液晶表示パネルの一構成例を説明する為の断面図である。

【0232】

図8は画素構成を詳しく説明するため一画素の一部分を示している。なお、実施形態8で図7を用いて説明した液晶表示パネルの一構成と異なるところは、ゲート電極201下に導電膜801が接して設けられているところである。本発明の第9の実施の形態に係る液晶表示パネルでは導電膜801もゲート電極201の一部として機能する。

【0233】

本発明の第9の実施形態に係る液晶表示パネルでは、第2の電極601及び導電膜801を同一工程により形成し、導電膜701及びゲート電極201を同一工程により形成する

20

【0234】

そしてこれらの形成は、まず、第2の電極601及び導電膜801となる第1の導電膜を形成し、その上にゲート電極201及び導電膜701となる第2の導電膜を形成する。そして、第2の導電膜上にレジスト膜を形成し、露光光が遮光される遮光部と、露光光が一部通過する半透部と、を有する露光マスクを用いて、レジスト膜の露光を行う。そして、現像を行い、二つの膜厚を有する第1のレジストパターンと、膜厚がほぼ一様な第2のレジストパターンを形成する。第1の導電膜及び第2の導電膜を、第1のレジストパターン及び第2のレジストパターンを用いてエッチングし、第1の導電膜及び第2の導電膜を第1のレジストパターン及び第2のレジストパターンとほぼ同一のパターンに分離する。第1のレジストパターン及び第2のレジストパターンをアッシング又はエッチングしてそれぞれ第3のレジストパターン及び第4のレジストパターンを形成する。

【0235】

分離後の第2の導電膜を、第3のレジストパターン及び第4のレジストパターンをマスクとして用いてエッチングする。すると、第3のレジストパターンを用いてエッチングした第2の導電膜のパターンは、第1の導電膜のパターンより小さくなる。つまり、第3のレジストパターンを用いてエッチングした第2の導電膜を導電膜701に用いることができる。

【0236】

(実施の形態10)

本発明の第10の実施形態に係る液晶表示パネルの構成について説明する。

40

【0237】

本発明の第10の実施形態に係る液晶表示パネルは、第1の基板上にゲート電極及び液晶素子の第2の電極を有し、ゲート電極及び液晶素子の第2の電極を覆うように第1の絶縁膜を有し、ゲート電極上に第1の絶縁膜を介してトランジスタの半導体層と、液晶素子の第2の電極上に第1の絶縁膜を介して液晶素子の第1の電極と、を有し、トランジスタの半導体層と、液晶素子の第1の電極と、を覆うように第2の絶縁膜を有し、第2の絶縁膜には孔(コンタクトホール)が設けられ、第2の絶縁膜上に形成された配線が孔を介してトランジスタの半導体層と接続されている。そして第1の基板は、トランジスタを有する面を内側にして、第2の基板と張り合わされている。第1の基板と、第2の基板との間に

50

は液晶層を有している。

【0238】

なお、トランジスタの半導体層と、液晶素子の第1の電極と、は同層の膜である。

【0239】

また、液晶素子の第1の電極及び液晶素子の第2の電極はスリットを有する電極又は櫛形電極である。

【0240】

図9は、本発明の第10の実施形態に係る液晶表示パネルの一構成例を説明する為の断面図である。

【0241】

図9は画素構成を詳しく説明するため一画素の一部分を示している。なお、実施形態6で図2を用いて説明した液晶表示パネルの一構成と異なるところは、第2の電極203fの代わりに第2の電極901が設けられているところである。

【0242】

図1の共通電極(第2の電極102f)には画素電極(第1の電極102e)と同一工程により形成した膜を用いている。ところが、図9の共通電極(第2の電極901)は基板100上であって、第1の絶縁膜202下に形成されている。

【0243】

第2の電極901としては、反射性を有する導電膜でもいいし、透光性を有する導電膜でもよい。反射性を有する導電膜としては、アルミニウム(A1)膜、銅(Cu)膜、アルミニウム又は銅を主成分とする薄膜、クロム(Cr)膜、タンタル(Ta)膜、窒化タンタル膜、チタン(Ti)膜、タンゲステン(W)膜、モリブデン(Mo)膜等の金属膜が挙げられる。透光性を有する導電膜としては、インジウム錫酸化物(ITO)膜、インジウム亜鉛酸化物(IZO)膜、酸化珪素を含むインジウム錫酸化物(ITSO)膜、酸化亜鉛(ZnO)膜、酸化スズカドミウム(CTO)膜などの透明導電膜が挙げられる。本発明の第10の実施形態に係る液晶表示パネルは、反射型液晶表示パネルでも透過型液晶表示パネルでもよく、第2の電極901が反射性を有する導電膜の場合には、反射型液晶表示パネルが好適であり、第2の電極901が透光性を有する導電膜の場合には、透過型液晶表示パネルが好適である。

【0244】

(実施の形態11)

本発明の第11の実施形態に係る液晶表示パネルの構成について説明する。

【0245】

本実施の形態では、液晶表示パネルに偏光板若しくは偏光膜を備えた場合の構成について説明する。

【0246】

本発明の第2の実施形態に係る液晶表示パネルに偏光板を適用した本発明の第11の実施形態に係る液晶表示パネルの第1の構成は、第1の基板上に第1の絶縁膜を有し、第1の絶縁膜上にトランジスタの半導体層と、液晶素子の第1の電極及び第2の電極と、を有し、トランジスタの半導体層と、液晶素子の第1の電極及び第2の電極と、を覆うように第2の絶縁膜を有し、トランジスタの半導体層上に第2の絶縁膜を介してゲート電極を有し、ゲート電極及び第2の絶縁膜を覆うように第3の絶縁膜を有し、第3の絶縁膜及び第2の絶縁膜には孔(コンタクトホール)が設けられ、第3の絶縁膜上に形成された配線が孔を介してトランジスタの半導体層と接続されている。そして第1の基板は、トランジスタを有する面を内側にして、第2の基板と張り合わされている。第1の基板と、第2の基板との間には液晶層を有している。

【0247】

なお、トランジスタの半導体層と、液晶素子の第1の電極及び液晶素子の第2の電極と、は同層の膜である。

【0248】

10

20

30

40

50

また、液晶素子の第1の電極及び液晶素子の第2の電極はスリットを有する電極又は櫛形電極である。

【0249】

ここで、本発明の第11の実施形態に係る液晶表示パネルは偏光板又は偏光膜を有している。第1の基板の外側の面（液晶層が設けられていない面）及び第2の基板の外側の面（液晶層が設けられていない面）に偏光板を有していてもいいし、第3の絶縁膜の上若しくは下、又は第2の基板の内側の面（液晶層が設けられている面）に偏光膜を有していてもいい。

【0250】

本発明の第3の実施形態に係る液晶表示パネルに偏光板を適用した本発明の第11の実施形態に係る液晶表示パネルの第2の構成は、第1の基板上に液晶素子の第2の電極を有し、液晶素子の第2の電極を覆うように第1の絶縁膜を有し、第1の絶縁膜上にトランジスタの半導体層と、液晶素子の第1の電極と、を有し、トランジスタの半導体層と、液晶素子の第1の電極と、を覆うように第2の絶縁膜を有し、トランジスタの半導体層上に第2の絶縁膜を介してゲート電極を有し、ゲート電極及び第2の絶縁膜を覆うように第3の絶縁膜を有し、第3の絶縁膜及び第2の絶縁膜には孔（コンタクトホール）が設けられ、第3の絶縁膜上に形成された配線が孔を介してトランジスタの半導体層と接続されている。そして第1の基板は、トランジスタを有する面を内側にして、第2の基板と張り合わされている。第1の基板と、第2の基板との間には液晶層を有している。

10

【0251】

なお、トランジスタの半導体層と、液晶素子の第1の電極と、は同層の膜である。

【0252】

また、液晶素子の第1の電極はスリットを有する電極又は櫛形電極であり、液晶素子の第2の電極はプレート状電極である。

【0253】

ここで、本発明の第11の実施形態に係る液晶表示パネルは偏光板又は偏光膜を有している。第1の基板の外側の面（液晶層が設けられていない面）及び第2の基板の外側の面（液晶層が設けられていない面）に偏光板を有していてもいいし、第3の絶縁膜の上若しくは下、又は第2の基板の内側の面（液晶層が設けられている面）に偏光膜を有していてもいい。

30

【0254】

本発明の第4の実施形態に係る液晶表示パネルに偏光板を適用した本発明の第11の実施形態に係る液晶表示パネルの第3の構成は、第1の基板上に液晶素子の第2の電極を有し、液晶素子の第2の電極上に液晶素子の第2の電極よりも面積の小さい反射性の導電膜を有し、液晶素子の第2の電極及び導電膜を覆うように第1の絶縁膜を有し、第1の絶縁膜上にトランジスタの半導体層と、液晶素子の第1の電極と、を有し、トランジスタの半導体層と、液晶素子の第1の電極と、を覆うように第2の絶縁膜を有し、トランジスタの半導体層上に第2の絶縁膜を介してゲート電極を有し、ゲート電極及び第2の絶縁膜を覆うように第3の絶縁膜を有し、第3の絶縁膜及び第2の絶縁膜には孔（コンタクトホール）が設けられ、第3の絶縁膜上に形成された配線が孔を介してトランジスタの半導体層と接続されている。そして第1の基板は、トランジスタを有する面を内側にして、第2の基板と張り合わされている。第1の基板と、第2の基板との間には液晶層を有している。

40

【0255】

なお、トランジスタの半導体層と、液晶素子の第1の電極と、は同層の膜である。

【0256】

また、液晶素子の第1の電極はスリットを有する電極又は櫛形電極であり、液晶素子の第2の電極はプレート状電極である。

【0257】

ここで、本発明の第11の実施形態に係る液晶表示パネルは偏光板又は偏光膜を有している。第1の基板の外側の面（液晶層が設けられていない面）及び第2の基板の外側の面（

50

液晶層が設けられていない面)に偏光板を有していてもいいし、第3の絶縁膜の上若しくは下、又は第2の基板の内側の面(液晶層が設けられている面)に偏光膜を有していてもいい。

【0258】

本発明の第5の実施形態に係る液晶表示パネルに偏光板を適用した本発明の第11の実施形態に係る液晶表示パネルの第4の構成は、第1の基板上に液晶素子の第2の電極を有し、液晶素子の第2の電極を覆うように第1の絶縁膜を有し、第1の絶縁膜上にトランジスタの半導体層と、液晶素子の第1の電極と、を有し、トランジスタの半導体層と、液晶素子の第1の電極と、を覆うように第2の絶縁膜を有し、トランジスタの半導体層上に第2の絶縁膜を介してゲート電極を有し、ゲート電極及び第2の絶縁膜を覆うように第3の絶縁膜を有し、第3の絶縁膜及び第2の絶縁膜には孔(コンタクトホール)が設けられ、第3の絶縁膜上に形成された配線が孔を介してトランジスタの半導体層と接続されている。そして第1の基板は、トランジスタを有する面を内側にして、第2の基板と張り合わされている。第1の基板と、第2の基板との間には液晶層を有している。

【0259】

なお、トランジスタの半導体層と、液晶素子の第1の電極と、は同層の膜である。

【0260】

また、液晶素子の第1の電極及び液晶素子の第2の電極は、スリットを有する電極又は櫛形電極であり、プランチ部分が互い違いに配置されている。

【0261】

ここで、本発明の第11の実施形態に係る液晶表示パネルは偏光板又は偏光膜を有している。第1の基板の外側の面(液晶層が設けられていない面)及び第2の基板の外側の面(液晶層が設けられていない面)に偏光板を有していてもいいし、第3の絶縁膜の上若しくは下、又は第2の基板の内側の面(液晶層が設けられている面)に偏光膜を有していてもいい。

【0262】

本発明の第6の実施形態に係る液晶表示パネルに偏光板を適用した本発明の第11の実施形態に係る液晶表示パネルの第5の構成は、第1の基板上にゲート電極を有し、ゲート電極を覆うように第1の絶縁膜を有し、ゲート電極上に第1の絶縁膜を介してトランジスタの半導体層と、第1の基板上に第1の絶縁膜を介して液晶素子の第1の電極及び液晶素子の第2の電極と、を有し、トランジスタの半導体層と、液晶素子の第1の電極及び液晶素子の第2の電極と、を覆うように第2の絶縁膜を有し、第2の絶縁膜には孔(コンタクトホール)が設けられ、第2の絶縁膜上に形成された配線が孔を介してトランジスタの半導体層と接続されている。そして第1の基板は、トランジスタを有する面を内側にして、第2の基板と張り合わされている。第1の基板と、第2の基板との間には液晶層を有している。

【0263】

なお、トランジスタの半導体層と、液晶素子の第1の電極及び液晶素子の第2の電極と、は同層の膜である。

【0264】

また、液晶素子の第1の電極及び液晶素子の第2の電極は、スリットを有する電極又は櫛形電極であり、プランチ部分が互い違いに配置されている。

【0265】

ここで、本発明の第11の実施形態に係る液晶表示パネルは偏光板又は偏光膜を有している。第1の基板の外側の面(液晶層が設けられていない面)及び第2の基板の外側の面(液晶層が設けられていない面)に偏光板を有していてもいいし、第2の絶縁膜の上若しくは下、又は第2の基板の内側の面(液晶層が設けられている面)に偏光膜を有していてもいい。

【0266】

本発明の第7の実施形態に係る液晶表示パネルに偏光板を適用した本発明の第11の実施

10

20

30

40

50

形態に係る液晶表示パネルの第6の構成は、第1の基板上にゲート電極及び液晶素子の第2の電極を有し、ゲート電極及び液晶素子の第2の電極を覆うように第1の絶縁膜を有し、ゲート電極上に第1の絶縁膜を介してトランジスタの半導体層と、液晶素子の第2の電極上に第1の絶縁膜を介して液晶素子の第1の電極と、を有し、トランジスタの半導体層と、液晶素子の第1の電極と、を覆うように第2の絶縁膜を有し、第2の絶縁膜には孔（コンタクトホール）が設けられ、第2の絶縁膜上に形成された配線が孔を介してトランジスタの半導体層と接続されている。そして第1の基板は、トランジスタを有する面を内側にして、第2の基板と張り合わされている。第1の基板と、第2の基板との間には液晶層を有している。

【0267】

10

なお、トランジスタの半導体層と、液晶素子の第1の電極と、は同層の膜である。

【0268】

また、液晶素子の第1の電極はスリットを有する電極又は櫛形電極であり、液晶素子の第2の電極はプレート状電極である。

【0269】

ここで、本発明の第11の実施形態に係る液晶表示パネルは偏光板又は偏光膜を有している。第1の基板の外側の面（液晶層が設けられていない面）及び第2の基板の外側の面（液晶層が設けられていない面）に偏光板を有していてもいいし、第2の絶縁膜の上若しくは下、又は第2の基板の内側の面（液晶層が設けられている面）に偏光膜を有していてもいい。

20

【0270】

本発明の第8の実施形態に係る液晶表示パネルに偏光板を適用した本発明の第11の実施形態に係る液晶表示パネルの第7の構成は、第1の基板上にゲート電極及び液晶素子の第2の電極を有し、液晶素子の第2の電極上に液晶素子の第2の電極よりも面積の小さい反射性の導電膜を有し、ゲート電極及び液晶素子の第2の電極及び導電膜を覆うように第1の絶縁膜を有し、ゲート電極上に第1の絶縁膜を介してトランジスタの半導体層と、液晶素子の第2の電極上に第1の絶縁膜を介して液晶素子の第1の電極と、を有し、トランジスタの半導体層と、液晶素子の第1の電極と、を覆うように第2の絶縁膜を有し、第2の絶縁膜には孔（コンタクトホール）が設けられ、第2の絶縁膜上に形成された配線が孔を介してトランジスタの半導体層と接続されている。そして第1の基板は、トランジスタを有する面を内側にして、第2の基板と張り合わされている。第1の基板と、第2の基板との間には液晶層を有している。

30

【0271】

なお、トランジスタの半導体層と、液晶素子の第1の電極と、は同層の膜である。

【0272】

また、液晶素子の第1の電極はスリットを有する電極又は櫛形電極であり、液晶素子の第2の電極はプレート状電極である。

【0273】

ここで、本発明の第11の実施形態に係る液晶表示パネルは偏光板又は偏光膜を有している。第1の基板の外側の面（液晶層が設けられていない面）及び第2の基板の外側の面（液晶層が設けられていない面）に偏光板を有していてもいいし、第2の絶縁膜の上若しくは下、又は第2の基板の内側の面（液晶層が設けられている面）に偏光膜を有していてもいい。

40

【0274】

本発明の第9の実施形態に係る液晶表示パネルに偏光板を適用した本発明の第11の実施形態に係る液晶表示パネルの第8の構成は、第1の基板上に第1の導電膜及び液晶素子の第2の電極を有し、第1の導電膜上にゲート電極を有し、液晶素子の第2の電極上に液晶素子の第2の電極よりも面積の小さい反射性の第2の導電膜を有し、ゲート電極及び液晶素子の第2の電極及び第2の導電膜を覆うように第1の絶縁膜を有し、ゲート電極上に第1の絶縁膜を介してトランジスタの半導体層と、液晶素子の第2の電極上に第1の絶縁膜

50

を介して液晶素子の第1の電極と、を有し、トランジスタの半導体層と、液晶素子の第1の電極と、を覆うように第2の絶縁膜を有し、第2の絶縁膜には孔（コンタクトホール）が設けられ、第2の絶縁膜上に形成された配線が孔を介してトランジスタの半導体層と接続されている。そして第1の基板は、トランジスタを有する面を内側にして、第2の基板と張り合わされている。第1の基板と、第2の基板との間には液晶層を有している。

【0275】

なお、トランジスタの半導体層と、液晶素子の第1の電極と、は同層の膜である。

【0276】

また、第1の導電膜と液晶素子の第2の電極と、は同層の膜であり、ゲート電極と第2の導電膜とは同層の膜である。

10

【0277】

また、液晶素子の第1の電極はスリットを有する電極又は櫛形電極であり、液晶素子の第2の電極はプレート状電極である。

【0278】

ここで、本発明の第11の実施形態に係る液晶表示パネルは偏光板又は偏光膜を有している。第1の基板の外側の面（液晶層が設けられていない面）及び第2の基板の外側の面（液晶層が設けられていない面）に偏光板を有していてもいいし、第2の絶縁膜の上若しくは下、又は第2の基板の内側の面（液晶層が設けられている面）に偏光膜を有していてもいい。

20

【0279】

本発明の第10の実施形態に係る液晶表示パネルに偏光板を適用した本発明の第11の実施形態に係る液晶表示パネルの第9の構成は、第1の基板上にゲート電極及び液晶素子の第2の電極を有し、ゲート電極及び液晶素子の第2の電極を覆うように第1の絶縁膜を有し、ゲート電極上に第1の絶縁膜を介してトランジスタの半導体層と、液晶素子の第2の電極上に第1の絶縁膜を介して液晶素子の第1の電極と、を有し、トランジスタの半導体層と、液晶素子の第1の電極と、を覆うように第2の絶縁膜を有し、第2の絶縁膜には孔（コンタクトホール）が設けられ、第2の絶縁膜上に形成された配線が孔を介してトランジスタの半導体層と接続されている。そして第1の基板は、トランジスタを有する面を内側にして、第2の基板と張り合わされている。第1の基板と、第2の基板との間には液晶層を有している。

30

【0280】

なお、トランジスタの半導体層と、液晶素子の第1の電極と、は同層の膜である。

【0281】

また、液晶素子の第1の電極及び液晶素子の第2の電極はスリットを有する電極又は櫛形電極である。

40

【0282】

ここで、本発明の第11の実施形態に係る液晶表示パネルは偏光板又は偏光膜を有している。第1の基板の外側の面（液晶層が設けられていない面）及び第2の基板の外側の面（液晶層が設けられていない面）に偏光板を有していてもいいし、第2の絶縁膜の上若しくは下、又は第2の基板の内側の面（液晶層が設けられている面）に偏光膜を有していてもいい。

【0283】

まず、基板の外側に偏光板を備えた構成について詳しく説明する。つまり、配向膜が形成された面とは反対側の面に偏光板を備えている。実施の形態1乃至10で示した液晶表示パネルに偏光板を備えることができるが、本実施の形態においては、実施の形態2の図1及び実施の形態6の図2の構成に偏光板を備えた場合を例に詳しく説明する。

【0284】

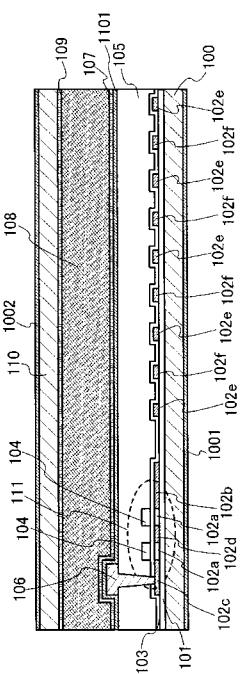

まず、図1の構成の基板の外側に偏光板を備えた構成を図10に示す。図10は基板100の第1の配向膜107が形成された面とは反対側の面に偏光板1001が設けられている。また、基板110の第2の配向膜109が形成された面とは反対側の面に偏光板10

50

0 2 が設けられている。偏光板 1 0 0 1 と偏光板 1 0 0 2 とは光の吸収軸が直交するよう に配置されている。

#### 【 0 2 8 5 】

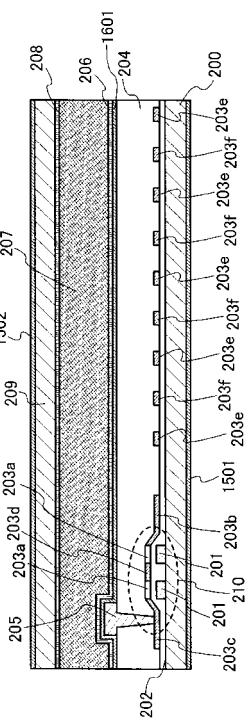

まず、図 2 の構成の基板の外側に偏光板を備えた構成を図 1 5 に示す。図 1 5 は基板 2 0 0 の第 1 の配向膜 2 0 6 が形成された面とは反対側の面に偏光板 1 5 0 1 が設けられてい る。また、基板 2 0 9 の第 2 の配向膜 2 0 8 が形成された面とは反対側の面に偏光板 1 5 0 2 が設けられている。偏光板 1 5 0 1 と偏光板 1 5 0 2 とは光の吸収軸が直交するよう に配置されている。

#### 【 0 2 8 6 】

次に、基板の内側に偏光膜を備えた構成について詳しく説明する。つまり、配向膜が形成 10 された面側に偏光膜を備えている。実施の形態 1 乃至 1 0 で示した液晶表示パネルに偏光 膜を備えることができるが、本実施の形態においては、実施の形態 2 の図 1 及び実施の形 態 6 の図 2 の構成に偏光膜を備えた場合を例に詳しく説明する。

#### 【 0 2 8 7 】

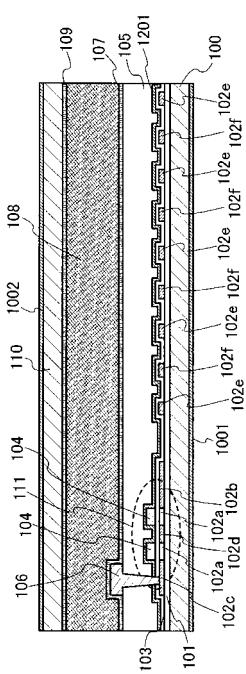

まず、図 1 の構成の基板の内側に偏光膜を備えた構成を図 1 1 に示す。図 1 1 は基板 1 0 0 の第 1 の配向膜 1 0 7 が形成された面側に偏光膜 1 1 0 1 が形成されている。つまり、配線 1 0 6 及び第 3 の絶縁膜 1 0 5 上に偏光膜 1 1 0 1 が形成されている。また、基板 1 1 0 の第 2 の配向膜 1 0 9 が形成された面側に偏光膜 1 1 0 2 が形成されている。つまり、基板 1 1 0 と第 2 の配向膜 1 0 9 との間に偏光膜 1 1 0 2 が形成されている。偏光膜 1 1 0 1 と偏光膜 1 1 0 2 とは光の吸収軸が直交するように形成されている。偏光膜 1 1 0 1 及び偏光膜 1 1 0 2 は二色性染料の水溶液をインキとして直接印刷して形成するこ 20 ができる。例えば、スロットダイコーターなどの装置を用いて印刷すると凹凸のある面にも 印刷が可能となる。

#### 【 0 2 8 8 】

また、図 1 の構成の基板の内側に偏光膜を備えた他の構成を図 1 2 に示す。第 2 の絶縁膜 1 0 3 及びゲート電極 1 0 4 上に偏光膜 1 2 0 1 が形成されている。また、基板 1 1 0 と 第 2 の配向膜 1 0 9 との間に偏光膜 1 2 0 2 が形成されている。偏光膜 1 2 0 1 と偏光膜 1 2 0 2 とは光の吸収軸が直交するように形成されている。偏光膜 1 2 0 1 及び偏光膜 1 2 0 2 は二色性染料の水溶液をインキとして直接印刷して形成するこ 30 ができる。例えば、スロットダイコーターなどの装置を用いて印刷すると凹凸のある面にも 印刷が可能となる。

#### 【 0 2 8 9 】

まず、図 2 の構成の基板の内側に偏光膜を備えた構成を図 1 6 に示す。図 1 6 は基板 2 0 0 の第 1 の配向膜 2 0 6 が形成された面側に偏光膜 1 6 0 1 が形成されている。つまり、配線 2 0 5 及び第 2 の絶縁膜 2 0 4 上に偏光膜 1 6 0 1 が形成されている。また、基板 2 0 9 の第 2 の配向膜 2 0 8 が形成された面側に偏光膜 1 6 0 2 が形成されている。つまり、基板 2 0 9 と第 2 の配向膜 2 0 8 との間に偏光膜 1 6 0 2 が形成されている。偏光膜 1 6 0 1 と偏光膜 1 6 0 2 とは光の吸収軸が直交するように形成されている。偏光膜 1 6 0 1 及び偏光膜 1 6 0 2 は二色性染料の水溶液をインキとして直接印刷して形成するこ 40 ができる。例えば、スロットダイコーターなどの装置を用いて印刷すると凹凸のある面にも 印刷が可能となる。

#### 【 0 2 9 0 】

また、図 2 の構成の基板の内側に偏光膜を備えた他の構成を図 1 7 に示す。第 1 の絶縁膜 2 0 2 、トランジスタ 2 1 0 の半導体層（チャネル形成領域 2 0 3 a 、不純物領域 2 0 3 b 、不純物領域 2 0 3 c 、不純物領域 2 0 3 d ）、第 1 の電極 2 0 3 e 、第 2 の電極 2 0 3 f 上に偏光膜 1 7 0 1 が形成されている。また、基板 2 0 9 と第 2 の配向膜 2 0 8 との 間に偏光膜 1 7 0 2 が形成されている。偏光膜 1 7 0 1 と偏光膜 1 7 0 2 とは光の吸収軸 が直交するように形成されている。偏光膜 1 7 0 1 及び偏光膜 1 7 0 2 は二色性染料の水 溶液をインキとして直接印刷して形成するこ 50 ができる。例えば、スロットダイコーター などの装置を用いて印刷すると凹凸のある面にも 印刷が可能となる。

**【 0 2 9 1 】**

次に、基板の内側に偏光膜、基板の外側に偏光板を備えた構成について説明する。つまり、配向膜が形成された面側に偏光膜を備え、配向膜が形成された面とは反対側の面に偏光板を備えている。実施の形態1乃至10で示した液晶表示パネルに偏光板を備えることができるが、本実施の形態においては、実施の形態2の図1及び実施の形態6の図2の構成に偏光板を備えた場合を例に説明する。

**【 0 2 9 2 】**

まず、図1の構成の基板の内側に偏光膜、基板の外側に偏光板を備えた構成を図13に示す。図13は基板100の第1の配向膜107が形成された面側に偏光膜1101が設けられ、第1の配向膜107が形成された面とは反対側の面に偏光板1001が設けられている。また、基板110の第2の配向膜109が形成された面とは反対側の面に偏光板1002が設けられている。偏光板1001と偏光板1002とは光の吸収軸が直交するように配置されている。10

**【 0 2 9 3 】**

また、図1の構成の内側に偏光膜、基板の外側に偏光板を備えた他の構成を図14に示す。図14は基板100の第1の配向膜107が形成された面側に偏光膜1201が設けられ、第1の配向膜107が形成された面とは反対側の面に偏光板1001が設けられている。また、基板110の第2の配向膜109が形成された面とは反対側の面に偏光板1002が設けられている。偏光板1001と偏光板1002とは光の吸収軸が直交するように配置されている。20

**【 0 2 9 4 】**

まず、図2の構成の内側に偏光膜、基板の外側に偏光板を備えた構成を図18に示す。図18は基板200の第1の配向膜206が形成された面側に偏光膜1601が設けられ、第1の配向膜206が形成された面とは反対側の面に偏光板1501が設けられている。また、基板209の第2の配向膜208が形成された面とは反対側の面に偏光板1502が設けられている。偏光板1501と偏光板1502とは光の吸収軸が直交するように配置されている。30

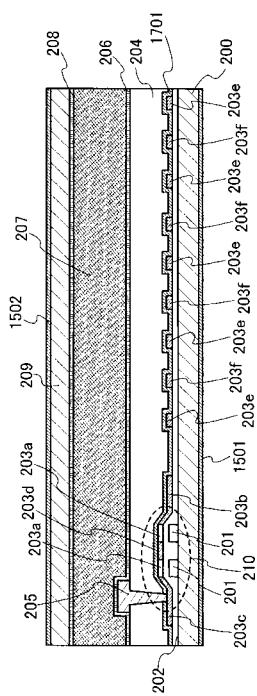

**【 0 2 9 5 】**

また、図2の構成の内側に偏光膜、基板の外側に偏光板を備えた他の構成を図19に示す。図19は基板200の第1の配向膜206が形成された面側に偏光膜1701が設けられ、第1の配向膜206が形成された面とは反対側の面に偏光板1501が設けられている。また、基板209の第2の配向膜208が形成された面とは反対側の面に偏光板1502が設けられている。偏光板1501と偏光板1502とは光の吸収軸が直交するように配置されている。30

**【 0 2 9 6 】****(実施の形態12)**

本発明の第12の実施形態に係る液晶表示パネルの構成について説明する。

**【 0 2 9 7 】**

本実施の形態では、凹凸形状を含む反射電極を備えた場合の液晶表示パネルの構成について説明する。本実施の形態の液晶表示パネルは、外光を乱反射することができるため、表示中の輝度を向上させることができると共に、反射による写り込みを防止することができる。なお、実施の形態1乃至11で示した液晶表示パネルにおいて、反射電極を有する構成であれば本実施の形態に示す構成は適宜適用することができる。40

**【 0 2 9 8 】**

まず、図3の構成の第2の電極301に凹凸形状を含む構成を図20に示す。図20では基板100上に絶縁物2001が形成されている。絶縁物2001としては複数の突起物が配置されていてもよいし、凹凸形状を含む一続きの膜であってもよい。そして、絶縁物2001を覆うように第2の電極301が形成されている。第2の電極301は絶縁物2001の凹凸形状に起因した凹凸が形成されている。よって、第2の電極301が反射性を有する導電膜である場合には外光を乱反射することができるため、表示中の輝度を向上50

させることができると共に、反射による写り込みを防止することができる。

【0299】

また、図21に示すように、第2の電極301に凹凸形状を形成し、絶縁物2001を有しない構成であってもよい。

【0300】

また、図4の構成の導電膜401に凹凸形状を含む構成を図22に示す。図22では第2の電極301上に絶縁物2201が形成されている。絶縁物2201としては複数の突起物が配置されていてもよいし、凹凸形状を含む一続きの膜であってもよい。そして、絶縁物2201を覆うように導電膜401が形成されている。導電膜401は絶縁物2201の凹凸形状に起因した凹凸が形成されている。よって、導電膜401が反射性を有する導電膜である場合には外光を乱反射することができるため、表示中の輝度を向上させることができると共に、反射による写り込みを防止することができる。

【0301】

また、図23に示すように、導電膜401に凹凸形状を形成し、絶縁物2201を有しない構成であってもよい。

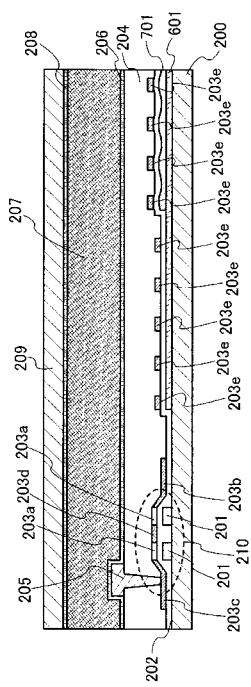

【0302】

また、図6の構成の第2の電極601に凹凸形状を含む構成を図24に示す。図24では基板200上に絶縁物2401が形成されている。絶縁物2401としては複数の突起物が配置されていてもよいし、凹凸形状を含む一続きの膜であってもよい。そして、絶縁物2401を覆うように第2の電極601が形成されている。第2の電極601は絶縁物2401の凹凸形状に起因した凹凸が形成されている。よって、第2の電極601が反射性を有する導電膜である場合には外光を乱反射することができるため、表示中の輝度を向上させることができると共に、反射による写り込みを防止することができる。

【0303】

また、図25に示すように、第2の電極601に凹凸形状を形成し、絶縁物2401を有しない構成であってもよい。

【0304】

また、図7の構成の導電膜701に凹凸形状を含む構成を図26に示す。図26では第2の電極601上に絶縁物2601が形成されている。絶縁物2601としては複数の突起物が配置されていてもよいし、凹凸形状を含む一続きの膜であってもよい。そして、絶縁物2601を覆うように導電膜701が形成されている。導電膜701は絶縁物2601の凹凸形状に起因した凹凸が形成されている。よって、導電膜701が反射性を有する導電膜である場合には外光を乱反射することができるため、表示中の輝度を向上させることができると共に、反射による写り込みを防止することができる。

【0305】

また、図27に示すように、導電膜701に凹凸形状を形成し、絶縁物2601を有しない構成であってもよい。

【0306】

(実施の形態13)

本発明の第13の実施形態に係る液晶表示パネルの構成について説明する。

【0307】

本実施の形態では、液晶層の厚さを一様でなく、部分的に変化させた場合の液晶表示パネルの構成について説明する。本実施の形態の液晶表示パネルは、液晶層の厚さを調整することにより視認性を改善することができる。

【0308】

というのも、液晶層は、屈折率異方性を有しているため、液晶層を通る距離によって、光の偏光状態が変わってくる。そのため、画像を表示する場合に、正しく表示できなくなってしまう。そこで、光の偏光状態を調整する必要がある。そのための方法として、光を反射させて表示を行う部分（反射領域）の液晶層の厚さ（いわゆるセルギャップ）を薄くすることにより、反射領域を光りが2回通っても、透過領域に比べて距離が長くなりすぎな

10

20

30

40

50

いようにすればよい。

【0309】

なお、反射領域での液晶層の厚さは、透過領域における液晶層の厚さの2分の1となることが望ましい。ここで、2分の1とは、人間の目で視認できない程度のずれを有していても良い程度のずれ量も含む。

【0310】

ただし、光は基板と垂直な方向、つまり法線方向のみから入射するわけではない。斜めから入射する場合も多い。よって、それらの場合を総合して、反射領域と透過領域とで、光の通る距離が概ね同じ程度になればよい。したがって、反射領域での液晶層の厚さは、透過領域における液晶層の厚さの概ね3分の1以上、3分の2以下となることが望ましい。

10

【0311】

そこで、液晶層の厚さ（いわゆるセルギャップ）を薄くするために、厚さを調整する膜を配置すればよい。

【0312】

液晶素子の電極が設けられている基板側に、厚さを調整する膜を配置することにより、膜の形成が容易にできるようになる。つまり、液晶素子の電極が設けられている基板側では、様々な膜を形成している。従って、これらの膜を用いて厚さを調整する膜を形成すればよいので、膜を形成する上で、困難が少なくてすむ。また、他の機能を有する膜と同一の工程により形成することも可能となるため、プロセス工程を簡略化でき、コストを低減することが出来る。

20

【0313】

なお、液晶層の厚さを調整する膜は、対向基板側に配置されていてもよい。

【0314】

対向基板側に、液晶層の厚さを調整する膜を配置することにより、液晶素子の電極を、反射領域と透過領域において、同一平面（下層の配線や電極などによって多少のずれが生じても、本実施の形態において示す液晶層の厚さを調整する膜の厚さによるずれに比べてはるかに小さいずれは同一平面に含むものとする）上に配置することが可能となる。そのため、画素電極と共通電極との距離が、透過領域と反射領域とで、概ね等しくすることが可能となる。電界のかかり方や強度は、電極間の距離によって変化するため、電極の間隔を同程度であることにより、反射領域と透過領域とにおいて、液晶層に加わる電界も同程度にすることが出来るため、液晶分子の制御が正確に行うことが出来る。また、反射領域と透過領域とで、液晶分子の回転度合いが概ね等しくなるので、透過型として表示する場合と、反射型として表示する場合とで、概ね等しい階調として画像を表示することが出来る。

30

【0315】

また、液晶層の厚さを調整する膜があると、その近傍において、液晶分子の配向状態が乱れてしまう可能性があり、ディスクリネーションなどの不良を生んでしまう可能性がある。しかし、対向基板上に液晶層の厚さを調整する膜を配置することにより、液晶素子の電極から離すことができるので、電界のかかり方が弱くなるため、液晶分子の配向状態が乱れにくくなってしまうことを防ぐことが出来る。

40

【0316】

また、対向基板は、カラーフィルターやブラックマトリックスなどを形成するだけなので、工程数が少ない。よって、対向基板に液晶層の厚さを調整する膜を形成しても、歩留まりを低下させにくくなる。仮に、不良が出ても、工程数がすくなく、コストも安いので、製造コストが無駄になる量を少なくすることが出来る。

【0317】

なお、対向基板に液晶層の厚さを調整する膜を形成する場合、厚さ調整膜の中に、光を拡散させて輝度を向上させることができるように散乱材として機能する粒子を含ませてもよい。粒子は、ギャップ調整膜を構成している基材（例えばアクリル樹脂など）と屈折率が異なると共に、透光性を有する樹脂材料から成る。このように粒子を含ませることによっ

50

て、光を散乱させることができ、表示画像のコントラスト、輝度も向上する。

【0318】

以上のような構成を有する本発明の液晶表示装置は、広視野角であり、また表示画面を見る角度に依存した色味の変化が少なく、さらに太陽光が照らされた外界においても暗い室内（若しくは夜の屋外）においても良好に視認される画像を提供することができる。

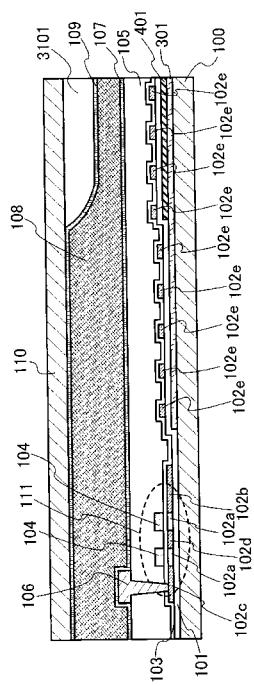

【0319】

まず、図4の構成の導電膜401の上側（反射領域）の液晶層の厚さを薄くする構成を図28に示す。図28では第3の絶縁膜105上に第4の絶縁膜2801を有する。第4の絶縁膜2801は導電膜401にほぼ重なるように形成されている。

【0320】

光を反射させて表示を行う領域（反射領域）において、第4の絶縁膜2801は液晶層108の厚さを調整する為に設けられている。第4の絶縁膜2801を設けることによって反射領域における液晶層108の厚さを、透過領域における液晶層108の厚さよりも薄くすることが出来る。つまり、第2の電極301の上側の液晶層108のうち、第4の絶縁膜2801上側の液晶層つまり導電膜401上側の液晶層は厚さが薄くなっている。

【0321】

なお、第4の絶縁膜2801は屈折率異方性をほとんど有しないため、そこを光が通っても、偏光状態は変化しない。よって、第4の絶縁膜2801の有無や厚さなどは、大きな影響は与えない。

【0322】

なお、第3の絶縁膜105上に第4の絶縁膜2801が形成されていなくても、第2の電極301の上側の液晶層のうち、導電膜401上側の液晶層108の厚さを薄くすることができればよい。したがって、図31に示すように基板110において、第2の配向膜109が形成される面側に第4の絶縁膜3101が形成されていてもよい。

【0323】

次に、図7の構成の導電膜701の上側の液晶層の厚さを薄くする構成を図29に示す。図29では第2の絶縁膜204上に第3の絶縁膜2901を有する。第3の絶縁膜2901は導電膜701にほぼ重なるように形成されている。

【0324】

光を反射させて表示を行う領域（反射領域）において、第3の絶縁膜2901は液晶層207の厚さを調整する為に設けられている。第3の絶縁膜2901を設けることによって反射領域における液晶層207の厚さを、透過領域における液晶層207の厚さよりも薄くすることが出来る。つまり、第2の電極601の上側の液晶層207のうち、第3の絶縁膜2901上側の液晶層207、つまり導電膜701上側の液晶層207は厚さが薄くなっている。

【0325】

なお、第3の絶縁膜2901は屈折率異方性をほとんど有しないため、そこを光が通っても、偏光状態は変化しない。よって、第3の絶縁膜2901の有無や厚さなどは、大きな影響は与えない。

【0326】

なお、第2の絶縁膜204上に第3の絶縁膜2901が形成されていなくても、第2の電極601の上側の液晶層207のうち、導電膜701上側の液晶層207の厚さを薄くすることができればよい。したがって、図32に示すように基板209において、第2の配向膜208が形成される面側に第3の絶縁膜3201が形成されていてもよい。

【0327】

次に、図8の構成の導電膜701の上側の液晶層の厚さを薄くする構成を図30に示す。図30では第2の絶縁膜204上に第3の絶縁膜3001を有する。第3の絶縁膜3001は導電膜701にほぼ重なるように形成されている。

【0328】

光を反射させて表示を行う領域（反射領域）において、第3の絶縁膜3001は液晶層2

10

20

30

40

50

07の厚さを調整する為に設けられている。第3の絶縁膜3001を設けることによって反射領域における液晶層207の厚さを、透過領域における液晶層207の厚さよりも薄くすることが出来る。つまり、第2の電極601の上側の液晶層207のうち、第3の絶縁膜3001上側の液晶層207、つまり導電膜701上側の液晶層207は厚さが薄くなっている。

### 【0329】

なお、第3の絶縁膜3001は屈折率異方性をほとんど有しないため、そこを光が通っても、偏光状態は変化しない。よって、第3の絶縁膜3001の有無や厚さなどは、大きな影響は与えない。

### 【0330】

なお、第2の絶縁膜204上に第3の絶縁膜3001が形成されていなくても、第2の電極601の上側の液晶層のうち、導電膜701上側の液晶層の厚さを薄くすることができればよい。したがって、図33に示すように基板209において、第2の配向膜208が形成される面側に第3の絶縁膜3301が形成されていてもよい。

### 【0331】

#### (実施の形態14)

本発明の第14の実施形態に係る液晶表示パネルの構成について説明する。

### 【0332】

本実施の形態では、液晶表示パネルに位相差板を備えた場合の構成について説明する。

### 【0333】

まず、基板の外側に位相差板を備えた構成について説明する。つまり、配向膜が形成された面とは反対側の面に位相差板を備えている。実施の形態1乃至13で示した液晶表示パネルに位相差板を備えることができるが、実施の形態11の図10及び図15の構成に位相差板を備えた場合を例に説明する。

### 【0334】

まず、図10の構成の基板の外側に位相差板を備えた構成を図34に示す。図34は基板100の第1の配向膜107が形成された面とは反対側の面に偏光板1001が設けられ、偏光板1001と基板100との間に位相差板3401が設けられている。また、基板110の第2の配向膜109が形成された面とは反対側の面に偏光板1002が設けられ、偏光板1002と基板110との間に位相差板3402が設けられている。

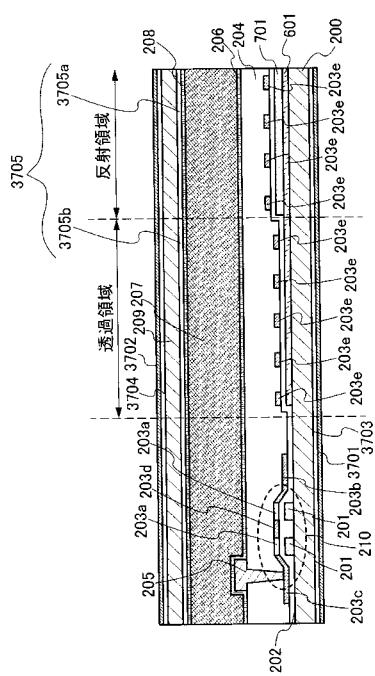

### 【0335】

まず、図15の構成の基板の外側に位相差板を備えた構成を図36に示す。図36は基板200の第1の配向膜206が形成された面とは反対側の面に偏光板1501が設けられ、偏光板1501と基板200との間に位相差板3601が設けられている。また、基板209の第2の配向膜208が形成された面とは反対側の面に偏光板1502が設けられ、偏光板1502と基板209との間に位相差板3602が設けられている。偏光板1501と偏光板1502とは光の吸収軸が直交するように配置されている。

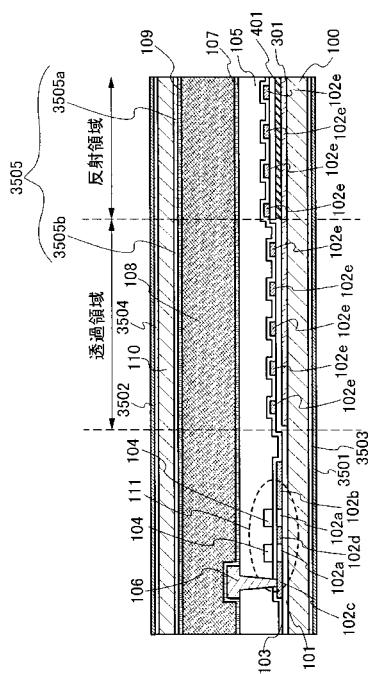

### 【0336】

次に、基板の内側に位相差膜を備えた構成について説明する。つまり、配向膜が形成された面側に位相差膜を備えている。この位相差膜は、半透過型の液晶表示パネルにおいて、反射領域上の部分において位相差を有している。そして、透過領域上の部分においては位相差は概略0とする。

### 【0337】

まず、図4の構成の基板の内側に位相差膜を備えた構成を図35に示す。図35は基板100の第1の配向膜107が形成された面とは反対側の面に偏光板3501が設けられ、偏光板3501と基板100との間に位相差板3503が設けられている。また、基板110の第2の配向膜109が形成された面とは反対側の面に偏光板3502が設けられ、偏光板3502と基板110との間に位相差板3504が設けられている。そして、基板110の第2の配向膜109が形成された面側に位相差膜3505が形成されている。位相差膜3505は反射領域上の部分3505aにおいて位相差を有している。そして、透

10

20

30

40

50

過領域上の部分 3505b において位相差は概略 0 とする。

### 【0338】

次に、図 7 の構成の基板の内側に位相差膜を備えた構成を図 37 に示す。図 37 は基板 200 の第 1 の配向膜 206 が形成された面とは反対側の面に偏光板 3701 が設けられ、偏光板 3701 と基板 200との間に位相差板 3703 が設けられている。また、基板 209 の第 2 の配向膜 208 が形成された面とは反対側の面に偏光板 3702 が設けられ、偏光板 3702 と基板 209との間に位相差板 3704 が設けられている。そして、基板 209 の第 2 の配向膜 208 が形成された面側に位相差膜 3705 が形成されている。位相差膜 3705 は反射領域上の部分 3705a において位相差を有している。そして、透過領域上の部分 3705b において位相差は概略 0 とする。

10

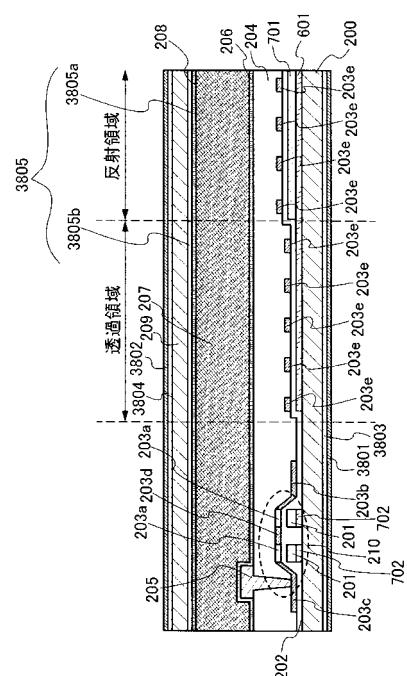

### 【0339】

次に、図 8 の構成の基板の内側に位相差膜を備えた構成を図 38 に示す。図 38 は基板 200 の第 1 の配向膜 206 が形成された面とは反対側の面に偏光板 3801 が設けられ、偏光板 3801 と基板 200との間に位相差板 3803 が設けられている。また、基板 209 の第 2 の配向膜 208 が形成された面とは反対側の面に偏光板 3802 が設けられ、偏光板 3802 と基板 209との間に位相差板 3804 が設けられている。そして、基板 209 の第 2 の配向膜 208 が形成された面側に位相差膜 3805 が形成されている。位相差膜 3805 は反射領域上の部分 3805a において位相差を有している。そして、透過領域上の部分 3805b において位相差は概略 0 とする。

20

### 【0340】

#### (実施の形態 15)

本発明の第 15 の実施形態に係る液晶表示パネルの構成について説明する。

### 【0341】

実施の形態 1 乃至 14 においては、画素電極と共に電極とが同層の導電膜でない場合には、画素電極が共通電極よりも液晶層により配置されていたが、本実施の形態においては、共通電極が画素電極よりも液晶層により配置された場合の液晶表示パネルの構成について説明する。

### 【0342】

まず、図 3 の構成において、第 1 の電極 102e を共通電極とし、第 2 の電極 301 を画素電極とした場合の構成を図 39 に示す。トランジスタ 111 の不純物領域 102b と、第 2 の電極 301 とはコンタクトホールを介して配線 3901 によって接続されている。よって、ゲート電極 104 の電位の変化によりトランジスタ 111 がオンして、配線 106 に供給される信号が第 2 の電極 301 に入力される。つまり、この信号の伝送情報は電位であり、第 2 の電極 301 に電荷が蓄積されて信号に応じた電位が入力される。そして、第 1 の電極 102e には複数の画素に渡って共通の電位が入力されている。こうして、第 1 の電極 102e と第 2 の電極 301 との電位差で発生した電界によって液晶層 108 の液晶分子の配列が変化する。

30

### 【0343】

次に、図 5 の構成において、第 1 の電極 102e を共通電極とし、第 2 の電極 501 を画素電極とした場合の構成を図 41 に示す。トランジスタ 111 の不純物領域 102b と、第 2 の電極 501 とはコンタクトホールを介して配線 4101 によって接続されている。よって、ゲート電極 104 の電位の変化によりトランジスタ 111 がオンして、配線 106 に供給される信号が第 2 の電極 501 に入力される。つまり、この信号の伝送情報は電位であり、第 2 の電極 501 に電荷が蓄積されて信号に応じた電位が入力される。そして、第 1 の電極 102e には複数の画素に渡って共通の電位が入力されている。こうして、第 1 の電極 102e と第 2 の電極 501 との電位差で発生した電界によって液晶層 108 の液晶分子の配列が変化する。

40

### 【0344】

次に、図 6 の構成において、第 1 の電極 203e を共通電極とし、第 2 の電極 601 を画素電極とした場合の構成を図 40 に示す。トランジスタ 210 の不純物領域 203b と、

50

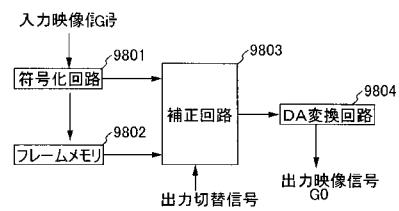

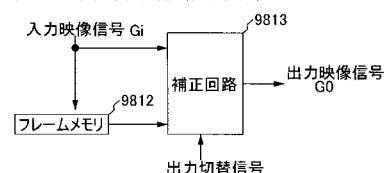

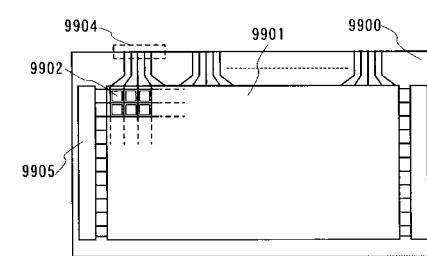

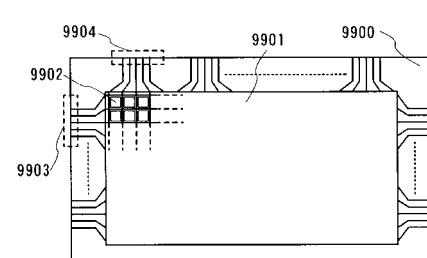

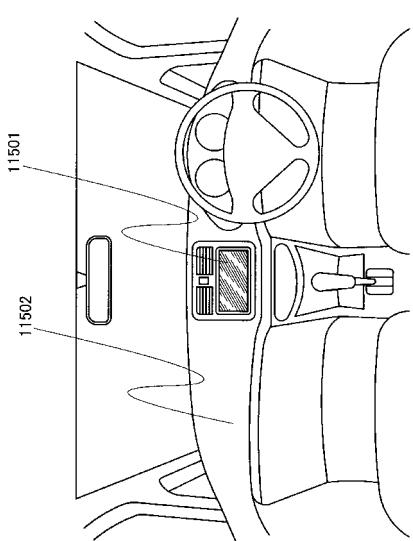

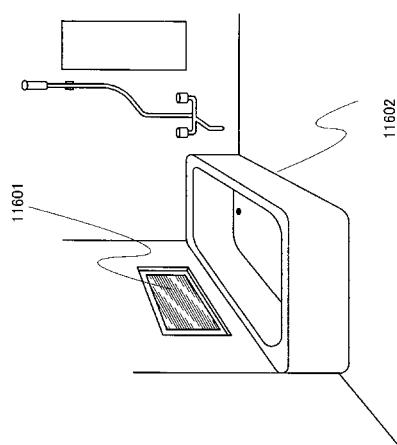

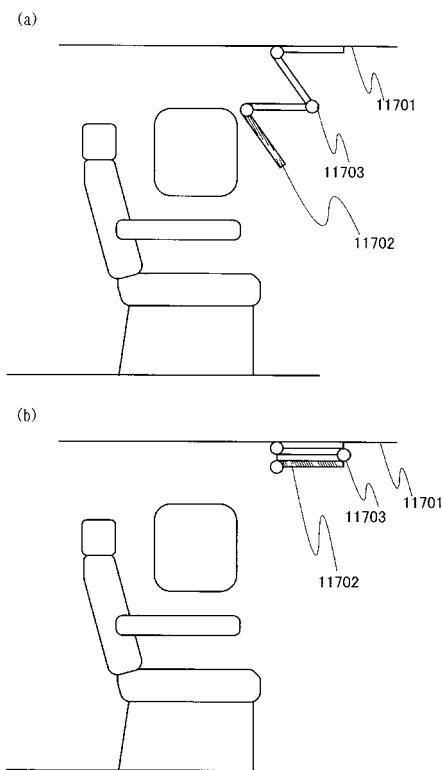

第2の電極601とはコンタクトホールを介して配線4001によって接続されている。よって、ゲート電極201の電位の変化によりトランジスタ210がオンして、配線205に供給される信号が第2の電極601に入力される。つまり、この信号の伝送情報は電位であり、第2の電極601に電荷が蓄積されて信号に応じた電位が入力される。そして、第1の電極203eには複数の画素に渡って共通の電位が入力されている。こうして、第1の電極203eと第2の電極601との電位差で発生した電界によって液晶層207の液晶分子の配列が変化する。