등록특허 10-2403143

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2022년05월27일

(11) 등록번호 10-2403143

(24) 등록일자 2022년05월24일

- (51) 국제특허분류(Int. Cl.)

*G01S 7/521* (2006.01) *G01S 15/89* (2006.01)

*G01S 7/52* (2006.01) *H03K 17/687* (2006.01)

- (52) CPC특허분류

*G01S 7/521* (2021.01)

*G01S 15/8915* (2013.01)

- (21) 출원번호 10-2018-7031301

- (22) 출원일자(국제) 2017년03월31일

심사청구일자 2020년03월25일

- (85) 번역문제출일자 2018년10월29일

- (65) 공개번호 10-2018-0127463

- (43) 공개일자 2018년11월28일

- (86) 국제출원번호 PCT/US2017/025269

- (87) 국제공개번호 WO 2017/173211

국제공개일자 2017년10월05일

(30) 우선권주장

15/087,943 2016년03월31일 미국(US)

## (56) 선행기술조사문헌

JP2008272471 A\*

WO2015189982 A1\*

JP2012095168 A

US20150032002 A1

\*는 심사관에 의하여 인용된 문헌

전체 청구항 수 : 총 12 항

심사관 : 김민성

## (54) 발명의 명칭 양극성 펄서를 위한 대칭 수신기 스위치

**(57) 요 약**

초음파 디바이스들을 위한 회로가 설명된다. 복수의 레벨의 양극성 펄스들을 제공할 수 있는 멀티레벨 펄서가 설명된다. 멀티레벨 펄서는 펄싱 회로 및 펄서 및 피드백 회로를 포함한다. 대칭 스위치들도 설명된다. 대칭 스위치들은 수신 회로로부터의 신호들을 차단하기 위해 초음파 수신 회로에 대한 입력들로서 위치될 수 있다.

**대 표 도 - 도9**

(52) CPC특허분류

*G01S 7/52017* (2013.01)

*G01S 7/5202* (2013.01)

*G01S 7/52047* (2021.01)

*H03K 17/6874* (2013.01)

---

## 명세서

### 청구범위

#### 청구항 1

초음파 디바이스로서,

용량성 초음파 트랜스듀서;

상기 용량성 초음파 트랜스듀서에 연결되고, 출력 단자로부터 양극성 입력 신호를 상기 용량성 초음파 트랜스듀서에 제공하도록 구성되는 양극성 펄서;

상기 용량성 초음파 트랜스듀서에 의해 출력된 전기 신호를 처리하도록 구성되는 수신 회로; 및

제1 트랜지스터 및 제2 트랜지스터를 포함하는 대칭 스위치

를 포함하고,

상기 대칭 스위치는 상기 양극성 펄서의 상기 출력 단자와 상기 용량성 초음파 트랜스듀서 사이에 연결되는 입력 단자를 갖고, 상기 수신 회로에 연결되는 출력 단자를 갖고,

상기 제1 트랜지스터는 제1 게이트, 제1 소스 및 제1 드레인을 갖고, 상기 제2 트랜지스터는 제2 게이트, 제2 소스 및 제2 드레인을 가지며,

상기 제1 게이트는 상기 제2 게이트에 접속되고, 상기 제1 게이트 및 상기 제2 게이트의 전위는 제1 단자를 통해 제1 제어 신호에 의해 제어되고, 상기 제1 소스는 상기 제2 소스에 접속되고, 상기 제1 소스 및 상기 제2 소스의 전위는 제2 단자를 통해 제2 제어 신호에 의해 제어되고,

상기 제1 게이트 및 상기 제1 소스는 제1 시간에 제1 동일한 전위에, 그리고 제2 시간에 제2 동일한 전위에 연결되거나 연결가능한, 초음파 디바이스.

#### 청구항 2

제1항에 있어서, 상기 수신 회로는 전류-전압 변환기(current-to-voltage converter)를 포함하는, 초음파 디바이스.

#### 청구항 3

제2항에 있어서, 상기 전류-전압 변환기는 트랜스-임피던스 증폭기(TIA: trans-impedance amplifier)를 포함하는, 초음파 디바이스.

#### 청구항 4

제1항에 있어서, 상기 대칭 스위치의 상기 제1 트랜지스터 및 상기 제2 트랜지스터는 p형 금속 산화물 반도체(PMOS) 트랜지스터들인, 초음파 디바이스.

#### 청구항 5

제1항에 있어서, 상기 대칭 스위치의 상기 제1 트랜지스터 및 상기 제2 트랜지스터는 n형 금속 산화물 반도체(NMOS) 트랜지스터들인, 초음파 디바이스.

#### 청구항 6

초음파 디바이스로서,

용량성 초음파 트랜스듀서;

상기 용량성 초음파 트랜스듀서에 연결되고, 출력 단자로부터 양극성 입력 신호를 상기 용량성 초음파 트랜스듀서에 제공하도록 구성되는 양극성 펄서;

상기 용량성 초음파 트랜스듀서에 의해 출력된 전기 신호를 처리하도록 구성되는 수신 회로; 및

제1 트랜지스터 및 제2 트랜지스터를 포함하는 대칭 스위치

를 포함하고,

상기 대칭 스위치는 상기 양극성 펄서의 상기 출력 단자와 상기 용량성 초음파 트랜스듀서 사이에 연결되는 입력 단자를 갖고, 상기 수신 회로에 연결되는 출력 단자를 갖고,

상기 제1 트랜지스터는 제1 게이트, 제1 소스 및 제1 드레인을 갖고, 상기 제2 트랜지스터는 제2 게이트, 제2 소스 및 제2 드레인을 가지며, 상기 제1 게이트는 상기 제2 게이트에 접속되고, 상기 제1 소스는 상기 제2 소스에 접속되고, 상기 대칭 스위치는 상기 제2 드레인에 접속된 제3 드레인을 갖는 제3 트랜지스터를 추가로 포함하고,

상기 제1 게이트 및 상기 제2 게이트의 전위는 제1 단자를 통해 제1 제어 신호에 의해 제어되고, 상기 제1 소스 및 상기 제2 소스의 전위는 제2 단자를 통해 제2 제어 신호에 의해 제어되고,

상기 제3 트랜지스터는 제3 게이트를 갖고, 상기 제3 게이트의 전위는 제3 단자를 통해 제3 제어 신호에 의해 제어되고,

상기 제1 제어 신호, 상기 제2 제어 신호 및 상기 제3 제어 신호는 서로 상이하고, 상기 제1 단자, 상기 제2 단자 및 상기 제3 단자는 서로 상이한, 초음파 디바이스.

#### 청구항 7

초음파 디바이스를 동작시키는 방법으로서,

상기 초음파 디바이스의 송신 동작 모드 동안 양극성 펄서로부터의 양극성 펄서 신호를 용량성 초음파 트랜스듀서의 제1 단자에 제공하는 단계;

상기 송신 동작 모드 동안 상기 용량성 초음파 트랜스듀서의 상기 제1 단자와 수신 회로 사이에 연결된 대칭 스위치를 개방 상태로 동작시키는 단계 - 상기 대칭 스위치는 제1 게이트, 제1 소스 및 제1 드레인을 갖는 제1 트랜지스터와, 제2 게이트, 제2 소스 및 제2 드레인을 갖는 제2 트랜지스터를 포함하고, 상기 제1 게이트는 상기 제2 게이트에 접속되고, 상기 제1 소스는 상기 제2 소스에 접속됨 - ; 및

상기 초음파 디바이스의 수신 동작 모드 동안 상기 대칭 스위치를 폐쇄 상태로 동작시키는 단계

를 포함하고,

상기 송신 동작 모드 동안 상기 대칭 스위치를 개방 상태로 동작시키는 단계는, 상기 제1 게이트, 상기 제2 게이트, 상기 제1 소스, 및 상기 제2 소스를 제1 시간에 제1 동일한 전위에 연결하고, 상기 제1 게이트, 상기 제2 게이트, 상기 제1 소스, 및 상기 제2 소스를 제2 시간에 제2 동일한 전위에 연결하고, 상기 제1 게이트, 상기 제2 게이트, 상기 제1 소스, 및 상기 제2 소스를 제3 시간에 상기 제1 동일한 전위에 다시 연결하는 단계를 포함하고,

상기 제1 게이트 및 상기 제2 게이트의 전위는 제1 단자를 통해 제1 제어 신호에 의해 제어되고, 상기 제1 소스 및 상기 제2 소스의 전위는 제2 단자를 통해 제2 제어 신호에 의해 제어되는, 방법.

#### 청구항 8

제7항에 있어서, 상기 수신 회로의 전류-전압 변환기를 사용하여 상기 수신 동작 모드 동안 상기 용량성 초음파 트랜스듀서로부터의 전류를 전압으로 변환하는 단계를 추가로 포함하는, 방법.

#### 청구항 9

제8항에 있어서, 상기 용량성 초음파 트랜스듀서로부터의 전류를 전압으로 변환하는 단계는 트랜스 임피던스 증폭기(TIA)로 수행되는, 방법.

#### 청구항 10

제7항에 있어서, 상기 초음파 디바이스의 수신 동작 모드 동안 상기 대칭 스위치를 폐쇄 상태로 동작시키는 단계는, 상기 대칭 스위치의 상기 제1 트랜지스터의 상기 제1 드레인 상에서 상기 용량성 초음파 트랜스듀서의 출

력 신호를 수신하고, 상기 대칭 스위치의 상기 제2 트랜지스터의 상기 제2 드레인으로부터 상기 수신 회로에 상기 출력 신호를 제공하는 단계를 포함하는, 방법.

#### 청구항 11

제7항에 있어서, 상기 제1 동일한 전위는 접지 전위를 포함하고, 상기 제2 동일한 전위는 상기 양극성 펄서의 바이어스 전압을 포함하는, 방법.

#### 청구항 12

제1항에 있어서, 상기 제1 동일한 전위는 접지 전위를 포함하고, 상기 제2 동일한 전위는 상기 양극성 펄서의 바이어스 전압을 포함하는, 초음파 디바이스.

#### 청구항 13

삭제

#### 청구항 14

삭제

#### 청구항 15

삭제

#### 청구항 16

삭제

#### 청구항 17

삭제

#### 청구항 18

삭제

#### 청구항 19

삭제

#### 청구항 20

삭제

### 발명의 설명

#### 기술 분야

##### [0001] 관련 출원

본 출원은 대리인 관리번호가 B1348.70027US00이고 발명의 명칭이 "SYMMETRIC RECEIVER SWITCH FOR BIPOLAR PULSER"인 2016년 3월 31일자로 출원된 미국 특허 출원 제15/087,943호의 35 U.S.C. § 120 하에서의 이익을 주장하는 연속출원이며, 그것의 전체 내용은 참조에 의해 본 명세서에 포함된다.

##### [0003] 기술분야

본 출원은 초음파 이미징 및 고강도 집중 초음파(HIFU: high intensity focused ultrasound)를 위한 초음파 디바이스들에 관한 것이다.

#### 배경 기술

[0005] 일부 종래의 초음파 디바이스들은 초음파 트랜스듀서(ultrasonic transducer)에 펄스들을 제공하도록 구성되는

펄싱 회로들을 포함한다. 종종 초음파 트랜스듀서는 송신 및 수신에서 동작한다.

### 발명의 내용

- [0006] 본 출원의 양태들은 피드백을 갖는 펄서를 갖는 집적 회로를 포함하는 초음파-온-칩 디바이스(ultrasound-on-a-chip device)를 제공한다. 대칭 수신 스위치들은 또한 초음파-온-칩 디바이스 내에 제공되고, 초음파 트랜스듀서들을 구동하기 위한 멀티레벨 펄서들의 사용을 용이하게 하기 위해 초음파 트랜스듀서들의 출력에 연결된다.

- [0007] 본 출원의 양태는 용량성 초음파 트랜스듀서, 용량성 초음파 트랜스듀서에 연결되고, 출력 단자로부터 용량성 초음파 트랜스듀서에 양극성 입력 신호를 제공하도록 구성되는 양극성 펄서, 용량성 초음파 트랜스듀서에 의해 출력된 전기 신호를 처리하도록 구성되는 수신 회로, 및 제1 트랜지스터 및 제2 트랜지스터를 포함하는 대칭 스위치를 포함하는 초음파 디바이스에 관한 것이다. 대칭 스위치는 양극성 펄서의 출력 단자와 용량성 초음파 트랜스듀서 사이에 연결되는 입력 단자를 가지며 수신 회로에 연결되는 출력 단자를 갖는다.

- [0008] 본 출원의 양태는 초음파 디바이스를 동작시키는 방법으로서, 초음파 디바이스의 송신 동작 모드 동안 양극성 펄서로부터의 양극성 펄서 신호를 용량성 초음파 트랜스듀서의 제1 단자에 제공하는 단계, 송신 동작 모드 동안 용량성 초음파 트랜스듀서의 제1 단자와 수신 회로 사이에 연결된 대칭 스위치를 개방 상태로 동작시키는 단계, 및 초음파 디바이스의 수신 동작 모드 동안 대칭 스위치를 폐쇄 상태로 동작시키는 단계를 포함하는 방법에 관한 것이다.

### 도면의 간단한 설명

- [0009] 본 출원의 다양한 양태들 및 실시예들이 다음의 도면들을 참조하여 설명될 것이다. 도면들은 반드시 일정한 비율로 그려지는 것은 아님을 알아야 한다. 여러 도면들에 출현하는 항목들은 그것들이 출현하는 모든 도면들에서 동일한 참조 번호에 의해 표시된다.

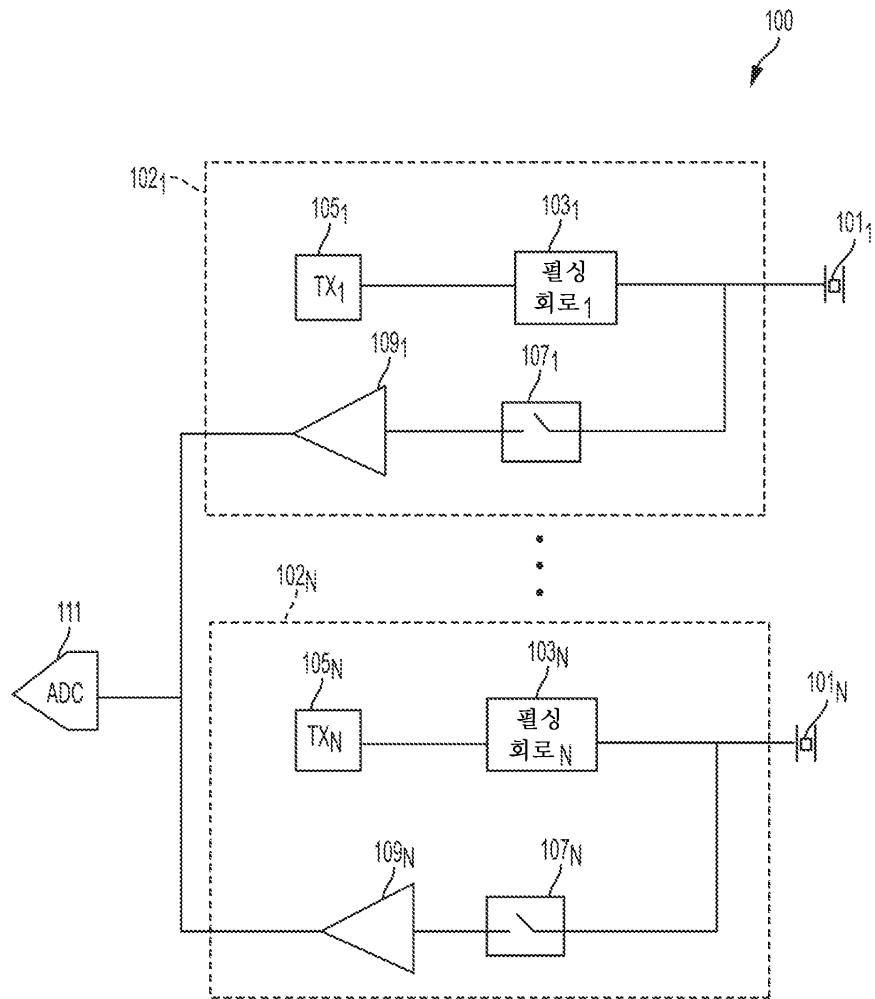

- 도 1은 본 출원의 비-제한적인 실시예에 따라, 복수의 펄싱 회로 및 복수의 수신기 스위치를 포함하는 초음파 디바이스를 도시하는 블록도이다.

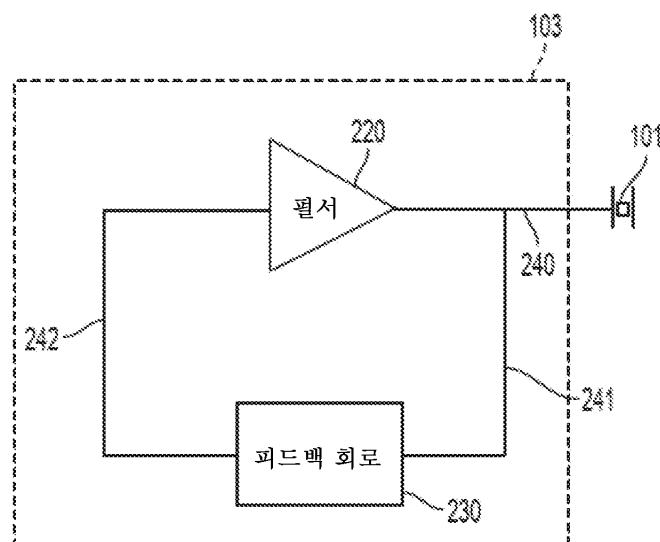

- 도 2는 본 출원의 비-제한적인 실시예에 따라, 용량성 초음파 트랜스듀서에 연결된 펄싱 회로를 도시하는 블록도이다.

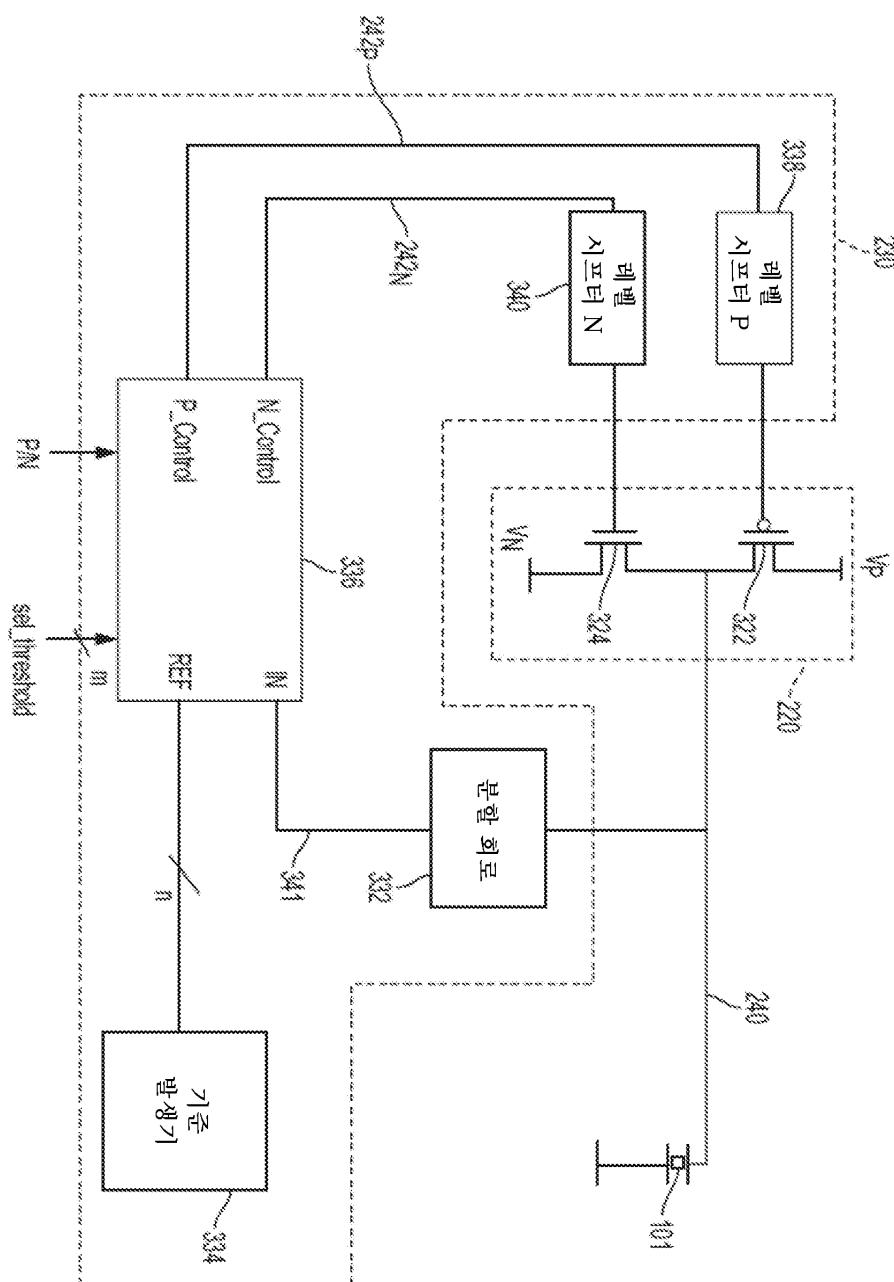

- 도 3은 본 출원의 비-제한적인 실시예에 따라, 펄서 및 피드백 회로를 포함하는 펄싱 회로를 도시하는 블록도이다.

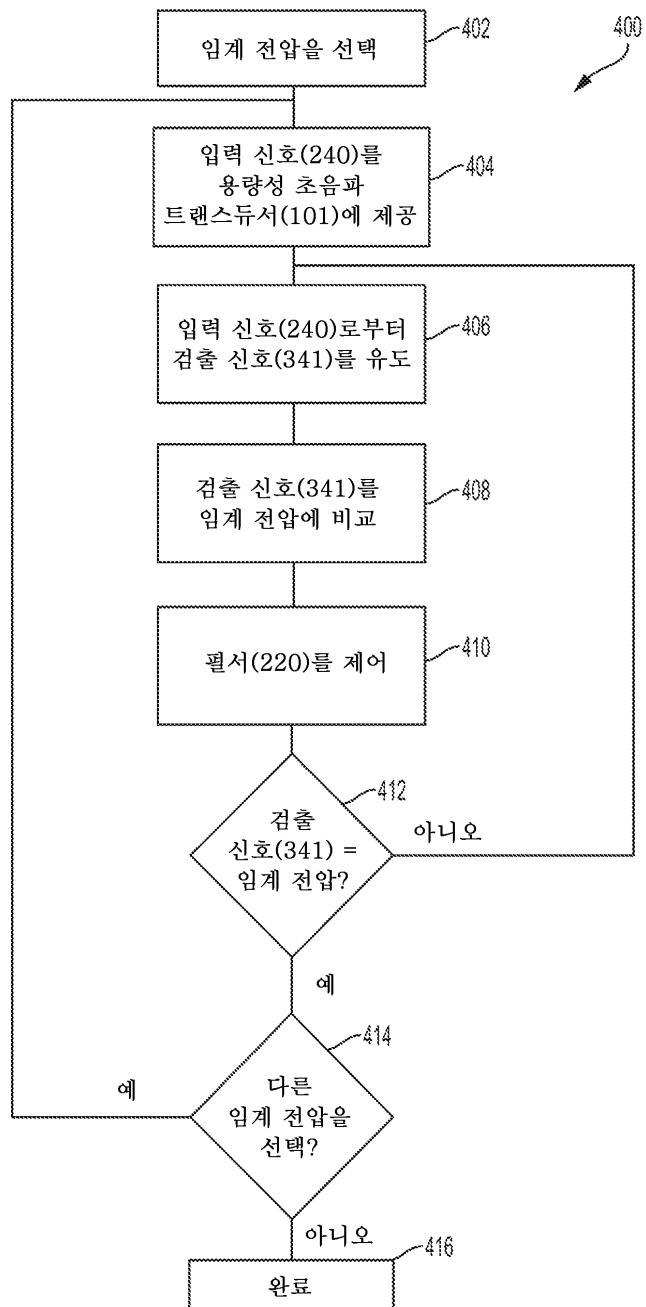

- 도 4는 본 출원의 비-제한적인 실시예에 따라, 용량성 초음파 트랜스듀서에 연결된 펄싱 회로를 동작시키는 방법의 동작들을 도시하는 블록도이다.

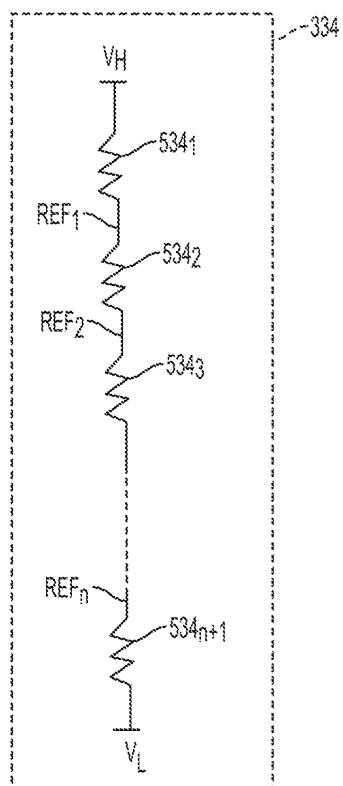

- 도 5a는 본 출원의 비-제한적인 실시예에 따라, 복수의 임계 전압을 발생시키도록 구성되는 저항성 래더를 도시하는 회로도이다.

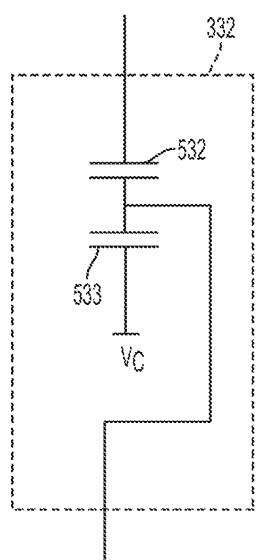

- 도 5b는 본 출원의 비-제한적인 실시예에 따라, 겸출 신호를 발생시키도록 구성되는 분할 회로를 도시하는 회로도이다.

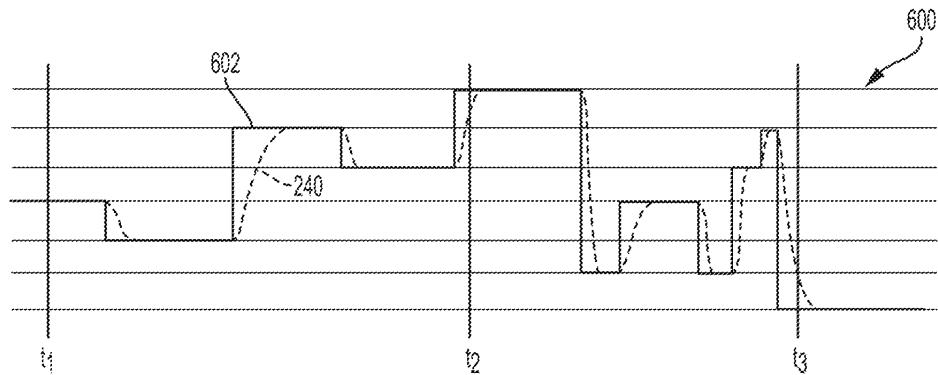

- 도 6a는 본 출원의 비-제한적인 실시예에 따라, 펄싱 회로에 의해 용량성 초음파 트랜스듀서에 제공되는 예시적인 신호를 나타내는 타이밍도를 도시한다.

- 도 6b는 본 출원의 비-제한적인 실시예에 따라, 펄싱 회로에 의해 용량성 초음파 트랜스듀서에 제공되는 아포다이즈된 신호를 나타내는 타이밍도를 도시한다.

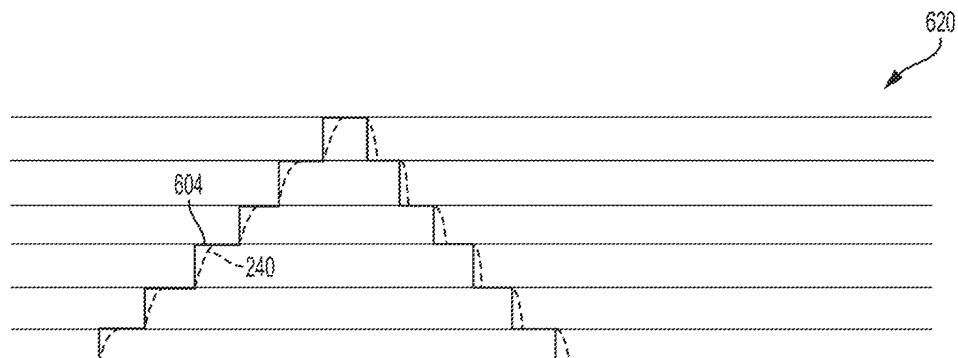

- 도 7은 본 출원의 비-제한적인 실시예에 따라, 복수의 용량성 초음파 트랜스듀서에 연결된 복수의 펄싱 회로를 도시하는 블록도이다.

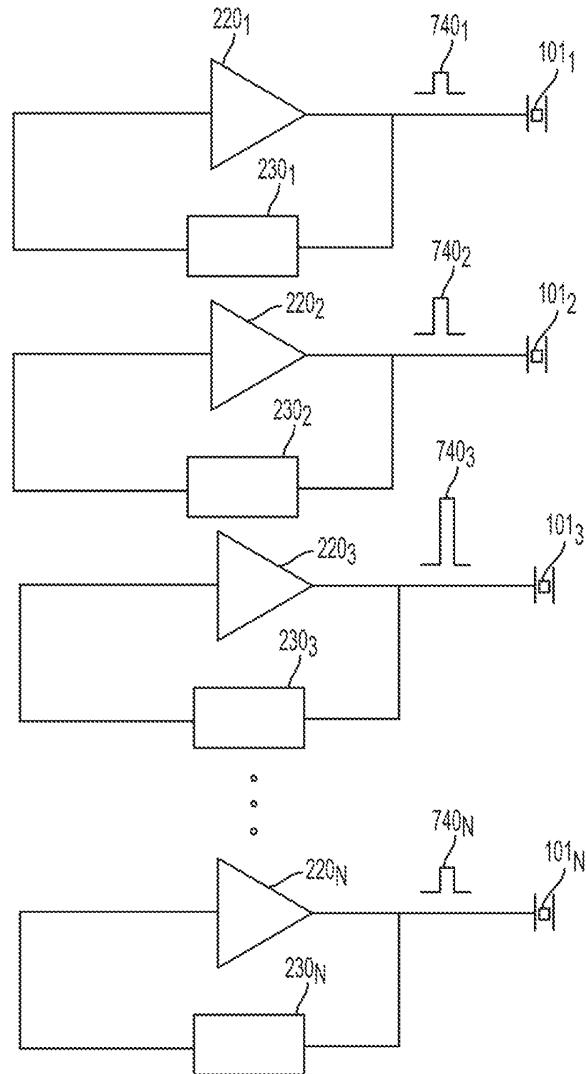

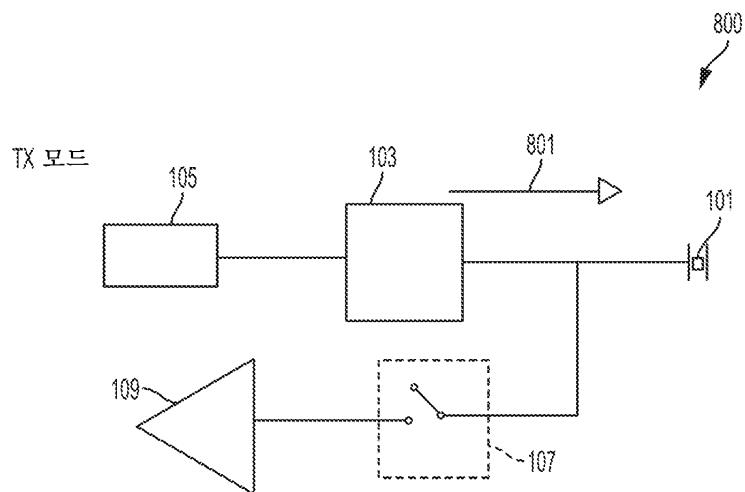

- 도 8a는 본 출원의 비-제한적인 실시예에 따라, 송신 모드에서 동작하는 초음파 디바이스를 도시하는 블록도이다.

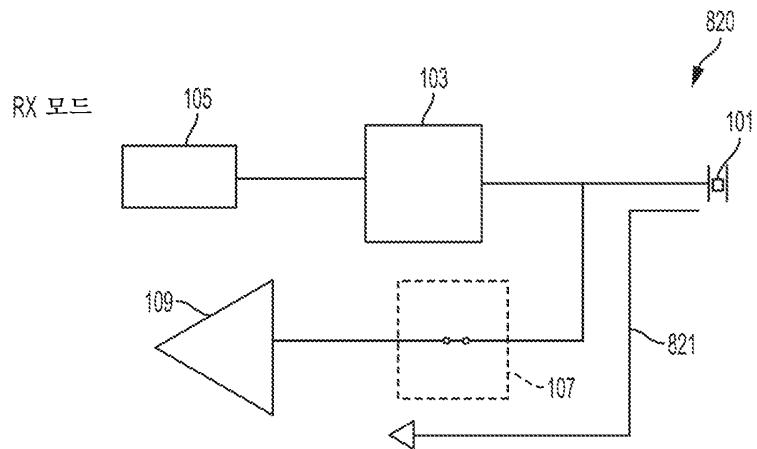

- 도 8b는 본 출원의 비-제한적인 실시예에 따라, 수신 모드에서 동작하는 초음파 디바이스를 도시하는 블록도이다.

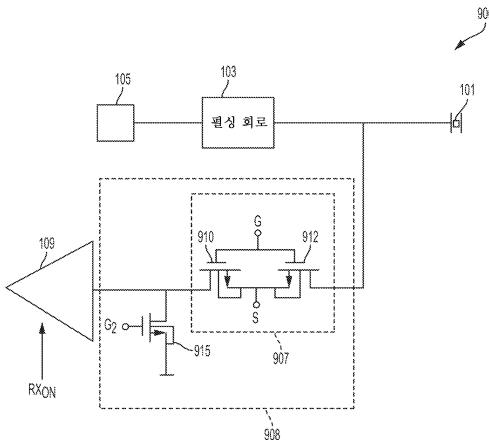

- 도 9는 본 출원의 비-제한적인 실시예에 따라, 대칭 스위치를 포함하는 초음파 디바이스를 도시하는

블록도이다.

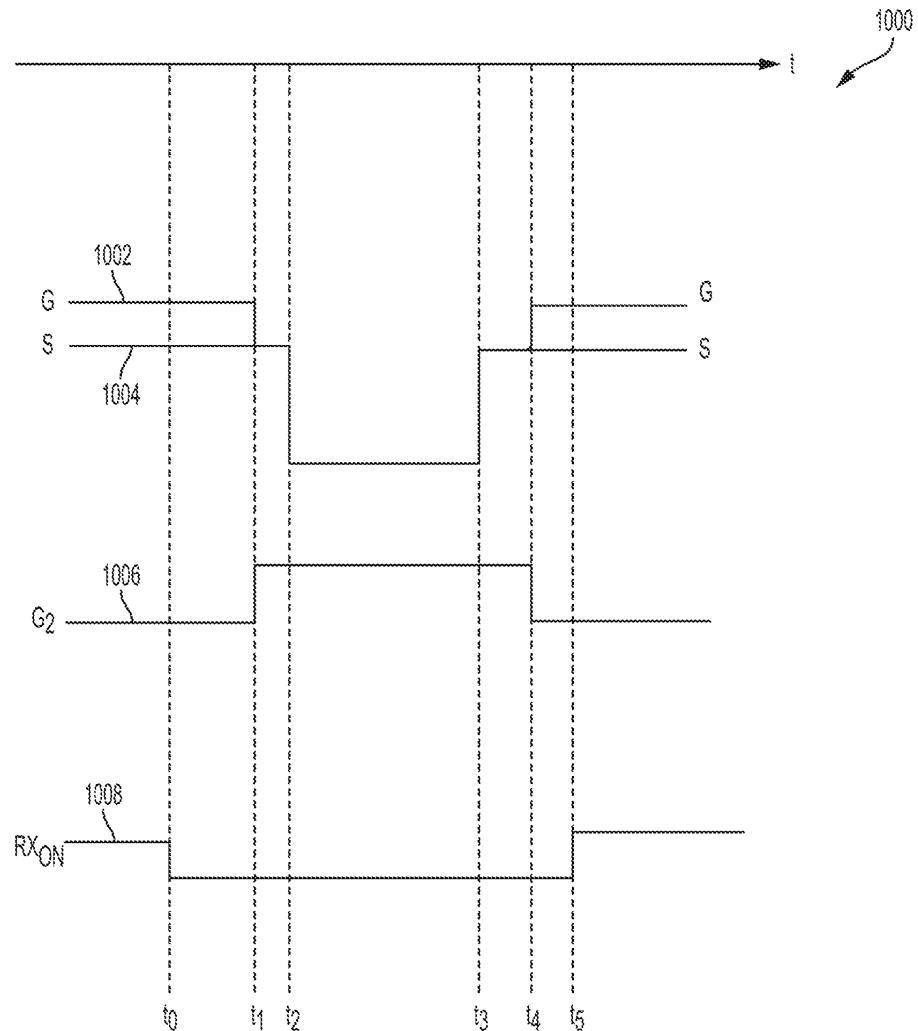

도 10은 본 출원의 비-제한적인 실시예에 따라, 도 9의 대칭 스위치를 구동하도록 구성되는 제어 신호들을 도시하는 타이밍도를 도시한다.

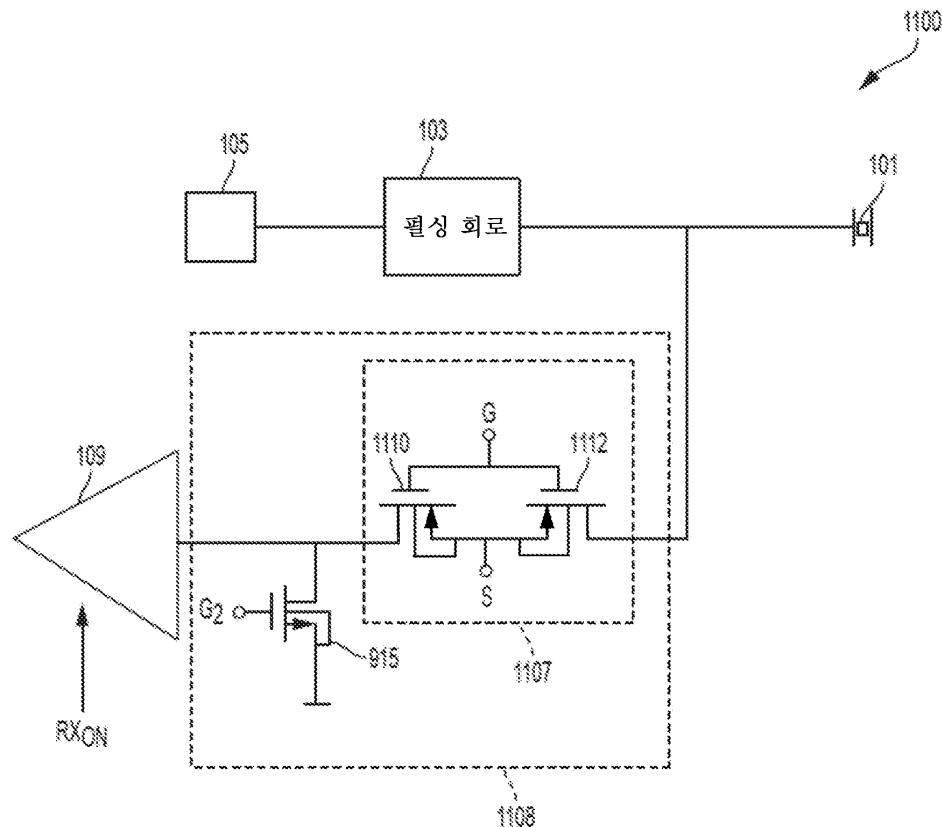

도 11은 본 출원의 비-제한적인 실시예에 따라, 대칭 스위치를 포함하는 대안적인 디바이스들을 나타내는 블록도이다.

### 발명을 실시하기 위한 구체적인 내용

[0010]

초음파-온-칩 디바이스는 본 명세서에서 "칩"으로도 지칭되는 반도체 다이 상의 회로와 통합된 초음파 트랜스듀서들을 포함할 수 있다. 초음파-온-칩 디바이스는 초음파 이미징, 테라피[예를 들어, 고강도 집중 초음파(HIFU)] 또는 둘 다를 수행하기 위해 초음파 프로브 내에서 이용될 수 있다. 따라서, 초음파 트랜스듀서들과 통합된 회로는 그러한 기능들을 지원할 수 있고, 프로브, 또는 청진기와 같은 다른 폼 팩터에서 사용되기에 적절한 형태를 취할 수 있다. 회로는 이미징 및/또는 HIFU에 적절한 초음파 신호들을 발생시키기 위해 초음파-온-칩 디바이스의 초음파 트랜스듀서들을 구동하는 데 사용되는 전기 펄스들을 발생시키는 펄싱 회로들을 포함할 수 있다. 펄싱 회로들은 디지털, 아날로그, 또는 혼합 아날로그-디지털일 수 있다.

[0011]

본 출원의 양태들은 피드백을 갖는 양극성 멀티레벨 펄싱 회로들을 제공한다. 본 출원인은 단극성 펄스들을 송신하도록 구성된 초음파 디바이스들이, 단극성 펄스에 연관된 직류(DC) 성분이 수신 회로를 포화시킬 수 있고, 따라서 생성되는 이미지의 콘트라스트를 열화시키는 것으로 인해 제한된 동적 범위를 나타낸다는 것을 인식했다. 단극성 펄스들은 제로(0) 이상의 전압들, 또는 대안적으로는 제로(0) 이하의 전압들만을 취하는 것들이다. 대조적으로, 본 출원인은 양극성 펄스들의 사용이 DC 성분의 영향을 제한하고, 따라서 단극성 펄스들을 이용하는 초음파 디바이스들에 비교하여 현저히 증가된 동적 범위 및 이미지 콘트라스트를 제공한다는 것을 인식했다. 따라서, 본 출원의 양태들은 양극성 펄스들을 송신하도록 구성되는 초음파 디바이스들을 제공한다. 양극성 펄스들은 제로(0)보다 크거나 제로보다 작거나 제로와 동일한 전압들을 취할 수 있다.

[0012]

초음파 이미지들의 콘트라스트는 이미징되는 타겟에 송신되는 펄스들의 시간 영역 및 공간 영역 아포다이즈(time-domain and space-domain apodization)를 수행함으로써 현저하게 향상될 수 있다는 본 출원인의 인식으로부터, 피드백을 갖는 멀티레벨 펄싱 회로들의 사용이 발생한다. 아포다이즈는 송신된 펄스들에 연관된 사이드 로브들(side-lobes)의 범위를 감소시킬 수 있고, 따라서 생성되는 이미지의 해상도를 증가시킨다. 시간적 및 공간적으로 아포다이즈된 펄스들의 발생은 복수의 값을 취할 수 있는 신호들을 제어하는 능력에 의해 용이해질 수 있다. 본 명세서에 설명되는 유형의 멀티레벨 펄스들은 선택가능한 값들의 세트 중에서 선택된 임의의 값을 취할 수 있고, 여기서 세트는 적어도 3개의 값을 포함할 수 있다. 이러한 멀티레벨 펄스들의 발생은 복수의 공급 전압이 제공되는 복잡한 펄서 설계들을 요구할 수 있다. 복수의 공급 전압을 제공하는 것은 비현실적일 수 있다. 초음파 디바이스가 핸드헬드형 초음파 프로브 또는 다른 컴팩트한 형태로 배치되어야 할 때 특히 그러할 수 있는데, 왜냐하면 추가의 오프 칩 공급 회로들이 요구될 수 있기 때문이다. 본 출원인은 피드백 회로들의 사용이 복수의 공급 전압에 의존하지 않고서 멀티레벨 펄스들의 발생 및 아포다이즈된 펄스들의 발생을 용이하게 할 수 있고, 따라서 초음파 디바이스의 설계를 단순화할 수 있음을 인식했다.

[0013]

본 출원의 양태들은 초음파 트랜스듀서를 수신 회로에 연결하는 대칭 스위치를 포함하는 초음파 디바이스들을 제공한다. 양극성 펄싱 회로들의 사용은 적어도 위에서 설명된 이유들로 이로울 수 있지만, 이것들은 또한 초음파 디바이스의 수신 회로에 해로울 수 있다. 송신 회로에 의해 발생되는 펄스들은 큰 포지티브 및 네거티브 전압 스파이크들을 견디도록 설계되어 있지 않을 수 있는 수신 회로에 우연히 전기적으로 직접 연결될 수 있다. 결과적으로, 적절한 보호가 제공되지 않으면 초음파 디바이스가 손상될 수 있다. 본 출원인은 양극성 펄스들에 연관된 포지티브 및 네거티브 전압 스파이크들을 차단하도록 설계된 적절히 위치된 대칭 스위치가 수신 회로에 대한 손상을 방지할 수 있고, 따라서 초음파 디바이스를 보호하고 양극성 펄싱 회로들의 사용을 용이하게 할 수 있음을 인식하였다.

[0014]

위에서 설명된 CMOS 회로 특징들은 상업적으로 가치있는 폼 팩터로 초음파 이미징 및/또는 HIFU를 수행하기에 적절한 초음파-온-칩 디바이스를 생성하는 것을 용이하게 할 수 있다.

[0015]

위에서 설명된 양태들 및 실시예들은 물론, 추가의 양태들 및 실시예들이 이하에서 더 설명된다. 이러한 양태들 및/또는 실시예들은 개별적으로, 모두 함께, 또는 둘 이상의 임의의 조합으로 사용될 수 있으며, 이는 본 출원이 이러한 점에서 제한되지 않기 때문이다.

- [0016] 위에서 설명된 바와 같이, 본 출원의 양태들은 양극성 멀티레벨 펄싱 회로, 및 양극성 멀티레벨 펄싱 회로를 수신 회로에 연결하는 대칭 스위치를 갖는 초음파 디바이스를 제공한다. 도 1은 본 출원의 양태들에 따른 그러한 특징들을 포함할 수 있는 초음파 디바이스의 일반적인 아키텍처를 도시한다. 초음파 디바이스(100)는 복수의 용량성 초음파 트랜스듀서( $101_1 \cdots 101_N$ )를 가지며, 여기서 N은 정수이다. 초음파 디바이스(100)는 복수의 회로 채널( $102_1 \cdots 102_N$ )을 포함할 수 있다. 회로 채널들( $102_1 \cdots 102_N$ )은 각각의 용량성 초음파 트랜스듀서( $101_1 \cdots 101_N$ )에 전기적으로 접속될 수 있다. 초음파 디바이스(100)는 아날로그-디지털 변환기(ADC)(111)를 추가로 포함할 수 있다.

- [0017] 일부 실시예들에서, 용량성 초음파 트랜스듀서들은 수신된 초음파 신호들을 표현하는 전기 신호들을 생성하는 센서들이다. 일부 실시예들에서, 용량성 초음파 트랜스듀서들은 또한 초음파 신호들을 송신할 수 있다. 일부 실시예들에서, 용량성 초음파 트랜스듀서들은 용량성 마이크로머시닝 초음파 트랜스듀서들(CMUT: capacitive micromachined ultrasonic transducer)일 수 있다. 그러나, 다른 실시예들에서, 다른 유형들의 용량성 초음파 트랜스듀서들이 사용될 수 있다.

- [0018] 회로 채널들( $102_1 \cdots 102_N$ )은 송신 회로, 수신 회로 또는 둘 다를 포함할 수 있다. 송신 회로는 각각의 펄싱 회로들( $103_1 \cdots 103_N$ )에 연결된 송신 디코더들( $105_1 \cdots 105_N$ )을 포함할 수 있다. 펄싱 회로들( $103_1 \cdots 103_N$ )은 초음파 신호들을 방출하도록 각각의 초음파 트랜스듀서들( $101_1 \cdots 101_N$ )을 제어할 수 있다.

- [0019] 본 출원의 양태들은 펄싱 회로들( $103_1 \cdots 103_N$ )에 관한 것이다. 일부 실시예들에서, 펄싱 회로들( $103_1 \cdots 103_N$ )은 양극성 펄스들을 발생시키도록 구성될 수 있다. 일부 실시예들에서, 펄싱 회로들( $103_1 \cdots 103_N$ )은 멀티레벨 펄스들을 발생시키도록 구성될 수 있다. 아래에 더 설명되는 바와 같이, 일부 실시예들에서, 펄싱 회로들( $103_1 \cdots 103_N$ )은 펄서들에 추가 회로를 더한 것을 포함할 수 있다. 일부 실시예들에서, 펄싱 회로들( $103_1 \cdots 103_N$ )은 펄서들 및 피드백 회로를 포함할 수 있다.

- [0020] 회로 채널들( $102_1 \cdots 102_N$ )의 수신 회로는 각각의 용량성 초음파 트랜스듀서들( $101_1 \cdots 101_N$ )로부터 출력된 전기 신호들을 수신할 수 있다. 도시된 예에서, 각각의 회로 채널( $102_1 \cdots 102_N$ )은 각각의 수신 스위치( $107_1 \cdots 107_N$ ), 및 수신 회로( $109_1 \cdots 109_N$ )를 포함한다. 수신 스위치들( $107_1 \cdots 107_N$ )은 주어진 초음파 트랜스듀서( $101_1 \cdots 101_N$ )로부터의 전기 신호의 판독을 활성화/비활성화하도록 제어될 수 있다. 수신 회로들( $109_1 \cdots 109_N$ )은 전류-전압 변환기들을 포함할 수 있다. 전류-전압 변환기들은 트랜스-임피던스 증폭기들(TIA)을 포함할 수 있으며, 그 이유로 인해, 수신 회로들( $109_1 \cdots 109_N$ )이 TIA들로서 도시되지만, 추가적인 및/또는 대안적인 회로가 수신 회로를 구성할 수 있다.

- [0021] 본 출원의 양태들은 수신 스위치들( $107_1 \cdots 107_N$ )에 관한 것이다. 일부 실시예들에서, 수신 스위치들( $107_1 \cdots 107_N$ )은 포지티브 및/또는 네거티브 전압들을 나타내는 전압 스파이크들을 차단하도록 구성되는 대칭 스위치들을 포함할 수 있다. 수신 스위치들( $107_1 \cdots 107_N$ )은 송신 모드 동안 수신 회로를 송신 회로로부터, 그리고 용량성 초음파 트랜스듀서로부터 전기적으로 분리하기 위해 개방 회로를 형성하도록 구성될 수 있다. 수신 스위치들( $107_1 \cdots 107_N$ )은 수신 모드 동안 수신 회로를 용량성 초음파 트랜스듀서에 전기적으로 연결하기 위한 단락 회로를 형성하도록 더 구성될 수 있다.

- [0022] 초음파 디바이스(100)는 ADC(111)를 추가로 포함할 수 있다. ADC(111)는 용량성 초음파 트랜스듀서들( $101_1 \cdots 101_N$ )에 의해 수신되는 신호들을 디지털화하도록 구성될 수 있다. 다양한 수신된 신호들의 디지털화는 직렬 또는 병렬로 수행될 수 있다. 단일 ADC가 도시되어 있고, 따라서 복수의 회로 채널에 의해 공유되는 것으로 보여지지만, 대안적인 실시예들은 회로 채널 당 하나의 ADC를 제공한다.

- [0023] 도 1은 초음파 디바이스의 회로의 일부로서 다수의 컴포넌트를 도시하지만, 본 명세서에 설명된 다양한 양태들은 도시된 컴포넌트들의 정확한 컴포넌트들 또는 구성에 한정되지 않는다는 것을 알아야 한다.

- [0024] 도 1의 컴포넌트들은 단일 기판 상에 또는 상이한 기판들 상에 위치될 수 있다. 단일 기판 상에 위치될 때, 기판은 일례로서 실리콘 기판과 같은 반도체 기판일 수 있고, 컴포넌트들은 그 위에 모듈리식 집적될 수 있다.

도시된 컴포넌트들이 동일한 기판 상에 있지 않을 때, 용량성 초음파 트랜스듀서들( $101_1 \cdots 101_N$ )은 제1 기판 상에 있을 수 있고, 나머지 도시된 컴포넌트들은 예로서 제2 기판 상에 있을 수 있다. 다른 대안으로서, 초음파 트랜스듀서들 및 도시된 회로의 일부는 동일한 기판 상에 있을 수 있는 한편, 다른 회로 컴포넌트들은 상이한 기판 상에 있을 수 있다. 복수의 기판이 사용될 때, 그것들은 실리콘 기판들과 같은 반도체 기판들일 수 있다.

[0025] 실시예에 따르면, 도 1의 컴포넌트들은 초음파 프로브의 일부를 형성한다. 초음파 프로브는 핸드헬드형일 수 있다. 일부 실시예들에서, 도 1의 컴포넌트들은 환자가 착용하도록 구성되는 초음파 패치의 일부를 형성한다.

[0026] 일부 비-제한적인 실시예들에 따라, 도 2는 도 1의 펄싱 회로들( $103_1 \cdots 103_N$ ) 중 임의의 것으로서 기능할 수 있는 펄싱 회로( $103$ )의 예를 도시한다. 일부 실시예들에서, 펄싱 회로( $103$ )는 펄서( $220$ ) 및 피드백 회로( $230$ )를 포함할 수 있다. 펄싱 회로( $103$ )는 용량성 초음파 트랜스듀서( $101$ )에 전기적으로 접속된 출력 단자를 가질 수 있고, 용량성 초음파 트랜스듀서( $101$ )에 입력 신호( $240$ )를 제공하도록 구성될 수 있다. 일부 실시예들에서, 펄서( $220$ )는 제로에 추가하여, 포지티브 및/또는 네거티브 값들을 취할 수 있는 양극성 펄스들을 발생시키도록 구성될 수 있다. 양극성 펄스들을 발생시킴으로써, 펄서( $220$ )는 펄스들에 연관된 임의의 DC 성분을 감소시키거나 억제할 수 있다. 앞에서 언급된 바와 같이, DC 성분들을 갖는 송신 펄스들은 초음파 디바이스( $100$ )에 의해 생성되는 이미지의 품질을 저하시킬 수 있다. 따라서, 통과대역 성분과 비교하여, DC 성분들은 이미징되는 매질을 통해 전파되는 동안 현저히 덜 감쇠될 수 있다. 결과적으로, 수신 회로는 통과대역 성분보다 현저하게 큰 DC 성분을 갖는 신호를 수신할 수 있다. 결과적으로, 수신 회로가 포화될 수 있고, 따라서 이미지의 동적 범위를 제한할 수 있다.

[0027] 일부 실시예들에서, 피드백 회로는 멀티레벨 펄스들을 발생시키기 위해 펄서를 제어하도록 구성될 수 있다. 본 명세서에 설명된 유형의 멀티레벨 펄스들은 선택가능한 값들의 세트 중에서 선택된 임의의 값을 취할 수 있고, 여기서 세트는 적어도 3개의 값을 포함할 수 있으며, 적어도 일부 실시예들에서는 4개 이상의 값(예를 들어, 3 내지 30개의 값, 4 내지 20개의 값, 4 내지 10개의 값, 또는 그러한 범위들 내의 임의의 개수)을 포함할 수 있다. 멀티레벨 펄스들의 사용은 형성되는 초음파 이미지의 파라미터를 최대화하기 위해 펄스의 엔벨로프의 최적화를 가능하게 할 수 있다. 예를 들어, 펄스들의 엔벨로프는 이미지 콘트라스트를 최대화하도록 엔지니어링될 수 있다. 구체적으로, 시간 영역 아포다이즈를 사용하면, 펄스들의 결과적인 주파수 콘텐츠는 큰 메인 로브 및 억제된 사이드 로브들을 나타낼 수 있고, 따라서 이미징 해상도를 증가시킨다. 시간 영역 아포다이즈는 거의 연속적인 원도우 함수들을 생성하기 위해 가능한 한 많은 전압 레벨을 나타내는 펄스들을 요구한다. 그러나, 다수의 레벨을 갖는 펄스들의 발생은 복잡한 펄싱 회로들을 요구할 수 있다. 그러므로, 레벨들의 수는 펄싱 회로들을 비교적 간단하고 컴팩트하게 유지하면서 시간 영역 아포다이즈를 수행할 수 있는 능력을 최대화할 수 있도록 선택되어야 한다. 일부 실시예들에서, 펄서( $220$ )는 3 내지 30 레벨, 5 내지 10 레벨, 또는 임의의 적절한 값 또는 값들의 범위 사이를 갖는 멀티레벨 펄스들을 발생시키도록 구성될 수 있다.

[0028] 멀티레벨 펄스들의 사용은 또한 공간 영역 아포다이즈를 가능하게 할 수 있다. 공간 영역 아포다이즈를 수행하기 위해, 다양한 용량성 초음파 트랜스듀서들은 공간 의존 진폭들을 갖는 입력 신호들로 구동되어야 할 것이다. 공간 의존 진폭들을 갖는 입력 신호들의 제공은 복수의 기준 전압에 대한 액세스를 갖는 것에 의해 용이해질 수 있다.

[0029] 일부 실시예들에서, 피드백 회로( $230$ )는 멀티레벨 펄스 발생을 용이하게 하도록 구성될 수 있다. 구체적으로, 피드백 회로( $230$ )는 복수의 기준 전압을 제공하도록 구성될 수 있다. 앞에서 언급된 바와 같이, 본 명세서에 설명된 유형의 피드백 회로들의 사용은 복수의 공급 전압에 의지하지 않는 멀티레벨 펄서들의 설계를 용이하게 할 수 있다. 일부 실시예들에서, 핸드헬드 품 팩터에 맞추기가 어려울 수 있는 상당한 크기의 초음파 프로브들을 야기할 수 있는 복수의 공급 전압을 포함하는 것이 바람직하지 않을 수 있다. 반대로, 본 명세서에 설명된 유형의 피드백 회로들은 기준 전압들을 발생시키기 위한 컴팩트한 회로를 제공할 수 있으며, 핸드헬드형 초음파 프로브들에 쉽게 포함될 수 있다.

[0030] 피드백 회로( $230$ )의 출력 단자는 펄서( $220$ )의 입력 단자에 전기적으로 연결될 수 있다. 피드백 회로( $230$ )의 입력 단자는 펄서( $220$ )의 출력 단자에 전기적으로 연결될 수 있다. 피드백 회로( $230$ )의 입력 단자는 입력 신호( $240$ )를 표현하는 검출 신호( $241$ )를 수신하도록 구성될 수 있다. 일부 실시예들에서, 입력 신호( $240$ ) 및 검출 신호( $241$ )는 전압이다. 일부 실시예들에서, 검출 신호( $241$ )는 입력 신호( $240$ )로부터 유도될 수 있다. 일부 실시예들에서, 검출 신호( $241$ )는 입력 신호( $240$ )에 비례할 수 있다. 피드백 회로( $230$ )는 검출 신호( $241$ )를 임계 전압에 비교할 수 있다. 일부 실시예들에서, 상기 임계 전압은 선택가능한 임계 전압들의 세트 중에서 선택될

수 있다.

[0031] 비교의 결과에 기초하여, 피드백 회로(230)는 제어 신호(242)를 펠서(220)의 입력 단자에 제공할 수 있다. 일부 실시예들에서, 피드백 회로(230)는 검출 신호(241)가 임계 전압보다 큰지, 임계 전압보다 작은지, 또는 임계 전압과 동일한지를 결정하도록 구성될 수 있다. 일부 실시예들에서, 피드백 회로(230)는 검출 신호(241)가 임계 전압의 범위 내에, 예컨대 임계 전압의 10% 이내, 임계 전압의 5% 이내, 또는 임의의 적절한 범위 내에 있는지를 결정하도록 구성될 수 있다. 임계 전압에 대한 검출 신호(241)의 값에 기초하여, 피드백 회로(230)는 입력 신호(240)의 현재 값을 유지하거나 입력 신호(240)를 변화시키도록 펠서(220)를 제어할 수 있다. 제한이 아닌 예로서, 검출 신호(241)의 값이 임계 전압보다 작으면, 피드백 회로(230)는 검출 신호(241)가 임계 전압과 동일하거나 임계 전압의 범위 내에 있을 때까지 입력 신호(240)의 값을 증가시키도록 펠서(220)를 제어할 수 있다. 검출 신호(241)의 값이 임계 전압보다 큰 경우, 피드백 회로(230)는 검출 신호(241)가 임계 전압과 동일하거나 임계 전압의 범위 내에 있을 때까지 입력 신호(240)의 값을 감소시키도록 펠서(220)를 제어할 수 있다.

[0032] 일부 실시예들에서, 용량성 초음파 트랜스듀서(101)에 연관된 커패시턴스는 검출 신호(241)가 선택된 임계 전압에 도달할 때 그것의 단자를 양단에 걸쳐 일정한 전압을 유지하기 위해 전하를 보유할 수 있다. 검출 신호(241)가 임계 전압보다 낮을 때, 펠서(220)는 용량성 초음파 트랜스듀서(101)에 연관된 커패시턴스를 충전하도록 제어될 수 있고, 따라서 입력 신호(240)를 증가시킨다. 검출 신호(241)가 임계 전압보다 클 때, 펠서(220)는 용량성 초음파 트랜스듀서(101)에 연관된 관련된 커패시턴스를 방전시키거나 네거티브로 충전하도록 제어될 수 있고, 따라서 입력 신호(240)를 감소시킨다.

[0033] 일부 실시예들에서, 피드백 회로(230)는 펠서(220)를 비동기식으로 제어할 수 있다. 따라서, 제어 신호(242), 입력 신호(240) 및 검출 신호(241)는 임의의 순간에 변경되도록 허용될 수 있다. 일부 실시예들에서, 펠싱 회로(100)는 클록 신호에 의해 타이밍이 정해질 수 있다. 그러나, 제어 신호(242)는 여전히 클록 신호에 의해 정의되지 않는 기간들 동안 변경되도록 허용될 수 있다.

[0034] 일부 실시예들에서, 용량성 초음파 트랜스듀서(101)는 바이어스 회로(도시되지 않음)에 연결될 수 있으며, 0보다 큰 절대값을 갖는 바이어스 전압을 수신하도록 구성될 수 있다. 바이어스 전압은 10V 내지 100V, 30V 내지 80V, 또는 임의의 적절한 값들 또는 값들의 범위 사이의 절대값을 가질 수 있다. 일부 실시예들에서, 용량성 초음파 트랜스듀서들을 바이어싱하면 증가된 선형도(degrees of linearity)를 나타내는 응답들을 초래할 수 있다.

[0035] 도 3은 도 2의 펠싱 회로의 비-제한적인 상세한 구현예이다. 일부 실시예들에서, 펠서(220)는 322 및 324와 같은 2개의 트랜지스터를 포함할 수 있다. 그러나, 펠서(220)는 이러한 점에서 제한되지 않으며, 임의의 적절한 수의 트랜지스터가 사용될 수 있다. 트랜지스터들은 금속 산화물 반도체 전계 효과 트랜지스터(MOSFET), 접합 전계 효과 트랜지스터(JFET), 양극성 접합 트랜지스터(BJT), 금속 반도체 전계 효과 트랜지스터(MESFET), 절연 게이트 전계 효과 트랜지스터(IGFET), 측면 확산형 금속 산화물 반도체 트랜지스터(LDMOS), 또는 이들의 임의의 적절한 조합을 포함할 수 있다. 펠서(220)는 트랜지스터(322) 및 트랜지스터(324)를 포함할 수 있다. 트랜지스터(322)는 트랜지스터(324)의 전도성 유형과 다른 한 유형의 전도성을 가질 수 있다. 예를 들어, 트랜지스터(322)는 전계 효과 하에서 이동하는 홀들에 의해 유지되는 드리프트 전류들에 기초하는 전도성을 가질 수 있다. 트랜지스터(324)는 전계 효과 하에서 이동하는 전자들에 의해 유지되는 드리프트 전류들에 기초하는 전도성을 가질 수 있다. 일부 실시예들에서, 트랜지스터(324)는 nMOSFET일 수 있고, 트랜지스터(322)는 pMOSFET일 수 있다. 트랜지스터들은 nMOS 트랜지스터(324)의 드레인이 pMOS 트랜지스터(322)의 드레인에 접속되도록 구성될 수 있다. 드레인들은 용량성 초음파 트랜스듀서(101)의 단자에 더 접속될 수 있다. nMOS 트랜지스터(324)의 소스는 공급 전압( $V_N$ )에 접속될 수 있다. 일부 실시예들에서,  $V_N$ 은 0보다 작을 수 있다.  $V_N$ 은 -100V 내지 -1V, -50V 내지 -20V, 또는 임의의 적절한 값들 또는 값들의 범위 사이일 수 있다. pMOS 트랜지스터(322)의 소스는 공급 전압( $V_P$ )에 접속될 수 있다. 일부 실시예들에서,  $V_P$ 는 제로보다 클 수 있다.  $V_P$ 는 1V 내지 100V, 20V 내지 50V, 또는 임의의 적절한 값들 또는 값들의 범위 사이일 수 있다. 트랜지스터들(322 및 324)의 게이트들에 제공된 전압들은 도 2의 피드백 회로(230)에 의해 발생될 수 있다.

[0036] 일부 실시예들에서, 피드백 회로(230)는 제어기(336), 분할 회로(332), 및 기준 발생기(334)를 포함할 수 있다. 일부 실시예들에서, 피드백 회로(230)는 레벨 시프터(338) 및 레벨 시프터(340)를 추가로 포함할 수 있다. 분할 회로(332)는 입력 신호(240)에 대응하는 전압을 수신하고, 검출 신호(341)를 출력하도록 구성될 수 있다. 분할 회로(332)는 입력 신호(240)에 비례하는 검출 신호(341)를 제공하도록 구성될 수 있다. 검출 신호(341)는

"In"으로 라벨링된 입력 단자를 통해 제어기(336)에 제공될 수 있다.

[0037] 기준 발생기(334)는 제어기(336)의 "Ref"로 라벨링된 단자에 선택가능한 임계 전압들의 세트를 제공하도록 구성될 수 있다. 일부 실시예들에서, 기준 발생기(334)는 n개의 커넥터를 통해 제어기(336)에 접속되고, 대응하는 커넥터들을 통해 n개의 임계 전압을 제공하도록 구성되며, 여기서 n은 2보다 큰 임의의 적절한 값을 취할 수 있다. 임계 전압들은 제로와 동일할 수 있거나 제로보다 클 수 있거나 제로보다 작을 수 있다.

[0038] 일부 실시예들에서, 피드백 회로(230)는 디지털 방식으로 제어될 수 있고, 제어기(336)는 디지털 제어기를 포함할 수 있다. 제어기(336)는 검출 신호(341)를 n개의 임계 전압 중에서 선택된 임계 전압에 비교한 것에 기초하여, 입력 신호(240)에 대응하는 전압을 유지, 증가 또는 감소시키기 위해 필터(220)를 제어하도록 구성될 수 있다. 제어기(336)는 기준 발생기(334)에 의해 제공된 n개의 임계 전압으로부터 임계 전압을 선택할 수 있다. 임계 전압은 신호  $sel\_threshold$ 를 통해 디지털 방식으로 선택될 수 있다. 신호  $sel\_threshold$ 는 m 비트를 포함할 수 있으며, 여기서 m은 n이  $2^m$ 과 동일하거나 그보다 작게 하는 것이다. 각각의 비트 조합은 n개의 임계 전압으로부터 하나의 임계 전압을 선택할 수 있다. 제한이 아닌 예로서, 000과 동일한  $sel\_threshold$  시퀀스는 8개의 임계 전압 중 가장 작은 것을 선택할 수 있고, 111과 동일한  $sel\_threshold$  시퀀스는 8개의 임계 전압 중 가장 큰 것을 선택할 수 있다. 또한, 신호  $sel\_threshold$ 는 비동기식으로 변경될 수 있다.

[0039] 일부 실시예들에서, 분할 회로(332)는 스케일링 인자에 의해 입력 신호(240)에 비례하는 검출 신호(341)를 제공할 수 있다. 그러한 실시예들에서, 기준 발생기(334)는 동일한 스케일링 인자에 의해 입력 신호(240)에 대해 스케일링되는 임계 전압들의 세트를 제공하도록 구성될 수 있다. 결과적으로, 검출 신호(341)는 2개의 신호 중 하나를 더 스케일링할 필요없이, 선택된 임계 전압과 직접 비교될 수 있다.

[0040] 일부 실시예들에서, 신호  $p/n$ 은 트랜지스터들(322 및 324)의 상태를 제어하기 위해 사용될 수 있다. 일부 실시예들에서,  $p/n$ 은 단일 비트 신호일 수 있다. 신호  $p/n$ 은 트랜지스터(322)를 활성화하기 위해 "p"로 설정되거나, 트랜지스터(324)를 활성화하기 위해 "n"으로 설정될 수 있다. 그러나, 트랜지스터들(322 및 324)의 상태를 제어하도록 구성되는 임의의 적절한 수의 비트가 또한 사용될 수 있다. 단일 비트의 값은 트랜지스터(322) 또는 트랜지스터(324) 중 어느 하나가 선형 모드인지 또는 포화 모드인지에 관계없이 전도 상태로 변하게 할 수 있다. 그러한 실시예에서, 한 번에 하나의 트랜지스터만이 전도 상태로 설정될 수 있다.

[0041]  $sel\_threshold$  및  $p/n$ 의 값에 기초하여, 제어기(336)는 "N\_control" 및 "P\_control"로 라벨링된 출력 단자들을 통해 제어 신호들( $242_p$  및  $242_N$ )을 출력할 수 있다. 제어 신호들( $242_p$  및  $242_N$ )은 함께, 도 2에 도시된 제어 신호(242)를 표현할 수 있다. 일부 실시예들에서, 신호( $242_p$ )는 pMOS 트랜지스터(322)의 상태를 제어하도록 구성되는 단일 비트를 포함할 수 있다. 일부 실시예들에서, 신호( $242_N$ )는 nMOS 트랜지스터(324)의 상태를 제어하도록 구성되는 단일 비트를 포함할 수 있다. 2개의 트랜지스터가 동시에 컷오프 상태에 있도록 허용될 수 있다.

[0042] 일부 실시예들에서, 제어 신호들( $242_p$  및  $242_N$ )은 각각 트랜지스터들(322 및 324)의 게이트들을 직접 구동할 수 있다. 다른 실시예들에서, 도 3에 도시된 바와 같이, 제어 신호들( $242_p$  및  $242_N$ )은 각각 레벨 시프터(338) 및 레벨 시프터(340)의 입력 단자들에 연결될 수 있다. 레벨 시프터(338) 및 레벨 시프터(340)의 출력 단자들은 각각 트랜지스터들(322 및 324)의 게이트들에 연결될 수 있다. 레벨 시프터들(338) 및 레벨 시프터(340)는 신호들( $242_p$  및  $242_N$ )에 기초하여 트랜지스터들을 그것들의 컷오프 또는 전도 상태로 구동하기 위해, 제어기(336)에 의해 발생된 전압들을 트랜지스터들(322 및 324)에 호환가능한 전압들에 적응시키도록 구성될 수 있다.

[0043] 검출 신호(341)가 선택된 임계 전압보다 낮을 때, 제어기(336)는 pMOS 트랜지스터(322)를 전도 상태로 전환하고 nMOS(324) 트랜지스터를 컷오프 상태로 전환하기에 적절한 값들로 제어 신호들( $242_p$  및  $242_N$ )을 출력하도록 구성될 수 있다. 이 경우, 전압 공급부( $V_p$ )로부터 용량성 초음파 트랜스듀서(101)로 흐르는 전류는 검출 신호(341)가 선택된 임계 전압, 또는 선택된 임계 전압의 미리 결정된 범위에 도달할 때까지 용량성 초음파 트랜스듀서(101)를 충전할 수 있다.

[0044] 검출 신호(341)가 선택된 임계 전압보다 큰 경우, 제어기(336)는 nMOS 트랜지스터(324)를 전도 상태로 전환하고 pMOS 트랜지스터(322)를 컷오프 상태로 전환하기에 적절한 값들로 제어 신호들( $242_p$  및  $242_N$ )을 출력하도록 구성될 수 있다. 이 경우, 용량성 초음파 트랜스듀서(101)로부터 전압 공급부( $V_N$ )로 흐르는 전류는, 검출 신호(341)가 선택된 임계 전압, 또는 선택된 임계 전압의 미리 결정된 범위에 도달할 때까지 용량성 초음파 트랜스

듀서(101)를 방전시키거나 네거티브로 충전할 수 있다.

[0045] 검출 신호(241)가 선택된 임계 전압과 동일하거나 선택된 임계 전압의 미리 결정된 범위 내에 있을 때, pMOS 트랜지스터(322) 및 nMOS 트랜지스터(324)는 둘 다 컷오프 상태로 전환되도록 신호들( $242_p$  및  $242_n$ )을 통해 제어될 수 있다. 이 경우, 용량성 초음파 트랜스듀서(101)로, 또는 용량성 초음파 트랜스듀서로부터 전류가 흐르지 않을 것이다. 결과적으로, 용량성 초음파 트랜스듀서(101)는 전기 전하를 보유할 수 있고, 따라서 그것의 단자들 양단에서 선택된 임계 전압에 대응하는 타겟 전압을 유지할 수 있다.

[0046] 위에서 설명된 바와 같이, 적어도 일부 실시예들에서는, 초음파 트랜스듀서들(101)이 그들의 전하를 유지하는 것이 바람직할 수 있기 때문에, 그러한 실시예들에서 초음파 트랜스듀서들은 용량성일 수 있다. 대조적으로, 저항성 초음파 트랜스듀서들의 사용은 그러한 상황들에서 제대로 동작하지 않을 수 있다.

[0047] 제어기(336)는 도 3과 관련하여 설명된 비-제한적인 실시예에서 신호들  $p/n$  및  $sel\_threshold$ 에 기초하여 펠서(220)를 제어하도록 구성될 수 있지만, 펠싱 회로(103)는 이러한 점에서 제한되지 않는다. 따라서, 임계 전압 또는 임계 전압의 범위가 도달될 때까지 입력 신호(240)를 유지, 증가 또는 감소시키기 위해 펠서(220)를 제어하도록 구성되는 임의의 신호 또는 신호들의 조합이 또한 사용될 수 있다.

[0048] 도 4는 일부 비-제한적인 실시예에 따라 용량성 초음파 디바이스를 구동하기 위해 펠싱 회로를 동작시키는 방법을 도시한다. 도 4의 방법은 도 2의 펠싱 회로 또는 도 3의 펠싱 회로와 관련하여 수행될 수 있다. 방법(400)은  $n$ 개의 선택가능한 임계 전압들의 세트 중에서 임계 전압이 선택될 수 있는 동작(402)에서 시작하며, 여기서  $n$ 은 2보다 큰 임의의 적절한 값을 취할 수 있다. 일부 실시예들에서, 임계 전압은  $m$  비트를 갖는 디지털 신호를 통해 선택될 수 있으며, 여기서  $n$ 은  $2^m$ 과 동일하거나 그보다 작다.

[0049] 방법(400)은 동작(404)으로 계속되며, 여기서 입력 신호(240)와 같은 입력 신호는 펠서(220)에 의해 용량성 초음파 트랜스듀서(101)에 제공될 수 있다. 본 출원의 일 양태에 따르면, 펠서(220)는 포지티브 및/또는 네거티브 전압들을 나타낼 수 있는 양극성 입력 신호를 제공하도록 구성될 수 있다. 본 명세서에 설명된 유형의 양극성 입력 신호들은 초음파 디바이스의 수신 회로를 포화시키지 않는 반향 신호들을 초래할 수 있다.

[0050] 본 출원의 다른 양태에 따르면, 펠서(220)는 복수의 선택가능한 값 중에서 선택된 값들을 나타낼 수 있는 멀티레벨 펠스를 제공하도록 구성될 수 있다. 멀티레벨 펠스들을 발생시킬 수 있는 펠싱 회로들은 시간 영역 및 공간 영역 아포다이즈를 용이하게 할 수 있으며, 이는 향상된 이미지 콘트라스트를 초래할 수 있다. 본 명세서에 설명된 유형의 멀티레벨 펠스들의 발생은 핸드헬드형 초음파 프로브들을 더 크게 할 수 있는 추가의 전압 공급 회로들에 의지하지 않고서, 임계 전압들의 세트로부터 선택된 임계 전압을 제공하도록 설계된 피드백 회로들에 의해 용이해질 수 있다.

[0051] 동작(406)에서, 검출 신호(341)와 같은 검출 신호는 입력 신호(240)로부터 유도될 수 있다. 검출 신호(341)는 입력 신호(240)를 표현할 수 있다. 따라서, 검출 신호(341)는 입력 신호(240)와 동일하거나 입력 신호에 비례할 수 있다.

[0052] 동작(408)에서, 검출 신호(341)는 동작(402)에서 선택된 임계 전압에 비교될 수 있다. 일부 실시예들에서, 검출 신호(341)는 스케일링 인자에 의해 입력 신호(240)에 비례한다. 그러한 실시예들에서, 임계 전압은 동일한 스케일링 인자에 의해 입력 신호(240)에 스케일링될 수 있다. 비교의 결과로서, 검출 신호(341)는 임계 전압과 동일하거나, 임계 전압보다 크거나, 임계 전압보다 작을 수 있다.

[0053] 동작(410)에서, 동작(408)에서 수행된 비교의 결과에 기초하여, 입력 신호(240)를 제어하기 위해, 제어 신호(242)가 펠서(220)에 제공될 수 있다. 제어 신호는 피드백 회로(230)에 의해 제공될 수 있다. 피드백 회로(230)는 디지털 방식으로 제어될 수 있다. 동작(412)에서, 검출 신호(341)가 선택된 임계 전압보다 낮은 경우, 제어 신호(242)는 입력 신호(240)에 대응하는 전압을 증가시키기 위해 펠서(220)를 제어할 수 있다. 일부 실시예들에서, 제어 신호(242)는 용량성 초음파 트랜스듀서(101)에 연관된 커패시턴스를 충전하기 위해, pMOS 트랜지스터(322)를 전도 상태로 전환할 수 있다.

[0054] 동작(412)에서, 검출 신호(341)가 선택된 임계 전압보다 큰 경우, 제어 신호(242)는 입력 신호(240)에 대응하는 전압을 감소시키기 위해 펠서(220)를 제어할 수 있다. 일부 실시예들에서, 제어 신호(242)는 용량성 초음파 트랜스듀서(101)에 연관된 커패시턴스를 방전시키거나 네거티브로 충전하기 위해, nMOS 트랜지스터(324)를 전도 상태로 전환할 수 있다.

[0055] 어느 경우에서든, 방법(400)은 동작(406)으로 되돌아갈 수 있고, 방법(400)은 검출 신호(341)가 선택된 임계 전

압과 동일하거나 선택된 임계 전압의 미리 정의된 범위 내에 있을 때까지 반복될 수 있다.

[0056] 동작(412)에서, 검출 신호(341)가 선택된 임계 전압과 동일하거나 선택된 임계 전압의 미리 정의된 범위 내에 있는 것으로 밝혀지는 경우, 제어 신호(242)는 입력 신호(240)의 현재 값을 유지하기 위해 펠서(220)를 제어할 수 있다. 일부 실시예들에서, 용량성 초음파 트랜스듀서(101)에 연관된 커패시턴스가 전류 전하를 보유하는 것을 허용하기 위해, 제어 신호(242)는 nMOS 트랜지스터(324) 및 pMOS 트랜지스터(322)를 컷오프 상태로 전환할 수 있다. 미리 정의된 범위는 선택된 임계 전압의 10% 이내, 선택된 임계 전압의 5% 이내, 또는 임의의 적절한 범위 내로 정의될 수 있다.

[0057] 입력 신호(240)가 임계 전압에 대응하는 전압에 도달하면, 동작(414)에서 n개의 선택가능한 임계 전압 중에서 다른 임계 전압이 선택될 수 있다. 동작(414)에서 다른 임계 전압이 선택되면, 방법(400)은 새롭게 선택된 임계 전압에 대해 동작(404)으로부터 반복될 수 있다. 새로운 임계 전압의 선택은 비동기식으로 수행될 수 있다. 그렇지 않고, 새로운 임계 전압이 선택되지 않으면, 방법(400)은 동작(416)에서 종료될 수 있다.

[0058] 도 5a는 일부 비-제한적인 실시예들에 따라, 도 3의 기준 발생기의 회로도를 도시한다. 기준 발생기(334)는 n개의 임계 전압( $ref_1 \cdots ref_n$ )을 발생시키도록 구성되는 저항성 래더(resistive ladder)를 포함할 수 있으며, 여기서 n은 2보다 큰 임의의 값을 취할 수 있다. 일부 실시예들에서, 저항성 래더는 직렬로 접속된  $n+1$ 개의 저항기( $534_1 \cdots 534_{n+1}$ )를 포함할 수 있다. 저항기( $534_1$ )는 공급 전압( $V_H$ )에 연결될 수 있다. 공급 전압( $V_H$ )은 도 3에 도시된 공급 전압( $V_P$ )과 동일할 수 있다. 저항기( $534_{n+1}$ )는 공급 전압( $V_L$ )에 연결될 수 있다. 공급 전압( $V_L$ )은 도 3에 도시된 공급 전압( $V_N$ )과 동일할 수 있다. 일부 실시예들에서,  $V_H-V_L$ 에 대응하는 전압 범위를 n개의 동일한 세그먼트로 분할하기 위해,  $n+1$ 개의 저항기는 모두 동일한 저항을 가질 수 있다. 다른 실시예들에서, 저항기들( $534_2 \cdots 534_{n+1}$ )은 R과 동일한 저항을 가질 수 있는 반면, 저항기( $534_1$ )는 xR과 동일한 저항을 가질 수 있고, 여기서 x는 0.01 내지 100의 임의의 값을 취할 수 있다. 그러나, 다른 값들도 가능하다. 그러한 실시예들에서,  $V_H-V_L$ 에 비례하는 스케일링된 전압 범위는 n개의 동일한 세그먼트로 분할될 수 있다.

[0059] 도 5b는 일부 비-제한적인 실시예들에 따라, 도 3의 분할 회로의 회로도를 도시한다. 분할 회로는 입력 신호(240)에 비례하는 검출 신호(341)를 발생시키도록 구성되는 용량성 분할기를 포함할 수 있다. 용량성 분할기는 커패시터(532) 및 커패시터(533)를 포함할 수 있다. 커패시터(532)는 펠서(220)의 출력에 연결된 하나의 단자, 및 제어기(336)의 입력에 연결된 하나의 단자를 가질 수 있다. 일부 실시예들에서, 커패시터(532)는 펠서(220)로부터 발생된 입력 신호(240)를 수신하도록 구성될 수 있다. 커패시터(533)는 제어기(336)의 동일한 입력에 연결된 하나의 단자 및 공급 전압( $V_C$ )에 연결된 하나의 단자를 가질 수 있다. 일부 실시예들에서, 커패시터(336)는 입력 신호(240)의 스케일링된 베타를 수신하도록 구성될 수 있다. 일부 실시예들에서, 공급 전압( $V_C$ )은 도 3에 도시된 공급 전압( $V_N$ )과 동일할 수 있다. 커패시터들(532 및 533)의 커패시턴스는 도 5a의 임계 전압들이 스케일링되는 것과 동일한 스케일링 인자에 의해 검출 신호(341)를 스케일링하도록 구성될 수 있다. 그러한 실시예들에서, 검출 신호(341)는 2개의 신호 중 임의의 신호를 먼저 스케일링할 필요 없이, n개의 임계 전압 중에서 선택된 임계 전압에 직접 비교될 수 있다.

[0060] 도 6a는 본 출원의 비-제한적인 실시예에 따라, 펠싱 회로에 의해 용량성 초음파 트랜스듀서에 제공되는 예시적인 신호를 보여주는 타이밍도를 도시한다. 구체적으로, 타이밍도(600)는 예시적인 타겟 신호(602) 및 예시적인 입력 신호(240)를 도시한다. 도 6a와 관련하여 제시된 비-제한적인 실시예에서, 임계 전압은 7개의 임계 전압 중에서 선택될 수 있다. 타겟 신호(602)는 입력 신호(240)에 의해 추종될 신호를 표현한다. 예를 들어  $t_1$ 에서, 입력 신호(240)가 타겟 신호(602)와 동일할 때, 검출 신호(341)는 현재의 임계 전압과 동일하다. 이 경우, 피드백 회로(230)는 입력 전압(240)을 현재 값으로 일정하게 유지하도록 펠서(220)를 제어할 수 있다. 예를 들어  $t_2$ 에서, 입력 전압(240)이 타겟 전압(602)보다 낮을 때, 피드백 회로(230)는 현재 타겟 전압이 도달될 때까지 입력 전압(240)을 감소시킬 수 있다. 일부 실시예들에서, 타겟 신호(602)는 비동기식으로 변경될 수 있다. 결과적으로, 타겟 전압(602)의 각각의 세그먼트의 지속기간은 다른 세그먼트들의 지속기간과 독립적으로 설정될 수 있다.

[0061] 일부 실시예들에서, 펠싱 회로(103)는 제로보다 큰 DC 성분을 갖는 입력 신호(240)를 발생시키도록 구성될 수

있다. DC 성분의 범위는 수신 회로가 포화에 도달하게 하지 않으면서 수신 회로를 바이어링하도록 선택될 수 있다.

[0062] 일부 실시예들에서, 입력 신호(240)는 타겟 신호(602)를 오버슈트(overshoot)할 수 있다(도시 생략). 이러한 오버슈트의 발생을 완화하기 위해, 피드백 회로(230)는 임계 전압을 스케우(skew)하도록 구성될 수 있다. 일부 실시예들에서, 임계 전압은 전압 오프셋을 임계 전압에 가산(또는 감산)함으로써 스케우될 수 있다. 예를 들어, 요구되는 출력 전압이 x 볼트인 경우, 임계 전압은 x와 y 사이의 차이가 오버슈팅 전압과 동일하도록 하는 y 볼트로 설정될 수 있다. 일부 실시예들에서, 임계 전압은 불균일한 저항성 래더를 통해 스케우될 수 있다.

[0063] 도 6b는 본 출원의 비-제한적인 실시예에 따라, 펠싱 회로에 의해 용량성 초음파 트랜스듀서에 제공되는 아포다이즈된 신호를 나타내는 타이밍도를 도시한다. 구체적으로, 타이밍도(620)는 아포다이즈된 타겟 신호(604) 및 아포다이즈된 입력 신호(240)를 도시한다. 피드백 회로(230)는 가우시안 윈도우, 해밍 윈도우, 플랫 탐 윈도우, 코사인 윈도우, 또는 임의의 적절한 윈도우 함수에 기초하여 입력 신호(240)의 시간 영역 아포다이즈를 수행하도록 구성될 수 있다. 본 명세서에 설명된 유형의 멀티레벨 펄스들은 연속적인 윈도우 함수들을 충실히 발행시키기에 충분한 정도의 입도성(granularity)을 제공한다.

[0064] 도 7은 본 출원의 비-제한적인 실시예에 따라, 복수의 용량성 초음파 트랜스듀서에 연결된 복수의 펠싱 회로를 도시하는 블록도이다. 일부 실시예들에서, 용량성 초음파 트랜스듀서들( $101_1, 101_2, 101_3 \dots 101_N$ )은 1D 어레이를 형성하도록 배치될 수 있다. 다른 실시예들에서, 용량성 초음파 트랜스듀서들( $101_1 \dots 101_N$ )은 2D 어레이를 형성하도록 배치될 수 있다. 용량성 초음파 트랜스듀서들( $101_1 \dots 101_N$ )은 펄서들( $220_1, 220_2, 220_3 \dots 220_N$ ) 중 각각의 펄서의 출력 단자에 연결될 수 있다. 피드백 회로들( $230_1, 230_2, 230_3 \dots 230_N$ )은 펄서들( $220_1 \dots 220_N$ ) 중 각각의 펄서의 입력 단자 및 출력 단자에 연결될 수 있다. 일부 실시예들에서, 피드백 회로들( $230_1 \dots 230_N$ )은 개별 회로들일 수 있다. 다른 실시예들에서, 피드백 회로들( $230_1 \dots 230_N$ )은 펄서들( $220_1 \dots 220_N$ )을 제어하도록 구성되는 단일 회로의 일부일 수 있다. 도 7에 도시된 바와 같이, 피드백 회로들( $230_1 \dots 230_N$ )은 공간 의존적인 진폭들을 나타내는 입력 신호( $740_1, 740_2, 740_3, \dots 740_N$ )를 발생시키도록 펄서들( $220_1 \dots 220_N$ )을 제어할 수 있다. 일부 실시예들에서, 피드백 회로들은 입력 신호들의 공간 영역 아포다이즈를 수행하기 위해 펄서들을 제어할 수 있다. 제한이 아닌 예로서, 입력 신호들( $740_1 \dots 740_N$ )은 어레이의 중심에서 더 큰 진폭들을 나타낼 수 있고, 미리 정의된 프로파일을 따라 어레이의 에지 쪽으로 감쇠할 수 있다. 공간 영역 아포다이즈 함수는 가우시안 윈도우, 해밍 윈도우, 플랫 탐 윈도우, 코사인 윈도우, 또는 임의의 적절한 윈도우 함수일 수 있다. 공간 영역 아포다이즈는 하나의 공간 차원 또는 두 개의 공간 차원에 걸쳐 수행될 수 있다. 공간 영역 아포다이즈를 수행함으로써, 어레이의 애피처가 효과적으로 변경될 수 있고, 따라서 방출된 초음파의 공간 프로파일을 최적화하는 수단을 제공한다. 일부 실시예들에서, 공간 프로파일은 공간 사이드 로브들을 최소화하도록 최적화될 수 있다. 최소한의 또는 억제된 사이드 로브들을 갖는 공간 프로파일들을 방출할 수 있는 초음파 디바이스들은 향상된 공간 해상도 및 그에 따라 증가된 이미지 콘트라스트를 나타낸다.

[0065] 일부 실시예들에서, 용량성 초음파 트랜스듀서(101)는 송신 및 수신 회로에 접속될 수 있다. 송신 동안, 펠싱 회로에 의해 발생된 양극성 입력 신호는 우연히 수신 회로에 연결될 수 있다. 일부 실시예들에서, 수신 회로는 펄서(220)로 발생된 유형의 큰 포지티브 및 네거티브 전압 스파이크들을 견디도록 설계되지 않은 컴포넌트들을 포함할 수 있다. 따라서, 양극성 펄스들을 수신 회로에 직접 연결하는 것은 하나 이상의 컴포넌트를 손상시키는 효과를 가질 수 있다.

[0066] 본 출원의 양태들에 따르면, 양극성 펄스들이 발생되고 있는 동안 수신 회로를 송신 회로로부터 분리하도록 구성되는 대칭 스위치가 제공된다. 여기에서 사용될 때, 대칭 스위치는 동일한 유형의 입력 및 출력 단자들을 갖는 트랜지스터 기반 스위치이다. 예를 들어, 스위치의 입력 및 출력 단자들은 둘 다 소스일 수 있거나, 둘 다 드레인일 수 있거나, 둘 다 이미터일 수 있거나, 둘 다 컬렉터일 수 있거나, 또는 다른 단자 유형들일 수 있다. 도 8a 및 도 8b는 본 출원의 비-제한적인 실시예에 따라 송신 모드 및 수신 모드에서 각각 동작하는 초음파 디바이스를 도시하는 블록도들이다. 대칭 스위치(107)는 펠싱 회로들(103)의 출력 단자에 접속된 입력 단자를 가질 수 있다. 일부 실시예들에서, 대칭 스위치(107)의 입력 단자는 펠싱 회로(103)의 펄서(220)의 출력 단자에 접속될 수 있다. 대칭 스위치(107)의 입력 단자는 용량성 초음파 트랜스듀서(101)의 단자에 더 접속될 수 있다. 일부 실시예들에서, 대칭 스위치(107)의 입력 단자는 펄서(220)의 출력 단자와 용량성 초음파 트랜스듀서(101)의 단자 사이에 연결될 수 있다. 대칭 스위치는 또한 수신 회로(109)의 입력 단자에 연결된 출력 단자

를 또한 가질 수 있다. 일부 실시예들에서, 수신 회로(109)는 반향 신호를 수신하는 것에 응답하여 용량성 초음파 트랜스듀서(101)에 의해 발생되는 전류를 변환하도록 구성되는 전류-전압 변환기를 포함한다. 일부 실시예들에서, 전류-전압 변환기는 트랜스-임피던스 증폭기(TIA)를 포함할 수 있다.

[0067] 도 8a에 도시된 바와 같이, 송신 모드(TX 모드)에서, 대칭 스위치(107)는 펄싱 회로(103)에 의해 발생된 펄스를 수신 회로(109)로부터 분리하기 위해 높은 임피던스를 제공하도록 구성될 수 있다. 일부 실시예들에서, 대칭 스위치(107)는 송신 모드 동안 개방 회로로서 동작하도록 구성될 수 있다. 화살표(801)는 송신 모드 동안 입력 신호(240)에 대응하는 신호 경로를 표현할 수 있다.

[0068] 도 8b에 도시된 바와 같이, 수신 모드(RX 모드)에서, 대칭 스위치(107)는 수신 회로(109)에 대한 반향 신호(또는 다른 수신 신호)를 수신하는 것에 응답하여 용량성 초음파 트랜스듀서(101)에 의해 발생된 펄스를 연결하기 위해 낮은 임피던스를 제공하도록 구성될 수 있다. 일부 실시예들에서, 대칭 스위치(107)는 수신 모드 동안 용량성 초음파 트랜스듀서(101)에 수신 회로(109)를 단락시키도록 구성될 수 있다. 일부 실시예들에서, 펄싱 회로(103)는 수신 모드 동안 높은 임피던스 상태에 있도록 구성될 수 있다. 화살표(821)는 수신 모드 동안 수신 신호에 대응하는 신호 경로를 표현할 수 있다.

[0069] 도 9는 본 출원의 비-제한적인 실시예에 따른 대칭 스위치를 포함하는 초음파 디바이스의 블록도(900)를 도시한다. 대칭 스위치(907)는 펄싱 회로(103)에 의해 발생된 양극성 펄스들에 연관된 포지티브 및 네거티브 전압들을 차단하도록 구성될 수 있고, 따라서 수신 회로(109)에 대한 손상을 방지한다.

[0070] 일부 실시예들에서, 대칭 스위치(907)는 2개의 트랜지스터(910 및 912)를 포함할 수 있다. 그러나, 대칭 스위치(907)는 송신 모드 동안 양극성 펄스들을 차단하도록 구성되는 임의의 적절한 수의 트랜지스터를 포함할 수 있다. 트랜지스터들(910 및 912)은 nMOS 또는 pMOS를 포함하는 금속 산화물 반도체 전계 효과 트랜지스터(MOSFET), 접합 전계 효과 트랜지스터(JFET), 양극성 접합 트랜지스터(BJT), 금속 반도체 전계 효과 트랜지스터(MESFET), 절연 게이트 전계 효과 트랜지스터(IGFET), 측면 확산형 금속 산화물 반도체 트랜지스터(LDMOS), 또는 이것들의 임의의 적절한 조합과 같은 임의의 유형일 수 있다. 일부 실시예들에서, 트랜지스터들(910 및 912) 둘 다는 nMOS이다. 트랜지스터(910)의 게이트는 트랜지스터(912)의 게이트에 단락될 수 있다. 일부 실시예들에서, 트랜지스터(910)의 게이트가 아닌 제2 단자는 트랜지스터(912)의 게이트가 아닌 제2 단자에 단락될 수 있다. 제한이 아닌 예로서, 트랜지스터(910)의 소스는 트랜지스터(912)의 소스에 단락될 수 있다. 트랜지스터(912)의 제3 단자, 예를 들어 드레인은 펄싱 회로(103)의 출력 단자와 용량성 초음파 트랜스듀서(101)의 단자 사이에 연결될 수 있다. 트랜지스터(910)의 제3 단자, 예를 들어 드레인은 수신 회로(109)의 입력 단자에 연결될 수 있다. 일부 실시예들에서, 트랜지스터(910)의 드레인은 수신 회로(109)의 입력 단자에 단락될 수 있다. 일부 실시예들에서, 트랜지스터(910)의 바디 단자는 트랜지스터(910)의 소스에 단락될 수 있고, 트랜지스터(912)의 바디 단자는 트랜지스터(912)의 소스에 단락될 수 있다.

[0071] 일부 실시예들에서, 스위칭 회로(908)는 송신 모드 동안 양극성 펄스들을 차단하기 위해 사용될 수 있다. 스위칭 회로(908)는 대칭 스위치(907) 및 트랜지스터(915)를 포함할 수 있다. 트랜지스터(915)는 임의의 적절한 유형의 트랜지스터 일 수 있다. 제한이 아닌 예로서, 트랜지스터(915)는 nMOS일 수 있다. 트랜지스터(915)는 수신 회로(109)의 입력 단자에 단락된 드레인을 갖도록 구성될 수 있다. 트랜지스터(915)의 소스는 접지 단자에 단락될 수 있다. 트랜지스터(915)의 바디 단자는 그것의 소스에 단락될 수 있다.

[0072] 일부 실시예들에서, 대칭 스위치는 pMOS 트랜지스터들을 포함할 수 있다. 도 11은 대칭 스위치를 포함하는 초음파 디바이스의 블록도(1100)를 도시하며, 여기서 대칭 스위치는 본 출원의 비-제한적인 실시예에 따라 2개의 pMOS 트랜지스터(1110 및 1112)를 포함한다. 도 11은 2개의 pMOS 트랜지스터를 포함하는 대칭 스위치를 도시하지만, 임의의 다른 적절한 수의 pMOS 트랜지스터가 사용될 수 있다.

[0073] 대칭 스위치(1107)는 트랜지스터(1110)의 게이트가 트랜지스터(1112)의 게이트에 단락될 수 있도록 구성될 수 있다. 일부 실시예들에서, 트랜지스터(1110)의 게이트가 아닌 제2 단자는 트랜지스터(1112)의 게이트가 아닌 제2 단자에 단락될 수 있다. 제한이 아닌 예로서, 트랜지스터(1110)의 소스는 트랜지스터(1112)의 소스에 단락될 수 있다. 트랜지스터(1112)의 제3 단자, 예를 들어 드레인은 펄싱 회로(103)의 출력 단자와 용량성 초음파 트랜스듀서(101)의 단자 사이에 연결될 수 있다. 트랜지스터(1110)의 제3 단자, 예를 들어 드레인은 수신 회로(109)의 입력 단자에 연결될 수 있다. 일부 실시예들에서, 트랜지스터(1110)의 드레인은 수신 회로(109)의 입력 단자에 단락될 수 있다. 일부 실시예들에서, 트랜지스터(1110)의 바디 단자는 트랜지스터(1110)의 소스에 단락될 수 있고, 트랜지스터(1112)의 바디 단자는 트랜지스터(1112)의 소스에 단락될 수 있다. 일부 실시예들에서, 스위칭 회로(1108)는 대칭 스위치(1107) 및 트랜지스터(915)를 포함할 수 있다.

- [0074] 스위칭 회로(908)는 송신 모드 동안 펄싱 회로(103)에 의해 발생된 양극성 펄스들을 차단하도록 구성되고, 수신 모드 동안 용량성 초음파 트랜스듀서(101)를 수신 회로(109)에 연결하도록 더 구성된 임의의 적절한 유형 및 개수의 제어 신호에 의해 제어될 수 있다. 제한이 아닌 예로서, 도 10은 본 출원의 비-제한적인 실시예에 따라, 도 9의 대칭 스위치를 구동하도록 구성되는 제어 신호들을 도시하는 타이밍도(1000)를 도시한다. 제어 신호(1002)는 단자 G를 통해 트랜지스터들(910 및 912)의 게이트들을 제어할 수 있다. 제어 신호(1004)는 단자 S를 통해 트랜지스터들(910 및 912)의 소스들을 제어할 수 있다. 제어 신호(1006)는 단자 G<sub>2</sub>를 통해 트랜지스터(915)의 게이트를 제어할 수 있다. 일부 실시예들에서, 수신 회로(109)는 제어 신호(1008)로 턴온 및 턴오프될 수 있다. 예를 들어, 제어(1008)는 수신 회로(109)의 전압 공급을 인에이블/디스에이블할 수 있다.

- [0075] t<sub>0</sub> 전에, 스위칭 회로(908)는 수신 모드에서 동작하도록 구성될 수 있다. 이 기간 동안, 제어 신호(1002)는 제어 신호(1004)보다 끌 수 있다. 일부 실시예들에서, 제어 신호들(1002 및 1004) 둘 다가 제로보다 끌 수 있다. 이러한 방식으로, 트랜지스터들 둘 다는 제로보다 큰 게이트-소스 전압을 가질 수 있고, 따라서 전류들을 전도하도록 구성될 수 있다. 제어 신호(1006)는 트랜지스터(915)를 컷오프 상태로 유지하기 위해 트랜지스터(915)의 임계 전압 미만이거나 제로일 수 있다. 일부 실시예들에서, 제어 신호(1008)는 수신 회로(109)를 인에이블하는 값으로 설정될 수 있다.

- [0076] t<sub>0</sub>와 t<sub>1</sub> 사이에서, 제어 신호(1008)는 수신 회로(109)를 디스에이블하는 값으로 설정될 수 있다.

- [0077] t<sub>1</sub>과 t<sub>2</sub> 사이에서, 제어 신호(1002)는 제어 신호(1004)와 동일한 값으로 설정될 수 있다. 결과적으로, 트랜지스터들(910 및 912)은 그것들의 컷오프 모드로 전환될 수 있다. 일부 실시예들에서, 제어 신호(1006)는 트랜지스터(915)의 임계 전압보다 높은 값으로 설정될 수 있다. 결과적으로, 수신 회로(109)의 입력 단자는 제로와 동일한 전압으로 강제될 수 있다.

- [0078] t<sub>2</sub>와 t<sub>3</sub> 사이에서, 제어 신호들(1002 및 1004)은 네거티브 전압으로 설정될 수 있다. 일부 실시예들에서, 제어 신호들(1002 및 1004)은 동시에 네거티브 전압으로 설정될 수 있다. 일부 실시예들에서, 네거티브 전압은 도 3에 도시된 V<sub>N</sub>과 동일할 수 있다.

- [0079] t<sub>3</sub>과 t<sub>4</sub> 사이에서, 제어 신호들(1002 및 1004)은 제로로, 또는 펄싱 회로(103)의 바이어스 전압으로 설정될 수 있다. 일부 실시예들에서, 제어 신호들(1002 및 1004)은 동시에 펄싱 회로(103)의 바이어스 전압으로 또는 제로로 설정될 수 있다.

- [0080] t<sub>4</sub>와 t<sub>5</sub> 사이에서, 제어 신호(1002)는 트랜지스터들(910 및 912)의 게이트-소스 전압들이 임계값보다 높게 되는 전압으로 설정될 수 있다. 일부 실시예들에서, 제어 신호(1006)는 트랜지스터(915)의 임계 전압보다 낮은 값으로 설정될 수 있고, 그에 의해 수신 회로(109)의 입력 단자에 연관된 전압은 자유롭게 변동할 수 있게 된다.

- [0081] t<sub>5</sub> 후에, 제어 신호(1008)는 수신 회로(109)를 인에이블하는 값으로 설정될 수 있다.

- [0082] 일부 실시예들에서, 수신 모드는 t<sub>0</sub> 이전 및 t<sub>5</sub> 이후의 기간들에 의해 정의될 수 있고, 송신 모드는 t<sub>0</sub>와 t<sub>5</sub> 사이의 기간에 의해 정의될 수 있다. 다른 실시예들에서, 수신 모드는 t<sub>1</sub> 이전 및 t<sub>4</sub> 이후의 기간들에 의해 정의될 수 있고, 송신 모드는 t<sub>1</sub>과 t<sub>4</sub> 사이의 기간에 의해 정의될 수 있다. 일부 실시예들에서, t<sub>0</sub>는 t<sub>1</sub>과 동일할 수 있다. 일부 실시예들에서, t<sub>1</sub>은 t<sub>2</sub>와 동일할 수 있다. 일부 실시예들에서, t<sub>3</sub>는 t<sub>4</sub>와 동일할 수 있다. 일부 실시예들에서, t<sub>4</sub>는 t<sub>5</sub>와 동일할 수 있다.

- [0083] 본 출원의 양태들은 하나 이상의 이점을 제공할 수 있으며, 그들 중 일부는 앞에서 설명되었다. 이하에서는, 이러한 이점들의 일부 비-제한적인 예들이 설명된다. 모든 양태들 및 실시예들이 이하에 설명되는 이점들 전부를 반드시 제공하지는 않는다는 것을 알아야 한다. 또한, 본 출원의 양태들은 이하에 설명된 것들에 추가적인 이점들을 제공할 수 있다는 것을 알아야 한다.

- [0084] 본 출원의 양태들은 수신 회로의 포화를 야기하지 않고서 수신될 수 있는 양극성 펄스들을 발생하도록 구성되는 펄싱 회로들을 제공한다. 그러나, 수신 회로들은 양극성 펄스들에 연관된 큰 포지티브 및 네거티브 전압 스파이크들을 견디도록 설계되지 않은 컴포넌트들을 포함할 수 있다.

- [0085] 본 출원의 양태들은 송신 모드 동안 수신 회로를 송신 회로로부터 분리하도록 구성되며, 따라서 양극성 펄스들

에 의해 야기되는 수신 회로의 손상을 방지하는 대칭 스위치들을 제공한다.

[0086] 시간 영역 및 공간 영역 아포다이즈된 펄스들의 발생은 멀티레벨 펄스들을 제어하는 능력을 요구한다. 본 출원의 양태들은 추가의 공급 전압들에 의지하지 않고서 시간 영역 및 공간 영역 아포다이즈를 제공하도록 구성되는 피드백 회로들을 제공한다. 따라서, 초음파 디바이스들에 추가의 공급 전압들을 통합하면, 상당한 크기의 핸드 헬드형 초음파 프로브들이 야기될 수 있다.

[0087] 이와 같이, 본 출원의 기술의 몇몇 양태들 및 실시예들을 설명하였지만, 본 기술분야의 통상의 기술자에게는 다양한 변경들, 수정들 및 개선들이 쉽게 떠오를 것임을 알아야 한다. 이러한 변경들, 수정들 및 개선들은 본 출원에 설명된 기술의 사상 및 범위 내에 있는 것으로 의도된다. 그러므로, 상술한 실시예들은 단지 예로서 제시된 것이고, 첨부된 청구항들 및 그것의 등가물들의 범위 내에서, 본 발명의 실시예들은 구체적으로 설명된 것과 다르게 실시될 수 있음을 이해해야 한다. 추가로, 본 명세서에 설명된 둘 이상의 특징, 시스템, 제품, 재료 및 /또는 방법의 임의의 조합은 그러한 특징, 시스템, 제품, 재료 및/또는 방법이 상호 모순되지 않는 경우, 본 개시내용의 범위 내에 포함된다.

[0088] 또한, 설명된 바와 같이, 일부 양태들은 하나 이상의 방법으로서 구현될 수 있다. 방법의 일부로서 수행되는 동작들은 임의의 적절한 방식으로 순서가 정해질 수 있다. 따라서, 동작들이 예시된 것과는 다른 순서로 수행되는 실시예들이 구성될 수 있으며, 이는 예시적인 실시예들에서 순차적인 동작들로서 도시되어 있더라도, 일부 동작들을 동시에 수행하는 것을 포함할 수 있다.

[0089] 본 명세서에서 정의되고 사용되는 모든 정의들은 사전적 정의들, 참조에 의해 포함된 문헌들 내의 정의들, 및/ 또는 정의된 용어들의 통상적인 의미들을 통제하는 것으로 이해되어야 한다.

[0090] 본 명세서 및 청구항들에서 사용되는 단수 표현들[즉, 부정 관사 "a" 및 "an"]은 반대로 명백하게 표시되어 있지 않는 한 "적어도 하나"를 의미하는 것으로 이해되어야 한다.

[0091] 본 명세서 및 청구항들에서 사용되는 "및/또는"이라는 문구는 그와 같이 결합된 구성요소들, 즉 일부 경우들에서는 결합적으로 존재하고 다른 경우들에서는 분리적으로 존재하는 구성요소들의 "어느 하나 또는 둘 다"를 의미하는 것으로 이해되어야 한다.

[0092] 본 명세서 및 청구항들에서 사용되는 바와 같이, 하나 이상의 구성요소의 목록을 참조한 "적어도 하나"라는 문구는 구성요소들의 목록 내의 구성요소들 중 임의의 하나 이상으로부터 선택된 적어도 하나의 구성요소를 의미하지만, 구성요소들의 목록 내에 구체적으로 나열된 각각의 모든 구성요소 중 적어도 하나를 반드시 포함하지는 않으며 구성요소들의 목록 내의 구성요소들의 임의의 조합들을 배제하지 않는 것으로 이해되어야 한다. 이 정의는, 또한 "적어도 하나"라는 문구가 참조하는 구성요소들의 목록 내에 구체적으로 식별된 구성요소들 외의 구성요소들이, 구체적으로 식별된 구성요소들에 관련되는지 아니면 관련되지 않는지에 관계없이 임의로 존재할 수 있음을 허용한다.

[0093] "대략" 및 "약"이라는 용어들은 일부 실시예들에서 타겟 값의 ±20% 이내, 일부 실시예들에서 타겟 값의 ±10% 이내, 일부 실시예들에서 타겟 값의 ±5% 이내, 심지어는 일부 실시예들에서 타겟 값의 ±2% 이내를 의미하기 위해 사용될 수 있다. "대략" 및 "약"이라는 용어들은 타겟 값을 포함할 수 있다.

[0094] 청구항들은 물론, 상술한 명세서에서, "포함하는(comprising, including)", "지니는(carrying)", "갖는(having)", "함유하는(containing)", "수반하는(involving)", "유지하는(holding)", "구성되는(composed of)" 등과 같은 모든 전이 문구들은 개방단으로, 즉 포함하지만 그에 제한되지 않음을 의미하는 것으로 이해되어야 한다. "이루어지는(consisting of)" 및 "본질적으로 이루어지는(consisting essentially of)"이라는 전이 문구들은 각각 폐쇄 또는 준-폐쇄 전이 문구들일 것이다.

## 도면

## 도면1

## 도면2

도면3

## 도면4

도면5a

도면5b

도면6a

도면6b

도면7

도면8a

## 도면8b

## 도면9

도면10

도면11