OFICINA ESPAÑOLA DE

PATENTES Y MARCAS

ESPAÑA

(11) Número de publicación: **2 315 317**

(51) Int. Cl.:

**G06T 1/20** (2006.01)

(12)

### TRADUCCIÓN DE PATENTE EUROPEA

T3

(96) Número de solicitud europea: **01994868 .6**

(96) Fecha de presentación : **28.12.2001**

(97) Número de publicación de la solicitud: **1346320**

(97) Fecha de publicación de la solicitud: **24.09.2003**

(54) Título: **Procesador, circuito y procedimiento para procesar imágenes en una red de procesadores paralelos.**

(30) Prioridad: **28.12.2000 FI 20002864**

(73) Titular/es: **Ari Paasio**

**Hollanterinpolku 4**

**20660 Littoinen, FI**

(45) Fecha de publicación de la mención BOPI:

**01.04.2009**

(72) Inventor/es: **Paasio, Ari**

(45) Fecha de la publicación del folleto de la patente:

**01.04.2009**

(74) Agente: **Curell Suñol, Marcelino**

**ES 2 315 317 T3**

Aviso: En el plazo de nueve meses a contar desde la fecha de publicación en el Boletín europeo de patentes, de la mención de concesión de la patente europea, cualquier persona podrá oponerse ante la Oficina Europea de Patentes a la patente concedida. La oposición deberá formularse por escrito y estar motivada; sólo se considerará como formulada una vez que se haya realizado el pago de la tasa de oposición (art. 99.1 del Convenio sobre concesión de Patentes Europeas).

# ES 2 315 317 T3

## DESCRIPCIÓN

Procesador, circuito y procedimiento para procesar imágenes en una red de procesadores paralelos.

### 5 Campo técnico de la invención

La presente invención se refiere a un circuito y a un procedimiento para procesar imágenes en una red de procesadores paralelos, y más particularmente para procesar imágenes en una red de procesadores paralelos analógicos.

### 10 Antecedentes de la invención

Una red de procesadores paralelos incluye varios procesadores idénticos (células) dispuestos de forma regular. Cada célula presenta una señal de entrada, un estado dinámico y una señal de salida.

15 La idea en una red de procesadores paralelos para procesar imágenes es que un procesador (célula) corresponde a un píxel, y por tanto, es posible proporcionar una red de procesadores paralelos que puede realizar un procesamiento muy rápido (en teoría). Un problema para integrar este tipo de red de procesadores paralelos en un chip es que el tamaño de los procesadores no se ha minimizado para permitir implementar la integración de decenas o centenas de miles de procesadores en un chip sin reducir la desventaja.

20 En una red de procesadores paralelos, las células están conectadas a sus células adyacentes (también pueden estar conectadas por ejemplo a todas las demás células en una red de procesadores paralelos), es decir, afectan a un estado dinámico de sus células adyacentes. Esta influencia está correlacionada directamente con la entrada de la célula y su propia salida dinámica. Estas características permiten un procesamiento de señales en tiempo real porque el procesamiento de datos se produce en todas las células al mismo tiempo.

25 Una red de procesadores paralelos puede implementarse para procesar imágenes, por ejemplo para filtrar ruido “de sal y pimienta” de una imagen. Se han presentado varios procedimientos para filtrar ruido de una imagen, de los que uno de los procedimientos generalmente usados son los filtros de mediana. Un filtro de mediana es un caso especial de un filtro de orden de rango en el que puede seleccionarse una mediana de los números, aunque también puede seleccionarse cualquier otra unidad de número de orden de rango. Estos casos incluyen por ejemplo hallar un máximo o un mínimo a partir de una serie específica de números. Las operaciones, que utilizan un procedimiento basándose en hallar un máximo o un mínimo a partir de la serie específica de números se utilizan ampliamente en el procesamiento de imágenes, por ejemplo, cuando se implementan operaciones de morfología matemática.

30 35 Un caso especial de filtrado de orden de rango es el filtrado de mediana, por ejemplo se extrae la quinta corriente más grande de nueve corrientes. Una extensión respecto al filtrado de mediana básico se describe por ejemplo, en L. Yin, R. Yang, M. Gabbouj e Y. Neuvo, “Weighted Median Filters: A Tutorial”, IEEE Transaction on Circuits and Systems - II, vol. 43, páginas 157-192, 1996, en el que a cada entrada se le pueden dar diferentes pesos para favorecer la selección de ciertas variables. En este esquema de ponderación un peso de una magnitud, por ejemplo, de tres asignado a una cierta variable significa prácticamente que la variable se introduce tres veces en la lista de variables a partir de las que se selecciona la mediana. Esto también significa que el número total de variables a partir de las que ha de realizarse la selección ha aumentado en dos.

40 45 50 55 60 Se han descrito algunas implementaciones analógicas para filtrar imágenes. En un artículo de G.Fikos, S.Vlassis y S.Siskos, “High-Speed, Accurate Analogue CMOS Rank Filter”, Electronics Letters, vol. 36, n.º 7, páginas 593-594, 2000, se propone un extractor de rangos de modo de corriente en el que un circuito es adecuado para entradas múltiples. Además, puede seleccionarse el rango extraído, es decir, el filtrado de rangos implica la selección de la k-ésima corriente I (k) más grande. Una célula básica de la implementación es un comparador de corriente, que presenta una corriente de salida. La célula básica contiene dos bloques de construcción diferentes, uno para realizar la comparación real y uno para proporcionar la salida de corriente. La salida de corriente de la célula básica se realiza mediante generadores de corriente complementarios, es decir, un generador proporciona corrientes de salida positivas y el otro proporciona corrientes de salida negativas, con conmutadores en sus salidas. Se supone que las magnitudes de las corrientes de salida de estos generadores de corriente presentan magnitudes iguales dentro de una célula básica, y también dentro de todo el sistema. Por tanto el sistema no puede realizar filtrado de orden de rango ponderado. Los conmutadores de salida se controlan mediante una tensión que se genera dentro de la célula básica mediante un comparador de corriente con salida de tensión. Una pluralidad de células básicas proporcionan su salida de corriente a un nodo común en el que la suma de las corrientes de salida se compara con otra corriente. Esta otra corriente se genera mediante un generador de corriente que debe poder proporcionar tanto corrientes positivas como negativas, cada vez de una polaridad, y controlando la magnitud y signo de este generador de corriente particular, pueden extraerse corrientes de entrada al sistema que presenten un orden de rango predeterminado.

65 Las implementaciones analógicas para procesar imágenes descritas en la técnica anterior no permiten una función programable o son demasiado complejas para integrarse en un chip en gran número de procesadores. Algunas de las estructuras descritas en la técnica anterior presentan también un consumo de energía esencialmente alto, y por tanto, no resulta preferido integrar miles de procesadores en un chip.

# ES 2 315 317 T3

## Sumario de la presente invención

Un objetivo de la presente invención consiste en superar o por lo menos mitigar las desventajas de la técnica anterior. La presente invención proporciona un circuito según la reivindicación 1 y un procedimiento según la reivindicación 11 que permiten procesadores más pequeños en una red de procesadores paralelos analógicos.

Según un primer aspecto de la presente invención se proporciona un procesador en una red de procesadores paralelos analógicos, para procesamiento de imágenes, comprendiendo el procesador:

- 10 una pluralidad de circuitos, en la que un circuito comprende un primer transistor y un segundo transistor, que reciben tensiones de alimentación respectivas y funcionan como generadores de corriente, proporcionando una tensión de salida, y un acoplamiento de coeficiente, que recibe la tensión de salida proporcionada por el primer transistor y el segundo transistor, proporcionando una función de conmutación para una corriente de salida de circuito;

- 15 un transistor de polarización; y

- un transistor de salida.

20 Preferentemente, el transistor de polarización proporciona una corriente de salida que se ajusta a un valor en el que puede determinarse una corriente con un número de orden de rango específico del conjunto de corrientes de salida del primer transistor, o transistores respectivos.

25 Preferentemente, el transistor de salida proporciona una corriente de salida del procesador.

30 Preferentemente, el acoplamiento de coeficiente comprende: un tercer transistor, que funciona como un generador de corriente y un cuarto transistor, que proporciona una función de conmutación. Más preferentemente, el acoplamiento de coeficiente proporciona tres modos de funcionamiento: el cuarto transistor conduce la corriente, el cuarto transistor conduce una cantidad limitada de la corriente, o el cuarto transistor no conduce la corriente.

35 Preferentemente, el tercer transistor recibe una tensión de coeficiente que es programable.

40 Preferentemente, la tensión de salida proporcionada por el primer transistor y el segundo transistor es la tensión de control del cuarto transistor.

45 Preferentemente, el primer transistor presenta una entrada para la tensión de alimentación y una entrada para una tensión de control.

50 Preferentemente, el segundo transistor presenta una entrada para la tensión de alimentación y una entrada para una tensión de control, en el que la tensión de control se forma a partir de una corriente de salida del cuarto transistor junto con otras corrientes de salida recibidas de transistores respectivos de un procesador y del transistor de polarización.

55 Preferentemente, por lo menos uno de los transistores es un transistor PMOS.

60 Preferentemente, por lo menos uno de los transistores es un transistor NMOS.

65 Preferentemente, el procesador comprende además por lo menos un transistor para proporcionar una corriente de salida que se suma con el primer transistor.

70 Segundo aspecto de la presente invención: Según un segundo aspecto de la presente invención está previsto un circuito para procesar imágenes en una red de procesadores paralelos analógicos, comprendiendo el circuito:

75 un primer transistor y un segundo transistor, que reciben tensiones de alimentación respectivas y funcionan como generadores de corriente, proporcionando una tensión de salida; y

80 un acoplamiento de coeficiente, que recibe la tensión de salida proporcionada por el primer transistor y el segundo transistor, proporcionando una función de conmutación para una corriente de salida de circuito.

85 Segundo aspecto de la presente invención: Segundo aspecto de la presente invención: Según un tercero aspecto de la presente invención está previsto un procedimiento para procesar imágenes en una red de procesadores paralelos analógicos, comprendiendo el procedimiento:

90 recibir una tensión fuente y una tensión de control en un primer transistor, y formar una corriente de salida del primer transistor;

95 recibir una tensión fuente y una tensión de control en un segundo transistor, y formar una corriente de salida del segundo transistor;

## ES 2 315 317 T3

recibir una tensión fuente y una tensión de coeficiente en un tercer transistor, y proporcionar una corriente de entrada a un cuarto transistor;

5 recibir una tensión de entrada, que se define con respecto a las corrientes de salida del primer transistor y el segundo transistor, y una corriente de entrada del tercer transistor en el cuarto transistor;

determinar un modo de funcionamiento en el cuarto transistor basándose en la tensión de entrada y la corriente de entrada; y

10 proporcionar una corriente de salida del cuarto transistor para su procesamiento adicional.

Preferentemente, la tensión de coeficiente es programable.

15 Preferentemente, el modo de funcionamiento es uno de los siguientes:

el cuarto transistor conduce la corriente de entrada;

el cuarto transistor conduce una cantidad limitada de la corriente de entrada; o

20 el cuarto transistor no conduce la corriente de entrada.

25 Preferentemente, la corriente de salida del cuarto transistor está prevista para formar una tensión de control del segundo transistor, y otros transistores respectivos en un procesador, junto con otras corrientes de salida recibidas de transistores respectivos y de un transistor de polarización del procesador en una red de procesadores paralelos analógicos.

30 Preferentemente, el procedimiento comprende además un transistor de polarización que proporciona una corriente de salida que se ajusta a un valor en el que puede determinarse una corriente con un número de orden de rango específico del conjunto de corrientes de salida del primer transistor, o transistores respectivos.

Según un cuarto aspecto de la presente invención está previsto un procesador para procesar imágenes en una red de procesadores paralelos analógicos, comprendiendo el procesador:

35 una pluralidad de circuitos, en la que un circuito comprende un primer transistor y un segundo transistor, que reciben tensiones de alimentación respectivas y funcionan como generadores de corriente, proporcionando una tensión de salida y un tercer transistor, que recibe una tensión fuente y la tensión de salida proporcionada por el primer transistor y el segundo transistor, proporcionando una función de commutación para una corriente de salida de circuito;

40 un transistor de polarización, que proporciona una corriente de salida que se ajusta a un valor en el que puede determinarse una corriente con un número de orden de rango específico del conjunto del primer transistor, o transistores respectivos; y

45 un transistor de salida para proporcionar una corriente de salida del procesador para el siguiente proceso.

Según un quinto aspecto de la presente invención está previsto un procedimiento para procesar imágenes en una red de procesadores paralelos analógicos, comprendiendo el procedimiento:

50 recibir una tensión fuente y una tensión de control en un primer transistor, y formar una corriente de salida del primer transistor;

55 recibir una tensión fuente y una tensión de control en un segundo transistor, y formar una corriente de salida del segundo transistor;

recibir una tensión de entrada, que se define con respecto a las corrientes de salida del primer transistor y el segundo transistor, y una tensión fuente en un tercer transistor;

60 determinar un modo de funcionamiento en el tercer transistor basándose en la tensión fuente y la tensión de entrada;

proporcionar una corriente de salida del tercer transistor para su procesamiento adicional;

65 formar una tensión de control del segundo transistor de las corrientes de salida de por lo menos un tercer transistor y un transistor de polarización de un procesador, en el que la corriente de salida del transistor de polarización se ajusta a un valor en el que puede determinarse una corriente con un número de orden de rango específico de un conjunto de corrientes de salida de los primeros transistores; y

conducir la tensión de control a por lo menos un segundo transistor en el procesador.

La presente invención proporciona una implementación analógica sencilla que puede programarse según un número de orden de rango o un coeficiente ponderado. La presente invención logra además un consumo de energía inferior que las implementaciones de la técnica anterior. La presente invención es también fácil de implementar en un sistema existente, porque la presente invención implementa los transistores que ya existen en unidades de procesador para procesar imágenes.

## 10 Breve descripción de los dibujos

Para poner más claramente de manifiesto la presente invención y con el fin de mostrar cómo la misma puede ponerse en práctica, a continuación se hará referencia, a título de ejemplo, a los dibujos adjuntos, en los que:

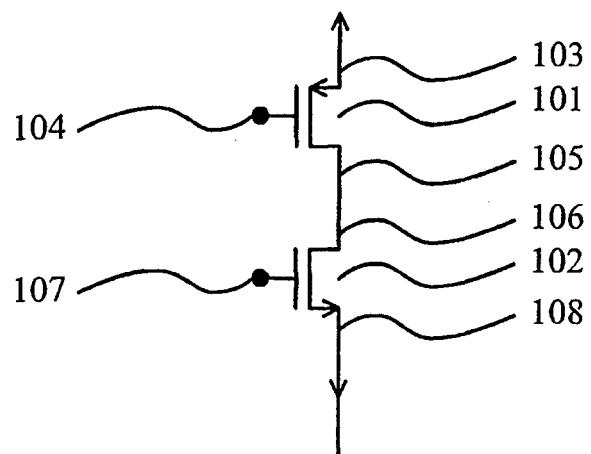

15 La figura 1 muestra un acoplamiento de coeficiente implementado en la forma de realización preferida de la presente invención.

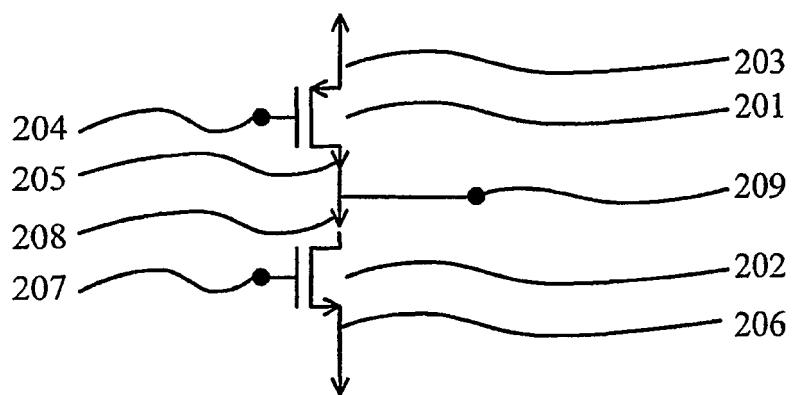

20 La figura 2 muestra una estructura que presenta dos generadores de corriente, y una tensión de salida resultado, según una forma de realización preferida de la presente invención.

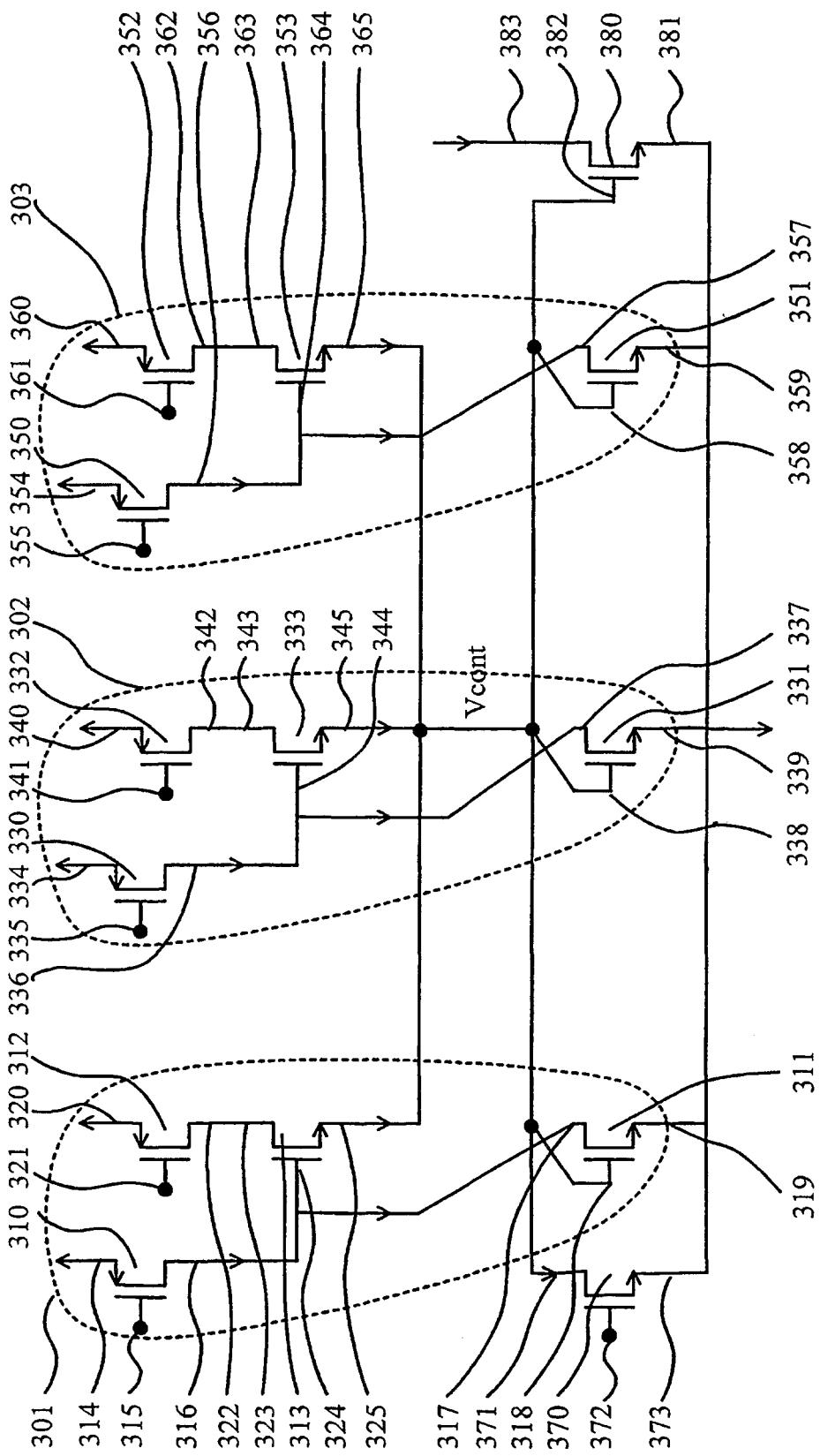

La figura 3 muestra un concepto inventivo de la presente invención.

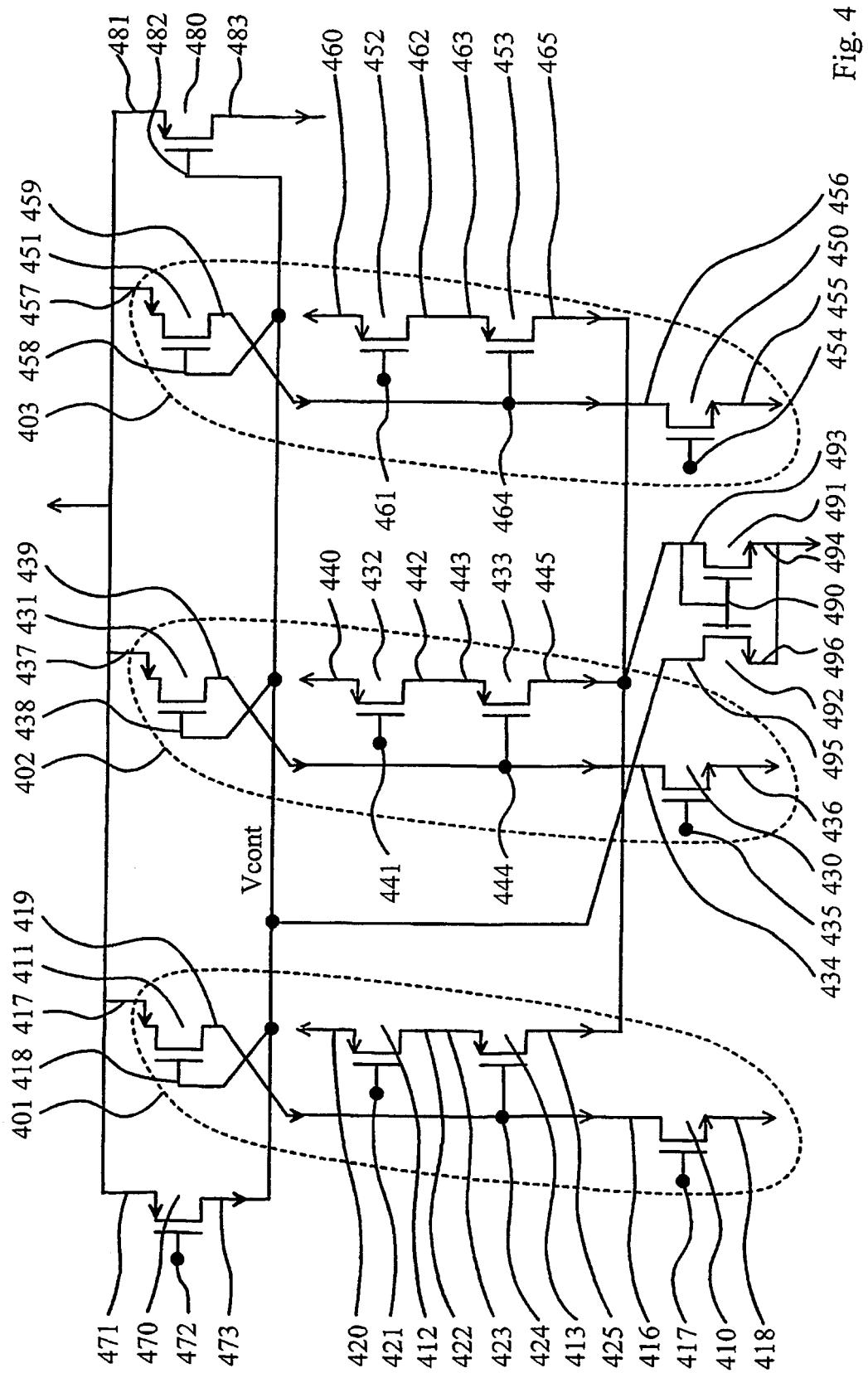

La figura 4 muestra una forma de realización alternativa del concepto inventivo de la presente invención.

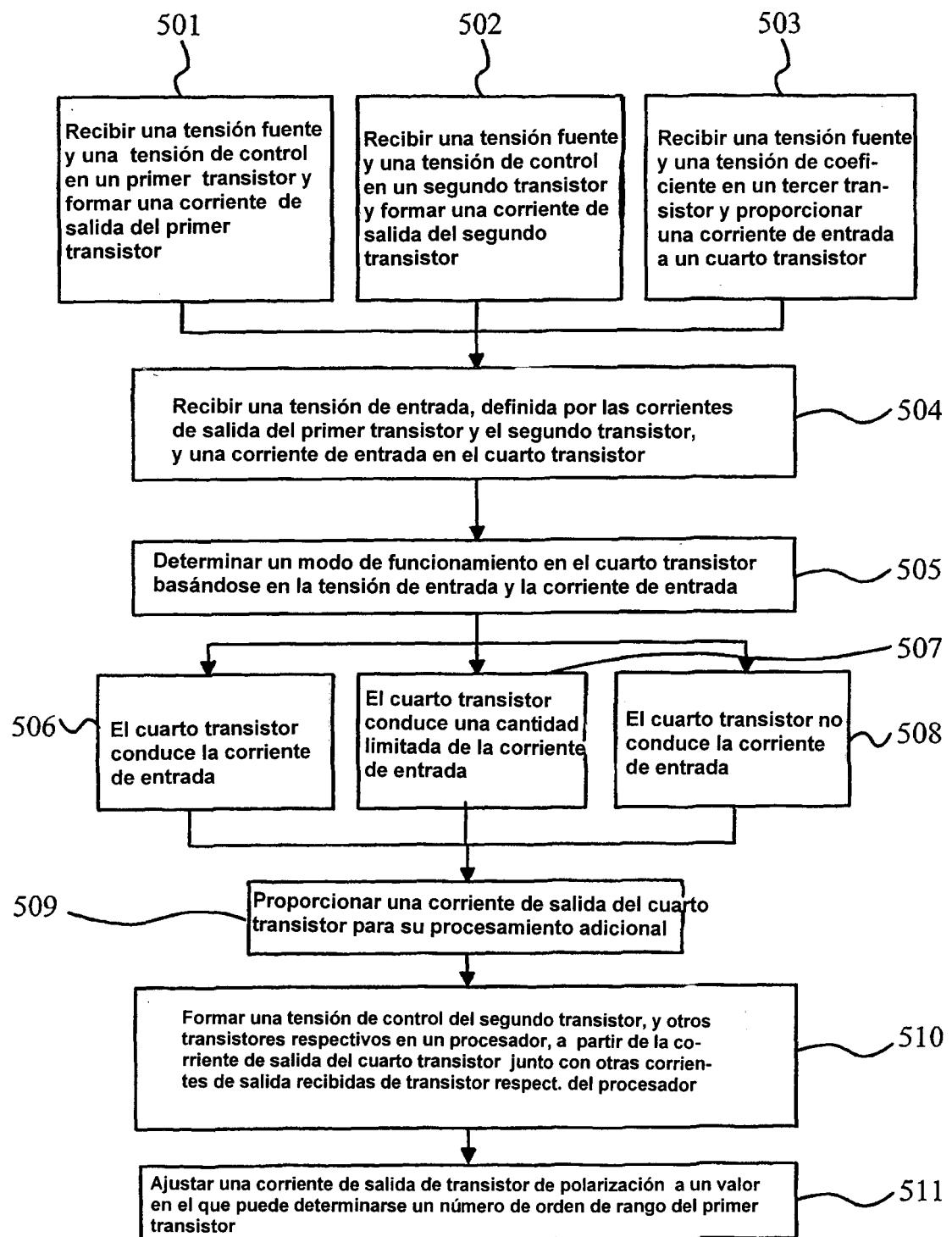

25 La figura 5 es un diagrama de flujo que ilustra el procedimiento de la forma de realización preferida de la presente invención.

## 30 Descripción detallada de algunas formas de realización

La presente invención está concebida para su implementación en una red de procesadores paralelos analógicos, aunque puede implementarse también de modo que sólo un circuito se implemente en un sistema. La presente invención puede implementarse para procesar y/o analizar imágenes, y consigue un cálculo de alta velocidad (por encima de  $10^{12}$  cálculos por segundo) en un chip.

La figura 1 muestra un acoplamiento de coeficiente implementado en la forma de realización preferida de la presente invención. En esta ilustración a título de ejemplo, el acoplamiento de coeficiente presenta dos transistores 101, 102. El primer transistor 101 presenta una entrada 103 para una tensión fuente, y una entrada 104 para una tensión de coeficiente. Además, el primer transistor 101 presenta una salida 105 para proporcionar una corriente al segundo transistor 102, es decir, el primer transistor 101 es un generador de corriente del segundo transistor 102. La tensión de coeficiente usada en la presente invención es programable. La tensión de coeficiente puede programarse por ejemplo, según valores de peso predeterminados mediante algoritmos de filtrado de orden de rango ponderado.

45 El segundo transistor 102 presenta una entrada 106 para la corriente conducida del primer transistor 101 y una entrada 107 para una tensión de control. El segundo transistor 102 también presenta una salida 108 para una corriente de salida. El segundo transistor 102 funciona como un conmutador en un acoplamiento de coeficiente, determinando modos de funcionamiento.

50 En la presente invención, hay tres modos de funcionamiento para un circuito de acoplamiento de coeficiente. El primer modo de funcionamiento se produce cuando el conmutador conduce toda la corriente sin restringir la cantidad de la corriente proporcionada por un generador de corriente. En un primer modo de funcionamiento la tensión de control del segundo transistor es suficientemente alta de modo que no se produce la restricción de la corriente. Normalmente esta tensión es muy próxima a la tensión de alimentación positiva. En tal caso, la tensión de coeficiente del primer transistor define la corriente de salida. En un segundo modo de funcionamiento, un conmutador conduce algo de corriente pero restringe la cantidad de la corriente proporcionada por el generador de corriente. Cuando se produce el segundo modo de funcionamiento, la corriente de salida del acoplamiento está entre el valor de corriente proporcionado por el generador de corriente en un caso ilimitado y 0. En un tercer modo de funcionamiento, el conmutador no conduce nada de corriente. En el tercer modo de funcionamiento, el conmutador no conduce la corriente, porque la tensión de control está en bajo nivel, y por tanto, la corriente de salida del acoplamiento de coeficiente es 0. En esta presentación a modo de ejemplo, el generador de corriente es un transistor PMOS y el conmutador es un transistor NMOS. Otra posibilidad es formar un acoplamiento de coeficiente, en el que un generador de corriente es un transistor NMOS y un conmutador es un transistor PMOS. En este caso, las polaridades de las tensiones son opuestas, es decir, una tensión alta en la descripción anterior será una tensión baja en este caso y viceversa.

65 La figura 2 muestra una estructura que presenta dos generadores de corriente, es decir, transistores 201 y 202. El primer transistor 201 presenta una entrada 203 para una tensión fuente, y una entrada 204 para una tensión de control. Además, el primer transistor 201 presenta una salida 205 para proporcionar una corriente al segundo transistor 202.

## ES 2 315 317 T3

El segundo transistor 202 presenta una entrada 206 para una tensión fuente, y una entrada 207 para una tensión de control. El segundo transistor 202 presenta además una salida 208 para una corriente de salida. La figura 2 también muestra una tensión de salida que es una tensión resultado producida de la diferencia de valor de corriente relativa entre la corriente recibida del primer transistor 201 y la corriente recibida del segundo transistor 202.

En la estructura según la figura 2, el primer transistor 201 tiende a alimentar una corriente de salida a través del segundo transistor 202. El valor de la corriente proporcionada por el primer transistor 201 depende de la tensión de control del primer transistor 201. El segundo transistor 202 puede dejar pasar una corriente, que se define por la tensión de control del segundo transistor 202.

Dependiendo de los valores relativos de las corrientes de salida no restringidas del primer transistor 201 y el segundo transistor 202, la tensión de salida resultado es muy aproximada o bien a una tensión fuente recibida en el primer transistor 201 o a una tensión fuente recibida en el segundo transistor 202, el valor resultado puede estar también entre estos valores. En caso de que la corriente de salida no restringida del primer transistor tienda a ser superior que la corriente de salida no restringida del segundo transistor, el valor de salida resultado es muy aproximado a la tensión fuente del primer transistor. En caso de que la corriente de salida no restringida del segundo transistor tienda a ser superior a la corriente de salida no restringida del primer transistor, el valor de tensión de salida resultado es muy aproximado a la tensión fuente del segundo transistor. En caso de que las corrientes de salida no restringidas sean esencialmente iguales, la tensión de salida resultado está entre los valores de las tensiones fuente del primer transistor y el segundo transistor.

La figura 3 muestra un concepto inventivo de la presente invención. La figura 3 muestra tres circuitos 301, 302 y 303, cada uno de los cuales comprende cuatro transistores, un transistor de polarización 370 y un transistor de salida 380. El circuito 301 comprende cuatro transistores 310, 311, 312 y 313, de los que los transistores 310 y 311 forman una estructura dada a conocer con referencia a la figura 2, y los transistores 312 y 313 forman un acoplamiento de coeficiente dado a conocer con referencia a la figura 1. El transistor 310 funciona como el primer transistor 201 en la figura 2, que presenta entradas similares y una salida, es decir, una entrada 314 para una tensión fuente, una entrada 315 para una tensión de control y una salida 316 para proporcionar una corriente a un transistor 311 siguiente. El transistor 311 funciona como el segundo transistor 202 en la figura 2, que presenta entradas similares y una salida, es decir, una entrada 317 para una tensión fuente, una entrada 318 para una tensión de control y una salida 319 para proporcionar una corriente de salida. Los transistores 312 y 313 forman un acoplamiento de coeficiente que corresponde al acoplamiento de coeficiente dado a conocer con referencia a la figura 1, que presenta entradas (320, 321, 323 y 324) similares y salidas (322 y 325). El acoplamiento de coeficiente (es decir, los transistores 312 y 313) funciona de igual manera que el acoplamiento de coeficiente en la figura 1. El circuito 302 (circuito 303) comprende los transistores 330-333 (350-353), que presentan entradas y salidas 334-345 (354-365), que corresponden a los transistores 310-313 y las entradas y salidas 314-319 del circuito 301. Un transistor de polarización 370 presenta una entrada 371 para una tensión fuente, una entrada 372 para una tensión de control y una salida 373 para proporcionar una corriente de salida del transistor de polarización 370. Un transistor de salida 380, a su vez, presenta una entrada 381 para una tensión fuente, una entrada 382 para una tensión de control y una salida 383 para proporcionar una corriente de salida del sistema. La corriente de salida del transistor de salida 380 puede conducirse por ejemplo, a otro procesador en una red de procesadores paralelos o a una unidad de memoria.

El aparato de la figura 3 puede evaluar la primera, segunda y tercera mayores de las corrientes de salida de los transistores 310, 330 y 350. Un experto en la materia aprecia que aunque existen sólo tres circuitos presentes en esta exposición, el número de circuitos, y por tanto también el número de las corrientes de salida de los primeros transistores, puede ser diferente (por ejemplo, cuatro o más), y el mismo procedimiento de evaluación todavía es aplicable al sistema.

Puede haber una situación en la que sea necesario añadir alguna corriente no negativa en cada corriente de entrada del sistema, cuando se implementa morfología matemática. En esta situación, hay uno o más transistores similares al primer transistor en cada circuito, en el que una corriente de salida del(de los) transistor(es) añadido(s) se suma(n) a la corriente de salida del primer transistor para formar una corriente de salida suma de estos transistores, que se evaluará del mismo modo que la corriente de salida del primer transistor en la siguiente presentación simplificada del proceso aplicado en la presente invención. El(transistor(es) añadido(s) es (son) similar(es) al primer transistor, es decir, en caso de que el primer transistor sea un transistor PMOS el(transistor(es) añadido(s) es (son) también (un) transistor(es) PMOS. Si el primer tipo de transistor es un transistor NMOS, el(transistor(es) añadido(s) es (son) también (un) transistor(es) NMOS.

En esta exposición a título de ejemplo, los transistores 380, 311, 331 y 351 son del mismo tamaño, y debido a que presentan la misma tensión de control (V<sub>cont</sub>) y las mismas tensiones de alimentación, puede entenderse que corrientes de salida no restringidas de los transistores 380, 311, 331 y 351 sean del mismo valor.

A título de ejemplo, la corriente de salida del transistor 310 es superior a la corriente de salida del transistor 330, que a su vez es superior a la corriente de salida del transistor 350. Los transistores 311, 331 y 351, que son por ejemplo transistores NMOS, proporcionan corrientes de salida iguales en un caso no restringido. Además, las tensiones de control de los transistores 312, 332 y 352 son del mismo valor, y los tamaños de los transistores 312, 332 y 352 son los mismos. Aunque las tensiones de control y los tamaños de los transistores 312, 332 y 352 son los mismos en esta presentación a modo de ejemplo, son del mismo tamaño para simplificar la presentación. Las tensiones de control

## ES 2 315 317 T3

y los tamaños de los transistores 312, 332 y 352 pueden diferir por ejemplo de modo que las corrientes de salida de los transistores 312, 332 y 352 se definen en relación a un coeficiente ponderado, por ejemplo, la corriente de salida del transistor 332 es tres veces más grande que los valores de las corrientes de salida de los transistores 312 y 352. La corriente de salida no restringida de los transistores 312, 332 y 352 se denomina corriente de referencia (Iref). En un equilibrio estable algunas de las corrientes de salida de los transistores 312, 332 y 352 pueden no estar restringidas por los transistores de conmutador 313, 333 y 353 adjuntos, respectivamente, algunas de las corrientes de salida pueden estar restringidas por los conmutadores y algunas corrientes de salida pueden ser 0 correspondiendo a los tres modos de funcionamiento descritos con referencia a la figura 1. Las condiciones de equilibrio se controlan por una corriente de polarización, la corriente de salida del transistor de polarización 370, de tal modo que la suma de las corrientes de salida a través de los conmutadores 313, 333 y 353 es igual a la corriente de salida del transistor de polarización 370.

En primer lugar, se examinará el mayor valor de las corrientes de salida de los transistores 310, 330 y 350. El valor de corriente de salida del transistor de polarización 370 se selecciona para estar entre el valor de corriente de referencia y 0 (con una restricción de que el valor no debe ser exactamente 0). El valor de la corriente de salida del transistor de polarización 370 puede ser, por ejemplo, la mitad del valor de la corriente de referencia. Entonces el equilibrio del sistema es según lo que se expone a continuación. La tensión ( $V_{cont}$ ), que es también una tensión de control de los transistores 311, 331 y 351, será un valor tal que el valor de corriente de salida del transistor 311 será igual al valor de corriente de salida del transistor 310. En esta situación, el transistor 313 conducirá parte de la corriente de salida del transistor 312, y el valor de la corriente de salida del transistor 313 es igual al valor de corriente de salida del transistor de polarización 370. Debido a que el valor de la corriente de salida del transistor 331 es superior al valor de la corriente de salida del transistor 330, el valor potencial de la tensión de control del transistor 333 resultará tan bajo que el transistor 333 no conducirá la corriente de salida del transistor 332, es decir, el valor de la corriente de salida del transistor 333 es igual a 0. En esta situación, puede aplicarse lo mismo al circuito 303, es decir, el valor de la corriente de salida del transistor 353 será igual a 0. Debido a que la tensión de control del transistor de salida 380 es también  $V_{cont}$ , el valor de la corriente de salida del transistor de salida 380 será igual a los valores de las corrientes de salida de los transistores 310 y 311 (que son iguales), es decir, la corriente de salida del transistor de salida 380 es igual al valor mayor de las corrientes de salida de los transistores.

A continuación se presentará cómo se evaluará el segundo valor mayor de corriente de salida de los transistores 310, 330 y 350. Para conseguir este resultado, el valor de corriente de entrada del transistor de polarización 370 se seleccionará para estar entre los valores de la corriente de referencia (Iref) y la corriente de referencia multiplicada por dos ( $2*Iref$ ), por ejemplo, el valor de la corriente de entrada del transistor de polarización 370 es la corriente de referencia multiplicada por 1,5 ( $1,5*Iref$ ). En tal situación, el equilibrio del sistema es el siguiente. La tensión de control de los transistores 313, 333 y 353 será un valor tal, en el que los valores de las corrientes de salida de los transistores 330 y 331 será igual. En esta situación, el valor de la corriente de salida del transistor 310 es mayor que el valor de la corriente de salida del transistor 311, y por tanto, la tensión de control del transistor 313 crecerá hasta que el transistor 313 conduzca la corriente de salida del transistor 312. El valor de corriente de salida del transistor 333 es igual al valor en el que el valor de corriente de salida del transistor de polarización 370 se deduce por el valor de corriente de salida del transistor 310, que en este caso es igual a la corriente de referencia (Iref). Debido a que el valor de la corriente de salida del transistor 351 es superior al valor de la corriente de salida del transistor 350, el valor potencial de la tensión de control del transistor 353 resultará tan bajo que el transistor 353 no conducirá la corriente de salida del transistor 352, es decir, el valor de la corriente de salida del transistor 353 es igual a 0. En el equilibrio del sistema, el valor de corriente de salida del transistor 331 es igual al valor de corriente de salida del transistor 330, y debido a que las tensiones de control del transistor 331 y el transistor de salida 380 son iguales, también la corriente de salida del sistema es igual a la corriente de salida del transistor 330.

Si se evalúa el tercer valor mayor de las corrientes de salida de los transistores 310, 330 y 350, puede aplicarse el siguiente proceso. Se conoce que el tercer valor mayor de corriente de salida es también el valor de corriente de salida más pequeño, que en este ejemplo es el valor de corriente de salida del transistor 350. En este ejemplo, se ajustará la corriente de polarización entre  $2*Iref$  y  $3*Iref$ , por ejemplo la corriente de polarización es igual a  $2,5*Iref$ . En una situación de este tipo, el equilibrio del sistema se produce cuando los conmutadores 313 y 333 conducen las corrientes respectivas y el conmutador 353 conduce una cantidad limitada de la corriente recibida del transistor 352. En este caso la corriente de salida del transistor de salida 380 es igual a la corriente de salida del transistor 351, que también es igual a la corriente de salida del transistor 350.

Aunque en la forma de realización anterior, se analizó el valor mayor de corriente de salida, tras lo cual se analizó el segundo valor mayor de corriente de salida, no es necesario analizar los valores de corriente de salida en este orden específico. La presente invención permite hallar cualquier valor de corriente de salida. En general, es posible hallar cualquier valor de corriente de salida ordenado, cuando el valor de corriente de polarización se ajusta entre  $(N-1)*Iref$  y  $N*Iref$ , en el que N es igual al número de orden de rango que se quiere hallar e Iref es el valor de referencia descrito en los párrafos anteriores. En la presente invención, es posible usar la siguiente fórmula para una corriente de polarización para seleccionar el orden de rango (por ejemplo, la sexta mayor) corriente de entrada:

$$(((N-1) + N)/2)*Iref$$

65

Cuando se analiza con la fórmula anterior qué transistor presenta el sexto valor mayor de corriente de salida, N es igual a 6 y el valor de corriente de polarización por tanto es igual a  $5,5*Iref$ .

## ES 2 315 317 T3

Cuando se implementa una red de procesadores paralelos analógicos según la presente invención, la red de procesadores paralelos analógicos comprende una pluralidad de procesadores. La red de procesadores paralelos analógicos comprende además una pluralidad de unidades de memoria. La corriente de salida del transistor de salida 380 se proporciona a una unidad de memoria en una red de procesadores paralelos analógicos, en la que desde la unidad de memoria puede proporcionar una tensión a las entradas 315 (335 y 355 respectivamente) de los transistores 310 (330 y 350 respectivamente) de otro procesador.

En una forma de realización alternativa de la presente invención, el acoplamiento de coeficiente, mostrado en la figura 3, se sustituye por un tipo diferente de acoplamiento. En esta forma de realización de la presente invención el acoplamiento comprende sólo un transistor. El objetivo de la forma de realización alternativa de la presente invención es minimizar el espacio requerido para un procesador en el chip. Para lograr este resultado, debe equilibrarse la función programable del acoplamiento de coeficiente.

En esta forma de realización alternativa de la presente invención, los transistores 312, 332 y 352 se eliminan de los circuitos 301, 302 y 303. Cada uno de los transistores 313, 333 y 353 recibe una tensión fuente y proporciona una corriente de salida para un procesamiento adicional según la función de conmutación de los transistores 313, 333 y 353. La tensión fuente se ajusta preferentemente lo suficientemente baja con el fin de mantener la corriente de unidad (es decir, Iref) prácticamente baja.

Excepto la estructura simplificada del acoplamiento (y la eliminación de la estructura de coeficiente del acoplamiento) que proporciona una función de conmutación del circuito, el proceso de la estructura sigue siendo esencialmente similar a la forma de realización preferida de la presente invención que se describe con respecto a la figura 3.

La figura 4 muestra una forma de realización alternativa del concepto inventivo de la presente invención. La figura 4 muestra tres circuitos 401, 402 y 403, cada uno de los cuales comprende cuatro transistores, un transistor de polarización 470 y un transistor de salida 480. El circuito 401 comprende cuatro transistores 410, 411, 412 y 413. El transistor 410 presenta una entrada 414 para una tensión fuente, una entrada 415 para una tensión de control y una salida 416 para proporcionar una corriente de salida del transistor 410. El transistor 411 presenta una entrada 417 para una tensión fuente, una entrada 418 para una tensión de control y una salida 419 para proporcionar una corriente de salida. Los transistores 412 y 413 forman un acoplamiento de coeficiente que presenta entradas 420, 421, 423 y 424 y salidas 422 y 425. El acoplamiento de coeficiente (es decir, los transistores 412 y 413) funciona de igual manera que el acoplamiento de coeficiente en la figura 3 excepto en que los transistores 412 y 413 son del mismo tipo, por ejemplo, transistores PMOS. Este cambio del tipo de transistor de conmutación 413 también cambia la lógica cuando el commutador 413 conduce o no al opuesto. Este cambio de modos de funcionamiento también requiere el uso del espejo 490 de corriente para invalidar la corriente combinada recibida de los transistores 413, 433 y 453. El espejo 490 de corriente presenta dos transistores 491 y 492, que a su vez presentan entradas 493 y 495 y salidas 493 y 496. Además, el transistor de polarización 470 se ha cambiado también a un transistor PMOS. También el transistor 410 se ha cambiado de un transistor PMOS a un transistor NMOS, y el transistor 411 se ha cambiado de un transistor NMOS a un transistor PMOS.

El circuito 402 (circuito 403) comprende los transistores 430-433 (450-453), que presentan entradas y salidas 434-445 (454-465), que corresponden a transistores 410-413 y las entradas y salidas 414-419 del circuito 401. Un transistor de polarización 470 presenta una entrada 471 para una corriente de entrada, una entrada 472 para una tensión de control y una salida 473 para proporcionar una corriente de salida del transistor de polarización 470. Un transistor de salida 480, a su vez, presenta una entrada 481 para una corriente de entrada, una entrada 482 para una tensión de control y una salida 483 para proporcionar una corriente de salida del sistema. La corriente de salida del transistor de salida 480 puede conducirse por ejemplo, a otro procesador en una red de procesadores paralelos o a una unidad de memoria.

Como en la forma de realización preferida de la presente invención (tal como se ha descrito con referencia a la figura 3), la forma de realización alternativa de la presente invención puede también evaluar la corriente con un número de orden de rango específico del conjunto de las corrientes de salida de los transistores 410, 430 y 450. Lo mismo puede aplicarse a los procesadores que presentan por ejemplo, nueve circuitos, con un procedimiento de evaluación similar tal como se ha aplicado a la forma de realización alternativa de la presente invención.

Puede haber también uno o más transistores similares al primer transistor añadido en cada circuito, en el que una corriente de salida del(de los) transistor(es) añadido(s) se suma(n) a la corriente de salida del primer transistor para formar una corriente de salida suma de estos transistores, que se evaluará del mismo modo que la corriente de salida del primer transistor en la siguiente presentación simplificada del proceso aplicado en la presente invención. El(los) transistor(es) añadido(s) es (son) similar(es) al primer transistor, es decir, en caso de que el primer transistor sea un transistor PMOS el (los) transistor(es) añadido(s) es (son) también (un) transistor(es) PMOS. Si el primer tipo de transistor es un transistor NMOS, el(los) transistor (es) añadido(s) es (son) también (un) transistor(es) NMOS(s).

En esta exposición a título de ejemplo, los transistores 480, 411, 431 y 451 son del mismo tamaño, y debido a que presentan la misma tensión de control (Vcont) y las mismas tensiones de alimentación, puede entenderse que las corrientes de salida de los transistores 480, 411, 431 y 451 son del mismo valor.

## ES 2 315 317 T3

A título de ejemplo, la corriente de salida del transistor 410 es superior a la corriente de salida del transistor 430, que a su vez es superior a la corriente de salida del transistor 450. Los transistores 411, 431 y 451 proporcionan corrientes de salida iguales en un caso no restringido. Además, se supone en este caso que las tensiones de control de los transistores 412, 432 y 452 presentan el mismo valor, y los tamaños de los transistores 412, 432 y 452 son los mismos. La corriente de salida no restringida de los transistores 412, 432 y 452 se denomina corriente de referencia (Iref).

En esta exposición a título de ejemplo, se definirá el valor mayor de las corrientes de salida de los transistores 410, 430 y 450. El valor de corriente de salida del transistor de polarización 470 se ajustará para ser igual a la mitad de la corriente de referencia ( $0,5*Iref$ ). En un equilibrio estable, la corriente de salida del transistor 492 del espejo 490 de corriente es igual a la corriente de salida del transistor de polarización 470, es decir, la corriente de entrada (corriente suma de las corrientes de salida de los transistores 413, 433 y 453) del espejo de corriente es igual a la corriente de salida del transistor de polarización 470. La tensión de control (Vcont) se ha ajustado a un valor en el que la corriente de salida del transistor 411 es igual a la corriente de salida del transistor 410, y por tanto, el transistor 413 conduce parcialmente la corriente de salida del transistor 412.

Debido a que el valor de la corriente de salida del transistor 431 es superior al valor de la corriente de salida del transistor 430, el valor potencial de la tensión de control del transistor 433 resultará tan alto que el transistor 433 no conducirá la corriente de salida del transistor 432, es decir, el valor de la corriente de salida del transistor 433 es igual a 0. En esta situación, lo mismo puede aplicarse al circuito 403, es decir, el valor de la corriente de salida del transistor 453 será igual a 0. Debido a que la tensión de control del transistor de salida 480 es también Vcont, el valor de la corriente de salida del transistor de salida 480 será igual a los valores de las corrientes de salida de los transistores 410 y 411 (que son iguales), es decir, la corriente de salida del transistor de salida 480 es igual al valor mayor de las corrientes de salida de los transistores.

Las otras dos corrientes de salida de los transistores 410, 430 y 450 pueden extraerse ajustando el valor de corriente de salida del transistor de polarización 470 para ser igual a  $1,5*Iref$  (cuando se evalúa el segundo valor mayor de los transistores 410, 430 y 450), ajustando el valor de corriente de salida del transistor de polarización 470 para ser igual a  $2,5*Iref$  (cuando se evalúa el tercer valor mayor de los transistores 410, 430 y 450). La fórmula para hallar qué transistor presenta por ejemplo, el sexto valor mayor de corriente de salida presentado haciendo referencia a la figura 3 también es aplicable a la forma de realización alternativa de la presente invención descrita haciendo referencia a la figura 4.

En una forma de realización alternativa de la presente invención, el acoplamiento de coeficiente mostrado en la figura 4, se sustituye por un tipo diferente de acoplamiento. En esta forma de realización de la presente invención el acoplamiento comprende sólo un transistor.

En esta forma de realización alternativa de la presente invención, los transistores 412, 432 y 452 se eliminan de los circuitos 401, 402 y 403. Cada uno de los transistores 413, 433 y 453 recibe una tensión fuente y proporciona una corriente de salida para su procesamiento adicional según la función de conmutación de los transistores 413, 433 y 453. La tensión fuente se ajusta preferentemente lo suficientemente baja con el fin de mantener la corriente de unidad (es decir, Iref) prácticamente baja.

Excepto la estructura simplificada del acoplamiento (y la eliminación de la estructura de coeficiente del acoplamiento) que proporciona función de conmutación del circuito, el proceso de la estructura sigue siendo esencialmente similar a la forma de realización preferida de la presente invención que se describe con respecto a la figura 4.

Cuando se implementa una red de procesadores paralelos analógicos según la presente invención, la red de procesadores paralelos analógicos comprende una pluralidad de procesadores. La red de procesadores paralelos analógicos comprende además una pluralidad de unidades de memoria. La corriente de salida del transistor de salida 480 se proporciona a una unidad de memoria en una red de procesadores paralelos analógicos, en la que desde la unidad de memoria se proporciona una tensión a la entrada 417 (437 y 457 respectivamente) de los transistores 410 (430 y 450 respectivamente) de otro procesador.

Haciendo referencia a continuación a la figura 5, que es un diagrama de flujo que ilustra el procedimiento de la forma de realización preferida de la presente invención. En la figura 5 en la etapa 501, un primer transistor recibe una tensión fuente y una tensión de control del sistema, y forma una corriente de salida del primer transistor. Esencialmente al mismo tiempo, un segundo transistor recibe una tensión fuente y una tensión de control del sistema, y proporciona una corriente de salida del segundo transistor (etapa 502). El primer transistor tiende a alimentar una corriente de salida a través del segundo transistor. Dependiendo de los valores relativos de las corrientes de salida no restringidas del primer transistor y el segundo transistor, la tensión de salida resultado es muy aproximada o bien a la tensión fuente recibida en el primer transistor o a la tensión fuente recibida en el segundo transistor. Esencialmente al mismo tiempo que las etapas 501 y 502, un tercer transistor recibe una tensión fuente y una tensión de coeficiente y proporciona una corriente de entrada a un cuarto transistor (etapa 503). La tensión de coeficiente recibida en el tercer transistor puede ser programable. En la etapa 504, el cuarto transistor recibe una tensión de entrada (que es una tensión de control del cuarto transistor) definida mediante las corrientes de salida del primer transistor y el segundo transistor, y una corriente de entrada recibida del tercer transistor en el cuarto transistor.

## ES 2 315 317 T3

En la etapa 505, el cuarto transistor determina un modo de funcionamiento basándose en la tensión de entrada recibida del primer transistor y el segundo transistor, y la corriente de entrada recibida del tercer transistor. En caso de que el valor de corriente de salida del primer transistor sea superior al valor de corriente de salida del segundo transistor, el cuarto transistor conduce toda la corriente de entrada recibida del tercer transistor sin restringir la cantidad de la

- 5 corriente proporcionada por el tercer transistor (etapa 506). En este caso la corriente de entrada recibida del tercer transistor define la corriente de salida del cuarto transistor. En caso de que la corriente de salida del segundo transistor sea esencialmente igual a la corriente de salida del primer transistor, el cuarto transistor conduce una cantidad limitada de la corriente de entrada recibida del tercer transistor en el cuarto transistor (etapa 507). En este caso, la corriente de salida del cuarto transistor está entre el valor de corriente de entrada del cuarto transistor y 0. Preferentemente, el valor

10 de la corriente de salida del cuarto transistor es igual a un valor de corriente de salida de un transistor de polarización del sistema, si se extrae una corriente máxima. Si no, el valor de la corriente de salida del cuarto transistor debe ser esencialmente igual a un valor que es la corriente de salida del transistor de polarización menos  $(N-1)*Iref$ , en el que N es igual al número de orden de rango que se extrae. Si el valor de corriente de salida proporcionado por el segundo transistor es superior al valor de corriente de salida proporcionado por el primer transistor, el valor potencial

15 de la tensión de control del cuarto transistor será de modo que el cuarto transistor no conducirá la corriente de entrada recibida del tercer transistor en el cuarto transistor (etapa 508), es decir, la corriente de salida del cuarto transistor es esencialmente igual a 0.

En la etapa 509, la corriente de salida del cuarto transistor se proporciona para su procesamiento adicional en el

20 sistema. En la etapa 510, una tensión de control del segundo transistor, y otros transistores respectivos en un procesador, se forma a partir de la corriente de salida del cuarto transistor junto con otras corrientes de salida recibidas de transistores respectivos del procesador. La corriente suma de la corriente de salida del cuarto transistor y otras corrientes de salida recibidas de transistores respectivos y un transistor de polarización del procesador forma una tensión de control (Vcont), que se conduce al segundo transistor y transistores respectivos en el procesador. La tensión de control

25 (Vcont) se conduce también a un transistor de polarización. La corriente de salida de transistor de polarización se ajusta a un valor en el que puede determinarse una corriente con un número de orden de rango específico del conjunto de las corrientes de salida de los primeros transistores (etapa 511). La corriente de polarización, es decir, la corriente de salida del transistor de polarización, controla unas condiciones de equilibrio de modo que la suma de las corrientes de salida del cuarto transistor y sus transistores respectivos en el procesador es igual a la corriente de salida del

30 transistor de polarización. Esto puede implementarse debido a que la tensión de control del transistor de polarización puede programarse a un cierto valor.

Cuando se evalúa un orden de rango de las corrientes de salida del primer transistor y los transistores respectivos en un procesador, puede aplicarse el procedimiento descrito haciendo referencia a las figuras 3 y 4.

35 Aunque el procedimiento de la presente invención se ha presentado con las etapas en un orden específico en esta presentación, un experto en la materia aprecia que casi cada etapa se produce esencialmente al mismo tiempo en un circuito. Además, sólo las etapas 501, 503 y 511 permanecen constantes durante el procesamiento, y las otras etapas, es decir, las etapas 502, 504-510, tienen lugar todo el tiempo hasta que se alcance el equilibrio del sistema.

40 En un procedimiento alternativo de la presente invención, se elimina la etapa 503, y el "cuarto transistor" (que es un tercer transistor en la forma de realización alternativa de la presente invención) recibe una tensión fuente directamente (en la forma de realización preferida de la presente invención el tercer transistor recibía la tensión fuente y proporcionaba una corriente de entrada del cuarto transistor al cuarto transistor). La forma de realización alternativa

45 de la presente invención corresponde a la forma de realización preferida de la invención en etapas distintas de la etapa 503.

50 El experto en la materia apreciará que pueden introducirse diversas modificaciones en las formas de realización descritas anteriormente sin apartarse del alcance de la presente invención, según se da a conocer en las reivindicaciones adjuntas. Por ejemplo el número de circuitos, en un procesador en una red de procesadores paralelos analógicos, que se evaluará es normalmente superior a 3. Aunque el número de circuitos, y por tanto, también el número de las corrientes de salida del primer transistor y los transistores respectivos en un procesador difieran, sigue aplicándose el mismo procedimiento de evaluación al sistema según se da a conocer en la presente memoria.

55

60

65

**REIVINDICACIONES**

5 1. Circuito (301, 302, 303) para procesar imágenes en una red de procesadores paralelos analógicos, comprendiendo el circuito (301, 302, 303):

10 un subcircuito generador de corriente que comprende un primer transistor MOS (310, 330, 350) dispuesto en serie con un segundo transistor MOS (311, 331, 351), en el que el segundo transistor (311, 331, 351) es del tipo complementario con respecto al primer transistor (310, 330, 350) y en el que el primer transistor (310, 330, 350) y el segundo transistor (311, 331, 351) están dispuestos para recibir las tensiones de alimentación respectivas y para proporcionar las corrientes de salida respectivas, en el que una tensión de salida del subcircuito generador de corriente se determina mediante las corrientes de salida de los primer y segundo transistores y en el que la corriente de salida del segundo transistor se controla mediante una tensión de nodo de suma; y

15 un subcircuito de acoplamiento de coeficiente que comprende un tercer transistor (312, 332, 352) dispuesto en serie con un cuarto transistor (313, 333, 353), en el que el tercer transistor (312, 332, 352) está dispuesto para recibir una tensión de alimentación y para proporcionar una corriente de salida, y en el que el cuarto transistor (313, 333, 353) está dispuesto para recibir la tensión de salida del subcircuito generador de corriente como una tensión de control y la corriente de salida del tercer transistor (312, 332, 352) como una corriente de entrada, y para proporcionar una función de commutación para una corriente de salida de subcircuito de acoplamiento de coeficiente que se proporciona al nodo de suma.

20 2. Procesador en una red de procesadores paralelos analógicos, para procesamiento de imágenes, comprendiendo el procesador:

25 por lo menos dos circuitos según la reivindicación 1;

30 un transistor de polarización (370) acoplado de manera funcional al nodo de suma y dispuesto para proporcionar una corriente de polarización para controlar la suma de las corrientes de salida de los subcircuitos de acoplamiento de coeficiente; y

35 un transistor de salida (380) acoplado de manera funcional al nodo de suma y dispuesto para proporcionar una corriente de salida del procesador, en el que dicha corriente de salida se determina mediante la tensión de nodo de suma.

3. Procesador según la reivindicación 2, en el que el transistor de polarización proporciona una corriente de salida que se ajusta a un valor en el que puede determinarse una corriente con un número de orden de rango específico del conjunto de corrientes de salida del primer transistor, o transistores respectivos.

40 4. Procesador según cualquiera de las reivindicaciones anteriores, en el que cada uno de los subcircuitos de acoplamiento de coeficiente proporciona uno de los tres modos de funcionamiento:

el cuarto transistor conduce la corriente de salida del tercer transistor que le acompaña;

el cuarto transistor conduce una cantidad limitada de la corriente de salida del tercer transistor que le acompaña;

45 el cuarto transistor no conduce la corriente de salida del tercer transistor que le acompaña;

5. Procesador según cualquiera de las reivindicaciones anteriores, en el que el tercer transistor recibe una tensión de coeficiente que es programable.

50 6. Procesador según cualquiera de las reivindicaciones anteriores, en el que el primer transistor presenta una entrada para la tensión de alimentación y una entrada para una tensión de control.

55 7. Procesador según cualquiera de las reivindicaciones anteriores, en el que el segundo transistor presenta una entrada para la tensión de alimentación y una entrada para una tensión de control, en el que la tensión de control se forma a partir de una corriente de salida del cuarto transistor junto con otras corrientes de salida recibidas de los transistores respectivos de un procesador y del transistor de polarización.

60 8. Procesador según cualquiera de las reivindicaciones anteriores, en el que por lo menos uno de los transistores es un transistor PMOS.

9. Procesador según cualquiera de las reivindicaciones anteriores, en el que por lo menos uno de los transistores es un transistor NMOS.

65 10. Procesador según cualquiera de las reivindicaciones anteriores, en el que el procesador comprende además por lo menos un transistor para proporcionar una corriente de salida que se suma con la corriente de salida del primer transistor.

# ES 2 315 317 T3

11. Procedimiento para procesar imágenes en una red de procesadores paralelos analógicos, comprendiendo el procedimiento:

5        recibir una tensión fuente y una tensión de control en un primer transistor MOS (310, 330, 350), y formar una corriente de salida del primer transistor; recibir una tensión fuente y una tensión de control en un segundo transistor MOS (311, 331, 351), dispuesto en serie con dicho primer transistor, en el que el segundo transistor es del tipo complementario con respecto al primer transistor, y formar una corriente de salida del segundo transistor;

10      recibir una tensión fuente y una tensión de coeficiente en un tercer transistor (312, 332, 352), y proporcionar una corriente de entrada a un cuarto transistor (313, 333, 353);

15      recibir una tensión de entrada, que se determina mediante las corrientes de salida del primer transistor (310, 330, 350) y el segundo transistor (311, 331, 351), y una corriente de entrada del tercer transistor (312, 332, 352) en el cuarto transistor (313, 333, 353);

20      activar un modo predeterminado de funcionamiento en el cuarto transistor (313, 333, 353) mediante la tensión de entrada y la corriente de entrada; y proporcionar una corriente de salida del cuarto transistor (313, 333, 353) para su procesamiento adicional.

25      12. Procedimiento según la reivindicación 11, en el que la tensión de coeficiente es programable.

30      13. Procedimiento según la reivindicación 11 ó 12, en el que el modo predeterminado de funcionamiento es uno de los siguientes:

35      el cuarto transistor conduce la corriente de entrada;

40      el cuarto transistor conduce una cantidad limitada de la corriente de entrada; o

45      el cuarto transistor no conduce la corriente de entrada.

50      14. Procedimiento según cualquiera de las reivindicaciones 11 a 13, en el que la corriente de salida del cuarto transistor está prevista para formar una tensión de control del segundo transistor, y otros transistores respectivos en un procesador, junto con otras corrientes de salida recibidas de transistores los respectivos y de un transistor de polarización del procesador en una red de procesadores paralelos analógicos.

55      15. Procedimiento según cualquiera de las reivindicaciones 11 a 14, en el que el procedimiento comprende además un transistor de polarización que proporciona una corriente de salida que se ajusta a un valor en el que puede determinarse una corriente con un número de orden de rango específico del conjunto de corrientes de salida del primer transistor, o transistores respectivos.

60

65

Fig. 1

Fig. 2

Fig. 3

Fig. 4

Fig. 5