(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4271286号

(P4271286)

(45) 発行日 平成21年6月3日(2009.6.3)

(24) 登録日 平成21年3月6日(2009.3.6)

(51) Int.Cl.

H04N 1/405 (2006.01)

G02B 26/10 (2006.01)

F 1

H04N 1/40

G02B 26/10B

Z

請求項の数 8 (全 12 頁)

(21) 出願番号 特願平10-324122

(22) 出願日 平成10年11月13日(1998.11.13)

(65) 公開番号 特開平11-317871

(43) 公開日 平成11年11月16日(1999.11.16)

審査請求日 平成17年11月14日(2005.11.14)

(31) 優先権主張番号 970,816

(32) 優先日 平成9年11月14日(1997.11.14)

(33) 優先権主張国 米国(US)

(73) 特許権者 398038580

ヒューレット・パッカード・カンパニー

HEWLETT-PACKARD COMPANY

アメリカ合衆国カリフォルニア州パロアルト ハノーバー・ストリート 3000

(74) 代理人 100099623

弁理士 奥山 尚一

(74) 代理人 100096769

弁理士 有原 幸一

(74) 代理人 100107319

弁理士 松島 鉄男

(72) 発明者 ロバート・ディー・モリソン

アメリカ合衆国アイダホ州 スターフェラモルツ レイン 11800

最終頁に続く

(54) 【発明の名称】パルス幅変調回路

## (57) 【特許請求の範囲】

## 【請求項 1】

単一パルス同期信号に応答して、多重パルス信号の位相ロックしたパルス幅変調を連続的に変化させるための回路であって、

(a) 現像のためにピクセル・パターンへとイメージを分解してピクセル化し、該ピクセル・パターンに対応する出力信号を与えるためのイメージ生成回路と、

(b) 複数のデータ・ストリームを生成するように前記出力信号を微分する回路と、

(c) 基準信号に同期した複数の位相変調回路であって、複数の遅延ステップにおいて複数のクロック信号を与えるためのクロック生成回路を含むものである、複数の位相変調回路と、

(d) 前記微分された出力信号を受信し、複数の分離したデータ・ストリームを与えるための回路を含み、該位相変調回路に供給される複数のデータ・ストリームのそれぞれに順序づけを行うためのデータ出力選択回路であって、該データ・ストリームのそれぞれが前記位相変調回路の各1つに供給されるものであるデータ出力選択回路と、

(e) 前記位相変調回路の出力信号に応答して、ある走査パターンによってイメージ走査装置を駆動する駆動回路であって、該走査パターンが前記ピクセルのパターンに対応しているものである駆動回路と、

(f) 前記駆動回路に供給される单一の出力信号になるように前記位相変調回路からの前記データを組み合わせるための回路と

を含んでなり、

10

20

前記複数の位相変調回路は、前記複数の分離したデータ・ストリームに対応しており、前記複数の遅延ステップのうちの選択されたステップに従って、前記それぞれのデータ・ストリーム中の前記データを変調するものである回路。

【請求項 2】

( a ) 前記データ出力選択回路は、前記位相変調回路に前記ピクセル・パターンに対応する前記出力信号を供給するものであり、

( b ) 単一の複合イメージのために前記駆動回路に供給されるイメージデータを制限するための回路を含む請求項 1 に記載の回路。

【請求項 3】

单一の複合イメージのために前記駆動回路に供給される前記イメージデータを制限するための回路は、複数の X - O R ゲートを含み、該 X - O R ゲートは、データを单一の変調回路に制限することにより前記位相変調回路を調整できるようにするものである請求項 2 に記載の回路。 10

【請求項 4】

前記複数の遅延ステップにおける複数のクロック信号を前記位相変調回路に与えるためのクロック信号遅延連鎖をさらに含み、該複数のクロック信号は、各遅延ステップにおいて予想された遅延時間に基づいて、所定のピクセルに関して前記イメージ走査装置を駆動するための所定の遅延時間を与えるように決められている請求項 1 に記載の回路。

【請求項 5】

前記データ・ストリームを前記位相変調回路に与えるデータ出力選択回路をさらに含み、該データ出力選択回路が複数のサイクルからなる静止時間を与えるものである請求項 4 に記載の回路。 20

【請求項 6】

( a ) 複数の遅延ステップに対応して複数のクロック信号を前記駆動回路に与えるクロック発生回路と、

( b ) その各々が順次に接続された複数の D フリップ・フロップを含む前記位相変調回路であって、該フリップ・フロップのそれぞれが、該フリップ・フロップの接続順序に順番に対応している前記遅延ステップのそれぞれの遅延素子から信号を受け取るものである前記位相変調回路と、

( c ) 所望の位相変調を与える、前記フリップ・フロップと前記遅延素子の集合体とを含む請求項 1 に記載の回路。 30

【請求項 7】

電子的な走査の解像度を向上するために、データ走査においてデータ強度を制御するための方法であって、

( a ) ピクセル化されたイメージを受信するステップと、

( b ) 該ピクセル化されたイメージを微分することによって、該ピクセル化されたイメージを複数のデータ・ストリームへと分離するステップと、

( c ) 前記微分されたピクセル化されたイメージから得られた情報をを利用して、前記複数のデータ・ストリームの各 1 つを位相変調回路に対して順序づけて、該データ・ストリームに対応する該位相変調回路に前記ピクセル化されたイメージを与えるステップと、 40

( d ) 遅延連鎖を与えるステップと、

( e ) 該遅延連鎖によって設定された時間遅延を備えた前記位相変調回路のそれぞれにおいて前記データ・ストリームを選択するステップと、

( f ) 複数のデータ・ストリームにおける被変調データを組み合わせて、所望の位相変調された単一の出力信号を与えるステップと

を含んでなる方法。

【請求項 8】

( a ) 複数の遅延ステップにおいて遅延連鎖を与えるステップと、

( b ) 互いに順次に接続された複数のフリップ・フロップを利用して、前記遅延連鎖における複数の遅延ステップに対応するフリップ・フロップにクロック信号を与えるステッ 50

と、

(c) 前記フリップ・フロップと前記クロック信号との組み合わせを利用して、前記所望の位相変調された単一の出力信号を与えるステップと

を含む請求項7に記載の方法。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、レーザ・プリンタに用いられるような電子写真イメージ形成装置に関するものである。とりわけ、本発明は、こうした電子写真イメージ形成装置において形成されるイメージ品質を高めるために、光または他のエネルギーの走査ビームの、位相ロックしたパルス幅変調をより正確に制御することに関するものである。 10

【0002】

【従来の技術及びその問題点】

電子写真式プリントでは、プリント・イメージに対応する静電荷パターンが、光学フォトレスエプタ(O P R)上において現像される。そしてトナーがO P Rに塗布され、このトナーが静電荷によってはじかれずに保持されることによってプリント・イメージが形成される。次に、プリント・イメージはプリント媒体(通常は紙)に転写される。

【0003】

O P Rは、可視スペクトル光と、可視光のスペクトル以外の光エネルギーのどちらにも作用する。望ましい実施態様の場合、近赤外レーザ光を用いることが望まれるが、本発明に関連して記載するO P Rは、放射エネルギーに応答するいかなる光学フォトレスエプタをも意味するものである。 20

【0004】

レーザ・プリンタは、レーザ・ダイオードのようなレーザ光源による一連の走査線で光学フォトレスエプタ(O P R)上の感光材料の帯電表面上を走査することによってプリント・イメージを生じる。各走査線はピクセル領域に分割され、レーザ・ビームは、選択されたピクセル領域が露光されるように変調される。この露光によって表面電荷が除去される。従って、O P Rが露光されると、その位置においてO P Rの放電が生じ、その結果、O P R上にトナーが現像され、さらに、トナーがプリント媒体(通常は紙)上の対応する位置に転写される。 30

【0005】

レーザをオン／オフすることは別として、レーザのパワーを変調するのは実際的ではない。制御が困難な、あまりにも多くの環境要因が存在し、非飽和モードにおけるダイオードの動作が役に立たなくなる。しかし、実際のピクセル・サイズ分より短い時間期間にわたくつてレーザを(完全に)オン／オフすることによって同じ効果を得ることが可能である。これは、パルス幅変調信号の標準的な応用例である。さらに、ピクセル部分を右または左へずらしたり、その目立った輝度を修正することが所望される場合がある(例えば対角線に現れるぎざぎざのエッジを防ぐため)。従って、精密に制御されたやり方でレーザをオン／オフできるレーザ・プリンタを提供することが所望される。また、レーザ・ビームの走査に対して位相がロックされるようにしたこのタイプの変調を可能にする設計を提供することも所望される。そうでなければ、連続した線が正確に整列しないからである。 40

【0006】

レーザ光によってO P R電荷の除去が生じる場所に、エマルジョン中のトナー粒子が集中し、イメージが形成される。O P Rの帯電した場所では、トナー粒子がO P Rによって保持されない(非イメージ領域)。これにより、レーザ・プリンタは特にラスタ化されたプリント・パターンに適合することが可能になるが、他のタイプの走査技法に関連するレーザ・プリンタを構成することも可能である。

【0007】

プリンタの解像度は、部分的には、レーザまたは光学素子によって生成される光イメージのサイズの関数である。本発明は、光イメージの強化に向けられたものである。 50

**【 0 0 0 8 】**

本出願の譲受人であるHewlett-Packard Companyは、ピクセル化イメージを生じるハード・コピー装置に関するイメージ品質向上のための技法を開発した。この技法には、プリントしようとするイメージのビット・マップと記憶されている所定のテンプレートまたはパターンを突き合わせて、あらかじめ選択されたビット・マップ・フィーチャの発生を検出するステップが含まれている。一致が生じると、補償パターンが生成され、この結果、プリント品質が向上する。この技法については、譲受人が上と同じである、Charles Chen-Yuan Tunngに対する米国特許第4,847,641号に記載がある。この技法の成果の1つは、対角線のぎざぎざのエッジを緩和するために、対角線のエッジ部分に沿ってピクセルのサイズを変更することができるようになることである。現在のプリントの構成では、解像度を向上させるためには、より高度なアルゴリズムが利用される。10

**【 0 0 0 9 】**

レーザ・プリンタは、ピクセルと呼ばれる固定サイズの選択された小領域に黒のトナーを付着させることによって、ページのプリントを行う。ピクセル領域の一部にだけトナーを付着させることによって、グレーの陰影効果を生じることが可能である。これは、パルス幅変調（Pulse Width Modulation）を利用して実施することが可能である。しかし、パルス幅変調を施すだけでは不十分であり、レーザ走査の開始とピクセルの位相を同期させることも必要になり、「ビーム検出」と呼ばれるレーザ・スキヤナからの単一パルス同期信号によって、走査位相情報が得られる。20

**【 0 0 1 0 】**

ピクセル内における光エネルギー・レベルを変化させる方法がいくつか存在する。一般的な技法の1つであるパルス幅変調（Pulse Width Modulation）はただ単に、ピクセル走査時間内において光学素子（レーザ）に加えられるエネルギーの持続時間を変化させるだけのことである。こうして、エネルギー・レベルは、レーザのパワー出力ではなく、レーザがオンとなっている時間によって設定される。

**【 0 0 1 1 】**

レーザ・プリンタの場合、周波数位相ドリフトを補正するのに有効なフィードバック信号またはエラー信号が存在しないので、先行技術において知られているような位相ロック・ループを利用することはできない。ビーム検出信号によって各走査毎に单一のエッジが得られるのであるが、これは非常に周波数が低いので、位相ロック・ループを形成するのに用いることができない。譲受人が上と同じである米国特許第5,438,353号に記載のクロック発生器によって、本発明に利用可能な位相ロックの説明が得られる。このクロック発生器は、内部遅延連鎖のために発生する量子化効果の制限があるが、その範囲内でビーム検出信号の遷移に対して正確な位相アライメントがとれたクロック信号を発生する。クロック発生器は、一度このアライメントをとってしまうと、次のビーム検出信号が生じるまで再び位相を変化させることはない。レーザが走査を開始すると、ビーム検出信号がプリンタ・エンジンによって生成されるが、これは必然的に走査線1本あたり1回ということになる。30

**【 0 0 1 2 】**

前述の米国特許第5,438,353号には、レーザ駆動回路を駆動するために利用される変調入力信号のタイミング制御について記載されている。本発明は、米国特許第5,438,353号に記載されたクロック発生器の能力を改善するものである。もはや、ピクセルの「ON」または「OFF」をプリントすれば十分であるとはみなされない。つまり、可変ピクセル出力を連続して発生することができる望ましいと考えられる。40

**【 0 0 1 3 】**

レーザ・プリンタは、比較的高速度でページの極めて小さい領域に正確な量のトナーを付着させるその能力によって他のプリンタと区別されており、大部分の他のタイプのプリンタよりはるかに優れた画質が得られる。レーザ・プリンタは、プリント・イメージを保持するドラムまたは他の光学フォトレスポンサを走査することによって機能するので、この結50

果として、ページが光学フォトレスポンサを通過する際に、ページの垂直方向におけるそのイメージ固有の量子化が生じる。さらに、水平走査を変調する回路要素における制限によつてもイメージの量子化が起こるので、単一のセルつまりピクセルが目立つてしまう。ピクセルを十分に小さくすれば、量子化の影響も見分けがつかないほど小さくすることが可能である。しかし、実用上の制限がある。つまり、垂直方向の量子化が、データをシリアル形式で走査レーザに転送する能力によって制限を受けるわけである。

#### 【0014】

レーザ・プリンタの解像度は現在では十分であり、通常、ピクセル・レベルでも量子化は目立たない。一般にアーティファクト (artifacts) と称される干渉効果を生じる、間接的な量子化の影響がいくつか存在する。こうした欠陥は、レーザ・プリンタを用いて写真イメージを再生するとすぐに明らかになる。これは、写真イメージの再生にはハーフ・トーンが多く用いられるためである。プリンタが、量子化された着色領域と無着色領域によって連続して変動するハーフ・トーンの陰影をプリントしようとすると、不自然に見える場合が多い。黒と白（黒の顔料の場合）の領域を混合し、さらに、領域を極めて小さく保つことによって、目に連続したグレイの範囲であるように映るイメージを生じることが可能になる。レーザ出力を変調して、量子化ピクセル要素より小さい、極めて小さい帯電領域と非帯電領域にすれば、プリント写真における不自然さを低減することが可能になる。

#### 【0015】

この問題への取り組みは、位相の異なるいくつかのクロックを設けることによって行われてきた。こうしたアプローチの1つにおいては、クロックの位相が走査線の開始を示すビーム検出信号によってレーザ走査にロックされる。これによって、極めて高い水平ピクセル・レートであっても、1 / 8 ピクセルまでの正確なパルス幅変調を行うことが可能になる。プリンタ・エンジン・テクノロジ及び速度の進歩、並びに質の高い写真イメージをプリントしたいという要望のために、より精密なパルス幅変調方法が必要とされる。

#### 【0016】

先行技法では、電流源及び電圧コンパレータと共にコンデンサが利用されている。該コンデンサに流れる電流から生じる電圧の変化が電圧コンパレータに送られ、その結果、この回路は、制御された時刻においてトリガ・オン／オフする。このシステムには、再初期化時間によって最大動作周波数が制限され、回路がパルス幅変調範囲のどちら側のエンド（0 % 及び 100 %）においても線形性の問題を呈するという、潜在的な欠陥が存在する。また、温度及び電圧に関連した安定性、及びダイ・ロット（部品）のばらつきに関する問題もある。極めて重要な問題は、この技法は周波数が制限されるということである。プリンタの走査速度及びプリント速度は増し続けるものと予想されるので、このようなコンデンサによる方法は有利であるとは言えない。

#### 【0017】

##### 【発明の概要】

本発明によれば、任意に小さくすることが可能な個別遅延素子のサイズによる制約しか受けない、モジュール遅延連鎖内における個別遅延素子のサイズによる制約しか受けない、ラインのプリント中の任意の時間に所望の PWM エッジが得られるようにすることができる、クロック発生器を設けることが可能になる。

#### 【0018】

本発明によれば、例えば、ピクセル・サイズの 1 / 8 に PWM ステップを制限する先行技法とは異なり、ピクセルの連続可変パルス幅変調（PWM）を可能にする方法が得られる。従って、これによって、レーザの変調をより精密に制御する方法が得られる。本発明には、低コストで解像度を高める必要に関する問題を有効に解決する単一位相クロック発生器及び PWM 回路要素が含まれる。本発明の回路は、プリンタのレーザを制御するために用いられる専用集積回路（ASIC）に簡単に組み込むことが可能である。さらに、この技法は、他の方法よりもかなり高いピクセル周波数で実施することができるので、最高速のレーザ・プリンタに用いることが可能になる。

10

20

30

40

50

## 【0019】

クロック発生器から通常に受信する信号に対する調整において、本発明では、データを様々に遅延したものの間で動的にスイッチングすることを企図している。このデータの処理は、既知の安定ポイントを備えたデータ・ストリームを発生させることができるように、事前に実施することが可能である。この安定ポイントによって、位相シフトの選択のための時間が得られる。マルチブレクサによってこの選択が可能になり、マルチブレクスが済むと、全てのデータ・ストリームを再び組み合わせて、所望のレーザ出力信号を再生することが可能になる。

## 【0020】

本発明のシステムは、ピクセル・サイズより短い時間期間のレーザ・パルス持続時間の制御を可能にする。この制御によって、ピクセルの一部を右または左にずらすこととも、その有効強度 (effective intensity) を変化させることも可能になる。本発明によれば、レーザ・プリンタに用いられるタイプの位相同期環境においてこの機能が得られる。 10

## 【0021】

パルス幅変調は、異なる時間にストリームの異なる部分をイネーブルすることによって動的に変化させられ、この結果、パルス幅または位置の変更が可能になる。従って、これらの調整を施し、同時に、レーザを駆動するための振幅を常に 0 か 1 に保つことが可能になる。

## 【0022】

望ましい実施態様によれば、それぞれにおいて静止時間が存在するように符号化された複数のデータ・ストリームが生じる。この静止時間において、全ての遅延タップ (tap) が安定するので、マルチブレクサは、突然のグリッチを生じさせることなく、任意のタップを選択することが可能になる。この静止時間は信号の遊休時間であり、従ってデータ・ストリームに関して言えば、ストリームの非アクティブ時間である。この静止時間を利用すると、準安定の安全なやり方でデータ・ストリームのそれぞれにおいて変調の調整を実施することが可能になる。 20

## 【0023】

実施態様の 1 つでは、それぞれ、3 サイクルの静止時間が得られるように符号化される、4 つのデータ・ストリームが生じる。この静止時間において、全ての遅延タップ・バージョンが安定するので、マルチブレクサは、突然のグリッチを生じさせることなく、安全に任意のタップを選択することが可能になる。この静止時間は、信号の遊休時間であり、従って、データ・ストリームに関して言えば、ストリームの非アクティブ時間になる。静止時間を利用すると、準安定の安全なやり方で、データ・ストリームのそれぞれにおいて変調の調整を実施することが可能になる。 30

## 【0024】

入力データはエッジ検出のような識別形式に変換され、次に、AND ゲート及び X - OR (排他論理和) ゲートを利用して、4 つのストリームに分割される。次に、各ストリームは、順次遅延されたクロック入力によってクロックされるフリップ・フロップ連鎖に供給される。フリップ・フロップの出力は次にマルチブレクサに送られ、静止期間中にフリップ・フロップの出力がスイッチされる。マルチブレクサの出力はまとめて全て X - OR 演算が施され、もとの信号が復元される。 40

## 【0025】

遅延タップはタップ・カウントを備えているが、増進的な調整が所望の解像度を得るのに十分となるように、十分に小さいきざみで備えられている。こういった増進的な調整は、調整のきざみが、光学現像プロセスの残りの部分を精密に制御する能力を超えるほど十分に小さいので、無限調整といつても過言ではない。次に、このタップ・カウントを用いて、レーザ駆動回路を制御するために加えられる信号の正確な持続時間が検出される。これら遅延タップはクロックされてレジスタに記録され、これによって別の回路でカウントすることが可能になる。これによって、各タップの遅延時間を連続的に設定するクロック測定連鎖が確立される。これによって、回路設計は、温度、電圧、または、ダイ・ロット ( 50

コンポーネント) のばらつきから影響を受けないようになる。

#### 【0026】

データ・ストリームの1つはアクティブ・データ・ストリームとなっている。アクティブ・ストリームにおいては、アクティブ(非静止)・サイクル中のデータに、計算されたタップ選択数が伴うが、これは、データが遷移する所望の位相が安全に選択されるように、マルチプレクサによって利用される。全てのストリームがX-OR演算によって再び組み合わされ、もとの信号が復元する。結果生じる出力は、遅延連鎖量子化サイズを限界とするパルス幅変調能力を備えている。望ましい実施態様の場合、これは最悪のケースであるが、約500pSであり、一般にはこの約1/2、すなわち250pSである。この変調は、本発明を用いないで得られる変調の約35~70倍であり、コストまたはフォーマッタの複雑さをそう増やすことなく実現される。10

#### 【0027】

##### 【実施例】

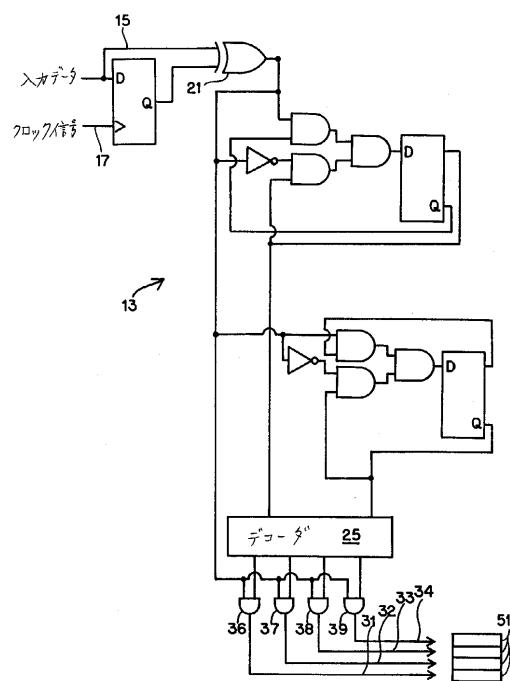

図1には、データ・エンコーダ13の望ましい実施態様が示されている。入力データ15及びクロック信号17を用いて、X-ORゲート21にデータを供給することによって、入力データの微分出力が得られる。次にこのデータはデコーダ25において復号化され、ANDゲート36~39を介して4つのデータ・ストリーム31~34のそれぞれに供給される。デコーダ25は入力データに含まれるイメージ強度情報を用いて、4つのデータ・ストリーム31~34の中から、データを供給するためのデータ・ストリームを選択する。これらの4つのデータ・ストリームは、4つの位相変調回路51の夫々に供給される。各位相変調回路51は、その出力において信号の位相を変化させる。20

#### 【0028】

図1の回路の場合、もとのデータは決してデコーダ25の出力側に通されることはないのであるが、その代わりに、対応するデータ・ストリームの遷移を許可するか否かの制御に用いられる。従って、4つのデータ・ストリームが、まとめてX-OR演算を施すことによって抽出することができる、入力データの間接的に符号化されたコピーであることは明らかである。

#### 【0029】

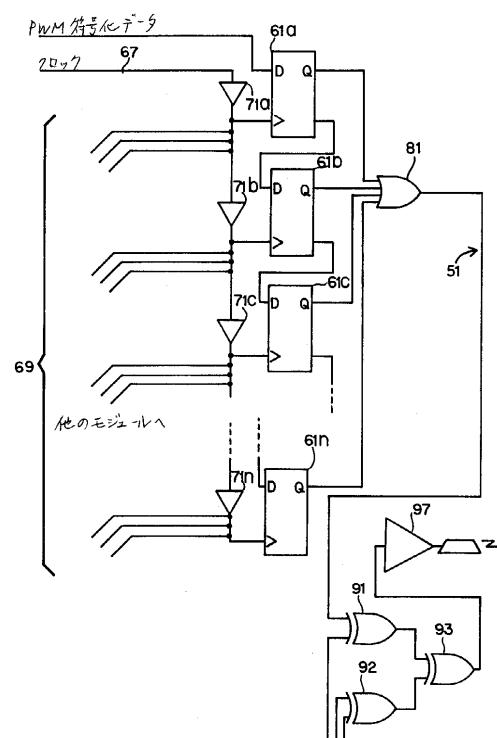

図2には、位相変調回路51が示されている。符号化データは、複数のDフリップ・フロップ61-1~61-n(nは任意の自然数)に選択的に供給される。Dフリップ・フロップ61は、クロック67からのタイミング信号によって同期がとられる。該タイミング信号は、クロック遅延連鎖69を介して伝送される。望ましい実施態様の場合、クロック遅延連鎖は、複数の対をなす反転バッファ71-1~71-n(nは任意の自然数)から構成されるが、他の好都合な遅延素子を用いることも可能である。30

#### 【0030】

遅延連鎖69は、データ・エンコーダ13から供給されるタイミング信号を、連続するDフリップ・フロップ61-1~61-nに順次送り出し、その結果、連続したフリップ・フロップ61からのデータは、増進的に遅延することになる。Dフリップ・フロップ61の出力はORゲート81に供給され、さらに、X-ORゲート91~93に供給される。X-ORゲート91~93は、レーザ・ドライバ97に単一のデータ・ストリームを供給する。40

#### 【0031】

遅延タップはタップ・カウントを備えている。望ましい実施態様の場合、クロック遅延連鎖69の最短遅延時間を基準にして総遅延時間を選択できるように、幾つかのタップが選択される。この最短遅延時間は一般に、動作温度が高く、動作電圧が低いものである。遅延タップは、クロックされてレジスタに記録され、保持されることが可能であり、その結果、別の回路でそのカウントを行うことが可能になる。これによって、クロック測定連鎖が確立される。特定のDフリップ・フロップ61-1~61-nを選択することによって、極めて小さいパルス幅変調のきざみが可能になる。

#### 【0032】

10

20

30

40

50

ANDゲート36～39からの4つのデータ・ストリーム31～34の出力が、位相変調回路51と同じであって、共通遅延連鎖69を共用する個別位相変調回路に供給される。個別位相変調回路の出力は、X-ORゲート<sub>91～93</sub>に供給され、この結果、单一データ・ストリームに対する省略時解釈となるデータの組み合わせ出力が送り出される。こうして、4つのデータ・ストリームのうちの3つにサイクル静止時間が存在することになる。

#### 【0033】

留意すべきは、フリップ・フロップ61の制御によって、3サイクルの静止時間が望ましくなるが、これとは異なる数のデータ・ストリームについても本発明を実施することができるという点である。複数のデータ・ストリームは、タイミング調整を可能にすると同時に、実質的な中断はなしに、レーザ・ドライバ97の順次制御を可能にするために利用される。複数データ・ストリームを利用するこによって、全ての遅延タップが安定するという保証を得ることができるので、マルチブレクサは、予期せぬグリッチを生じさせることなく、安全に任意のタップを選択することが可能になる。

10

#### 【0034】

デコーダが複数の変調回路51のうちの特定の1つを選択する場合、その特定の変調回路51からのデータが、X-ORゲート<sub>91～93</sub>に生じ、そのデータは、レーザ・ドライバ97に与えられるデータになる。

#### 【0035】

変調回路51は同じ遅延連鎖69を共用する。従って、各変調回路51は同様の変調特性を示すので、変調回路51は遅延を生じることなく、連続するピクセルに対して同一の機能を果たすことが可能である。X-ORゲート<sub>91～93</sub>を利用することによって、どの変調回路51が使用可能であるかに関係なく、所望のやり方で変調特性を再構成することが可能になる。対応する出力信号が、レーザ・ドライバ97に与えられる。

20

#### 【0036】

連続するDフリップ・フロップ61をデータ・エンコーダ13に接続することによって、計算論理を利用して連鎖をなす各フリップ・フロップに対するD制御を生成することが可能になる。こうした計算論理は、直接制御を可能にすることで、モジュール51の数を減少させることができる。代わりに、フリップ・フロップ61b～61nの一つ一つが順次、連鎖の中の先行するフリップ・フロップ61a～61(n-1)によって制御されるように、フリップ・フロップ61-1～61-nを接続することも可能である。連続するフリップ・フロップは夫々、反転バッファ71からタイミング信号を得るので、これによつて、図2の構成によつて示されるのと同じ結果が有効に達成される。従つて、各ストリーム毎にデータを発生するための方法がいくつか存在する。

30

#### 【0037】

本発明の説明は、レーザ・プリンタの望ましい実施態様に関連して行ってきた。ピクセル化イメージを生じる他の電子装置においても、本発明の技法を利用することが可能である。こうした装置の一例として、走査パターンを制御して、イメージング強度を制御できるようになると同時に、CRTの走査レートと同期がとれるようになることが所望される、広角CRTが挙げられるであろう。本発明の技法はレーザ・プリンタに特に有効であるが、レーザ・プリンタ以外の走査パターンに利用することができるし、他のタイプのプリンタに利用することも可能である。

40

#### 【0038】

##### 〔実施態様〕

なお、本発明の実施態様の例を以下に示す。

#### 【0039】

〔実施態様1〕 単一パルス同期信号に応答して、複数のパルスを有する信号に対して、位相同期パルス幅変調を連続的に変化させる回路であつて、

(a) イメージを、現像のためのピクセル・パターンに分解してピクセル化し、前記ピクセル・パターンに対応する出力信号(15)を送り出すイメージ生成回路と、

50

( b ) 基準信号に同期した複数の位相変調回路 ( 5 1 ) と、

( c ) 前記位相変調回路 ( 5 1 ) に供給される複数のデータ・ストリーム ( 3 1 ~ 3 4 )

夫々に順序づけを行うデータ出力選択回路 ( 2 5 、 3 6 ~ 3 8 ) と、

( d ) 前記ピクセル・パターンに対応する走査パターンでイメージ走査装置を駆動するた

めの駆動回路 ( 9 7 ) と

を設けてなる回路。

## 【 0 0 4 0 】

〔実施態様 2〕 被変調光エネルギー源の解像度を増すための連続可変位相同期パルス幅変

調回路であって、

- ( a ) イメージを、現像のためのピクセル・パターンに分解することによってピクセル化

し、ピクセル・パターンに対応する出力信号 ( 1 5 ) を送り出すイメージ生成回路と、

10

- ( b ) 前記出力信号 ( 1 5 ) を受信して、複数の分離したデータ・ストリーム ( 3 1 ~ 3

4 ) を送り出すマルチプレクサ ( 2 5 、 3 6 ~ 3 9 ) と、

( c ) 複数の遅延ステップで複数のクロック信号を送り出すクロック発生回路 ( 6 7 、 6

9 ) と、

( d ) 前記複数の分離したデータ・ストリームに対応しており、複数の遅延ステップのうち

の選択された遅延ステップで、それぞれのデータ・ストリーム中のデータに変調を施す

複数の変調回路 ( 5 1 ) と、

( e ) 変調回路 ( 5 1 ) からのデータを組み合わせて、单一出力信号にするための回路 ( 9

1 ~ 9 3 ) と、

20

( f ) ピクセル・パターンに対応する走査パターンで、单一出力信号に応答し、イメージ

走査装置を駆動するための駆動回路 ( 9 7 ) と

を設けて成る回路。

## 【 0 0 4 1 】

〔実施態様 3〕 ( a ) 位相変調回路 ( 5 1 ) にピクセル・パターンに対応する前記出力

信号を供給する回路を含むデータ出力選択回路と、

( b ) 駆動回路 ( 9 7 ) に供給されるイメージ・データを单一の複合イメージに制限する

ための回路 ( 9 1 、 9 2 、 9 3 ) と

をさらに備えることを特徴とする、実施態様 1 または実施態様 2 に記載の回路。

30

## 【 0 0 4 2 】

〔実施態様 4〕 駆動回路 ( 9 7 ) に供給されるイメージ・データを单一の複合イメージ

に制限するための前記回路に、複数の X - O R ゲート ( 9 1 、 9 2 、 9 3 ) が含まれることと、

前記 X - O R ゲート ( 9 1 、 9 2 、 9 3 ) は、データを单一の変調回路 ( 5 1 ) に制限す

ることによって、準安定の安全なやり方で位相変調回路 ( 5 1 ) の調整を可能にすること

を特徴とする、実施態様 3 に記載の回路。

## 【 0 0 4 3 】

〔実施態様 5〕 複数の遅延ステップ ( 7 1 - 1 ~ 7 1 - n ) における複数のクロック信

号を位相変調回路 ( 5 1 ) に加えるクロック信号遅延連鎖 ( 6 9 ) がさらに含まれること

と、

40

前記複数のクロック信号が、各遅延ステップ ( 7 1 ) 毎に予想される最短遅延時間に基づ

いた所定の最悪のケースにおけるピクセルに関して、イメージ走査装置を駆動するための

最大タイミング長を予想していることを特徴とする、実施態様 1 または実施態様 2 に記載

の回路。

## 【 0 0 4 4 】

〔実施態様 6〕 ( a ) 遅延連鎖 ( 6 9 ) を形成するクロック発生器と、

( b ) 前記遅延連鎖 ( 6 9 ) の遅延連鎖量子化サイズの限界までパルス幅変調した信号を

ドライバに供給するデータを組み合わせる、マルチプレクサ ( 2 5 、 3 6 ~ 3 9 ) 及び回

路と

をさらに含むことを特徴とする、実施態様 5 に記載の回路。

50

**【0045】**

[実施態様7] 前記データ・ストリーム(31～34)を位相変調回路(51)に供給し、これによって、複数のサイクルからなる静止時間をもたらし、その結果、安定したやり方で選択を行うことができるようにするデータ出力選択回路をさらに含むことを特徴とする、実施態様5に記載の回路。

**【0046】**

[実施態様8] (a) 複数の遅延タイミング・ステップ(71-1～71-n)に対応する複数のクロック信号を駆動回路(97)に加えるクロック発生回路と、

(b) 連続して接続された複数のDフリップ・フロップ(61-1～61-n)を備えた位相変調回路(51)であって、前記フリップ・フロップ(61-1～61-n)のそれぞれが、フリップ・フロップ(61-1～61-n)の接続順序に順序が対応する遅延タイミング・ステップ(71-1～71-n)のそれぞれから信号を受信する、位相変調回路と、

(c) 所望の位相変調範囲が得られるようにした、フリップ・フロップ(61-1～61-n)と遅延タイミング・ステップ(71-1～71-n)の組み合わせとをさらに含むことを特徴とする、実施態様1または実施態様2に記載の回路。

**【0047】**

[実施態様9] 電子走査の解像度を高めるため、データ走査におけるデータ強度を制御するための方法であって、

(a) ピクセル化イメージを受信する(15)ステップと、

(b) ピクセル化イメージを複数のデータ・ストリーム(31～34)に分離するステップと、

(c) 複数のデータ・ストリーム(31～34)の夫々を位相変調回路(51)に対して順序づけすることによって、前記複数のデータ・ストリームに対応する前記位相変調回路(51)にピクセル化イメージを供給するステップと、

(d) 増進的な遅延連鎖(69)を設けるステップと、

(e) 前記遅延連鎖(69)によって設定された時間遅延で、前記位相変調回路においてデータ・ストリーム(31～34)を選択的に変調するステップと、

(f) 複数のデータ・ストリーム(31～34)における被変調データを組み合わせることによって、変調後、順序づけされたデータのほぼ中断のないデータ出力を可能にするステップと

を設けてなる方法。

**【0048】**

[実施態様10] (a) 複数の遅延タイミング・ステップ(71-1～71-n)において増進的な遅延連鎖(69)を設けるステップと、

(b) 互いに順次接続された複数のフリップ・フロップ(61-1～61-n)を利用して、増進的な駆動連鎖における複数の遅延タイミング・ステップ(71-1～71-n)に対応するタイミング信号を供給するステップと、

(c) フリップ・フロップ(61-1～61-n)と遅延タイミング・ステップ(71-1～71-n)の組み合わせを利用して、所望の位相変調範囲が得られるようにするステップと

を含むことを特徴とする、実施態様9に記載の方法。

**【図面の簡単な説明】**

【図1】本発明に用いられるデータ・エンコーダを示す図である。

【図2】本発明の望ましい実施態様に従って構成された位相変調回路を示す図である。

**【符号の説明】**

13 データ・エンコーダ

15 入力データ

17 クロック信号

21 X - OR ゲート

10

20

30

40

50

|     |           |    |

|-----|-----------|----|

| 2 5 | デコーダ      |    |

| 3 1 | データ・ストリーム |    |

| 3 2 | データ・ストリーム |    |

| 3 3 | データ・ストリーム |    |

| 3 4 | データ・ストリーム |    |

| 3 6 | ANDゲート    | 10 |

| 3 7 | ANDゲート    |    |

| 3 8 | ANDゲート    |    |

| 3 9 | ANDゲート    |    |

| 4 1 | X - ORゲート |    |

| 4 2 | X - ORゲート |    |

| 4 3 | X - ORゲート |    |

| 4 4 | X - ORゲート |    |

| 5 1 | パルス幅変調回路  |    |

| 6 1 | フリップ・フロップ |    |

| 6 7 | クロック      |    |

| 6 9 | クロック遅延連鎖  |    |

| 7 1 | 反転バッファ    |    |

| 9 1 | X - ORゲート | 20 |

| 9 2 | X - ORゲート |    |

| 9 3 | X - ORゲート |    |

| 9 7 | レーザ・ドライバ  |    |

【図1】

【図2】

---

フロントページの続き

審査官 秦野 孝一郎

(56)参考文献 特開平04-023565 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H04N 1/40