(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5144170号

(P5144170)

(45) 発行日 平成25年2月13日(2013.2.13)

(24) 登録日 平成24年11月30日(2012.11.30)

(51) Int.Cl.

F 1

|                     |                  |            |      |

|---------------------|------------------|------------|------|

| <b>H01L 21/60</b>   | <b>(2006.01)</b> | H01L 21/92 | 602P |

| <b>H01L 21/3205</b> | <b>(2006.01)</b> | H01L 21/88 | T    |

| <b>H01L 21/768</b>  | <b>(2006.01)</b> | H01L 21/92 | 602Q |

| <b>H01L 23/522</b>  | <b>(2006.01)</b> | H01L 21/92 | 604T |

請求項の数 5 (全 15 頁)

(21) 出願番号

特願2007-213554 (P2007-213554)

(22) 出願日

平成19年8月20日 (2007.8.20)

(65) 公開番号

特開2009-49170 (P2009-49170A)

(43) 公開日

平成21年3月5日 (2009.3.5)

審査請求日

平成22年8月16日 (2010.8.16)

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

(74) 代理人 100089071

弁理士 玉村 静世

(72) 発明者 秋葉 俊彦

東京都千代田区大手町二丁目6番2号 株式会社ルネサステクノロジ内

(72) 発明者 佐藤 斎尚

東京都千代田区大手町二丁目6番2号 株式会社ルネサステクノロジ内

(72) 発明者 内藤 孝洋

東京都千代田区大手町二丁目6番2号 株式会社ルネサステクノロジ内

最終頁に続く

(54) 【発明の名称】半導体装置の実装方法

## (57) 【特許請求の範囲】

## 【請求項 1】

以下の工程を含むことを特徴とする半導体装置の実装方法：

(a) 第1の面と、前記第1の面に形成され、且つ第1ピッチで配置された複数の第1ランドと、前記第1の面に形成され、且つ前記複数の第1ランドよりも小さく形成され、且つ前記複数の第1ランドよりも前記第1の面の中央部寄りに前記第1ピッチよりも小さな第2ピッチで配置された複数の第2ランドと、前記複数の第1ランドにそれぞれ接続され、且つ第1の高さを有し、且つ第1の径を有する複数の第1バンプと、前記複数の第2ランドにそれぞれ接続され、且つ前記第1の高さよりも小さな第2の高さを有し、且つ前記第1の径よりも小さな第2の径を有する複数の第2バンプと、を備えた半導体装置を準備する工程；

(b) 前記複数の第1バンプを介して前記半導体装置を実装基板に実装し、前記複数の第1バンプおよび前記複数の第2バンプをアンダーフィル樹脂で覆う工程、

ここで、

前記半導体装置は、さらに、回路が形成された半導体集積回路チップを備えており、前記回路として、第1回路と前記第1回路に信号線によって接続される第2回路とを有し、

前記第2回路に接続される外部端子の一部又は全部は、前記第2バンプであり、前記第1回路に接続される外部端子の全部は、前記第1バンプである。

## 【請求項 2】

10

20

請求項 1 記載の半導体装置の実装方法において、

前記複数の第 1 バンプは、前記実装基板への接続に用いられる端子、前記実装基板への接続並びにスクリーニングテスタとの接続に用いられる端子、及び前記実装基板への接続に用いられず、且つスクリーニングテスタとの接続に用いられる端子に割り当てられ、

前記複数の第 2 バンプは、前記実装基板への接続に用いられず且つスクリーニングテスタとの接続に用いられない端子に割り当てられる。

#### 【請求項 3】

請求項 2 記載の半導体装置の実装方法において、

前記複数の第 2 バンプのうちスクリーニングテスタとの接続に用いられない端子は出力端子又は入出力端子である。

10

#### 【請求項 4】

請求項 3 記載の半導体装置の実装方法において、

前記複数の第 1 バンプのうちスクリーニングテスタとの接続に用いられる端子は入力端子である。

#### 【請求項 5】

請求項 1 記載の半導体装置の実装方法において、

前記第 1 回路は、命令を実行する中央処理装置を含み、

前記第 2 回路は、前記中央処理装置によって制御される周辺回路を含む。

#### 【発明の詳細な説明】

##### 【技術分野】

20

##### 【0001】

本発明は、S i P (システムインパッケージ)、B G A (ボールグリッドアレイ)、L G A (ランドグリッドアレイ)、W P P (ウェーハパッケージプロセス)等に代表される面実装のパッケージ形態を有する半導体装置における外部端子の配置構造に関する。

##### 【背景技術】

##### 【0002】

半導体装置の高集積化、高機能化が進むにつれ、多くの機能を 1 つの半導体装置内に内蔵する傾向にある。これにより端子数の増加が進み、単に端子ピッチを確保しながら端子配置を行おうとすればパッケージが大型化する。これによるコスト低減若しくはパッケージの小型化が従来より要請されている。

30

##### 【0003】

本発明完成後の先行技術調査において見出された特許文献 1 には、顧客が使用しない端子（通常は基板と接続する必要がない試験用端子）と顧客が使用する端子をエリア分けし、後者に比べて前者の端子配列を狭ピッチとする技術について記載される。特許文献 2 には、格子状に配置した B G A 動作用外部端子間に L G A (バンプ形成しない) にて検査用端子（検査時にのみ使用する検査端子）を配列する技術について記載されている。

##### 【0004】

【特許文献 1】特開 2004 - 342947 号公報

【特許文献 2】特開 2004 - 22664 号公報

#### 【発明の開示】

##### 【発明が解決しようとする課題】

##### 【0005】

本発明者は半導体装置の限られたスペースに多くの外部端子を配置することについて検討した。例えば、中央処理装置と共に多くの周辺回路を搭載した汎用マイクロコンピュータにおいて、顧客毎に使用する機能が異なる場合、顧客によっては使用されない外部端子が発生する。このとき、使用されない端子を外部端子として設けなければその分だけ外部端子の配列に余裕ができる。しかしながら、半導体製造メーカーは出荷前にデバイステストを行わなければならないから、顧客毎に外部端子の機能が相違されることになれば、回路的に同一の構成を備える半導体装置であっても、テスト項目の制限が相違し、新規テストプログラム開発およびテスト時間増加など、開発量産のコストアップを招く要因となる。

40

50

そこで、顧客が使用する外部端子と使用しない外部端子の双方を配置し、後者の端子配列ピッチを前者よりも小さくすることについて検討した。しかしながら、単にそのような切り分けで端子配列ピッチの大小を決定するだけでは不都合のあることが本発明者によって見出された。第1は、顧客の使用しない端子配列ピッチの小さい端子の高さが顧客の使用する端子配列ピッチの大きな端子と同じ場合、実装基板上において不所望なリークを生じないようにするために、顧客の使用しない端子の直下には配線パターンを形成しない方がよいという制約を生ずる。この点について特許文献1では考慮されていない。第2は、高さを低くするために顧客が使用しない端子をランドだけで形成し、バンプを設けないとすると、不良のために半導体製造メーカーに戻ってきた半導体装置の不良解析を行うためにアンダーフィル樹脂から顧客が使用しない端子を構成するランドを露出させるのに手間がかかる。この点について特許文献2は考慮していない。第3は、顧客が使用しない外部端子であってもスクリーニングに使用する場合があり、そのような外部端子の配置ピッチが小さい場合にはスクリーニングテスタのテスター端子をそれに対応させなければならず、テスターのコストアップを招く。この点について特許文献1, 2では考慮されていない。スクリーニングテストは通常動作よりも過大な動作電圧及び動作タイミングを与えて動作させるテストであり、デバイスの機能テストのように回路の機能を全て検証することを要しないから、全ての外部端子を用いなくてもよい。出力端子又は入出力端子に接続される回路に対してはその出力機能を利用することにより、内部の回路動作を介して加速試験に適するタイミングや電圧の信号を外部インターフェースバッファまで伝達することが可能である。よって、スクリーニングに利用する外部端子は選別可能である。この意味で、スクリーニングテストに用いる外部端子については端子数を制限できる可能性があることから、他のテスト端子同様にそのピッチを小さくしなくとも済む余地が残されていることが本発明者によって明らかにされ。10

#### 【0006】

本発明の目的は、外部端子との不所望なリークを抑制するための実装基板側の制約を緩和することができる半導体装置を提供することにある。

#### 【0007】

本発明の別の目的は、不良解析等のためにアンダーフィル樹脂から外部端子を露出させることが容易な半導体装置を提供することにある。

#### 【0008】

本発明の更に別の目的はスクリーニングテストのコストアップを抑制することができる半導体装置を提供することにある。30

#### 【0009】

本発明の前記並びにその他の目的と新規な特徴は本明細書の記述及び添付図面から明らかになるであろう。

#### 【課題を解決するための手段】

#### 【0010】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば下記の通りである。

#### 【0011】

すなわち、半導体装置の外部端子を相対的に径とピッチが大きなバンプと小さなバンプに分け、前者よりも後者を半導体装置の中央寄りに配置する。大きなバンプの一部は半導体装置を実装する実装基板との接続に用いられ、大きなバンプの残りは実装基板への接続には用いないがスクリーニングテスターへの接続に用いられる。小さなバンプは半導体装置を実装する実装基板との接続にもスクリーニングテスターとの接続に用いられない。これにより、実装基板側では小さなバンプの領域直下に配線パターンがあつても不所望なリークの虞は無い。小さなバンプがアンダーフィル樹脂で覆われていても、表面を削ることによって容易に露出させることができ、小さなバンプの代わりにランドだけを設けた場合に比べ、不良解析のための端子露出作業が容易になる。スクリーニングテスターと接続される外部端子はピッチと径が共に大きくされているのでスクリーニングテストに特別なピンピッ4050

チ変換アダプタ等を必要とせず、プローブに対するD U Tとしての半導体装置の位置決めについても特に高精度を要しない。

**【発明の効果】**

**【0012】**

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば下記のとおりである。

**【0013】**

すなわち、外部端子との不所望なリークを抑制するための実装基板側の制約を緩和することができる。

**【0014】**

また、不良解析等のためにアンダーフィル樹脂から外部端子を露出させることが容易である。

10

**【0015】**

また、テスターのコストアップを抑制することができる。

**【発明を実施するための最良の形態】**

**【0016】**

1. 実施の形態の概要

先ず、本願において開示される発明の代表的な実施の形態について概要を説明する。代表的な実施の形態についての概要説明で括弧を付して参照する図面中の参照符号はそれが付された構成要素の概念に含まれるものを見示すに過ぎない。

20

**【0017】**

[1] 本発明の代表的な実施の形態に係る半導体装置(1)は、回路が形成された半導体集積回路チップ(2)を有する。この半導体装置は、所定ピッチで配置された複数の第1外部端子(P<sub>us</sub>, P<sub>u</sub>, P<sub>s</sub>)と、前記第1外部端子よりも半導体装置の中央部寄りに最小ピッチが前記所定ピッチよりも小さなピッチで配置された複数の第2外部端子(P)とを有する。前記第1外部端子は第1ランド(LND1)に接続された第1バンプ(BMP1)によって形成される。前記第2外部端子は前記第1ランドよりも小さな第2ランド(LND2)に接続され前記第1バンプよりも高さと径が小さな第2バンプ(BMP2)によって形成される。これにより、実装基板側では第2バンプの領域直下に配線パターンがあつても不所望なリークの虞は無い。第2バンプがアンダーフィル樹脂で覆われていても、表面を削ることによって容易に露出させることができ、第2バンプの代わりにランドだけを設けた場合に比べ、不良解析のための端子露出作業が容易になる。

30

**【0018】**

一つの具体的な形態として、前記複数の第1外部端子は、半導体装置を実装する実装基板への接続に用いられる端子(P<sub>u</sub>)、前記実装基板への接続並びにスクリーニングテスターとの接続に用いられる端子(P<sub>us</sub>)、及び前記実装基板への接続に用いられず且つスクリーニングテスターとの接続に用いられる端子(P<sub>s</sub>)に割り当てられる。前記複数の第2外部端子は、前記実装基板への接続に用いられず且つスクリーニングテスターとの接続に用いられない端子(P)に割り当てられる。このような端子割り当てにより、実装基板側では第2バンプの領域直下に配線パターンがあつても不所望なリークの虞は無い。第2バンプがアンダーフィル樹脂で覆われていても、表面を削ることによって容易に露出させることができ、第2バンプの代わりにランドだけを設けた場合に比べ、不良解析のための端子露出作業が容易になる。実装基板との接続の可否に拘わらずスクリーニングテスターと接続される外部端子はピッチと径が共に大きな第1バンプで形成されているのでテスターに特別なピンピッチ変換アダプタ等を必要とせず、また、プローブに対するD U Tとしての半導体装置の位置決めについても特に高精度を要しない。

40

**【0019】**

[2] 別の実施の形態に係る半導体装置は、上記半導体装置に比べて、第2外部端子が前記第1ランドよりも小さな第2ランドによって形成されている点が相違され、第1外部端子と第2外部端子に対する端子機能の割り当ては同一とされる(図1の(D), (E))

50

)。これによれば、第2外部端子を形成するのにバンプを形成する手間がない半面、不良解析のために第2外部端子をアンダーフィル樹脂から露出させる作業に手間がかかる。その他の作用効果は上記同様である。

#### 【0020】

[3]更に別の実施の形態に係る半導体装置は、上記半導体装置に比べて、第1外部端子が第1ランドにより、第2外部端子が第2ランドにより形成されている点が相違され、第1外部端子と第2外部端子に対する端子機能の割り当ては同一とされる(図1の(F),(G))。これによれば、バンプを形成する手間はないが、スクリーニングテスト等においてプローブを直接ランドに接触させるため、接触圧力が高すぎたり、DUTに対するプローブの位置決め制度が低すぎる場合には、半導体チップに機械的なダメージを与える虞がある。10

#### 【0021】

[4]上記それぞれの半導体装置における更に具体的な形態として、前記複数の第1外部端子のうちスクリーニングテストとの接続に用いられない端子は出力端子又は入出力端子である。出力端子又は入出力端子に接続される回路に対してはその出力機能を利用することにより、内部の回路動作を介して加速試験に適するタイミングや電圧の信号を外部インターフェースバッファまで伝達することが可能である。したがって、スクリーニングのみに利用される端子数の削減に資することができる。

#### 【0022】

また、前記複数の第1外部端子のうちスクリーニングテストとの接続に用いられる端子は入力端子である。上記より明らかのように少なくとも入力端子についてはスクリーニング用端子とするのがよい。20

#### 【0023】

更に具体的な形態として前記回路は、第1回と前記第1回路に信号線によって接続される第2回路とを有する。前記第2回路に接続される外部端子の一部又は全部は前記第2外部端子であり、前記第1回路に接続される外部端子の全部は前記第1外部端子である。第2回路の一部に使用しない回路が含まれていても、その回路はテスト対象になる。第2回路は第1回路に信号線で接続されているので当該使用されない回路の故障は他の回路の誤動作の原因になるからである。使用しない回路に第2外部端子を接続する意義はここにある。第2回路が第1回路に信号線で接続されていなくても、外部電源端子が共通化されている場合、クロストークや誘導によるノイズ伝播等による悪影響等を考慮すれば、第2外部端子を設ける意義のあることは言うまでもない。30

#### 【0024】

更に具体的な形態として、前記第1回路は命令を実行する中央処理装置を含み、前記第2回路は前記中央処理装置によって制御される周辺回路を含む。マイクロコンピュータ等の半導体装置において使用される周辺回路は顧客毎に相違する場合があるからである。

#### 【0025】

また、別の具体的な形態として、前記半導体集積回路チップを単数又は複数有し、半導体集積回路チップを一面に搭載し、他面に前記第1外部端子及び第2外部端子が形成された配線基板を有する、グリッド・アレイ・パッケージ形態を半導体装置に採用することができる。グリッド・アレイ・パッケージ形態とはBGA又はLGA等のパッケージ形態である。40

#### 【0026】

また、別の具体的な形態として、前記半導体集積回路チップのボンディングパッド形成面の上にボンディングパッドに接続して延在する引き出し配線が形成され、前記第1外部端子及び第2外部端子は対応する引き出し配線の先端部に形成された、ウェーハ・プロセス・パッケージ形態を半導体装置に採用してもよい。

#### 【0027】

[5]更に別の実施の形態に係る半導体装置は、上記各実施の形態の半導体装置における第1外部端子のうち前記実装基板への接続に用いられず且つスクリーニングテストとの50

接続に用いられる端子を大きさと径の小さな端子(PPs)に変更し、第2外部端子よりも大きなピッチだけを維持するようにしたものである。

#### 【0028】

更に詳しくは、前記第1外部端子を、第1ランドに接続された第1バンプ(BMP\_F)と、前記第1ランドよりも小さな第2ランドに接続され前記第1バンプよりも高さと径が小さな第2バンプ(BMP\_S)とによって形成する。前記第2外部端子を、前記第1ランドよりも小さな第3ランドに接続され前記第1バンプ電極よりも高さと径が小さい第3バンプ(BMP\_T)によって形成する。前記複数の第1バンプは、半導体装置を実装する実装基板への接続に用いられる端子、及び前記実装基板への接続並びにスクリーニングテスタとの接続に用いられる端子に割り当てられる。前記第2バンプは、前記実装基板への接続に用いられず且つスクリーニングテスタとの接続に用いられる端子に割り当てられる。前記複数の第3バンプは、前記実装基板への接続に用いられず且つスクリーニングテスタとの接続に用いられない端子に割り当てられる。10

#### 【0029】

これによれば、先に説明した実施の形態に比べて、スクリーニングテストにおいてプローブに対するDUTとしての半導体装置の位置決め高精度を高くすることが必要になる点を除いて上記同様の作用及び効果を得る。

#### 【0030】

この実施の形態に対し、前記第2外部端子を前記第1ランド(LNF\_F)よりも小さな第3ランド(LND\_T)で形成する変更、また、前記第1外部端子及び第2外部端子の全てをランドで形成する変更を採用することも可能である。20

#### 【0031】

##### 2. 実施の形態の詳細

実施の形態について更に詳述する。

#### 【0032】

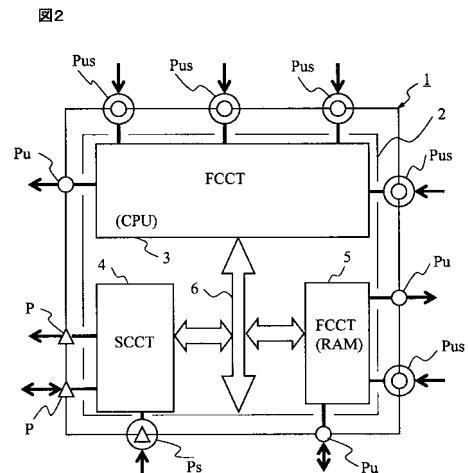

図2には本発明に係る半導体装置のブロック図が例示される。同図に示される半導体装置1は例えばCMOS集積回路製造技術等により単結晶シリコンのような1個の半導体チップに形成された半導体集積回路チップ2を有する。半導体集積回路チップ2は第1回路(F CCT)3, 5及び第2回路(SCCT)4を備え、それらはバス6で接続される。第1回路3, 5は例えば命令をフェッチして実行する中央処理装置(CPU)及びCPUのワーク領域等に用いられるランダムアクセスメモリ(RAM)を有する。第2回路4はCPUの周辺回路とされ、例えばタイマ(TMR)、シリアル・コミュニケーション・インターフェース(SCI)、ADC(アナログ・ディジタル・コンバータ)、DAC(ディジタル・アナログ・コンバータ)、ウォッチャ・ドッグ・タイマ(WDT)、ディジタル・シグナル・プロセッサ(DSP)等の回路を有する。30

#### 【0033】

半導体集積回路チップ2はBGA、LGA又はWPP等の面実装型のパッケージ形態で封止され、そのパッケージには外部端子として代表的に示された外部端子Pu\_s, Pu, Ps, Pが配置される。ここでは第2回路4を使用しない場合を一例とするもので、第1回路3, 5は、半導体装置1を搭載して用いる実装基板(図示せず)に接続され、他方の第2回路4は実装基板との接続は必要とされない。前記外部端子Puは半導体装置1を実装する実装基板への接続に用いられスクリーニングテスタとの接続に用いられない端子、前記端子Pu\_sは前記実装基板への接続並びにスクリーニングテスタとの接続に用いられる端子である。前記端子Psは前記実装基板への接続に用いられず且つスクリーニングテスタとの接続に用いられない端子であり、前記端子Pは前記実装基板への接続に用いられず且つスクリーニングテスタとの接続に用いられない端子である。要するに、端子Pu\_s, Puは実装基板に接続される端子、P, Psは実装基板に接続されない端子である。スクリーニングテスタに接続される端子Pu\_s, Psは実装基板に接続される端子と接続されない端子の双方に跨っている。外部端子Pu\_s, Pu, Psのサフィックス“u”は実装基板に接続されることを意味し、サフィックス“s”はスクリーニングテスタに接続され4050

ることを意味する。

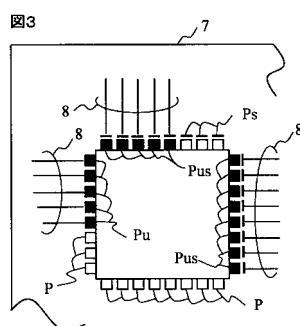

**【0034】**

図3には半導体装置1を実装基板に搭載した状態が例示される。7は実装基板であり、8は半導体装置1が接続される配線パターンを総称し、前記端子Pus, Puに接続される。

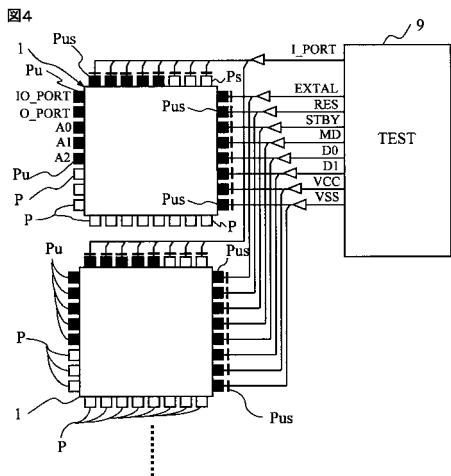

**【0035】**

図4には複数個の半導体装置1がスクリーニングテスタ(TEST)9に接続された状態を例示する。スクリーニングテスタ9に接続された端子Pus, Psは、例えば入力ポート端子I\_PORT、クロック入力端子EXTAL、リセット信号入力端子RES、スタンバイ信号入力端子STBY、モード信号入力端子MOD、データ入力端子D0~D1、電源端子VCC, グランド端子VSSとされる。実装基板7に接続される端子のうちスクリーニングテスタに非接続の端子Puは、例えば出力ポート端子IO\_PORT、出力ポート端子O\_PORT、アドレス出力端子A0~A2とされる。尚、図3、図4における外部端子P, Pus, Ps, Puは作図上半導体装置1の縁辺に沿って図示してあるが、実際にはBGA, LGA, WPPのパッケージ形態の配列になっている。また、端子の数も作図上相違されるが実際には整合されている。

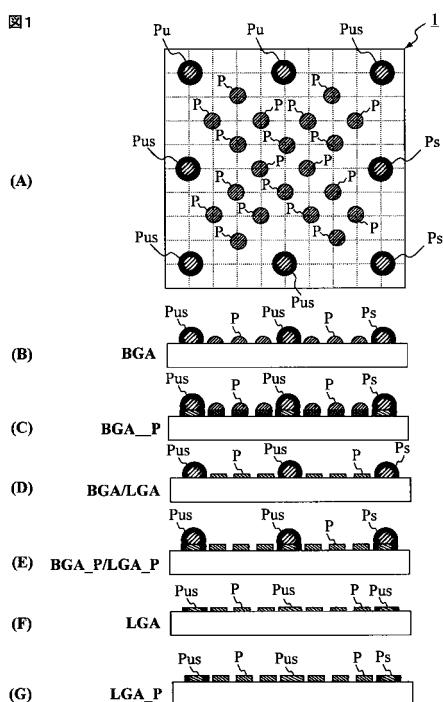

**【0036】**

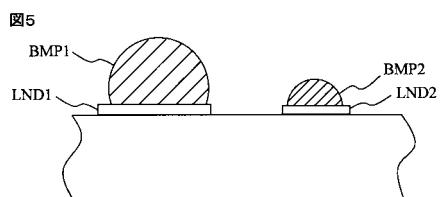

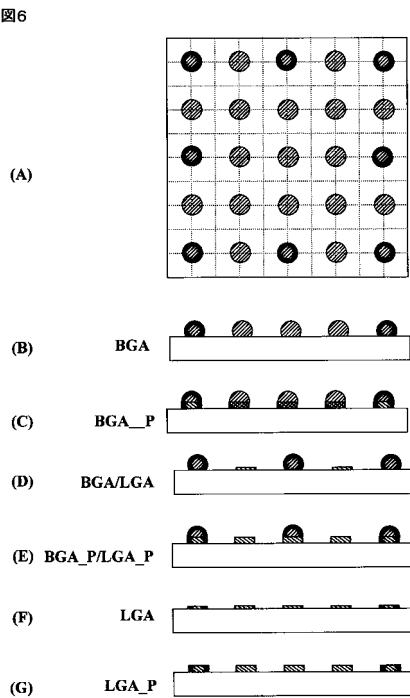

図1には本発明に係る半導体装置の外部端子の配列が例示される。図1の(A)は平面図、(B)~(G)は正面図である。図1の(A)に例示されるように半導体装置1において、前記端子Pus, Pu, Psは所定ピッチ例えばxy方向に1mmピッチで配置された第1外部端子を構成する。前記端子Pは前記第1外部端子Pus, Pu, Psよりも半導体装置1の中央部寄りに最小ピッチが前記1mmピッチよりも小さなピッチで配置された第2外部端子を構成する。前記第1外部端子Pus, Pu, Psは図5に例示されるように第1ランドLND1に接続された第1バンプBMP1によって形成される。前記第2外部端子Pは前記第1ランドLND1よりも小さな第2ランドLND2に接続され前記第1バンプBMP1よりも高さと径が小さな第2バンプBMP2によって形成される。図1の(B)にはランドLND1, LND2の図示を省略してある。図1の(B)は第1外部端子Pus, Pu, Ps及び第2外部端子Pともにバンプで形成したBGAパッケージ形態の側面断面を概略的に示している。(C)のようにランドを厚く形成した構造(BGA\_Pパッケージ形態)、(D)のように第2外部端子Pをランドで形成した構造(BGA/LGAパッケージ形態)を採用する事も可能である。また、図1の(E)のように(D)の形態においてランドを厚く形成した構造(BGA\_P/LGA\_Pパッケージ形態)、(F)のように第1外部端子Pus, Pu, Ps及び第2外部端子Pともにランドで形成した構造(LGAパッケージ形態)、又は(G)のように(F)の形態においてランドを厚く形成した構造(LGA\_Pパッケージ形態)を採用することも可能である。

**【0037】**

図6には図1の外部端子構造に対して第1外部端子Pus, Pu, Ps及び第2外部端子Pの全てを等しいピッチで且つ等しい大きさで形成した場合の比較例が示される。図6の(A)は平面図、(B)~(G)は正面図である。図6の(A)~(G)は図1の(A)~(G)に対応される。

**【0038】**

上記半導体装置1によれば以下の作用効果を得る。

**【0039】**

[1]図1(B)のBGA形態、(C)のBGA\_P形態、(D)のBGA/LGA形態、(E)のBGA\_p/LGA\_P形態においては第2外部端子Pは第1外部端子Pu, Ps, Puに比べ高さと径が小さいから、実装基板7では第2外部端子Pの領域直下に配線パターンがあつても不所望なリークの虞は無い。

**【0040】**

[2]図1(B)のBGA形態、(C)のBGA\_P形態では、第2電極Pがアンダーフィル樹脂で覆われていても、表面を削ることによって容易に露出させることができ、(

10

20

30

40

50

D) の LGA 形態のように第 2 電極 P をバンプの代わりにランドだけで形成した場合に比べ、不良解析のための端子露出作業が容易になる。要するに、第 2 電極を覆っているアンダーフィル樹脂の切削代を多く取ることができ、半導体集積回路チップの回路領域を損傷させる虞を未然に回避することができる。

#### 【0041】

[3] 実装基板 7 との接続の可否に拘わらずスクリーニングテスタ 9 と接続される外部端子 P<sub>s</sub>, P<sub>us</sub> は図 1 の (B)、(C)、(D)、(E) の形態ではのピッチと径が共に大きなバンプで形成されているのでスクリーニングテスタ 9 に特別なピンピッチ変換アダプタ等を必要とせず、また、プローブに対する DUT としての半導体装置 1 の位置決めについても特に高精度を要しない。これによって、スクリーニングテストのテストコストを低減することが可能になる。図 1 の (F)、(G) の形態では第 2 外部端子 P は上記と同じ大きなピッチで配置されているが、ランド若しくはランドを厚くしたポストによって形成されているので、プローブに対する DUT としての半導体装置 1 の位置決めについては (B)、(C)、(D)、(E) の形態に比べて高精度を要する。プローブによる半導体集積回路チップの回路領域に対する機械的なダメージを小さくしなければならないからである。スクリーニングテスタに特別なピンピッチ変換アダプタを必要としないことは上記同様である。

#### 【0042】

[4] 前記複数の第 1 外部端子 P<sub>us</sub>, P<sub>s</sub>, P<sub>u</sub> のうちスクリーニングテスタとの接続に用いられない端子 P<sub>u</sub> は出力端子又は入出力端子であり、出力端子又は入出力端子に接続される回路に対してはその出力機能を利用することにより、内部の回路動作を介して加速試験に適するタイミングや電圧の信号を外部インターフェースバッファまで伝達することが可能である。したがって、スクリーニングのみに利用される端子数を削減することができ、ひいては、大きなピッチで配置すべき大きな外部端子の数が多くなり過ぎるのを抑制することができる。

#### 【0043】

[5] 汎用マイクロコンピュータのような半導体装置 1 の内部回路の一部に特定顧客が使用しない回路がある場合でも当該回路の削減や内部バスからの切り離しを行わないようにすることにより、半導体装置を製造するためのマスクパターンの変更を要しない。このとき、特定顧客が使用しない回路に対してもデバイステストの対象になる。例えば図 2 のように使用しない回路 4 はバス 6 を介して第 1 の回路 3, 5 に影響を与える場合もあるからである。したがって、図 2 の外部端子 P のように特定ユーザには使用されない端子は少なくともデバイステストのために配置することが必須であるが、端子ピッチ及び端子サイズを小さくすることによってパッケージの小型化に寄与する。

#### 【0044】

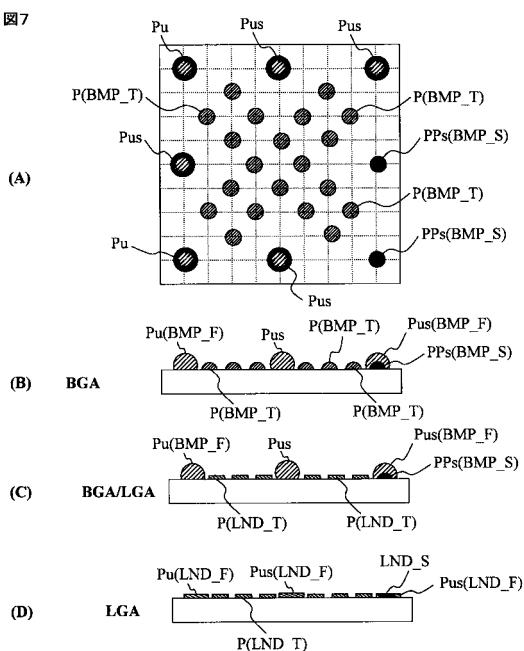

図 7 には半導体装置の別の例が示される。図 7 の (A) は平面図、(B) ~ (D) は正面図である。同図に示される半導体装置 1 A は、図 1 で説明した半導体装置 1 に対し、実装基板への接続に用いられずスクリーニングテスタとの接続に用いられる外部端子を P<sub>P<sub>s</sub></sub> のように小さく形成した点が相違される。外部端子 P<sub>P<sub>s</sub></sub> もその他の第 1 外部端子 P<sub>us</sub>, P<sub>u</sub> と同じピッチで配置されている。即ち、前記外部端子 P<sub>us</sub>, P<sub>u</sub> を、第 1 ランドに接続された第 1 バンプ B M P\_F とによって形成し、前記外部端子 P<sub>P<sub>s</sub></sub> を前記第 1 ランドよりも小さな第 2 ランドに接続され前記第 1 バンプよりも高さと径が小さな第 2 バンプ B M P\_S によって形成する。前記外部端子 P を、前記第 1 ランドよりも小さな第 3 ランドに接続され前記第 1 バンプよりも高さと径が小さいた第 3 バンプ B M P\_T によって形成する。その他の構成は図 1 と同じであるからその詳細な説明は省略する。図 7 では (A) の平面図の他、(B) の BGA 形態、(C) BGA / LGA 形態、及び (D) の LGA 形態の概略側面断面構造を例示する。これによれば、先に説明した図 1 の構造に比べて、スクリーニングテストにおいてプローブに対する DUT としての半導体装置の位置決め高精度を高くすることが必要になる点を除いて上記同様の作用及び効果を得る。

#### 【0045】

10

20

30

40

50

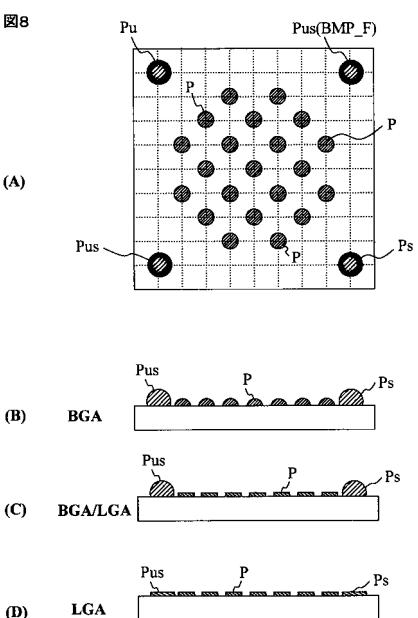

図8には第1外部端子P<sub>us</sub>, P<sub>u</sub>, P<sub>s</sub>及び第2外部端子Pの数や配置の異なる別の例が示される。図8の(A)は平面図、(B)~(D)は正面図である。図1に比べて第1外部端子P<sub>us</sub>, P<sub>u</sub>, P<sub>s</sub>のピッチが大きくされ、第2外部端子Pの配列形態が相違される。この配列において図1と同様の作用効果を得る。

#### 【0046】

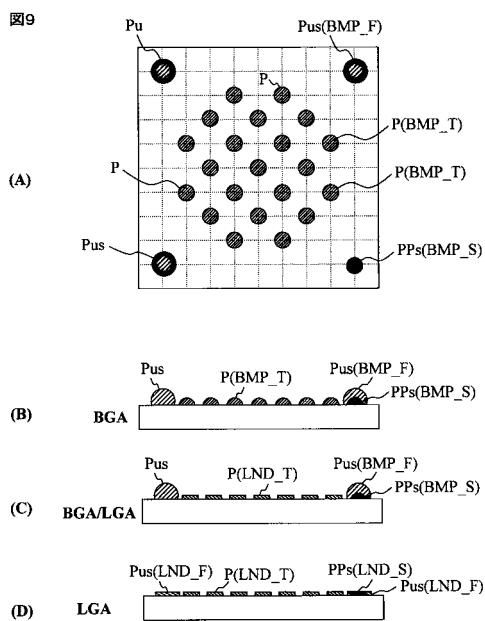

図9には図8の端子配列に対し、スクリーニングテスターとの接続のみに用いられる外部端端子PPSのように第3バンプBMP\_Tにより小さく形成した構成が例示される。図9の(A)は平面図、(B)~(D)は正面図である。外部端子PPSもその他の第1外部端子P<sub>us</sub>, P<sub>s</sub>と同じピッチで配置されている。この構成においても図7と上記同様の作用及び効果を得る。

10

#### 【0047】

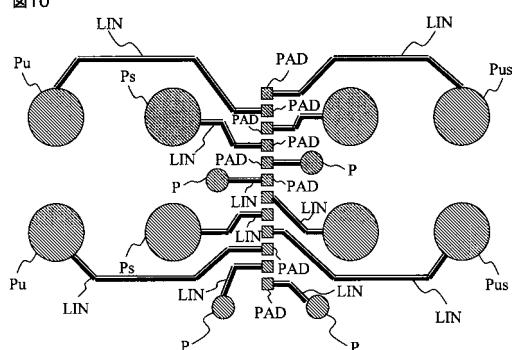

図10にはWPPパッケージ形態における端子配列が例示される。WPPパッケージ形態では半導体集積回路チップのボンディングパッド形成領域PADの上にボンディングパッドPADに接続して延在する引き出し配線LINが形成され、前記第1外部端子P<sub>us</sub>, P<sub>u</sub>, P<sub>s</sub>及び第2外部端子Pは対応する引き出し配線LINの先端部に例えば半田バンプ電極によって形成される。WPPパッケージ形態においても図1の場合と同様の作用効果を得る。

#### 【0048】

以上本発明者によってなされた発明を実施形態に基づいて具体的に説明したが、本発明はそれに限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは言うまでもない。

20

#### 【0049】

例えば、バンプの形状は球形に限定されず、立方体形状、逆三角錐台形状、逆円錐台形状等であってもよい。外部端子の数、一つのパッケージに納められる半導体集積回路チップの数、第1回路及び第2回路の具体的な種類や数等については適宜変更可能である。

#### 【0050】

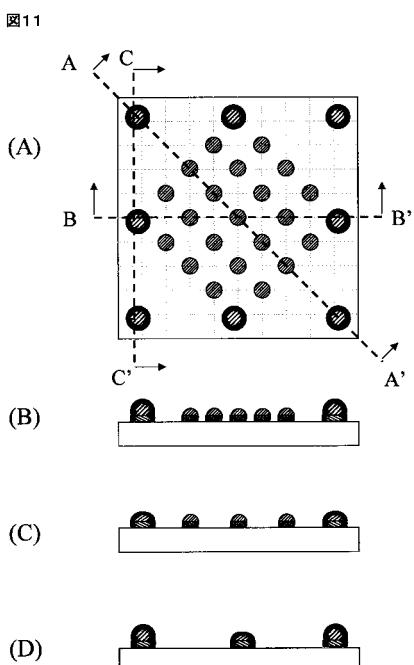

また、本発明の実施の形態では、配線基板の周囲に配置され（各辺に沿って配置され）、第1バンプが接続される第1ランドの径が、第2バンプが接続される第2ランドの径よりも小さく形成されていることについて説明したが、これに限定されるものではなく、例えば図11に示すように、半導体装置を実装する実装基板の電極とは接続されないが、スクリーニングテスターとの接続に使用される第2ランドには、第1バンプの高さよりも低い第2バンプが形成されればよく、第2ランドの径は第1ランドの径と同じ寸法であってもよい。これは、スクリーニングテストが、プローブ針をバンプに接触させて行うが、このときランドの径が相対的に大きいほうが確実にプローブ針をバンプに接触させ易いためである。しかしながら、単にランドを大きくしてしまうと、形成されるバンプの高さも高くなってしまう。スクリーニングテストに使用されるバンプは、半導体装置を実装する実装基板の電極には接続しないため、バンプの高さはできるだけ低く形成しておきたい。そこで、図11（図11（B）は図11（A）におけるA-A'線の断面図、図11（C）は図11（A）におけるB-B'線の断面図、図11（D）は図11（A）におけるC-C'線の断面図）に示すような構成とすれば、実装基板との接触を避けながら、スクリーニングテストをより確実に行うことができる。

30

#### 【0051】

また、本発明の実施の形態におけるWPPパッケージでは、半導体チップ（半導体集積回路チップ）のボンディングパッドから引き出し配線を介して隣接するボンディングパッド同士の間隔を広げ、引き出し配線の先端部に半田バンプを形成することについて説明したが、これに限定されるものではなく、例えば半導体チップに形成される複数のボンディングパッド同士の間隔が予め広く配置されれば、引き出し配線を各ボンディングパッドから延在させる必要はない。しかしながら、半導体チップに形成されるボンディングパッドの寸法（面積、径）は、配線基板に形成されるランドに比べると相対的に小さいため、これらのボンディングパッドに直接半田バンプを形成した場合、形成される半田バンプ

40

50

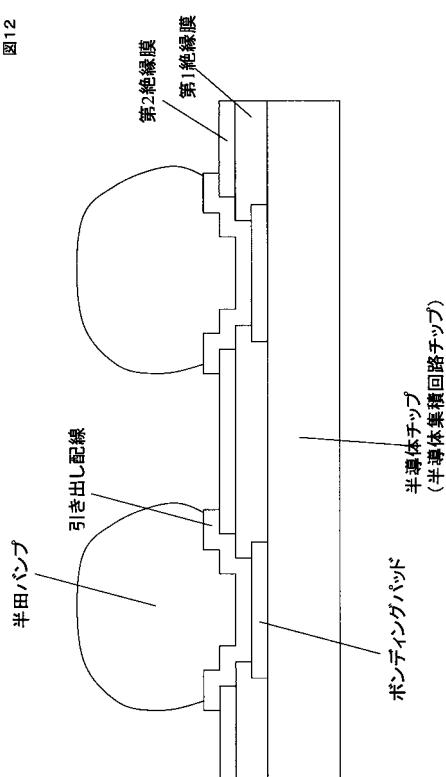

も小さく（低く）なってしまう。そこで、図12に示すように、ボンディングパッド上に第1絶縁膜および第2絶縁膜を介して引き出し配線を形成し、半田バンプが接続される領域を広げることで、形成される半田バンプを相対的に大きく（高く）することができ、W P Pパッケージ（半導体装置、半導体チップ、半導体集積回路チップ）の実装強度を向上することができる。

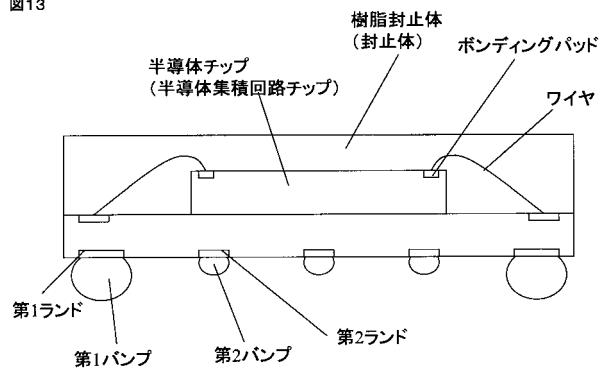

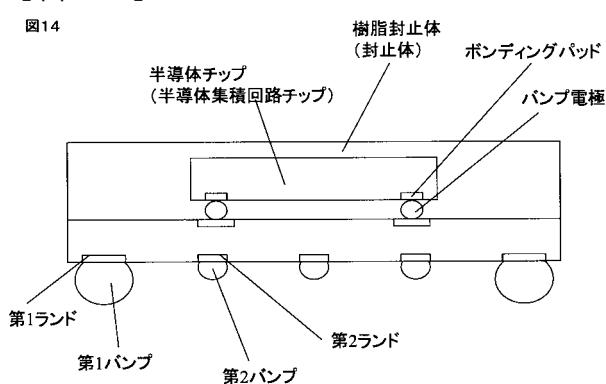

また、本発明の実施の形態では、B G A型またはL G A型のパッケージについても説明したが、樹脂封止体（封止体）で覆われている半導体チップ（半導体集積回路チップ）と、半導体チップを支持（搭載）する配線基板との電気的な接続は、図13に示すように、複数のワイヤを用いても良く、さらには図14に示すように、バンプ電極を介してフリップチップ接続しても良い。10

**【図面の簡単な説明】**

**【0052】**

**【図1】**図1は本発明に係る半導体装置における外部端子の配列を例示する説明図である。。

**【図2】**図2は本発明に係る半導体装置を例示するプロック図である。

**【図3】**図3は半導体装置を実装基板に搭載した状態を例示する説明図である。

**【図4】**図4は複数個の半導体装置がスクリーニングテスタに接続された状態を例示する説明図である。

**【図5】**図5は第1外部端子が形成される第1バンプと第2の外部端子が形成される第2バンプを例示する縦断面図である。20

**【図6】**図1の外部端子構造に対して第1外部端子及び第2外部端子の全てを等しいピッチで且つ等しい大きさで形成した場合の比較例を示し説明図である。

**【図7】**図7は図1で説明した半導体装置に対して実装基板への接続に用いられずスクリーニングテスタとの接続に用いられる外部端端子を小さく形成した点が相違される半導体装置を例示する説明図である。

**【図8】**図8は図1に比べて第1外部端子のピッチが大きくされ第2外部端子の配列形態が相違された別の半導体装置の例を示す説明図である。

**【図9】**図9は図8の端子配列に対してスクリーニングテスタとの接続のみに用いられる外部端端子を第3バンプB M P \_ Tにより小さく形成した半導体装置を例示する説明図である。30

**【図10】**図10はW P Pパッケージ形態を採用した半導体装置における端子配列を例示する説明図である。

**【図11】**図11は本発明に係る半導体装置における変形例の外部端子の配列を例示する説明図である。

**【図12】**図12はW P Pパッケージ形態を採用した半導体装置における変形例の端子配列を例示する説明図である。

**【図13】**図13は樹脂封止体で覆われている半導体チップと半導体チップを支持する配線基板との電気的な接続に複数のワイヤを用いた例を示す説明図である。

**【図14】**図14は樹脂封止体で覆われている半導体チップと半導体チップを支持する配線基板との電気的な接続にバンプ電極を介してフリップチップ接続した例を示す説明図である。40

**【符号の説明】**

**【0053】**

1 半導体装置

2 半導体集積回路チップ

3 , 5 第1回路（F C C T）

4 第2回路（S C C T）

6 バス

P u 実装基板への接続に用いられスクリーニングテスタとの接続に用いられない端子

P u s 前記実装基板への接続並びにスクリーニングテスタとの接続に用いられる端子50

P s 前記実装基板への接続に用いられず且つスクリーニングテスタとの接続に用いられる端子

P 前記実装基板への接続に用いられず且つスクリーニングテスタとの接続に用いられない端子

7 実装基板

8 配線パターン

9 スクリーニングテスタ (T E S T )

L N D 1 第1ランド

B M P 1 第1バンプ

L N D 2 第2ランド

B M P 2 第2バンプ

B M P \_ F 第1バンプ

B M P \_ S 第2バンプ

B M P \_ T 第3バンプ

P A D ボンディングパッド形成領域

L I N 引き出し配線

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【図12】

【図13】

図13

【図14】

図14

---

フロントページの続き

(72)発明者 山岸 一繁

東京都千代田区大手町二丁目6番2号 株式会社ルネサステクノロジ内

(72)発明者 安村 文次

東京都千代田区大手町二丁目6番2号 株式会社ルネサステクノロジ内

(72)発明者 槙平 尚宏

東京都千代田区大手町二丁目6番2号 株式会社ルネサステクノロジ内

審査官 今井 拓也

(56)参考文献 特開2004-335858(JP,A)

特開2007-115904(JP,A)

特開平03-172782(JP,A)

特開昭63-271966(JP,A)

特開2002-174667(JP,A)

特開2004-078996(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/60

H01L 21/3205

H01L 21/768

H01L 23/522