(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2017-219839

(P2017-219839A)

(43) 公開日 平成29年12月14日(2017.12.14)

|                              |             |             |

|------------------------------|-------------|-------------|

| (51) Int.Cl.                 | F 1         | テーマコード (参考) |

| <b>G09G 3/3233 (2016.01)</b> | G09G 3/3233 | 5C080       |

| <b>G09G 3/20 (2006.01)</b>   | G09G 3/20   | 624B        |

|                              | G09G 3/20   | 612U        |

|                              | G09G 3/20   | 621A        |

|                              | G09G 3/20   | 622D        |

審査請求 未請求 請求項の数 7 O L (全 33 頁)

(21) 出願番号 特願2017-108174 (P2017-108174)

(22) 出願日 平成29年5月31日 (2017.5.31)

(31) 優先権主張番号 特願2016-111536 (P2016-111536)

(32) 優先日 平成28年6月3日 (2016.6.3)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 三宅 博之

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

F ターム (参考) 5C080 AA06 AA10 BB05 DD06 DD08

DD09 DD12 DD26 DD27 EE19

EE29 FF11 FF12 JJ01 JJ02

JJ03 JJ04 JJ05 JJ06 JJ07

KK02 KK07 KK43 KK47 KK49

KK50

最終頁に続く

(54) 【発明の名称】表示装置、表示モジュール、電子機器、および駆動方法

## (57) 【要約】

【課題】発光素子の発光期間を制御することで、視認性向上させる。

【解決手段】信号線と、第1の走査線と、第2の走査線と、画素回路とを有する表示装置であって、画素回路は、発光素子と、第1のトランジスタと、第2のトランジスタと、を有している。第2のトランジスタはバックゲートを有し、バックゲートに、第2の走査線が電気的に接続されている。第2の走査線は、第2のトランジスタの閾値電圧を制御する機能を有し、発光素子の発光期間を制御する機能を有する表示装置。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

信号線と、第1の走査線と、第2の走査線と、画素回路と、を有する表示装置であって、

前記画素回路は、発光素子と、第1のトランジスタと、第2のトランジスタと、を有し、

前記第1のトランジスタのゲートは、前記第1の走査線と電気的に接続され、

前記第1のトランジスタのソースまたはドレインの一方は、前記信号線と電気的に接続され、

前記第1のトランジスタのソースまたはドレインの他方は、前記第2のトランジスタのゲートと電気的に接続され、

前記第2のトランジスタは、バックゲートを有し、

前記第2のトランジスタのソースまたはドレインの一方は、前記発光素子の一方の電極と電気的に接続され、

前記第2の走査線は前記バックゲートに、電気的に接続された表示装置。

**【請求項 2】**

請求項1において、

前記第1または前記第2のトランジスタは、チャネル形成領域に酸化物半導体を有することを特徴とする表示装置。

**【請求項 3】**

請求項1または2のいずれかにおいて、

前記発光素子は、有機化合物層を有することを特徴とする表示装置。

**【請求項 4】**

表示部と、ゲートドライバと、を有する表示装置の駆動方法であって、

前記表示部は、複数の信号線と、複数の第1の走査線と、複数の第2の走査線と、第1の画素回路と、第2の画素回路と、を有し、

前記第1の画素回路および前記第2の画素回路は、発光素子と、第1のトランジスタと、第2のトランジスタと、を有し、

前記第2のトランジスタはバックゲートを有し、

前記ゲートドライバは、複数の前記第1の走査線に、電気的に接続され、

前記ゲートドライバは、複数の前記第2の走査線に、電気的に接続され、

前記第1の走査線は、前記第1の画素回路が有する第1のトランジスタのゲートと、前記第2の画素回路が有する第1のトランジスタのゲートと、に電気的に接続され、

前記第2の走査線は、前記第1の画素回路が有する第2のトランジスタのバックゲートと、前記第2の画素回路が有する第2のトランジスタのバックゲートと、に電気的に接続され、

前記ゲートドライバは、複数の前記第1の走査線に第1の走査信号を出力する機能を有し、

前記ゲートドライバは、複数の前記第2の走査線に第2の走査信号を出力する機能を有し、

1フレーム期間は、第1の期間と、第2の期間と、を有し、

第1の期間において、前記発光素子の発光および階調を制御し、

第2の期間において、前記発光素子の消灯を制御する表示装置の駆動方法。

**【請求項 5】**

請求項4において、

前記第1の期間の後に、前記第2の期間を有する表示装置の駆動方法であって、

前記第1の期間は、

前記ゲートドライバが前記第1の走査線に前記第1の走査信号を与え、

前記信号線が、前記第1のトランジスタを介して前記第2のトランジスタのゲートに信号を与え、

10

20

30

40

50

前記信号に応じた電流が前記第2のトランジスタから前記発光素子に与えられ、

前記第2の走査信号、前記第2のトランジスタのソースの電圧以上の電圧を前記第2の

トランジスタの前記バックゲートに与え、

前記第2のトランジスタは、前記バックゲートの電圧により第2のトランジスタの電流

の大きさが制御され、

電流の大きさを制御することで、前記発光素子の発光および階調を制御し、

前記第2の期間は、

前記第2の走査信号、前記第2のトランジスタのソースの電圧よりも小さな電圧を前記

第2のトランジスタの前記バックゲートに与え、

前記第2のトランジスタは、前記バックゲートの電圧により閾値電圧が制御され、

10

前記閾値電圧を制御することで、前記発光素子を消灯させることで発光時間を制御する

表示装置の駆動方法。

#### 【請求項6】

請求項1乃至3のいずれか一に記載の表示装置と、

タッチセンサと、

を有することを特徴とする表示モジュール。

#### 【請求項7】

請求項1乃至3のいずれか一に記載の表示装置、または請求項6に記載の表示モジュー

ルと、

操作キーまたはパッテリと、

20

を有することを特徴とする電子機器。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明の一態様は、表示装置、表示モジュール、および電子機器に関する。

##### 【0002】

なお、本発明の一態様は、上記の技術分野に限定されない。本明細書等で開示する発明

の一態様の技術分野は、物、方法、または、製造方法に関する。または、本発明は、プロ

セス、マシン、マニュファクチャ、または、組成物（コンポジション・オブ・マター）に

に関する。特に、本発明の一態様は、半導体装置、表示装置、発光装置、蓄電装置、記憶装

置、それらの駆動方法、またはそれらの製造方法に関する。

30

##### 【背景技術】

##### 【0003】

スマートフォン、タブレット等のモバイル機器が普及している。さらにヘッドマウント

ディスプレイや、デジタル化された車載用表示機器といった、新しい機器が使用されるよ

うになってきており、高い視認性と、消費電力の低減が求められている。

##### 【0004】

アクティブマトリクス型有機ELディスプレイは、高い応答速度、高視野角等で優れて

いるホールド型の表示方式（以下、ホールド型駆動と記す）である。ホールド型駆動は、

1フレーム期間（1フレームとは表示する画像の単位を表す）に発光素子が発光して

いる。発光輝度は1フレーム期間の輝度を積算して階調を制御している。一例として1秒間に

60フレームを表示する表示装置は、画像を1秒間に60回表示する。この場合、1フレ

ーム期間は、約16.67msの時間を表している。

40

##### 【0005】

他の駆動方式としてインパルス型の表示方式（以下、インパルス型駆動と記す）がある

。インパルス型駆動では、画素回路の選択期間に1フレーム期間における積算輝度と同じ

輝度で発光させ階調を制御している。

##### 【0006】

なお、ホールド型駆動またはインパルス型駆動では、発光輝度を電圧により指定する電

圧設定方式のほか、電流により指定する電流設定方式が知られている。

50

**【0007】**

有機EL素子の応答性は、液晶素子に比べて高いものの、ホールド型駆動では、動画表示において動画解像度を落としてしまう動画ボケが発生する。動画解像度とは、動画を表示したときの見た目での解像度のことであり、動画を表示したときに人が感じる解像度のことである。例えば、楔形の図形を画面にスクロールさせ、画像の更新間隔を識別できる限界の解像度のことである。

**【0008】**

例えば、特許文献1では、インパルス型駆動と、ホールド型駆動を組み合わせることで、階調を制御し、視認性を上げる制御方法が提案されている。

**【0009】**

例えば、特許文献2では、表示フレームに黒を挿入することで、動画像解像度を向上する方法が提案されており、かつ有機EL素子の発光期間を減らすことで、有機EL素子の短寿命化の抑制方法について記載されている。

10

**【先行技術文献】****【特許文献】****【0010】**

【特許文献1】特開2009-9049号公報

【特許文献2】特開2011-85768号公報

**【発明の概要】****【発明が解決しようとする課題】**

20

**【0011】**

ホールド型駆動では、表示領域において、アクティブマトリックス型のディスプレイ起因の動画ボケが発生するため、動画像等を表示した際に輪郭が不明瞭になるなどの問題がある。

**【0012】**

ホールド型駆動では、1フレームごとに表示が更新されるため積分輝度を用いている。そのため、階調の変化を認識するためには輝度を積分する期間が必要になるため、コントラストが上がらない問題がある。

**【0013】**

点順次によるインパルス型駆動では、ホールド型駆動のような動画ボケは抑えられるものの、発光期間が短いため、静止画などを表示するときに、ちらつきを発生させる問題がある。

30

**【0014】**

点順次によるインパルス型駆動では、画素回路の選択期間に1フレーム期間における積算輝度と同じ輝度で発光させるためにドライバーには高い電流供給能力が必要である。

**【0015】**

上記問題に鑑み、本発明の一態様は、新規な構成の表示装置を提供することを課題の一とする。または、本発明の一態様は表示の視認性を向上させる表示装置を提供することを課題の一とする。本発明の一態様は、消費電力を低減させる表示装置を提供することを課題の一とする。

40

**【0016】**

なお本発明の一態様の課題は、上記列挙した課題に限定されない。上記列挙した課題は、他の課題の存在を妨げるものではない。なお他の課題は、以下の記載で述べる、本項目で言及していない課題である。本項目で言及していない課題は、当業者であれば明細書又は図面等の記載から導き出せるものであり、これらの記載から適宜抽出することができる。なお、本発明の一態様は、上記列挙した記載、及び／又は他の課題のうち、少なくとも一つの課題を解決するものである。

**【課題を解決するための手段】****【0017】**

本発明の一態様は、信号線と、第1の走査線と、第2の走査線と、画素回路と、を有す

50

る表示装置であって、画素回路は、発光素子と、第1のトランジスタと、第2のトランジスタとを有し、第1のトランジスタのゲートは、第1の走査線と電気的に接続され、第1のトランジスタのソースまたはドレインの一方は、信号線と電気的に接続され、第1のトランジスタのソースまたはドレインの他方は、第2のトランジスタのゲートと電気的に接続され、第2のトランジスタは、バックゲートを有し、第2のトランジスタのソースまたはドレインの一方は、発光素子の一方の電極と電気的に接続され、第2の走査線は前記バックゲートに、電気的に接続された表示装置である。

#### 【0018】

上記表示装置において、第1または第2のトランジスタは、チャネル形成領域に酸化物半導体を有することが好ましい。10

#### 【0019】

上記表示装置において、発光素子は、有機化合物層を有することが好ましい。

#### 【0020】

本発明の一態様は、表示部と、ゲートドライバと、を有する表示装置の駆動方法であつて、表示部は、複数の信号線と、複数の第1の走査線と、複数の第2の走査線と、第1の画素回路と、第2の画素回路と、を有し、第1の画素回路および第2の画素回路は、発光素子と、第1のトランジスタと、第2のトランジスタと、を有し、第2のトランジスタはバックゲートを有し、ゲートドライバは、複数の第1の走査線に、電気的に接続され、ゲートドライバは、複数の第2の走査線に、電気的に接続され、第1の走査線は、第1の画素回路が有する第1のトランジスタのゲートと、第2の画素回路が有する第1のトランジスタのゲートと、に電気的に接続され、第2の走査線は、第1の画素回路が有する第2のトランジスタのバックゲートと、第2の画素回路が有する第2のトランジスタのバックゲートと、に電気的に接続され、ゲートドライバは、複数の第1の走査線に第1の走査信号を出力する機能を有し、ゲートドライバは、複数の第2の走査線に第2の走査信号を出力する機能を有し、1フレーム期間は、第1の期間と、第2の期間と、を有し、第1の期間において、発光素子の発光および階調を制御し、第2の期間において、発光素子の消灯を制御する表示装置の駆動方法である。20

#### 【0021】

上記構成において、第1の期間の後に、第2の期間を有する表示装置の駆動方法であつて、第1の期間は、ゲートドライバが第1の走査線に第1の走査信号を与え、信号線が、第1のトランジスタを介して第2のトランジスタのゲートに信号を与え、信号に応じた電流が第2のトランジスタから発光素子に与えられ、第2の走査信号、第2のトランジスタのソースの電圧以上の電圧を第2のトランジスタのバックゲートに与え、第2のトランジスタは、バックゲートの電圧により第2のトランジスタの電流の大きさが制御され、電流の大きさを制御することで、発光素子の発光および階調を制御し、第2の期間は、第2の走査信号、第2のトランジスタのソースの電圧よりも小さな電圧を前記第2のトランジスタの前記バックゲートに与え、第2のトランジスタは、バックゲートの電圧により閾値電圧が制御され、閾値電圧を制御することで、発光素子を消灯させることで発光期間を制御する表示装置の駆動方法が好ましい。30

#### 【0022】

上記各構成において、表示装置と、タッチセンサと、を有することを特徴とする表示モジュールが好ましい。

#### 【発明の効果】

#### 【0023】

本発明の一態様は、新規な構成の表示装置を提供することができる。または、本発明の一態様は、表示の視認性を向上させる表示装置を提供することができる。本発明の一態様は消費電力を低減させる表示装置を提供することができる。

#### 【0024】

なお本発明の一態様の効果は、上記列挙した効果に限定されない。上記列挙した効果は、他の効果の存在を妨げるものではない。なお他の効果は、以下の記載で述べる、本項目40

で言及していない効果である。本項目で言及していない効果は、当業者であれば明細書又は図面等の記載から導き出せるものであり、これらの記載から適宜抽出することができる。なお、本発明の一態様は、上記列挙した効果、及び／又は他の効果のうち、少なくとも一つの効果を有するものである。従って本発明の一態様は、場合によっては、上記列挙した効果を有さない場合もある。

**【図面の簡単な説明】**

**【0025】**

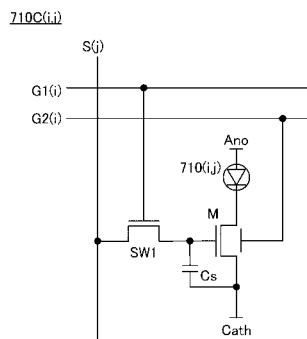

【図1】画素回路の構成を説明する図。

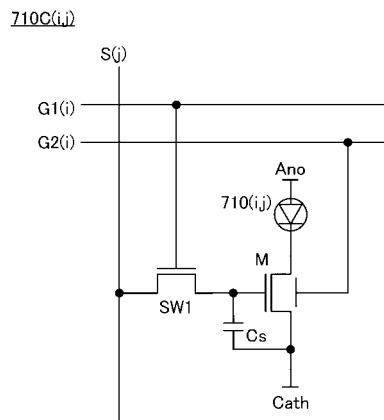

【図2】表示装置の構成を示すブロック図。

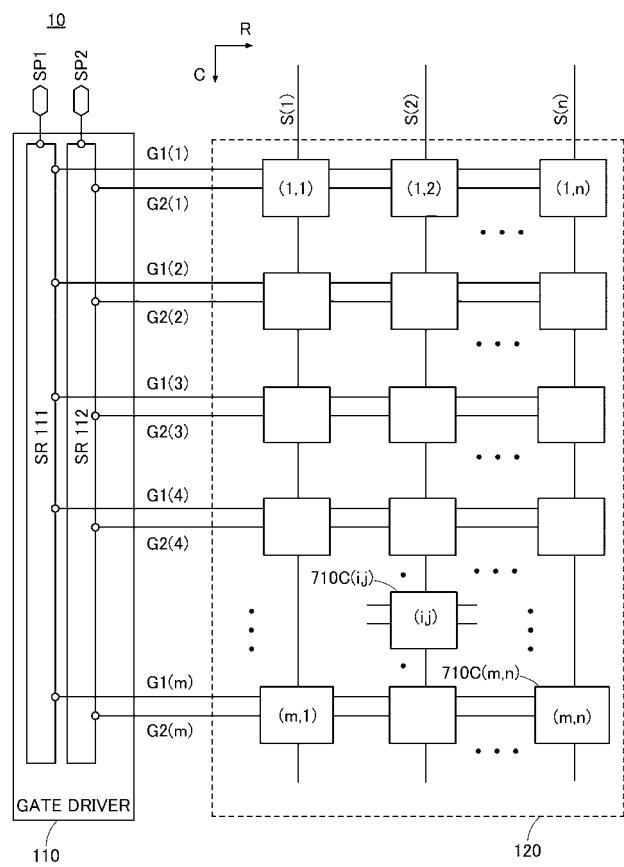

【図3】(A)：トランジスタの接続を説明する図。(B)：トランジスタの電気特性の一例を示す図。 10

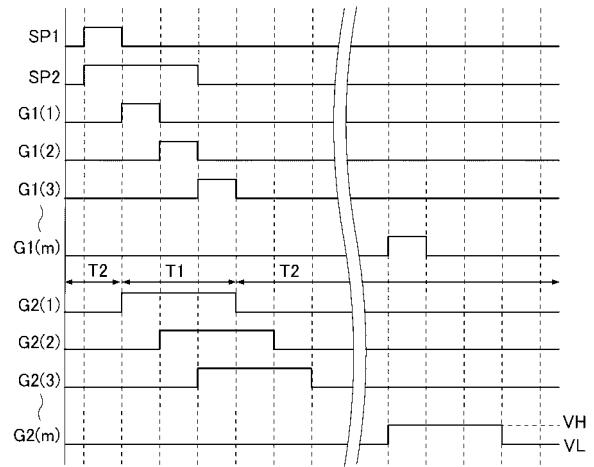

【図4】表示装置の動作例を示すタイミングチャート

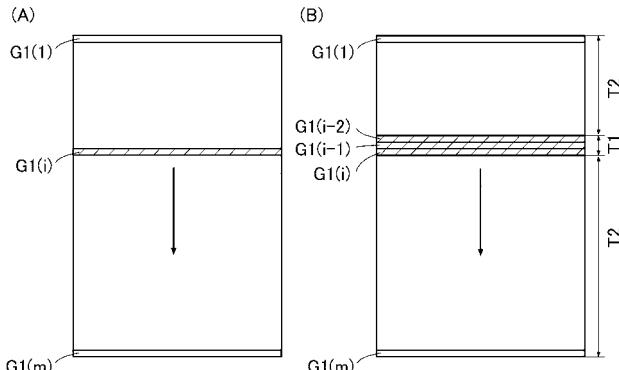

【図5】(A)：表示の一例を示す図。(B)：表示の一例を示す図。

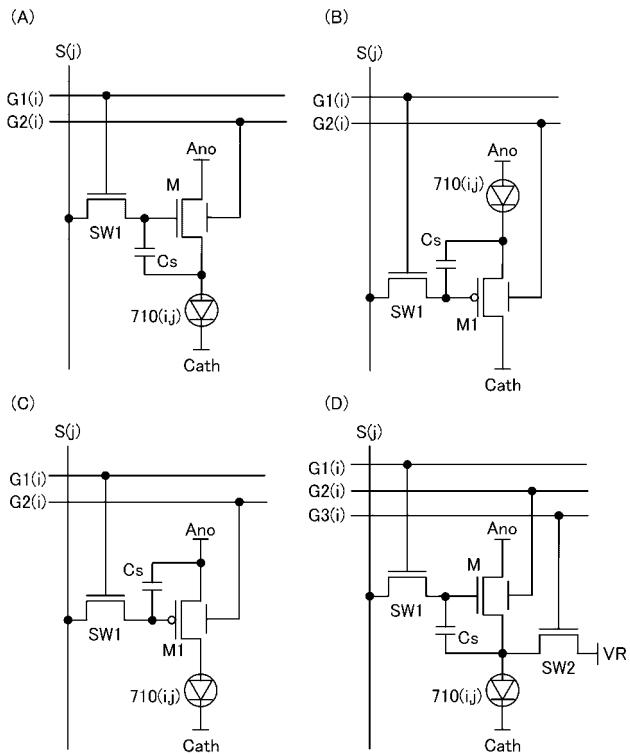

【図6】(A)(B)(C)(D)：画素回路の構成を説明する図。

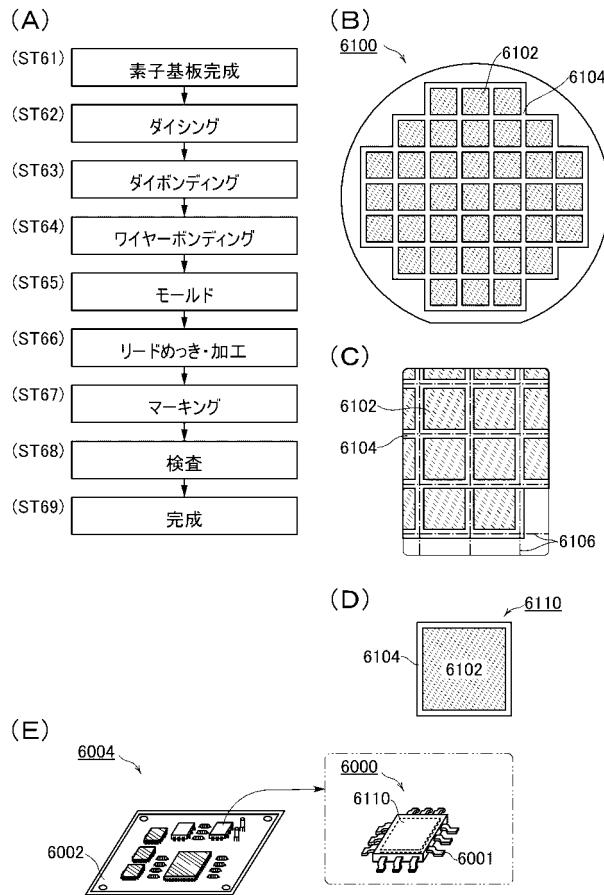

【図7】(A)：電子部品の作製方法例を示すフローチャート。(B)：半導体ウエハの上面図。(C)：半導体ウエハの部分拡大図。(D)：チップの拡大図。(E)：電子部品の斜視模式図。 20

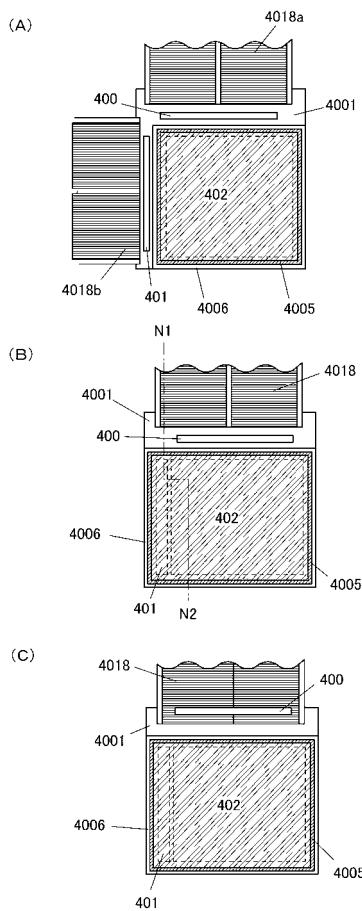

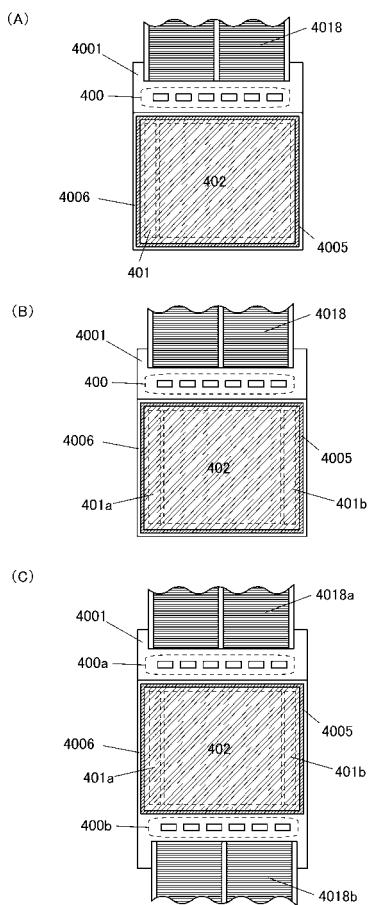

【図8】(A)(B)(C)：表示パネルの構成例を示す上面図。

【図9】(A)(B)(C)：表示パネルの構成例を示す上面図。

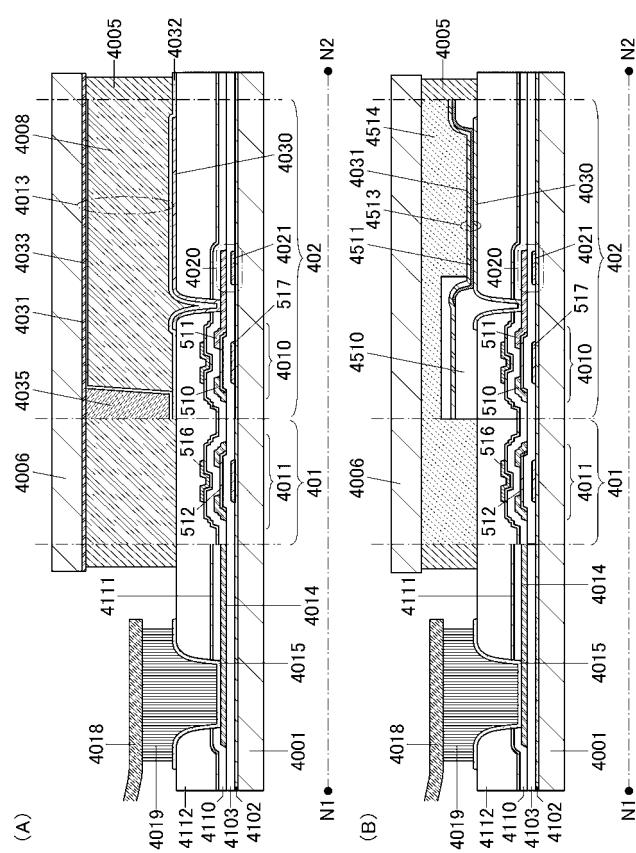

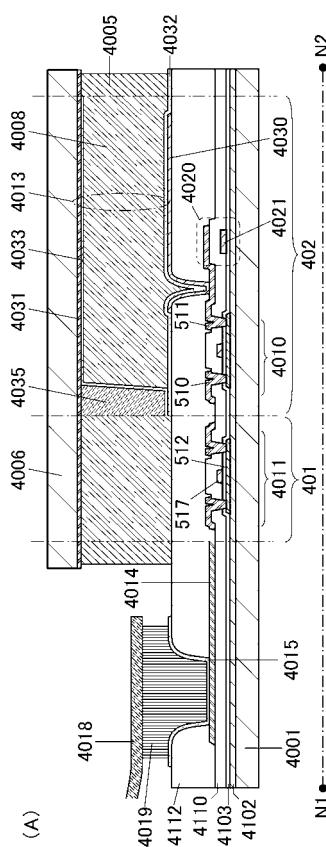

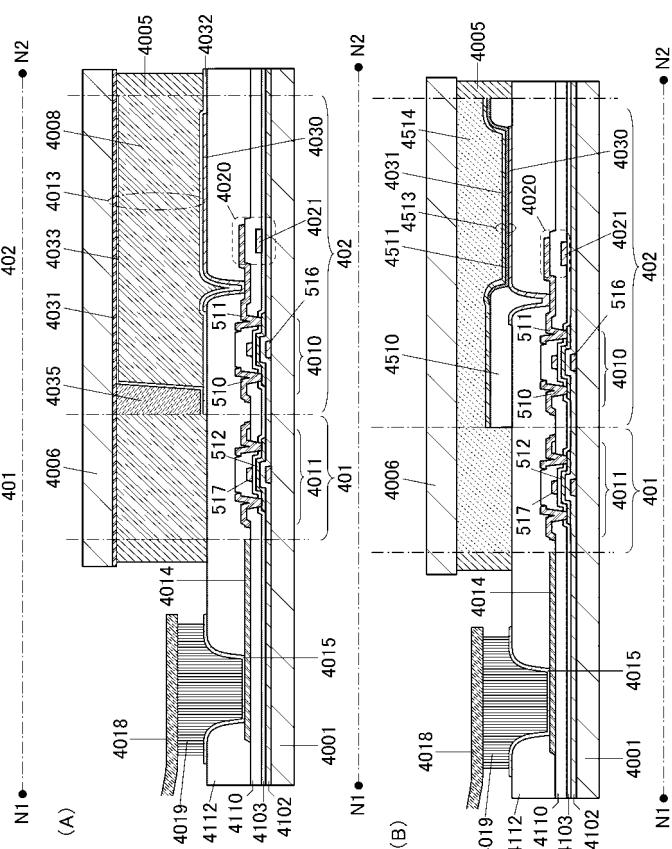

【図10】(A)(B)：表示パネルの構成例を示す断面図。 20

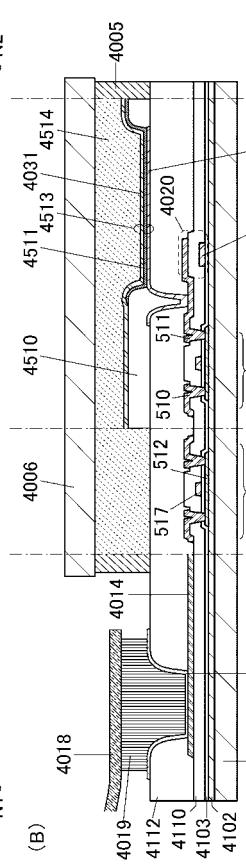

【図11】(A)(B)：表示パネルの構成例を示す断面図。

【図12】(A)(B)：表示パネルの構成例を示す断面図。

【図13】表示モジュールの例を示す図。

【図14】(A)(B)：タッチパネルの構成例を示す模式図。

【図15】(A)(B)(C)：電子機器の構成例を示す図。

【図16】(A)(B)(C)(D)(E)：電子機器の構成例を示す図。

**【発明を実施するための形態】**

**【0026】**

以下、実施の形態について図面を参照しながら説明する。但し、実施の形態は多くの異なる態様で実施することが可能であり、趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は、以下の実施の形態の記載内容に限定して解釈されるものではない。 30

**【0027】**

また、図面において、大きさ、層の厚さ、又は領域は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。なお図面は、理想的な例を模式的に示したものであり、図面に示す形状又は値などに限定されない。

**【0028】**

また、本明細書にて用いる「第1」、「第2」、「第3」という序数詞は、構成要素の混同を避けるために付したものであり、数的に限定するものではないことを付記する。

**【0029】**

また、本明細書において、「上に」、「下に」などの配置を示す語句は、構成同士の位置関係を、図面を参照して説明するために、便宜上用いている。また、構成同士の位置関係は、各構成を描写する方向に応じて適宜変化するものである。従って、明細書で説明した語句に限定されず、状況に応じて適切に言い換えることができる。 40

**【0030】**

また、本明細書等において、トランジスタとは、ゲートと、ドレインと、ソースとを含む少なくとも三つの端子を有する素子である。そして、ドレイン(ドレイン端子、ドレイン領域またはドレイン電極)とソース(ソース端子、ソース領域またはソース電極)の間にチャネル領域を有しており、チャネル形成領域を介して、ソースとドレインとの間に電流を流すことができるものである。なお、本明細書等において、チャネル領域とは、電流 50

が主として流れる領域をいう。

【0031】

また、ソースやドレインの機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため、本明細書等においては、ソースやドレインの用語は、入れ替えて用いることができるものとする。

【0032】

また、本明細書等において、「平行」とは、二つの直線が-10°以上10°以下の角度で配置されている状態をいう。したがって、-5°以上5°以下の場合も含まれる。また、「垂直」とは、二つの直線が80°以上100°以下の角度で配置されている状態をいう。したがって、85°以上95°以下の場合も含まれる。10

【0033】

また、本明細書等において、「膜」という用語と、「層」という用語とは、互いに入れ替えることが可能である。例えば、「導電層」という用語を、「導電膜」という用語に変更することが可能な場合がある。または、例えば、「絶縁膜」という用語を、「絶縁層」という用語に変更することが可能な場合がある。

【0034】

また、本明細書等において、特に断りがない場合、オフ電流とは、トランジスタがオフ状態（非導通状態、遮断状態、ともいう）にあるときのドレイン電流をいう。オフ状態とは、特に断りがない場合、nチャネル型トランジスタでは、ゲートとソースの間の電圧 $V_{gs}$ がしきい値電圧 $V_{th}$ よりも低い状態、pチャネル型トランジスタでは、ゲートとソースの間の電圧 $V_{gs}$ がしきい値電圧 $V_{th}$ よりも高い状態をいう。例えば、nチャネル型のトランジスタのオフ電流とは、ゲートとソースの間の電圧 $V_{gs}$ がしきい値電圧 $V_{th}$ よりも低いときのドレイン電流を言う場合がある。20

【0035】

トランジスタのオフ電流は、 $V_{gs}$ に依存する場合がある。従って、トランジスタのオフ電流がI以下である、とは、トランジスタのオフ電流がI以下となる $V_{gs}$ の値が存在することを言う場合がある。トランジスタのオフ電流は、所定の $V_{gs}$ におけるオフ状態、所定の範囲内の $V_{gs}$ におけるオフ状態、または、十分に低減されたオフ電流が得られる $V_{gs}$ におけるオフ状態、等におけるオフ電流を指す場合がある。30

【0036】

一例として、しきい値電圧 $V_{th}$ が0.5Vであり、 $V_{gs}$ が0.5Vにおけるドレイン電流が $1 \times 10^{-9} A$ であり、 $V_{gs}$ が0.1Vにおけるドレイン電流が $1 \times 10^{-1} A$ であり、 $V_{gs}$ が-0.5Vにおけるドレイン電流が $1 \times 10^{-19} A$ であり、 $V_{gs}$ が-0.8Vにおけるドレイン電流が $1 \times 10^{-22} A$ であるようなnチャネル型トランジスタを想定する。当該トランジスタのドレイン電流は、 $V_{gs}$ が-0.5Vにおいて、または、 $V_{gs}$ が-0.5V以上-0.8V以下の範囲において、 $1 \times 10^{-19} A$ 以下であるから、当該トランジスタのオフ電流は $1 \times 10^{-19} A$ 以下である、と言う場合がある。当該トランジスタのドレイン電流が $1 \times 10^{-22} A$ 以下となる $V_{gs}$ が存在するため、当該トランジスタのオフ電流は $1 \times 10^{-22} A$ 以下である、と言う場合がある。40

【0037】

また、本明細書等では、チャネル幅Wを有するトランジスタのオフ電流を、チャネル幅Wあたりを流れる電流値で表す場合がある。また、所定のチャネル幅（例えば1μm）あたりを流れる電流値で表す場合がある。後者の場合、オフ電流の単位は、電流／長さの次元を持つ単位（例えば、A/μm）で表される場合がある。

【0038】

トランジスタのオフ電流は、温度に依存する場合がある。本明細書において、オフ電流は、特に記載がない場合、室温、60、85、95、または125におけるオフ電流を表す場合がある。または、当該トランジスタが含まれる半導体装置等の信頼性が保

10

20

30

40

50

証される温度、または、当該トランジスタが含まれる半導体装置等が使用される温度（例えば、5以上35以下の温度）におけるオフ電流、を表す場合がある。トランジスタのオフ電流がI以下である、とは、室温、60、85、95、125、当該トランジスタが含まれる半導体装置等の信頼性が保証される温度、または、当該トランジスタが含まれる半導体装置等が使用される温度（例えば、5以上35以下の温度）、におけるトランジスタのオフ電流がI以下となるV<sub>gs</sub>の値が存在することを指す場合がある。

#### 【0039】

トランジスタのオフ電流は、ドレインとソースの間の電圧V<sub>ds</sub>に依存する場合がある。本明細書において、オフ電流は、特に記載がない場合、V<sub>ds</sub>が0.1V、0.8V、1V、1.2V、1.8V、2.5V、3V、3.3V、10V、12V、16V、または20Vにおけるオフ電流を表す場合がある。または、当該トランジスタが含まれる半導体装置等の信頼性が保証されるV<sub>ds</sub>、または、当該トランジスタが含まれる半導体装置等において使用されるV<sub>ds</sub>におけるオフ電流、を表す場合がある。トランジスタのオフ電流がI以下である、とは、V<sub>ds</sub>が0.1V、0.8V、1V、1.2V、1.8V、2.5V、3V、3.3V、10V、12V、16V、20V、当該トランジスタが含まれる半導体装置等の信頼性が保証されるV<sub>ds</sub>、または、当該トランジスタが含まれる半導体装置等において使用されるV<sub>ds</sub>におけるトランジスタのオフ電流がI以下となるV<sub>gs</sub>の値が存在することを指す場合がある。

#### 【0040】

上記オフ電流の説明において、ドレインをソースと読み替えてよい。つまり、オフ電流は、トランジスタがオフ状態にあるときのソースを流れる電流を言う場合もある。

#### 【0041】

また、本明細書等では、オフ電流と同じ意味で、リーク電流と記載する場合がある。また、本明細書等において、オフ電流とは、例えば、トランジスタがオフ状態にあるときに、ソースとドレインとの間に流れる電流を指す場合がある。

#### 【0042】

なお、電圧とは2点間における電位差のことをいい、電位とはある一点における静電場の中にある単位電荷が持つ静電エネルギー（電気的な位置エネルギー）のことをいう。ただし、一般的に、ある一点における電位と基準となる電位（例えば接地電位）との電位差のことを、単に電位もしくは電圧と呼び、電位と電圧が同義語として用いられることが多い。このため、本明細書では特に指定する場合を除き、電位を電圧と読み替えてよいし、電圧を電位と読み替えてよいこととする。

#### 【0043】

##### （実施の形態1）

本実施の形態では、画素回路が有するトランジスタのバックゲートに、電気的に接続された走査線から信号を与えることで、表示を制御する機能を有する表示装置について、図1乃至図6を用いて説明する。

#### 【0044】

図1に、画素回路710C(i,j)の構成例を示す。図2に、表示装置10の構成を示すブロック図を示す。図2の表示装置10の表示部120の、画素回路の一つを、画素回路710C(i,j)として説明する。表示部120は、行方向にm個(mは1以上の整数)、列方向にn個(nは1以上の整数)、合計m×n個の画素回路がマトリクス状に配置されている。なおiは1以上m以下の整数であり、jは1以上n以下の整数である。

#### 【0045】

画素回路710C(i,j)は、発光素子710(i,j)を有する。発光素子710(i,j)は、一例として直流駆動される発光素子が好ましい。発光素子710(i,j)の階調は、電圧または電流に応じた信号によって制御される。

#### 【0046】

画素回路710C(i,j)は、トランジスタSW1、トランジスタM、容量素子Cs

10

20

30

40

50

、および発光素子 710 ( i , j ) を有する。

【 0047 】

発光素子 710 ( i , j ) は、画素電極、対向電極、およびこれらに挟まれている有機化合物層を有する発光素子である。画素電極は、陽極または陰極のいずれか一方であり、対向電極は、陽極または陰極のいずれか他方である。有機化合物層は、発光層を含む。

【 0048 】

画素回路 710C ( i , j ) のトランジスタ SW1 のゲートは、走査線 G1 ( i ) と電気的に接続される。トランジスタ SW1 のソースまたはドレインの一方が信号線 S ( j ) と電気的に接続される。トランジスタ SW1 のソースまたはドレインの他方は、容量素子 Cs の一方の電極およびトランジスタ M のゲートと電気的に接続される。

10

【 0049 】

トランジスタ M のドレインには、画素電極が電気的に接続される。画素電極は、発光素子 710 ( i , j ) を介して対向電極に接続される。トランジスタ M のソースは、Cat h 端子に電気的に接続される。Cat h 端子は、容量素子 Cs の他方の電極が電気的に接続される。また、トランジスタ M のバックゲートは、走査線 G2 ( i ) と電気的に接続される。上記トランジスタ M の一対のゲートは、チャネル形成領域を間に介して、互いに重なる領域を有することが好ましい。

【 0050 】

トランジスタ M のソースには、Cat h 端子を介してカソード電圧が与えられる。対向電極には、Ano 端子を介してアノード電圧が与えられる。

20

【 0051 】

容量素子 Cs の他方の電極がトランジスタ M のソースと電気的に接続された例を示したが、ドレインと電気的に接続してもよいし、他の電圧が与えられる配線または電極と電気的に接続してもよい。

【 0052 】

信号線 S ( j ) から与えられる信号の電圧によって、発光素子 710 ( i , j ) の駆動電流は制御される。駆動電流の大きさは、発光素子 710 ( i , j ) の階調を示している。

【 0053 】

図 2 に示す表示装置 10 はゲートドライバ 110 、および表示部 120 を有する。ゲートドライバ 110 は、シフトレジスタ回路 111 およびシフトレジスタ回路 112 を有する。表示部 120 は、画素回路 710C ( 1 , 1 ) 乃至画素回路 710C ( m , n ) を有する。

30

【 0054 】

本実施の形態で説明する表示部 120 は、画素回路 710C ( 1 , 1 ) 乃至画素回路 710C ( m , n ) と、第 1 の走査線 G1 ( 1 ) 乃至 G1 ( m ) と、第 2 の走査線 G2 ( 1 ) 乃至 G2 ( m ) と、信号線 S ( 1 ) 乃至 S ( n ) とを有する。

【 0055 】

図 3 ( A ) は、画素回路 710C ( i , j ) の有するトランジスタ M を示す。トランジスタ M の電気特性を測定するために、トランジスタ M のそれぞれの端子に印加する電圧条件を表 1 に示す。

40

【 0056 】

トランジスタ M のゲートに電気的に接続するのは VG 端子 ( 以下 VG と記す ) であり、ソースに電気的に接続するのは VS 端子 ( 以下 VS と記す ) であり、ドレインに電気的に接続するのは VD 端子 ( 以下 VD と記す ) であり、バックゲートに電気的に接続るのは VBG 端子 ( 以下 VBG と記す ) である。

【 0057 】

図 3 ( B ) に示す P1 乃至 P4 の電気特性は、VBG に異なる電圧を与え、測定した結果を示す。

【 0058 】

50

## 【表1】

| No. | VD  | VS | VBG | VG    |     |       |

|-----|-----|----|-----|-------|-----|-------|

|     |     |    |     | START | END | STEP  |

| P1  | 10V | 0V | 0V  | -15V  | 15V | 0.25V |

| P2  | 10V | 0V | -5V |       |     |       |

| P3  | 10V | 0V | 5V  |       |     |       |

| P4  | 10V | 0V | 10V |       |     |       |

## 【0059】

ここでは、ゲートとソースとの間に係るゲート電圧を変化させながら測定した。ソースとドレインとの間に流れる電流をドレイン電流IDとして測定した。上記の測定方法をIDVG測定、もしくはVGID測定という。

10

## 【0060】

測定したトランジスタは、半導体層に酸化物半導体が適用され、チャネル長は4μm、チャネル幅は50μmである。

## 【0061】

P1はVBGに0Vの電圧を与えたときの電気的特性である。VGが0Vになったときのドレイン電流IDは測定下限以下である。これは、トランジスタのチャネル部に酸化物半導体を用いたときの特性を示している。

20

## 【0062】

ここでは、測定下限を $1 \times 10^{-12} A$ 以下とする。IDVG測定は、Agilent社製半導体パラメータ・アナライザ(Semiconductor Parameter Analyzer、モデル：4155C)を用いた。

20

## 【0063】

P2はVBGに-5Vの電圧を与えたときの電気的特性である。P1の電気特性がプラス側にシフトしており、ドレイン電流IDが測定下限以下になるVGの電圧がプラス側にシフトしていることを示している。このことからトランジスタの閾値電圧がプラスシフトしたことを見ている。

30

## 【0064】

P3はVBGに5Vの電圧を与えたときの電気的特性である。P1の電気特性がマイナス側にシフトしている。ドレイン電流IDが測定下限以下になるVGの電圧がマイナス側にシフトしていることを示している。このことからトランジスタの閾値電圧がマイナスシフトしたことを見ている。

30

## 【0065】

P4はVBGに10Vの電圧を与えたときの電気的特性である。P3に比べて電気特性がさらにマイナス側にシフトしている。ドレイン電流IDが測定下限以下になるVGの電圧がマイナス側にさらにシフトしていることを示している。P3に比べ、トランジスタの閾値電圧がさらにマイナスシフトしたことを見ている。

40

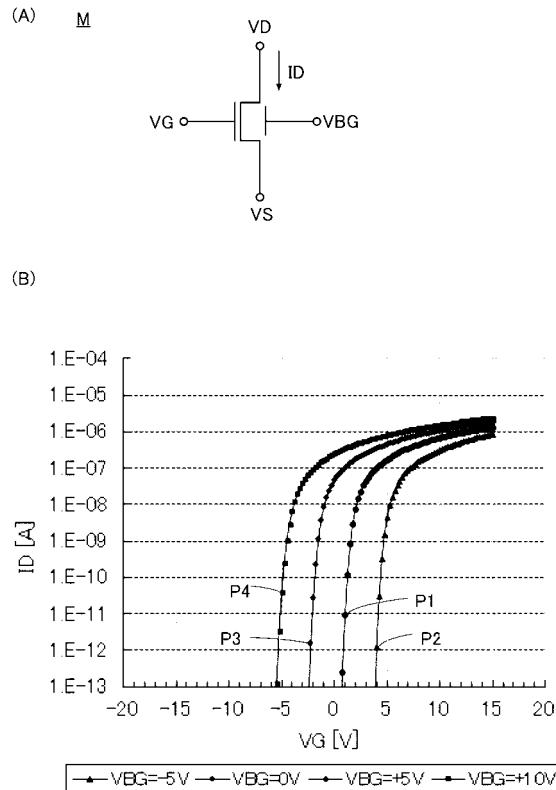

## 【0066】

図4は、図3で説明したトランジスタを用いた表示装置10のタイミングチャートを示す。ゲートドライバ110は、スタートパルスSP1と、スタートパルスSP2と2つの入力信号で画素回路710C(i,j)を制御する。

40

## 【0067】

スタートパルスSP1の信号がシフトレジスタ回路111に与えられる。シフトレジスタ回路111は、走査線G1(1)を制御する信号を出力し、順次、走査線G1(2)乃至G1(m)を選択する。

## 【0068】

スタートパルスSP2の信号がシフトレジスタ回路112に与えられる。シフトレジスタ回路112は、走査線G2(1)を制御する信号を出力し、順次、走査線G2(2)乃至G2(m)を選択する。

## 【0069】

50

スタートパルス S P 1 により選択された走査線 G 1 の信号は、画素回路 7 1 0 C ( i , j ) のトランジスタ SW 1 のゲートに与えられることで、信号線 S ( j ) により与えられた信号の電圧を、トランジスタ M のゲートに与える。したがって、トランジスタ M のゲートに与えられた電圧に応じて、発光素子 7 1 0 ( i , j ) は発光する。

#### 【 0 0 7 0 】

トランジスタ M のバックゲートには、トランジスタ M のソースの電圧以上の電圧を与える。トランジスタ M の閾値電圧がマイナス側にシフトすることで、電流を増加させることができ。したがって信号線 S ( j ) により与える信号の電圧を小さくすることができる。図 4 で示した T 1 は、発光素子 7 1 0 ( i , j ) が発光している期間を示す。

#### 【 0 0 7 1 】

スタートパルス S P 2 により選択された走査線 G 2 の信号は、画素回路 7 1 0 C ( i , j ) のトランジスタ M のバックゲートに与えられることで、トランジスタ M の電気特性をシフトさせることができる。

#### 【 0 0 7 2 】

トランジスタ M のバックゲートに対しトランジスタ M のソースの電圧より小さい電圧を与えることで、発光素子 7 1 0 ( i , j ) に流れる電流を発光に寄与しない電流値まで小さくすることができる。したがって、バックゲートに与える電圧により、発光期間を制御することができる。T 2 の期間は、走査線 G 2 の信号により、発光素子 7 1 0 ( i , j ) が消灯している期間を示す。

#### 【 0 0 7 3 】

トランジスタのバックゲートに与える電圧は、発光素子 7 1 0 ( i , j ) の電気特性によって異なるので、適宜発光素子の特性に合わせた最適な電圧を与える。

#### 【 0 0 7 4 】

図 5 ( A ) および図 5 ( B ) について説明する。図 5 ( A ) は、スタートパルス S P 1 およびスタートパルス S P 2 に同じパルス幅で信号を与えて表示した例を示す。まず、G 1 ( i ) によって表示が更新される。次の走査線 G 1 ( i + 1 ) が選択されるのと同じタイミングで G 2 ( i ) の信号が、トランジスタ M のソースの電圧より小さい電圧になる。G 1 ( i ) で選択され発光していた領域は、消灯する。

#### 【 0 0 7 5 】

図 5 ( B ) は図 4 で示したタイミングチャートで駆動したときの表示を示す。図 5 ( B ) の G 1 ( i ) 、 G 1 ( i - 1 ) および G 1 ( i - 2 ) の走査線に相当する表示領域が発光しており、それ以外は消灯していることを示す。発光期間は、明示的にハッチング処理を行っている。ホールド型の駆動を行うと、走査線で選択された画素回路の表示が更新される。発光素子は 1 フレーム期間、発光している。それに対して、図 1 の画素回路を用いることで、線順次のインパルス型駆動として表示を更新することができる。

#### 【 0 0 7 6 】

したがって発光素子が発光し表示する期間は、スタートパルス S P 2 によって制御されることになる。スタートパルス S P 2 の信号の幅を可変にすることで、動画のように表示の動きが速いときは、発光期間を短くすることで動画解像度を向上させることができる。また静止画のような表示の動きが少ないときに発光期間を長くし、発光輝度を抑制することで積算輝度を確保することができる。したがって、消費電力を小さくすることができる。線順次によるインパルス型駆動は、点順次によるインパルス駆動に比べ、発光期間が長くなり、積算輝度が大きくなるため、ちらつきを抑え、視認性を向上させることができる。

#### 【 0 0 7 7 】

さらに、スタートパルス S P 2 は、モバイル機器のバッテリモニタによって検出された状態に応じてパルス幅を決めてよい。図 5 ( A ) は、図 5 ( B ) と比べると発光期間が短い。したがって同じ表示品質にするためには、積算輝度を考慮して信号線 S ( j ) により与える信号の電圧を高くする必要がある。消費電力を小さくするには、信号は低い電圧にすることが望ましい。バッテリの充電状況に応じてスタートパルス S P 2 の信号の幅を

10

20

30

40

50

最適化することで、消費電力を小さくし、最適な表示品質を提供することができる。

【0078】

1秒間に60フレーム表示する表示装置では、連続する表示フレームに意図的に黒表示のフレームを挿入することで動画解像度を向上する方法がある。一例として黒表示のフレームを挿入するとき、表示の品質を維持するためには1秒間に表示するフレーム数を60フレームより多くする必要がある。

【0079】

図1の画素回路を用いることで、1フレーム期間内で発光期間と消灯期間を制御することができる。したがって、線順次によるインパルス型駆動として表示を制御できる。さらにインパルス型駆動で動画解像度を向上させることで、視認性を向上させることができる。

10

【0080】

なお、本実施の形態で説明する表示装置10に用いられるトランジスタ、容量素子等の各種素子のデバイス構造には、特段の制約はない。表示部120の有する画素回路710C(i,j)およびゲートドライバ110のそれぞれの機能に適したデバイス構造を選択すればよい。例えば、トランジスタのデバイス構造としては、トップゲート型、ボトムゲート型、ゲート(フロントゲート)とボトムゲート双方を備えたデュアルゲート型、および1つの半導体層に対して複数のゲート電極を有するマルチゲート型が挙げられる。トランジスタの活性層(チャネル形成領域)を構成する半導体の種類(組成や結晶構造等)にも特段の制約はない。活性層に用いられる半導体としては、単結晶半導体、非単結晶半導体に大別される。非単結晶としては、多結晶半導体、微結晶半導体、非晶質半導体などが挙げられる。半導体材料には、Si、Ge、C等の第14族元素を1種または複数含む半導体(例えば、シリコン、シリコンゲルマニウム、炭化シリコン等)、酸化物半導体、窒化ガリウム等の化合物半導体等が挙げられる。

20

【0081】

図1の画素回路710C(i,j)は、同じ導電型のトランジスタで構成されている例を示している。ここでは、トランジスタSW1およびトランジスタMが、nチャネル型トランジスタであり、かつ半導体層に酸化物半導体が適用された例を示している。ここでは、トランジスタSW1はボトムゲート型トランジスタであり、トランジスタMはバックゲートを有するデュアルゲート型トランジスタである。

30

【0082】

なお本発明の一様態は図1の画素回路710C(i,j)の回路構成に限らない。図1とは異なる画素回路710C(i,j)の回路構成の一例について図6(A)乃至(D)に図示する。

【0083】

図6(A)が図1と異なる点を説明する。トランジスタMのソースには、画素電極が電気的に接続される。画素電極は、発光素子710(i,j)を介して対向電極に接続される。トランジスタMのドレインは、Ano端子に電気的に接続される。容量素子Csの一方の電極はトランジスタMのゲートと電気的に接続されている。また容量素子Csの他方の電極はトランジスタMのソースと電気的に接続されるが、ドレインに電気的に接続されてもよい。

40

【0084】

図6(B)が図1と異なる点を説明する。トランジスタM1の活性層が、p型の導電型で構成されている。

【0085】

図6(C)が図6(A)と異なる点を説明する。トランジスタM1の活性層が、p型の導電型で構成されている。容量素子Csの一方の電極はトランジスタM1のゲートと電気的に接続されている。また他方の電極はトランジスタM1のソースと電気的に接続されるが、ドレインに電気的に接続されてもよい。ソースに接続された場合は、トランジスタM1のソースに与えられる電圧が、Ano端子から与えられる。したがってトランジスタM

50

のソースとゲート間に係る電圧を制御しやすい。

【0086】

図6(D)の画素回路710C(i,j)は、さらに走査線G3(i)と、トランジスタSW2と、VR端子とを有している。トランジスタSW2のゲートは、走査線G3(i)と電気的に接続されている。

【0087】

VR端子に与えられる電圧は、Cat h端子に与えられる電圧を基準とし、発光素子710(i,j)が発光しない大きさの電圧範囲であることが好ましい。トランジスタSW1を介して、トランジスタMのゲートに信号が与えられる前、もしくは同時にトランジスタSW2を介して、トランジスタMのソースにVR端子から電圧が与えられる。トランジスタMのソースに与えられる電圧が、VR端子から与えられるため、トランジスタMのソースとゲート間に係る電圧を制御しやすい。

10

【0088】

以上、本実施の形態で示す構成、方法は、他の実施の形態で示す構成、方法と適宜組み合わせて用いることができる。

【0089】

(実施の形態2)

本実施の形態では、半導体装置の一例として、ICチップ、電子部品、電子機器等について説明する。

20

【0090】

<電子部品の作製方法例>

図7(A)は、電子部品の作製方法例を示すフローチャートである。電子部品は、半導体パッケージ、またはIC用パッケージともいう。この電子部品は、端子取り出し方向や、端子の形状に応じて、複数の規格や名称が存在する。そこで、本実施の形態では、その一例について説明することにする。

30

【0091】

トランジスタで構成される半導体装置は、組み立て工程(後工程)を経て、プリント基板に脱着可能な部品が複数合わさることで完成する。後工程については、図7(A)に示す各工程を経ることで完成させることができる。具体的には、前工程で得られる素子基板が完成(ステップST61)した後、基板の裏面を研削する。この段階で基板を薄膜化して、前工程での基板の反り等を低減し、部品の小型化を図る。次に、基板を複数のチップに分離するダイシング工程を行う(ステップST62)。

30

【0092】

図7(B)は、ダイシング工程が行われる前の半導体ウエハ6100の上面図である。図7(C)は、図7(B)の部分拡大図である。半導体ウエハ6100には、複数の回路領域6102が設けられている。回路領域6102には、本発明の形態に係る半導体装置(例えば、メモリ、タイマ、CPU等)が設けられている。

【0093】

複数の回路領域6102は、それぞれが分離領域6104に囲まれている。分離領域6104と重なる位置に分離線(「ダイシングライン」ともいう)6106が設定される。ダイシング工程(ステップST62)では、分離線6106に沿って半導体ウエハ6100を切断することで、回路領域6102を含むチップ6110を、半導体ウエハ6100から切り出す。図7(D)に、チップ6110の拡大図を示す。

40

【0094】

分離領域6104に導電層や半導体層を設けてもよい。分離領域6104に導電層や半導体層を設けることで、ダイシング工程時に生じうるESDを緩和し、ダイシング工程に起因する歩留まりの低下を防ぐことができる。また、一般にダイシング工程は、基板の冷却、削りくずの除去、帯電防止などを目的として、炭酸ガスなどを溶解させて比抵抗を下げた純水を切削部に供給しながら行なう。分離領域6104に導電層や半導体層を設けることで、当該純水の使用量を削減することができる。よって、半導体装置の生産コストを

50

低減することができる。また、半導体装置の生産性を高めることができる。

#### 【0095】

ステップST62を行った後、分離したチップを個々にピックアップしてリードフレーム上に搭載し接合する、ダイボンディング工程を行う(ステップST63)。ダイボンディング工程におけるチップとリードフレームとの接着方法は、製品に適した方法を選択すればよい。例えば、接着は樹脂やテープによって行えばよい。ダイボンディング工程は、インターポーヴ上にチップを搭載し接合してもよい。ワイヤーボンディング工程で、リードフレームのリードとチップ上の電極とを金属の細線(ワイヤー)で電気的に接続する(ステップST64)。金属の細線には、銀線や金線を用いることができる。ワイヤーボンディングは、ボールボンディングとウェッジボンディングの何れでもよい。

10

#### 【0096】

ワイヤーボンディングされたチップは、エポキシ樹脂等で封止される、モールド工程が施される(ステップST65)。モールド工程を行うことで電子部品の内部が樹脂で充填され、機械的な外力による内蔵される回路部やワイヤーに対するダメージを低減することができ、また水分や埃による特性の劣化を低減することができる。リードフレームのリードをメッキ処理する。そしてリードを切断および成形加工する(ステップST66)。めっき処理によりリードの錆を防止し、後にプリント基板に実装する際のはんだ付けをより確実に行うことができる。パッケージの表面に印字処理(マーキング)を施す(ステップST67)。検査工程(ステップST68)を経て、電子部品が完成する(ステップST69)。上掲した実施の形態の半導体装置を組み込むことで、低消費電力で、小型な電子部品を提供することができる。

20

#### 【0097】

完成した電子部品の斜視模式図を図7(E)に示す。図7(E)では、電子部品の一例として、QFP(Quad Flat Package)の斜視模式図を示している。図7(E)に示すように、電子部品6000は、リード6001およびチップ6110を有する。

20

#### 【0098】

電子部品6000は、例えばプリント基板6002に実装される。このような電子部品6000が複数組み合わされて、それぞれがプリント基板6002上で電気的に接続されることで、電子機器に搭載することができる。完成した回路基板6004は、電子機器等の内部に設けられる。電子部品6000を搭載することで、電子機器の消費電力を削減することができる。または、電子機器を小型化することが容易になる。

30

#### 【0099】

##### (実施の形態3)

本実施の形態では、上記実施の形態に示す表示パネルのより具体的な構成例について、図8乃至図12を用いて説明を行う。なお、本実施の形態では、表示パネルの一例として、液晶素子を用いた表示パネルおよび発光素子を用いた表示パネルについて説明する。

#### 【0100】

図8(A)乃至(C)は、表示パネルの構成例を示す上面図である。

40

#### 【0101】

図8(A)において、第1の基板4001上に設けられた画素部402を囲むようにして、シール材4005が設けられ、画素部402がシール材4005および第2の基板4006によって封止されている。図8(A)においては、第1の基板4001上のシール材4005によって囲まれている領域とは異なる領域に、別途用意された基板上に単結晶半導体又は多結晶半導体で形成された信号線駆動回路400、および走査線駆動回路401が設けられている。また、信号線駆動回路400、走査線駆動回路401、または画素部402に与えられる各種信号および電位は、FPC(Flexible printed circuit)4018a、FPC4018bから供給されている。

#### 【0102】

図8(B)および図8(C)において、第1の基板4001上に設けられた画素部40

50

2と、走査線駆動回路401とを囲むようにして、シール材4005が設けられている。また画素部402と、走査線駆動回路401の上に第2の基板4006が設けられている。よって画素部402と、走査線駆動回路401とは、第1の基板4001とシール材4005と第2の基板4006とによって、表示素子と共に封止されている。図8(B)および図8(C)においては、第1の基板4001上のシール材4005によって囲まれている領域とは異なる領域に、別途用意された基板上に単結晶半導体又は多結晶半導体で形成された信号線駆動回路400が設けられている。図8(B)および図8(C)においては、信号線駆動回路400、走査線駆動回路401、または画素部402に与えられる各種信号および電位は、FPC4018から供給されている。

## 【0103】

また図8(B)および図8(C)は、信号線駆動回路400として、ICなど、画素部402とは異なる工程で形成した回路を第1の基板4001に設けている例を示しているが、この構成に限定されない。走査線駆動回路401をICなどで形成しても良いし、信号線駆動回路400の一部または走査線駆動回路401の一部のみをICなどで形成して設けても良い。

## 【0104】

なお、ICなどで形成した駆動回路の接続方法は、特に限定されるものではなく、ワイヤーボンディング、COG(Chip On Glass)、TCP(Tape Carrier Package)、COF(Chip On Film)などを用いることができる。図8(A)は、COGにより信号線駆動回路400、走査線駆動回路401を設けている例であり、図8(B)は、COGにより信号線駆動回路400を設けている例であり、図8(C)は、TCPにより信号線駆動回路400を設けている例である。

## 【0105】

信号線駆動回路400をICで形成する場合、ICの数は1つとは限らず、複数のICで信号線駆動回路400を構成してもよい。同様に、走査線駆動回路401をICで形成する場合、ICの数は1つとは限らず、複数のICで走査線駆動回路401を構成してもよい。図9(A)は、一例として、信号線駆動回路400を6個のICで構成している。複数のICで信号線駆動回路を構成することで、画素部402の高精細化に対応することができる。

## 【0106】

走査線駆動回路401は、画素部402の左右両端に設けてもよい。図9(B)は、画素部402の両端に走査線駆動回路401aおよび走査線駆動回路401bを設けた場合の構成例である。

## 【0107】

信号線駆動回路400は、画素部402の上下両端に設けてもよい。図9(C)は信号線駆動回路400aおよび信号線駆動回路400bを、画素部402の上下両端に設けた場合の構成例である。それぞれの信号線駆動回路は6個のICで構成されている。図10(A)および図10(B)は、図8(B)中でN1-N2の鎖線で示した部位の断面構成を示す断面図である。

## 【0108】

図10(A)および図10(B)に示す表示パネルは電極4015を有しており、電極4015はFPC4018が有する端子と異方性導電層4019を介して、電気的に接続されている。また、電極4015は、絶縁層4110、絶縁層4111、および絶縁層4112に形成された開口において配線4014と電気的に接続されている。電極4015は、第1の電極層4030と同じ導電層から形成されている。

## 【0109】

また第1の基板4001上に設けられた画素部402と走査線駆動回路401は、トランジスタを複数有しており、図10(A)および図10(B)では、画素部402に含まれるトランジスタ4010と、走査線駆動回路401に含まれるトランジスタ4011とを例示している。図10(A)では、トランジスタ4010およびトランジスタ4011

10

20

30

40

50

上に、絶縁層 4112 が設けられ、図 10 (B) では、絶縁層 4112 の上に隔壁 4510 が形成されている。

#### 【0110】

また、トランジスタ 4010 およびトランジスタ 4011 は、絶縁層 4102 上に設けられている。また、トランジスタ 4010 およびトランジスタ 4011 は、絶縁層 4102 上に形成された電極 517 を有し、電極 517 上に絶縁層 4103 が形成されている。絶縁層 4103 上に半導体層 512 が形成されている。半導体層 512 上に電極 510 および電極 511 が形成され、電極 510 および電極 511 上に絶縁層 4110 および絶縁層 4111 が形成され、絶縁層 4110 および絶縁層 4111 上に電極 516 が形成されている。電極 510 および電極 511 は、配線 4014 と同じ導電層で形成されている。

10

#### 【0111】

トランジスタ 4010 およびトランジスタ 4011 において、電極 517 はゲート電極としての機能を有し、電極 510 はソース電極またはドレイン電極の一方としての機能を有し、電極 511 はソース電極またはドレイン電極の他方としての機能を有し、電極 516 はバックゲート電極としての機能を有する。

#### 【0112】

トランジスタ 4010 およびトランジスタ 4011 はボトムゲート構造であり、かつ、バックゲートを有することで、オン電流を増大させることができる。また、トランジスタの閾値を制御することができる。

#### 【0113】

トランジスタ 4010 およびトランジスタ 4011 において、半導体層 512 はチャネル形成領域としての機能を有する。半導体層 512 として、結晶シリコン、多結晶シリコン、非晶質シリコン、酸化物半導体、有機半導体、などを用いればよい。また、必要に応じて、半導体層 512 の導電率を高めるため、または、トランジスタの閾値を制御するために、半導体層 512 に不純物を導入してもよい。

20

#### 【0114】

半導体層 512 として酸化物半導体を用いた場合、半導体層 512 はインジウム (In) を含むことが好ましい。半導体層 512 がインジウムを含む酸化物半導体の場合、半導体層 512 はキャリア移動度 (電子移動度) が高くなる。

#### 【0115】

ただし、半導体層 512 は、インジウムを含む酸化物半導体に限定されない。半導体層 512 は、例えば、亜鉛スズ酸化物、ガリウムスズ酸化物などの、インジウムを含まず、亜鉛を含む酸化物半導体、ガリウムを含む酸化物半導体、スズを含む酸化物半導体などであっても構わない。なお、酸化物半導体の一例については、実施の形態 6 にて詳細に説明する。

30

#### 【0116】

また、図 10 (A) および図 10 (B) に示す表示パネルは、容量素子 4020 を有する。容量素子 4020 は、電極 511 と電極 4021 が絶縁層 4103 を介して重なる領域を有する。電極 4021 は、電極 517 と同じ導電層で形成されている。

40

#### 【0117】

図 10 (A) は、表示素子として液晶素子を用いた液晶表示パネルの一例である。図 10 (A) において、表示素子である液晶素子 4013 は、第 1 の電極層 4030、第 2 の電極層 4031、および液晶層 4008 を含む。なお、液晶層 4008 を挟持するように配向膜として機能する絶縁層 4032、絶縁層 4033 が設けられている。第 2 の電極層 4031 は第 2 の基板 4006 側に設けられ、第 1 の電極層 4030 と第 2 の電極層 4031 は液晶層 4008 を介して重畠する。

#### 【0118】

またスペーサ 4035 は絶縁層を選択的にエッチングすることで得られる柱状のスペーサであり、第 1 の電極層 4030 と第 2 の電極層 4031 との間隔 (セルギャップ) を制御するために設けられている。なお球状のスペーサを用いていても良い。

50

## 【0119】

表示素子として、液晶素子を用いる場合、サーモトロピック液晶、低分子液晶、高分子液晶、高分子分散型液晶、強誘電性液晶、反強誘電性液晶等を用いることができる。これらの液晶材料は、条件により、コレステリック相、スマートチック相、キューピック相、カイラルネマチック相、等方相等を示す。

## 【0120】

また、配向膜を用いないブルー相(Blue Phase)を示す液晶を用いてもよい。ブルー相は液晶相の一つであり、コレステリック液晶を昇温していくと、コレステリック相から等方相へ転移する直前に発現する相である。ブルー相は狭い温度範囲でしか発現しないため、温度範囲を改善するために5重量%以上のカイラル剤を混合させた液晶組成物を液晶層に用いる。ブルー相を示す液晶とカイラル剤とを含む液晶組成物は、応答速度が1 msec以下と短く、また、光学的等方性であるため配向処理が不要であり、且つ、視野角依存性が小さい。また配向膜を設けなくてもよいのでラビング処理も不要となるため、ラビング処理によって引き起こされる静電破壊を防止することができ、作製工程中の液晶表示パネルの不良や破損を軽減することができる。よって液晶表示パネルの生産性を向上させることができるとなる。

10

## 【0121】

また、画素(ピクセル)をいくつかの領域(サブピクセル)に分け、それぞれ別の方向に分子を倒すよう工夫されているマルチドメイン化あるいはマルチドメイン設計といわれる方法を用いることができる。

20

## 【0122】

また、液晶材料の固有抵抗は、 $1 \times 10^9 \cdot \text{cm}$ 以上であり、好ましくは $1 \times 10^{11} \cdot \text{cm}$ 以上であり、さらに好ましくは $1 \times 10^{12} \cdot \text{cm}$ 以上である。なお、本明細書における固有抵抗の値は、20で測定した値とする。

30

## 【0123】

トランジスタ4010に酸化物半導体トランジスタを用いた場合、トランジスタ4010は、オフ状態における電流値(オフ電流値)を低くすることができる。よって、画像信号等の電気信号の保持時間を長くすることができ、電源オン状態では書き込み間隔も長く設定できる。よって、リフレッシュ動作の頻度を少なくすることができるため、消費電力を抑制する効果を奏する。

## 【0124】

また、表示パネルにおいて、ブラックマトリクス(遮光層)、偏光部材、位相差部材、反射防止部材などの光学部材(光学基板)などを適宜設けてもよい。例えば、偏光基板および位相差基板による円偏光を用いてもよい。また、光源としてバックライト、サイドライトなどを用いてもよい。

## 【0125】

図10(B)は、表示素子としてEL素子などの発光素子を用いた表示パネルの一例である。EL素子は有機EL素子と無機EL素子に区別される。

## 【0126】

有機EL素子は、電圧を印加することにより、一方の電極から電子、他方の電極から正孔がそれぞれEL層に注入される。そして、それらキャリア(電子および正孔)が再結合することにより、発光性の有機化合物が励起状態を形成し、その励起状態が基底状態に戻る際に発光する。このようなメカニズムから、このような発光素子は、電流励起型の発光素子と呼ばれる。なお、EL層は、発光性の化合物以外に、正孔注入性の高い物質、正孔輸送性の高い物質、正孔ロック材料、電子輸送性の高い物質、電子注入性の高い物質、またはバイポーラ性の物質(電子輸送性および正孔輸送性が高い物質)などを有していてもよい。EL層は、蒸着法(真空蒸着法を含む)、転写法、印刷法、インクジェット法、塗布法などの方法で形成することができる。

40

## 【0127】

無機EL素子は、その素子構成により、分散型無機EL素子と薄膜型無機EL素子とに

50

分類される。分散型無機EL素子は、発光材料の粒子をバインダ中に分散させた発光層を有するものであり、発光メカニズムはドナー準位とアクセプター準位を利用するドナー・アクセプター再結合型発光である。薄膜型無機EL素子は、発光層を誘電体層で挟み込み、さらにそれを電極で挟んだ構造であり、発光メカニズムは金属イオンの内殻電子遷移を利用する局在型発光である。

#### 【0128】

図10(B)は、発光素子4513として有機EL素子を用いた例を説明する。

#### 【0129】

図10(B)において、発光素子4513は、画素部402に設けられたトランジスタ4010と電気的に接続している。なお発光素子4513の構成は、第1の電極層4030、発光層4511、第2の電極層4031の積層構造であるが、この構成に限定されない。発光素子4513から取り出す光の方向などに合わせて、発光素子4513の構成は適宜変えることができる。

10

#### 【0130】

隔壁4510は、有機絶縁材料、又は無機絶縁材料を用いて形成する。特に感光性の樹脂材料を用い、第1の電極層4030上に開口部を形成し、その開口部の側面が連続した曲率を持って形成される傾斜面となるように形成することが好ましい。

20

#### 【0131】

発光層4511は、単数の層で構成されていても、複数の層が積層されるように構成されてもどちらでも良い。

#### 【0132】

発光素子4513に酸素、水素、水分、二酸化炭素等が侵入しないように、第2の電極層4031および隔壁4510上に保護層を形成してもよい。保護層としては、窒化シリコン、窒化酸化シリコン、酸化アルミニウム、窒化アルミニウム、酸化窒化アルミニウム、窒化酸化アルミニウム、DLC(Diamond-Like Carbon)などを形成することができる。また、第1の基板4001、第2の基板4006、およびシール材4005によって封止された空間には充填材4514が設けられ密封されている。このように、外気に曝されないように気密性が高く、脱ガスの少ない保護フィルム(貼り合わせフィルム、紫外線硬化樹脂フィルム等)やカバー材でパッケージング(封入)することが好ましい。

30

#### 【0133】

充填材4514としては窒素やアルゴンなどの不活性な気体の他に、紫外線硬化樹脂または熱硬化樹脂を用いることができ、PVC(ポリビニルクロライド)、アクリル樹脂、ポリイミド、エポキシ樹脂、シリコーン樹脂、PVB(ポリビニルブチラル)またはEVA(エチレンビニルアセテート)などを用いることができる。また、充填材4514に乾燥剤が含まれていてもよい。

40

#### 【0134】

シール材4005には、ガラスフリットなどのガラス材料や、二液混合型の樹脂などの常温で硬化する硬化樹脂、光硬化性の樹脂、熱硬化性の樹脂などの樹脂材料を用いることができる。また、シール材4005に乾燥剤が含まれていてもよい。

#### 【0135】

また、必要であれば、発光素子の射出面に偏光板、又は円偏光板(楕円偏光板を含む)、位相差板(1/4板、1/2板)、カラーフィルタなどの光学フィルムを適宜設けてよい。また、偏光板又は円偏光板に反射防止膜を設けてよい。例えば、表面の凹凸により反射光を拡散し、映り込みを低減できるアンチグレア処理を施すことができる。

#### 【0136】

また、発光素子をマイクロキャビティ構造とすることで、色純度の高い光を取り出すことができる。また、マイクロキャビティ構造とカラーフィルタを組み合わせることで、映り込みが低減し、表示画像の視認性を高めることができる。

#### 【0137】

50

第1の電極層4030、第2の電極層4031は、酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、インジウム錫酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの透光性を有する導電性材料を用いることができる。

#### 【0138】

また、第1の電極層4030、第2の電極層4031はタングステン(W)、モリブデン(Mo)、ジルコニウム(Zr)、ハフニウム(Hf)、バナジウム(V)、ニオブ(Nb)、タンタル(Ta)、クロム(Cr)、コバルト(Co)、ニッケル(Ni)、チタン(Ti)、白金(Pt)、アルミニウム(Al)、銅(Cu)、銀(Ag)などの金属、またはその合金、もしくはその金属窒化物から一種以上を用いて形成することができる。

10

#### 【0139】

また、第1の電極層4030、第2の電極層4031として、導電性高分子(導電性ポリマーともいう)を含む導電性組成物を用いて形成することができる。導電性高分子としては、いわゆる電子共役系導電性高分子を用いることができる。例えば、ポリアニリンまたはその誘導体、ポリピロールまたはその誘導体、ポリチオフェンまたはその誘導体、もしくは、アニリン、ピロールおよびチオフェンの2種以上からなる共重合体またはその誘導体等が挙げられる。

#### 【0140】

発光素子4513が光を取り出すため、少なくとも第1の電極層4030または第2の電極層4031の一方が透明であればよい。表示パネルは、光の取り出し方によって、上面射出(トップエミッション)構造と、下面射出(ボトムエミッション)構造と、両面射出(デュアルエミッション)構造に分類される。上面射出構造は、トランジスタおよび発光素子が形成された基板とは逆側の面(上面)から光を取り出す場合をいう。下面射出構造は、トランジスタおよび発光素子が形成された基板の面(下面)から光を取り出す場合をいう。両面射出構造は、上面と下面の両方から光を取り出す場合をいう。例えば、上面射出構造の場合、第2の電極層4031を透明にすればよい。例えば、下面射出構造の場合、第1の電極層4030を透明にすればよい。例えば、両面射出構造の場合、第1の電極層4030および第2の電極層4031を透明にすればよい。

20

#### 【0141】

図11(A)は、図10(A)に示すトランジスタ4011および4010に、トップゲート型のトランジスタを設けた場合の断面図を示している。同様に、図11(B)は、図10(B)に示すトランジスタ4011および4010に、トップゲート型のトランジスタを設けた場合の断面図を示している。

#### 【0142】

図11(A)、(B)のトランジスタ4010、4011において、電極517はゲート電極としての機能を有し、電極510はソース電極またはドレイン電極の一方としての機能を有し、電極511はソース電極またはドレイン電極の他方としての機能を有する。

#### 【0143】

図11(A)、(B)のその他の構成要素の詳細については、図10(A)、(B)の記載を参照すればよい。

#### 【0144】

図12(A)は、図11(A)に示すトランジスタ4011およびトランジスタ4010に、バックゲートとして機能する電極516を設けた場合の断面図を示している。同様に、図12(B)は、図11(B)に示すトランジスタ4011およびトランジスタ4010に、バックゲートとして機能する電極516を設けた場合の断面図を示している。

30

#### 【0145】

トランジスタ4010およびトランジスタ4011はトップゲートおよびバックゲートを有することで、オン電流を増大させることができる。また、トランジスタの閾値を制御

することができる。

**【0146】**

図12(A)、(B)のその他の構成要素の詳細については、図10(A)、(B)の記載を参照すればよい。

**【0147】**

(実施の形態4)

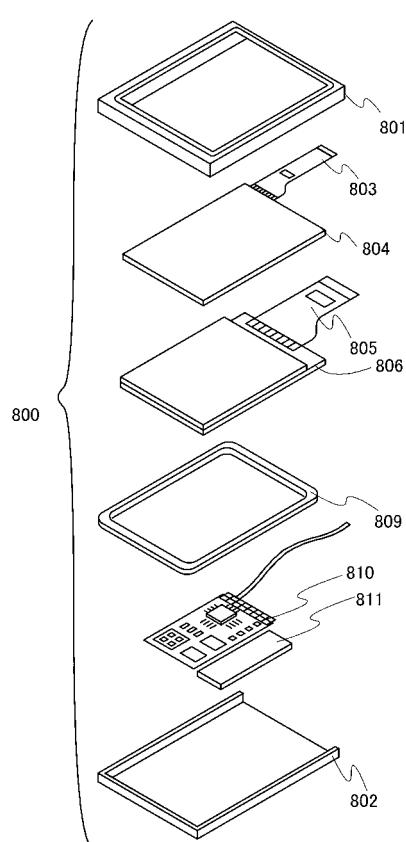

次いで上記実施の形態に示す表示パネルを用いた表示モジュールの応用例について、図13を用いて説明を行う。

**【0148】**

図13に示す表示モジュール800は、上部カバー801と下部カバー802との間に、FPC803に接続されたタッチパネル804、FPC805に接続された表示パネル806、フレーム809、プリント基板810、バッテリ811を有する。なお、バッテリ811、タッチパネル804などは、設けられない場合もある。

**【0149】**

上記実施の形態で説明した表示パネルは、図13における表示パネル806に用いることができる。

**【0150】**

上部カバー801および下部カバー802は、タッチパネル804および表示パネル806のサイズに合わせて、形状や寸法を適宜変更することができる。

**【0151】**

タッチパネル804は、抵抗膜方式または静電容量方式のタッチパネルを表示パネル806に重畳して用いることができる。また、表示パネル806の対向基板(封止基板)に、タッチパネル機能を持たせるようにすることも可能である。または、表示パネル806の各画素内に光センサを設け、光学式のタッチパネルとすることも可能である。または、表示パネル806の各画素内にタッチセンサ用電極を設け、静電容量方式のタッチパネルとすることも可能である。この場合、タッチパネル804を省略することも可能である。

**【0152】**

上部カバー801は光路を有してもよい。プリント基板810に実装された光源もしくは光源モジュールから照射された光が、上部カバー801に設けられた光路を通り、上部カバーの1辺より照射され、光を照射する1辺とは異なる他の一辺の光路に入射される光の有無をプリント基板810に実装された光センサもしくは光センサモジュールによって判断することで、指やペンなどのタッチなどによる画面タッチの有無を検出することも可能である。この場合、表示パネル806または表示パネル806の対向基板にタッチパネル機能を持たせなくともよく、さらにタッチパネル804を省略することも可能である。

**【0153】**

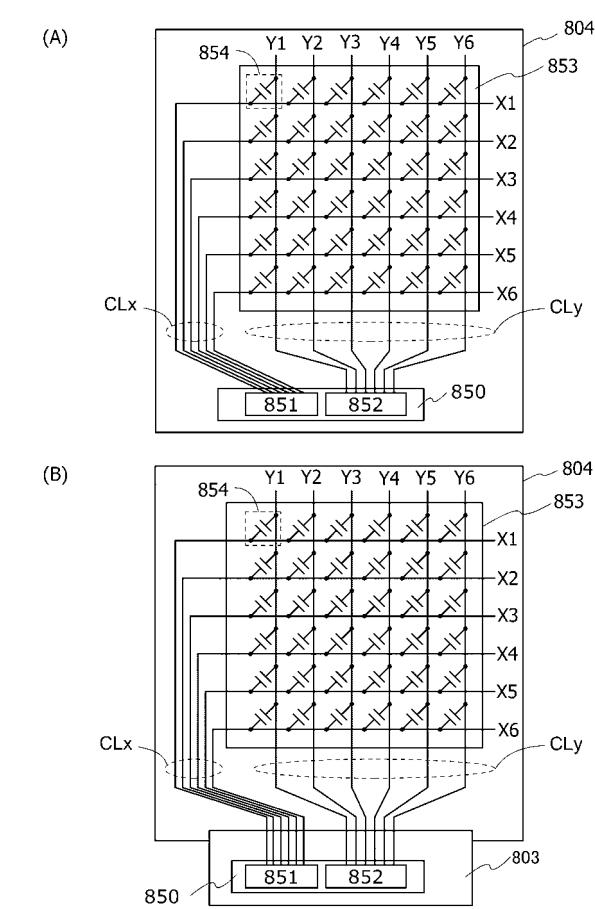

図14(A)は、タッチパネル804の一例として相互容量方式のタッチセンサを用いた場合の構成例を示す模式図である。なお図14(A)では、一例として、パルス電圧が与えられる配線CLxをX1-X6の6本の配線、電流の変化を検知する配線CLyをY1-Y6の6本の配線として示している。なお、配線の数は、これに限定されない。また図14(A)は、配線CLxおよび配線CLyが重畳すること、または、配線CLxおよび配線CLyが近接して配置されることで形成される容量素子854を図示している。

**【0154】**

配線CLxおよび配線CLyはIC850に電気的に接続されている。IC850は、駆動回路851および検出回路852を含む。

**【0155】**

駆動回路851は、一例としては、X1乃至X6の配線に順にパルス電圧を印加するための回路である。X1乃至X6の配線にパルス電圧が印加されることで、容量素子854を形成する配線CLxおよび配線CLyの間に電界が生じる。そしてパルス電圧によって容量素子854に電流が流れる。この配線間に生じる電界が、指やペンなどのタッチによる遮蔽等により変化する。つまり、指やペンなどのタッチなどにより、容量素子854の

10

20

30

40

50

容量値が変化する。このように、指やペンなどのタッチなどにより、容量値に変化を生じさせることを利用して、被検知体の近接、または接触を検出することができる。

#### 【0156】

検出回路852は、容量素子854での容量値の変化による、Y1乃至Y6の配線での電流の変化を検出するための回路である。Y1乃至Y6の配線では、被検知体の近接または接触がないと検出される電流値に変化はないが、検出する被検知体の近接または接触により容量値が減少する場合には電流値が減少する変化を検出する。なお電流の検出は、電流量の総和を検出してよい。その場合には、積分回路等を用いて検出を行えばよい。または、電流のピーク値を検出してよい。その場合には、電流を電圧に変換して、電圧値のピーク値を検出してもよい。

10

#### 【0157】

図14(A)において、駆動回路851と検出回路852は同一のICで形成されているが、それぞれの回路を異なるICに形成してもよい。検出回路852は、ノイズの影響を受けて誤動作し易い。一方で、駆動回路851はノイズの発生源になり得る。駆動回路851と検出回路852を異なるICで形成することで、検出回路852の誤動作を防ぐことができる。

20

#### 【0158】

また、駆動回路851、検出回路852および表示パネル806の駆動回路を1つのICで形成してもよい。その場合、表示モジュール全体に占めるICのコストを低減させることができる。

20

#### 【0159】

図14(A)においてIC850はタッチパネル804に配置されているが、IC850はFPC803に配置されてもよい。その場合の模式図を図14(B)に示す。

#### 【0160】

再び、図13に戻る。

#### 【0161】

フレーム809は、表示パネル806の保護機能の他、プリント基板810の動作により発生する電磁波を遮断するための電磁シールドとしての機能を有する。またフレーム809は、放熱板としての機能を有していてもよい。

30

#### 【0162】

プリント基板810は、電源回路、ビデオ信号およびクロック信号を出力するための信号処理回路を有する。さらに、タッチ検出のための光源および光センサを有してもよい。光源の波長域は、780nmより大きい波長域が望ましく、1.6μmより大きな波長域がより望ましい。光センサは、光源の波長域の光を検出する機能を有する。電源回路に電力を供給する電源としては、外部の商用電源であっても良いし、別途設けたバッテリ811による電源であってもよい。バッテリ811は、商用電源を用いる場合には、省略可能である。

30

#### 【0163】

また、表示モジュール800には、偏光板、位相差板、プリズムシートなどの部材を追加して設けてもよい。

40

#### 【0164】

##### (実施の形態5)

本実施の形態では、本発明の一態様の電子機器および照明装置について、図面を用いて説明する。

#### 【0165】

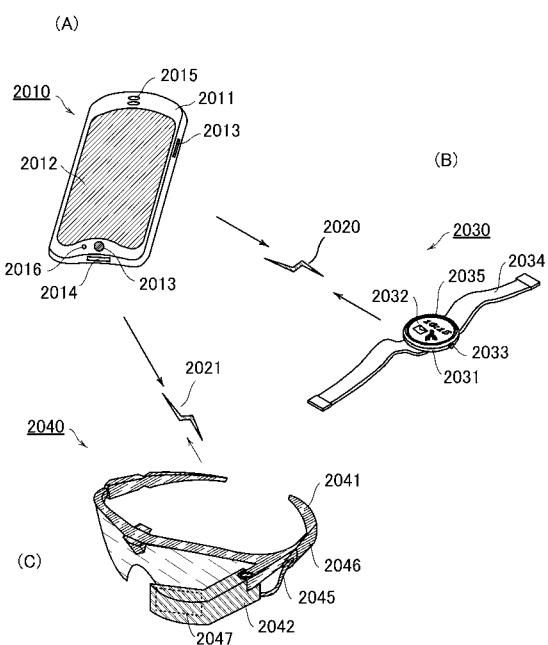

図15(A) - 図16(E)を参照して、電子機器の構成例を示す。図15(A) - 図16(C)の電子機器の表示部には、タッチセンサを有するタッチパネルを用いてもよい。タッチパネルを用いることで、表示部を電子機器の入力部としても機能させることができる。

40

#### 【0166】

50

図15(A)に示す情報端末2010は、筐体2011に組み込まれた表示部2012の他、操作ボタン2013、外部接続ポート2014、スピーカ2015、マイクロフォン2016を有する。ここでは、表示部2012の表示領域は、湾曲している。情報端末2010は、バッテリで駆動する携帯型情報端末であり、タブレット型情報端末、あるいはスマートフォンとして使用することができる。情報端末2010は、電話、電子メール、手帳、インターネット接続、音楽再生等の機能を有する。指などで表示部2012に触れることで、情報を入力することができる。また、電話を掛ける、文字を入力する、表示部2012の画面切り替え動作などの各種の操作は、指などで表示部2012に触れることで行われる。また、マイクロフォン2016から音声を入力することで、情報端末2010を操作することもできる。操作ボタン2013の操作により、電源のオン／オフ動作や、表示部2012の画面切り替え動作などの各種の操作を行うこともできる。

10

## 【0167】

図15(B)に腕時計型の情報端末の一例を示す。情報端末2030は、筐体2031、表示部2032、リュウズ2033、ベルト2034、検知部2035を有する。リュウズ2033を回転することで情報端末2030を操作することができる。表示部2032を指で触ることで、情報端末2030を操作することができる。

## 【0168】

検知部2035は、例えば、使用環境の情報、生体情報を取得する機能を備える。マイクロフォン、撮像素子、加速度センサ、方位センサ、圧力センサ、温度センサ、湿度センサ、照度センサ、測位センサ(例えば、GPS(全地球測位システム))等を検知部2035に設けてもよい。

20

## 【0169】

情報端末2010および情報端末2030に同じ規格の無線通信装置を組み込み、無線信号2020により双方向の通信を行うようにしてもよい。例えば、情報端末2010が電子メール、電話などを着信すると、情報端末2030の表示部2032に着信を知らせる情報が表示される。

## 【0170】

図15(C)に、眼鏡型の情報端末の例を示す。情報端末2040は、装着部2041、筐体2042、ケーブル2045、バッテリ2046、表示部2047を有する。バッテリ2046は装着部2041に収納されている。表示部2047は筐体2042に設けられている。筐体2042は、プロセッサ、無線通信装置、記憶装置、各種の電子部品を内蔵する。ケーブル2045を介してバッテリ2046から筐体2042内の表示部2047および電子部品に電力が供給される。表示部2047には無線によって送信された映像等の各種の情報が表示される。実施の形態1で示した線順次によるインパルス駆動を用いることで、ちらつきを抑えながら、動画解像度の向上と、消費電力の低減とを提供することができる。

30

## 【0171】

無線信号を用いた通信を行う情報端末などは、通信に用いるアンテナによって、電磁結合方式、電磁誘導方式、電波方式のいずれか一においてエネルギーを生成する機能を有することができる。

40

## 【0172】

筐体2042にカメラを設けてもよい。カメラによって、使用者の眼球やまぶたの動きを検知することで、情報端末2040を操作することができる。

## 【0173】

装着部2041に、温度センサ、圧力センサ、加速度センサ、生体センサ等の各種センサを設けてもよい。例えば、生体センサによって、使用者の生体情報を取得し、筐体2042内の記憶装置に記憶させる。例えば、無線信号2021によって、情報端末2010と情報端末2040間で双方向の通信可能にする。情報端末2040は、記憶している生体情報を情報端末2010に送信する。情報端末2010は、受信した生体情報から使用者の疲労度、活動量などを算出する。

50

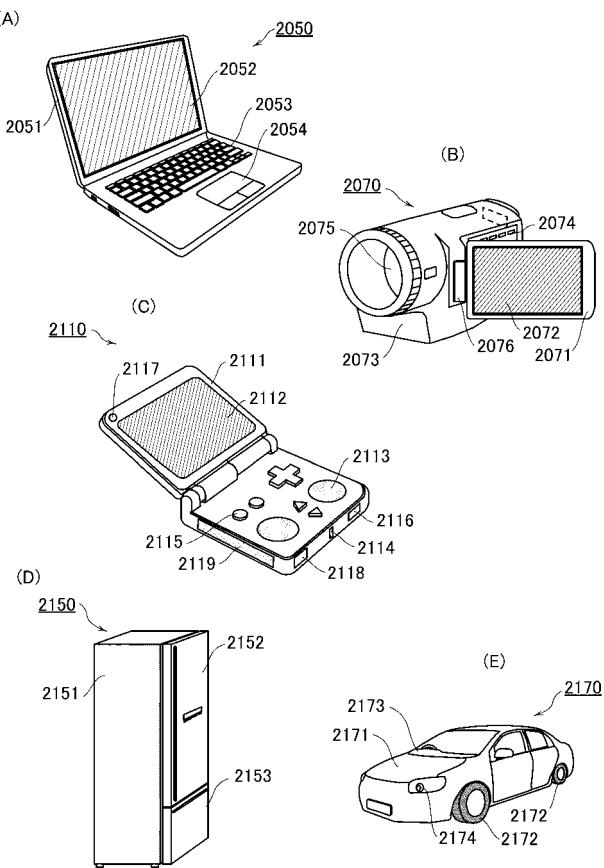

## 【0174】

図16(A)に示すノート型PC(パーソナルコンピュータ)2050は、筐体2051、表示部2052、キーボード2053、ポインティングデバイス2054を有する。表示部2052のタッチ操作で、ノート型PC2050を操作することができる。

## 【0175】

図16(B)示すビデオカメラ2070は、筐体2071、表示部2072、筐体2073、操作キー2074、レンズ2075、接続部2076を有する。表示部2072は筐体2071に設けられ、操作キー2074およびレンズ2075は筐体2073に設けられている。筐体2071と筐体2073とは、接続部2076により接続されており、筐体2071と筐体2073間の角度は、接続部2076により変更が可能である。接続部2076における筐体2071と筐体2073間の角度に従って、表示部2072の映像を切り替える構成としてもよい。表示部2072のタッチ操作によって、録画の開始および停止の操作、倍率ズーム調整、撮影範囲の変更などの各種の操作を実行できる。

10

## 【0176】

図16(C)に示す携帯型遊技機2110は、筐体2111、表示部2112、スピーカ2113、LEDランプ2114、操作キーボタン2115、接続端子2116、カメラ2117、マイクロフォン2118、記録媒体読込部2119を有する。

## 【0177】

図16(D)に示す電気冷凍冷蔵庫2150は、筐体2151、冷蔵室用扉2152、および冷凍室用扉2153等を有する。

20

## 【0178】

図16(E)に示す自動車2170は、車体2171、車輪2172、ダッシュボード2173、およびライト2174等を有する。実施の形態2のプロセッサは、自動車2170内の各種のプロセッサに用いられる。

## 【0179】

(実施の形態6)

< C A C - O S の構成 >

以下では、本発明の一態様で開示されるトランジスタに用いることができるC A C ( C l o u d - A l i g n e d C o m p o s i t e ) - O S の構成について説明する。

30

## 【0180】

C A C - O S とは、例えば、酸化物半導体を構成する元素が、0.5 nm以上10 nm以下、好ましくは、1 nm以上2 nm以下、またはその近傍のサイズで偏在した材料の一構成である。なお、以下では、酸化物半導体において、一つあるいはそれ以上の金属元素が偏在し、該金属元素を有する領域が、0.5 nm以上10 nm以下、好ましくは、1 nm以上2 nm以下、またはその近傍のサイズで混合した状態をモザイク状、またはパッチ状ともいう。

## 【0181】

なお、酸化物半導体は、少なくともインジウムを含むことが好ましい。特にインジウムおよび亜鉛を含むことが好ましい。また、それらに加えて、アルミニウム、ガリウム、イットリウム、銅、バナジウム、ベリリウム、ホウ素、シリコン、チタン、鉄、ニッケル、ゲルマニウム、ジルコニウム、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タンゲステン、またはマグネシウムなどから選ばれた一種、または複数種が含まれていてもよい。

40

## 【0182】

例えば、In-Ga-Zn酸化物におけるC A C - O S ( C A C - O S の中でもIn-Ga-Zn酸化物を、特にC A C - I G Z Oと呼称してもよい)とは、インジウム酸化物(以下、 $In_{X_1}O_{Y_1}$  ( $X_1$ は0よりも大きい実数)とする)、またはインジウム亜鉛酸化物(以下、 $In_{X_2}Zn_{Y_2}O_{Z_2}$  ( $X_2$ 、 $Y_2$ 、および $Z_2$ は0よりも大きい実数)とする)と、ガリウム酸化物(以下、 $Ga_{X_3}O_{Y_3}$  ( $X_3$ は0よりも大きい実数)とする)、またはガリウム亜鉛酸化物(以下、 $Ga_{X_4}Zn_{Y_4}O_{Z_4}$  ( $X_4$ 、 $Y_4$ 、および $Z_4$ は

50

0よりも大きい実数)とする)などと、に材料が分離することでモザイク状となり、モザイク状の  $In_{n_x}O_{x_1}$ 、または  $In_{n_x}Z_{n_y}O_{z_2}$  が、膜中に均一に分布した構成(以下、クラウド状ともいう)である。

#### 【0183】

つまり、CAC-O<sub>S</sub>は、GaO<sub>x\_3</sub>が主成分である領域と、In<sub>n\_x</sub>Z<sub>n\_y</sub>O<sub>z\_2</sub>、またはInO<sub>x\_1</sub>が主成分である領域とが、混合している構成を有する複合酸化物半導体である。なお、本明細書において、例えば、第1の領域の元素Mに対するInの原子数比が、第2の領域の元素Mに対するInの原子数比よりも大きいことを、第1の領域は、第2の領域と比較して、Inの濃度が高いとする。

#### 【0184】

なお、IGZOは通称であり、In、Ga、Zn、およびOによる1つの化合物をいう場合がある。代表例として、InGaO<sub>3</sub>(ZnO)<sub>m1</sub>(m1は自然数)、またはIn<sub>(1+x\_0)</sub>Ga<sub>(1-x\_0)</sub>O<sub>3</sub>(ZnO)<sub>m0</sub>(-1 < x\_0 < 1, m0は任意数)で表される結晶性の化合物が挙げられる。

#### 【0185】

上記結晶性の化合物は、単結晶構造、多結晶構造、またはCAC構造を有する。なお、CAC構造とは、複数のIGZOのナノ結晶がc軸配向を有し、かつa-b面においては配向せずに連結した結晶構造である。

#### 【0186】

一方、CAC-O<sub>S</sub>は、酸化物半導体の材料構成に関する。CAC-O<sub>S</sub>とは、In、Ga、Zn、およびOを含む材料構成において、一部にGaを主成分とするナノ粒子状に観察される領域と、一部にInを主成分とするナノ粒子状に観察される領域とが、それぞれモザイク状にランダムに分散している構成をいう。従って、CAC-O<sub>S</sub>において、結晶構造は副次的な要素である。

#### 【0187】

なお、CAC-O<sub>S</sub>は、組成の異なる二種類以上の膜の積層構造は含まないものとする。例えば、Inを主成分とする膜と、Gaを主成分とする膜との2層からなる構造は、含まない。

#### 【0188】

なお、GaO<sub>x\_3</sub>が主成分である領域と、In<sub>n\_x</sub>Z<sub>n\_y</sub>O<sub>z\_2</sub>、またはInO<sub>x\_1</sub>が主成分である領域とは、明確な境界の観察が難しい場合がある。

#### 【0189】

なお、ガリウムの代わりに、アルミニウム、イットリウム、銅、バナジウム、ベリリウム、ホウ素、シリコン、チタン、鉄、ニッケル、ゲルマニウム、ジルコニウム、モリブデン、ラントン、セリウム、ネオジム、ハフニウム、タンタル、タングステン、またはマグネシウムなどから選ばれた一種、または複数種の金属元素が含まれている場合、CAC-O<sub>S</sub>は、一部に該金属元素を主成分とするナノ粒子状に観察される領域と、一部にInを主成分とするナノ粒子状に観察される領域とが、それぞれモザイク状にランダムに分散している構成をいう。

#### 【0190】

CAC-O<sub>S</sub>は、例えば基板を意図的に加熱しない条件で、スパッタリング法により形成することができる。また、CAC-O<sub>S</sub>をスパッタリング法で形成する場合、成膜ガスとして、不活性ガス(代表的にはアルゴン)、酸素ガス、及び窒素ガスの中から選ばれたいずれか一つまたは複数を用いればよい。また、成膜時の成膜ガスの総流量に対する酸素ガスの流量比は低いほど好ましく、例えば酸素ガスの流量比を0%以上30%未満、好ましくは0%以上10%以下とすることが好ましい。

#### 【0191】

CAC-O<sub>S</sub>は、X線回折(XRD: X-ray diffraction)測定法のひとつであるOut-of-plane法による1/2スキャンを用いて測定したときに、明確なピークが観察されないという特徴を有する。すなわち、X線回折から、測定領

10

20

30

40

50

域の a - b 面方向、および c 軸方向の配向は見られないことが分かる。

#### 【 0 1 9 2 】

また C A C - O S は、プローブ径が 1 nm の電子線（ナノビーム電子線ともいう）を照射することで得られる電子線回折パターンにおいて、リング状に輝度の高い領域と、該リング領域に複数の輝点が観測される。従って、電子線回折パターンから、C A C - O S の結晶構造が、平面方向、および断面方向において、配向性を有さない n c ( n a n o - c r y s t a l ) 構造を有することがわかる。

#### 【 0 1 9 3 】

また例えれば、In - Ga - Zn 酸化物における C A C - O S では、エネルギー分散型 X 線分光法 ( E D X : Energy Dispersive X-ray spectrometer ) を用いて取得した E D X マッピングにより、 $GaO_{x_3}$  が主成分である領域と、 $In_{x_2}Zn_{y_2}O_{z_2}$ 、または  $InO_{x_1}$  が主成分である領域とが、偏在し、混合している構造を有することが確認できる。

10

#### 【 0 1 9 4 】

C A C - O S は、金属元素が均一に分布した I G Z O 化合物とは異なる構造であり、I G Z O 化合物と異なる性質を有する。つまり、C A C - O S は、 $GaO_{x_3}$  などが主成分である領域と、 $In_{x_2}Zn_{y_2}O_{z_2}$ 、または  $InO_{x_1}$  が主成分である領域と、に互いに相分離し、各元素を主成分とする領域がモザイク状である構造を有する。

#### 【 0 1 9 5 】

ここで、 $In_{x_2}Zn_{y_2}O_{z_2}$ 、または  $InO_{x_1}$  が主成分である領域は、 $GaO_{x_3}$  などが主成分である領域と比較して、導電性が高い領域である。つまり、 $In_{x_2}Zn_{y_2}O_{z_2}$ 、または  $InO_{x_1}$  が主成分である領域を、キャリアが流れることにより、酸化物半導体としての導電性が発現する。従って、 $In_{x_2}Zn_{y_2}O_{z_2}$ 、または  $InO_{x_1}$  が主成分である領域が、酸化物半導体中にクラウド状に分布することで、高い電界効果移動度 ( $\mu$ ) が実現できる。

20

#### 【 0 1 9 6 】

一方、 $GaO_{x_3}$  などが主成分である領域は、 $In_{x_2}Zn_{y_2}O_{z_2}$ 、または  $InO_{x_1}$  が主成分である領域と比較して、絶縁性が高い領域である。つまり、 $GaO_{x_3}$  などが主成分である領域が、酸化物半導体中に分布することで、リーク電流を抑制し、良好なスイッチング動作を実現できる。

30

#### 【 0 1 9 7 】

従って、C A C - O S を半導体素子に用いた場合、 $GaO_{x_3}$  などに起因する絶縁性と、 $In_{x_2}Zn_{y_2}O_{z_2}$ 、または  $InO_{x_1}$  に起因する導電性とが、相補的に作用することにより、高いオン電流 ( $I_{on}$ )、および高い電界効果移動度 ( $\mu$ ) を実現することができる。

#### 【 0 1 9 8 】

また、C A C - O S を用いた半導体素子は、信頼性が高い。従って、C A C - O S は、ディスプレイをはじめとするさまざまな半導体装置に最適である。

#### 【 0 1 9 9 】

本実施の形態は、少なくともその一部を本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

40

#### 【 符号の説明 】

#### 【 0 2 0 0 】

G 1 走査線

G 2 走査線

G 3 走査線

M 1 トランジスタ

S 信号線

S P 1 スタートパルス

S P 2 スタートパルス

10

20

30

40

50

|         |           |    |

|---------|-----------|----|

| S W 1   | トランジスタ    |    |

| S W 2   | トランジスタ    |    |

| 1 0     | 表示装置      |    |

| 1 1 0   | ゲートドライバ   |    |

| 1 1 1   | シフトレジスタ回路 |    |

| 1 1 2   | シフトレジスタ回路 |    |

| 1 2 0   | 表示部       |    |

| 4 0 0   | 信号線駆動回路   |    |

| 4 0 0 a | 信号線駆動回路   | 10 |

| 4 0 0 b | 信号線駆動回路   |    |

| 4 0 1   | 走査線駆動回路   |    |

| 4 0 1 a | 走査線駆動回路   |    |

| 4 0 1 b | 走査線駆動回路   |    |

| 4 0 2   | 画素部       |    |

| 5 1 0   | 電極        |    |

| 5 1 1   | 電極        |    |

| 5 1 2   | 半導体層      |    |

| 5 1 6   | 電極        |    |

| 5 1 7   | 電極        |    |

| 7 1 0   | 発光素子      | 20 |

| 7 1 0 C | 画素回路      |    |

| 8 0 0   | 表示モジュール   |    |

| 8 0 1   | 上部カバー     |    |

| 8 0 2   | 下部カバー     |    |

| 8 0 3   | FPC       |    |

| 8 0 4   | タッチパネル    |    |

| 8 0 5   | FPC       |    |

| 8 0 6   | 表示パネル     |    |

| 8 0 9   | フレーム      |    |

| 8 1 0   | プリント基板    | 30 |

| 8 1 1   | バッテリ      |    |

| 8 5 0   | I C       |    |

| 8 5 1   | 駆動回路      |    |

| 8 5 2   | 検出回路      |    |

| 8 5 4   | 容量素子      |    |

| 2 0 1 0 | 情報端末      |    |

| 2 0 1 1 | 筐体        |    |

| 2 0 1 2 | 表示部       |    |

| 2 0 1 3 | 操作ボタン     |    |

| 2 0 1 4 | 外部接続ポート   | 40 |

| 2 0 1 5 | スピーカ      |    |

| 2 0 1 6 | マイクロフォン   |    |

| 2 0 2 0 | 無線信号      |    |

| 2 0 2 1 | 無線信号      |    |

| 2 0 3 0 | 情報端末      |    |

| 2 0 3 1 | 筐体        |    |

| 2 0 3 2 | 表示部       |    |

| 2 0 3 3 | リュウズ      |    |

| 2 0 3 4 | ベルト       |    |

| 2 0 3 5 | 検知部       | 50 |

|           |             |    |

|-----------|-------------|----|

| 2 0 4 0   | 情報端末        |    |

| 2 0 4 1   | 装着部         |    |

| 2 0 4 2   | 筐体          |    |

| 2 0 4 5   | ケーブル        |    |

| 2 0 4 6   | バッテリ        |    |

| 2 0 4 7   | 表示部         |    |

| 2 0 5 1   | 筐体          |    |

| 2 0 5 2   | 表示部         |    |

| 2 0 5 3   | キー ボード      |    |

| 2 0 5 4   | ポインティングデバイス | 10 |

| 2 0 7 0   | ビデオカメラ      |    |

| 2 0 7 1   | 筐体          |    |

| 2 0 7 2   | 表示部         |    |

| 2 0 7 3   | 筐体          |    |

| 2 0 7 4   | 操作キー        |    |

| 2 0 7 5   | レンズ         |    |

| 2 0 7 6   | 接続部         |    |

| 2 1 1 0   | 携帯型遊技機      |    |

| 2 1 1 1   | 筐体          |    |

| 2 1 1 2   | 表示部         | 20 |

| 2 1 1 3   | スピーカ        |    |

| 2 1 1 4   | LEDランプ      |    |

| 2 1 1 5   | 操作キー ボタン    |    |

| 2 1 1 6   | 接続端子        |    |

| 2 1 1 7   | カメラ         |    |

| 2 1 1 8   | マイクロフォン     |    |

| 2 1 1 9   | 記録媒体読込部     |    |

| 2 1 5 0   | 電気冷凍冷蔵庫     |    |

| 2 1 5 1   | 筐体          |    |

| 2 1 5 2   | 冷蔵室用扉       | 30 |

| 2 1 5 3   | 冷凍室用扉       |    |

| 2 1 7 0   | 自動車         |    |

| 2 1 7 1   | 車体          |    |

| 2 1 7 2   | 車輪          |    |

| 2 1 7 3   | ダッシュボード     |    |

| 2 1 7 4   | ライト         |    |

| 2 0 5 0   | ノート型PC      |    |

| 4 0 0 1   | 基板          |    |

| 4 0 0 5   | シール材        |    |

| 4 0 0 6   | 基板          | 40 |

| 4 0 0 8   | 液晶層         |    |

| 4 0 1 0   | トランジスタ      |    |

| 4 0 1 1   | トランジスタ      |    |

| 4 0 1 3   | 液晶素子        |    |

| 4 0 1 4   | 配線          |    |

| 4 0 1 5   | 電極          |    |

| 4 0 1 8   | FPC         |    |

| 4 0 1 8 b | FPC         |    |

| 4 0 1 9   | 異方性導電層      |    |

| 4 0 2 0   | 容量素子        | 50 |

|         |        |    |

|---------|--------|----|

| 4 0 2 1 | 電極     |    |

| 4 0 3 0 | 電極層    |    |

| 4 0 3 1 | 電極層    |    |

| 4 0 3 2 | 絶縁層    |    |

| 4 0 3 3 | 絶縁層    |    |

| 4 0 3 5 | スペーサ   |    |

| 4 1 0 2 | 絶縁層    | 10 |

| 4 1 0 3 | 絶縁層    |    |

| 4 1 1 0 | 絶縁層    |    |

| 4 1 1 1 | 絶縁層    |    |

| 4 1 1 2 | 絶縁層    |    |

| 4 5 1 0 | 隔壁     |    |

| 4 5 1 1 | 発光層    |    |

| 4 5 1 3 | 発光素子   |    |

| 4 5 1 4 | 充填材    |    |

| 6 0 0 0 | 電子部品   |    |

| 6 0 0 1 | リード    |    |

| 6 0 0 2 | プリント基板 | 20 |

| 6 0 0 4 | 回路基板   |    |

| 6 1 0 0 | 半導体ウエハ |    |

| 6 1 0 2 | 回路領域   |    |

| 6 1 0 4 | 分離領域   |    |

| 6 1 0 6 | 分離線    |    |

| 6 1 1 0 | チップ    |    |

【図1】

【図2】

【図3】

【図4】

【図5】

120

【図6】

710C(i,j)

【 四 7 】

【 図 8 】

【図9】

【 図 1 0 】

【図 1 1】

【図 1 2】

【図 1 4】

【図 1 3】

【図15】

【図16】

---

フロントページの続き

F ターム(参考) 5C380 AA01 AA02 AB06 AB09 AB11 AB12 AB13 AB21 AB22 AB23

AB25 AB28 AC02 AC08 AC10 AC11 AC12 BA03 BA08 BA28

BB09 BE05 BE12 CA12 CA48 CA49 CB02 CB18 CB26 CB32

CC01 CC03 CC26 CC33 CC63 CC64 CD012 CD013 CE02 CF07

CF68 DA02 DA06 DA41 DA42