(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5288479号

(P5288479)

(45) 発行日 平成25年9月11日(2013.9.11)

(24) 登録日 平成25年6月14日(2013.6.14)

(51) Int.Cl.

F 1

|             |               |                  |      |      |         |

|-------------|---------------|------------------|------|------|---------|

| <b>G09G</b> | <b>3/20</b>   | <b>(2006.01)</b> | G09G | 3/20 | 6 7 0 M |

| <b>G02F</b> | <b>1/133</b>  | <b>(2006.01)</b> | G09G | 3/20 | 6 2 4 D |

| <b>H01L</b> | <b>21/822</b> | <b>(2006.01)</b> | G09G | 3/20 | 6 2 1 G |

| <b>H01L</b> | <b>27/04</b>  | <b>(2006.01)</b> | G09G | 3/20 | 6 1 1 A |

| <b>G09G</b> | <b>3/36</b>   | <b>(2006.01)</b> | G09G | 3/20 | 6 2 3 B |

請求項の数 1 (全 12 頁) 最終頁に続く

(21) 出願番号

特願2009-108404 (P2009-108404)

(22) 出願日

平成21年4月27日(2009.4.27)

(65) 公開番号

特開2010-256734 (P2010-256734A)

(43) 公開日

平成22年11月11日(2010.11.11)

審査請求日

平成24年2月21日(2012.2.21)

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部 1753 番地

(74) 代理人 100102864

弁理士 工藤 実

(72) 発明者 西村 浩一

神奈川県川崎市中原区下沼部 1753 番地

NECエレクトロニクス株式会社内

審査官 中村 直行

最終頁に続く

(54) 【発明の名称】表示パネルドライバ

## (57) 【特許請求の範囲】

## 【請求項 1】

第 1 及び第 2 アンプと、

第 1 ~ 第 n 偶数出力ノードと (n は、2 以上の整数)、

第 1 ~ 第 n 奇数出力ノードと、

表示パネルのデータ線にそれぞれに接続される第 1 及び第 2 出力パッドと、

第 1 ~ 第 n スイッチブロックと、

第 1 ~ 第 n 偶数静電保護抵抗と、

第 1 ~ 第 n 奇数静電保護抵抗

とを具備し、

前記第 1 ~ 第 n スイッチブロックのうちの第 i スイッチブロックは、前記第 1 及び第 2 アンプと、前記第 i 偶数出力ノード及び前記第 i 奇数出力ノードとの間の接続関係を切り換えるように構成され、

前記第 1 ~ 第 n 偶数静電保護抵抗が、それぞれ、前記第 1 ~ 第 n 偶数出力ノードと前記第 1 出力パッドとの間に接続され、

前記第 1 ~ 第 n 奇数静電保護抵抗が、それぞれ、前記第 1 ~ 第 n 奇数出力ノードと前記第 2 出力パッドとの間に接続され、

前記第 1 アンプは、前記表示パネルの対向電極に供給される共通電圧より低い駆動電圧を生成するように構成され、

前記第 2 アンプは、前記共通電圧より高い駆動電圧を生成するように構成され、

10

20

前記第1～第nスイッチブロックのうちの第iスイッチブロックは、

前記第1アンプと前記第i偶数出力ノードとの間に設けられた第1スイッチと、

前記第2アンプと前記第i奇数出力ノードとの間に設けられた第2スイッチと、

前記第1アンプと前記第i奇数出力ノードとの間に設けられた第3スイッチと、

前記第2アンプと前記第i偶数出力ノードとの間に設けられた第4スイッチ

とを備えている

表示パネルドライバ。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

10

本発明は、表示パネルドライバに関し、特に、表示パネルドライバの出力回路において、パッドに接続される静電保護抵抗の影響をできるだけ少なくする手法に関する。

##### 【背景技術】

##### 【0002】

20

L C D (liquid crystal display) ドライバその他の表示パネルドライバを集積回路によって実現する場合、一般的には、出力回路の出力段とパッド間に静電保護抵抗が直列に挿入される。もし、この静電保護抵抗を直列に挿入しない場合は、出力段のトランジスタのサイズを必要に大きくしたり、出力トランジスタを静電保護用素子で構成したりしなければならない等、特別な工夫が必要であるからである。しかしながら、このように特別なことをすると寄生容量が増えたり、チップサイズが増えたり、所望の特性が実現出来ない等々の問題点が多々発生する。

##### 【0003】

出力回路の出力段とパッド間に静電保護抵抗が直列に挿入される場合、その静電保護抵抗の抵抗値は、静電気から内部トランジスタを保護する目的で定められた基準を満たす範囲に設定される。静電保護抵抗は、一般的には、数十～数百の抵抗値に設定される。この範囲より小さい抵抗値だとM I L 規格 (Military Standard) やE I A J (Electronic Industries Association of Japan) で決められた静電保護基準を満足することができない。

##### 【0004】

30

しかしながら、表示パネルドライバの出力回路に静電保護抵抗を接続すると、出力特性が劣化してしまう。以下では、出力回路に静電保護抵抗を接続した場合の出力特性の劣化について議論する。

##### 【0005】

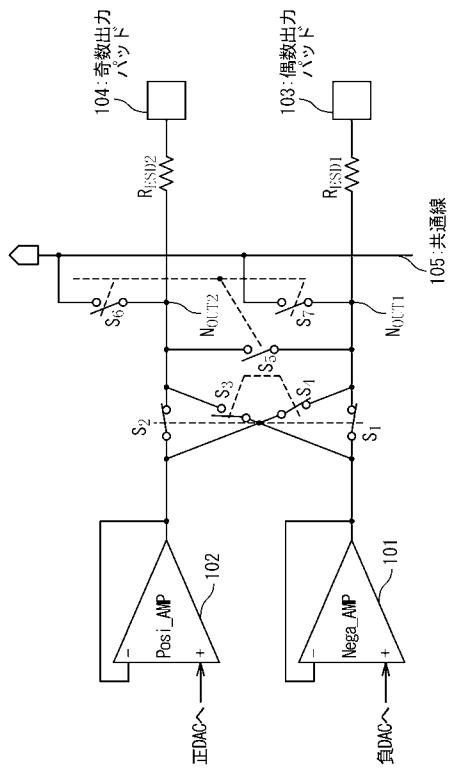

図1は、アナログ増幅回路を使ったL C D ドライバの出力回路の例を示す回路構成図である。図1には、出力回路のうち2つの出力パッドに対応する部分のみが図示されている。図1のL C D ドライバの出力回路は、負側アンプ101と、正側アンプ102と、偶数出力パッド103と、奇数出力パッド104と、共通線105と、静電保護抵抗R<sub>E S D 1</sub>、R<sub>E S D 2</sub>と、スイッチS<sub>1</sub>～S<sub>7</sub>とを備えている。負側アンプ101、正側アンプ102は、いずれも、ボルテッジフォロワ接続されており、各々の正転入力端子は、それぞれ、正側D / Aコンバータ (Digital to Analog Converter) と負側D / Aコンバータに接続される。

40

##### 【0006】

スイッチS<sub>1</sub>は偶数出力ノードN<sub>O U T 1</sub>と負側アンプ101の出力の間に接続され、スイッチS<sub>2</sub>は奇数出力ノードN<sub>O U T 2</sub>と正側アンプ102の出力の間に接続されている。スイッチS<sub>3</sub>は奇数出力ノードN<sub>O U T 2</sub>と負側アンプ101の出力の間に接続され、スイッチS<sub>4</sub>は偶数出力ノードN<sub>O U T 1</sub>と正側アンプ102の出力の間に接続されている。スイッチS<sub>1</sub>～S<sub>4</sub>は連動して動作する。スイッチS<sub>5</sub>は、偶数出力ノードN<sub>O U T 1</sub>と奇数出力ノードN<sub>O U T 2</sub>の間に接続され、スイッチS<sub>6</sub>は、奇数出力ノードN<sub>O U T 2</sub>と共通線105の間に接続され、スイッチS<sub>7</sub>は、偶数出力ノードN<sub>O U T 1</sub>と共通線105の間に接続される。スイッチS<sub>5</sub>～S<sub>7</sub>は連動して動作する。

50

## 【0007】

一方、静電保護抵抗  $R_{ESD1}$  は、偶数出力ノード  $N_{OUT1}$  と偶数出力パッド 103 の間に接続され、静電保護抵抗  $R_{ESD2}$  は、奇数出力ノード  $N_{OUT2}$  と奇数出力パッド 104 の間に接続される。尚、実際には、静電保護のために静電保護抵抗  $R_{ESD1}$ 、 $R_{ESD2}$  以外にも静電保護ダイオード等々も並列的に使用するのが一般的であるが、本発明と直接関係ないので、ここではその回路の図面への記載と、その説明を省略する。

## 【0008】

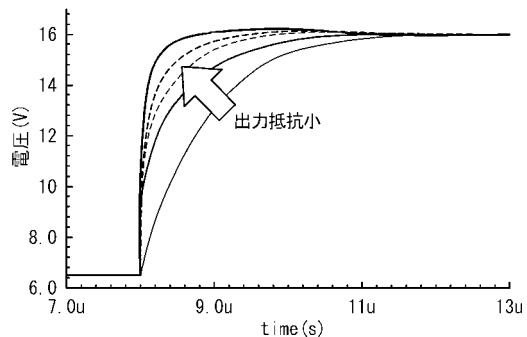

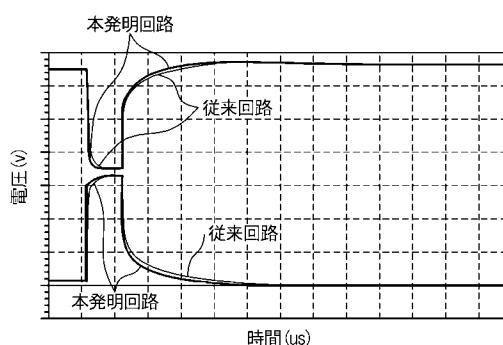

これらの静電保護抵抗  $R_{ESD1}$ 、 $R_{ESD2}$  は、静電破壊を防止する一方で出力波形を劣化させてしまう。入力端子に矩形波を入力した場合の出力波形を、静電保護抵抗の抵抗値を変えてプロットしたのが図 2 である。この図 2 からわかるように静電保護抵抗の値が大きくなるにつれて出力波形が鈍ってくる様子がわかる。理想的にはこの静電保護抵抗の抵抗値がゼロの時に特性が最良になるが、実際にはある規定された抵抗値の静電保護抵抗を入れなければならないので、その抵抗値に応じて特性が制限されてしまう。

## 【0009】

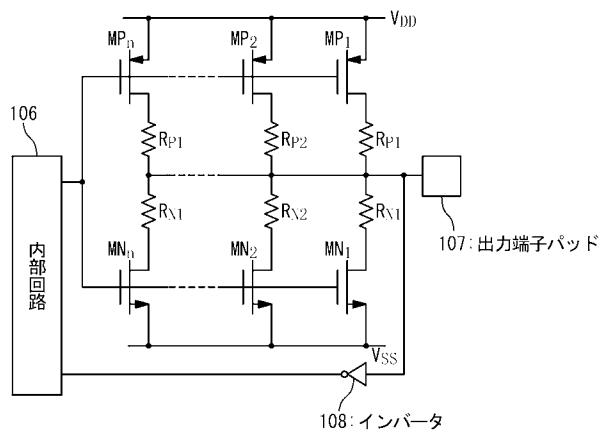

一方で、デジタル回路の出力回路について、静電保護抵抗の影響を低減させることを目的とした構成が、例えば特開 2001-358300 号公報（特許文献 1）に開示されている。図 3 を参照して、この公報に記載された出力回路を説明する。図 3 の出力回路は、 $n$  個の PMOS トランジスタ  $MP_1 \sim MP_n$  と、 $n$  個の NMOS トランジスタ  $MN_1 \sim MN_n$  と、PMOS 用静電保護抵抗  $R_{P1} \sim R_{Pn}$  と、NMOS 用静電保護抵抗  $R_{N1} \sim R_{Nn}$  と、内部回路 106 と、出力端子パッド 107 と、インバータ 108 とを備えている。 $PMOS$  トランジスタ  $MP_1 \sim MP_n$  は、各々のソースが正電源電圧 ( $V_{DD}$ ) の電源線に共通接続されており、また、NMOS 用静電保護抵抗  $R_{N1} \sim R_{Nn}$  は、各々のソースが負電源電圧 ( $V_{SS}$ ) の電源線に共通接続されている。インバータ 108 は、その入力が出力端子パッド 107 に接続され、出力が内部回路 106 に接続されている。 $PMOS$  トランジスタ  $MP_1 \sim MP_n$  の各々のゲートと NMOS トランジスタ  $MN_1 \sim MN_n$  の各々のゲートは、内部回路 106 の出力に共通に接続されている。また、PMOS 用静電保護抵抗  $R_{P1} \sim R_{Pn}$  は、PMOS トランジスタ  $MP_1 \sim MP_n$  のドレインと出力端子パッド 107との間に接続され、NMOS 用静電保護抵抗  $R_{N1} \sim R_{Nn}$  は、NMOS トランジスタ  $MN_1 \sim MN_n$  のドレインと出力端子パッド 107との間に接続されている。

## 【0010】

図 3 を参照すると、PMOS 用静電保護抵抗  $R_{P1} \sim R_{Pn}$  と、NMOS 用静電保護抵抗  $R_{N1} \sim R_{Nn}$  は、静電気サージから MOS トランジスタの破壊を防ぐために挿入されるもので、デバイスプロセスにもよるが、その抵抗値は通常数十 ~ 数百 程度である。静電保護抵抗  $R_{P1} \sim R_{Pn}$ 、 $R_{N1} \sim R_{Nn}$  の実際の抵抗値は、各デバイスプロセスの実力値にもより様々であるが、基準を満たす抵抗値に設定する必要がある。上述のように静電保護抵抗において発生する電圧降下は出力回路の特性劣化の原因になるが、図 3 に示すように複数個の MOS トランジスタを並列接続することにより、流れる電流を  $n$  個の静電保護抵抗に分散化することが可能である。すなわち 1 個の静電保護抵抗に流れる電流は、本来の電流の  $1/n$  になる。これにより各静電保護抵抗に流れる電流による電圧降下も  $1/n$  になり、ひいては出力回路の特性劣化を防止することができる。

## 【先行技術文献】

## 【特許文献】

## 【0011】

## 【特許文献 1】特開 2001-358300 号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0012】

上述したように静電保護抵抗の抵抗値を下げれば出力特性が良くなることが分かっている。よって図 3 に図示されている回路と同様な考え方で出力を分割して、実効的な静電保

10

20

30

40

50

護抵抗の抵抗値を下げる事が考えられる。しかし図3の回路はデジタル回路における出力回路への適用例であって、例えば図1に示すような表示パネルドライバの出力回路のように、出力にスイッチ回路が入る例では、この従来技術をそのまま適用することはできない。それは、スイッチを構成するトランジスタ回路とCMOSロジックの回路は異なるからである。スイッチは、NチャンネルMOSトランジスタ単体で構成される場合もあり、またはPチャンネルMOSトランジスタ単体で構成される場合もあり、更には、1対のNチャンネルMOSトランジスタとPチャンネルMOSトランジスタを備えるトランスマニアゲート回路の場合もある。このように回路が異なるので、その最適な対処方法は、従来回路とは異なる。すなわち従来回路の単なる適用はできないという問題がある。

**【課題を解決するための手段】**

10

**【0013】**

本発明の基本的なコンセプトは、表示パネルドライバの出力回路において、アンプと出力パッドとを接続する経路を複数設け、それぞれの経路に静電保護抵抗を挿入するということである。これにより見かけの出力抵抗を下げることができ、ひいては出力波形の劣化の程度を改善することができる。

**【0014】**

具体的には、本発明の一の観点において、表示パネルドライバが、第1及び第2アンプと、第1～第n偶数出力ノードと（nは、2以上の整数）、第1～第n奇数出力ノードと、表示パネルのデータ線にそれぞれに接続される第1及び第2出力パッドと、第1～第nスイッチブロックと、第1～第n偶数静電保護抵抗と、第1～第n奇数静電保護抵抗とを具備する。第1～第nスイッチブロックのうちの第iスイッチブロックは（iは1以上n以下の任意の整数）、第1及び第2アンプと第i偶数出力ノード及び第i奇数出力ノードとの間の接続関係を切り換えるように構成されている。第1～第n偶数静電保護抵抗は、それぞれ、第1～第n偶数出力ノードと第1出力パッドとの間に接続されており、第1～第n奇数静電保護抵抗は、それぞれ、第1～第n奇数出力ノードと第2出力パッドとの間に接続されている。

20

**【発明の効果】**

**【0015】**

本発明によれば、必要な静電保護抵抗値を保ちつつ、出力特性を改善することができる出力回路を備えた表示パネルドライバが提供される。

30

**【図面の簡単な説明】**

**【0016】**

【図1】従来のLCDドライバの出力回路の構成を示す回路図である。

【図2】出力電圧波形と静電保護抵抗の抵抗値との関係を示すグラフである。

【図3】従来のデジタル回路における出力回路の構成を示す回路図である。

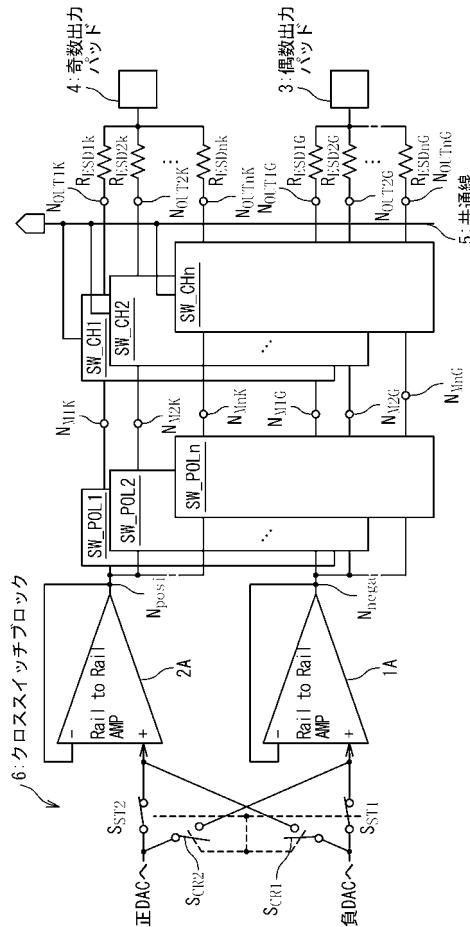

【図4】本発明の第1の実施形態におけるLCDドライバの出力回路の構成を示す回路図である。

【図5】本発明の出力回路と従来技術の出力回路の出力特性を比較するグラフである。

【図6A】本発明の第2の実施形態におけるLCDドライバの出力回路の構成を示す回路図である。

40

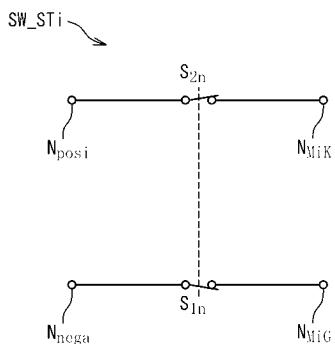

【図6B】第2の実施形態における極性切換スイッチブロックの構成を示す回路図である。

【図6C】第2の実施形態における極性切換スイッチブロックの構成を示す回路図である。

【図7A】本発明の第3の実施形態におけるLCDドライバの出力回路の構成を示す回路図である。

【図7B】第3の実施形態におけるストレートスイッチブロックの構成を示す回路図である。

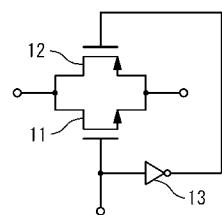

【図8】トランスマニアゲートの構成を示す回路図である。

**【発明を実施するための形態】**

50

## 【0017】

(第1の実施形態)

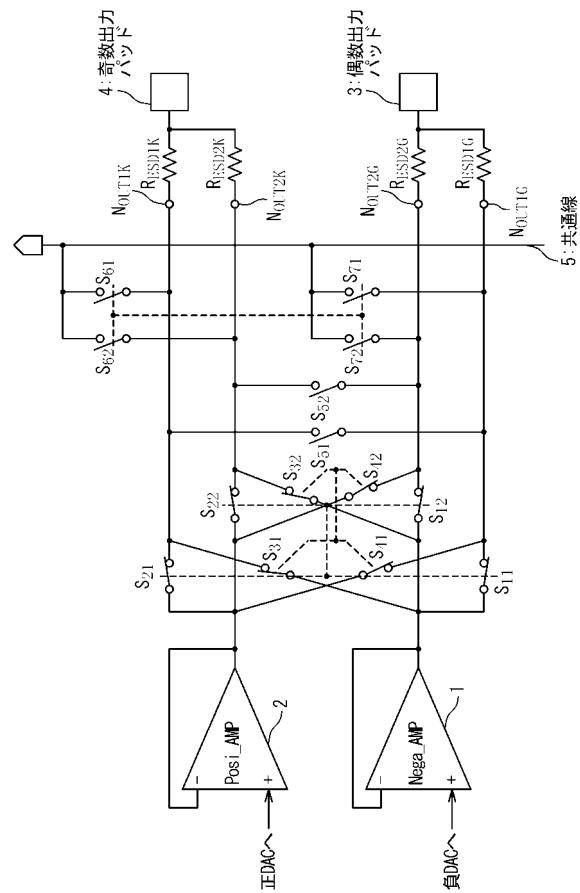

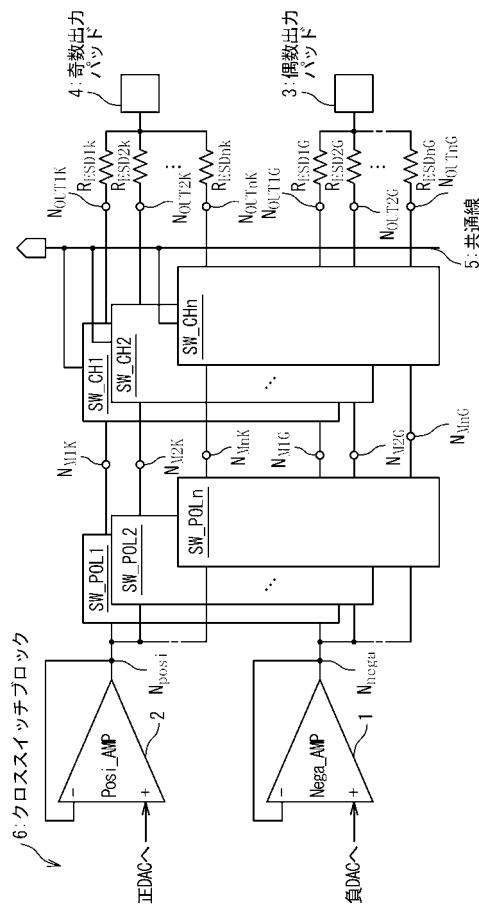

図4は、本発明の第1の実施形態のLCDドライバの出力回路の構成を示す回路図である。第1の実施形態の出力回路は、負側アンプ1と、正側アンプ2と、偶数出力パッド3と、奇数出力パッド4と、静電保護抵抗 $R_{ESD1G}$ 、 $R_{ESD2G}$ 、 $R_{ESD1K}$ 、 $R_{ESD2K}$ とを備えている。偶数出力パッド3と奇数出力パッド4とは、LCDパネルのデータ線に接続されるパットである。負側アンプ1は、“負極性”の駆動電圧を生成する演算増幅器であり、正側アンプ2は、“正極性”の駆動電圧を生成する演算増幅器である。ここで、本明細書において“正極性”とは、LCDパネルの対向電極に供給される共通電圧より高いことを意味し、逆に、“負極性”とは、当該共通電圧より低いことを意味することに留意されたい。負側アンプ1と正側アンプ2それぞれの正転入力端子は、それぞれ、各々負側D/Aコンバータ(Digital to Analog Converter)と正側D/Aコンバータに接続される。負側D/Aコンバータは、画像データに応じて“負極性”の階調電圧を負側アンプ1の正転入力端子に供給し、正側D/Aコンバータは、LCDドライバに供給された画像データに応じて“正極性”の階調電圧を正側アンプ2の正転入力端子に供給する。負側アンプ1と正側アンプ2のそれぞれは、ボルテッジフォロワ接続されており、供給された階調電圧と同一の駆動電圧を出力する。負側アンプ1によって生成された“負極性”の駆動電圧は、偶数出力パッド3と奇数出力パッド4の一方に供給され、正側アンプ2によって生成された“正極性”の駆動電圧は、偶数出力パッド3と奇数出力パッド4の他方に供給される。また、静電保護抵抗 $R_{ESD1G}$ は、出力ノード $N_{OUT1G}$ と偶数出力パッド3の間に接続され、静電保護抵抗 $R_{ESD2G}$ は、出力ノード $N_{OUT2G}$ と偶数出力パッド3の間に接続されている。また、静電保護抵抗 $R_{ESD1K}$ は、出力ノード $N_{OUT1K}$ と奇数出力パッド4の間に接続され、静電保護抵抗 $R_{ESD2K}$ は、出力ノード $N_{OUT2K}$ と奇数出力パッド4の間に接続されている。

## 【0018】

第1の実施形態の出力回路は、更に、14個のスイッチ：スイッチ $S_{1,1} \sim S_{7,1}$ 、 $S_{1,2} \sim S_{7,2}$ を備えている。スイッチ $S_{1,1} \sim S_{4,1}$ は、負側アンプ1及び正側アンプ2の出力と出力ノード $N_{OUT1G}$ 、 $N_{OUT1K}$ の間の接続関係を切り替えるためのスイッチ群である。スイッチ $S_{1,1}$ は、偶数出力ノード $N_{OUT1G}$ と負側アンプ1の出力の間に接続され、スイッチ $S_{2,1}$ は、奇数出力ノード $N_{OUT1K}$ と正側アンプ2の出力の間に接続される。スイッチ $S_{3,1}$ は、奇数出力ノード $N_{OUT1K}$ と負側アンプ1の出力の間に接続され、スイッチ $S_{4,1}$ は、偶数出力ノード $N_{OUT1G}$ と正側アンプ2の出力の間に接続される。同様に、スイッチ $S_{1,2} \sim S_{4,2}$ は、負側アンプ1及び正側アンプ2の出力と出力ノード $N_{OUT2G}$ 、 $N_{OUT2K}$ の間の接続関係を切り替えるためのスイッチ群である。スイッチ $S_{1,2}$ は、偶数出力ノード $N_{OUT2G}$ と負側アンプ1の出力の間に接続され、スイッチ $S_{2,2}$ は、奇数出力ノード $N_{OUT2K}$ と正側アンプ2の出力の間に接続される。スイッチ $S_{3,2}$ は、奇数出力ノード $N_{OUT2K}$ と負側アンプ1の出力の間に接続され、スイッチ $S_{4,2}$ は、偶数出力ノード $N_{OUT2G}$ と正側アンプ2の出力の間に接続される。スイッチ $S_{1,1} \sim S_{4,1}$ 、 $S_{1,2} \sim S_{4,2}$ により、偶数出力パッド3及び奇数出力パッド4から出力される駆動電圧の極性を反転させる動作が可能になる。

## 【0019】

スイッチ $S_{5,1}$ 、 $S_{5,2}$ 、 $S_{6,1}$ 、 $S_{7,1}$ 、 $S_{6,2}$ 、 $S_{7,2}$ は、電荷回収スイッチとして機能するスイッチ群である。スイッチ $S_{5,1}$ は、偶数出力ノード $N_{OUT1G}$ と奇数出力ノード $N_{OUT1K}$ の間に接続され、スイッチ $S_{5,2}$ は、偶数出力ノード $N_{OUT2G}$ と奇数出力ノード $N_{OUT2K}$ の間に接続されている。スイッチ $S_{6,1}$ は、奇数出力ノード $N_{OUT1K}$ と共に線5の間に接続され、スイッチ $S_{7,1}$ は、偶数出力ノード $N_{OUT1G}$ と共に線5の間に接続される。同様に、スイッチ $S_{6,2}$ は、奇数出力ノード $N_{OUT2K}$ と共に線5の間に接続され、スイッチ $S_{7,2}$ は、偶数出力ノード $N_{OUT2G}$ と共に線5の間に接続される。

## 【0020】

10

20

30

40

50

上記のスイッチのうち、スイッチ  $S_{1\ 1}$ 、 $S_{2\ 1}$ 、 $S_{1\ 2}$ 、 $S_{2\ 2}$  は連動して動作する。また、スイッチ  $S_{3\ 1}$ 、 $S_{4\ 1}$ 、 $S_{3\ 2}$ 、 $S_{4\ 2}$  は連動して動作する。また、スイッチ  $S_{5\ 1}$ 、 $S_{5\ 2}$ 、 $S_{6\ 1}$ 、 $S_{6\ 2}$ 、 $S_{7\ 1}$ 、 $S_{7\ 2}$  は連動して動作する。

#### 【0021】

図4を参照して本実施形態の出力回路の動作を説明する。基本的な動作は、図2に図示された従来回路と同じである。スイッチ  $S_{1\ 1}$ ～ $S_{4\ 1}$ 、 $S_{1\ 2}$ ～ $S_{4\ 2}$  は、極性反転機能を受け持つスイッチ群である。これらのスイッチは、負側アンプ1と正側アンプ2のうちの一方を偶数出力パッド3に接続し、他方を奇数出力パッド4に接続する。スイッチ  $S_{5\ 1}$ 、 $S_{6\ 1}$ 、 $S_{7\ 1}$ 、 $S_{5\ 2}$ 、 $S_{6\ 2}$ 、 $S_{7\ 2}$  は、電荷回収スイッチとして機能する。

#### 【0022】

図1と異なる点は、本実施形態では、負側アンプ1と出力パッド（偶数出力パッド3又は奇数出力パッド4）とを接続する経路が2つ設けられ、同様に、正側アンプ2と出力パッド（偶数出力パッド3又は奇数出力パッド4）とを接続する経路が2つ設けられることである。各経路には、基準を満たすような抵抗値の静電保護抵抗（ $R_{ESD1G}$ 、 $R_{ESD2G}$ 、 $R_{ESD1K}$ 、 $R_{ESD2K}$ ）が挿入されている。これにより、偶数出力パッド3又は奇数出力パッド4を流れる電流は、2つの経路に分流されることになる。静電保護抵抗  $R_{ESD1G}$ 、 $R_{ESD2G}$ 、 $R_{ESD1K}$ 、 $R_{ESD2K}$  の抵抗値が同一である場合には、静電保護抵抗  $R_{ESD1G}$ 、 $R_{ESD2G}$  を流れる電流は同一であり、静電保護抵抗  $R_{ESD1K}$ 、 $R_{ESD2K}$  を流れる電流が同一である。即ち、すなわちパッドから入出力される電流の半分ずつが前述した2つの経路から供給されることになる。これにより、静電保護抵抗  $R_{ESD1G}$ 、 $R_{ESD2G}$ 、 $R_{ESD1K}$ 、 $R_{ESD2K}$  に流れる電流は、必要な出力電流の半分となり、これにより、出力過渡応答波形の改善ができる。

#### 【0023】

その改善効果を示したのが、図5である。図5は、従来技術の図1の回路と本実施形態の図4の回路とについてシミュレーションし、シミュレーションによって得られた電圧波形を重ね合わせたグラフである。太線は、本実施形態の回路の出力電圧の波形を示しており、細線は従来技術の回路の出力電圧の波形を示している。スルーレートで決まる立ち上がりと立ち下がり波形の部分はほとんど変化ないが、いわゆる波形の肩のところは出力抵抗値（この場合は静電保護抵抗値）で波形形状が決まることは前述した通り（図2参照）である。この図5を参照すると、従来回路に比べ、出力の過渡特性が改善できていることがわかる。出力振幅の10% / 90%の値でみれば20%程度の改善効果ができることが確認できた。更に波形が真ん中に寄っている時間が電荷回収の波形であり、真ん中に寄るほど電荷回収の効率が良い。その観点から本願発明はこの電荷回収期間により真ん中に寄っているので、従来例に比べ電荷回収効率もアップしていることがわかる。

#### 【0024】

##### （第2の実施形態）

図6Aは、第2の実施形態の出力回路の構成を示すブロック図である。図6Aの回路構成は図4の回路構成を一般化したもので、第2の実施形態の出力回路では、負側アンプ1と出力パッド（偶数出力パッド3又は奇数出力パッド4）とを接続する経路がn個設けられ、同様に、正側アンプ2と出力パッド（偶数出力パッド3又は奇数出力パッド4）とを接続する経路がn個設けられる。図4の回路構成は、図6Aの回路構成においてnを2とした場合の例である。

#### 【0025】

詳細には、第2の実施形態の出力回路は、負側アンプ1と、正側アンプ2と、偶数出力パッド3と、奇数出力パッド4と、静電保護抵抗  $R_{ESD1G}$ ～ $R_{ESDnG}$ 、 $R_{ESD1K}$ ～ $R_{ESDnK}$  とを備えている。静電保護抵抗  $R_{ESD1G}$ ～ $R_{ESDnG}$  は、それぞれ、偶数出力ノード  $N_{OUT1G}$ ～ $N_{OUTnG}$  と偶数出力パッド3の間に接続され、静電保護抵抗  $R_{ESD1K}$ ～ $R_{ESDnK}$  は、それぞれ、奇数出力ノード  $N_{OUT1K}$ ～ $N_{OUTnK}$  と奇数出力パッド4の間に接続されている。

#### 【0026】

10

20

30

40

50

第2の実施形態の出力回路には、更に、極性切換スイッチブロック SW\_POL1 ~ SW\_POLn と、電荷回収スイッチブロック SW\_CH1 ~ SW\_CHn とが設けられている。極性切換スイッチブロック SW\_POL1 ~ SW\_POLn は、負側アンプ1及び正側アンプ2の出力と、出力ノード N\_OUT1G ~ N\_OUTnG、N\_OUT1K ~ N\_OUTnK との間の接続関係を切り換える機能を有している。一方、電荷回収スイッチブロック SW\_CH1 ~ SW\_CHn は、それぞれ、出力ノード N\_OUT1G ~ N\_OUTnG、N\_OUT1K ~ N\_OUTnK と共に線5との間の接続関係を切り換える機能を有している。加えて、各電荷回収スイッチブロック SW\_CHi は、出力ノード N\_OUTiG と出力ノード N\_OUTiK とを短絡する機能を有している。

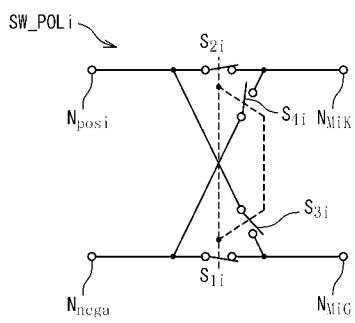

## 【0027】

10

各極性切換スイッチブロック SW\_POLi は、いわゆるクロススイッチ構成となっている。すなわち、図6Bに示されているように、各極性切換スイッチブロック SW\_POLi は、スイッチ S1i ~ S4i を備えている。スイッチ S1i は、負側アンプ1の出力 N\_neg\_a と偶数中間ノード N\_MiG の間に接続され、スイッチ S2i は、正側アンプ2の出力 N\_pos\_i と奇数中間ノード N\_MiK の間に接続されている。また、スイッチ S3i は、正側アンプ2の出力 N\_posi と偶数中間ノード N\_MiG の間に接続され、スイッチ S4i は、負側アンプ1の出力 N\_neg\_a と奇数中間ノード N\_MiK の間に接続されている。

## 【0028】

20

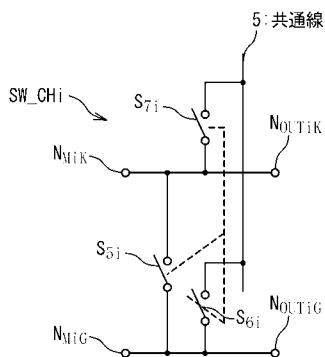

一方、各電荷回収スイッチブロック SW\_CHi は、図6Cに示されているように、スイッチ S5i ~ S7i を備えている。スイッチ S5i は、奇数出力ノード N\_OUTik と偶数出力ノード N\_OUTiG との間に接続されている。スイッチ S6i は、偶数出力ノード N\_OUTiG と共に線5の間に接続され、スイッチ S7i は、奇数出力ノード N\_OUTik と共に線5の間に接続されている。電荷回収スイッチブロック SW\_CHi の内部では、奇数中間ノード N\_MiK と奇数出力ノード N\_OUTik とが直接に接続され、偶数中間ノード N\_MiG と偶数出力ノード N\_OUTiG とが直接に接続されていることに留意されたい。

## 【0029】

スイッチ SW\_POL1 ~ SW\_POLn に含まれるスイッチは全て連動して動作する。また、スイッチ SW\_CH1 ~ SW\_CHn に含まれるスイッチは全て連動して動作する。

30

## 【0030】

図6Aの回路の動作は、基本的には図4の回路と同様である。ここでnの数を増やせば増やすほど、実効的な静電保護抵抗の値は小さくなる。すなわち図2において出力抵抗値が小さくなることから、出力波形は理想に近づく。

## 【0031】

## (第3の実施形態)

図7Aは、第3の実施形態における出力回路の構成を示すブロック図である。図7Aの回路では、図6Aの回路における負側アンプ1及び正側アンプ2が、Rail-to-Rail構成のアンプ1A、2Aに置き換えられている。これに伴い、アンプ1A及び2Aと正側D/Aコンバータ及び負側D/Aコンバータとの間にクロススイッチブロック6が挿入され、更に、極性切換スイッチブロック SW\_POL1 ~ SW\_POLn が、ストレートスイッチブロック SW\_ST1 ~ SW\_STn に置換される。クロススイッチブロック6は、スイッチ S\_ST1、S\_ST2、S\_CRL1、S\_CRL2 を備えている。スイッチ S\_ST1 は、負側D/Aコンバータの出力とアンプ1Aの正転入力端子の間に接続され、スイッチ S\_ST2 は、正側D/Aコンバータの出力とアンプ2Aの正転入力端子の間に接続される。また、スイッチ S\_CRL1 は、負側D/Aコンバータの出力とアンプ2Aの正転入力端子の間に接続され、スイッチ S\_CRL2 は、正側D/Aコンバータの出力とアンプ1Aの正転入力端子の間に接続される。

40

## 【0032】

50

本実施形態では、アンプ1A、2AがRail-to-Rail構成なので、アンプ1A、2Aの入出力電圧範囲は負電源電圧 $V_{SS}$ から正電源電圧 $V_{DD}$ までである。従って、アンプ1A、2Aには、正側D/Aコンバータから出力される正極性の階調電圧と、負側D/Aコンバータから出力される階調電圧のどちらでも入力することが可能である。また、DACとアンプの間にいわゆるクロススイッチを挿入して、同一のアンプで正極性、と負側を出力することが可能になる。従って、アンプ1A、2Aの出力には、クロススイッチを接続する必要はない。本実施形態では、図7Bに示されているように、ストレートスイッチブロックSW\_ST1～SW\_STnのそれぞれは、電荷回収時にアンプ1A、2Aを偶数出力パッド3、奇数出力パッド4から切り離すスイッチのみで構成されている。このような構成でも、偶数出力パッド3、奇数出力パッド4のそれぞれに、正極性の駆動電圧と負極性の駆動電圧を出力することが可能である。これ以外の動作は第2の実施形態と同じである。

### 【0033】

#### (スイッチの構成)

上述の第1～第3の実施形態の出力回路におけるスイッチとしては、様々なものが使用され得る。スイッチとして、NMOSトランジスタが使用されてもよく、PMOSトランジスタが使用されてもよい。また、図8に図示されているような、ドレインとソースが共通に接続された一対のNMOSトランジスタ11及びPMOSトランジスタ12で構成されたトランスファーゲートが使用されてもよい。この場合、NMOSトランジスタ11及びPMOSトランジスタ12のゲートにはインバータ13を用いて互いに相補の制御信号が供給される。これにより、NMOSトランジスタ11及びPMOSトランジスタ12は同時にオン状態になり、又は同時にオフ状態になる。

### 【0034】

スイッチとしてNチャンネルMOSトランジスタを使うか、PチャンネルMOSトランジスタを使うか、またはトランスファーゲートを使うかの判断基準は、スイッチに印加される電圧に応じて決定されることが望ましい。例えば、正電源電圧を $V_{DD}$ とすると、スイッチにかかる電圧が、ほぼ $V_{DD}/2$ より高い場合はPチャンネルMOSトランジスタを使用することが好ましく、逆に、スイッチにかかる電圧がほぼ $V_{DD}/2$ より低い場合はNチャンネルMOSトランジスタを使用することが好ましい。また、負電源電圧 $V_{SS}$ から正電源電圧 $V_{DD}$ まで全入力電圧範囲で動作させる必要がある場合はトランスファーゲートを使用することが好ましい。

### 【0035】

以上には、本発明の実施形態が様々に記載されているが、本発明は、上記の実施形態に限定して解釈してはならない。本発明は、当業者には自明的な様々な変更が可能であることに留意されたい。特に、本発明が、LCDドライバのみならず、他の表示パネルを駆動する表示ドライバにも適用可能であることは、当業者には自明的であろう。

### 【符号の説明】

#### 【0036】

1：負側アンプ

2：正側アンプ

1A、2A：アンプ

3：偶数出力パッド

4：奇数出力パッド

5：共通線

6：クロススイッチブロック

11：NMOSトランジスタ

12：PMOSトランジスタ

13：インバータ

101：負側アンプ

102：正側アンプ

10

20

30

40

50

- 103 : 偶数出力パッド

- 104 : 奇数出力パッド

- 105 : 共通線

- 106 : 内部回路

- 107 : 出力端子パッド

- 108 : インバータ

【図1】

【図2】

【図3】

【図4】

【図5】

【図6A】

【図 6 B】

【図 6 C】

【図 7 A】

【図 7 B】

【図 8】

---

フロントページの続き

(51)Int.Cl.

F I

G 0 9 G 3/20 6 2 1 B

G 0 2 F 1/133 5 0 5

G 0 2 F 1/133 5 5 0

H 0 1 L 27/04 H

G 0 9 G 3/36

(56)参考文献 特開2002-175052(JP,A)

特開2000-260948(JP,A)

特開2003-308050(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 0 9 G 3 / 0 0 - 3 / 3 8

G 0 2 F 1 / 1 3 3

H 0 1 L 2 1 / 8 2 2

H 0 1 L 2 7 / 0 4