(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4711404号

(P4711404)

(45) 発行日 平成23年6月29日(2011.6.29)

(24) 登録日 平成23年4月1日(2011.4.1)

(51) Int.Cl.

F 1

|             |               |                  |        |           |

|-------------|---------------|------------------|--------|-----------|

| <b>G02F</b> | <b>1/1343</b> | <b>(2006.01)</b> | GO 2 F | 1/1343    |

| <b>G02F</b> | <b>1/133</b>  | <b>(2006.01)</b> | GO 2 F | 1/133 550 |

| <b>G02F</b> | <b>1/1368</b> | <b>(2006.01)</b> | GO 2 F | 1/1368    |

| <b>G09F</b> | <b>9/30</b>   | <b>(2006.01)</b> | GO 9 F | 9/30 338  |

請求項の数 8 (全 21 頁)

|           |                              |

|-----------|------------------------------|

| (21) 出願番号 | 特願2005-234352 (P2005-234352) |

| (22) 出願日  | 平成17年8月12日 (2005.8.12)       |

| (65) 公開番号 | 特開2007-47664 (P2007-47664A)  |

| (43) 公開日  | 平成19年2月22日 (2007.2.22)       |

| 審査請求日     | 平成20年5月28日 (2008.5.28)       |

|           |                                                      |

|-----------|------------------------------------------------------|

| (73) 特許権者 | 502356528<br>株式会社 日立ディスプレイズ<br>千葉県茂原市早野3300番地        |

| (74) 代理人  | 100083552<br>弁理士 秋田 収喜                               |

| (73) 特許権者 | 506087819<br>パナソニック液晶ディスプレイ株式会社<br>兵庫県姫路市飾磨区妻鹿日田町1-6 |

| (74) 代理人  | 100083552<br>弁理士 秋田 収喜                               |

| (74) 代理人  | 110000154<br>特許業務法人はるか国際特許事務所                        |

| (72) 発明者  | 桶 隆太郎<br>千葉県茂原市早野3300番地 株式会社<br>日立ディスプレイズ内           |

最終頁に続く

(54) 【発明の名称】表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

TFT素子および画素電極が画素単位で配置された表示パネルを有する表示装置であって

、

前記表示パネルは、

有効表示領域内を通る複数のゲート電極線および複数のドレイン電極線を有し、

前記有効表示領域の外側であり、かつ、前記ゲート電極線の延在方向の一方の端部側に位置するドレイン電極線に沿った領域には、前記ドレイン電極線の延在方向の一方の端部側から数えて偶数本目のゲート電極線に接続されたTFT素子を有する第1のダミー画素が配置され、

前記有効表示領域の外側であり、かつ、前記ゲート電極線の延在方向の他方の端部側に位置するドレイン電極線に沿った領域には、前記ドレイン電極線の延在方向の前記一方の端部側から数えて奇数本目のゲート電極線に接続されたTFT素子を有する第2のダミー画素が配置されており、

各ドレイン電極線は、当該ドレイン電極線に接続された各画素のTFT素子が、延在方向に沿って交互に配置されており、

前記ゲート電極線の延在方向の端部に位置する2本の前記ドレイン電極線は、それぞれ前記有効表示領域内に配置された複数のTFT素子と、複数の前記第1または第2のダミー画素のTFT素子とに接続されており、かつ、前記各ドレイン電極線に接続された前記有効表示領域内のTFT素子と前記第1または第2のダミー画素のTFT素子とは、前記各ドレイ

10

20

ン電極線の延在方向に沿って交互に配置されており、

複数の前記第1のダミー画素の間、または複数の前記第2のダミー画素の間には、第3のダミー画素が配置されていることを特徴とする表示装置。

**【請求項2】**

前記第1のダミー画素が配置された端部が、前記ゲート電極線の入力端側であることを特徴とする請求項1に記載の表示装置。

**【請求項3】**

前記第1および第2のダミー画素は、前記有効表示領域内の画素と同じ構成であることを特徴とする請求項1または請求項2に記載の表示装置。

**【請求項4】**

前記第1および第2のダミー画素は、TFT素子のみを有することを特徴とする請求項1または請求項2に記載の表示装置。

**【請求項5】**

前記第1または第2のダミー画素の外側に、ダミーのドレイン電極線を有することを特徴とする請求項1に記載の表示装置。

**【請求項6】**

前記第3のダミー画素は、前記有効表示領域内の画素の画素電極と同じ導電層に、前記有効表示領域内を通る前記ドレイン電極線とは接続していないダミーの電極層を有することを特徴とする請求項1に記載の表示装置。

**【請求項7】**

前記第1または第2のダミー画素の外側にダミーのドレイン電極線を有し、

前記第3のダミー画素は、前記ダミーのドレイン電極線および前記ダミーの電極層と接続されたTFT素子を有することを特徴とする請求項6に記載の表示装置。

**【請求項8】**

前記ダミー画素が配置された領域は、遮光されていることを特徴とする請求項1に記載の表示装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、表示装置に関し、特に、TFT素子が画素単位で配置された表示パネルを有する表示装置に適用して有効な技術に関するものである。

**【背景技術】**

**【0002】**

従来、テレビなどの表示装置には、液晶表示パネルを用いた液晶表示装置がある。

**【0003】**

前記液晶表示パネルは、一対の基板の間に液晶材料を封入した表示パネルである。このとき、一方の基板には、たとえば、TFT素子や画素電極が画素単位で配置されている。また、他方の基板には、たとえば、前記画素電極と対向する位置にカラーフィルタが配置されている。

**【0004】**

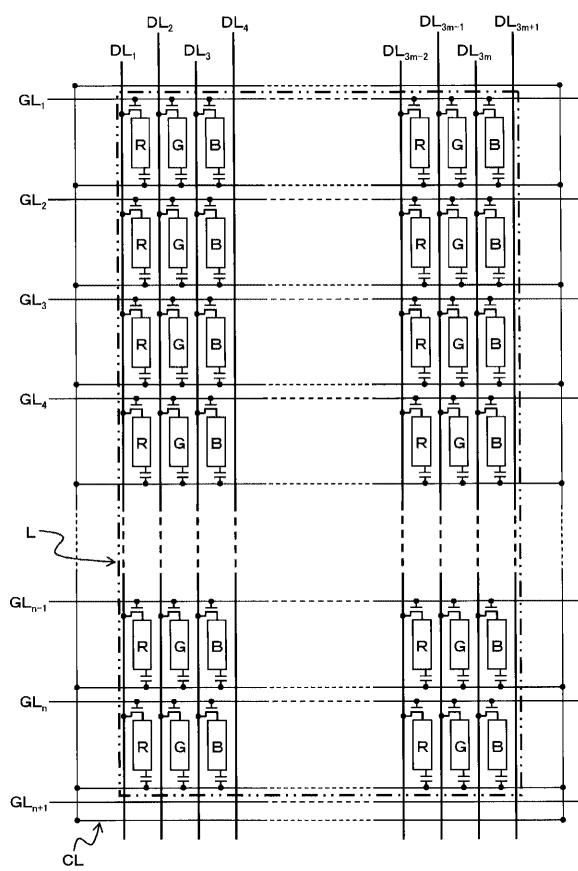

またこのとき、前記TFT素子などが配置された基板上の回路構成は、たとえば、図31に示すようになっており、有効表示領域Lのドット数が横mドット×縦nドットの表示装置の場合、3m+1本のドレイン電極線DLとn+1本のゲート電極線GLが配置されている。なお、図31には、1つのドットがR画素、G画素、B画素の3つの画素からなる場合を示している。また、図31において紙面右端のドレイン電極線DL<sub>3m+1</sub>と紙面下端のゲート電極線GL<sub>n+1</sub>はダミーである。

**【0005】**

また、この液晶表示パネルでは、たとえば、図31に示したように、ドレイン電極線DLの延在方向に沿って並んでいる各画素のTFT素子は、すべて同じドレイン電極線に接続されている。たとえば、ドレイン電極線DL<sub>1</sub>に沿って並んでいるR画素のTFT素子は、す

10

20

30

40

50

べてドレイン電極線 D L<sub>1</sub>に接続されている。

**【0006】**

一方、TFTを隣接するドレイン電極線に交互に配置した例が、特許文献1に記載されている。

**【特許文献1】特開平10-90712号公報**

**【発明の開示】**

**【発明が解決しようとする課題】**

**【0007】**

前記テレビなどの液晶表示装置では、画面のちらつきを抑えたり、動画の表示性能を向上させたりするための高リフレッシュレート化が進んでいる。

10

**【0008】**

しかしながら、表示パネル上の回路構成が、図31に示したような構成の場合、高リフレッシュレート化が進むにつれて、TFT素子の書き込み不足が生じ、画質が劣化するという問題があった。

**【0009】**

本発明の目的は、たとえば、液晶表示装置の高周波動作による画質の劣化を低減することが可能な技術を提供することにある。

**【0010】**

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面によって明らかになるであろう。

20

**【課題を解決するための手段】**

**【0011】**

本願において開示される発明の概略を説明すれば、以下の通りである。

**【0012】**

(1) TFT素子および画素電極が画素単位で配置された表示パネルを有する表示装置であって、前記表示パネルは、有効表示領域内を通る複数のゲート電極線および複数のドレイン電極線を有し、前記有効表示領域の外側であり、かつ、前記ゲート電極線の延在方向の一方の端部側に位置するドレイン電極線に沿った領域には、前記ドレイン電極線の延在方向の一方の端部側から数えて偶数本目のゲート電極線に接続されたTFT素子を有する第1のダミー画素が配置され、前記有効表示領域の外側であり、かつ、前記ゲート電極線の延在方向の他方の端部側に位置するドレイン電極線に沿った領域には、前記ドレイン電極線の延在方向の前記一方の端部側から数えて奇数本目のゲート電極線に接続されたTFT素子を有する第2のダミー画素が配置されており、各ドレイン電極線は、当該ドレイン電極線に接続された各画素のTFT素子が、延在方向に沿って交互に配置されており、前記ゲート電極線の延在方向の端部に位置する2本の前記ドレイン電極線は、それぞれ、前記有効表示領域内に配置された複数のTFT素子と、複数の前記第1または第2のダミー画素のTFT素子とに接続されており、かつ、前記各ドレイン電極線に接続された前記有効表示領域内のTFT素子と前記第1または第2のダミー画素のTFT素子とは、前記各ドレイン電極線の延在方向に沿って交互に配置されており、複数の前記第1のダミー画素の間、または複数の前記第2のダミー画素の間には、第3のダミー画素が配置されている表示装置である。

30

**【0013】**

(2) 前記(1)において、前記第1のダミー画素が配置された端部が、前記ゲート電極線の入力端側の表示装置である。

**【0014】**

(3) 前記(1)または(2)において、前記第1および第2のダミー画素は、有効表示領域内の画素と同じ構成の表示装置である。

**【0015】**

(4) 前記(1)または(2)において、前記第1および第2のダミー画素は、TFT素子のみを有する表示装置である。

**【0016】**

40

50

(5) 前記(1)において、前記第1または第2のダミー画素の外側に、ダミーのドレン電極線を有する表示装置である。

【0018】

(6) 前記(1)において、前記第3のダミー画素は、前記有効表示領域内の画素の画素電極と同じ導電層に、前記有効表示領域内を通る前記ドレン電極線とは接続していないダミーの電極層を有する表示装置である。

【0019】

(7) 前記(6)において、前記第1または第2のダミー画素の外側にダミーのドレン電極線を有し、前記第3のダミー画素は、前記ダミーのドレン電極線および前記ダミーの電極層と接続されたTFT素子を有する表示装置である。 10

【0021】

(8) 前記(1)において、前記ダミー画素が配置された領域は、遮光されている表示装置である。

【発明の効果】

【0026】

本発明の表示装置は、隣接するドレン電極線に、1フレームの間に渡り、コモン電位に対しそれぞれ反対の極性の信号を与えるように駆動することができる。その際、TFT素子がドレン電極線に交互に接続していることにより、1フレームの間映像信号線の極性を同一としながら、マトリクス状の画素の画素電極に書き込まれる信号を隣接する画素で互いに極性が反転するドット反転とができる。これにより、従来のフレーム反転の欠点であったフリッカを解消することができる。またフレーム反転の特徴である、極性の切り替わる間隔が長いことにより、ドレン信号線への充放電回数がドット反転に比べ激減し、高リフレッシュレート、たとえば、100Hz以上、具体的には120Hzでのフレームレートでの駆動が可能となる。 20

【0027】

一方、このような配置では、表示に用いられるドレン電極線の最外のラインに格段の配慮を払わないと、最外のラインの容量が他のラインと大きく異なり、最外の表示画素で他のラインと輝度の差が生じてしまうことが判明した。

【0028】

本発明では、このようなドレン電極線の電位としてはフレーム反転でありながら表示としてドット反転を実現できる表示装置にて、ゲート線と直交する方向の表示ラインのうちの、最外周の表示ラインの輝度ムラの発生を回避することができるという特有かつ顕著な効果を実現することができる。 30

【0029】

このためには、たとえば、前記手段(1)のように、有効表示領域の外側に第1および第2のダミー画素を配置する。そして、各ドレン電極線には、たとえば、ドレン電極線の向かって右側に配置された画素のTFT素子と、向かって左側に配置された画素のTFT素子を交互に接続する。またこのとき、第1および第2のダミー画素は、たとえば、前記手段(2)のように、ゲート電極線の入力端側に、偶数本目のゲート電極線と接続されたTFT素子を有する第1のダミー画素を配置する。またこのとき、第1および第2のダミー画素は、前記手段(3)のように有効表示領域内の画素と同じ構成であってもよいし、前記手段(4)のようにTFT素子のみを設けてもよい。 40

【0030】

また、第1および第2のダミー画素を配置した場合、各ダミー画素のTFT素子が接続されたドレン電極線は、各ダミー画素に書き込み信号を印加するタイミングに、たとえば、黒色表示用の信号を印加する。また、第1のダミー画素に関しては、1つ前の表示領域内の画素に印加する信号と同じ信号を印加し、第2のダミー画素に関しては、1つ後の表示領域内の画素に印加する信号と同じ信号を印加してもよい。

【0031】

またこのとき、たとえば、前記手段(5)のように、ダミーのドレン電極線を追加し 50

てもよい。このとき、前記ダミーのドレン電極線には、たとえば、コモン信号を印加する。またこのとき、ダミーのドレン電極線は、第1のダミー画素の外側のみ、または第2のダミー画素の外側のみに追加してもよいし、第1のダミー画素の外側および第2のダミー画素の外側の両方に追加してもよい。

#### 【0032】

また、前記第1および第2のダミー画素を配置した場合、各ダミー画素は1画素おきに配置される。そのため、ダミー画素の間に段差が生じ、たとえば、配向膜を設けるときのラビング工程において、前記段差によるラビング強度のばらつきが発生する可能性がある。そこで、本発明の表示装置では、前記手段(1)のように、第3のダミー画素を設け、段差を低減する。このとき、第3のダミー画素は、たとえば、前記手段(6)のようにダミーの電極層のみを設けてもよいし、前記手段(7)のようにダミーの電極層およびTFT素子を設けてもよい。

10

#### 【0033】

また、前記手段(1)における前記第1、第2、および第3のダミー画素は、有効表示領域の外側に配置される画素である。そのため、本発明の表示装置では、前記手段(8)のように、前記ダミー画素が配置された領域を遮光することが好ましい。

#### 【発明を実施するための最良の形態】

#### 【0035】

以下、本発明について、図面を参照して実施の形態(実施例)とともに詳細に説明する。

20

なお、実施例を説明するための全図において、同一機能を有するものは、同一符号を付け、その繰り返しの説明は省略する。

#### 【0036】

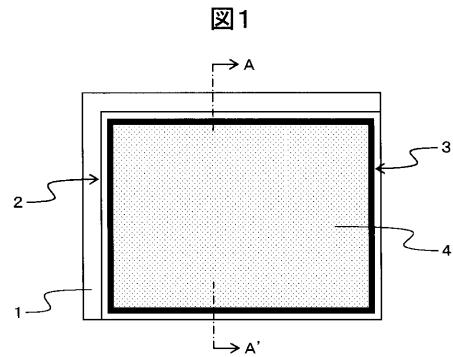

図1および図2は、本発明が適用される表示装置が有する表示パネルの概略構成の一例を示す模式図であり、図1は液晶表示パネルの構成例を示す正面図、図2は図1のA-A'線断面図である。

#### 【0037】

本発明が適用される表示装置は、たとえば、TFT素子が画素単位で配置された液晶表示パネルを有する液晶表示装置である。前記液晶表示パネルは、たとえば、図1および図2に示すように、一対の基板1,2が環状のシール材3で接着されており、各基板1,2およびシール材3で囲まれた空間内に液晶材料4が封入された表示パネルである。このとき、一方の基板1には、前記TFT素子や画素電極が配置されており、他方の基板2には、前記画素電極と対向する位置にカラーフィルタが配置されている。

30

#### 【0038】

また、図1および図2に示したような液晶表示パネルを有する液晶表示装置は、前記液晶表示パネルを挟むように配置された一対の偏光板や、偏光板で挟まれた液晶表示パネルの後方に配置されたバックライトユニットなどを有する。なお、これらの基本的な構成については、従来の液晶表示装置と同じ構成でよいので、詳細な説明は省略する。

#### 【0039】

以下、図1および図2に示したような液晶表示パネルを有する表示装置における、前記TFT素子や画素電極が配置された基板1(以下、TFT基板という)の回路構成について説明する。

40

#### 【実施例】

#### 【0040】

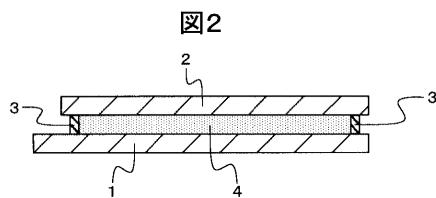

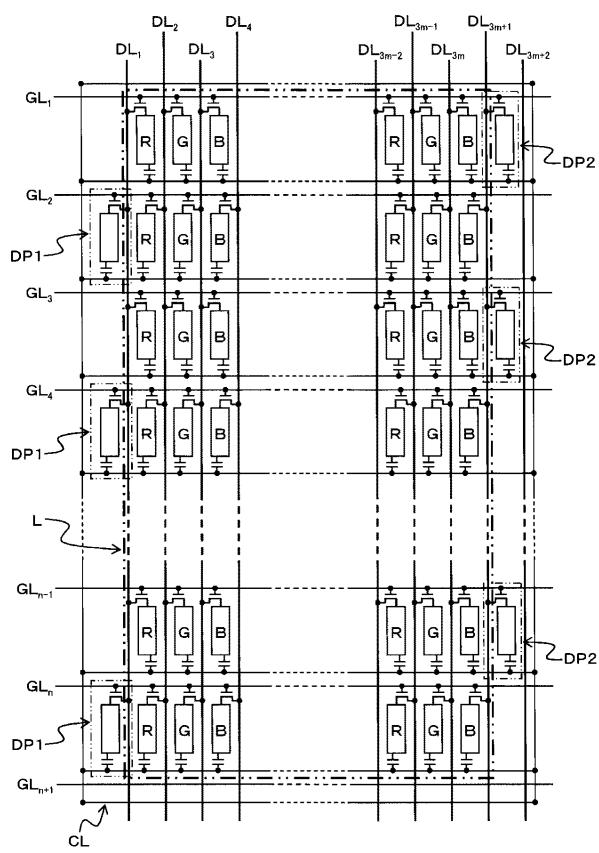

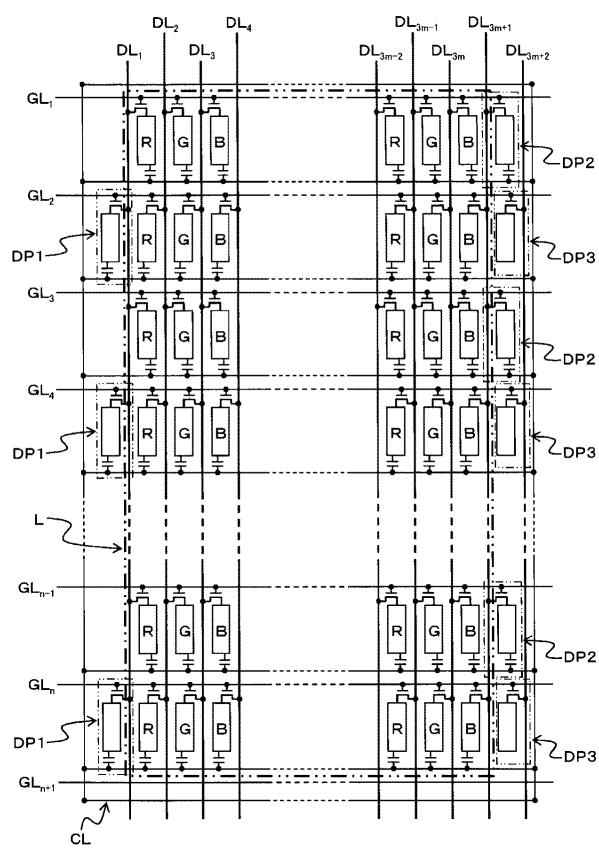

図3は、本発明による一実施例のTFT基板の回路構成を示す模式図である。

#### 【0041】

本実施例のTFT基板1は、たとえば、図3に示すように、水平方向に延在し、上下方向に並んで配置されたn+1本のゲート電極線G\_Lと、上下方向に延在し、水平方向に並んで配置された3m+1本のドレン電極線D\_Lと、水平方向に延在し、上下方向に並んで配置された共通信号線C\_Lとを有する。なお、以下の説明は共通信号線C\_Lを持つ例を挙

50

げて行うが、持たない例でもそのまま適用できる。

**【0042】**

また、各ゲート電極線 G L と各ドレイン電極線 D L の交点には、ゲート電極線 G L およびドレイン電極線と接続されたTFT素子が配置されている。このとき、TFT素子のソース電極は、画素電極 P X と接続されている。また、画素電極 P X と、共通信号線 C L に接続されたコモン電極（図示しない）との間に容量素子が形成されている。共通信号線 C L に接続されたコモン電極が無い例としては、TFT基板 1 に対向する基板 2 にコモン電極を形成し、そのコモン電極と画素電極 P X の間に容量素子が形成される、いわゆる縦電界方式の構成が一例として上げられる。

**【0043】**

なお、図 3 に示した例は、カラー液晶表示パネルに用いるTFT基板であり、水平方向に並んだ 3 つの画素、すなわち R と記された画素電極 P X を有する R 画素、G と記された画素電極 P X を有する G 画素、B と記された画素電極 P X を有する B 画素で有効表示領域 L 上の 1 ドットが構成されている。

**【0044】**

有効表示領域 L では、TFT素子がドレイン電極線 D L に交互に接続している。すなわち、奇数番のゲート電極線 G L により制御される画素のTFT素子は、当該画素を構成する左側のドレイン電極線 D L に接続し、偶数番のゲート電極線 G L により制御される画素のTFT素子は、当該画素を構成する右側のドレイン電極線 D L に接続している。

**【0045】**

また、本実施例のTFT基板 1 では、有効表示領域 L の端部のうち、ゲート電極線 G L の延在方向の端部の外側に、ダミー画素が配置されている。このとき、ドレイン電極線 D L<sub>1</sub> が配置された側の端部の外側は、偶数本目のゲート電極線 G L と接続されたTFT素子を有する第 1 のダミー画素 D P 1 が配置されている。また、ドレイン電極線 D L<sub>3m+1</sub> が配置された側の端部の外側は、奇数本目のゲート電極線 G L と接続されたTFT素子を有する第 2 のダミー画素 D P 2 が配置されている。このとき、前記第 1 および第 2 のダミー画素 D P 1, D P 2 は、有効表示領域 L 内の各画素と同じ構成とする。

**【0046】**

また、各ドレイン電極線 D L に右側から接続するTFT素子と、当該ドレイン電極線 D L に左側から接続するTFT素子とが、当該ドレイン電極線 D L の延在方向に沿って交互に配置されている。

**【0047】**

そして、左側よりドレイン電極線 D L の番号を配置した場合、有効表示領域 L に最隣接する左側のラインには、偶数番のゲート信号線 G L により制御されるダミー画素をTFTの接続順が有効表示領域 L 内と同じになるように配置する。これにより有効表示領域の左最外側のドレイン信号線 D L<sub>1</sub> に接続されるTFT素子の数が、有効表示領域 L 内の他のドレイン電極線と一致するため、D L<sub>1</sub> の負荷と他のドレイン電極線の負荷が一致し、D L<sub>1</sub> に接続した表示画素に他のラインに接続した画素に対し輝度変動が生じることを回避することができる。

**【0048】**

同様に、有効表示領域 L に最隣接する右側のラインには、奇数番のゲート信号線により制御されるダミー画素をTFT素子の接続順が有効表示領域 L 内と同じになるように配置する。これにより有効表示領域 L の右最外側のドレイン信号線 D L<sub>3m+1</sub> に接続されるTFT素子の数が、有効表示領域内の他のドレイン信号線と一致するため、D L<sub>3m+1</sub> の負荷と他のドレイン電極線の負荷が一致し、D L<sub>3m+1</sub> に接続した表示画素に他のラインに接続した画素に対し輝度変動が生じることを回避することができる。

**【0049】**

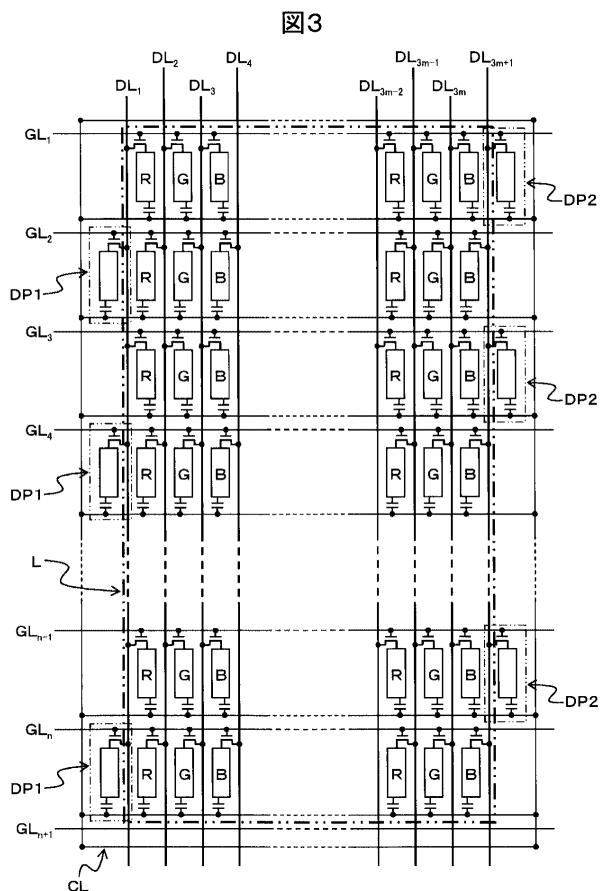

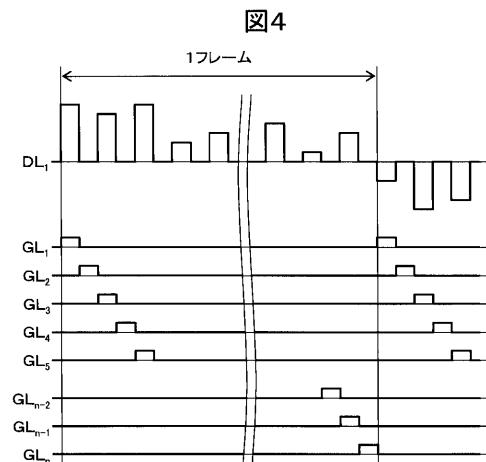

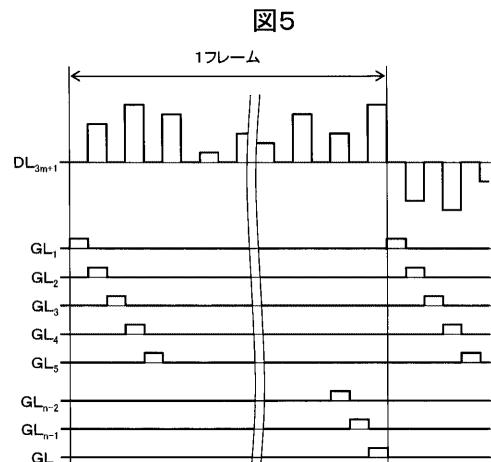

図 4 は、本実施例の表示パネルのドレイン電極線 D L<sub>1</sub> に印加する信号のタイムチャートの一例を示す図である。また、図 5 は、本実施例の表示パネルのドレイン電極線 D L<sub>3m+1</sub> に印加する信号のタイムチャートの一例を示す図である。

10

20

30

40

50

## 【0050】

TFT基板1に、図3に示したような構成の回路を設けた場合、第1のダミー画素D P 1が配置された端部側のドレン電極線D L<sub>1</sub>には、当該ドレン電極線D L<sub>1</sub>の一方側(右側)から有効表示領域L内のR画素のTFT素子が接続されており、かつ当該ドレン電極線D L<sub>1</sub>の他方側(左側)から第1のダミー画素D P 1のTFT素子が接続されている。また、当該R画素のTFT素子と当該第1のダミー画素D P 1のTFT素子は、ドレン電極線D L<sub>1</sub>の延在方向に沿って交互に配置されている。このとき、ドレン電極線D L<sub>1</sub>に、紙面上方側から書き込み信号を印加するとすれば、印加する信号は、たとえば、図4に示すように、奇数本目のゲート電極線G L<sub>1</sub>, G L<sub>3</sub>, G L<sub>5</sub>にゲート信号が印加されるタイミングでR画素に書き込む信号が印加され、偶数本目のゲート電極線G L<sub>2</sub>, G L<sub>4</sub>にゲート信号が印加されるタイミングでダミー画素D P 1を黒色表示させる信号が印加されるようとする。

## 【0051】

一方、第2のダミー画素D P 2が配置された端部側のドレン電極線D L<sub>3m+1</sub>は、第2のダミー画素D P 2のTFT素子と、有効表示領域L内のB画素のTFT素子が延在方向に沿って交互に接続されている。このとき、ドレン電極線D L<sub>3m+1</sub>に、紙面上方側から書き込み信号を印加するとすれば、印加する信号は、たとえば、図5に示すように、奇数本目のゲート電極線G L<sub>1</sub>, G L<sub>3</sub>, G L<sub>5</sub>にゲート信号が印加されるタイミングでダミー画素D P 2を黒色表示させる信号が印加され、偶数本目のゲート電極線G L<sub>2</sub>, G L<sub>4</sub>にゲート信号が印加されるタイミングでB画素に書き込む信号が印加されるようとする。

## 【0052】

また、たとえば、ドレン電極線D L<sub>2</sub>に印加する信号は、奇数本目のゲート電極線G L<sub>1</sub>, G L<sub>3</sub>, G L<sub>5</sub>にゲート信号が印加されるタイミングでG画素に書き込む信号が印加され、偶数本目のゲート電極線G L<sub>2</sub>, G L<sub>4</sub>にゲート信号が印加されるタイミングでR画素に書き込む信号が印加されるようとする。

## 【0053】

有効表示領域Lの外となるダミー画素は、通常、遮光層にて遮光される。このため、ダミー画素に加える電位は特に限定されるものではない。しかし黒データを書き込むことにより、確実に黒状態とできるため、電位を常に安定化できる点で望ましい。

## 【0054】

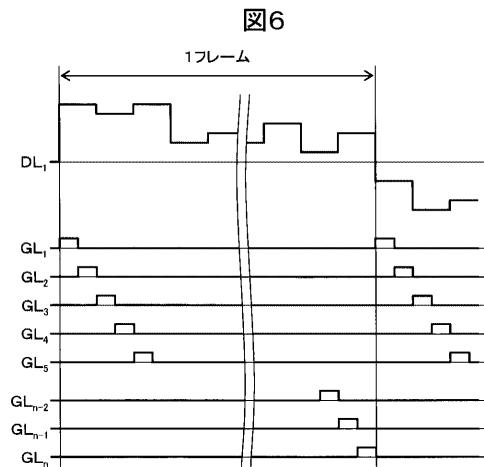

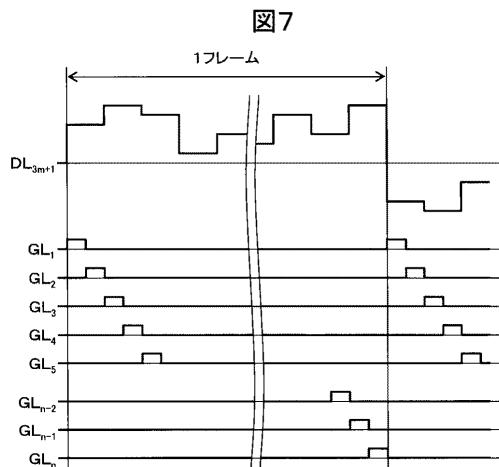

図6は、本実施例の表示パネルのドレン電極線D L<sub>1</sub>に印加する信号のタイムチャートの他の例を示す図である。また、図7は、本実施例の表示パネルのドレン電極線D L<sub>3m+1</sub>に印加する信号のタイムチャートの他の例を示す図である。

## 【0055】

本実施例において、ドレン電極線D L<sub>1</sub>に信号を印加するときには、図4に示したように、第1のダミー画素D P 1に黒色表示をさせるだけでなく、種々の方法が考えられる。つまり、たとえば、図5に示すように、1つ前のR画素に書き込む信号と同じ信号を印加してもよい。同様に、ドレン電極線D L<sub>3m+1</sub>に信号を印加するときには、たとえば、図6に示すように、1つ後のB画素に書き込む信号と同じ信号を印加してもよい。

## 【0056】

また図6や図7は、有効表示領域の他のドレン電極線に加えられる一般的信号の例として説明に用いることもできる。特徴的なことは1フレーム期間中極性が一定であることである。その上で、ドレン電極線延在方向に隣接する任意の2つの画素間で、画素中のTFT素子が接続するドレン電極線を異ならせる、すなわち一方の画素のTFT素子を右側のドレン電極線に接続し、他方の画素のTFT素子を左側のドレン電極線に接続することにより、表示としてはドット反転が実現する。このように信号自体の極性反転の回数が、1フレーム毎に1回となるため、ライン毎に反転する従来のドット反転に比べ信号の極性反転の回数を数百分の1、たとえばXGAでは768分の1に激減することができる。ドレン電極線の信号が極性反転すると、ドレン電極線の充放電に伴いドレン電極線の電位が安定化するまで時間を要するため、この時間分、実効的な書き込み時間が減少してしまう。

10

20

30

40

50

このため従来のドット反転では100Hz以上の高周波数での書き込みは困難であった。これに対し本願では、フレーム中に極性反転が無くなるため充放電時間がそのまま書き込みに寄与できるため、100Hz以上の高周波数、たとえば120Hzのような、入力信号60Hzに対し倍速となる駆動が実現できるようになる。そしてその際、表示画像としてはドット反転が維持されるため、フリッカのような弊害も生じないものとなっている。

#### 【0057】

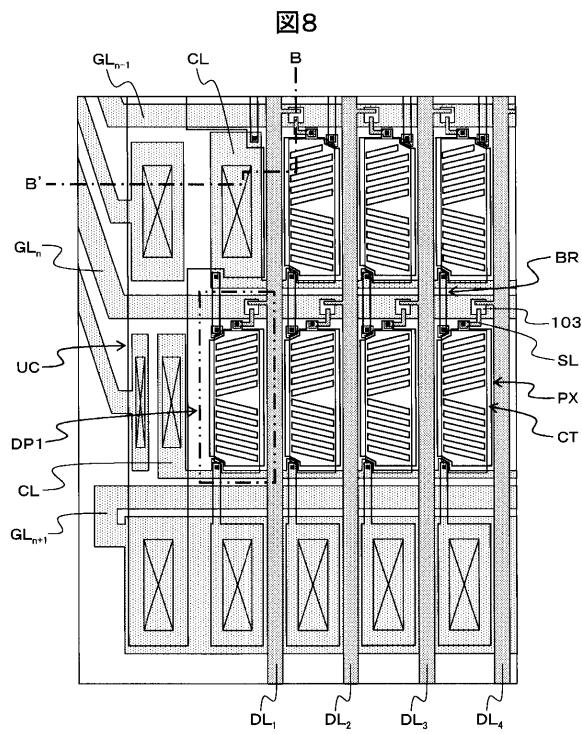

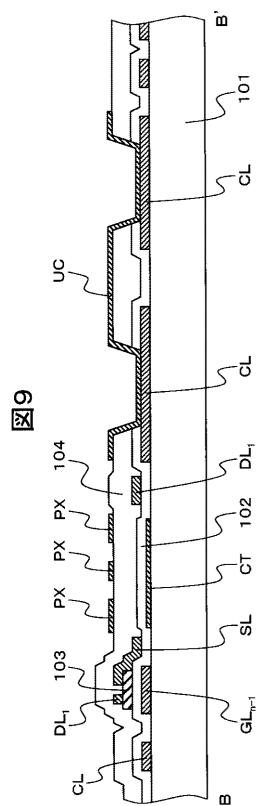

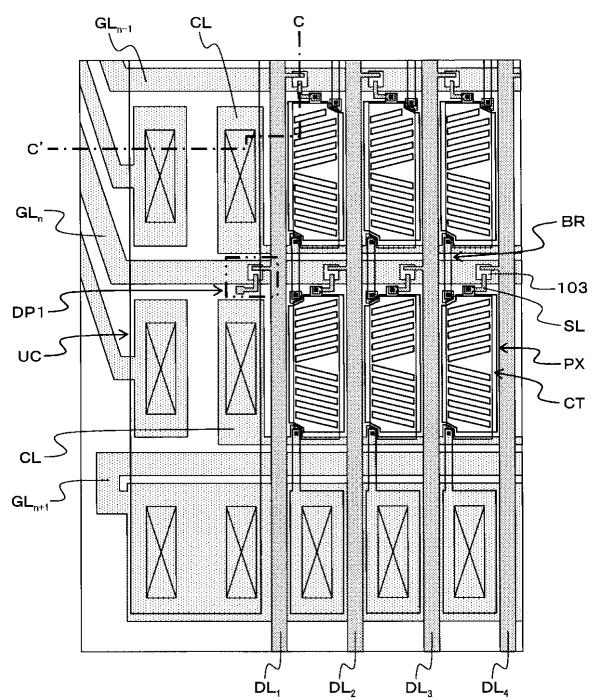

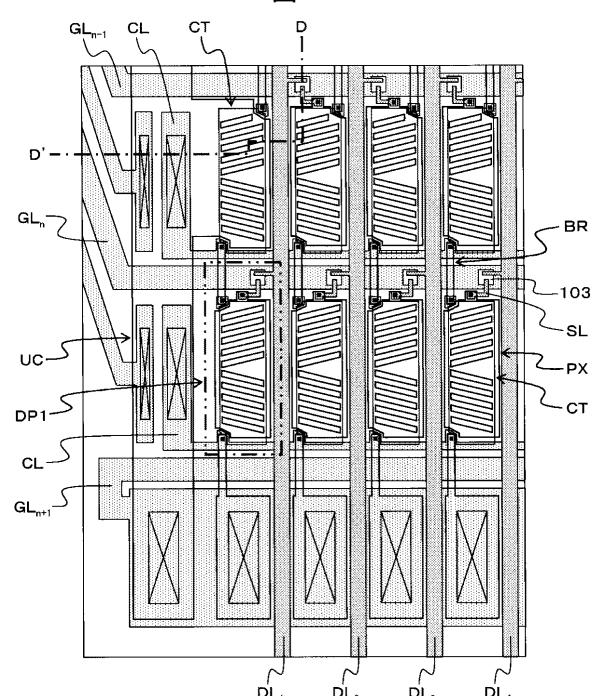

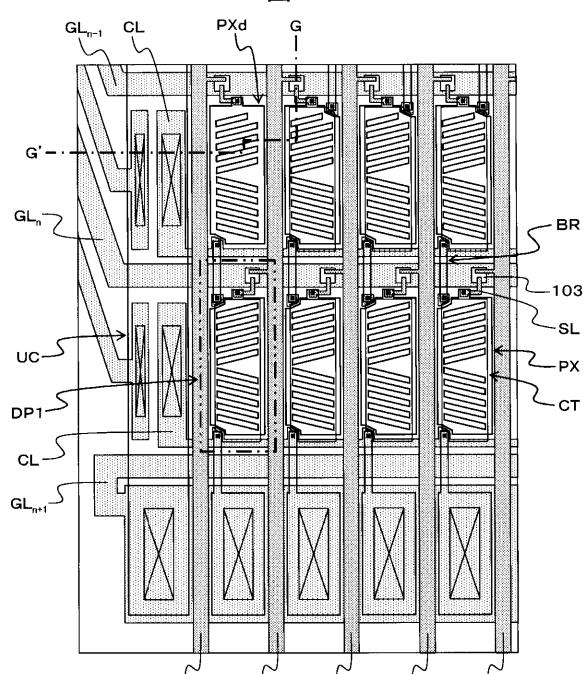

図8および図9は、本実施例の回路構成を適用したTFT基板の構成例を示す模式図であり、図8は有効表示領域の端部の拡大平面図、図9は図8のB-B'線断面図である。なお、図8では、ゲート電極線の本数nが偶数の例となっている。

#### 【0058】

本実施例の回路構成、すなわち図3に示したような回路構成のTFT基板1は、たとえば、図8および図9に示したような構成になる。なお、図8において2点鎖線で囲んだ領域が、左側のダミー画素D P 1である。図8中の四角の中に×印が記されている部分はコンタクトホールを示している。

#### 【0059】

このとき、TFT基板1は、たとえば、ガラス基板101上にゲート電極線G Lおよび共通信号線C L、ならびに前記共通信号線C Lと接続されたコモン電極C Tが設けられている。また、ゲート電極線G Lの上層には第1層間絶縁膜102を介在させて半導体層103およびドレイン電極線D L、ならびにソース電極S Lが設けられている。このとき、各ドレイン電極線D Lは、図8に示したように、画素の右側に配置された半導体層103と、画素の左側に配置された半導体層103に交互に接続するように分岐している。

#### 【0060】

また、ドレイン電極線D L<sub>1</sub>の左側の領域では、ゲート電極線G L<sub>n-1</sub>とG L<sub>n</sub>の間にはTFT素子が無く、コモン電位の共通信号線C Lの平面状電極が形成されている。これにより黒表示となり、該領域の電位安定化が実現する。また、ゲート電極線G L<sub>n</sub>とG L<sub>n+1</sub>の間には、ドレイン電極線D L<sub>1</sub>に接続したTFT素子より信号が供給されるダミー画素電極が形成されている。この画素は、たとえば、図4や図5のように黒データを加えると黒表示となる。

#### 【0061】

また、前記ドレイン電極線D Lなどの上層には、第2層間絶縁膜104を介在させて、表示領域には画素電極P Xや上下で隣り合う画素のコモン電極C Tを接続するブリッジ配線B Rが配置されている。またダミー領域にはコモン電位の電極U C、ならびに上下で隣り合う画素のコモン電極C Tを接続するブリッジ配線B Rなどが設けられている。このとき、画素電極P Xは、スルーホールによって前記ソース電極S Lと接続されている。また、画素電極P Xには、たとえば、スリットが設けられている。また、コモン電位の電極U Cは、スルーホールによって前記共通信号線C Lと接続されている。これにより共通信号線のバスラインの役割を果たしている。また、前記ブリッジ配線B Rは、スルーホールによって前記各画素のコモン電極C Tと接続されている。

#### 【0062】

なお、図8および図9は、TFT基板1の構成の一例を示した図であり、TFT素子、画素電極P X、コモン電極C T等の構成は、適宜変更可能であることはもちろんである。

#### 【0063】

以上説明したように、本実施例の液晶表示パネルによれば、高リフレッシュレート化による画質の劣化を低減できる。

#### 【0064】

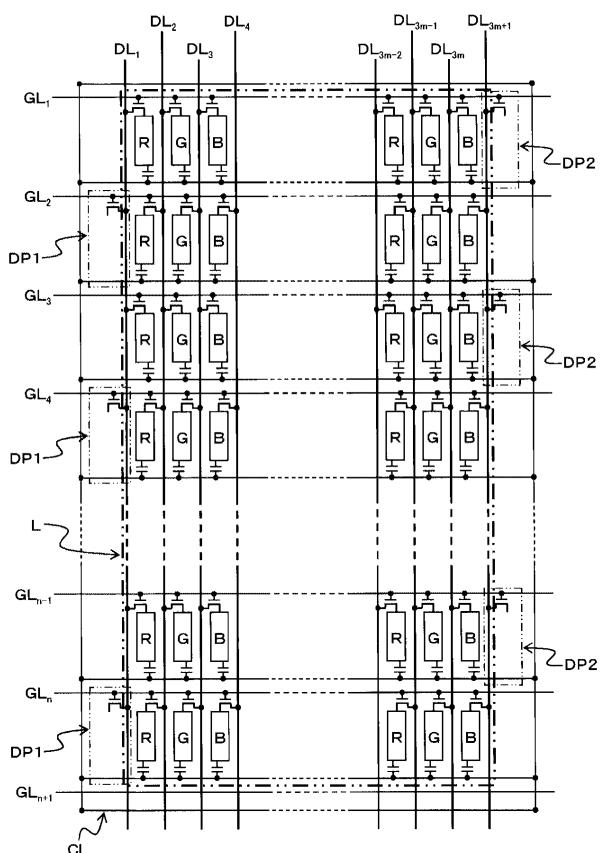

図10は、前記実施例の第1の変形例を説明するための模式図であり、TFT基板の回路構成を示す図である。

#### 【0065】

前記実施例では、図3に示したように、ドレイン電極線D Lが3m+1本であったが、これに限らず、たとえば、図10に示すように、第2のダミー画素D P 2の外側に、さら

10

20

30

40

50

にダミーのドレイン電極線  $D_L_{3m+2}$  を設けてもよい。

#### 【0066】

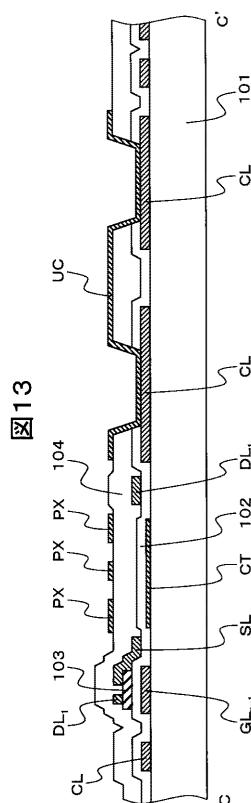

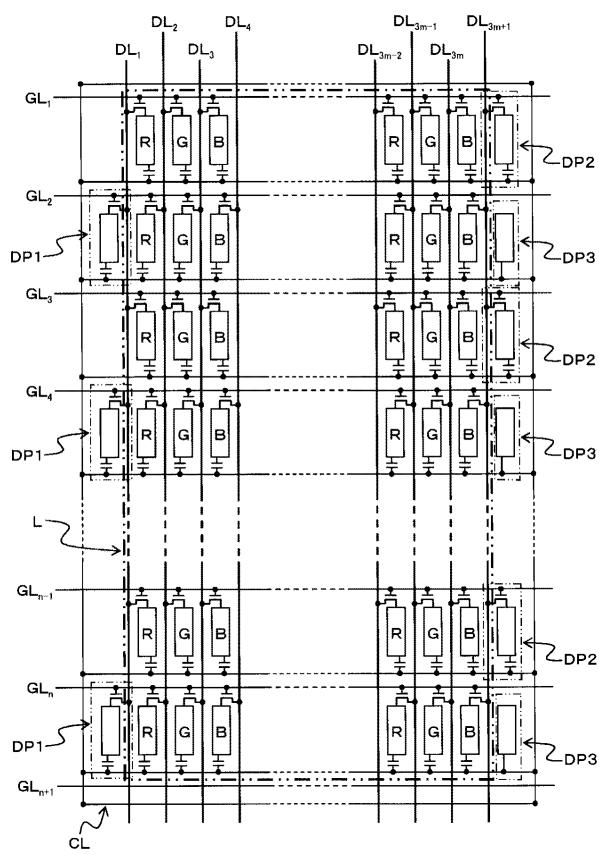

図11乃至図13は、前記実施例の第2の変形例を説明するための模式図であり、図11はTFT基板の回路構成を示す図、図12は図11の回路構成を適用したTFT基板の構成例を示す拡大平面図、図13は図12のC-C'線断面図である。

#### 【0067】

前記実施例では、図3に示したように、第1および第2のダミー画素DP1, DP2として、有効表示領域L内の画素と同じ構成のダミー画素を配置したが、これに限らず、たとえば、図11に示すように、TFT素子のみを配置してもよい。これは、ドレイン電極線の主な負荷容量が、TFT素子による容量であるためである。なお、図11に示した回路構成は、第1および第2のダミー画素DP1, DP2をTFT素子のみにした点以外は、図3に示した回路構成と同じである。10

#### 【0068】

図11に示したような回路構成を適用したTFT基板1は、たとえば、図12および図13に示したような構成になる。なお、図12において2点鎖線で囲んだ領域が第1のダミー画素DP1のTFT素子である。また、図12および図13に示したTFT基板1の構成は、図8において2点鎖線で囲んだ第1のダミー画素DP1をTFT素子のみにしただけであり、その他の構成は図8および図9に示した構成と同じである。また、図12および図13も、TFT基板1の構成の一例を示した図であり、TFT素子、画素電極PX、コモン電極CT等の構成は、適宜変更可能であることはもちろんである。20

#### 【0069】

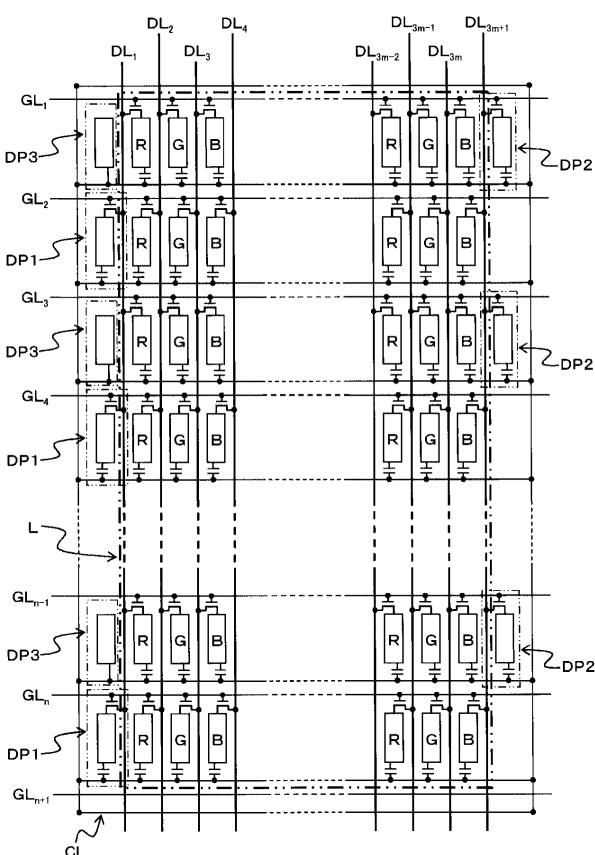

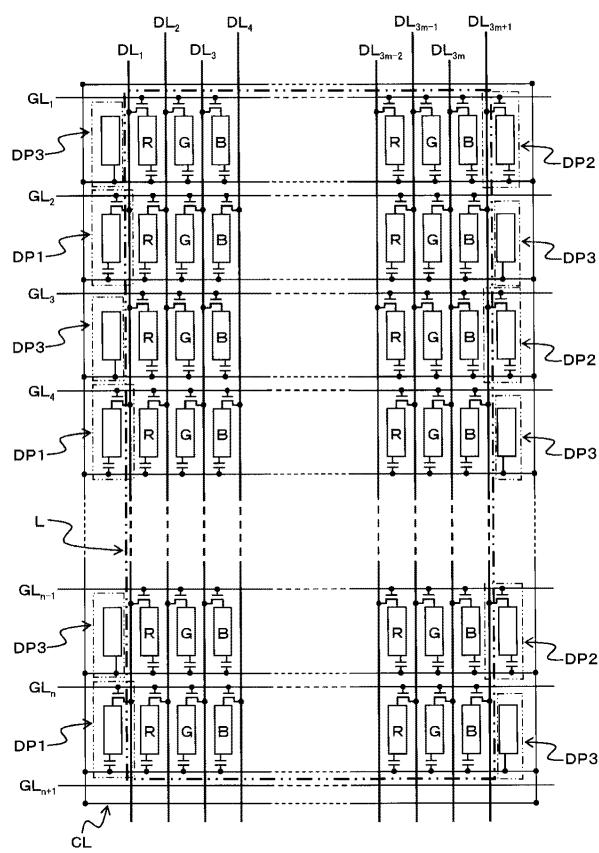

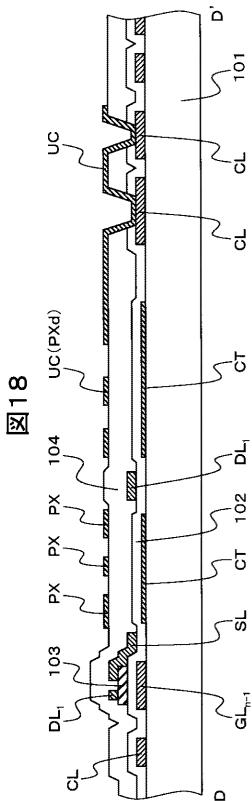

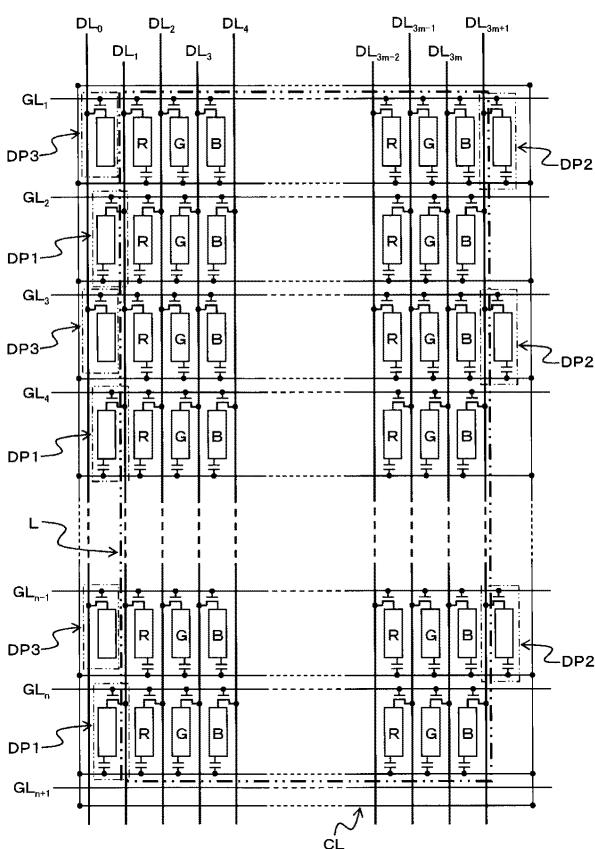

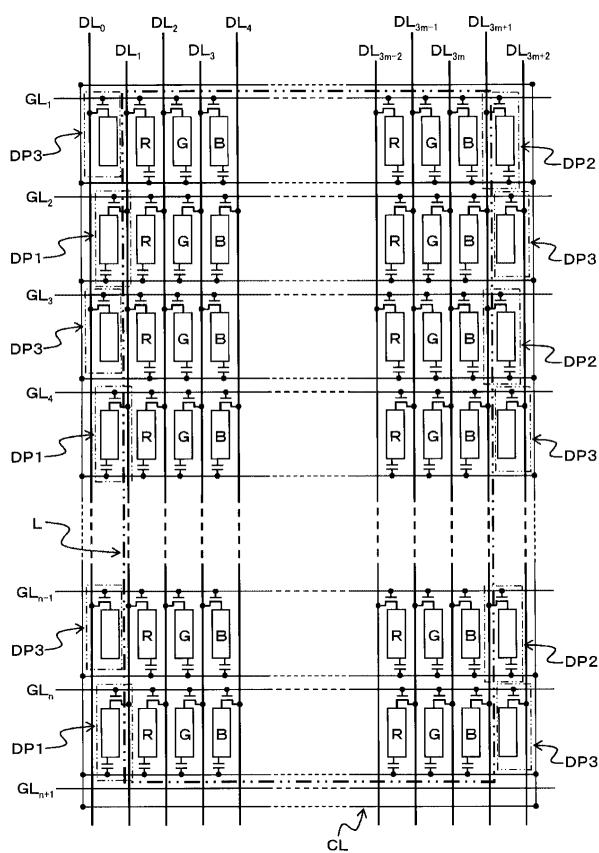

図14乃至図18は、前記実施例の第3の変形例を説明するための模式図であり、図14乃至図16はそれぞれTFT基板の回路構成を示す図、図17は図15の回路構成を適用したTFT基板の構成例を示す拡大平面図、図18は図17のD-D'線断面図である。

#### 【0070】

これまでの説明では、たとえば、図3に示したように、偶数番目あるいは奇数番目にダミー画素DP1, DP2を配置している。しかしながら、本発明の表示装置では、たとえば、図14に示すように、第2のダミー画素DP2の間に第3のダミー画素DP3を配置してもよい。このとき、第3のダミー画素DP3は、第2のダミー画素DP2と異なり、たとえば、共通信号線CLと接続されたダミー電極のみを設ける。またこのとき、第3のダミー画素DP3は、たとえば、図15に示すように、第1のダミー画素DP1の間に配置してもよいし、図16に示すように、第1のダミー画素DP1の間と第2のダミー画素DP2の間の両方に配置してもよい。30

#### 【0071】

このような構成、たとえば、図15に示したような回路構成にする場合の一例を図17および図18に示す。第3のダミー画素DP3には、たとえば、図17および図18に示すように、コモン電位の電極UCと一体的として、有効表示領域内の画素の画素電極PXと同じ層にダミーの画素電極を設けることができる。これにより、有効表示領域の左側にある第1のダミー画素DP1と第3のダミー画素DP3が交互に並んでいる列の最上層には、画素電極とコモン電極とが交互に配置される。40

#### 【0072】

このような構成にすると、たとえば、1つおきに配置されている第1のダミー画素DP1と、その間の第3のダミー画素DP3の間で、段差構造の差を小さくすることができる。そのため、たとえば、TFT基板1上に配向膜を設けるときのラビング工程において、前記段差によるラビング強度のばらつきの発生を回避することができる。

#### 【0073】

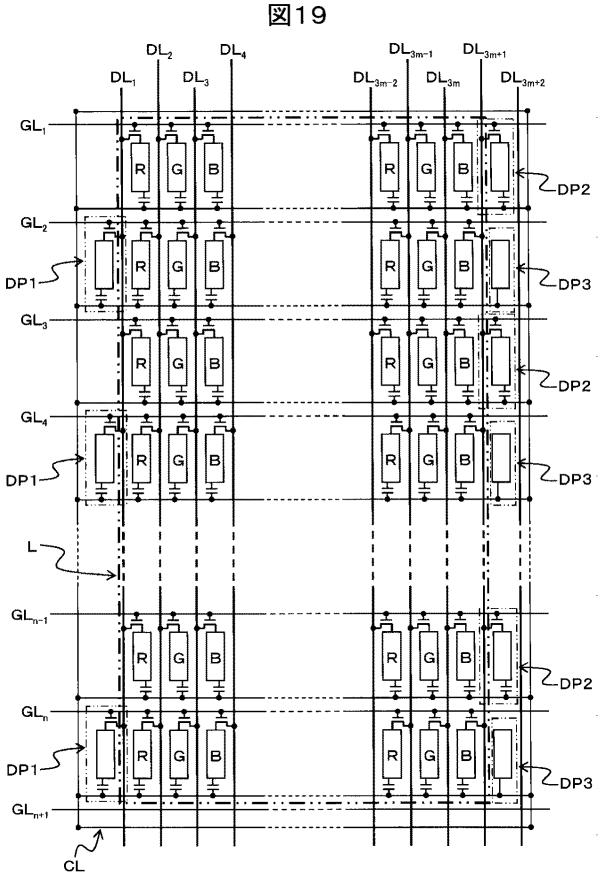

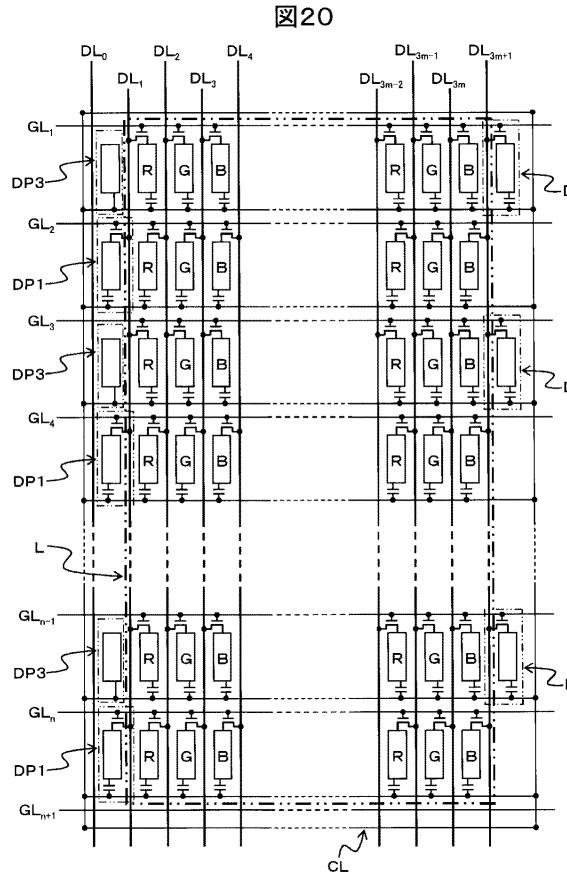

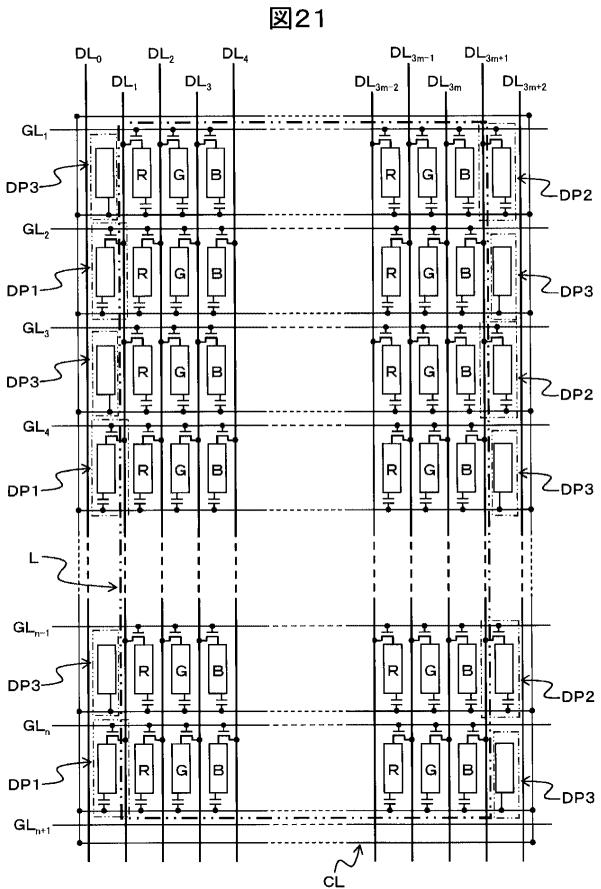

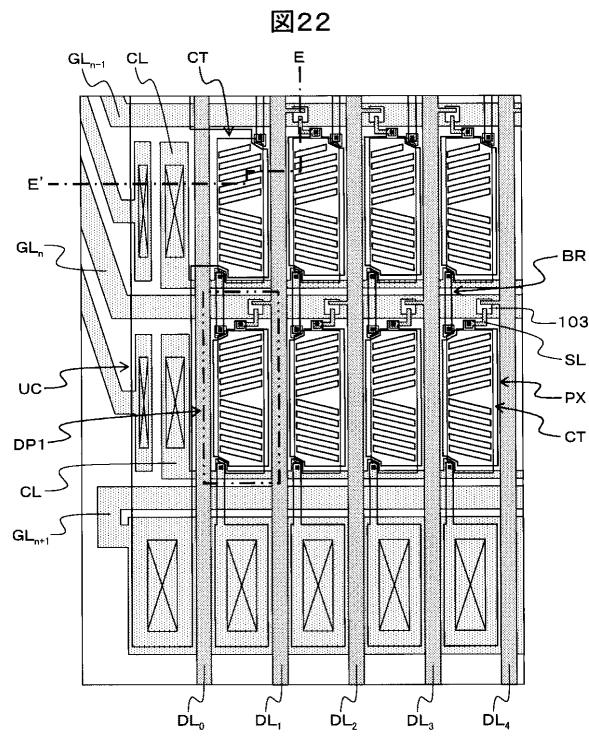

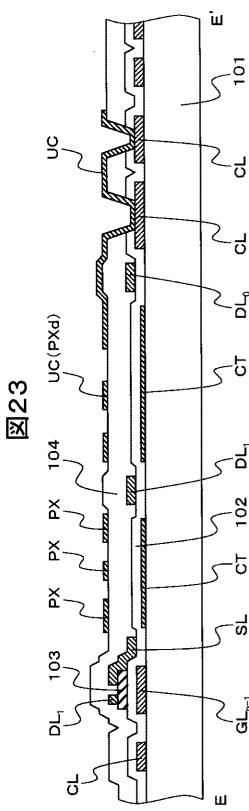

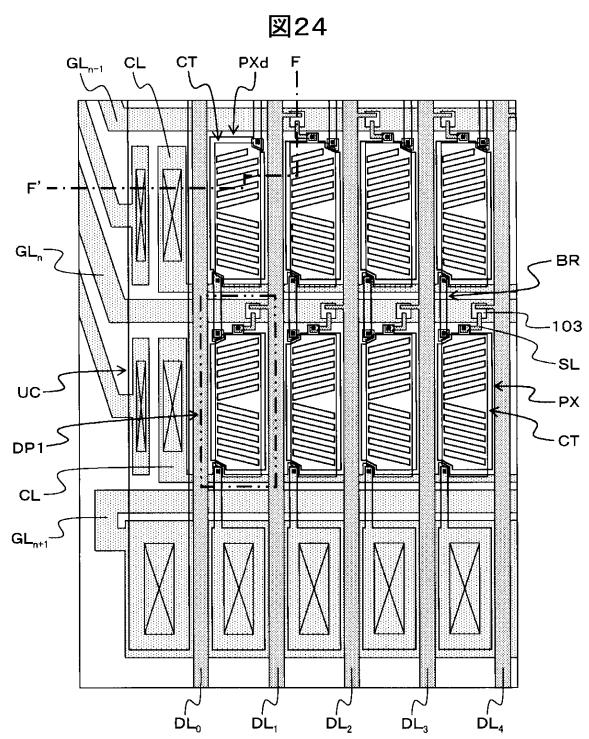

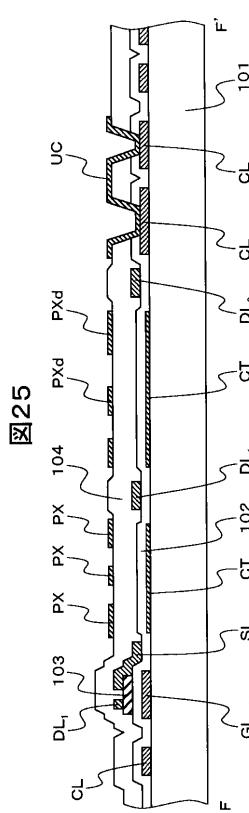

図19乃至図25は、前記実施例の第4の変形例を説明するための模式図であり、図19乃至図21はそれぞれTFT基板の回路構成を示す図、図22は図20の回路構成を適用したTFT基板の構成例を示す拡大平面図、図23は図22のE-E'線断面図、図24は図20の回路構成を適用したTFT基板の他の構成例を示す拡大平面図、図25は図24の50

F - F' 線断面図である。

**【0074】**

図14乃至図18は、図3に示した回路構成を基本構成とし、第1のダミー画素D P 1の間または第2のダミー画素D P 2の間、あるいはその両方に第3のダミー画素D P 3を配置した回路構成を示している。しかしながら、第3のダミー画素D P 3を配置する場合、たとえば、図19に示すように、第2のダミー画素D P 2の間のみに第3のダミー画素D P 3を配置し、さらにその外側にダミーのドレイン電極線D L<sub>3m+2</sub>を配置してもよい。また、たとえば、図20に示すように、第1のダミー画素D P 1の間のみに第3のダミー画素D P 3を配置し、さらにその外側にダミーのドレイン電極線D L<sub>0</sub>を配置してもよい。またさらに、これらを組み合わせて、たとえば、図21に示すように、第1のダミー画素D P 1の間と第2のダミー画素D P 2の間の両方に配置し、その外側にそれぞれドレイン電極線D L<sub>0</sub>, D L<sub>3m+2</sub>を配置してもよい。10

**【0075】**

このような構成、たとえば、図20に示したような回路構成にする場合の一例を図22および図23に示す。第3のダミー画素D P 3には、たとえば、図22および図23に示すように、コモン電位の電極U Cと一体的であり、有効領域内の画素の画素電極P Xと同じ層にダミーの画素電極P X dを設ける。このような構成にすると、たとえば、1つおきに配置されている第1のダミー画素と、その間の第3のダミー画素の間の段差構造の差を小さくすることができる。そのため、たとえば、TFT基板1上に配向膜を設けるときのラビング工程において、前記段差によるラビング強度のばらつきの発生を回避することができる。20

**【0076】**

また、図20に示したような回路構成にする場合、第3のダミー画素D P 3に設けるダミーの画素電極P X dは、たとえば、図24に示すように、ブリッジ配線B Rと一体化し、第1のダミー画素D P 1のコモン電極C Tと接続することでコモン電位にしてもよい。

**【0077】**

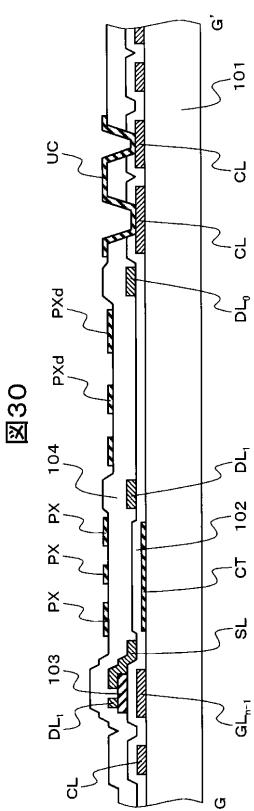

図26乃至図30は、前記実施例の第5の変形例を説明するための模式図であり、図26乃至図28はそれぞれTFT基板の回路構成を示す図、図29は図27の回路構成を適用したTFT基板の構成例を示す拡大平面図、図30は図29のG - G' 線断面図である。

**【0078】**

前記第3および第4の変形例では、第3のダミー画素D P 3として、コモン電位の画素電極P X dを設ける例を挙げた。しかしながら、第3のダミー画素D P 3には、これに限らず、たとえば、図26に示すように、第2のダミー画素D P 2の間にTFT素子および画素電極のみを配置してもよい。このとき、第2のダミー画素D P 2の外側には、ダミーのドレイン電極線D L<sub>3m+2</sub>を配置しておき、第3のダミー画素D P 3のTFT素子を接続しておく。また、たとえば、図27に示すように、第1のダミー画素D P 1の間のみに第3のダミー画素D P 3を配置し、さらにその外側にダミーのドレイン電極線D L<sub>0</sub>を配置してもよい。またさらに、これらを組み合わせて、たとえば、図28に示すように、第1のダミー画素D P 1の間と第2のダミー画素D P 2の間の両方に配置し、その外側にそれぞれドレイン電極線D L<sub>0</sub>, D L<sub>3m+2</sub>を配置してもよい。30

**【0079】**

このような構成、たとえば、図27に示したような回路構成にする場合の一例を図29および図30に示す。第3のダミー画素D P 3には、たとえば、図29および図30に示すように、有効領域内の画素の画素電極P Xと同じ層にダミーの画素電極P X dを設ける。またこのとき、ダミーの画素電極P X dと重なるコモン電極C Tは設けないようにする。このような構成にすると、たとえば、1つおきに配置されている第1のダミー画素D P 1と、その間の第3のダミー画素D P 3の間の段差構造の差を小さくすることができる。そのため、たとえば、TFT基板1上に配向膜を設けるときのラビング工程において、前記段差によるラビング強度のばらつきの発生を回避することができる。40

**【0080】**

10

20

30

40

50

以上、本発明を、前記実施例に基づき具体的に説明したが、本発明は、前記実施例に限定されるものではなく、その要旨を逸脱しない範囲において、種々変更可能であることはもちろんである。

**【0081】**

たとえば、前記実施例およびその変形例では、図1および図2に示したような液晶表示パネルのTFT基板1を例に挙げている。しかしながら、本発明は、前記液晶表示パネルに限らず、TFT素子が画素単位で配置された種々の表示パネルに適用可能であることはもちろんである。

**【図面の簡単な説明】**

**【0082】**

10

【図1】本発明が適用される表示装置が有する表示パネルの概略構成の一例を示す模式図であり、液晶表示パネルの構成例を示す正面図である。

**【図2】**図1のA-A'線断面図である。

**【図3】**本発明による一実施例のTFT基板の回路構成を示す模式図である。

【図4】本実施例の表示パネルのドレイン電極線DL<sub>1</sub>に印加する信号のタイムチャートの一例を示す図である。

【図5】本実施例の表示パネルのドレイン電極線DL<sub>3m+1</sub>に印加する信号のタイムチャートの一例を示す図である。

【図6】本実施例の表示パネルのドレイン電極線DL<sub>1</sub>に印加する信号のタイムチャートの他の例を示す図である。

20

【図7】本実施例の表示パネルのドレイン電極線DL<sub>3m+1</sub>に印加する信号のタイムチャートの他の例を示す図である。

【図8】本実施例の回路構成を適用したTFT基板の構成例を示す模式図であり、有効表示領域の端部の拡大平面図である。

**【図9】**図8のB-B'線断面図である。

【図10】前記実施例の第1の変形例を説明するための模式図であり、TFT基板の回路構成を示す図である。

【図11】前記実施例の第2の変形例を説明するための模式図であり、TFT基板の回路構成を示す図である。

**【図12】**図11の回路構成を適用したTFT基板の構成例を示す拡大平面図である。

30

**【図13】**図12のC-C'線断面図である。

【図14】前記実施例の第3の変形例を説明するための模式図であり、TFT基板の回路構成を示す図である。

【図15】前記実施例の第3の変形例を説明するための模式図であり、TFT基板の回路構成の他の例を示す図である。

【図16】前記実施例の第3の変形例を説明するための模式図であり、TFT基板の回路構成の他の例を示す図である。

**【図17】**図15の回路構成を適用したTFT基板の構成例を示す拡大平面図である。

**【図18】**図17のC-C'線断面図である。

【図19】前記実施例の第4の変形例を説明するための模式図であり、TFT基板の回路構成を示す図である。

40

【図20】前記実施例の第4の変形例を説明するための模式図であり、TFT基板の回路構成の他の例を示す図である。

【図21】前記実施例の第4の変形例を説明するための模式図であり、TFT基板の回路構成の他の例を示す図である。

**【図22】**図20の回路構成を適用したTFT基板の構成例を示す拡大平面図である。

**【図23】**図22のD-D'線断面図である。

**【図24】**図20の回路構成を適用したTFT基板の他の構成例を示す拡大平面図である。

**【図25】**図24のF-F'線断面図である。

**【図26】**前記実施例の第5の変形例を説明するための模式図であり、TFT基板の回路構

50

成を示す図である。

【図27】前記実施例の第5の変形例を説明するための模式図であり、TFT基板の回路構成の他の例を示す図である。

【図28】前記実施例の第5の変形例を説明するための模式図であり、TFT基板の回路構成の他の例を示す図である。

【図29】図27の回路構成を適用したTFT基板の構成例を示す拡大平面図である。

【図30】図29のG-G'線断面図である。

【図31】従来のTFT基板の回路構成を示す図である。

【符号の説明】

【0083】

1 ... TFT基板

1 0 1 ... ガラス基板

1 0 2 ... 第1層間絶縁膜

1 0 3 ... 半導体層

1 0 4 ... 第2層間絶縁膜

2 ... CF基板

3 ... シール材

4 ... 液晶材料

G L ... ゲート電極線

D L ... ドレイン電極線

C L ... 共通信号線

P X ... 画素電極

P X d ... ダミーの画素電極

C T ... コモン電極

S L ... ソース電極

B R ... ブリッジ配線

D P 1 ... 第1のダミー画素

D P 2 ... 第2のダミー画素

D P 3 ... 第3のダミー画素

10

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

図10

【図11】

図11

【図12】

図12

【図13】

【図14】

図14

【図15】

図15

【図16】

図16

【図17】

図17

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

図26

【図27】

図27

【図28】

図28

【図29】

図29

【図30】

【図31】

図31

---

フロントページの続き

(72)発明者 鴨志田 健太

千葉県茂原市早野3300番地 株式会社日立ディスプレイズ内

(72)発明者 盛 育子

千葉県茂原市早野3300番地 株式会社日立ディスプレイズ内

審査官 小濱 健太

(56)参考文献 特開2004-341134(JP,A)

国際公開第2004/097786(WO,A1)

(58)調査した分野(Int.Cl., DB名)

G 02 F 1 / 1343

G 02 F 1 / 1368

G 02 F 1 / 133