(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6542120号

(P6542120)

(45) 発行日 令和1年7月10日(2019.7.10)

(24) 登録日 令和1年6月21日(2019.6.21)

(51) Int.Cl.

H03F 1/32 (2006.01)

H03F 3/24 (2006.01)

F 1

H03F 1/32

H03F 3/24

請求項の数 14 (全 11 頁)

(21) 出願番号 特願2015-524332 (P2015-524332)

(86) (22) 出願日 平成25年7月18日 (2013.7.18)

(65) 公表番号 特表2015-525036 (P2015-525036A)

(43) 公表日 平成27年8月27日 (2015.8.27)

(86) 國際出願番号 PCT/US2013/051149

(87) 國際公開番号 WO2014/018379

(87) 國際公開日 平成26年1月30日 (2014.1.30)

審査請求日 平成28年7月13日 (2016.7.13)

(31) 優先権主張番号 61/674,771

(32) 優先日 平成24年7月23日 (2012.7.23)

(33) 優先権主張国 米国(US)

(73) 特許権者 511257056

ダリ システムズ カンパニー リミテッド

イギリス国領 ケイマン諸島 ジョージ

タウン グランド ケイマン, ウグラン

ド ハウス サウス チャーチ ストリート,

ピーオー ボックス 309, オ

フィス オブ メープルス コーポレート

サービシーズ リミテッド

(74) 代理人 100104824

弁理士 犢場 仁

(74) 代理人 100137969

弁理士 岡部 憲昭

最終頁に続く

(54) 【発明の名称】ワイヤレス通信システムにおける広帯域デジタルプリディストーションのために周波数が広く離間している信号を整合させるための方法及びシステム

## (57) 【特許請求の範囲】

## 【請求項 1】

周波数が広く離間している信号を時間的に整合させるためのシステムであって、

デジタルプリディストーション入力とデジタルプリディストーション出力を有するデジタルプリディストーションプロセッサと、

前記デジタルプリディストーション出力に結合されており、電力増幅器出力において送信信号を提供するように動作可能な電力増幅器と、

前記電力増幅器出力に結合されているフィードバックループであって、前記フィードバックループが、

前記電力増幅器出力に結合され、フィードバック信号を出力するアナログ - デジタル変換器ユニットであって、前記アナログ - デジタル変換器ユニットがサンプリングレートおよび対応するサンプリング周期を有する、アナログ - デジタル変換器ユニットと、

前記アナログ - デジタル変換器ユニットに結合され、前記サンプリング周期の分数に基づき前記フィードバック信号を時間シフトさせるように構成される適応的非整数遅延フィルタと、

前記適応的非整数遅延フィルタに結合され、前記デジタルプリディストーション出力からの入力を受信する遅延推定器と、

前記遅延推定器および前記デジタルプリディストーションプロセッサに結合されているデジタルプリディストーション係数推定器と、

を備える、フィードバックループと、

10

20

を備える、システム。

**【請求項 2】**

前記遅延推定器が、制御アルゴリズムをさらに備える、請求項 1 に記載のシステム。

**【請求項 3】**

前記適応的非整数遅延フィルタが、3 次又はより高次の L a g r a n g e F a r r o w フィルタに基づく、請求項 1 に記載のシステム。

**【請求項 4】**

前記アナログ - デジタル変換器ユニットがアナログ - デジタル変換器とデジタル周波数遮断器を含む、請求項 1 に記載のシステム。

**【請求項 5】**

前記遅延推定器は、タイミング誤差の関数を計算するように動作可能である、請求項 1 に記載のシステム。

**【請求項 6】**

前記遅延推定器は、前記送信信号と前記適応的非整数遅延フィルタの出力をフィルタリングすることにより、前記タイミング誤差の前記関数を計算するように動作可能である、請求項 5 に記載のシステム。

**【請求項 7】**

前記タイミング誤差の前記関数が、振幅 2 乗関数を含む、請求項 5 に記載のシステム。

**【請求項 8】**

前記適応的非整数遅延フィルタは低域通過フィルタである、請求項 1 に記載のシステム。

**【請求項 9】**

前記適応的非整数遅延フィルタが、遅延パラメータを含む、請求項 1 に記載のシステム。

**【請求項 10】**

前記デジタルプリディストーション係数推定器は、前記遅延パラメータを使用してプリディストーション係数を推定するように動作可能である、請求項 9 に記載のシステム。

**【請求項 11】**

前記遅延パラメータは、刻み幅パラメータを乗算したカウンタにより計算される、請求項 9 に記載のシステム。

**【請求項 12】**

前記刻み幅パラメータが 0 から 1 までの範囲である、請求項 11 に記載のシステム。

**【請求項 13】**

前記時間シフトさせる値は、前記遅延パラメータを前記サンプリングレートで割った値に等しい、請求項 12 に記載のシステム。

**【請求項 14】**

前記遅延パラメータが 0 から 1 までの範囲である、請求項 9 に記載のシステム。

**【発明の詳細な説明】**

**【関連出願の相互参照】**

**【0 0 0 1】**

[0001]本出願は、2012年7月23日に提出された、「Method and System for Aligning Signals Widely Spaced in Frequency for Wideband Digital Predistortion in Wireless Communication Systems」と題する米国特許仮出願第61/674,771号に対する優先権を主張し、当該特許仮出願の開示は、本明細書によって、参照によりその全体がすべての目的で本明細書に援用される。

**【発明の背景】**

**【0 0 0 2】**

10

20

30

40

50

[0002]プリディストーションは、電力増幅器の線形性を改善するために、通信システムにおいて使用される技法である。電力増幅器は非線形的な入力／出力特性を有する可能性があるため、電力増幅器の入力／出力特性を線形化するためにプリディストーションが使用される。本質的には、電力増幅器に供給される入力に「インバースディストーション」が導入され、それによって、電力増幅器の非線形特性が相殺される。

#### 【0003】

[0003]移動体通信システムにおける電力増幅器を線形化するために使用される現行のプリディストーション技術には、主に、アナログ回路によって I F / R F において実装されるアナログプリディストータ、及び、デジタル信号処理 (D S P : d i g i t a l s i g n a l p r o c e s s i n g ) 技法によるベースバンドにおけるデジタルプリディストータがある。10

#### 【0004】

[0004]アナログプリディストータは、電力増幅器の線形化をもたらすために、誤差減算及び電力マッチングの原理に基づく。電力増幅器の非線形特性は複雑で、多くの変数を伴う可能性があるため、アナログプリディストーションの結果として、プリディストーション精度が最適なものではなくなり、相当の電力を消費することになる。

#### 【0005】

[0005]プリディストーション技術において為されている進展にもかかわらず、デジタルプリディストーションシステムのための方法及びシステムを改善することが、当該技術分野において必要とされている。20

#### 【発明の概要】

#### 【0006】

[0006]したがって、上記の問題を鑑みて本発明が成されており、本発明の目的は、広帯域デジタルプリディストーションシステムのために、送信信号とフィードバック信号との間の遅延を推定するロバストな方法を提供することである。上記の目的を達成するために、本発明の一実施形態によれば、本技法は、フィードバック経路内の F a r r o w 構造に基づく非整数遅延フィルタ、及び、フィードバック経路遅延を正確に制御するためのアルゴリズムの使用に基づく。本発明の実施形態は、送信信号とフィードバック信号とを、いかなる時も高い精度で時間的に整合させることができることである。30

#### 【0007】

[0007]本発明の一実施形態によれば、周波数が広く離間している搬送波を用いた広帯域デジタルプリディストーションのための単純で確実な遅延推定方法が提供される。本発明は、広帯域デジタルプリディストーションシステムのために、送信信号とフィードバック信号とを時間的に整合させる方法を提供する。上記の目的を達成するために、本発明の一実施形態によれば、本技法は、設計及び制御が非常に単純である 3 次 L a g r a n g e F a r r o w 構造に基づくプログラム可能非整数遅延フィルタの使用に基づく。本明細書に説明する実施形態は、瞬時 1 0 0 M H z 帯域幅を超えて、デジタルプリディストーションシステムにおいて信号を整合させることができる。

#### 【0008】

[0008]本発明の一実施形態によれば、周波数が広く離間している信号を時間的に整合させるためのシステムが提供される。システムは、デジタルプリディストーション (D P D : d i g i t a l p r e d i s t o r t i o n ) プロセッサと、D P D プロセッサに結合されており、電力増幅器出力において送信信号を提供するように動作可能な電力増幅器とを含む。システムはまた、電力増幅器出力に結合されているフィードバックループをも含む。フィードバックループは、適応的非整数遅延フィルタと、適応的非整数遅延フィルタに結合されている遅延推定器と、遅延推定器に結合されている D P D 係数推定器とを含む。40

#### 【0009】

[0009]本発明の別の実施形態によれば、信号を時間的に整合させる方法が提供される。方法は、a ) 遅延パラメータの値を計算するステップと、b ) 複数の送信信号を受信する50

ステップと、c) 複数のフィードバック信号を受信するステップとを含む。方法はまた、d) 複数の送信信号及び複数のフィードバック信号を使用してタイミング誤差に関する関数を求めるステップと、e) タイミング誤差に関する関数が所定閾値以上であることを判定するステップと、f) カウンタを増分するステップとをも含む。方法は、g) a) ~ f) のうちの 1 つ又は複数を 1 回以上反復するステップと、h) タイミング誤差に関する関数が所定閾値未満であることを判定するステップと、i) 遅延パラメータを固定するステップとをさらに含む。

#### 【0010】

[0010] 本発明を用いて、従来技法にまさる多数の利点が達成される。たとえば、本発明の実施形態は、フィードバック経路における遅延の制御を強化することを可能にし、デジタルプリディストーションシステムの性能特性を改善する。本発明のこれらの及び他の実施形態は、その利点及び特徴の多くとともに、以下の本文及び添付の図面に関連してより詳細に説明される。10

#### 【図面の簡単な説明】

#### 【0011】

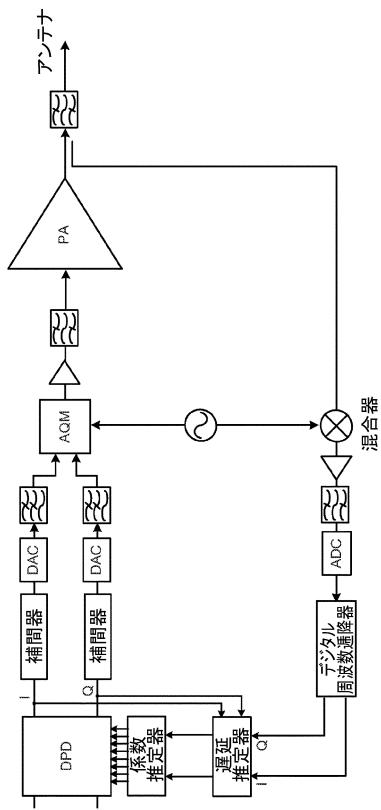

【図 1】本発明の一実施形態による遅延推定を用いたデジタルプリディストーションを含む多搬送波広帯域システムを示す概略ブロック図である。

#### 【0012】

【図 2】本発明の一実施形態による広帯域信号を整合させるためのシステムを示す概略ブロック図である。20

#### 【0013】

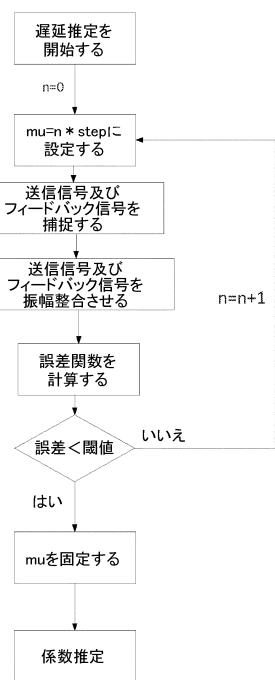

【図 3】本発明の一実施形態による信号を時間的に整合させる方法を示す簡略化された流れ図である。

#### 【特定の実施形態の詳細な説明】

#### 【0014】

[0014] 本発明は、一般的に、多重化変調技法を使用した広帯域通信システムに関する。より詳細には、本発明は、ワイヤレス送信機における広帯域デジタルプリディストーション線形化のために、周波数が広く離間している信号を整合させる方法に関する。

#### 【0015】

[0015] 無線周波数 (RF : r a d i o f r e q u e n c y ) 電力増幅器 (PA : power amplifier) の線形性及び効率は、ワイヤレス通信システムにおいてスペクトル効率の重要性が増している中で、高いピーク対平均電力比 (PAR : peak to average power ratio) を有する非定包絡線デジタル変調方式にとって重要な設計課題になっている。RF PA は、PA の出力に振幅変調 - 振幅変調 (AM - AM : amplitude modulation - amplitude modulation) 及び振幅変調 - 位相変調 (AM - PM : amplitude modulation - phase modulation) ディストーションをもたらす非線形性を有する。非線形性の影響により、隣接するチャネルのスペクトル再成長、及び、誤差ベクトル振幅 (EVM : error vector magnitude) を劣化させる帯域内ディストーションがもたらされる。それゆえ、様々な線形化技法のうちの 1 つが、一般的に RF PA に適用される。フィードバック、フィードフォワード及びプリディストーションのような様々な線形化技法が、文献において提案されている。30

#### 【0016】

[0016] 最も有望な線形化技法は、近年のデジタル信号プロセッサの進歩を利用するベースバンドデジタルプリディストーション (DPD) である。DPD は、広く使用されている従来のフィードフォワード線形化技法と比較してシステム複雑度を低減しながら、良好な線形性、良好な電力効率を達成することができる。その上、ソフトウェア実装態様は、デジタルプリディストータに、多標準環境に適した再構成可能性をもたらす。加えて、効率強化技法を使用する PA そのようなドハティ電力増幅器 (DPA : Doherty power amplifier) は、線形性を犠牲にして従来の PA 設計よりも高い効率4050

を達成することが可能である。それゆえ、D P Dを、効率強化技法を使用するD P Aと組み合わせることによって、システムの線形性及び全体的な効率を最大限に引き出せる可能性がある。

#### 【 0 0 1 7 】

[0017]一般的なワイヤレス通信システムの瞬時帯域幅は、約20MHz～25MHzをサポートする。デジタルプリディストーションアルゴリズムの一般的な遅延推定は、2倍以上のオーバーサンプリングによって、送信信号とフィードバック信号との間の大小関係を使用する。

#### 【 0 0 1 8 】

[0018]しかしながら、次世代ワイヤレスシステムの瞬時帯域幅の要件(>25MHz)は増大し続けており、これは、広帯域の複数の搬送波が、周波数が広く離間する可能性があることを意味し、たとえば、搬送波間隔は、65MHzの瞬時帯域幅をサポートするシステムについて最大60MHzになる可能性がある。瞬時帯域幅の要件の増大によって、搬送波間隔が大きいことに起因して、非常に短い時間差でいくつかの相関ピークが生じる可能性がある。相関ピークが生じることによって大きな遅延整合誤差が生じる可能性があり、これは望ましいことではない。したがって、本発明の実施形態は、確実な遅延推定を用いる広帯域デジタルプリディストーションシステムを提供する。

#### 【 0 0 1 9 】

[0019]図1は、デジタルプリディストーション(DPD)回路、補間器、デジタル-アナログ変換器、変調器、電力増幅器、デュブレクサ、PAの出力に結合される出力に対する無線周波数遅降回路、デジタルプリディストーションフィードバック経路のためのアナログ-デジタル変換器、及びデジタル周波数遅降器を示す概略ブロック図である。デジタルプリディストーションシステムは、複合信号(I及びQ)の振幅に基づく遅延推定を利用する。通常、フィードバックADCのサンプルレートは、デジタルプリディストータのサンプルレートの2倍である。たとえば、デジタルプリディストーションサンプルレートが125MHzである場合、フィードバックADCのサンプルレートは一般的に少なくとも250MHzであり、これは、ハードウェア制御可能遅延の最小分解能が4ns(1/250MHz)であることを意味する。いくつかの実装態様において、この最小分解能は、周波数が広く離間している搬送波の場合に所望の精度で送信とフィードバック経路との間の遅延を整合させるほど十分に小さくはない。

#### 【 0 0 2 0 】

[0020]遅延推定器は、フィードバック経路からの入力、並びに、DPD回路の出力からの入力を受信する。遅延推定器は、これらの入力の間の差を計算し、誤差最小化プロセスの一部として信号を時間的に整合させるために係数推定器に入力を与える。本発明のいくつかの実施形態において、遅延推定器は、DPD回路の出力における同相成分及びフィードバック信号の同相成分並びにDPD回路の出力における直角位相成分及びフィードバック信号の直角位相成分の間のタイミング誤差の関数である値をもたらす。

#### 【 0 0 2 1 】

[0021]タイミング誤差に関連する関数とも称され得る、タイミング誤差の関数の計算の一例として、関数は、複合フィードバック信号とDPD回路の複合出力との間の平均2乗誤差とすることができます。

#### 【 数 1 】

$$\text{誤差} = (\hat{I} - I)^2 + (\hat{Q} - Q)^2$$

式中、

#### 【 数 2 】

$\hat{I}$

は同相フィードバック信号であり、

10

20

30

40

## 【数3】

$\hat{Q}$

は直角位相フィードバック信号であり、

Iは同相出力D P D信号であり、

Qは直角位相出力D P D信号である。

## 【0022】

[0022]図2は、本発明の一実施形態による広帯域信号を整合させるためのシステムを示す概略ブロック図である。図2に示すシステムは、デジタルプリディストーション(D P D)回路と、補間器と、デジタル-アナログ変換器と、変調器と、電力増幅器と、デュブレクサと、P Aの出力に結合される出力に対する無線周波数遅降回路と、フィードバック経路のためのアナログ-デジタル変換器と、デジタル周波数遅降器と、いくつかの実施形態において0~1に及ぶ制御可能パラメータ(mu)を有する非整数遅延フィルタとを含む。

10

## 【0023】

[0023]本発明の本発明によれば、非整数遅延フィルタは、非整数遅延フィルタは、単純な実装を可能にし、デジタルプリディストーションサンプルレートにおける動作を可能にする3次L a g r a n g e F a r r o w構造に基づいて実装される。特定の用途に対する必要に応じて、より高次のL a g r a n g e F a r r o wフィルタを使用することができる。最小遅延分解能はサンプルレートの10倍以上とすることができ、これは、最小遅延分解能を、1 G H zのサンプルレートを有するフィードバックA D Cについて0.1 n s程度に小さくすることができます。無論、最小遅延分解能は、いくつかの実装態様においてはビット数に依存することになる。同様の最小遅延をもたらすために、従来のシステムであれば、ハードウェアにおける10 G H zサンプルレート補間器、又は、複雑で時間のかかるソフトウェアフィルタリングアルゴリズムを使用することになる。

20

## 【0024】

[0024]非整数遅延フィルタは、サンプリングレートの分数による信号のシフト(すなわち、信号の時間シフト)を可能にする。一例として、サンプリングレートが100 M H zであったとすると、従来のシステムは、各サンプル間に10 n s(すなわち、1/100 M H z)をもたらすレートでしかサンプリングしない。図2に示すように、非整数遅延フィルタは、muとして示すパラメータを含む。パラメータは、パラメータは、信号のシフトが、サンプリングレートの所定分数、たとえば、サンプリングレートの1/10によって遅延を変化させることを可能にする。したがって、非整数遅延フィルタは、最小遅延を、0~1に及ぶmu値について10 n sから1 n sに低減することを可能にする。したがって、本発明の実施形態は、広帯域通信システムにおけるデジタルプリディストーションのコンテキストにおける非整数遅延フィルタリングを利用する。

30

## 【0025】

[0025]図2を再び参照すると、非整数遅延フィルタは、パラメータmuの関数としての可変遅延を用いる低域通過フィルタとしての役割を果たす。動作中のパラメータmuの変動に関する追加の記述を以下に与える。

40

## 【0026】

[0026]図3は、本発明の一実施形態による信号を時間的に整合させる方法を示す流れ図である。遅延推定が開始すると、カウンタ(n)が0に設定され、muがカウンタに刻み幅を乗算した値に設定され(mu = n \* step)、したがってmuは0に設定される。刻み幅は、多様な値、たとえば、0.2、0.1、0.05などに設定することができる。一例として、A D Cが1 M H zのサンプルレート(すなわち、サンプルあたり1 μ s)において動作しており、刻み幅が0.1に設定される場合、カウンタは0.1 μ sの最小遅延分解能をもたらすために増分されるため、muは0.1の倍数に設定されることになる。

50

## 【0027】

[0027]信号は、D P D回路の出力及びフィードバック経路の出力（すなわち、デジタル周波数遅降器の出力）において捕捉される。D P D回路の出力とフィードバック経路の出力とは振幅整合される。2つの経路の整合された捕捉信号を使用して、タイミング誤差の関数の計算が、図2に示すような遅延推定器において実行される。最初の反復中、 $n = 0$ 及び $m_u = 0$ であり、非整数遅延フィルタに対するパラメータ $m_u = 0$ がもたらされる。結果もたらされるタイミング誤差の関数が所定閾値以上である場合、カウンタが増分され、次の反復について $m_u$ が再計算される（すなわち、この例では2回目の反復について $m_u = 1 * step = 1 * 0 . 1 = 0 . 1$ ）。プロセスは、タイミング誤差の関数が所定閾値未満になり、 $m_u$ が固定され、遅延推定器からの値が係数推定器（すなわち、係数推定アルゴリズム）に与えられるまで反復する。刻み幅はこの例における0 . 1の値には限定されず、必要に応じて他の値、たとえば、0 . 2、0 . 1、0 . 05などに設定することができます。10

## 【0028】

[0028]本発明の実施形態は、信号誤差を所定レベルまで低減するためのリアルタイムの適応的処理を可能にする。当業者には明白になるように、所定数のシンボルが捕捉され（たとえば、4000サンプル）、遅延推定値を求めるためにタイミング誤差の関数の計算が実行され、その後、係数推定器に遅延が与えられる。

## 【0029】

[0029]図3を参照すると、信号を時間的に整合させる方法が提供される。方法は、a) 遅延パラメータの値を計算するステップと、b) 複数の送信信号を受信するステップと、c) 複数のフィードバック信号を受信するステップとを含む。図3に示すように、遅延パラメータの値を計算するステップは、カウンタに刻み幅パラメータを乗算するステップを含むことができる。刻み幅パラメータは、0 ~ 1に及ぶことができる。方法はまた、d) 複数の送信信号及び複数のフィードバック信号を使用してタイミング誤差の関数を求めるステップと、e) タイミング誤差の関数が所定閾値以上であることを判定するステップとをも含む。複数の送信信号及び複数のフィードバック信号を使用してタイミング誤差の関数を求めるステップは、複数の送信信号及び複数のフィードバック信号をフィルタリングするサブステップと、タイミング誤差を推定するサブステップとを含むことができる。20

## 【0030】

[0030]方法は、f) カウンタを増分するステップと、g) a) ~ f) を1回以上反復するステップとをさらに含む。いくつかの実施形態において、a) ~ f) のサブセットは1回以上反復される。図3に示すように、a) ~ f) の反復は、タイミング誤差の関数が所定閾値以上である限り実行される。30

## 【0031】

[0031]方法は、数回の反復及び遅延パラメータの値の増大の後、h) タイミング誤差の関数が所定閾値未満であることを判定するステップと、i) 遅延パラメータを固定するステップとを含む。一実施形態において、方法はまた、遅延パラメータを使用してプリディストーション係数を推定するステップをも含む。

## 【0032】

[0032]図3に示す特定のステップは、本発明の一実施形態による信号を時間的に整合させる特定の方法を提供することが諒解されるべきである。代替的な実施形態による他の一連のステップも実行されてもよい。たとえば、本発明の代替的な実施形態は、上記に概説したステップを異なる順序で実行してもよい。その上、図3に示す個々のステップは、個々のステップに対する必要に応じて、様々な順序で実行されてもよい複数のサブステップを含んでもよい。さらに、特定の用途に応じてさらなるステップが追加又は削除されてもよい。当業者であれば、多くの変形形態、変更形態、及び代替形態を認識しよう。40

## 【0033】

[0033]本明細書に説明する例及び実施形態は例示のみを目的としていること、並びに、本明細書に記載する例及び実施形態に照らして様々な改変又は変更が当業者に示唆され、50

本出願の趣旨及び範囲並びに添付の特許請求項の範囲内に含まれるべきであることも理解される。

[発明の項目]

[項目1]

周波数が広く離間している信号を時間的に整合させるためのシステムであって、

デジタルプリディストーション（D P D）プロセッサと、

前記デジタルプリディストーションプロセッサに結合されており、電力増幅器出力において送信信号を提供するように動作可能な電力増幅器と、

前記電力増幅器出力に結合されているフィードバックループと、

を備えており、

前記フィードバックループが、

適応的非整数遅延フィルタと、

前記適応的非整数遅延フィルタに結合されている遅延推定器と、

前記遅延推定器に結合されているデジタルプリディストーション係数推定器と、

を備える、システム。

[項目2]

前記遅延推定器が、制御アルゴリズムをさらに備える、項目1に記載のシステム。

[項目3]

前記非整数遅延フィルタが、3次又はより高次のL a g r a n g e F a r r o w フィタに基づく、項目1に記載のシステム。

[項目4]

信号を時間的に整合させるための方法であって、

a) 遅延パラメータの値を計算するステップと、

b) 複数の送信信号を受信するステップと、

c) 複数のフィードバック信号を受信するステップと、

d) 前記複数の送信信号及び前記複数のフィードバック信号を使用してタイミング誤差の関数を求めるステップと、

e) 前記タイミング誤差の前記関数が所定閾値以上であることを判定するステップと、

f) カウンタを増分するステップと、

g) a) ~ f) を1回以上反復するステップと、

h) 前記タイミング誤差の前記関数が前記所定閾値未満であることを判定するステップと、

i) 前記遅延パラメータを固定するステップと、

を含む、方法。

[項目5]

前記遅延パラメータを使用してプリディストーション係数を推定するステップをさらに含む、項目4に記載の方法。

[項目6]

前記遅延パラメータの前記値を計算するステップが、前記カウンタに刻み幅パラメータを乗算するステップを含む、項目4に記載の方法。

[項目7]

前記刻み幅パラメータが0から1までの範囲である、項目6に記載の方法。

[項目8]

前記複数の送信信号及び前記複数のフィードバック信号を使用して前記タイミング誤差の前記関数を求めるステップが、

前記複数の送信信号及び前記複数のフィードバック信号をフィルタリングするサブステップと、

前記タイミング誤差を推定するサブステップと、

を含む、項目4に記載の方法。

[項目9]

10

20

30

40

50

前記タイミング誤差の前記関数が、振幅2乗関数を含む、項目4に記載の方法。

[項目10]

前記タイミング誤差の前記関数が、振幅ピーク相関関数を含む、項目4に記載の方法。

[項目11]

前記タイミング誤差の前記関数が、誤差ベクトル振幅(EVM)関数を含む、項目4に記載の方法。

[項目12]

信号を時間的に整合させるための方法であつて、

a) カウンタを使用して遅延フィルタの遅延パラメータの値を計算するステップと、

b) 複数の送信信号を受信するステップと、

c) 複数のフィードバック信号を受信するステップと、

d) 前記複数の送信信号及び前記複数のフィードバック信号を使用してタイミング誤差の関数を求めるステップと、

e) 前記タイミング誤差の前記関数が所定閾値以上であることを判定するステップと、

f) 前記カウンタを増分するステップと、

g) a) ~ f) を1回以上反復するステップと、

h) 前記タイミング誤差の前記関数が前記所定閾値未満であることを判定するステップと、

i) 前記遅延フィルタの前記遅延パラメータを固定するステップと、

を含む、方法。

10

[項目13]

前記遅延パラメータを使用してプリディストーション係数を推定するステップをさらに含む、項目12に記載の方法。

[項目14]

前記遅延パラメータの前記値を計算するステップが、前記カウンタに刻み幅パラメータを乗算するステップを含む、項目12に記載の方法。

[項目15]

前記刻み幅パラメータが0から1までの範囲である、項目14に記載の方法。

[項目16]

前記複数の送信信号及び前記複数のフィードバック信号を使用して前記タイミング誤差の前記関数を求めるステップが、

30

前記複数の送信信号及び前記複数のフィードバック信号をフィルタリングするサブステップと、

前記タイミング誤差を推定するサブステップと、

を含む、項目12に記載の方法。

[項目17]

前記タイミング誤差の前記関数が、振幅2乗関数を含む、項目12に記載の方法。

[項目18]

前記タイミング誤差の前記関数が、振幅ピーク相関関数を含む、項目12に記載の方法。

40

[項目19]

前記タイミング誤差の前記関数が、誤差ベクトル振幅(EVM)関数を含む、項目12に記載の方法。

[項目20]

前記遅延フィルタは非整数遅延フィルタを含む、項目12に記載の方法。

【図1】

【図2】

FIG. 1

FIG. 2

【図3】

FIG. 3

---

フロントページの続き

(72)発明者 キム，ワン ジョン

アメリカ合衆国，カリフォルニア州，パロ アルト，スイート 88，ユニヴァーシティ

アベニュー 125

審査官 及川 尚人

(56)参考文献 国際公開第2007/013177 (WO, A1)

特表2002-514028 (JP, A)

特開2011-041049 (JP, A)

特表2006-524832 (JP, A)

特開2007-221244 (JP, A)

特開2011-091499 (JP, A)

特開2010-273064 (JP, A)

特開2001-189685 (JP, A)

国際公開第02/017586 (WO, A1)

(58)調査した分野(Int.Cl., DB名)

H03F 1/32

H03F 3/24