(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7286286号

(P7286286)

(45)発行日 令和5年6月5日(2023.6.5)

(24)登録日 令和5年5月26日(2023.5.26)

(51)国際特許分類

|        |                 |        |       |   |

|--------|-----------------|--------|-------|---|

| H 01 L | 25/04 (2023.01) | H 01 L | 25/04 | Z |

| H 01 L | 25/18 (2023.01) | H 01 L | 23/12 | E |

| H 01 L | 23/12 (2006.01) | H 05 K | 1/14  | E |

| H 05 K | 1/14 (2006.01)  |        |       |   |

F I

請求項の数 22 (全35頁)

(21)出願番号 特願2018-170434(P2018-170434)

(22)出願日 平成30年9月12日(2018.9.12)

(65)公開番号 特開2019-54245(P2019-54245A)

(43)公開日 平成31年4月4日(2019.4.4)

審査請求日 令和3年9月8日(2021.9.8)

(31)優先権主張番号 10-2017-0116517

(32)優先日 平成29年9月12日(2017.9.12)

(33)優先権主張国・地域又は機関

韓国(KR)

(73)特許権者 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区三星路 12

9

129, Samsung-ro, Yeo

ngtong-gu, Suwon-si

, Gyeonggi-do, Repub

lic of Korea

(74)代理人 110000051

弁理士法人共生国際特許事務所

朴正植

(72)発明者

大韓民国 京畿道 水原市 灵通区 勸善路

908番ギル, 72, 103棟 90

最終頁に続く

(54)【発明の名称】 インタポーヴを含む電子装置

## (57)【特許請求の範囲】

## 【請求項1】

電子装置であって、

第1接続端子が形成される第1回路基板と、

前記第1接続端子に接続されて前記第1回路基板に配置されるアプリケーションプロセッサと、

ピアが形成され、前記第1回路基板の少なくとも一部領域を取り囲んで前記ピアの第1端部が前記第1接続端子と電気的に接続されるように第1面が前記第1回路基板に付着されるインタポーヴと、

第2接続端子が形成され、前記第2接続端子が前記ピアの第2端部と電気的に接続されて前記第1回路基板及び前記インタポーヴと共に内部空間を形成するように前記第1面と反対方向の前記インタポーヴの第2面に付着される第2回路基板と、

前記第2接続端子に接続されて前記第2回路基板に配置されるコミュニケーションプロセッサと、

前記コミュニケーションプロセッサに電気的に接続されるアンテナと、を有し、

前記インタポーヴは、メッキ部材を含み、

前記メッキ部材は、前記インタポーヴの上面、側面及び下面に配置され、

前記メッキ部材及び前記ピアは、互いに接続されることを特徴とする電子装置。

## 【請求項2】

前記第2回路基板の上部には、前記第2接続端子と電気的に接続された第3接続端子が

形成されることを特徴とする請求項 1 に記載の電子装置。

【請求項 3】

第 4 接続端子が形成され、前記第 4 接続端子と電気的に接続される第 5 接続端子が形成され、前記第 5 接続端子は前記アンテナと電気的に接続される第 3 回路基板をさらに有することを特徴とする請求項 2 に記載の電子装置。

【請求項 4】

前記第 3 接続端子と前記第 4 接続端子との間を電気的に接続するコネクタをさらに有することを特徴とする請求項 3 に記載の電子装置。

【請求項 5】

前記第 2 回路基板及び前記第 3 回路基板の間にバッテリーが配置されることを特徴とする請求項 3 に記載の電子装置。 10

【請求項 6】

前記第 1 回路基板は、前記インタポーザと付着された第 1 面及び前記第 1 面と反対方向に形成された第 2 面を含み、

前記第 1 回路基板の前記第 2 面には、シールド部材が配置されることを特徴とする請求項 1 に記載の電子装置。

【請求項 7】

前記ピアの下部には前記第 1 回路基板の前記第 1 接続端子と電気的に接続される第 1 パッドが形成され、

前記ピアの上部には前記第 2 回路基板の前記第 2 接続端子と電気的に接続される第 2 パッドが形成されることを特徴とする請求項 1 に記載の電子装置。 20

【請求項 8】

前記第 2 回路基板は、前記インタポーザと接触する第 1 面及び前記第 1 面と反対方向に形成された第 2 面を含み、

前記第 2 回路基板の前記第 2 面には、シールド部材が配置されることを特徴とする請求項 1 に記載の電子装置。

【請求項 9】

前記インタポーザは、側面に少なくとも一つのメッキ部材を含むことを特徴とする請求項 1 に記載の電子装置。

【請求項 10】

前記インタポーザは、少なくとも一つ以上を備え、

前記少なくとも一つ以上のインタポーザは、少なくとも一つのスリットを介して分離されて形成されることを特徴とする請求項 1 に記載の電子装置。 30

【請求項 11】

前記ピアは、前記インタポーザの少なくとも一部を貫いて形成されるホールと、

前記ホールの少なくとも一部を取り囲むメッキパッドと、

前記メッキパッドの少なくとも一部を取り囲む絶縁領域とを含むことを特徴とする請求項 1 に記載の電子装置。

【請求項 12】

前記ピアは、電気信号を伝達するインナーピア (inner via) と、

前記インナーピアの少なくとも一部を取り囲むメッキパッドと、

前記メッキパッドの少なくとも一部を取り囲む絶縁領域とを含むことを特徴とする請求項 1 に記載の電子装置。 40

【請求項 13】

前記インタポーザは、前記ピアの少なくとも一部を取り囲むグラウンド領域と、

前記グラウンド領域の第 1 側に形成され、配線が存在しない第 1 キープアウト領域と、

前記グラウンド領域の第 2 側に形成され、前記配線が存在しない第 2 キープアウト領域とを含むことを特徴とする請求項 1 に記載の電子装置。

【請求項 14】

前記インタポーザの前記グラウンド領域と前記ピアのメッキパッドは、一体で接続され

50

ることを特徴とする請求項 1 3 に記載の電子装置。

【請求項 1 5】

前記インタポーザは、前記グラウンド領域の外側又は内側の少なくとも一部が除去されることを特徴とする請求項 1 3 に記載の電子装置。

【請求項 1 6】

前記インタポーザは、前記グラウンド領域の一部が除去された領域に、前記インタポーザの少なくとも一部面をカバーするメッキ部材を含み、

前記メッキ部材は、前記ビアと一体で接続され、前記グラウンド領域と一体で接続されることを特徴とする請求項 1 5 に記載の電子装置。

【請求項 1 7】

前記インナービア及び前記メッキパッドは、前記インタポーザ上の他の領域に形成され、前記インナービアとメッキパッドは一体で接続されることを特徴とする請求項 1 2 に記載の電子装置。

【請求項 1 8】

電子装置であって、

第 1 接続端子が形成される第 1 回路基板と、

前記第 1 接続端子に接続されて前記第 1 回路基板に配置される第 1 電子部品と、

ビアが形成され、前記第 1 回路基板の少なくとも一部領域を取り囲んで前記ビアの第 1 端部が前記第 1 接続端子と電気的に接続されるように第 1 面が前記第 1 回路基板に付着されるインタポーザと、

第 2 接続端子が形成され、前記第 2 接続端子が前記ビアの第 2 端部と電気的に接続されて前記第 1 回路基板及び前記インタポーザと共に内部空間を形成するように前記第 1 面と反対方向の前記インタポーザの第 2 面に付着される第 2 回路基板と、

前記第 2 接続端子に接続されて前記第 2 回路基板に配置される第 2 電子部品と、

前記第 2 電子部品に電気的に接続されるアンテナと、を有し、

前記インタポーザは、メッキ部材を含み、

前記メッキ部材は、前記インタポーザの上面、側面及び下面に配置され、

前記メッキ部材及び前記ビアは、互いに接続されることを特徴とする電子装置。

【請求項 1 9】

電子装置において、

第 1 接続端子が形成される第 1 回路基板と、

前記第 1 接続端子に接続されて前記第 1 回路基板に配置される第 1 電子部品と、

メッキ部材及びビアが形成され、前記第 1 回路基板の少なくとも一部領域を取り囲んで前記ビアの第 1 端部が前記第 1 接続端子と電気的に接続されるように第 1 面が前記第 1 回路基板に付着されるインタポーザと、

第 2 接続端子が形成され、前記第 2 接続端子が前記ビアの第 2 端部と電気的に接続されて前記第 1 回路基板及び前記インタポーザと共に内部空間を形成するように前記第 1 面と反対方向の前記インタポーザの第 2 面に付着される第 2 回路基板と、

前記第 2 接続端子に接続されて前記第 2 回路基板に配置される第 2 電子部品と、

前記第 2 電子部品に電気的に接続されるアンテナと、を有し、

前記メッキ部材は、前記インタポーザの上面、側面及び下面に配置され、

前記メッキ部材及び前記ビアは、互いに接続されることを特徴とする電子装置。

【請求項 2 0】

前記第 2 回路基板の上部には、前記第 2 接続端子と電気的に接続される第 3 接続端子が形成されることを特徴とする請求項 1 8 又は 1 9 に記載の電子装置。

【請求項 2 1】

第 4 接続端子が形成され、前記第 4 接続端子と電気的に接続される第 5 接続端子が形成されて、前記第 5 接続端子は前記アンテナと電気的に接続される第 3 回路基板をさらに有することを特徴とする請求項 2 0 に記載の電子装置。

【請求項 2 2】

10

20

30

40

50

前記第3接続端子と前記第4接続端子との間を電気的に接続するコネクタをさらに有することを特徴とする請求項21に記載の電子装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、インタポーラを含む電子装置に関し、特に、印刷回路基板の面積を縮小し、電子装置のバッテリー拡張空間を確保することができる電子装置に関する。

【背景技術】

【0002】

ポータブル端末機などのような電子装置は小型化及び多機能化されるべき必要がある。

このために、電子装置は多様な部品が実装された印刷回路基板（例えば、PCB（printed circuit board）、PBA（printed board assembly）及びFPCB（flexible printed circuit board）など）を含む。

印刷回路基板は、電子装置（例えば、スマートフォン）に必要なプロセッサ、メモリー、カメラ、放送受信モジュール及び通信モジュールなどを含むことができる。

印刷回路基板は実装された複数個の電子部品を接続する回路配線を含むことができる。

【0003】

しかし、電子装置の使用時間を増やすためには、バッテリーの容量が増加されなければならない。

電子装置に内装された印刷回路基板が単層から形成された場合、バッテリーの容量を拡張させるための空間の確保が難しいことがある。

電子装置のバッテリー容量を増加させるためには、内装された印刷回路基板の面積を縮小し、バッテリー拡張空間を確保しなければならないという課題がある。

【先行技術文献】

【特許文献】

【0004】

【文献】特開2009-10569号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明は上記従来の電子装置における課題点に鑑みてなされたものであって、本発明の目的は、第1回路基板及び第2回路基板の間にビア及び部品実装用空間が形成されたインタポーラを插入し、第1回路基板及び第2回路基板を積層させることによって、印刷回路基板の面積を縮小し、前記縮小された印刷回路基板の面積ほど電子装置のバッテリー拡張空間を確保することができる電子装置を提供することにある。

【課題を解決するための手段】

【0006】

上記目的を達成するためになされた本発明による電子装置は、第1接続端子が形成される第1回路基板と、前記第1接続端子に接続されて前記第1回路基板に配置されるアプリケーションプロセッサと、ビアが形成され、前記第1回路基板の少なくとも一部領域を取り囲んで前記ビアの第1端部が前記第1接続端子と電気的に接続されるように第1面が前記第1回路基板に付着されるインタポーラと、第2接続端子が形成され、前記第2接続端子が前記ビアの第2端部と電気的に接続されて前記第1回路基板及び前記インタポーラと共に内部空間を形成するように前記第1面と反対方向の前記インタポーラの第2面に付着される第2回路基板と、前記第2接続端子に接続されて前記第2回路基板に配置されるコミュニケーションプロセッサと、前記コミュニケーションプロセッサに電気的に接続されるアンテナと、を有し、前記インタポーラは、メッキ部材を含み、前記メッキ部材は、前記インタポーラの上面、側面及び下面に配置され、前記メッキ部材及び前記ビアは、互いに接続されることを特徴とする。

10

20

30

40

50

## 【0007】

また、上記目的を達成するためになされた本発明による電子装置は、第1接続端子が形成される第1回路基板と、前記第1接続端子に接続されて前記第1回路基板に配置される第1電子部品と、ビアが形成され、前記第1回路基板の少なくとも一部領域を取り囲んで前記ビアの第1端部が前記第1接続端子と電気的に接続されるように第1面が前記第1回路基板に付着されるインタポーラと、第2接続端子が形成され、前記第2接続端子が前記ビアの第2端部と電気的に接続されて前記第1回路基板及び前記インタポーラと共に内部空間を形成するように前記第1面と反対方向の前記インタポーラの第2面に付着される第2回路基板と、前記第2接続端子に接続されて前記第2回路基板に配置される第2電子部品と、前記第2電子部品に電気的に接続されるアンテナと、を有し、前記インタポーラは、メッキ部材を含み、前記メッキ部材は、前記インタポーラの上面、側面及び下面に配置され、前記メッキ部材及び前記ビアは、互いに接続されることを特徴とする。

## 【0008】

また、上記目的を達成するためになされた本発明による電子装置は、第1接続端子が形成される第1回路基板と、前記第1接続端子に接続されて前記第1回路基板に配置される第1電子部品と、メッキ部材及びビアが形成され、前記第1回路基板の少なくとも一部領域を取り囲んで前記ビアの第1端部が前記第1接続端子と電気的に接続されるように第1面が前記第1回路基板に付着されるインタポーラと、第2接続端子が形成され、前記第2接続端子が前記ビアの第2端部と電気的に接続されて前記第1回路基板及び前記インタポーラと共に内部空間を形成するように前記第1面と反対方向の前記インタポーラの第2面に付着される第2回路基板と、前記第2接続端子に接続されて前記第2回路基板に配置される第2電子部品と、前記第2電子部品に電気的に接続されるアンテナと、を有し、前記メッキ部材は、前記インタポーラの上面、側面及び下面に配置され、前記メッキ部材及び前記ビアは、互いに接続されることを特徴とする。

## 【発明の効果】

## 【0009】

本発明に係る電子装置によれば、第1回路基板及び第2回路基板の間にビア(via)及び部品実装用空間が形成されたインタポーラを挿入し、第1回路基板及び第2回路基板を積層させることによって、印刷回路基板の面積を縮小し、縮小された印刷回路基板の面積ほど電子装置のバッテリー拡張空間を確保することができるという効果がある。

## 【図面の簡単な説明】

## 【0010】

【図1】本発明の一実施形態によるネットワーク環境内の電子装置の構成を示すブロック図である。

【図2】本発明の一実施形態による電子装置の一部構成に対する分解斜視図である。

【図3】本発明の一実施形態による電子装置の一部構成に対する組立結合図である。

【図4】本発明の一実施形態による電子装置の第1回路基板、第2回路基板、第3回路基板の接続関係を概略的に示す斜視図である。

【図5】本発明の一実施形態による電子装置の第1回路基板、第2回路基板、第3回路基板の接続関係を概略的に示す側面図である。

【図6】本発明の一実施形態による電子装置の第1回路基板、第2回路基板、第3回路基板の構成及び接続関係を概略的に示すブロック図である。

【図7】本発明の一実施形態による電子装置の第1回路基板及び第2回路基板に対する他の構成を示す断面図である。

【図8】本発明の一実施形態による電子装置の第1回路基板及び第2回路基板に対するまた他の構成を示す断面図である。

【図9】本発明の一実施形態による電子装置の第1回路基板及び第2回路基板の接続関係を概略的に示す斜視図である。

【図10】本発明の一実施形態による電子装置の第1回路基板及び第2回路基板の接続関係を概略的に示す側面図である。

10

20

30

40

50

【図11】本発明の一実施形態による電子装置のインタポーザの概略を示す図である。

【図12】本発明の他の実施形態による電子装置のインタポーザの概略を示す図である。

【図13】本発明の一実施形態による電子装置のビアの第1の例及びインタポーザの第1の例を示す図である。

【図14】本発明の一実施形態による電子装置のビアの第2の例及びインタポーザの第2の例を示す図である。

【図15】本発明の一実施形態による電子装置のビアの第3の例及びインタポーザの第3の例を示す図である。

【図16】本発明の一実施形態による電子装置のインタポーザの第4の例の構成を示す図である。

10

【図17】本発明の一実施形態による電子装置のインタポーザの第5の例の構成を示す図面である。

【図18】本発明の一実施形態による電子装置のインタポーザの第6の例の構成を示す図面である。

【図19】本発明の一実施形態による電子装置のインタポーザ、ビア、及び側面メッキ部材の構成を示す図である。

【図20A】本発明の一実施形態による電子装置のビア、インタポーザ及び第1回路基板の構成を説明するための図であり、インタポーザに形成されたビアの断面図である。

【図20B】本発明の一実施形態による電子装置のビア、インタポーザ及び第1回路基板の構成を説明するための図であり、第1回路基板（又は第2回路基板）に形成された第3導電パッドの構成を示す断面図である。

20

【図20C】本発明の一実施形態による電子装置のビア、インタポーザ及び第1回路基板の構成を説明するための図であり、第1回路基板（又は第2回路基板）に形成された第3導電パッドの構成を示す平面図である。

【図21A】本発明の一実施形態による電子装置のビア、インタポーザ、及び第1回路基板の他の構成を説明するための図であり、インタポーザに形成されたビアの断面図である。

【図21B】本発明の一実施形態による電子装置のビア、インタポーザ、及び第1回路基板の他の構成を説明するための図であり、第1回路基板（又は第2回路基板）に形成された第3導電パッドの構成を示す断面図である。

【図21C】本発明の一実施形態による電子装置のビア、インタポーザ、及び第1回路基板の他の構成を説明するための図であり、第1回路基板（又は第2回路基板）に形成された第3導電パッドの構成を示す平面図である。

30

【図22】本発明の一実施形態による電子装置のインタポーザ及び側面メッキ部材の構成を示す側面図である。

【図23】本発明の一実施形態による電子装置のビアの他の構成を示す図である。

【発明を実施するための形態】

【0011】

次に、本発明に係る電子装置を実施するための形態の具体例を図面を参照しながら説明する。

【0012】

本明細書の実施形態及びここに用いる用語は、本明細書に記載した技術を特定の実施形態に対して限定しようとするものではなく、当該実施形態の多様な変更、均等物、及び／又は代替物を含むことで理解されなければならない。

図面の説明と関連して類似の構成要素に対しては類似の参照符号が用いられることができる。

単数の表現は文脈上、明白に意図しない限り、複数の表現を含むことができる。

本文書において、“A又はB”、“A及び／又はBのうちの少なくとも一つ”、“A、B又はC”又は“A、B及び／又はCのうちの少なくとも一つ”などの表現は、共に羅列された項目のすべての可能な組合を含むことができる。

“第1”、“第2”、“一番目”又は“二番目”などの表現は当該構成要素を、順序又は重要度に

40

構わずに修飾することができ、一つの構成要素を他の構成要素と区分するために用いられるだけ当該構成要素を限定しない。どんな（例えば、第1構成要素が異なる（例えば、第2構成要素に“（機能的又は通信的に）接続され”たり“接続されて”いると言及された時には、前記どんな構成要素が前記他の構成要素に直接的に接続されたり、他の構成要素（例えば、第3構成要素）を介して接続されることができる。

本明細書で用いられる用語“モジュール”は、ハードウェア、ソフトウェア又はファームウェアから構成されたユニットを含み、例えば、ロジック、論理ブロック、部品、又は回路などの用語と相互互換的に用いられることがある。モジュールは、一体から構成された部品又は一つ又はその以上の機能を実行する最小単位又はその一部となることができる。例えば、モジュールはASIC(application-specific integrated circuit)から構成することができる。10

多様な実施形態による構成要素（例えば、モジュール又はプログラム）それぞれは単数又は複数の個体から構成されることが可能、前述の当該サブ構成要素のうちの一部サブ構成要素が省略されたり、又は他のサブ構成要素が多様な実施形態にさらに含まれることができる。

追加的に、一部構成要素（例えば、モジュール又はプログラム）は、一つの個体に統合され、統合される以前のそれぞれの当該構成要素により行われる機能を同一又は類似に行うことができる。多様な実施形態による、モジュール、プログラム又は他の構成要素によって行われる動作は順次、並列的、繰り返し的又はヒューリスティックするように実行されたり、少なくとも一部動作が他の手順で実行されたり、省略されたり、又は他の動作が追加されることがある。20

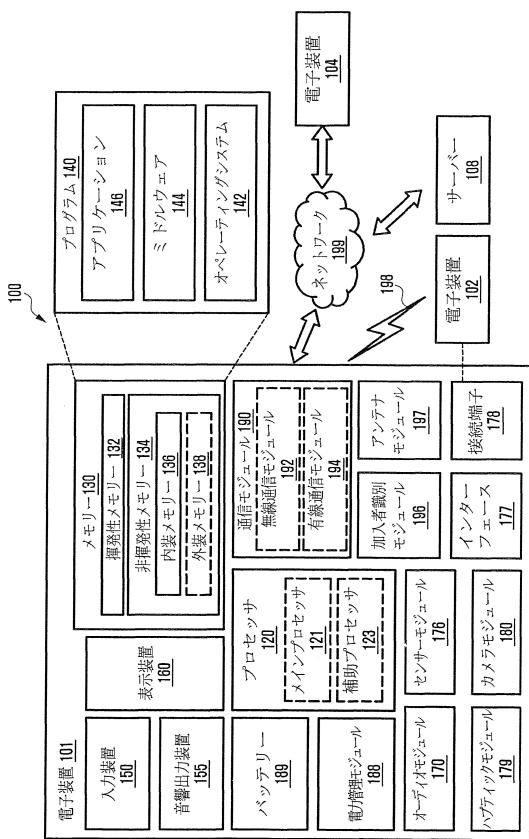

#### 【0013】

図1は、本発明の一実施形態によるネットワーク環境100内の電子装置101の構成を示すブロック図である。

図1を参照すると、ネットワーク環境100において電子装置101は、第1ネットワーク198（例えば、近距離無線通信）を介して電子装置102と通信するか、又は第2ネットワーク199（例えば、遠距離無線通信）を介して電子装置104又はサーバー108と通信することができる。

一実施形態によれば、電子装置101は、サーバー108を介して電子装置104と通信することができる。30

#### 【0014】

一実施形態によれば、電子装置101は、プロセッサ120、メモリー130、入力装置150、音響出力装置155、表示装置160、オーディオモジュール170、センサー・モジュール176、インターフェース177、ハプティックモジュール179、カメラモジュール180、電力管理モジュール188、バッテリー189、通信モジュール190、加入者識別モジュール196、及びアンテナモジュール197を含み得る。

他の実施形態では、電子装置101にはこの構成要素の内の少なくとも一つ（例えば、表示装置160又はカメラモジュール180を省略することや、他の構成要素が追加することができる。

また他の実施形態では、例えば、表示装置160（例えば、ディスプレイ）にエンベッディングされたセンサー・モジュール176（例えば、指紋センサー、虹彩センサー、又は照度センサー）の場合のように一部の構成要素が統合されて具現することができる。40

#### 【0015】

プロセッサ120は、例えば、ソフトウェア（例えば、プログラム140）を駆動してプロセッサ120に接続された電子装置101の少なくとも一つの他の構成要素（例えば、ハードウェア又はソフトウェア構成要素）を制御することができ、多様なデータ処理及び演算を行う。

プロセッサ120は、他の構成要素（例えば、センサー・モジュール176又は通信モジュール190）から受信した命令又はデータを揮発性メモリー132にロードして処理し、結果データを非揮発性メモリー134に記憶する。50

## 【0016】

一実施形態によれば、プロセッサ120は、メインプロセッサ121（例えば、中央処理装置又はアプリケーションプロセッサ）、及びこれとは独立的に操作され、追加的に、メインプロセッサ121より低電力で使用できたり、或いは指定された機能に特化された補助プロセッサ123（例えば、グラフィック処理装置、イメージシグナルプロセッサ、センサー用サブプロセッサ、又はコミュニケーションプロセッサ）を含むことができる。

ここで、補助プロセッサ123は、メインプロセッサ121と別個で、又はエンベッシングされて操作することができる。

## 【0017】

このような場合、補助プロセッサ123は、例えば、メインプロセッサ121がインアクティブ（例えば、スリップ）状態にあるうちにメインプロセッサ121の代わりに、又はメインプロセッサ121がアクティブ（例えば、アプリケーション実行）状態にあるうちにメインプロセッサ121と共に、電子装置101の構成要素の内の少なくとも一つの構成要素（例えば、表示装置160、センサーモジュール176、又は通信モジュール190）に係る機能又は状態の少なくとも一部を制御することができる。

一実施形態によれば、補助プロセッサ123（例えば、イメージシグナルプロセッサ又はコミュニケーションプロセッサ）は、機能的に関連ある他の構成要素（例えば、カメラモジュール180又は通信モジュール190）の一部構成要素として具現することができる。

## 【0018】

メモリー130は、電子装置101の少なくとも一つの構成要素（例えば、プロセッサ120又はセンサーモジュール176）によって用いられる多様なデータ、例えば、ソフトウェア（例えば、プログラム140）及び、これに関係する命令に対する入力データ又は出力データを記憶する。

メモリー130は、揮発性メモリー132又は非揮発性メモリー134を含むことができる。

## 【0019】

プログラム140は、メモリー130に記憶されるソフトウェアとして、例えば、オペレーティングシステム142、ミドルウェア144、又はアプリケーション146を含むことができる。

入力装置150は、電子装置101の構成要素（例えば、プロセッサ120に用いられる命令又はデータを電子装置101の外部（例えば、ユーザ）から受信するための装置として、例えば、マイク、マウス、又はキーボードを含むことができる。

音響出力装置155は、音響信号を電子装置101の外部で出力するための装置として、例えば、マルチメディア再生又は録音再生のように一般的な用途で用いられるスピーカーと電話受信専用で用いられるレシーバーを含むことができる。

一実施形態によれば、レシーバーは、スピーカーと一体又は別途に形成することができる。

## 【0020】

表示装置160は、電子装置101のユーザに情報を視覚的に提供するための装置として、例えば、ディスプレイ、ホログラム装置、又はプロジェクター及び当該装置を制御するための制御回路を含み得る。

一実施形態によれば、表示装置160は、タッチ回路（touch circuitry）又はタッチに対する圧力の強度を測定することができる圧力センサーを含むことができる。

オーディオモジュール170は、音と電気信号を双方向で変換させることができる。

一実施形態によれば、オーディオモジュール170は、入力装置150を介して音を取得したり、音響出力装置155、又は電子装置101と有線又は無線で接続された外部電子装置（例えば、電子装置102（例えば、スピーカー又はヘッドフォン））を介して音を出力することができる。

10

20

30

40

50

**【0021】**

センサーモジュール176は、電子装置101の内部の動作状態（例えば、電力又は温度）、又は外部の環境状態に対応する電気信号又はデータ値を生成する。

センサーモジュール176は、例えば、ジェスチャーセンサー、ジャイロセンサー、気圧センサー、マグネットックセンサー、加速度センサー、グリップセンサー、近接センサー、カラーセンサー、IR (infrared) センサー、生体センサー、温度センサー、湿度センサー、又は照度センサーを含むことができる。

**【0022】**

インターフェース177は、外部電子装置（例えば、電子装置102）と有線又は無線で接続することができる指定されたプロトコルをサポートする。

一実施形態によれば、インターフェース177は、HDMI（登録商標）(high definition multimedia interface)、USB (universal serial bus) インターフェース、SDカードインターフェース、又はオーディオインターフェースを含むことができる。

**【0023】**

接続端子178は、電子装置101と外部電子装置（例えば、電子装置102）を物理的に接続させることができるコネクタ、例えば、HDMI（登録商標）コネクタ、USBコネクタ、SDカードコネクタ、又はオーディオコネクタ（例えば、ヘッドフォンコネクタ）を含むことができる。

**【0024】**

ハブティックモジュール179は、電気的信号をユーザが触覚又は運動感覚を介して認知できるようにする機械的な刺激（例えば、振動又は動き）又は電気的な刺激に変換する。

ハブティックモジュール179は、例えば、モーター、圧電素子、又は電気刺激装置を含むことができる。

カメラモジュール180は、静止画像及び動画を撮影することができる。

一実施形態によれば、カメラモジュール180は、一つ以上のレンズ、イメージセンサー、イメージシグナルプロセッサ、又はフラッシュを含むことができる。

**【0025】**

電力管理モジュール188は、電子装置101に供給される電力を管理するためのモジュールであり、例えば、PMIC (power management integrated circuit) の少なくとも一部として構成され得る。

バッテリー189は、電子装置101の少なくとも一つの構成要素に電力を供給するための装置であり、例えば、再充電不可能な1次電池、再充電可能な2次電池、又は燃料電池を含むことができる。

**【0026】**

通信モジュール190は、電子装置101と外部電子装置（例えば、電子装置102、電子装置104、又はサーバー108）の間の有線又は無線通信チャンネルの確立、及び確立された通信チャンネルを通じての通信の実行をサポートする。

通信モジュール190は、プロセッサ120（例えば、アプリケーションプロセッサ）と独立的に操作される、有線通信又は無線通信をサポートする一つ以上のコミュニケーションプロセッサを含むことができる。

**【0027】**

一実施形態によれば、通信モジュール190は、無線通信モジュール192（例えば、セルラー通信モジュール、近距離無線通信モジュール、又はGNSS (global navigation satellite system) 通信モジュール）又は有線通信モジュール194（例えば、LAN (local area network) 通信モジュール、又は電力線通信モジュール）を含み、その中に該当する通信モジュールを用いて第1ネットワーク198（例えば、ブルートゥース（登録商標）、Wi-Fi direct（登録商標）又はIrDA (infrared data association) のような近距離通信ネットワーク）又は第2ネットワーク199（例えば、セルラネットワーク

10

20

30

40

50

、インターネット、又はコンピューターネットワーク（例えば、L A N 又はW A N ）のような遠距離通信ネットワーク）を介して外部電子装置と通信することができる。

【 0 0 2 8 】

上述した多くの種類の通信モジュール 1 9 0 は一つのチップで具現するか、又はそれぞれ別途のチップで具現することができる。

一実施形態によれば、無線通信モジュール 1 9 2 は、加入者識別モジュール 1 9 6 に記憶されたユーザ情報を用いて通信ネットワーク内で電子装置 1 0 1 を区別及び認証することができる。

【 0 0 2 9 】

アンテナモジュール 1 9 7 は、信号又は電力を外部に送信したり、外部から受信するための一つ以上のアンテナを含む。

一実施形態によれば、通信モジュール 1 9 0 （例えば、無線通信モジュール 1 9 2 ）は、通信方式に適合したアンテナを介して信号を外部電子装置で送信したり、外部電子装置から受信することができる。

【 0 0 3 0 】

上記構成要素のうちの一部構成要素は、周辺機器の間の通信方式（例えば、バス、G P I O ( g e n e r a l p u r p o s e i n p u t / o u t p u t ) 、S P I ( s e r i a l p e r i p h e r a l i n t e r f a c e ) 、又はM I P I ( m o b i l e i n d u s t r y p r o c e s s o r i n t e r f a c e ) ）を介して互いに接続されて信号（例えば、命令又はデータ）を相互間に交換することができる。

【 0 0 3 1 】

一実施形態によれば、命令又はデータは、第 2 ネットワーク 1 9 9 に接続されたサーバー 1 0 8 を介して電子装置 1 0 1 と外部の電子装置 1 0 4 の間に送信又は受信することができる。

電子装置（ 1 0 2 、 1 0 4 ）それぞれは、電子装置 1 0 1 と同一又は他の種類の装置であっても良い。

一実施形態によれば、電子装置 1 0 1 で実行される動作の全部又は一部は、他の一つ又は複数の外部電子装置で実行することができる。

【 0 0 3 2 】

一実施形態によれば、電子装置 1 0 1 がある機能やサービスを自動に、又はリクエストにより実行しなければならない場合に、電子装置 1 0 1 は、機能又はサービスを自身が実行する代りに、又は追加的にそれと関連した少なくとも一部機能を外部電子装置にリクエストすることができる。

リクエストを受信した外部電子装置は、リクエストされた機能又は追加機能を実行し、その結果を電子装置 1 0 1 へ伝達することができる。

電子装置 1 0 1 は、受信した結果をそのまま、又は追加的に処理してリクエストされた機能やサービスを提供することができる。

このため、例えば、クラウドコンピュータ、分散コンピュータ、又はクライアント - サーバーコンピュータ技術などを用いることができる。

【 0 0 3 3 】

本明細書で開示した多様な実施形態による電子装置は、多様な形態の装置となることができる。

電子装置は、例えば、ポータブル通信装置（例えば、スマートフォン）、コンピューター装置、ポータブルマルチメディア装置、ポータブル医療機器、カメラ、ウェアラブル装置、又は家電装置の内の少なくとも一つを含むことができる。

本実施形態による電子装置は、前述した機器で限定されない。

【 0 0 3 4 】

本明細書の多様な実施形態は、機器（ m a c h i n e ）（例えば、コンピューター）で読み取り可能な記憶媒体（ m a c h i n e - r e a d a b l e s t o r a g e m e d i a ）（例えば、内装メモリー 1 3 6 又は外装メモリー 1 3 8 ）に記憶された命令語を含む

10

20

30

40

50

ソフトウェア（例えば、プログラム 140）で具現されることがある。

機器は、記憶媒体から記憶された命令語を呼び出し、呼び出しされた命令語によって動作が可能な装置として、開示された実施形態による電子装置（例えば、電子装置 101 を含むことができる。

命令がプロセッサ（例えば、プロセッサ 120）によって実行される場合、プロセッサが直接、又はプロセッサの制御下に他の構成要素を用いて命令に該当する機能を行うことができる。

命令は、コンパイラー又はインタプリターによって生成又は実行されるコードを含むことができる。

機器で読み取り可能な記憶媒体は、非一時的（non-transitory）記憶媒体の形態で提供されることがある。ここで、「非一時的」は記憶媒体が信号（signal）を含ませず実在（angible）するということを意味するだけ、データが記憶媒体に半永久的又は臨時的に記憶されることを区分しない。10

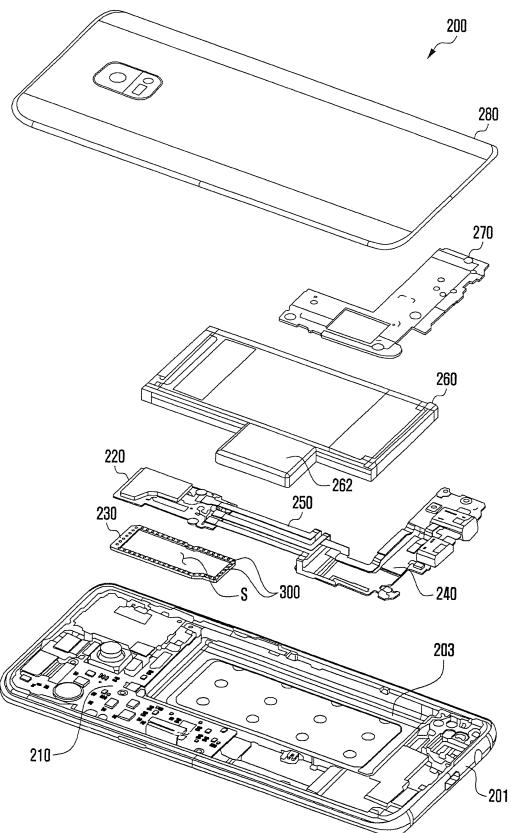

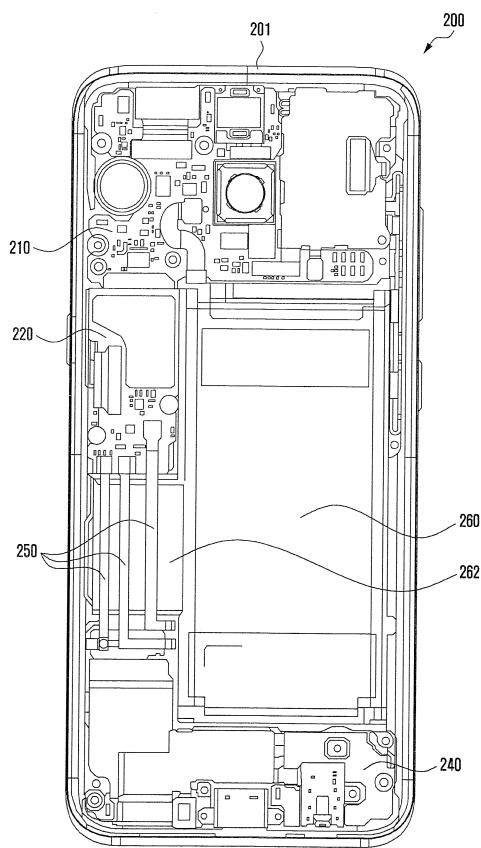

#### 【0035】

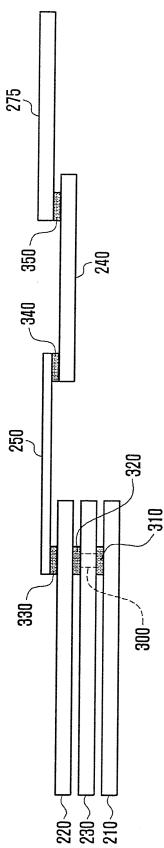

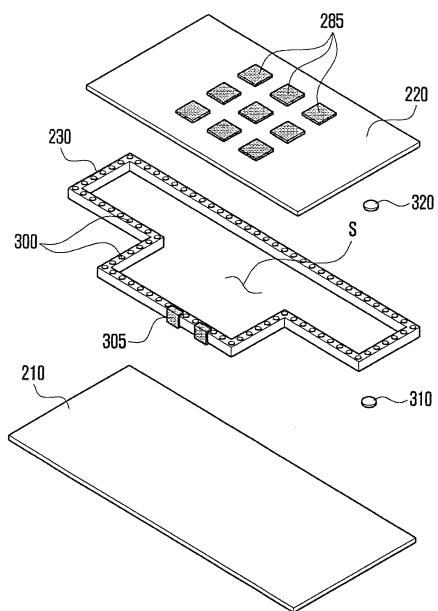

図 2 は、本発明の一実施形態による電子装置の一部構成に対する分解斜視図であり、図 3 は、本発明の一実施形態による電子装置の一部構成に対する組立結合図である。

図 2 及び図 3 を参照すると、本発明の一実施形態による電子装置 200 は、ハウジング 201、第 1 回路基板 210、第 2 回路基板 220、インタポーザ 230、第 3 回路基板 240、コネクタ 250、第 1 バッテリー 260、第 2 バッテリー 262、アンテナモジュール 270、及び後面カバー 280 を含む。20

#### 【0036】

実施形態によれば、電子装置 200 は、図 1 の電子装置（101、102、104 の内の少なくとも一つ）を含み得る。

第 1 バッテリー 260 及び第 2 バッテリー 262 は、図 1 のバッテリー 189 を含み得る。

アンテナモジュール 270 は、図 1 のアンテナモジュール 197 を含み得る。

後面カバー 280 は、図 1 の電子装置 101 の後面に備えられる。

第 1 回路基板 210、第 2 回路基板 220、及び第 3 回路基板 240 は、それぞれ、異なる構成要素と電気的に接続するための少なくとも一つの接続端子（例えば、コネクタ）を含む。30

第 1 回路基板 210、第 2 回路基板 220、及び第 3 回路基板 240 は、それぞれ PCB (printed circuit board)、PBA (printed board assembly) 及び FPCB (flexible printed circuit board)などを含み得る。

#### 【0037】

ハウジング 201 は、上述した電子装置 200 内の構成要素である、第 1 回路基板 210、第 2 回路基板 220、インタポーザ 230、第 3 回路基板 240、コネクタ 250、第 1 バッテリー 260、第 2 バッテリー 262、アンテナモジュール 270、及び後面カバー 280 を収容するように側面ベッセル構造から構成され得る。

ハウジング 201 の外部露出面の少なくとも一部は、導電性物質（例えば、金属）から構成することができる。40

ハウジング 201 の外部露出面の少なくとも一部は、電子装置 200 のアンテナで用いることができる。

#### 【0038】

一実施形態によれば、ハウジング 201 は、内部に支持部材 203（例えば、プラケット）を含むことができる。

支持部材 203 は、電子装置 200 内の構成要素を内部に収容して支持することができる。

支持部材 203 は、ハウジング 201 の一面に一体で形成することができる。

支持部材 203 は、例えば、金属材質及び／又は非金属（例えば、ポリマー）材質で形

10

20

30

40

50

成することができる。

【0039】

第1回路基板210は、ハウジング201の少なくとも一部に配置され得る。

第1回路基板210は、電子装置200の操作に必要なプロセッサ（例えば、図1のプロセッサ120）、メモリー（例えば、図1のメモリー130）、通信回路（例えば、図1の通信モジュール190）、電力管理モジュール（例えば、図1の電力管理モジュール188）及び／又はインターフェース（例えば、図1のインターフェース177）を含み得る。

【0040】

一実施形態によれば、プロセッサ（例えば、図1のプロセッサ120）は、例えば、中央処理処置、アプリケーションプロセッサ（application processor：A P）（例えば、図6のアプリケーションプロセッサ212）、コールプロセッサ（call processor：C P）（例えば、図6のコールプロセッサ214）、グラフィック処理処置、イメージシグナルプロセッサ、センサー用サブプロセッサ、又はコミュニケーションプロセッサの内の一つ又はその以上を含むことができる。

10

【0041】

メモリー（例えば、図1のメモリー130）は、例えば、揮発性メモリー又は非揮発性メモリーを含むことができる。

通信回路（例えば、図1の通信モジュール190）は、例えば、無線通信モジュール（例えば、図1の無線通信モジュール192）又は有線通信モジュール（例えば、図1の有線通信モジュール194）を含むことができる。

20

インターフェース（例えば、図1のインターフェース177）は、例えば、HDMI（登録商標）（high definition multimedia interface）、USB（universal serial bus）インターフェース、SDカードインターフェース、及び／又はオーディオインターフェースを含むことができる。

インターフェースは、例えば、電子装置200を外部電子装置（例えば、図1の電子装置102）と電気的又は物理的に接続させることができ、USBコネクタ、SDカード/MMCコネクタ、又はオーディオコネクタを含み得る。

【0042】

第2回路基板220は、インタポーラ230を介して第1回路基板210上に積層され得る。

30

第2回路基板220は、トランシーバ（transceiver）（例えば、図6のトランシーバ221）又はコールプロセッサ（例えば、図6のコールプロセッサ214）とトランシーバが統合されている無線通信モジュール（例えば、Wi-Fiモジュール（wi-fi module））を含むことができる。

インタポーラ230は、第1回路基板210と第2回路基板220との間に配置される。

インタポーラ230は、第1回路基板210又は第2回路基板220に実装された少なくとも一つの部品（例えば、図6のアプリケーションプロセッサ212、コールプロセッサ214、トランシーバ221又はWi-Fiモジュール）が配置される空間（S）を含む。

インタポーラ230は、第1回路基板210及び第2回路基板220を電気的に接続するための少なくとも一つのビア300を含み得る。

40

【0043】

第3回路基板240は、信号又は電力を外部に送信したり外部から受信するための少なくとも一つのアンテナ（例えば、図4のアンテナ275）又はアンテナと接続される接続端子をさらに含むことができる。

コネクタ250は、第1回路基板210、第2回路基板220、及び第3回路基板240を電気的に接続する。

【0044】

第1バッテリー260（例えば、図1のバッテリー189）は、電子装置200の少なくとも一つの構成要素に電力を供給する。

50

第2バッテリー262は、電子装置200の少なくとも一つの構成要素に電力を供給することができる。

第2バッテリー262は、第1バッテリー260の容量を増加させた補助バッテリーであっても良い。

第2バッテリー262は、インタポーザ230を介して第1回路基板210及び第2回路基板220を積層させることによって確保された空間に配置される。

#### 【0045】

一実施形態によれば、第2バッテリー262は、第2回路基板220と第3回路基板240との間に配置されることもできる。

一実施形態によれば、コネクタ250は、第2回路基板220と第3回路基板240を電気的に接続し、第1バッテリー260又は第2バッテリー262の上部、下部、又は側面の内の少なくとも一つに配置される。

一実施形態によれば、第1バッテリー260及び第2バッテリー262は、例えば、再充電不可能な1次電池、又は再充電可能な2次電池、又は燃料電池を含むことができる。

#### 【0046】

第1バッテリー260及び第2バッテリー262は、電子装置200のハウジング201内部に一体に配置することができ、電子装置200のハウジング201と脱着/付着可能に配置することもできる。

第1バッテリー260及び第2バッテリー262は、一つのパック(pack)から構成することもできる。

第1バッテリー260及び第2バッテリー262は、それぞれ、第1バッテリー260及び第2バッテリー262それぞれの容量を把握する互いに異なる燃料ゲージ(fuel gauge)を含むことができ、さらに、互いに異なる充電器(charger)を用いることができる。

このようなことにより、サイズが互いに異なるバッテリーを効率的に管理することができる。

第1バッテリー260及び第2バッテリー262は、一つのセル(cell)から構成することもできる。

#### 【0047】

アンテナモジュール270は、第3回路基板240及び後面カバー280の間に配置される。

アンテナモジュール270(例えば、図1のアンテナモジュール197)は第3回路基板240に接続される。

アンテナモジュール270は、図4に示したアンテナ275を含むことができる。

第3回路基板240は、アンテナモジュール270と接続される接続端子を含むことができる。

一実施形態によれば、アンテナモジュール270は、例えば、外部装置と通信をしたり、充電に必要な電力を無線で送受信することができる。

他の実施形態によれば、ハウジング201の一部露出面及び/又は支持部材203の一部又はその組み合わせによってアンテナ構造が形成することができる。

後面カバー280は、電子装置200(例えば、図1の電子装置101)の後面を保護するカバーであれば良い。

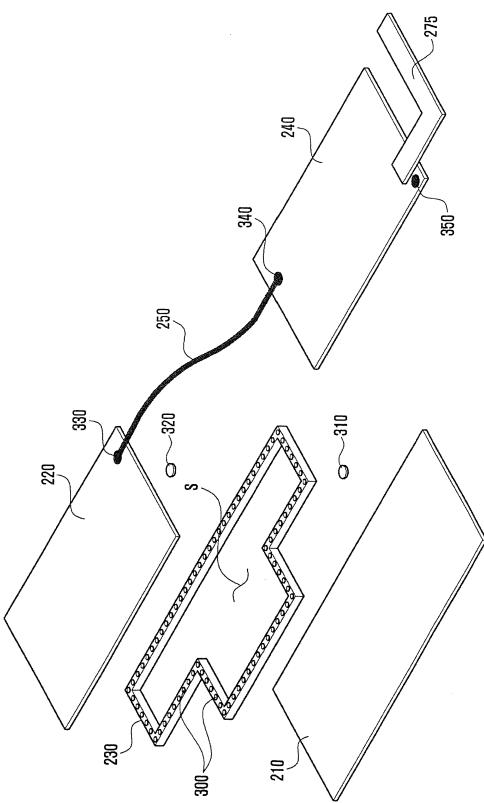

#### 【0048】

図4は、本発明の一実施形態による電子装置の第1回路基板、第2回路基板、第3回路基板の接続関係を概略的に示す斜視図であり、図5は、本発明の一実施形態による電子装置の第1回路基板、第2回路基板、第3回路基板の接続関係を概略的に示す側面図である。

図4及び図5を参照すると、本発明の一実施形態による電子装置200は、第1回路基板210、第2回路基板220、インタポーザ230、及び第3回路基板240を含む。

#### 【0049】

第1回路基板210には通信回路(例えば、図1の通信モジュール190)が配置され

10

20

30

40

50

る。

通信回路は、例えば、アプリケーションプロセッサ(application processor: AP) (例えば、図6のアプリケーションプロセッサ212) 及びコールプロセッサ(call processor: CP) (例えば、図6のコールプロセッサ214)などを含むことができる。

第1回路基板210は、第1面(例えば、上部)に通信回路の出力と電気的に接続される第1接続端子310が形成される。

#### 【0050】

第2回路基板220は、例えば、トランシーバ(例えば、図6のトランシーバ221)又はWi-Fiモジュール(wifi module)を含むことができる。

第2回路基板220は、第1面(例えば、下部)に第2接続端子320が配置され、第2面(例えば、上部)に第3接続端子330が配置される。

第2接続端子320は、第2回路基板220に実装された部品(例えば、通信回路など)と電気的に接続(例えば、デジタル信号)される。

第3接続端子330は、第3回路基板240に形成された第4接続端子340と電気的に接続(例えば、アナログ信号)される。

#### 【0051】

一実施形態によれば、第3接続端子330は第1回路基板210に形成された第1接続端子310以外の他の接続端子(例えば、第6接続端子(図示せず))を介して第1回路基板210と接続され得る。

一実施形態によれば、コネクタ250と接続される第3接続端子330は、第1回路基板210に配置される。

これを介して、電子装置200の落下時、後面カバー280がコネクタ250のヘッド(head)に衝撃を加えた後、インタポーラ230が押されて破損してしまうことを防止することができる。

#### 【0052】

第3接続端子330は、第1回路基板210に形成された第1接続端子310以外の他の接続部材を介して第1回路基板210と電気的に接続され、第2回路基板220からインタポーラ230を介して第1回路基板210に損失無しで信号が伝達され得る。

一実施形態によれば、インピーダンスマッチングのためにインタポーラ230は第1回路基板210及び第2回路基板220と異なる誘電率を持つことができる。

一実施形態によれば、第2回路基板220は第2接続端子320がビア300の第2端部(例えば、上部)と電気的に接続され、第1回路基板210及びインタポーラ230と共に内部空間(S)を形成するように第1面(例えば、下部面)と反対方向のインタポーラ230の第2面(例えば、上部面)に付着される。

#### 【0053】

インタポーラ230は、第1回路基板210と第2回路基板220との間に配置される。

インタポーラ230は、第1回路基板210又は第2回路基板220に実装された少なくとも一つの部品(例えば、図6のアプリケーションプロセッサ212)、コールプロセッサ214、トランシーバ221、又はWi-Fiモジュールが配置される空間(S)を持つ。

インタポーラ230は、長方形又はそれ以外の他の多様な形態で構成することができる。

インタポーラ230は、第1回路基板210の第1面(例えば、上部面)に形成された第1接続端子310と第2回路基板220の第1面(例えば、下部面)に形成された第2接続端子320を電気的に接続するための少なくとも一つのビア300を含む。

一実施形態によれば、インタポーラ230は、第1回路基板210の少なくとも一部領域を少なくとも一部取り囲み、ビア300の第1端部(例えば、下部)が第1接続端子310と電気的に接続されるように第1面(例えば、下部面)が第1回路基板210に付着される。

#### 【0054】

10

20

30

40

50

第3回路基板240は、第1側に第4接続端子340が配置され、第2側に第5接続端子350が配置される。

第4接続端子340及び第5接続端子350は電気的に接続され得る。

第3回路基板240に形成された第5接続端子350はアンテナ275（例えば、図1のアンテナモジュール197）と電気的に接続することができる。

一実施形態によれば、第3接続端子330は第2回路基板220上に配置されることで説明したが、第3接続端子330は第1回路基板210に第6接続端子（図示せず）として配置することもできる。

第6接続端子が第1回路基板210に配置される場合、第6接続端子は第3回路基板240に形成された第4接続端子340とコネクタ250を介して電気的に接続される。

コネクタ250は、F P C B *type*、coaxial *type*、connecto r *type*などのR F信号をシールディングして回路基板を接続する接続部材であれば良い。

#### 【0055】

第2回路基板220の第2面（例えば、上部）に形成された第3接続端子330及び第3回路基板240の第1側に形成された第4接続端子340は、コネクタ250を介して電気的に接続され得る。

一実施形態によれば、第3接続端子330は、第2回路基板220に形成されることは限定されない。

例えば、第3接続端子330は、インタポーラ230に形成されたビア300のサイズ及び/又は誘電率などの変更を通じるインピーダンスマッチングを介して損失（loss）を最小化することができれば、第1回路基板210上に配置されることもできる。

#### 【0056】

一実施形態によれば、第1回路基板210は、第2回路基板220のトランシーバを介して受信したインフェーズ（in phase）信号及びクワドラチャ（quadrature）信号を復号化してデータ（raw data）を抽出することができる。

第2回路基板220は、R F（radio frequency）バンドを分離してキャリア（carrier）周波数信号を含むアナログデータを処理することができる。

インタポーラ230は、キャリア周波数信号を含まないベースバンド（baseband）信号を第1回路基板210に伝達することができる。

インタポーラ230は、インフェーズ（in phase）信号及びクワドラチャ（quadrature）信号が含まれたデジタル信号を処理することができる。

コネクタ250は、R F（radio frequency）バンドが分離されたアナログ信号を、第2回路基板220に形成された第3接続端子330を介して第3回路基板240の第4接続端子340に伝達することができる。

#### 【0057】

一実施形態によれば、第1回路基板210は、R F（radio frequency）バンドに係るデジタル信号を、インタポーラ230を介して第2回路基板220に伝達することができる。

第2回路基板220は、R F（radio frequency）バンドの損失（loss）を最小化するため、第1回路基板310ではない、アンテナ275が接続された第3回路基板240でR F（radio frequency）バンドに係るデジタル信号を伝達することができる。

一実施形態によれば、アンテナ275と電気的に接続されたR Fバンドが分離されたアナログ信号は、インタポーラ230を介して第1回路基板210に伝達する。

インタポーラ230は、R Fバンドが分離されたアナログ信号の損失を最小化するためのインピーダンスマッチングのために誘電率又はビア300のサイズを調整することができる。

この場合、インタポーラ230からのアナログ信号は、第1回路基板210で伝達する。

この伝達したアナログ信号は、第1回路基板210上のまた他の接続端子を介して第3

10

20

30

40

50

回路基板 240 の第 4 接続端子へ伝達する。

【0058】

一実施形態によれば、RF バンドが分離されたアナログ信号をインピーダンスマッチングした後、損失なしに第 1 回路基板 210 に伝達するため、インタポーラ 230 に形成されたピア 300 はコネクタ 250 で模写してインピーダンスを計算することができる。

コネクタ 250 のインピーダンス算式は、以下に示す数式 1 の通りである。

【数 1】

$$Z_0 = \frac{138}{\sqrt{k}} \log \frac{d_1}{d_2} \quad \dots \text{数式 1}$$

10

ここで、 $Z_0$  はインピーダンスで、 $d_1$  はピア 300 を取り囲むシールドパターンの内径であり、 $d_2$  はピア 300 の外径であり、 $k$  は比誘電率である。

【0059】

例えば、ピア 300 を 0.4 p h i で通す場合、コネクタ 250 のインピーダンス ( $Z_0$ ) は 26.18 である一方、ピア 300 を 0.2 p h i で通す場合、コネクタ 250 のインピーダンス ( $Z_0$ ) は 46 であれば良い（例えば、第 1 回路基板 210 の「 $r = 4.4$ 」 $d_1$  は  $d_2$  に比べて 1 p h i である場合、インピーダンス値）。

20

この時、ピア 300 を 0.4 p h i で通す場合の誘電率を変更してコネクタ 250 のインピーダンス ( $Z_0$ ) を 50 に近接するように調整することができる。

【0060】

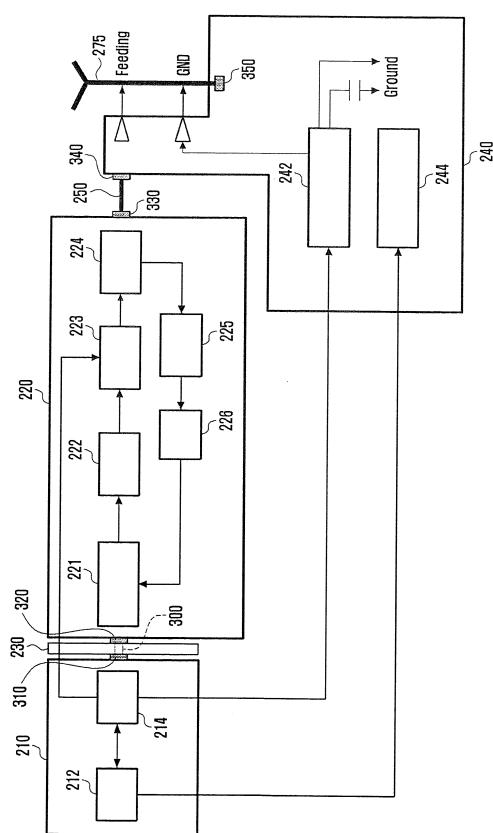

図 6 は、本発明の一実施形態による電子装置の第 1 回路基板、第 2 回路基板、第 3 回路基板の構成及び接続関係を概略的に示すブロック図である。

図 6 を参照すると、本発明の一実施形態による電子装置 200 は、第 1 回路基板 210 、第 2 回路基板 220 、インタポーラ 230 、及び第 3 回路基板 240 を含む。

第 1 回路基板 210 は、例えば、アプリケーションプロセッサ (212、AP) 及びコール (プロセッサ 214、CP) を含むことができる。

30

第 1 回路基板 210 は、第 1 面に第 1 接続端子 310 を含む。

【0061】

一実施形態によれば、アプリケーションプロセッサ 212 は、電子装置 200 の操作に必要な構成要素（例えば、図 1 のプロセッサ 120、メモリー 130、通信モジュール 190、及び電力管理モジュール 188 など）の機能を制御することができる。

コールプロセッサ 214 は、電子装置 200 の通信プロトコルに関する信号を変調 (modulation) 及び復調 (demodulation) することができる。

第 2 回路基板 220 は、例えば、トランシーバ 221、第 1 フィルター 222、電力増幅器 223、スイッチ 224、第 2 フィルター 225、及び低雑音増幅器 226 を含むことができる。

第 2 回路基板 220 は、第 1 面に第 2 接続端子 320 が配置され、第 2 面に第 3 接続端子 330 が配置される。

40

第 2 接続端子 320 と第 3 接続端子 330 は、他の部品を介して電気的に接続される。

【0062】

一実施形態によれば、トランシーバ 221 は、第 1 回路基板 210 のコールプロセッサ 214 を介して変調された信号とキャリア周波数信号とをミキサーを介してミキシングして送信 (Tx) したり、受信 (Rx) した復調信号をキャリア周波数信号と分離して変調することができる。

第 1 フィルター 222 は、トランシーバ 221 から伝達された信号をマッチングしたり、キャリア周波数信号でノイズ信号をフィルタリングすることができる。

50

電力増幅器 223 は、第1フィルター 222 を介してフィルタリングされた送信 (T x) 信号の電流利得が増加するように増幅する。

スイッチ 224 は、送信 (T x) 信号又は受信 (R x) 信号の経路を分離する。

#### 【0063】

第2フィルター 225 は、スイッチ 224 を介して伝達された受信 (R x) 信号からノイズ信号をフィルタリングする。

低雑音増幅器 226 は、例えば、第2フィルター 225 を介して伝達された受信 (R x) 信号を増幅し、この増幅された信号をトランシーバ 221 に伝達する。

インタポーラ 230 は、第1回路基板 210 と第2回路基板 220 との間に配置される。

インタポーラ 230 は、第1回路基板 210 の第1面に形成された第1接続端子 310 と第2回路基板 220 の第1面に形成された第2接続端子 320 とを電気的に接続するためのピア 300 を含み得る。

#### 【0064】

第3回路基板 240 は、第1回路基板 210 に実装されたコールプロセッサ 214 を介して制御されるマッチングスイッチ 242、及びアプリケーションプロセッサ 212 を介して制御されるホール IC (244) を含むことができる。

一実施形態によれば、第1回路基板 210 に実装されたアプリケーションプロセッサ 212 及びコールプロセッサ 214 による制御信号は、第1回路基板 210 と第3回路基板 240 を電気的に接続する別途の接続部材 (例えば、コネクタ FPCB) で伝達することができる。

第3回路基板 240 は、第1側に第4接続端子 340 が配置され、第2側に第5接続端子 350 が配置される。

第4接続端子 340 と第5接続端子 350 とは電気的に接続される。

第3回路基板 240 に形成された第5接続端子 350 はアンテナ 275 と電気的に接続される。

#### 【0065】

一実施形態によれば、マッチングスイッチ 242 は、第3回路基板 240 の第5接続端子 350 に接続されたアンテナ 275 のグラウンド (GND) 又は供給 (feeding) のマッチングを調節することができる。

ホール IC (244) は、例えば、カバーがあるモバイル端末機 (例えば、フォルダフオン) の開放又は閉鎖を認識する。

アンテナ 275 は、特定波長に対する送信 (T x) 信号及び受信 (R x) 信号を送受信する。

一実施形態によれば、第2回路基板 220 の第2面に形成された第3接続端子 330 と第3回路基板 240 の第1側に形成された第4接続端子 340 とは、コネクタ 250 を介して電気的に接続され得る。

#### 【0066】

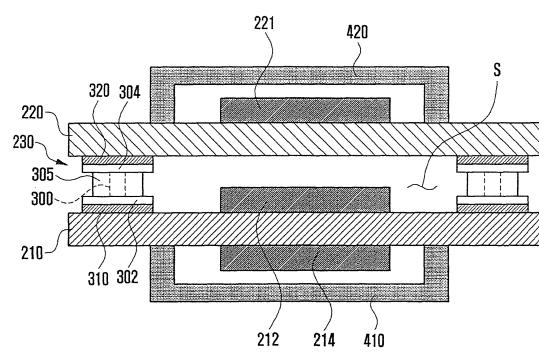

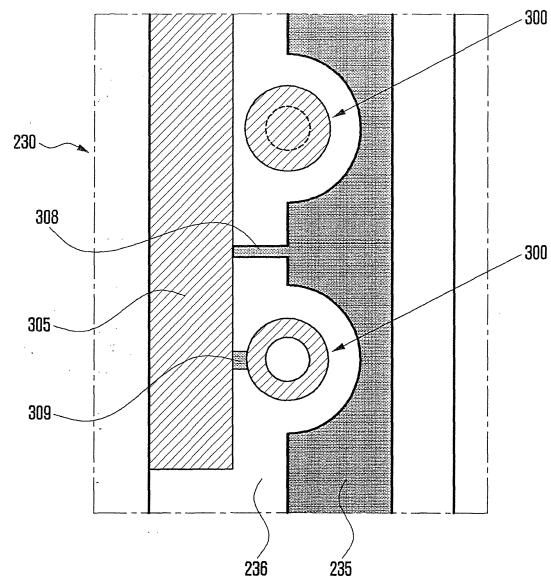

図7は、本発明の一実施形態による電子装置の第1回路基板及び第2回路基板に対する他の構成を示す断面図である。

図7を参照すると、本発明の一実施形態による電子装置 200 は、第1回路基板 210 、第2回路基板 220 、インタポーラ 230 、第1シールド部材 410 、及び第2シールド部材 420 を含む。

#### 【0067】

第1回路基板 210 の下部には、例えば、アプリケーションプロセッサ 212 が実装され得る。

第1回路基板 210 の下部に実装されたアプリケーションプロセッサ 212 の外部には第1シールド部材 410 が配置される。

第1シールド部材 410 は、例えば、電子装置 200 の第1回路基板 210 から出力されるノイズ信号を遮断し、電子装置 200 の外部から入力されるノイズを遮断する。

第1シールド部材 410 は、シールドカン (shield can) 又はEMI (e1

electromagnetic interference) モールディング部材であれば良い。

【0068】

第1回路基板210の上部には、例えば、コールプロセッサ214が実装され得る。

第1回路基板210の上部に実装されたコールプロセッサ214は、インタポーラ230内の部品実装空間(S)内に配置される。

第1回路基板210の第1面(例えば、上部)には第1接続端子310が配置される。

第2回路基板220の第1面(例えば、下部)には第2接続端子320が配置される。

一実施形態によれば、インタポーラ230は、ビア300、第1パッド302、第2パッド304、及び側面メッキ部材305を含む。

ビア300は、第1回路基板210に形成された第1接続端子310と第2回路基板220に形成された第2接続端子320とを電気的に接続する。

ビア300は、スルービア(through via)又はスタックビア(stack ed via)を含む。

【0069】

第1パッド302は、ビア300の下部に形成され、第1回路基板210の第1接続端子310と電気的に接続される。

第2パッド304は、ビア300の上部に形成され、第2回路基板220の第2接続端子320と電気的に接続される。

側面メッキ部材305は、ビア300の外側に備えることができる。

側面メッキ部材305は、第1回路基板210と第2回路基板220を結合(例えば、第1回路基板210又は第2回路基板220と電気的に接続される場合)したり、支持(例えば、第1回路基板210又は第2回路基板220と電気的に接続されない場合)することができる。

側面メッキ部材305は、選択的に用いることができる。

【0070】

第2回路基板220の上部には、例えば、トランシーバ221が実装され得る。

第2回路基板220の上部に実装されたトランシーバ221の外部には第2シールド部材420が配置される。

第2シールド部材420は、例えば、電子装置200の第2回路基板220から出力されるノイズ信号を遮断し、電子装置200の外部から入力されるノイズを遮断する。

第2シールド部材420は、シールドカン又はEMI(electromagnetic interference)モールディング部材あれば良い。

【0071】

一実施形態によれば、第1シールド部材410及び第2シールド部材420のEMIモールディング部材は次のような工程を経て第1回路基板210及び第2回路基板220にそれぞれ結合される。

第1工程において、第1回路基板210の下部の少なくとも一部及び第2回路基板220の上部の少なくとも一部にシールド用パッドを形成する。

第2工程において、第1回路基板210の下部の少なくとも一部及び第2回路基板220の上部の少なくとも一部に形成されたシールド用パッド上に第1シールド部材410及び第2シールド部材420を実装する。

第3工程において、第2工程を通じて第1シールド部材410及び第2シールド部材420の実装後、非導電モールディング液(例えば、エポキシモールドコンパウンド(epoxy molding compound; EMC)など)を塗布する。

第4工程において、第1シールド部材410及び第2シールド部材420が実装されたシールド用パッド近辺に塗布された、非導電モールディング液をレーザーを介して食刻する。

第5工程において、シールド用パッド及び非導電モールディング液に導電性金属をスパッタリング(sputtering)する。

10

20

30

40

50

## 【0072】

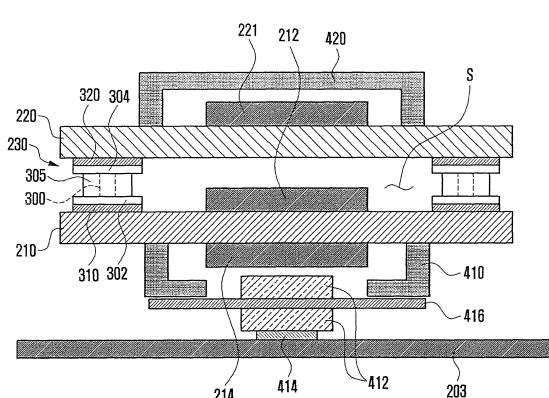

図8は、本発明の一実施形態による電子装置の第1回路基板及び第2回路基板に対するまた他の構成を示す断面図である。

図8を参照すると、本発明の一実施形態による電子装置200は、第1回路基板210、第2回路基板220、インタポーラ230、第1シールド部材410、ティム412、放熱部材414、銅シート416、及び第2シールド部材420を含む。

## 【0073】

第1回路基板210の下部には、例えば、アプリケーションプロセッサ212が実装され得る。

第1回路基板210の下部に実装されたアプリケーションプロセッサ212の外部には

10 第1シールド部材410が配置される。

第1シールド部材410は、例えば、電子装置200の第1回路基板210から出力されるノイズ信号を遮断し、電子装置200の外部から入力されるノイズを遮断する。

第1シールド部材410は、シールドカン又はEMI (electromagnetic interference) モールディング部材であれば良い。

## 【0074】

一実施形態によれば、第1シールド部材410の少なくとも一部は、開放され得る。

ティム(Thermal Interface Material: TIM)412は、第1段がアプリケーションプロセッサ212に隣接するように配置され、第2段が第1シールド部材410の開放された部分を貫いて配置される。

ティム412は、例えば、電子装置200のコールプロセッサ214から発生する熱を放熱部材414へ伝達する役目を行う。

例えば、ティム412は、熱伝達係数が大きい物質から構成され得る。

## 【0075】

銅シート416は、ティム412の第1段と第2段の間に配置される。

銅シート416は、第1シールド部材410の開放された部分を閉鎖することができる。

銅シート416は、電子装置200の内部で発生するノイズを遮断することができる。

放熱部材414は、支持部材203(例えば、ブラケット)上に配置される。

放熱部材414は、ティム412を介して伝達する熱を支持部材203で伝達し、支持部材203を介して外部に放出することができる。

## 【0076】

第1回路基板210の上部には、例えば、コールプロセッサ214が実装され得る。

第1回路基板210の上部に実装されたコールプロセッサ214は、インタポーラ230内の部品実装空間(S)内に配置される。

第1回路基板210の第1面(例えば、上部)には第1接続端子310が配置される。

第2回路基板220の第1面(例えば、下部)には第2接続端子320が配置される。

一実施形態によれば、インタポーラ230は、ビア300、第1パッド302、第2パッド304、及び側面メッキ部材305を含む。

ビア300は、第1回路基板210に形成された第1接続端子310と第2回路基板220に形成された第2接続端子320とを電気的に接続する。

ビア300は、スルービア(through via)又はスタックビア(stack via)を含む。

## 【0077】

第1パッド302は、ビア300の下部に形成され、第1回路基板210の第1接続端子310と電気的に接続される。

第2パッド304は、ビア300の上部に形成され、第2回路基板220の第2接続端子320と電気的に接続される。

側面メッキ部材305は、ビア300の外側に配置される。

側面メッキ部材305は、第1回路基板210と第2回路基板220を結合又は支持することができる。

10

20

30

40

50

側面メッキ部材 305 は、選択的に用いることができる。

【0078】

第2回路基板 220 の上部には、例えば、トランシーバ 221 が実装され得る。

第2回路基板 220 の上部に実装されたトランシーバ 221 の外部には第2シールド部材 420 が配置される。

第2シールド部材 420 は、例えば、電子装置 200 の第2回路基板 220 から出力されるノイズ信号を遮断し、電子装置 200 の外部から入力されるノイズを遮断する。

第2シールド部材 420 は、シールドカン又は EMI (electromagnetic interference) モールディング部材であれば良い。

【0079】

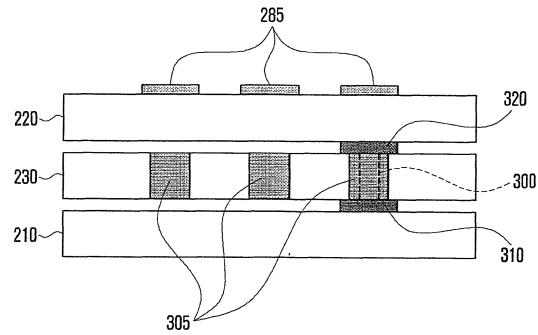

10

図9は、本発明の一実施形態による電子装置の第1回路基板及び第2回路基板の接続関係を概略的に示す斜視図であり、図10は、本発明の一実施形態による電子装置の第1回路基板及び第2回路基板の接続関係を概略的に示す側面図である。

図9及び図10を参照すると、本発明の一実施形態による電子装置 200 は、第1回路基板 210、第2回路基板 220、及びインタポーザ 230 を含む。

【0080】

第1回路基板 210 には通信回路（例えば、5G RF モジュール）が配置され得る。

第1回路基板 210 は、第1面（例えば、上部）に通信回路の出力と電気的に接続される第1接続端子 310 が形成される。

第2回路基板 220 の上部には、例えば、アレイアンテナ 285（例えば、図1のアンテナモジュール 197）が配置され得る。

20

第2回路基板 220 は、第1面（例えば、下部）に第2接続端子 320 が配置される。

アレイアンテナ 285 と第2接続端子 320 は電気的に接続され得る。

第2回路基板 220 は、電子装置 200 の高さを低めるため、一面にだけ電子部品を実装する。

一実施形態によれば、第2回路基板 220 の第2面（例えば、上部）には他のアンテナ素子を電気的に接続することができる第3接続端子（例えば、図4の第3接続端子 330）又は「cクリップ」が配置され得る。

【0081】

30

一実施形態によれば、アレイアンテナ 285 は、第2回路基板 220 にパターニングされた少なくとも一つのアンテナ又はアンテナ（例えば、図4のアンテナ 275）と接続された接続部材であれば良い。

すなわち、図4に示したように、アンテナ 275 が接続される第3回路基板 240 がない形態であっても良い。

インタポーザ 230 は、第1回路基板 210 と第2回路基板 220 との間に配置される。

インタポーザ 230 は、第1回路基板 210 に実装された少なくとも一つの部品（例えば、5G RF モジュール）が配置される空間（S）を有する。

インタポーザ 230 は、長方形又はそれ以外の他の多様な形態で構成することができる。

インタポーザ 230 は、第1回路基板 210 の第1面（例えば、上部）に形成された第1接続端子 310 と第2回路基板 220 の第1面（例えば、下部）に形成された第2接続端子 320 とを電気的に接続するためのビア 300 を含む。

40

【0082】

一実施形態によれば、図9及び図10に示した構成のように、本発明の一実施形態による電子装置 200 は、3Dビームフォーミングが可能となるように構成することができる。

例えば、5G RF のアレイアンテナを具現するため、第2回路基板 220 はアレイアンテナ 285 を含む。

また、インタポーザ 230 は、側面に少なくとも一つ以上の側面メッキ部材 305 を含む。

側面メッキ部材 305 は、アレイアンテナ 285 と接続される。

側面メッキ部材 305 は、アレイアンテナ 285 の一部として動作することができる。

50

側面メッキ部材 305 は、インタポーラ 230 の 3 面（例えば、上面、側面及び後面）をカバーすることができる。

側面メッキ部材 305 は“コ”字形状を持つことができる。

#### 【0083】

一実施形態によれば、図 9 及び図 10 に示した構成のように、本発明の一実施形態による電子装置 200 は、第 2 回路基板 220 上に Wi-Fi モジュールを実装した後、第 3 接続端子（例えば、図 4 の第 3 接続端子 330 を介して第 3 回路基板 240 で RF 信号を伝達したり、又は第 3 回路基板 240 で RF 信号を伝達せず、第 2 回路基板 220 に形成されたアンテナ接続端子（図 4 の第 5 接続端子 350 又は c クリップ）を介してアンテナ（例えば、図 4 のアンテナ 275）を直ちに接続するように構成することができる。

10

#### 【0084】

例えば、第 1 回路基板 210 に実装されたアプリケーションプロセッサ 212 は、第 2 回路基板 220 に実装された Wi-Fi モジュールを制御するデジタル信号をインタポーラ 230 のビア 300 を介して第 2 回路基板 220 へ伝達し、第 2 回路基板 220 上の Wi-Fi モジュールはデジタル信号を変調してアンテナ接続端子（図 4 の第 5 接続端子 350 又は c クリップ）を介して第 3 回路基板 240 ではないアンテナ 275 を介して直接 RF 信号を伝達することができる。

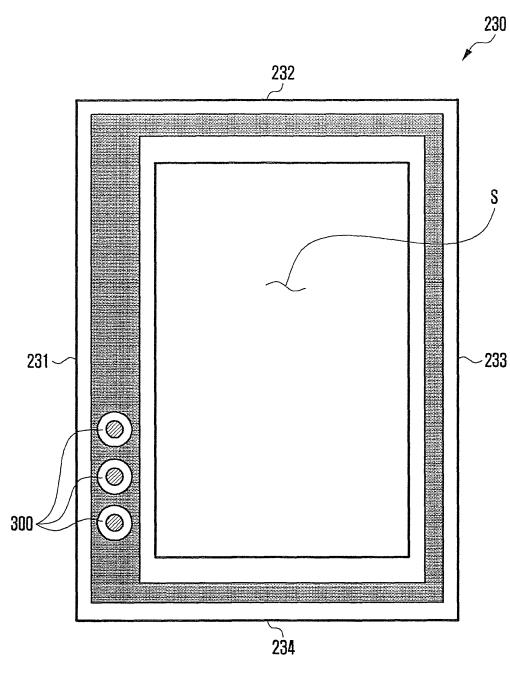

#### 【0085】

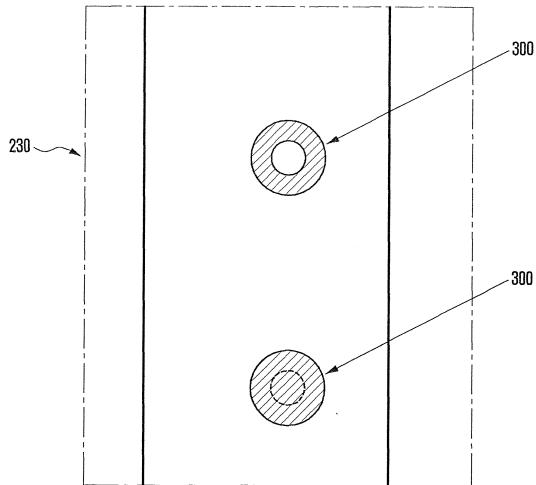

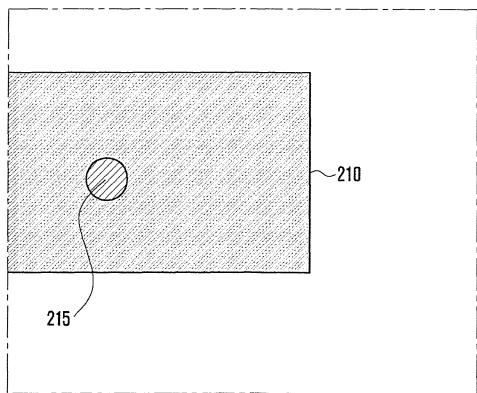

図 11 及び図 12 は、本発明のそれぞれの実施形態による電子装置のインタポーラの概略を示す図面である。

20

図 11 を参照すると、本発明の一実施形態による電子装置 200 のインタポーラ 230 は、ビア 300 がそれぞれ形成された第 1 部分 231、第 2 部分 232、第 3 部分 233、及び第 4 部分 234 が一体に接続されて構成される。

インタポーラ 230 が異なる多様な形態から構成されても、インタポーラ 230 を成すすべての部分を一体で構成する。

インタポーラ 230 は、第 1 回路基板 210 又は第 2 回路基板 220 に実装された少なくとも一つの部品（例えば、図 6 のアプリケーションプロセッサ 212、コールプロセッサ 214 又はトランシーバ 221）が配置される空間（S）を含む。

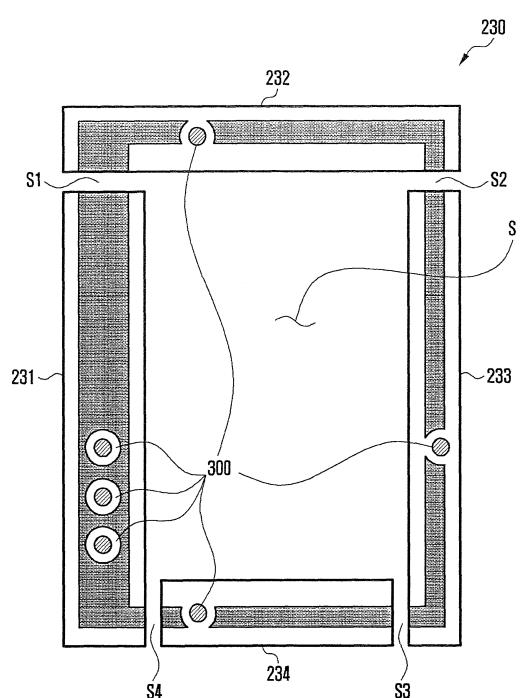

#### 【0086】

図 12 を参照すると、本発明の他の実施形態による電子装置 200 のインタポーラ 230 は、少なくとも一つ以上の部分によって構成される。

30

一実施形態によれば、インタポーラ 230 は、ビア 300 がそれぞれ形成された第 1 部分 231（例えば、第 1 インタポーラ）、第 2 部分 232（例えば、第 2 インタポーラ）、第 3 部分 233（例えば、第 3 インタポーラ），及び第 4 部分 234（例えば、第 4 インタポーラ）が第 1 スリット（s1）～第 4 スリット（s4）によりそれぞれ分離される。

例えば、第 1 部分 231 と第 2 部分 232 は、第 1 スリット（s1）によって分離され、第 2 部分 232 と第 3 部分 233 は、第 2 スリット（s2）によって分離され、第 3 部分 233 と第 4 部分 234 は、第 3 スリット（s3）によって分離され、第 4 部分 234 と第 1 部分 231 は、第 4 スリット（s4）によって分離される。

#### 【0087】

インタポーラ 230 が異なる多様な形態から構成されても、インタポーラ 230 を成すすべての部分がスリットによって互いに分離されて構成される。

40

一実施形態によれば、第 1 スリット（s1）～第 4 スリット（s4）は、それぞれ外部からノイズ信号が流入しない程度の間隔で構成される。

すなわち、第 1 スリット（s1）～第 4 スリット（s4）は、それぞれ外部のノイズ信号の電気的な波長より長さがより小さい間隔で構成することができる。

一実施形態によれば、インタポーラ 230 は、第 1 スリット（s1）～第 4 スリット（s4）を介して流入するノイズ信号を遮断するため、内部空間（S）の一部部品をシールドするシールド部材をさらに含むことができる。

シールド部材は、シールドカン又は EMI (electromagnetic int

50

erference) モールディング部材であれば良い。

【0088】

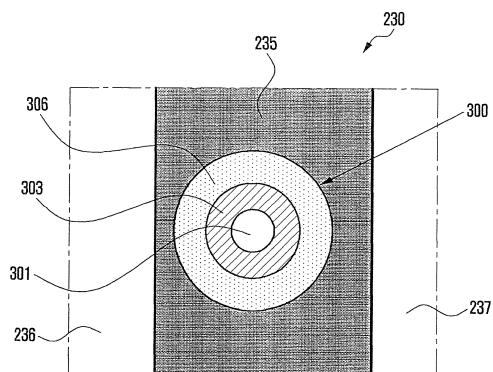

図13は、本発明の一実施形態による電子装置のビアの第1の例及びインタポーザの第1の例を示す図面である。

図13を参照すると、本発明の一実施形態による電子装置200のビア300は、スルービア(through via)から構成される。

【0089】

ビア300(例えば、スルービア)は、ホール301、メッキパッド303、及び絶縁領域306を含む。

ホール301は、例えば、ドリルによってインタポーザ230の少なくとも一部を貫いて形成される。

ホール301は、電気信号を伝達するために内壁がメッキ処理される。

メッキパッド303(例えば、図7の第1パッド302又は第2パッド304)は、ホール301の外側を取り囲んで形成される。

メッキパッド303は、銅箔及び金箔から構成することもできる。

金箔は、銅箔の腐食防止のために処理される金メッキであっても良い。

【0090】

絶縁領域306は、メッキパッド303の外側を取り囲んで形成される。

絶縁領域306は、ビア300のメッキパッド303がインタポーザ230の他の信号(例えば、グラウンド領域235)と接続しないように、例えば、銅箔をオープンした区間であってもよい。

銅箔をオープンした区間は、SR(solder resist)インクだけ塗布されてあり得る。

【0091】

図13を参照すると、本発明の一実施形態による電子装置200のインタポーザ230は、グラウンド領域235、第1キープアウト領域236、及び第2キープアウト領域237を含む。

グラウンド領域235は、ビア300の少なくとも一部(例えば、絶縁領域306)を取り囲むか、電気的に直接接続される。

グラウンド領域235は、銅箔及びSR(solder resist)インクから構成されることができる。

SRインクは、銅箔の腐食防止のために塗布されるインクであってもよい。

【0092】

第1キープアウト領域236は、グラウンド領域235の第1側に形成される。

第2キープアウト領域237は、グラウンド領域235の第2側に形成される。

すなわち、第1キープアウト領域236及び第2キープアウト領域237は、グラウンド領域235の両側に形成される。

第1キープアウト領域236及び第2キープアウト領域237は、インタポーザ230の外郭を望む形状にカッティングするためのラウティング(routing)に必要な誤差を勘案して形成された配線が存在しない区間であってもよい。

【0093】

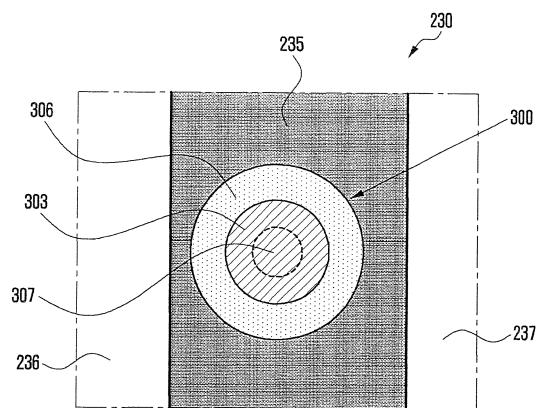

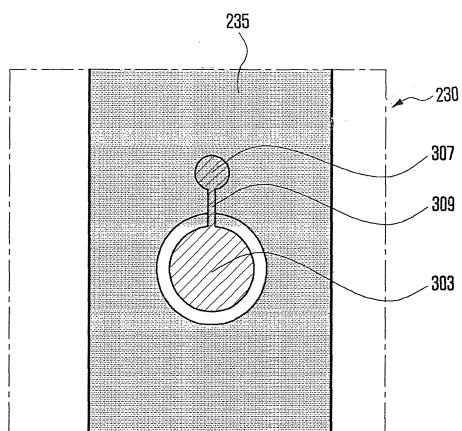

図14は、本発明の一実施形態による電子装置のビアの第2の例及びインタポーザの第2の例を示す図である。

図14を参照すると、本発明の一実施形態による電子装置200のビア300は、スタックビア(stacked via)から構成される。

ビア300(例えば、スタックビア)は、インナービア307、メッキパッド303、及び絶縁領域306を含む。

【0094】

インナービア307は、高速シグナルの移動のためにメッキパッド303(例えば、図7の第1パッド302又は第2パッド304)より小さく形成される。

10

20

30

40

50

メッキパッド 303 は、インナービア 307 の外側を取り囲む。

メッキパッド 303 は、インナービア 307 の末端部を閉鎖することができる。

メッキパッド 303 は、銅箔及び金箔から構成することができる。

金箔は、銅箔の腐食防止のために処理される金メッキであってもよい。

#### 【0095】

絶縁領域 306 は、メッキパッド 303 の外側を取り囲んで形成される。

絶縁領域 306 は、ビア 300 のメッキパッド 303 がインタポーヴ 230 の他の信号 (例えば、グラウンド領域 235) と接続されないように、例えば銅箔をオープンした区間であってもよい。

銅箔をオープンした区間は SR (solder resist) インクだけ塗布されて 10 あり得る。

#### 【0096】

図 14 を参照すると、本発明の一実施形態による電子装置 200 のインタポーヴ 230 は、グラウンド領域 235、第 1 キープアウト領域 236、及び第 2 キープアウト領域 237 を含む。

図 14 に示したインタポーヴ 230 は、図 13 に示したインタポーヴ 230 の領域構成と同一であっても良い。

#### 【0097】

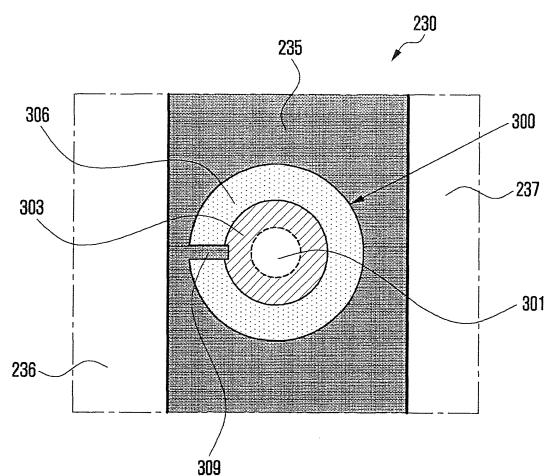

図 15 は、本発明の一実施形態による電子装置のビアの第 3 の例及びインタポーヴ の第 3 の例を示す図である。

図 15 を参照すると、本発明の一実施形態による電子装置 200 のビア 300 は、スルービア (through via) から構成される。

ビア 300 (例えば、スルービア) は、ホール 301、メッキパッド 303、及び絶縁領域 306 を含む。

図 15 に示したビア 230 は、図 13 に示したビア 230 の構成と同一であっても良く、図 15 に示したインタポーヴ 230 は、図 13 に示したインタポーヴ 230 の領域構成と同一であっても良い。

図 15 において、図 13 に示した構成と異なる点は、インタポーヴ 230 のグラウンド領域 235 とビア 300 のメッキパッド 303 は、配線 309 を用いて接続される。

#### 【0098】

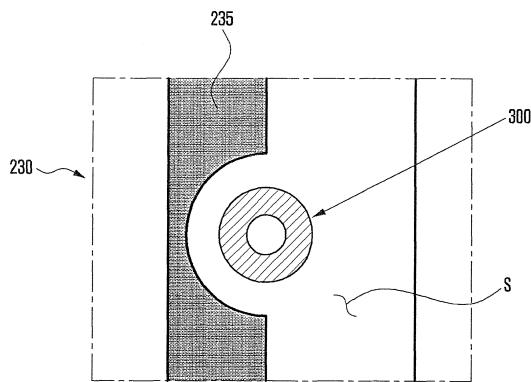

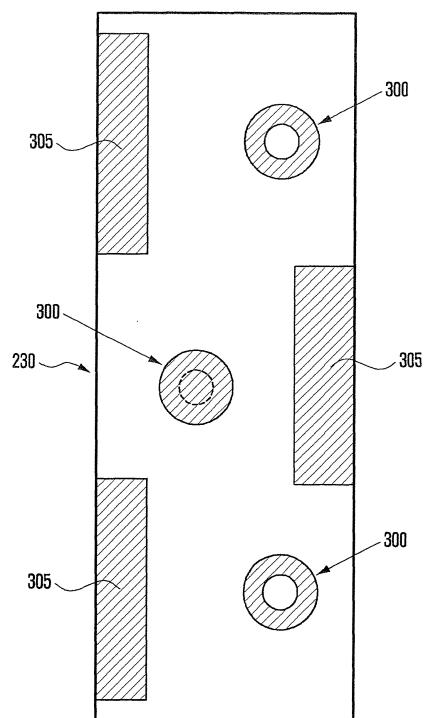

図 16 は、本発明の一実施形態による電子装置のインタポーヴ の第 4 の例の構成を示す図である。

図 16 を参照すると、本発明の一実施形態による電子装置 200 のインタポーヴ 230 は、グラウンド領域 235 の一部 (例えば、内側) が除去され、この除去されたグラウンド領域 235 程度インタポーヴ 230 の幅が縮小される。

#### 【0099】

図 17 は、本発明の一実施形態による電子装置のインタポーヴ の第 5 の例の構成を示す図である。

図 17 を参照すると、本発明の一実施形態による電子装置 200 のインタポーヴ 230 は、互いに異なるビア 300 (例えば、スタッカビア及びスルービア) を含む。

#### 【0100】

インタポーヴ 230 は、グラウンド領域 235 の一部 (例えば、外側) が除去され、この除去された領域及び第 1 キープアウト領域 236 に側面メッキ部材 305 が配置される。

側面メッキ部材 305 は、インタポーヴ 230 の 3 面 (例えば、上面、側面、及び後面) をカバーする。

側面メッキ部材 305 は “コ” 字形状を持つことができる。

他の実施形態によれば、インタポーヴ 230 は、グラウンド領域 235 の一部 (例えば、内側) が除去され、この除去された領域及び第 2 キープアウト領域 237 に側面メッキ部材 305 が配置される。

#### 【0101】

10

20

30

40

50

第1及び第2キープアウト領域(236、237)は、インタポーザ230の外郭を望む形状でカッティングするためのラウティング(routing)に必要な誤差を勘案して形成された配線が存在しない区間である。

したがって、ラウティング(routing)後、第1及び第2キープアウト領域(236、237)に別途の追加工程(例えば、ラウティング(routing)後、インタポーザ230側面の第1及び第2キープアウト領域(236、237)にドリルリング、銅メッキ及び金メッキなど)で側面メッキパッド305を形成することによって、既存で使用しなかった空間を活用することができ、これを介して除去されたグラウンド領域235の幅の一部程度インタポーザ230の幅を縮小させることができる。

#### 【0102】

一実施形態によれば、インタポーザ230の外側及び内側に配置された側面メッキ部材305は、互いに平行な位置に配置するか、又は、ジグザグ状に互いに行き違って配置することができる。

一実施形態によれば、側面メッキ部材305は、ビア300と一体で接続され得る。

例えば、側面メッキ部材305は、配線309を介してビア300と接続される。

側面メッキ部材305は、図9に示したアレイアンテナ285と接続されてアンテナの一部として動作することができる。

また他の実施形態によれば、側面メッキ部材305は、グラウンド領域235から延長された延長部308を介してグラウンド領域235と接続することができる。

ビア300及びグラウンド領域235と接続された側面メッキ部材305は、電子装置200の外部から入力されるノイズを遮断するシールド部材の役目を行うことができる。

#### 【0103】

図18は、本発明の一実施形態による電子装置のインタポーザの第6の例の構成を示す図である。

図18を参照すると、本発明の一実施形態による電子装置200のインタポーザ230は、互いに異なるビア300(例えば、スルービア及びスタックビア)を含む。

図18に示したインタポーザ230は、上述した図13～図15に比べ、ビア300を取り囲むグラウンド領域235が形成されない。

これにより、除去されたグラウンド領域235程度インタポーザ230の幅を縮小させることができる。

#### 【0104】

一実施形態によれば、電子装置200の信号が低速であるかインピーダンスシグナルのマージンが広い場合、又はインタポーザ230の高さが低くてインピーダンス歪みが誤差以内の場合にはグラウンド領域235を削除することができる。

インタポーザ230にグラウンド領域235が形成されていない場合、インタポーザ230は、シールド構造物であるシールドカン又はEMI(electromagnetic interference)モールディング材料から構成され得る。

他の実施形態によれば、インタポーザ230にグラウンド領域235が形成されていない場合、第1回路基板210及び第2回路基板220に実装されてインタポーザ230の内部空間(S)又は外部に配置された部品は、シールド構造物であるシールドカン又はEMI(electromagnetic interference)モールディングなどを介してシールディングされ、除去されたグラウンド領域235のノイズ遮蔽の役目を代わりに行うことができる。

#### 【0105】

図19は、本発明の一実施形態による電子装置のインタポーザ、ビア、及び側面メッキ部材の構成を示す図である。

図19を参照すると、本発明の一実施形態による電子装置200のインタポーザ230には互いに異なるビア(例えば、スルービア及びスタックビア)がジグザグ状に配置される。

他の実施形態によれば、インタポーザ230には互いに異なるビア(例えば、スルービ

10

20

30

40

50

ア及びスタックビア)を一直線上に配置することもできる。

また、他の実施形態によれば、インタポーラ230には同一ビア(例えば、スルービア又はスタックビア)をジグザグ状に配置することもできる。

また、他の実施形態によれば、インタポーラ230には同一ビア(例えば、スルービア又はスタックビア)を一直線上に配置することもできる。

#### 【0106】

一実施形態によれば、インタポーラ230には複数個の側面メッキ部材305がジグザグ状に配置される。

例えば、インタポーラ230の外側に形成された側面メッキ部材305は、電子装置200の外部から流入されるノイズ信号を遮断することができる。

インタポーラ230の内側に形成された側面メッキ部材305は、電子装置200の内部(例えば、第1回路基板210及び/又は第2回路基板220)から出力されるノイズ信号を遮断することができる。

これを介して、ビア300を第1及び第2キープアウト領域(236、237)に接するように移動させることができるのでインタポーラ230の幅を縮小させることができ、ビア300が移動して生じた反対側空間は側面メッキ部材305を生成することができる空間が確保されるので、インタポーラ230の幅を縮小しながらもインタポーラ230内外部のシールディングの役目もできるようになる。

#### 【0107】

図20A、図20B、及び図20Cは、本発明の一実施形態による電子装置のビア、インタポーラ及び第1回路基板の構成を説明するための図である。

図20Aは、本発明の一実施形態によるインタポーラに形成されたビアの断面図であり、図20Bは、本発明の一実施形態による第1回路基板(又は第2回路基板)に形成された第3導電パッドの構成を示す断面図であり、図20Cは、本発明の一実施形態による第1回路基板(又は第2回路基板)に形成された第3導電パッドの構成を示す平面図である。

#### 【0108】

図20Aを参照すると、本発明の一実施形態によるインタポーラ230は、ビア300(例えば、図13のスルービア)を含む。

ビア300は、ホール301、第1パッド302、及び第2パッド304を含む。

ホール301は、例えば、ドリルによってインタポーラ230の少なくとも一部を貫いて形成することができる。

第1パッド302(例えば、図7の第1パッド302及び第2パッド304(例えば、図7の第2パッド304)は、ホール301の外側を取り囲んで形成される。

第1パッド302は、インタポーラ230の下部を介して露出され、第2パッド304は、インタポーラ230の上部を介して露出される。

第1パッド302及び第2パッド304は、銅箔及び金箔から構成することができる。

一実施形態によれば、第1パッド302は、第1回路基板210に配置された第1接続端子310と電気的に接続され、第2パッド304は、第2回路基板220に配置された第2接続端子320と電気的に接続される。

#### 【0109】

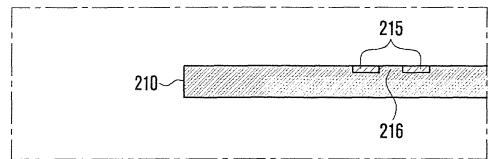

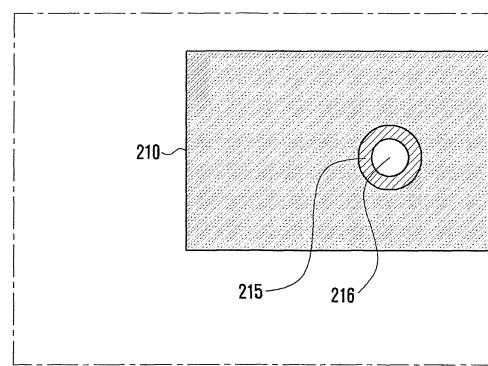

図20B及び図20Cを参照すると、本発明の一実施形態による第1回路基板210の上部には、インタポーラ230に形成されたビア300の第1パッド302との接続性を強化するために第3パッド215が配置される。

第3パッド215は、ビア300の第1パッド302と対応する位置に配置される。

一実施形態によれば、第1回路基板210に配置された第3パッド215の内部には非メッキ領域216を含むことができる。

非メッキ領域216は、ビア300のホール301と対応する位置に配置される。

#### 【0110】

非メッキ領域216の面積は、インタポーラ230の第1パッド302と第1回路基板210の第3パッド215を接続するための表面実装技術であるSMD(Surface

10

20

30

40

50

mount devices) 又はSMT (Surface mount technology) 適用時、第3パッド315に塗布された半田付け (soldering) 液がビア300のホール301に流入することを防止するように、ホール301の面積と同一であるかより大きく形成し得る。

他の実施形態によれば、第1回路基板210に配置された第3パッド215は、第2回路基板220にも配置することができる。

#### 【0111】

図21A、図21B、及び図21Cは、本発明の一実施形態による電子装置のビア、インタポーザ、及び第1回路基板の他の構成を説明するための図である。

図21Aは、本発明の一実施形態によるインタポーザに形成されたビアの断面図であり、図21Bは、本発明の一実施形態による第1回路基板(又は第2回路基板)に形成された第3導電パッドの構成を示す断面図であり、図21Cは、本発明の多様な実施形態による第1回路基板(又は第2回路基板)に形成された第3導電パッドの構成を示す平面図である。

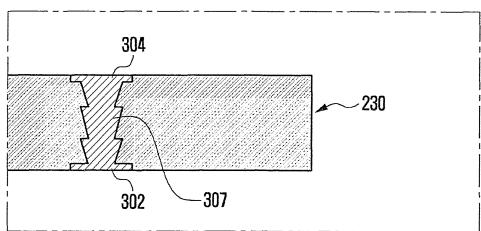

#### 【0112】

図21Aを参照すると、本発明の一実施形態によるインタポーザ230は、ビア300(例えば、図14のスタックビア)を含む。

ビア300は、インナービア307、第1パッド302、及び第2パッド304を含む。

インナービア307は、高速シグナルの移動のために第1パッド302及び/又は第2パッド304より小さく形成される。

第1パッド302(例えば、図7の第1パッド302)及び第2パッド304(例えば、図7の第2パッド304)は、インナービア307の上部及び下部を閉鎖する。

第1パッド302は、インタポーザ230の下部を介して露出され、第2パッド304はインタポーザ230の上部を介して露出される。

第1パッド302及び第2パッド304は、銅箔及び金箔から構成することができる。

一実施形態によれば、第1パッド302は、第1回路基板210に配置された第1接続端子310と電気的に接続され、第2パッド304は、第2回路基板220に配置された第2接続端子320と電気的に接続される。

#### 【0113】

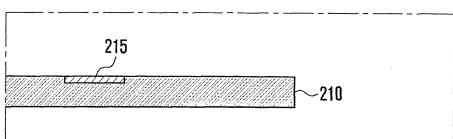

図21B及び図21Cを参照すると、本発明の一実施形態による第1回路基板210の上部には、インタポーザ230に形成されたビア300の第1パッド302との接続性を強化するために第3パッド215を配置することができる。

第3パッド215は、ビア300の第1パッド302と対応する位置に配置される。

他の実施形態によれば、第1回路基板210に配置された第3パッド215は、第2回路基板220にも配置することができる。

#### 【0114】

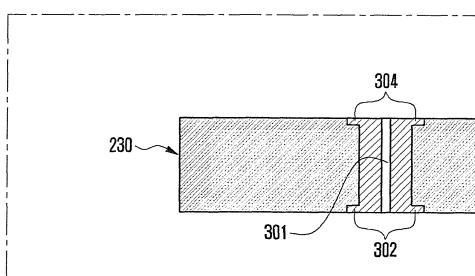

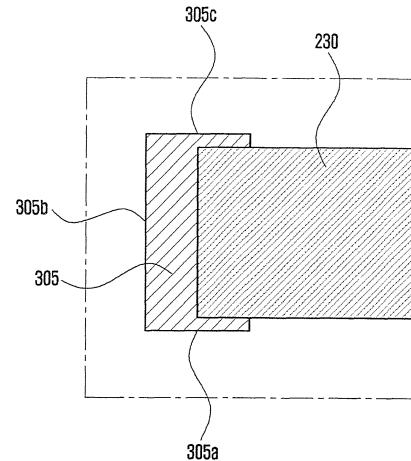

図22は、本発明の一実施形態による電子装置のインタポーザ及び側面メッキ部材の構成を示す側面図である。

図22を参照すると、本発明の一実施形態による側面メッキ部材305は、第1面305a(例えば、下面)、第2面305b(例えば、側面)及び第3面305c(例えば、上面)を含む。

すなわち、側面メッキ部材305は、インタポーザ230の3面(例えば、上面、側面及び後面)をカバーすることができる。

側面メッキ部材305は“コ”字形状を持つことができる。

#### 【0115】

一実施形態によれば、インタポーザ230に形成された側面メッキ部材305は、電子装置200の外部から流入されるノイズ信号を遮断することができる。

側面メッキ部材305は、電子装置200の内部(例えば、第1回路基板210及び/又は第2回路基板220)から出力されるノイズ信号を遮断することができる。

また他の実施形態によれば、側面メッキ部材305は、図9に示したアレイアンテナ2

10

20

30

40

50

85と接続されてアンテナの一部として動作することができる。

【0116】

図23は、本発明の一実施形態による電子装置のビアの他の構成を示す図である。

図23を参照すると、本発明の一実施形態によるインタポーザ230は、インナービア307、配線309、及びメッキパッド303を含む。

インナービア307は、図14に示したビア300（例えば、スタックビア）とは異なり、インナービア307とメッキパッド303がインタポーザ230上の異なる領域に形成される。

【0117】

この場合、インナービア307及びメッキパッド303は、配線309を利用して接続される。

10

インナービア307は外部に露出しないようにSR処理をすることができる、グラウンド領域235と分離して存在することもできる。

これを介して、第1回路基板210及び第2回路基板220を電気的に接続するため、インタポーザ230内には一直線上に直接接続されるビア形態以外に多様な形態の配線も存在するようにして配線の柔軟性を高めることができる。

【0118】

尚、本発明は、上述の実施携帯に限られるものではない。本発明の技術的範囲から逸脱しない範囲内で多様に変更実施することが可能である。

【符号の説明】

20

【0119】

200 電子装置

201 ハウジング

203 支持部材

210 第1回路基板

212 アプリケーションプロセッサ

214 コールプロセッサ

220 第2回路基板

221 トランシーバ

230 インタポーザ

240 第3回路基板

250 コネクタ

260 第1バッテリー

262 第2バッテリー

270 アンテナモジュール

275 アンテナ

280 後面カバー

300 ビア

302、304 (第1、第2)パッド

305 側面メッキ部材

40

310 第1接続端子

320 第2接続端子

330 第3接続端子

340 第4接続端子

350 第5接続端子

410、420 (第1、第2)シールド部材

412 ティム

414 放熱部材

416 銅シート

S 空間

50

【図面】

【図 1】

【 図 2 】

【 図 3 】

【図4】

【 5 】

【 四 6 】

【図7】

【図8】

【図 9】

【図 10】

10

【図 11】

【図 12】

20

30

40

50

【図 1 3】

【図 1 4】

10

【図 1 5】

【図 1 6】

20

30

40

50

【図17】

【図18】

10

【図19】

【図20A】

20

30

40

50

【図 2 0 B】

【図 2 0 C】

10

【図 2 1 A】

【図 2 1 B】

20

【図 2 1 C】

【図 2 2】

30

40

50

【図 2 3】

10

20

30

40

50

---

フロントページの続き

1号

(72)発明者 李 昭 英

大韓民国 京畿道 果川市 別陽路 12, 326棟 603号

審査官 河合 俊英

(56)参考文献 米国特許出願公開第2012/0243195(US, A1)

特開2017-130649(JP, A)

特開2015-080205(JP, A)

韓国公開特許第10-2013-0114330(KR, A)

特開2006-040870(JP, A)

国際公開第2013/172060(WO, A1)

米国特許出願公開第2010/0298027(US, A1)

特開2013-238578(JP, A)

(58)調査した分野 (Int.Cl., DB名)

H01L 25/04

H01L 23/12

H05K 1/14