(11) Numéro de publication :

**0 161 175** B1

(12)

## FASCICULE DE BREVET EUROPÉEN

45) Date de publication du fascicule du brevet :

(51) Int. Cl.4: G 09 G 1/16

17.08.88

(21) Numéro de dépôt : 85400734.1

(22) Date de dépôt : 12.04.85

- (54) Dispositif pour modifier l'aspect des points d'une image sur un écran d'une console de visualisation d'images graphiques.

- (30) Priorité: 17.04.84 FR 8406052

- (43) Date de publication de la demande : 13.11.85 Bulletin 85/46

- (45) Mention de la délivrance du brevet : 17.08.88 Bulletin 88/33

- 84 Etats contractants désignés : DE GB

- (56) Documents cités:

US-A- 4 303 986

WESCON CONFERENCE RECORD, vol. 25, septembre

1981, pages 31/5-1 31/5-10, El Sequndo, US; J.L.

WISE: "Color graphics with an advanced LSI controller"

- 73 Titulaire : THOMSON VIDEO EQUIPEMENT 94, rue du Fossé Blanc F-92230 Gennevilliers (FR)

- 72 Inventeur : Pham Van Cang, Luc THOMSON-CSF SCPI 173, bid Haussmann F-75379 Paris Cedex 08 (FR)

- Mandataire: Lincot, Georges et al THOMSON-CSF SCPI 19, avenue de Messine F-75008 Paris (FR)

) 161 175 B1

Il est rappelé que : Dans un délai de neuf mois à compter de la date de publication de la mention de la délivrance du brevet européen toute personne peut faire opposition au brevet européen délivré, auprès de l'Office européen des brevets. L'opposition doit être formée par écrit et motivée. Elle n'est réputée formée qu'après paiement de la taxe d'opposition (Art. 99(1) Convention sur le brevet européen).

. 25

30

45

La présente invention concerne un dispositif pour modifier l'aspect des points d'une image sur un écran d'une console de visualisation d'images graphiques, l'image étant analysée suivant le principe d'analyse des images de télévision, et la console étant commandée par un processeur

1

graphique.

Les consoles de visualisation commandées par un processeur graphique comportent une mémoire graphique à accès aléatoire interposée entre l'écran de la console et le processeur qui mémorise les données relatives à chaque point ou « pixel » du graphique apparaissant sur l'écran. La modification du graphique peut être obtenue à tout instant en changeant le contenu des données relatives à chaque point du graphique mémorisé à l'intérieur de la mémoire graphique, ce qui a pour effet d'agir sur la luminance et/ou la couleur de chaque point ou pixel du graphique qui est à modifier. La modification est habituellement effectuée par un opérateur qui introduit sur un clavier lié au processeur les instructions qui permettent la modification des données relatives à chacun des points modifiés. L'action de l'opérateur sur le clavier déclenche dans le processeur un cycle de modification, qui est exécuté soit par le lancement d'un programme particulier soit par la mise en action d'opérateurs logiques câblés.

Si les méthodes de programmation utilisées permettent d'effectuer à faible coût un nombre très élevé et complexe d'opérations de remplacement, elles ont pour inconvénient d'occuper beaucoup de temps de cycle de calcul du processeur. Par contre, l'utilisation de logiques câblées permet de gagner en temps de traitement mais a pour inconvénient d'être onéreuse et d'être limitée à l'utilisation d'opérateurs logiques élémentaires ce qui réduit très nettement les possibilités des systèmes à logiques câblées.

Le but de l'invention est de pallier les inconvénients précités.

A cet effet, l'invention a pour objet, un dispositif pour modifier l'aspect d'une image sur l'écran d'une console de visualisation d'images graphiques analysées suivant le principe d'analyse des images de télévision commandée par un processeur graphique, du type comprenant, une mémoire graphique de tous les points de l'écran interposée entre l'écran de la console de visualisation et le processeur, la mémoire graphique étant organisée en mots de n bits, chaque bit étant représentatif de l'état d'un point de l'image et ayant une valeur 1 ou 0 suivant que le point qu'il représente sur l'image est visible ou est confondu avec le fond de l'image et une mémoire d'attribut contenant les attributs de chacun des points de l'image, caractérisé en ce qu'il comprend également un décodeur pour sélectionner un bit dans chaque mot lu dans la mémoire graphique et un circuit de modification relié au décodeur, à la mémoire d'attribut et au processeur pour modifier chaque attribut du point correspondant au bit sélectionné d'un mot à l'aide de bits de modification fournis par le processeur et mémoriser chaque attribut modifié à l'intérieur de la mémoire d'attribut, et un circuit de reformation couplé au circuit de modification, au décodeur et à la mémoire graphique pour reconstituer le mot modifié et le mémoriser à l'intérieur de la mémoire graphique.

Le dispositif selon l'invention a pour principal avantage qu'il permet d'optimiser la durée des cycles de lecture, de modification et d'écriture de chaque point ou pixel dont les données correspondantes sont mémorisées dans la mémoire graphique ainsi que la gamme des opérations qui peuvent être effectuées à l'intérieur de ce cycle. En offrant la possibilité de traiter en parallèle chaque mot contenu dans la mémoire graphique avec chacun des attributs correspondants des points ou pixels, le dispositif selon l'invention présente une grande souplesse de traitement, pratiquement identique à celle que l'on obtient avec des systèmes à traitement purement logiciel tout en permettant des traitements plus rapides.

D'autres caractéristiques et avantages de l'invention apparaîtront au cours de la description faite au regard des dessins annexés donnés uniquement à titre d'exemple et dans lesquels :

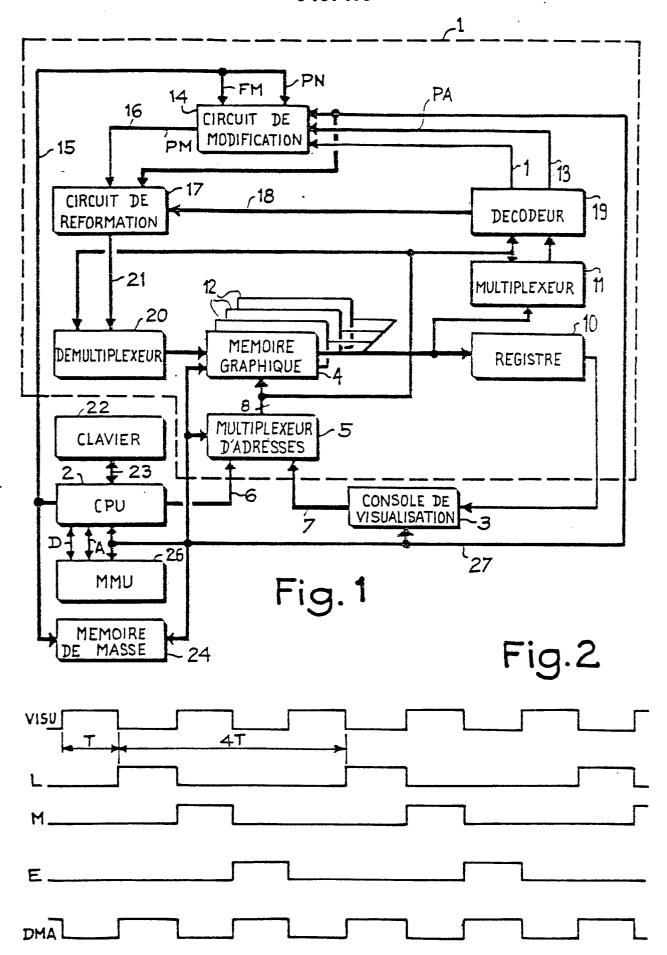

- la figure 1 est une représentation du dispositif selon l'invention;

- la figure 2 est une représentation des diagrammes des temps du cycle de rafraichissement de l'écran d'une console de visualisation balayé suivant le principe de balayage des écrans de télévision, du cycle de lecture, de modification et d'écriture de la mémoire graphique ainsi que du cycle d'accès direct DMA à la mémoire graphique:

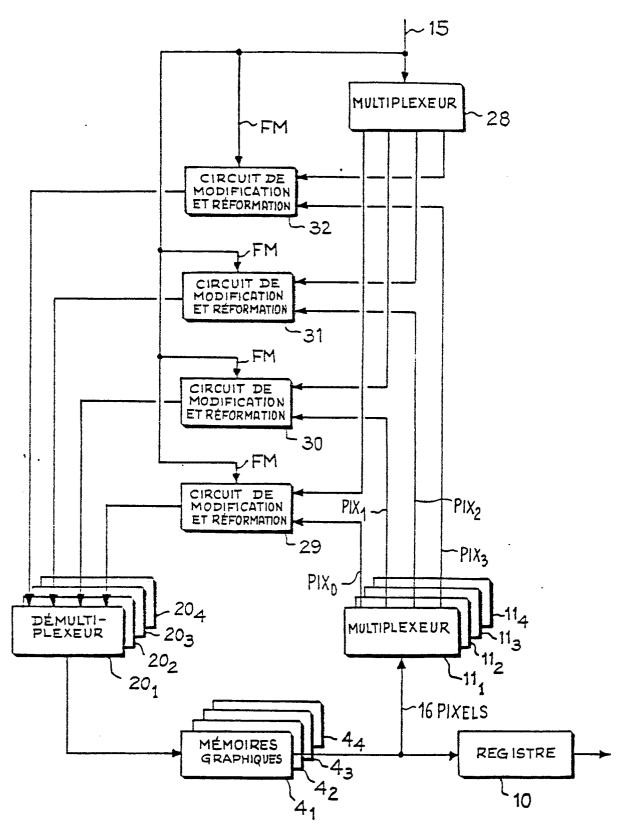

- la figure 3 est une représentation d'une organisation parallèle du dispositif de la figure 1 permettant la modification en parallèle de l'ensemble des données relatives aux points ou pixels de l'image d'un graphique contenus dans un mot de la mémoire graphique.

Le dispositif 1 pour modifier l'aspect des points d'une image inscrite sur un écran d'une console de visualisation selon l'invention est représenté sur la figure 1 à l'intérieur d'une ligne en pointillées, couplé entre un processeur 2 désigné par l'abréviation CPU qui est la contraction du terme anglo-saxon Central Processing Unit et une console de visualisation 3. Le dispositif 1 comprend une mémoire graphique 4 qui contient une représentation binaire matricielle de tous les points caractéristiques de l'image graphique qui est visualisée sur la console de visualisation 3, chaque bit d'information contenu dans la mémoire graphique 4 ayant, par exemple, la valeur 0 lorsqu'il correspond au fond uniforme du graphique et la valeur binaire 1 lorsqu'il correspond à un point ou pixel du graphique qui se détache sur le fond de celui-ci. La mémoire

graphique est organisée en mots de n bits représentant l'état de n pixels, chaque mot étant adressé soit par le processeur 2 ou par la console de visualisation 3 par l'intermédiaire d'un circuit multiplexeur d'adresse 5 à deux entrées de multiplexage, une première entrée de multiplexage étant reliée par la ligne d'adresse 6 à la sortie d'adresse du processeur 2 et une deuxième entrée d'adresse étant reliée par la ligne d'adresse 7 à la sortie d'adresse de la console de de visualisation 3. La sortie du multiplexeur d'adresse 5 est reliée aux entrées d'adressage de la mémoire graphique 4 au moyen de la ligne d'adresse 8. Les données lues dans la mémoire graphique 4 aux emplacements de mémoire désignées par les mots d'adresse appliqués sur la ligne d'adresse 8 sont appliquées respectivement aux entrées d'un registre parallèle-série 10 et aux entrées d'un circuit multiplexeur 11. Le dispositif 1 comprend également une mémoire d'attribut 12 formée éventuellement par p plans de mémoires supplémentaires de la mémoire graphique 4 qui contient les attributs codés sur p bits respectifs à chacun des n pixels représentés dans chaque mot de n bits contenus dans la mémoire graphique 4, cette mémoire d'attribut 12 étant adressée simultanément à la mémoire graphique 4 par la ligne d'adresse 8. Les mots lus dans la mémoire graphique et dans la mémoire d'attribut 12 sont appliqués aux circuits non représentés de la console de visualisation 3, par l'intermédiaire du registre 10, pour permettre la visualisation des pixels qu'ils représentent par la console de visualisation. Les mots d'attribut PA de chaque pixel, adressés par chacun des mots d'adresse appliqués sur la ligne d'adressage 8, sont appliqués par une ligne de données 13 sur une première entrée d'un circuit de modification 14 au travers du multiplexeur 11 et d'un décodeur 19 reliés en série. Le circuit de modification 14 est relié par des deuxième et troisième entrées aux sorties de données du processeur 2 au moyen d'une ligne de données 15 dans le but, d'appliquer des données de modification notées FM et PN sur les deuxième et troisième entrées du circuit de modification 14, pour modifier les valeurs des attributs des points ou pixels PA lus dans la mémoire d'attribut 12 et qui sont appliqués sur la première entrée du circuit de modification 14 par la ligne de données 13. La sortie du circuit de modification 14 est reliée par une ligne de donnée 16, à une entrée de donnée d'un circuit de reformation 17 pour enregistrer chaque attribut modifié PM par le circuit de modification 14 à l'emplacement qu'il occupe dans la mémoire d'attribut 12. Le circuit de reformation 17 est également relié par une deuxième entrée, au moyen de la ligne 18, à la sortie du décodeur 19 adressé par la ligne d'adresse 8 et relié par son entrée à la sortie du multiplexeur 11. Le décodeur 19 adressé par la ligne d'adresse 8 a pour but de sélectionner, à l'intérieur du mot de n bits appliqué à l'entrée du multiplexeur 11 chaque bit désigné par le mot d'adresse appliqué sur son entrée et le mot d'attribut PA codé sur p bits qui lui correspond.

Le bit représentatif du pixel sélectionné et son attribut PA sont appliqués respectivement à une quatrième entrée et à la première entrée du circuit de modification 14 dans le but de modifier éventuellement leurs valeurs en fonction des données de modification qui sont appliquées sur les deuxième et troisième entrée du circuit de modification 14. Les bits non sélectionnés par le décodeur 19 sont appliqués par la ligne 18 à l'entrée du circuit de reformation 17 qui reforme, en fonction de l'information modifiée ou non fournie à la sortie du circuit de modification 14. un nouveau mot binaire qui est appliqué à l'entrée d'un circuit démultiplexeur d'écriture 20 au moyen d'une ligne de données 21 pour écrire le mot éventuellement modifié et les attributs correspondants aux adresses qu'ils occupent normalement dans la mémoire graphique 4 et la mémoire d'attribut 12. Les données de modification de chacun des mots contenus dans la mémoire graphique 4 et la mémoire d'attribut 12 sont introduites à partir d'un clavier 22 qui est relié au processeur 2 par l'intermédiaire de la ligne de liaison 23. Une mémoire de masse 24 est éventuellement couplée par une ligne 25 au processeur 2 pour transférer à l'intérieur du processeur 2 les instructions de programme nécessaires au fonctionnement de l'ensemble. Le processeur 2 est également relié à une mémoire vive MMU 26 chargée de mémoriser en cours de fonctionnement les instructions et les données introduites à partir du clavier 22 ou de la mémoire de masse 24.

La mémoire graphique selon l'invention est à double accès par partage de cycle. Un premier cycle est réservé au fonctionnement de la console de visualisation 3, un deuxième cycle est réservé au fonctionnement du processus de modification contrôlé par le processeur 2, ce cycle de modification étant caractérisé par un cycle de lecture, un cycle de modification et un cycle de ré-écriture des informations modifiées dans la mémoire graphique et un troisième cycle de lecture directe de la mémoire graphique, l'ensemble de ces cycles étant représenté par le diagramme des temps de la figure 2. Les cycles de la figure 2 sont exécutés par le processeur 2 qui applique des signaux de commande sur le bus de commande 27 pour rafraichir les points ou pixels du graphique visualisés sur l'écran de la console de visualisation et commander les cycles de lecture et d'écriture de la mémoire graphique 4 et de la mémoire d'attribut 12. Sur la figure 2 le cycle de rafraichissement marqué « VISU » de la console de visualisation est représenté avec une durée T sur une période de 2T, le cycle de lecture L des informations contenues dans la mémoire graphique 4 et dans la mémoire d'attribut 12 est représenté entrelacé pendant une durée T en dehors de la durée de rafraichissement de la console de visualisation 3 sur une période de durée 4T, le cycle de modification M suit le cycle de lecture L avec une même durée T et une même période égale de durée 4T, le cycle d'écriture E suit le cycle de modification M avec une même durée T durant une période égale à 4T et le cycle d'accès direct à la mémoire

graphique et à la mémoire d'attribut a lieu pendant une durée T entre les instants de rafraichissement de la console de visualisation 3. A titre d'exemple, ce mode de partage de cycles peut être avantageusement utilisé pour la visualisation de mots de 16 pixels pendant une durée de 1184 nanosecondes et l'exécution de cycles de lecturemodification-écriture de deux fois 1184 nanosecondes par pixel ou point à modifier ce qui permet, de couvrir des plages de fonctionnement élevées, par exemple, un traitement de 720 points d'image ou pixels par ligne de balayage sur 576 lignes en respectant les normes CCIR du balayage de télévision à 625 lignes, le débit de la console de visualisation correspondant dans ce cas au standard de télévision numérique de 13,5 MHZ pour 25 image/seconde et la durée de cycle T étant voisine de 400 nanosecondes. Ces résultats sont obtenus en organisant par exemple la mémoire graphique en mots de 16 pixels et la mémoire d'attribut 12 en mots d'attribut de 3 bits, chacun des mots étant adressé par le processeur 2 par les bits d'adresse appliqués sur le bus d'adresse 8. Chaque mot lu dans la mémoire graphique 4 et dans la mémoire d'attribut 12 est appliqué à l'entrée du multiplexeur 11. La place d'un bit dans le mot correspondant au point ou pixel à modifier est sélectionnée par le multiplexeur 11 et le décodeur 19 à partir des quatre bits de poids faible du mot d'adresse en même temps que 3 bits d'attribut correspondants sont adressés dans la mémoire d'attribut 12 par le bus d'adresse 8. Les bits du mot non désignés par le multiplexeur 11 et le décodeur 19 sont dirigés directement vers les entrées du dispositif de reformation du mot 17 tandis que le bit sélectionné est pris en compte par le circuit de modification 14. Les 3 bits d'attribut lus dans la mémoire d'attribut 12 correspondant au point ou au pixel à modifier sont appliqués sur la première entrée du circuit de modification 14 pendant que le processeur 2 applique simultanément par la ligne de données 15,4 bits de modification PN en même temps que 6 bits de fonction correspondant à la fonction de modification FM choisie par l'opérateur permettant ainsi l'exécution de 64 fonctions de modification. Le bit du mot mémoire sélectionné et l'attribut correspondant sont modifiés pour former un mot PM sur 4 bits qui est obtenu à la sortie du circuit de modification 14 qui est fonction de la valeur 0 ou 1 du bit du point ou du pixel à modifier lu dans la mémoire graphique 4, de l'attribut correspondant lu dans la mémoire d'attribut 12, des données de modification PN fournies par le processeur 2 à l'entrée du circuit de modification 14 et de la fonction de modification transmise également sur la troisième entrée du circuit de modification 14 par le processeur 2. Cette transformation est effectuée à l'aide de mémoires mortes électriquement programmables du type connu sous la désignation anglo saxonne « EPROM » ou des mémoires vives du type connu sous la désignation anglo saxonne « RAM » contenant des tables de fonctions de modification de l'aspect des points de l'image graphique adres-

sés par le processeur 2 et par les bits d'attribut PA de chaque mot sélectionné de la mémoire d'attribut, pour remplir les multiples fonctions qui peuvent être données au circuit de modification, ces fonctions pouvant être des fonctions logiques simples du type ET logique, OU logique, OU EXCLUSIF, ou des fonctions plus compliquées permettant l'exécution, par exemple, d'interpolations linéaires entre « pixels » anciens et « pixels » nouveaux, des opérations conditionnelles, des opérations d'interpolation linéaires pour l'attribut de luminance d'un pixel en fonction de l'adressage fractionnaire du pixel nouveau pour résoudre en particulier les phénomènes d'aliasing connus des processeurs graphiques, ou encore pour exécuter des contrôles de texture d'image en superposition etc...

L'invention qui vient d'être décrite à l'aide du mode de réalisation représenté à la figure 1 n'est pas limitée à ce type de réalisation, il va de soi que d'autres modes de réalisation sont également possibles sans pour autant sortir du cadre même de l'invention, en particulier on concevra que l'invention s'applique également comme dans l'exemple représenté à la figure 3, à la réalisation de dispositifs plus complexes associant en parallèle le dispositif représenté à la figure 1 pour des versions de l'invention requérant un traitement rapide. Le dispositif représenté à la figure 3 se compose de quatre dispositifs du type représenté à la figure 1 composés en particulier respectivement de mémoires graphique 41, 42, 43 et 44 et de 4 circuits de modification et reformation 29, 30, 31, 32 similaires à l'exemple décrit à la figure 1 et qui permettent de traiter les pixels PIX<sub>0</sub>, PIX<sub>1</sub>, PIX<sub>2</sub>, PIX<sub>3</sub> consécutifs du mot de 16 pixels adressés dans les mémoires 4<sub>1</sub>,...4<sub>4</sub>. Le bus de données 15 agit sur les circuits de modification et reformation 29, 30, 31, 32 au travers d'un multiplexeur 28 qui dirige sur chacune des entrées des circuits placés à l'intérieur des circuits 29, 30, 31, 32 la donnée de modification PN et la fonction de modification FM. Cette organisation permet par exemple en mode de transfert conditionnel de modifier tous les pixels de la mémoire graphique concuremment avec la même fonction de modification FM appliquée sur chacun des circuits de modification et reformation 29, 30, 31, 32 tandis qu'en mode graphique, par exemple, en mode de trace de vecteurs, une seule fonction de modification FM correspondant au seul pixel adressé est activé. La vitesse de transfert conditionnel se trouve dans ces conditions très sensiblement accrue, en pratique il est possible avec une configuration parallèle permettant de traiter par exemple huit pixels parallèlement, et d'obtenir un temps d'accès équivalent à 1200ns/8 soit : 150 nanosecondes par pixel, soit un temps de transfert conditionnel de l'ordre de 80 millisecondes pour une image de 512×512 pixels.

## Revendications

1. Dispositif (1) pour modifier l'aspect des

points d'une image sur un écran d'une console de visualisation (3) d'images graphiques analysées suivant le principe d'analyse des images de télévision commandée par un processeur graphique (2) du type comprenant, une mémoire graphique (4) de tous les points de l'écran interposée entre l'écran de la console de visualisation (3) et le processeur (2), la mémoire graphique (4) étant organisée en mots de n bits, chaque bit étant représentatif de l'état d'un point de l'image et ayant une valeur 1 ou 0 suivant que le point qu'il représente sur l'image est visible ou est confondu avec le fond de l'image, et une mémoire d'attribut (12) contenant les attributs de chacun des points de l'image, caractérisé en ce qu'il comprend également un décodeur (19) pour sélectionner un bit dans chaque mot lu dans la mémoire graphique (4) et un circuit de modification (14) relié au décodeur (19), à la mémoire d'attribut (12) et au processeur (2) pour modifier chaque attribut du point correspondant au bit sélectionné d'un mot à l'aide de bits de modification fournis par le processeur (2) et mémoriser chaque attribut modifié à l'intérieur de la mémoire d'attribut (12), et un circuit de reformation (17) couplé au circuit de modification (14), au décodeur (19) et à la mémoire graphique (4) pour reconstituer le mot modifié et le mémoriser à l'intérieur de la mémoire graphique.

- 2. Dispositif selon la revendication 1, caractérisé en ce que le circuit de modification (14) est constitué par des mémoires programmables contenant des tables de fonction de modification de l'aspect des points de l'image graphique, adressées par le processeur graphique (2) et par les bits d'attribut de chaque mot sélectionné de la mémoire d'attribut (12).

- 3. Dispositif selon l'une quelconque des revendications 1 et 2, caractérisé en ce que les bits de modification et d'adressage des fonctions de modification sont engendrés par le processeur graphique (2) à partir d'instructions entrées dans le processeur (2) à partir d'un clavier (22).

- 4. Dispositif selon l'une quelconque des revendications 1 à 3, caractérisé en ce que la mémoire graphique (4) est adressée d'une part, par la console de visualisation et d'autre part, par le processeur graphique (2) au travers un multiplexeur d'adresse commandé par le processeur pour partager les cycles d'accès à la mémoire graphique initialisés par la console de visualisation (3) et le processeur (2).

- 5. Dispositif selon la revendication 4, caractérisé en ce que la mémoire graphique (4) est organisée en mots de longueur fixe.

- 6. Dispositif selon les revendications 4 et 5, caractérisé en ce que le cycle d'accès du processeur (2) à la mémoire graphique (4) se décompose en un cycle de lecture de chaque mot dans lequel se trouve le bit d'un point d'image à modifier, et du mot d'attribut correspondant dans la mémoire d'attribut (12), suivi par un cycle de modification du bit du point correspondant à modifier identifié à l'intérieur du mot lu dans la mémoire graphique et de modification du mot d'attribut lu dans la

mémoire d'attribut (12), également suivi par cycle de réécriture du mot contenant le bit modifié dans la mémoire graphique (4) et de réécriture du mot d'attribut modifié dans la mémoire d'attribut (12).

- 7. Dispositif selon l'une quelconque des revendications 2 à 6, caractérisé en ce que les mémoires programmables du circuit de modification sont des mémoires mortes électriquement programmables.

- 8. Dispositif selon l'une quelconque des revendications 2 à 6, caractérisé en ce que les mémoires vives programmables du circuit de modification sont des mémoires vives.

- 9. Dispositif pour modifier l'aspect des points d'une image sur un écran d'une console de visualisation (3) d'images graphiques analysées suivant le principe d'analyse des images de télévision, commandé par un processeur graphique (2), caractérisé en ce qu'il comprend plusieurs dispositifs selon l'une quelconque des revendications 1 à 8 couplés en parallèle.

- 10. Dispositif selon la revendication 9, caractérisé en ce que le couplage des dispositifs entre eux est obtenu à l'aide d'un circuit multiplexeur (28) qui dirige sur chacune des entrées des circuits de modification, la donnée de modification et la fonction de modification pour permettre la modification de tous les points de l'image graphique avec la même fonction de modification.

## Claims

- 1. A device (1) for modfying the aspect of the points of an image on the screen of a visualizing console (3) for graphic images analyzed in accordance with the television image analysis principle under the control of a graphic processor (2) of the type comprising: a graphic memory (4) for all the points on the screen placed between the screen of the visualizing console (3) and the processor (2), the graphic memory (4) being organized in words of n bits, each bit being representative of the state of one image point and having a value of 1 or 0 in accordance with whether the point that it represents on the image is visible or is merged with the background of the image, and an attribute memory (12) containing the attributes of each of the points of the image, characterized in that it also comprises a decoder (19) to select a bit in each read word in the graphic memory (4) and a modification circuit (14) connected with the decoder (19), with the attribute memory (12) and the with the processor (2) to modify each attribute of the point corresponding to the bit selected from a word with the aid of modification bits supplied by the processor (2) and to store each modified attribute in the interior of the attribute memory (12) and a reforming circuit (17) coupled with the modification circuit (14), with the decoder (19) and with the graphic memory (4) in order to reconstitute the modified word and to store it in the interior of the graphic memory.

- 2. The device as claimed in claim 1 charac-

terized in that the modification circuit (14) is constituted by programmable memories containing modification function tables for the aspect of the points of the graphic image, addressed by the graphic processor (2) and by the attribute bits of each selected word from the attribute memory (12).

- 3. The device as claimed in claim 1 or claim 2 characterized in that the modification and addressing bits for the modification functions are generated by the graphic processor (2) on the basis of instructions entered in the processor (2) using a keyboard (22).

- 4. The device as claimed in any one of the claims 1 through 3 characterized in that the graphic memory (4) is addressed, on the one hand, by the visualizing console and on the other hand by the graphic processor (2) via an address multiplexer controlled by the processor to share the access cycles to the graphic memory initialized between the visualizing console (3) and the processor (2).

- 5. The device as claimed in claim 4 characterized in that the graphic memory (4) is organized in fixed length words.

- 6. The device as claimed in claims 4 and 5 characterized in that the access cycle of the processor (2) to the graphic memory (4) is made up of a read cycle for each word in which the bit of a point of the image to be modified, and of the attribute corresponding word in the attribute memory (12) followed by a modification cycle for the bit of the corresponding bit to be modified identified in the interior of the read word in the graphic memory and the modification of the read attribute word in the attribute memory (12), also followed by the re-write cycle for the word containing the modified bit in the graphic memory (4) and for re-writing the attribute word in the attribute memory (12).

- 7. The device as claimed in any one of the claims 2 through 6 characterized in that the programmable memories of the modification circuit are electrically programmable ROMS.

- 8. The device as claimed in any one of the claims 2 through 6 characterized in that the programmable RAMS of the modification circuit are RAMS.

- 9. A device for modifying the aspect of the points of an image on a screen of a visualizing console (3) for graphic images analyzed using the television image principle of analysis controlled by a graphic processor (2) characterized in that that it comprises a plurality of devices as claimed in any one of the claims 1 through 8 coupled in parallel.

- 10. The device as claimed in claim 9 characterized in that the coupling together of the devices is produced with the aid of a multiplexing circuit (28) which supplies each of the inputs of the modification circuits with the modification data and the modification function in order to permit modification of all the points of the graphic image with the same modification function.

## Patentansprüche

- 1. Vorrichtung (1) zum Verändern des Aussehens der Punkte eines Bildes auf einem Bildschirm eines Sichtanzeigegeräts (3) für graphische, nach dem Analyseprinzip der Fernsehbilder analysierte Bilder, die von einem graphischen Prozessor (2) des Typs mit einem graphischen Speicher (4) aller Bildschirmpunkte gesteuert wird, welcher zwischen dem Bildschirm des Sichtanzeigegeräts (3) und dem Prozessor (2) eingefügt ist, wobei der graphische Speicher (4) in Wörter zu N-Bits organisiert ist, jedes Bit für den Zustand eines Bildpunktes repräsentativ ist und einen Wert 1 oder 0 aufweist, je nachdem, ob der Punkt, den er auf dem Bildschirm darstellt, sichtbar ist oder im Bildhintergrund verschwindet, sowie mit einem Attributspeicher (12), welcher die Attribute jedes der Bildpunkte beinhaltet, dadurch gekennzeichnet, daß sie ferner einen Decoder (19) zur Selektion eines Bits in jedem in dem graphischen Speicher (4) gelesenen Wort sowie eine Veränderungsschaltung (14) umfaßt, die mit dem Decoder (19), dem Attributspeicher (12) und dem Prozessor (2) verbunden ist, um jedes Attribut des dem selektierten Bit eines Worts entsprechenden Punkts mittels von dem Prozessor (2) gelieferter Veränderungsbits zu verändern, und um jedes veränderte Attribut innerhalb des Attributspeichers (12) zu speichern, sowie eine mit der Veränderungsschaltung (14), dem Decoder (19) und dem graphischen Speicher (4) gekoppelte Neubildungsschaltung (17), um das veränderte Wort wiederherzustellen und es innerhalb des graphischen Speichers zu spei-

- 2. Schaltung nach Anspruch 1, dadurch gekennzeichnet, daß die Veränderungsschaltung (14) aus programmierbaren Speichern besteht, die Funktionstabellen zum Verändern des Aussehens der Punkte des graphischen Bildes beinhalten und durch den graphischen Prozessor (2) sowie die Attributbits jedes selektierten Worts des Attributsspeichers (12) adressiert werden.

- 3. Vorrichtung nach Anspruch 1 oder 2, dadurch gekennzeichnet, daß die Bits zum Verändern und zum Adressieren der Veränderungsfunktionen durch den graphischen Prozessor (2), ausgehend von über eine Tastatur (22) in den Prozessor (2) eingegebenen Befehlen, erzeugt eind

- 4. Vorrichtung nach einem der Ansprüche 1 bis 3, dadurch gekennzeichnet, daß der graphische Speicher (4) einerseits durch das Sichtanzeigegerät und andererseits den graphischen Prozessor (2) adressiert wird, mittels eines Adressenmultiplexers, der über den Prozessor gesteuert wird, um die Zyklen des Zugriffs auf den graphischen Speicher zu teilen, die durch das Sichtanzeigegerät (3) und den Prozessor (2) initiiert werden.

- 5. Vorrichtung nach Anspruch 4, dadurch gekennzeichnet, daß der graphische Speicher (4) in Wörter mit fester Länge organisiert ist.

10

15

6. Vorrichtung nach den Ansprüchen 4 und 5, dadurch gekennzeichnet, daß der Zugriffszyklus des Prozessors (2) für den graphischen Speicher (4) aus einem Zyklus zum Auslesen jedes Worts, in welchem sich das Bit eines zu verändernden Bildpunkts befindet, sowie des entsprechenden Attributworts in dem Attributspeicher (12), besteht, aus einem Zyklus zum Verändern des Bits des entsprechenden, zu verändernden Punktes, der innerhalb des gelesenen Worts in dem graphischen Speicher identifiziert wird, auf den ein Zyklus zum Verändern des in dem Attributsspeicher (12) gelesenen Attributworts folgt, auf den wiederum ein Zyklus zum Neuschreiben des das veränderte Bit enthaltenden Worts in den graphischen Speicher (4) und ein Zyklus zum Neuschreiben des veränderten Attributworts in den Attributspeicher (12) folgen.

7. Vorrichtung nach einem der Ansprüche 2 bis 6, dadurch gekennzeichnet, daß die programmierbaren Speicher der Veränderungsschaltung elektrisch programmierbare Festwertspeicher sind.

8. Vorrichtung nach einem der Ansprüche 2 bis 6, dadurch gekennzeichnet, daß die programmierbaren Arbeitsspeicher der Veränderungsschaltung Arbeitsspeicher sind.

9. Vorrichtung zum Verändern des Aussehens der Funkte eines Bildes auf einem Bildschirm eines Sichtanzeigegeräts (3) für graphische Bilder, die nach dem Analyseprinzip der Fernsehbilder anlaysiert werden, die durch einen graphischen Prozessor (2) gesteuert wird, dadurch gekennzeichnet, daß sie mehrere parallelgekoppelte Vorrichtungen nach einem der Ansprüche 1 bis 8 umfaßt.

10. Vorrichtung nach Anspruch 9, dadurch gekennzeichnet, daß die Koppelung der Vorrichtungen mittels einer Multiplexerschaltung (28) erreicht wird, die das Veränderungsdatum sowie die Veränderungsfunktion zu jedem der Eingänge der Veränderungsschaltungen führt, um die Veränderung aller Punkte des graphischen Bildes mit derselben Veränderungsfunktion zu ermöglichen.

25

20

30

35

40

45

50

55

60

Fig.3