공개특허 10-2022-0129490

(19) 대한민국특허청(KR)

(12) 공개특허공보(A)(11) 공개번호 10-2022-0129490

(43) 공개일자 2022년09월23일

- (51) 국제특허분류(Int. Cl.)

*H01L 33/38* (2010.01) *H01L 33/00* (2010.01)

*H01L 33/30* (2010.01) *H01L 33/40* (2010.01)

- (52) CPC특허분류

*H01L 33/38* (2013.01)

*H01L 33/0093* (2020.05)

- (21) 출원번호 10-2022-0032791

- (22) 출원일자 2022년03월16일

심사청구일자 없음

- (30) 우선권주장

17/203,293 2021년03월16일 미국(US)

- (71) 출원인

에피스타 코포레이션

대만 신츄 시티 사이언스-베이스드 인더스트리얼

파크 리-신 로드 21

- (72) 발명자

시에 민-순

대만 신츄 시티 사이언스-베이스드 인더스트리얼

파크 리-신 로드 21

리 유-초

대만 신츄 시티 사이언스-베이스드 인더스트리얼

파크 리-신 로드 21

수에 웨이-젠

대만 신츄 시티 사이언스-베이스드 인더스트리얼

파크 리-신 로드 21

- (74) 대리인

김태홍, 김진희

전체 청구항 수 : 총 10 항

(54) 발명의 명칭 반도체 소자, 이 반도체 소자를 포함하는 반도체 장치 및 디스플레이 패널

### (57) 요 약

본 발명 내용은 반도체 소자 및 그 제조 방법을 제공한다. 반도체 소자는, 제 1 반도체 층, 활성 영역, 접촉층, 및 제 1 금속 원소를 함유하는 구조를 포함한다. 제 1 반도체 층은 표면을 가진다. 상기 표면은 제 1 부분 및 제 2 부분을 포함한다. 활성 영역은 제 1 부분에 위치하면서, AlGaInAs, InGaAsP, AlGaAsP 또는 AlGaInP를 포함한다. 접촉층은 산소(O) 원소 및 제 5 금속 원소를 포함하며, 제 2 부분에 위치한다. 제 1 금속 원소를 함유하는 구조는 접촉층 위에 위치한다. 접촉층은 제 1 금속 원소를 함유하는 구조 및 제 1 반도체 층에 직접 접촉한다.

**대 표 도** - 도1

10

(52) CPC특허분류

*H01L 33/0095* (2020.05)

*H01L 33/30* (2013.01)

*H01L 33/40* (2013.01)

---

## 명세서

### 청구범위

#### 청구항 1

제 1 부분 및 제 2 부분을 포함하는 표면을 갖는 제 1 반도체 층;

상기 제 1 부분에 위치하면서, AlGaInAs, InGaAsP, AlGaAsP 또는 AlGaInP를 포함하는 활성 영역;

상기 제 2 부분에 위치하면서, 상기 제 1 반도체 층과 다르거나 같은 도전 형태를 가지며, 산소(O) 원소 및 제 5 금속 원소를 포함하는 접촉층; 및

상기 접촉층 위에 위치하는 제 1 금속 원소를 함유하는 구조를 포함하고,

상기 접촉층은 상기 제 1 금속 원소를 함유하는 구조 및 상기 제 1 반도체 층에 직접 접촉하는, 반도체 소자.

#### 청구항 2

제 1 항에 있어서,

상기 제 1 금속 원소를 함유하는 구조는 상기 제 1 반도체 층에 직접 접촉되지 않고, 상기 제 1 금속 원소를 함유하는 구조는 상기 접촉층을 통해 상기 제 1 반도체 층에 전기적으로 연결되는, 반도체 소자.

#### 청구항 3

제 1 항에 있어서,

상기 제 1 반도체 층 아래에 위치하는 접합 구조를 더 포함하는, 반도체 소자.

#### 청구항 4

제 1 항에 있어서,

상기 접촉층 중에 단일 종류의 금속 원소만 포함하는, 반도체 소자.

#### 청구항 5

제 1 항에 있어서,

상기 제 1 반도체 층은 인화물 또는 비소화물을 포함하는, 반도체 소자.

#### 청구항 6

성장 기판을 제공하는 단계;

상기 성장 기판 위에 제 1 반도체 층과 활성 영역을 포함하는 반도체 스택을 형성하는 단계;

상기 반도체 스택을 접합 기판 위에 접합하는 단계;

상기 성장 기판을 제거하는 단계;

상기 제 1 반도체 층이 노출되도록 상기 반도체 스택의 일부를 제거하는 단계;

상기 제 1 반도체 층 위에 산소(O) 원소 및 제 5 금속 원소를 포함하는 접촉층을 형성하는 단계; 및

상기 접촉층 위에 제 1 금속 원소를 함유하는 구조를 형성하는 단계를 포함하는, 반도체 소자의 제조 방법.

#### 청구항 7

제 6 항에 있어서,

상기 제 1 반도체 층과 상기 접합 기판 사이에 접합 구조를 형성하는 단계를 더 포함하는, 반도체 소자의 제조 방법.

**청구항 8**

제 7 항에 있어서,

상기 접합 구조는 열경화성 폴리머를 포함하는, 반도체 소자의 제조 방법.

**청구항 9**

제 8 항에 있어서,

상기 접촉층 위에 제 1 금속 원소를 함유하는 구조를 형성하는 단계는, 제 1 온도에서 가열을 진행하는 단계를 포함하며, 상기 열경화성 폴리머는 열 분해 온도를 가지고, 상기 제 1 온도는 상기 열 분해 온도보다 낮거나, 또는 상기 제 1 온도와 상기 열 분해 온도 사이의 차이는 50°C 이하인, 반도체 소자의 제조 방법.

**청구항 10**

제 6 항에 있어서,

상기 제 1 금속 원소를 함유하는 구조는 합금을 포함하는, 반도체 소자의 제조 방법.

**발명의 설명****기술 분야**

[0001]

본 개시는 반도체 소자에 관한 것으로, 특히 발광 다이오드(Light emitting diode, LED)와 같은 반도체 발광 소자에 관한 것이다. 본 개시는 또한 반도체 소자의 제조 방법, 반도체 소자를 포함하는 반도체 장치 및 디스플레이 패널에 관한 것이다.

**배경 기술**

[0002]

반도체 소자는 각종 제품에 널리 사용되고 있으며, 각종 반도체 소자 관련 재료에 대한 연구 개발도 지속적으로 진행되고 있다. 예를 들어, III족 원소 및 V족 원소를 포함하는 III-V족 화합물 반도체 재료는, 발광 다이오드, 레이저 다이오드(Laser diode, LD), 광전 검출기(Opto electronic detector), 태양 전지(Solar cell), 또는 스위치(Switch) 또는 정류기(Rectifier)와 같은 전력 소자(Power device)와 같은 각종 반도체 소자의 제조에 적용될 수 있다. 최근, 반도체 소자는 조명, 의료, 디스플레이, 통신 및 감지 시스템 등 분야에 널리 사용되고 있다. 그 중에서, 발광 다이오드는 에너지 소비가 낮고, 사용 수명이 길어 다양한 분야에 널리 사용되고 있다.

**발명의 내용**

[0003]

본 발명은, 제 1 반도체 층, 활성 영역, 접촉층, 및 제 1 금속 원소를 함유하는 구조(first metal element-containing structure)를 포함하는 반도체 소자를 제공한다. 제 1 반도체 층은 표면을 가진다. 상기 표면은 제 1 부분 및 제 2 부분을 포함한다. 활성 영역은 제 1 부분에 위치하면서, AlGaInAs, InGaAsP, AlGaAsP 또는 AlGaInP를 포함한다. 접촉층은 제 2 부분에 위치하면서, 산소(O) 원소 및 제 5 금속 원소를 포함한다. 제 1 금속 원소를 함유하는 구조는 접촉층 위에 위치한다. 여기서, 접촉층은 제 1 금속 원소를 함유하는 구조 및 제 1 반도체 층에 직접 접촉한다.

[0004]

본 발명의 일 실시예에 있어서, 상기 제 1 금속 원소를 함유하는 구조는 제 1 반도체 층에 직접 접촉되지 않고, 제 1 금속 원소를 함유하는 구조는 접촉층을 통해 제 1 반도체 층에 전기적으로 연결된다.

[0005]

본 발명의 일 실시예에 있어서, 제 1 반도체 층 아래에 위치하는 접합 구조를 더 포함한다.

[0006]

본 발명의 일 실시예에 있어서, 접촉층 중에 단일 종류의 금속 원소만 포함한다.

[0007]

본 발명의 일 실시예에 있어서, 제 1 반도체 층은 인화물 또는 비소화물을 포함한다.

[0008]

본 발명은, 성장 기판을 제공하는 단계; 성장 기판 상에 제 1 반도체 층 및 활성 영역을 포함하는 반도체 스택을 형성하는 단계; 접합 기판에 반도체 스택을 접합하는 단계; 성장 기판을 제거하는 단계; 제 1 반도체 층이 노출되도록 반도체 스택의 일부를 제거하는 단계; 제 1 반도체 층 위에 산소(O) 원소 및 제 5 금속 원소를 포함하는 접촉층을 형성하는 단계; 및 접촉층 위에 제 1 금속 원소를 함유하는 구조를 형성하는 단계를 포함하는, 반도체 소자의 제조 방법을 제공한다.

- [0009] 본 발명의 일 실시예에 있어서, 제 1 반도체 층과 접합 기판 사이에 접합 구조를 형성하는 단계를 더 포함한다.

- [0010] 본 발명의 일 실시예에 있어서, 접합 구조는 열경화성 폴리머를 포함한다.

- [0011] 본 발명의 일 실시예에 있어서, 접촉층 위에 제 1 금속 원소를 함유하는 구조를 형성하는 단계는, 제 1 온도에서 가열을 진행하는 단계를 포함하며, 열경화성 폴리머는 열 분해 온도를 가지고, 제 1 온도는 열 분해 온도보다 낮거나, 또는 제 1 온도와 열 분해 온도의 차이는 50°C 이하이다.

- [0012] 본 발명의 일 실시예에 있어서, 제 1 금속 원소를 함유하는 구조는 합금을 포함한다.

### 도면의 간단한 설명

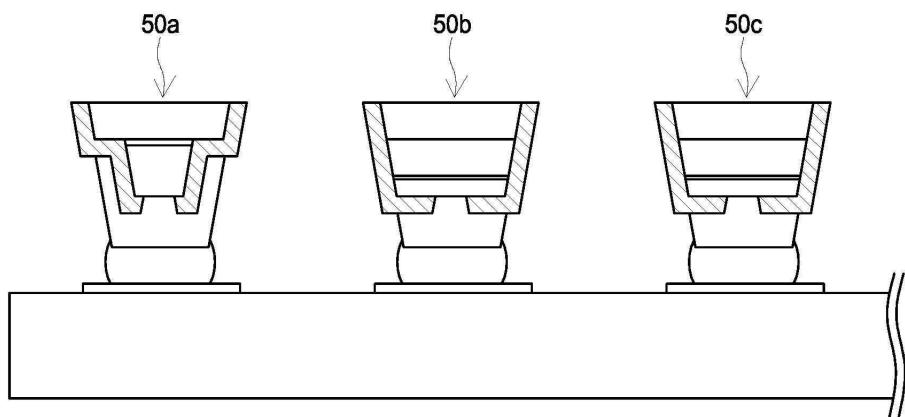

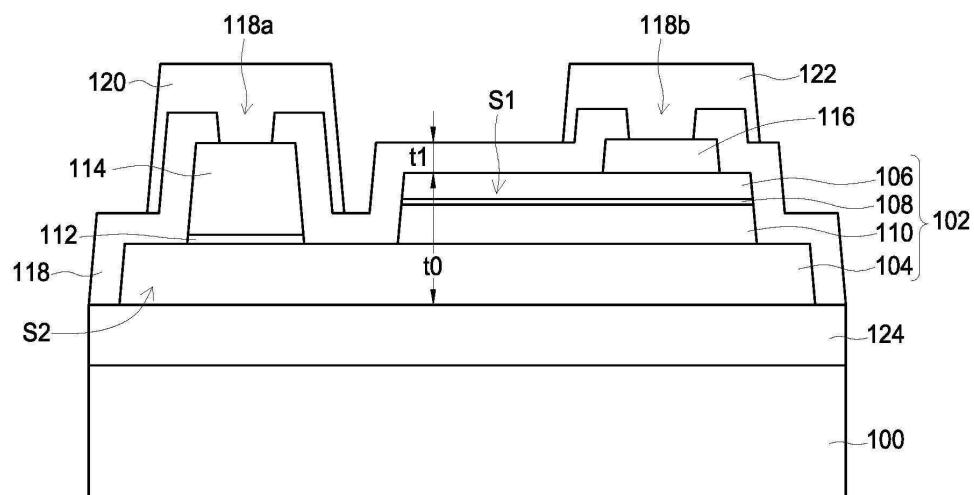

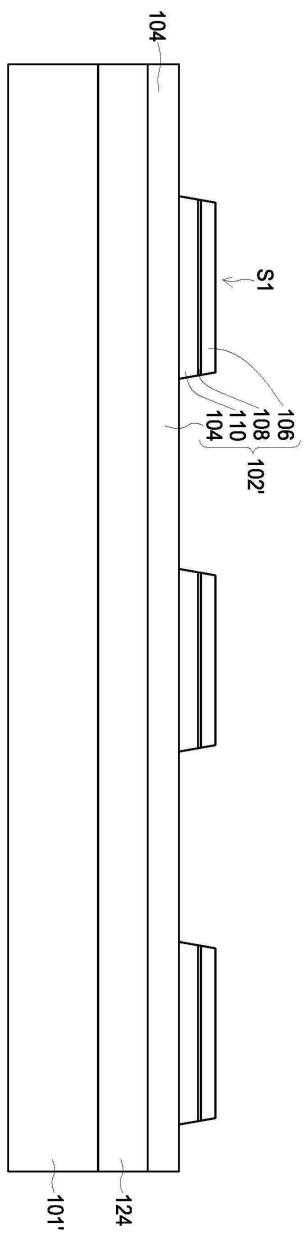

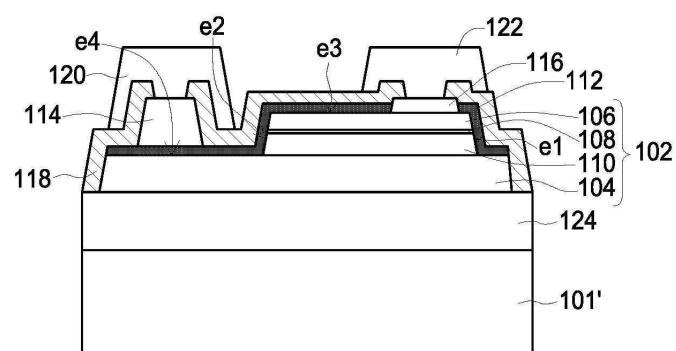

- [0013] 도 1은 본 개시의 일 실시예에 따른 반도체 소자의 개략적인 단면 구조도이다.

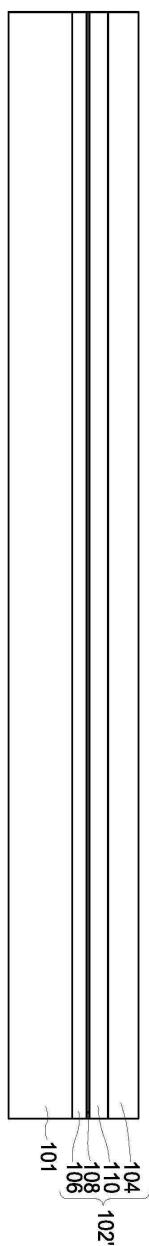

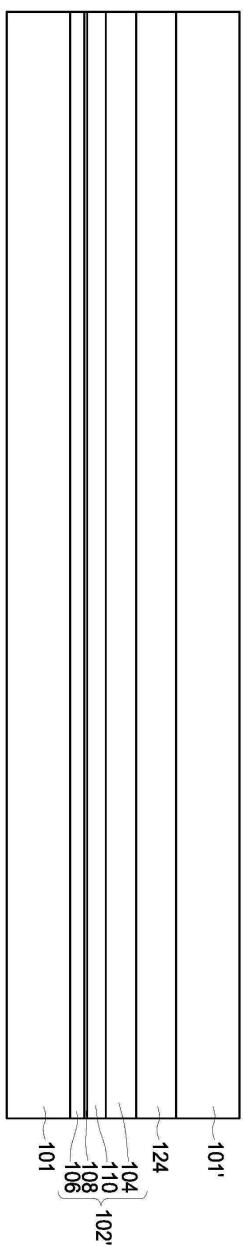

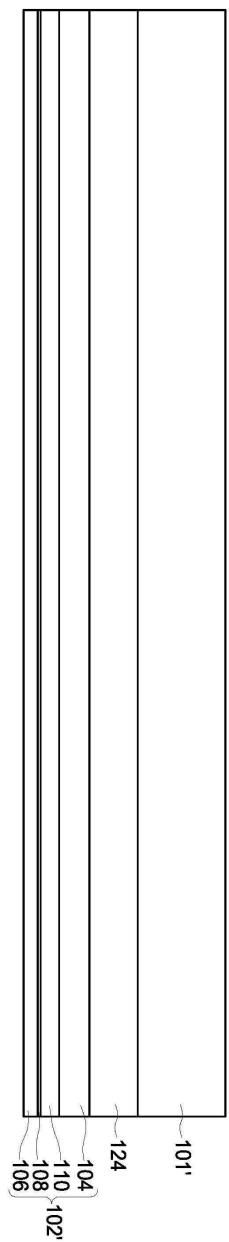

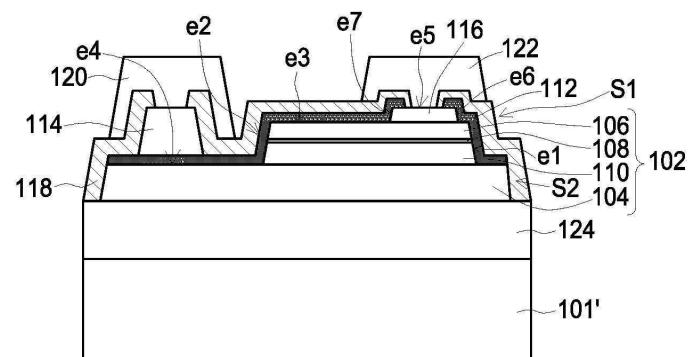

- 도 2a는 본 개시의 일 실시예에 따른 반도체 소자의 개략적인 평면도이고, 도 2b는 도 2a의 X-X` 선에 따른 반도체 소자의 개략적인 단면 구조도이다.

- 도 3a 내지 도 3j는 본 개시의 일 실시예에 따른 반도체 소자의 개략적인 제조 방법을 나타내는 도면이다.

- 도 3k는 본 개시의 일 실시예에 따른 반도체 소자의 개략적인 단면 구조도이다.

- 도 3l은 본 개시의 일 실시예에 따른 반도체 소자의 개략적인 단면 구조도이다.

- 도 3m은 본 개시의 일 실시예에 따른 반도체 소자의 개략적인 단면 구조도이다.

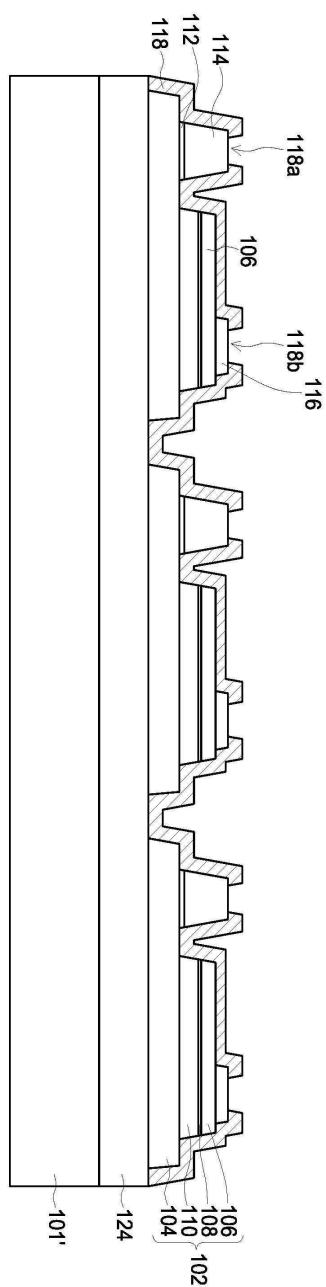

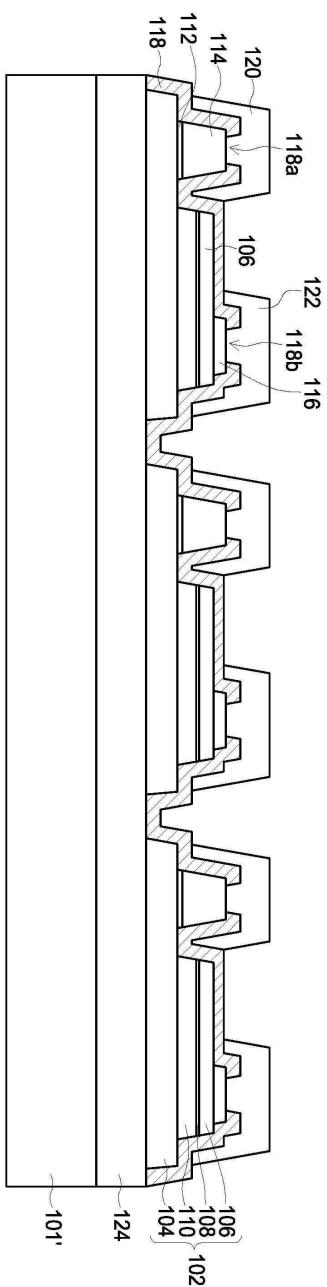

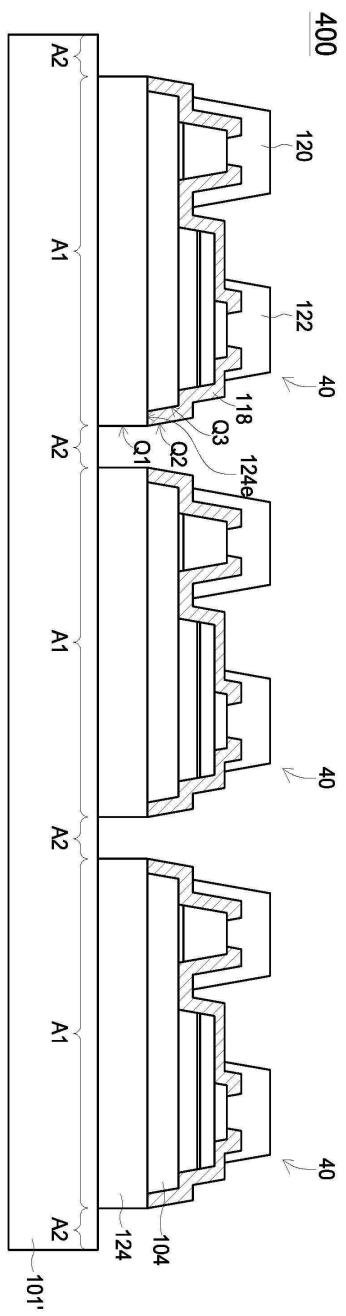

- 도 4a는 본 개시의 일 실시예에 따른 반도체 장치의 개략적인 단면 구조도이다.

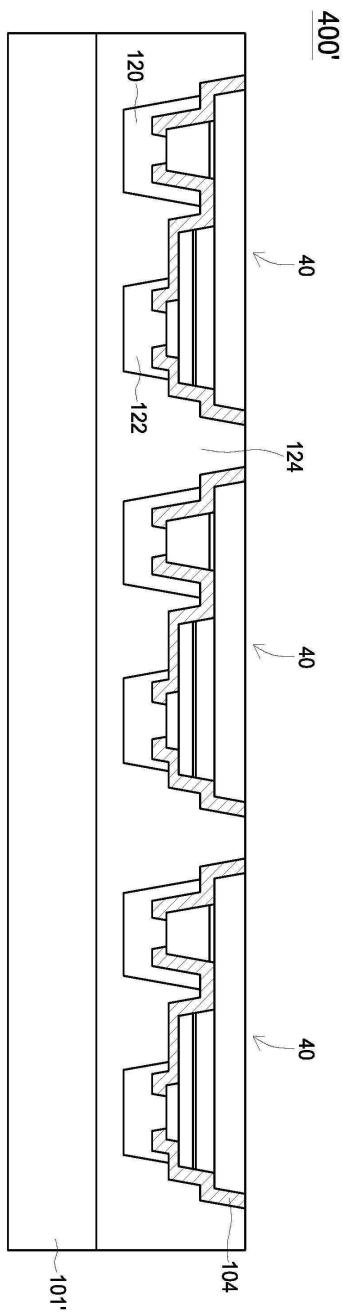

- 도 4b는 본 개시의 일 실시예에 따른 반도체 장치의 개략적인 단면 구조도이다.

- 도 5a는 본 개시의 일 실시예에 따른 디스플레이 패널의 개략적인 평면도이다.

- 도 5b 및 도 5c는 본 개시의 일 실시예에 따른 디스플레이 패널의 개략적인 부분 단면 구조도이다.

- 도 5d 및 도 5e는 본 개시의 일 실시예에 따른 디스플레이 패널의 개략적인 부분 단면 구조도이다.

### 발명을 실시하기 위한 구체적인 내용

- [0014] 이하의 실시예들은 도면과 함께 본 개시의 개념을 설명한다. 도면 또는 설명에 있어서, 유사하거나 동일한 구성 요소들은 유사하거나 동일한 부호를 사용하여 설명된다. 또한, 특별히 설명하지 않는 한, 도면의 각 소자들의 형상 또는 크기는 예시에 불과하며, 실제로 이에 제한되는 것은 아니다. 특히, 도면에 도시되지 않았거나 설명되지 않은 소자는 본 기술분야에서 통상적인 기술자에 의해 공지된 형태일 수 있다는 점에 유의해야 한다.

- [0015] 본 개시에서, 달리 설명되지 않는 한, 일반식 InGaP는  $In_{x_0}Ga_{1-x_0}P$ 를 나타내고, 여기서  $0 < x_0 < 1$ 이고; 일반식 AlInP는  $Al_{x_1}In_{1-x_1}P$ 를 나타내고, 여기서  $0 < x_1 < 1$ 이고; 일반식 AlGaInP는  $Al_{x_2}Ga_{x_3}In_{1-x_2-x_3}P$ 를 나타내고, 여기서  $0 < x_2 < 1$  및  $0 < x_3 < 1$ 이고; 일반식 InGaAsP는  $In_{x_4}Ga_{1-x_4}As_{x_5}P_{1-x_5}$ 를 나타내고, 여기서  $0 < x_4 < 1$  또  $0 < x_5 < 1$ 이고; 일반식 AlGaInAs는  $Al_{x_6}Ga_{x_7}In_{1-x_6-x_7}As$ 를 나타내고, 여기서  $0 < x_6 < 1$  또  $0 < x_7 < 1$ 이고; 일반식 InGaAs는  $In_{x_8}Ga_{1-x_8}As$ 를 나타내고, 여기서  $0 < x_8 < 1$ 이고; 일반식 AlGaAs는  $Al_{x_9}Ga_{1-x_9}As$ 를 나타내고, 여기서  $0 < x_9 < 1$ 이고; 일반식 InGaN은  $In_{x_{10}}Ga_{1-x_{10}}N$ 을 나타내고, 여기서  $0 < x_{10} < 1$ 이고; 일반식 AlGaN은  $Al_{x_{11}}Ga_{1-x_{11}}N$ 을 나타내고, 여기서  $0 < x_{11} < 1$ 이고; 일반식 AlGaAsP는  $Al_{x_{12}}Ga_{1-x_{12}}As_{x_{13}}P_{1-x_{13}}$ 을 나타내고, 여기서  $0 < x_{12} < 1$  또  $0 < x_{13} < 1$ 이고; 일반식 InGaAsN은  $In_{x_{14}}Ga_{1-x_{14}}As_{x_{15}}N_{1-x_{15}}$ 를 나타내고, 여기서  $0 < x_{14} < 1$  또  $0 < x_{15} < 1$ 이고; 일반식 AlInGaN은  $Al_{x_{16}}In_{x_{17}}Ga_{1-x_{16}-x_{17}}N$ 을 나타내고, 여기서  $0 < x_{16} < 1$  또  $0 < x_{17} < 1$ 이다. 상이한 목적에 따라 각 원소의 함유량은 조절할 수 있으며, 예를 들어, 에너지 준위를 조절하는 것에 한정되지 않으며, 또는, 반도체 소자가 발광 소자일 경우, 이에 의해 발광 소자의 피크 파장(peak wavelength) 또는 주파장(domain wavelength)을 조절할 수 있다.

- [0016] 본 개시의 반도체 소자는, 예를 들어, 발광 소자(예를 들어, 발광 다이오드(light-emitting diode) 또는 레이저 다이오드(laser diode))와 같은 광전 소자, 광 흡수 소자(예를 들어, 포토다이오드(photo-detector) 또는 태양 전지(solar cell))이며, 비-광전 소자(non-optoelectric device)일 수도 있다. 본 개시의 반도체 소자에 포함되는 각 층 조성 및/또는 도편트(dopant)는 이차이온질량분석기(secondary ion mass spectrometer, SIMS), 에너지 분산형 X선 분광계(Energy-dispersive X-ray spectroscopy, EDX), X선 광전자 분광계(X-ray

photoelectron spectroscopy, XPS) 또는 자외선 광전자 분광계(Ultraviolet Photoelectron Spectroscopy, UPS)와 같은 임의의 적절한 방식으로 분석하여 얻을 수 있다. 각 층의 두께 등 사이즈는, 투과전자현미경(transmission electron microscopy, TEM), 주사 전자 현미경(scanning electron microscope, SEM) 또는 주사 투과 전자 현미경(scanning transmission electron microscope, STEM)과 같은 임의의 적절한 방식으로 분석하여 얻을 수 있다.

[0017] 당업자라면 아래에 설명하는 각 실시예들에 근거해 다른 구성요소를 추가할 수 있음을 이해할 수 있다. 예를 들어, 특별히 설명하지 않는 한, "제 1 층(또는 구조)가 제 2 층(또는 구조) 위에 위치한다"와 같은 설명은 제 1 층(또는 구조)과 제 2 층(또는 구조)가 직접 접촉하는 실시예를 포함할 수 있고, 제 1 층(또는 구조)과 제 2 층(또는 구조)가 직접 접촉하지 않고, 그 사이에 기타 구조를 갖는 실시예를 포함할 수도 있다. 또한, 각 층(또는 구조)의 상하 위치 관계 등은 서로 다른 방향에서 관찰함에 따라 변경될 수 있음을 이해해야 한다.

[0018] 또한, 본 개시에서, 1층 또는 구조가 "대체로 M로 조성된다"라는 서술은 상기 층 또는 구조의 주요 조성이 M인 것을 나타내며, 상기 층 또는 구조가 도편트 또는 불가피한 불순물(impurities)을 포함하는 것을 배제하지 않는다.

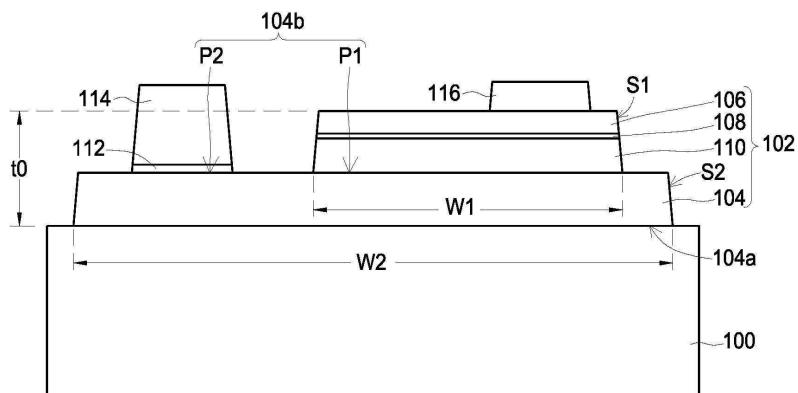

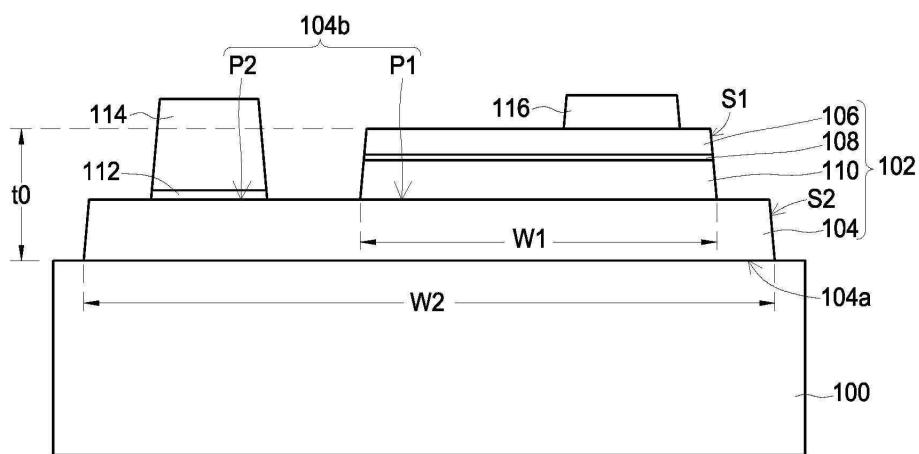

[0019] 도 1은 본 개시의 일 실시예에 따른 반도체 소자(10)의 개략적인 단면 구조도이다. 도 1에 도시된 바와 같이, 반도체 소자(10)는 베이스(100), 베이스(100) 위에 위치하는 반도체 구조(102)를 포함한다. 반도체 구조(102)는 에피택셜 구조일 수 있고, 제 1 반도체 층(104), 제 2 반도체 층(106) 및 제 1 반도체 층(104)과 제 2 반도체 층(106) 사이에 위치하는 활성 영역(108)을 포함할 수 있다. 일 실시예에서, 반도체 구조(102)는 활성 영역(108)과 제 1 반도체 층(104) 사이에 위치하는 제 3 반도체 층(110)을 더 포함한다. p형 또는 n형 층(접촉 층)(112)은 제 1 반도체 층(104) 위에 위치한다. 도 1에 도시된 바와 같이, 반도체 구조(102) 위에 제 1 금속 원소를 함유하는 구조(114) 및 제 2 금속 원소를 함유하는 구조(116)가 설치되어 있다. 구체적으로, 제 1 반도체 층(104)은 베이스(100)를 향하는 제 1 표면(104a) 및 제 1 금속 원소를 함유하는 구조(114) 및 제 2 금속 원소를 함유하는 구조(116)를 향하는 제 2 표면(104b)을 갖는다. 제 2 표면(104b)은 제 1 부분(P1) 및 제 2 부분(P2)을 포함한다.

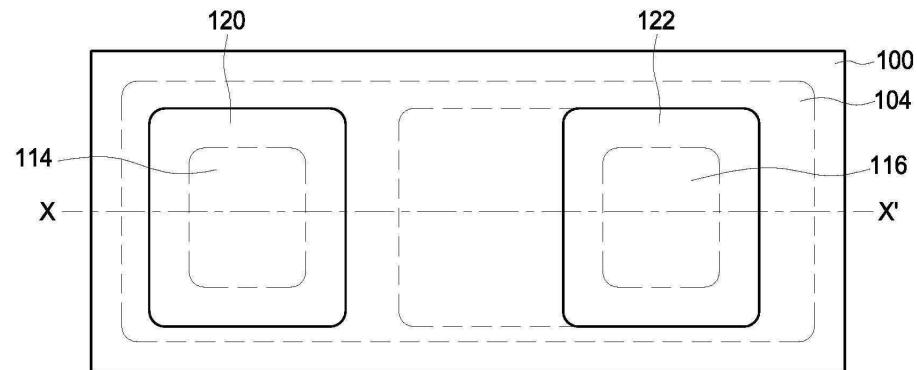

[0020] 일 실시예에서, 제 2 반도체 층(106), 활성 영역(108) 및 제 3 반도체 층(110)은 제 2 부분(P2)에 위치하지 않고 제 1 부분(P1)에 위치한다. p형 또는 n형 층(112)은 제 1 부분(P1)에 위치하지 않고 제 2 부분(P2)에 위치하며, 제 1 금속 원소를 함유하는 구조(114)는 이 p형 또는 n형 층(112) 위에 위치한다. 구체적으로, 이 p형 또는 n형 층(112)은 제 1 금속 원소를 함유하는 구조(114)와 제 1 반도체 층(104) 사이에 위치하면서, 제 1 금속 원소를 함유하는 구조(114)와 제 1 반도체 층(104)에 직접 접촉한다. 일 실시예에서, 제 1 반도체 층(104) 위에서 제 2 반도체 층(106), 활성 영역(108) 및 제 3 반도체 층(110)은 제 1 메사 구조(mesa structure)(S1)를 형성하고, 제 1 반도체 층(104)은 제 2 메사 구조(S2)를 형성한다. 도 1에 도시된 바와 같이, 제 1 메사 구조(S1)는 제 1 폭(W1)을 가지고, 제 2 메사 구조(S2)는 제 1 폭(W1)보다 큰 제 2 폭(W2)을 갖는다. 제 1 폭(W1)은 제 1 메사 구조(S1)의 최대 폭이고, 제 2 폭(W2)은 제 2 메사 구조(S2)의 최대 폭이다. 제 1 메사 구조(S1) 및 제 2 메사 구조(S2)는 각각 단면도에서 사다리꼴 형상 또는 직사각형 형상을 가질 수 있다.

[0021] 일 실시예에서, 제 1 메사 구조(S1)의 측면은 단면도에서 제 2 메사 구조(S2)의 측면과 동일 평면에 있지 않다. 일 실시예에서, 제 1 메사 구조(S1) 및 제 2 메사 구조(S2)는, 포인트 방전(point discharge)을 감소시키고 안정성을 개선하기 위해 평면도에서 각각 동근 직사각형 형상을 가질 수 있다. 일 실시예에서, 반도체 소자(10)는 평면도에서  $150\text{ }\mu\text{m}$  또는  $100\text{ }\mu\text{m}$  미만의 길이 및  $150\text{ }\mu\text{m}$  또는  $100\text{ }\mu\text{m}$  미만의 폭을 가질 수 있다. 반도체 소자(10)의 길이와 폭의 비는 0.3 내지 1의 범위에 있을 수 있다.

[0022] 베이스(100)는 도전성 또는 절연 재료를 포함할 수 있다. 상기 도전성 재료는 갈륨 비화물(GaAs), 인듐 인화물(InP), 실리콘 탄화물(SiC), 갈륨 인화물(GaP), 아연 산화물(ZnO), 갈륨 질화물(GaN), 알루미늄 질화물(AlN), 게르마늄(Ge) 또는 실리콘(Si) 등을 포함하고, 상기의 절연 재료는 사파이어(Sapphire) 등을 포함한다. 일 실시예에서, 베이스(100)는 성장 기판이고, 다시 말해서, 반도체 구조(102)는 유기금속화학증착법(metal organic chemical vapor deposition, MOCVD)에 의해 베이스(100) 상에 에피택셜 방식으로 형성된다. 일 실시예에 있어서, 베이스(100)는 성장 기판이 아니라 접합 기판이고, 접합 구조(124)를 통해 반도체 구조(102)에 접합될 수 있다(도 2b에 도시된 바와 같다). 일 실시예에 있어서, 반도체 소자(10)는 베이스(100)를 가지지 않을 수 있다. 반도체 구조(102)의 총 두께(t0)는  $10\text{ }\mu\text{m}$  이하일 수 있다. 총 두께(t0)와 반도체 소자(10)의 길이 또는 폭의 비율은 0.3 또는 0.1 미만과 같이 0.5 이하일 수 있으며, 제조 과정에서, 반도체 소자(10)의 구조적 안정성을 확보한다.

[0023]

일 실시예에 있어서, 제 1 반도체 층(104)은 제 1 도편트를 포함하고, 제 2 반도체 층(106)은 제 2 도편트를 포함하여, 제 1 반도체 층(104) 및 제 2 반도체 층(106)이 상이한 도전 형태를 갖도록 한다. 예를 들어, 제 1 반도체 층(104)은 n형이고, 제 2 반도체 층(106)은 p형이거나; 또는, 제 1 반도체 층(104)은 p형이고, 제 2 반도체 층(106)은 n형이다. 일 실시예에 있어서, 제 1 도편트 및 제 2 도편트는 각각 주기율표에서 제 II 족, 제 IV 족 또는 제 VI 족 원소를 포함할 수 있다. 예를 들어, 제 1 도편트 및 제 2 도편트는 각각 C, Zn, Si, Ge, Sn, Se, Mg 또는 Te를 포함할 수 있다. 제 1 반도체 층(104) 및 제 2 반도체 층(106)은 각각 전자 및 정공, 또는 정공 및 전자를 제공한다. 일 실시예에 있어서, 제 3 반도체 층(110)은 제 1 반도체 층(104)과 동일한 도전형태를 갖는다. 일 실시예에 있어서, 제 1 반도체 층(104), 제 2 반도체 층(106), 활성 영역(108) 및 제 3 반도체 층(110)은 각각 III-V족 반도체 재료를 포함한다. 일 실시예에 있어서, 상기 III-V족 반도체 재료는 원소 Al, Ga, As, P, N 또는 In을 포함한다. 구체적으로, 일 실시예에 있어서, 상기 III-V족 반도체 재료는, 2원 화합물 반도체(예를 들어, GaAs, GaP 또는 GaN), 3원 화합물 반도체(예를 들어, InGaAs, AlGaAs, InGaP, AlInP, InGaN 또는 AlGaN) 또는 4원 화합물 반도체(예를 들어, AlGaInAs, AlGaInP, AlInGaN, InGaAsP, InGaAsN 또는 AlGaAsP)일 수 있다. 일 실시예에 있어서, 활성 영역(108)은 대체로 3원 화합물 반도체(예를 들어, InGaAs, AlGaAs, InGaP, AlInP, InGaN 또는 AlGaN) 또는 4원 화합물 반도체(예를 들어, AlGaInAs, AlGaInP, AlInGaN, InGaAsP, InGaAsN 또는 AlGaAsP)로 구성된다. 일부 실시예에 있어서, 제 1 반도체 층(104), 제 2 반도체 층(106), 활성 영역(108) 및 제 3 반도체 층(110)은 원소 N을 포함하지 않는다. 일부 실시예에 있어서, 제 1 반도체 층(104), 제 2 반도체 층(106), 활성 영역(108) 및 제 3 반도체 층(110)은 각각 인화물(phosphide compound) 또는 비소화물(arsenide compound)을 포함한다.

[0024]

일 실시예에 따르면, 반도체 소자(10)가 발광 소자이고, 반도체 소자(10)가 작동할 때, 활성 영역(108)은 광선을 방출할 수 있다. 상기 광선은 가시광 또는 비가시광을 포함한다. 반도체 소자(10)에서 방출되는 피크 파장(peak wavelength)은 활성 영역(108)의 재료 구성에 의해 결정된다. 활성 영역(108)의 재료는, 3원 화합물 반도체(예를 들어, InGaN, InGaAs, AlGaN, AlGaAs 또는 InGaP) 또는 4원 화합물 반도체(예를 들어, InGaAsP, AlGaInAs 또는 AlGaInP)를 포함할 수 있다. 일 실시예에 따르면, 반도체 소자(10)는 400nm 내지 490nm의 피크 파장을 갖는 청색 광 또는 남색 광, 490nm 내지 550nm의 피크 파장을 갖는 녹색 광, 250nm 내지 400nm의 피크 파장을 갖는 자외광, 610nm 내지 700nm의 피크 파장을 갖는 적색 광, 530nm 내지 600nm의 피크 파장을 갖는 황색 광, 또는 700nm 내지 1700nm의 피크 파장을 갖는 적외광을 방출할 수 있다.

[0025]

제 1 금속 원소를 함유하는 구조(114) 및 제 2 금속 원소를 함유하는 구조(116)는 각각 단일 층 또는 복수 층일 수 있다. 제 1 금속 원소를 함유하는 구조(114) 및 제 2 금속 원소를 함유하는 구조(116)는 모두 접촉부로 할 수 있다. 일부 실시예에 의하면, 제 1 금속 원소를 함유하는 구조(114) 및 제 2 금속 원소를 함유하는 구조(116)는 외부 전원(도시하지 않음)과 전기적으로 연결될 수 있거나, 또는 기타 구조(후술하는 제 1 전극 패드(120) 및 제 2 전극 패드(122))를 통해 외부 전원(도시하지 않음)과 전기적으로 연결될 수 있다. 단면에 있어서, 제 1 금속 원소를 함유하는 구조(114) 및 제 2 금속 원소를 함유하는 구조(116)는 각각 사다리꼴 형상 또는 직사각형 형상을 가질 수 있다. 일 실시예에 있어서, 제 1 금속 원소를 함유하는 구조(114)는 제 1 금속 원소(M1)를 포함하고, 제 2 금속 원소를 함유하는 구조(116)는 제 2 금속 원소(M2)를 포함한다. 제 1 금속 원소(M1) 및 제 2 금속 원소(M2)는 동일하거나 상이할 수 있다. 일 실시예에 있어서, 제 1 금속 원소를 함유하는 구조(114)는 베릴륨(Be)을 함유하지 않는다.

[0026]

일 실시예에 있어서, 제 1 금속 원소를 함유하는 구조(114)는 제 1 금속 원소(M1)와 상이한 제 3 금속 원소(M3)를 더 포함한다. 일 실시예에 있어서, 제 1 금속 원소를 함유하는 구조(114)는 제 1 금속 원소(M1) 및 제 3 금속 원소(M3)를 함유하는 합금을 포함한다. 일 실시예에 있어서, 제 1 금속 원소를 함유하는 구조(114)는 p형 또는 n형 층(112)에 직접 접촉하는 제 1 층 및 제 1 층 위에 위치하는 제 2 층을 포함할 수 있다. 일 실시예에 있어서, 제 1 층은 제 1 금속 원소(M1)를 포함하고, 제 2 층은 제 3 금속 원소(M3)를 포함한다. 일 실시예에 있어서, 제 2 금속 원소를 함유하는 구조(116)는 제 2 금속 원소(M2)와 상이한 제 4 금속 원소(M4)를 더 포함한다. 일 실시예에 있어서, 제 2 금속 원소를 함유하는 구조(116)는 제 2 금속 원소(M2) 및 제 4 금속 원소(M4)를 함유하는 합금을 포함한다. 일 실시예에 있어서, 제 2 금속 원소를 함유하는 구조(116)는 제 2 반도체 층(106)에 직접 접촉하는 제 3 층 및 제 3 층 위에 위치하는 제 4 층을 포함할 수 있다. 일 실시예에 있어서, 제 3 층은 제 2 금속 원소(M2)를 포함하고, 제 4 층은 제 4 금속 원소(M4)를 포함한다. 일 실시예에 있어서, 제 3 금속 원소(M3) 및 제 4 금속 원소(M4)는 동일할 수 있다. 일 실시예에 있어서, 제 1 금속 원소(M1), 제 2 금속 원소(M2), 제 3 금속 원소(M3) 및 제 4 금속 원소(M4)는 각각 Ti, Ni, Al, Zn, Ge, Mo, W, V, Ga, Au 또는 Ag로부터 선택될 수 있다.

[0027]

일 실시예에 있어서, 제 1 금속 원소를 함유하는 구조(114)는 제 1 반도체 층(104)에 직접 접촉하지 않는다. 제 1 금속 원소를 함유하는 구조(114)는 p형 또는 n형 층(112)을 통해 제 1 반도체 층(104)에 전기적으로 연결될 수 있다. 일 실시예에 있어서, p형 또는 n형 층(112)의 재료는 수직 방향에서 제 1 접촉 저항률(contact resistivity)을 가지고, 수평 방향에서 제 2 접촉 저항률을 갖는다. 제 2 접촉 저항률은 제 1 접촉 저항률보다 클 수 있기 때문에, 전류가 주로 수직 방향을 따라 p형 또는 n형 층(112)을 통과하게 되고, p형 또는 n형 층(112)은 제 1 금속 원소를 함유하는 구조(114) 및 제 1 반도체 층(104)에 전기적으로 연결된다. 일부 실시예에 있어서, 제 1 접촉 저항률 및 제 2 접촉 저항률은, 예를 들어  $\Omega \cdot \text{cm}^2$ 를 단위로 측정될 수 있다. 일부 실시예에 있어서, p형 또는 n형 층(112)이 제 1 반도체 층(104)과 상이하거나 동일한 도전형태를 가질 때, p형 또는 n형 층(112)은 터널층으로 할 수 있다. 일부 실시예에 있어서, p형 또는 n형 층(112)이 제 1 반도체 층(104)과 동일한 도전형태를 가질 때, p형 또는 n형 층(112)은 제 1 반도체 층(104)과 제 1 금속 원소를 함유하는 구조(114) 사이의 에너지 장벽(energy barrier)(예를 들어, 쇼트키 장벽(Schottky barrier))을 더 감소시킬 수 있다. 일 실시예에 있어서, p형 또는 n형 층(112)은 수직 방향에서 활성 영역(108)과 중첩되지 않는다. 일 실시예에 있어서, 제 1 반도체 층(104)은, 제 1 반도체 층(104)과 제 1 금속 원소를 함유하는 구조(114) 사이의 접촉 저항을 감소시키도록  $1 \times 10^{19}/\text{cm}^3$  이상의 도편트 농도를 갖는다.

[0028]

제 1 반도체 층(104)의 재료는 전도대(conduction band) 및 가전자대(valence band)를 가지고, 전도대의 하단에지는  $E_c$ 로 표시하고, 가전자대의 상단에지는  $E_v$ 로 표시한다. p형 또는 n형 층(112)의 재료는 제 1 일함수(WF1)를 가지고, 제 1 금속 원소(M1)는 제 2 일함수(WF2)를 갖는다. 일부 실시예에 있어서, 제 1 반도체 층(104)의 도전형태가 n형일 때, 제 1 일함수(WF1)는  $WF1 < (E_c + E_v)/2$ 를 충족한다. 일부 실시예에 있어서, 제 1 반도체 층(104)의 도전형태가 p형일 때, 제 1 일함수(WF1)는  $WF1 > (E_c + E_v)/2$ 를 충족한다. 일부 실시예에 있어서, p형 또는 n형 층(112)의 도전형태가 n형일 때, 제 2 일함수(WF2)는 제 1 일함수(WF1)보다 크다. 일부 실시예에 있어서, p형 또는 n형 층(112)의 도전형태가 p형일 때, 제 1 일함수(WF1)는 제 2 일함수(WF2)보다 크다. 일부 실시예에 있어서, 상술한 관계들을 충족하는 제 1 반도체 층(104), p형 또는 n형 층(112) 및 제 1 금속 원소를 함유하는 구조(114)의 재료를 사용함으로써, p형 또는 n형 층(112)과 제 1 금속 원소를 함유하는 구조(114) 사이의 접촉 저항률(contact resistivity)이 더 개선될 수 있다. 일 실시예에 있어서, p형 또는 n형 층(112)의 재료는, p형 또는 n형 층(112)이 활성 영역(108)으로부터 방출되는 광을 흡수하는 것을 방지하도록 제 1 반도체 층(104)의 밴드갭(bandgap)보다 큰 밴드갭을 갖는다. 일 실시예에 있어서, p형 또는 n형 층(112)의 재료는 산소(O) 원소 및 제 5 금속 원소(M5)를 포함한다. 일 실시예에 있어서, 제 5 금속 원소(M5)와 제 1 금속 원소(M1) 또는 제 3 금속 원소(M3)는 동일하며, 이에 의해, p형 또는 n형 층(112)과 제 1 금속 원소를 함유하는 구조(114) 사이의 부착이 더 개선될 수 있고, 반도체 소자(10)의 열 안정성(thermal stability)도 향상될 수 있다. 일 실시예에 있어서, 제 5 금속 원소(M5)는 In, Ti, Al, Zn, Ni, Ga, Mo, V, W, 또는 Nb이다.

[0029]

p형 또는 n형 층(112)에 함유된 금속 원소에 관하여, p형 또는 n형 층(112) 중에 단일 종류의 금속 원소만 포함할 수 있다. 상기 금속 원소는 In, Ti, Al, Zn, Ni, Ga, Mo, V, W 또는 Nb를 포함할 수 있다. 일부 실시예에 있어서, p형 또는 n형 층(112)은 2종 이상의 금속 원소를 포함한다. 예를 들어, 일 실시예에 있어서, p형 또는 n형 층(112)은 제 5 금속 원소(M5)와 상이한 제 6 금속 원소(M6)를 더 포함한다. 제 5 금속 원소(M5) 및 제 6 금속 원소(M6)는 각각 In, Ti, Al, Zn, Ni, Ga, Mo, V, W 또는 Nb일 수 있다. 일 실시예에 있어서, p형 또는 n형 층(112)은 V족 원소(예를 들어, N, P 또는 As)를 더 포함한다. 구체적으로, 일 실시예에 있어서, p형 또는 n형 층(112)은 산소 원소 및 제 5 금속 원소(M5)에 의해 형성된 제 1 금속 산화물(metal oxide compound)을 더 포함할 수 있다. 일 실시예에 있어서, p형 또는 n형 층(112)은 산소 원소 및 제 6 금속 원소(M6)에 의해 형성된 제 2 금속 산화물을 더 포함할 수 있다. 일 실시예에 있어서, p형 또는 n형 층(112)은 산소 원소 및 V족 원소에 의해 형성된 제 3 금속 산화물을 더 포함할 수 있다. 예를 들어, 제 1 금속 산화물 또는 제 2 금속 산화물은 n형(예를 들어,  $TiO_x$ ,  $InO_x$ ,  $MoO_x$ ,  $VO_x$ ,  $WO_x$ ,  $GaO_x$  또는  $NbO_x$ ) 또는 p형(예를 들어,  $NiO_x$ )일 수 있다. 제 3 금속 산화물은  $PO_x$ ,  $NO_x$  또는  $AsO_x$ 일 수 있다. 일 실시예에 있어서, p형 또는 n형 층(112)은 0nm보다 크고 20nm 이하인 두께를 갖는다. 예를 들어, p형 또는 n형 층(112)의 두께는, 1nm, 2nm, 3nm, 4nm, 5nm, 6nm, 7nm, 8nm, 9nm, 10nm, 11nm, 12nm, 13nm, 또는 14nm와 같이 0.5nm 내지 15nm의 범위 내에 있을 수 있다. 일부 실시예에 있어서, p형 또는 n형 층(112)의 두께가 5nm 이하일 때, 제 1 금속 원소를 함유하는 구조(114)와 제 1 반도체 층(104) 사이의 접촉 저항률은 터널링 효과(tunneling effect)를 통해 개선될 수 있다.

[0030]

일부 실시예에 있어서, 제 1 반도체 층(104)이 인화물 또는 비소화물을 포함할 때, p형 또는 n형 층(112)의 존재는 제 1 반도체 층(104)과 제 1 금속 원소를 함유하는 구조(1M)가 직접 접촉되어 계면 화합물(interfacial

compound)을 형성하는 것을 방지할 수 있다. 예를 들어, 제 1 금속 원소를 함유하는 구조(114)가 Au를 포함하고 제 1 반도체 층(104)이 인화물(예를 들어, GaP)일 때, 상기 계면 화합물은 활성 영역(108)의 재료의 밴드갭 에너지(bandgap energy)보다 작은 밴드갭 에너지를 갖는  $\text{Au}_2\text{P}_3$ 일 수 있고, 따라서, 활성 영역(108)으로부터 방출되는 광을 흡수할 수 있다.

[0031] 도 2a는 본 개시의 일 실시예에 따른 반도체 소자(20)의 평면을 나타내는 도면이다. 도 2b는 도 2a의 X-X` 선에 따른 반도체 소자(20)의 개략적인 단면 구조도이다. 명확하게 도시하기 위해, 도 2a에는 설명에 필요한 어셈블리만 나타낸다(도면에 표시된 바와 같음).

[0032] 반도체 소자(20)와 반도체 소자(10)는, 반도체 소자(20)가 반도체 구조(102) 위에 위치하는 절연 구조(118), 제 1 금속 원소를 함유하는 구조(114)에 연결된 제 1 전극 패드(120), 제 2 금속 원소를 함유하는 구조(116)에 연결된 제 2 전극 패드(122) 및 제 1 반도체 층(104) 아래에 위치하는 접합 구조(124)를 더 포함하는 점에서 구별된다. 일 실시예에 있어서, 절연 구조(118)는 반도체 구조(102), 제 1 금속 원소를 함유하는 구조(114) 및 제 2 금속 원소를 함유하는 구조(116)를 대체로 등각으로 커버한다. 도 2b에 도시된 바와 같이, 절연 구조(118)는 제 1 개구(118a) 및 제 2 개구(118b)를 갖는다. 제 1 금속 원소를 함유하는 구조(114)는 제 1 개구(118a)를 통해 제 1 전극 패드(120)에 직접 접촉되고, 제 2 금속 원소를 함유하는 구조(116)는 제 2 개구(118b)를 통해 제 2 전극 패드(122)에 직접 접촉된다.

[0033] 제 1 전극 패드(120) 및 제 2 전극 패드(122)는 외부 전원(도시하지 않음)과의 전기적 연결을 위해 사용될 수 있고, 와이어 접합(wire-bonding) 또는 솔더 접합(solder bonding)과 같은 공정에서 발생하는 스트레스(stress)를 흡수하기 위한 완충 작용을 할 수 있다. 제 1 전극 패드(120)의 상면은 제 2 전극 패드(122)의 상면과 대체로 동일한 수평(허용 오차 약  $\pm 1\mu\text{m}$ )에 있을 수 있다. 일 실시예에 있어서, 제 1 전극 패드(120)는 절연 구조(118)의 일부를 커버하고, 제 1 개구(118a)를 채우며, 제 2 전극 패드(122)는 절연 구조(118)의 일부를 커버하고, 제 2 개구(118b)를 채운다. 일부 실시예에 있어서, 제 1 메사 구조(S1), 절연 구조(118) 및 제 1 전극 패드(122)는 수직 방향에서 중첩될 수 있다. 제 1 전극 패드(120) 및 제 2 전극 패드(122)는 각각 단일 층 또는 복수 층일 수 있다. 일 실시예에 있어서, 제 1 전극 패드(120) 및 제 2 전극 패드(122)의 재료는 Ni, Ti, Pt, Pd, Ag, Au, Al, Sn 또는 Cu를 포함하거나, 또는 상기 원소들의 합금을 포함한다.

[0034] 절연 구조(118)는 반도체 구조(102)를 수분 또는 오염으로부터 보호할 수 있고, 반도체 소자(20)의 신뢰성(reliability)을 개선할 수 있다. 일 실시예에 있어서, 절연 구조(118)는 산화물(예를 들어,  $\text{SiO}_2$ ) 또는 질화물(예를 들어,  $\text{SiN}_x$ )과 같은 유전체를 포함한다. 일 실시예에 있어서, 절연 구조(118)는 굴절율이 상이한 2종 이상의 반도체 재료를 교대로 적층하여 형성된 분산형 브래그 반사기(distributed Bragg reflector, DBR)와 같은 반사 구조를 포함한다. 일 실시예에 있어서, 절연 구조(118)는 반도체 구조(102)의 전체 두께(t0)의 15% 미만 또는 10% 미만인 두께(t1)를 갖는다.

[0035] 접합 구조(124)는 전기 절연(electrically-insulative) 구조일 수 있다. 일 실시예에 있어서, 접합 구조(124)는 열경화성 폴리머(thermosetting polymer)를 함유하는 메인 층(main layer)(도시하지 않음)을 포함한다. 일 실시예에 있어서, 상기 열경화성 폴리머는, 폴리이미드(polyimide), 에폭시 수지(epoxy resin), 폴리에스테르(polyester), 폴리우레탄(polyurethane), 벤조시클로부텐(benzocyclobutene, BCB) 또는 이들의 조합을 포함한다. 일 실시예에 있어서, 접합 구조(124)는 메인 층과 제 1 반도체 층(104) 사이, 또는 메인 층과 베이스(100) 사이에 위치하는 보조 층(auxiliary layer)(도시하지 않음)을 더 포함하여 이들 사이의 부착을 더 개선한다. 보조 층의 재료는 메인 층의 재료와 상이할 수 있다. 일 실시예에 있어서, 보조 층의 재료는 산화물(예를 들어,  $\text{SiO}_2$ ) 또는 질화물(예를 들어,  $\text{SiN}_x$ )을 포함한다. 기타 각 층 또는 구조의 위치, 상대 관계 및 재료 구성 등에 대한 내용 및 구조 변화예에 대해서는 전술한 실시예에서 자세하게 설명하였으므로, 여기서, 반복하여 설명하지 않는다.

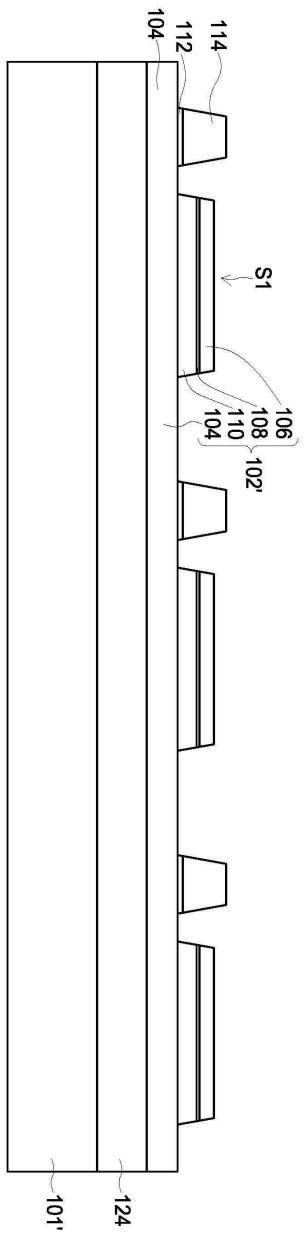

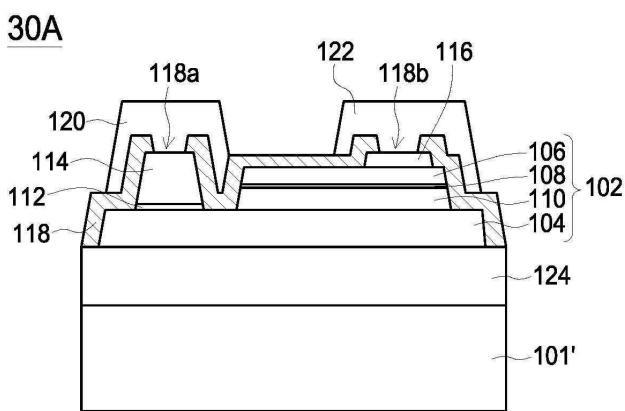

[0036] 도 3a 내지 도 3j는 본 개시의 일 실시예에 따른 반도체 소자(30A)의 제조 방법을 나타내는 도면이다. 제조 과정에서 복수의 반도체 소자가 형성될 수 있지만, 간소화를 위해, 이하 단락에서는 제조 과정에서의 단일 반도체 소자의 구조 변화에 대해 설명한다는 점에 유의해야 한다.

[0037] 도 3a에 도시된 바와 같이, 우선, 성장 기판(101)을 제공한다. 성장 기판(101)에 반도체 스택(102`)을 형성한다. 반도체 스택(102`)은 제 1 반도체 층(104), 제 2 반도체 층(106) 및 제 1 반도체 층(104)과 제 2 반도체 층(106) 사이에 위치하는 활성 영역(108)을 포함한다. 제 1 반도체 층(104)과 활성 영역(108) 사이에 제 3 반도체 층(110)이 형성되어 있다.

- [0038] 그 다음, 도 3b 및 도 3c를 참조하면, 접합 구조(124)를 통해 반도체 스택(102<sup>a</sup>)을 접합 기판(101<sup>a</sup>)에 접합하고, 성장 기판(101)을 제거한다.

- [0039] 이어서, 도 3d에 도시된 바와 같이, 제 1 반도체 층(104)의 일부를 노출시키고, 제 1 반도체 스택(104) 위에 제 1 메사 구조(S1)를 형성하도록, 도 3c의 구조를 반전하고 반도체 스택(102<sup>a</sup>)의 일부를 제거한다.

- [0040] 그 다음, 도 3e에 도시된 바와 같이, 제 1 반도체 층(104)의 노출된 부분에 p형 또는 n형 층(112)을 형성하고, 이 p형 또는 n형 층(112) 위에 제 1 금속 원소를 함유하는 구조(114)를 형성한다. 일 실시예에 있어서, p형 또는 n형 층(112)은 원자층 증착(atomic layer deposition, ALD) 또는 전자빔 증착(e-gun evaporation)과 같은 박막 증착(film deposition)에 의해 형성될 수 있다.

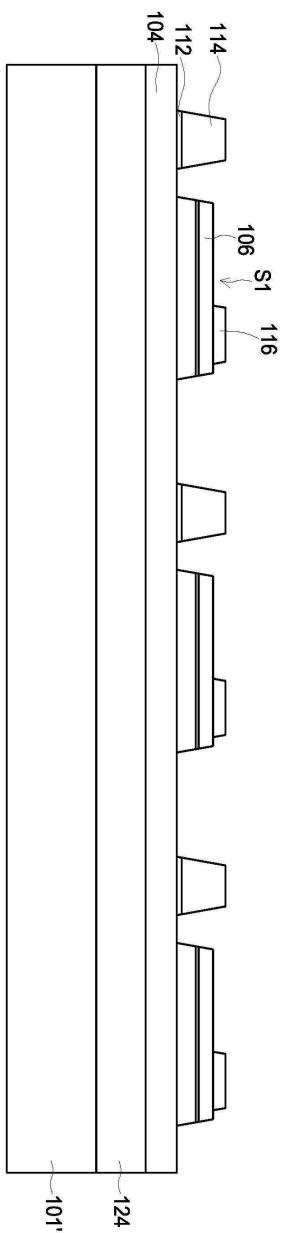

- [0041] 일 실시예에 있어서, 제 1 금속 원소를 함유하는 구조(114)를 형성하는 단계는, p형 또는 n형 층(112) 위에 제 1 금속 원소(M1)를 함유하는 구조를 형성하고, 제 1 온도에서 제 1 가열 단계를 수행하는 단계를 포함한다. 일 실시예에 있어서, 상기 가열 단계는 제 1 금속 원소(M1) 및 기타 금속 원소(예를 들어, 상술한 제 3 금속 원소(M3))를 함유하는 합금을 형성하기 위한 합금 제조 공정일 수 있다. 제 1 온도는 설비(예를 들어, 노(furnace))가 제 1 가열 단계에 제공하는 주변 온도일 수 있다. 일 실시예에 있어서, 제 1 온도는 접합 구조(124)에 포함된 열경화성 폴리머의 열 분해 온도 미만일 수 있거나, 또는 제 1 온도와 상기 열 분해 온도의 차이는 50°C 이하 또는 30°C 이하일 수 있으며, 이에 의해 프로세스 안정성(process stability)이 보장될 수 있다. 상기 열 분해 온도는 상기 열경화성 폴리머의 한시간 내의 중량 손실(weight loss)이 1%를 초과하는 온도일 수 있다.

- [0042] 도 3f 및 도 3g에 도시된 바와 같이, 제 1 메사 구조(S1)에 제 2 금속 원소를 함유하는 구조(116)를 더 형성하고, 제 1 반도체 층의 일부를 제거하여 제 2 메사 구조(S2)를 형성한다. 제 2 금속 원소를 함유하는 구조(116)를 형성하는 단계는 제 2 반도체 층(106) 위에 제 2 금속 원소(M2)를 함유하는 구조를 형성하고, 제 2 온도에서 제 2 가열 단계를 수행하는 단계를 포함할 수 있다. 제 2 온도는 설비(예를 들어, 노)에서 제 2 가열 단계로 제공하는 주변 온도일 수 있다. 일 실시예에 있어서, 제 1 온도와 제 2 온도의 차이는 50°C 미만 또는 30°C 미만이다. 일 실시예에 있어서, 제 1 온도 및 제 2 온도는 각각 500°C 미만 또는 400°C 미만이다. 일 실시예에 있어서, 제 1 온도 및 제 2 온도는 각각 200°C 이상 또는 300°C 이상이다.

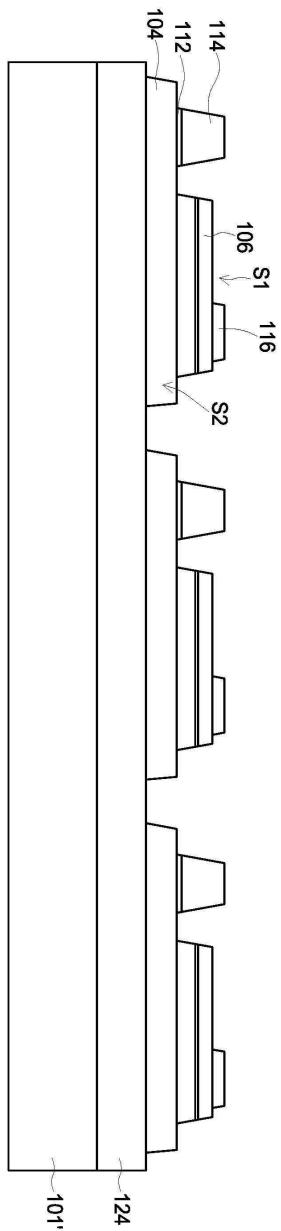

- [0043] 도 3h에 도시된 바와 같이, 이어서, 제 1 메사 구조(S1), 제 2 메사 구조(S2), 제 1 금속 원소를 함유하는 구조(114) 및 제 2 금속 원소를 함유하는 구조(116) 상에 절연 구조(118)를 등각으로 형성한다. 제 1 메사 구조(S1) 및 제 2 메사 구조(S2)의 측벽은 모두 절연 구조(118)에 의해 커버되고, 이에 의해, 반도체 구조(102)가 완전히 보호될 수 있도록 한다. 절연 구조(118)의 일부를 제거함으로써 제 1 개구(118a) 및 제 2 개구(118b)를 형성한다.

- [0044] 다음으로, 도 3i에 도시된 바와 같이, 제 1 금속 원소를 함유하는 구조(114) 위에 제 1 전극 패드(120)를 형성하고, 제 2 금속 원소를 함유하는 구조(116) 위에 제 2 전극 패드(122)를 형성한다.

- [0045] 도 3i에 도시된 바와 같은 구조는 레이저 절단(laser cutting)과 같은 절단 방법에 의해 복수의 반도체 소자(30A)로 더 분리될 수 있다. 도 3j는 각 반도체 소자(30A)의 구조를 도시한다.

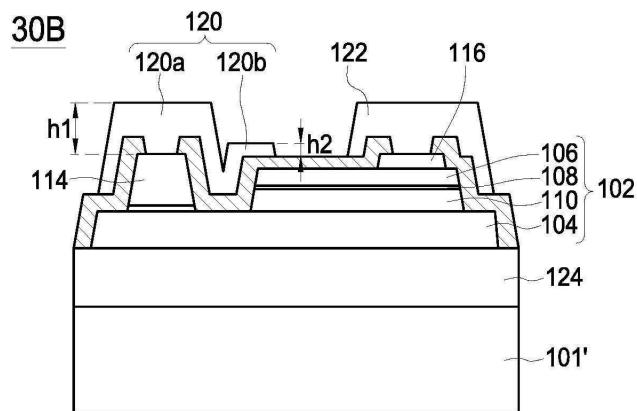

- [0046] 도 3k는 본 개시의 일 실시예에 따른 반도체 소자(30B)의 개략적인 단면 구조도이다. 도 3k에 도시된 바와 같이, 일 실시예에 있어서, 반도체 소자의 구조적 강도를 개선하기 위해, 제 1 전극 패드(120)도 제 1 메사 구조(S1)의 일부에 형성될 수 있다. 일 실시예에 있어서, 제 1 전극 패드(120)는 변하는 두께를 가질 수 있거나, 또는 제 1 전극 패드(120)는 평탄하지 않은(non-planar) 상면을 가질 수 있다. 도 3k에 도시된 바와 같이, 제 1 전극 패드(120)는 제 1 금속 원소를 함유하는 구조(114) 상에서 제 1 두께(h1)를 갖는 제 1 부분(120a) 및 제 1 메사 구조(S1) 상에서 제 2 두께(h2)를 갖는 제 2 부분(120b)을 포함할 수 있고, 제 2 두께(h2)는 제 1 두께(h1)보다 작을 수 있다.

- [0047] 도 3l은 본 개시의 일 실시예에 따른 반도체 소자(30C)의 개략적인 단면 구조도이다. 도 3l에 도시된 바와 같이, p형 또는 n형 층(112)은 반도체 구조(102)의 상면에 등각으로 형성된다. 일 실시예에 있어서, p형 또는 n형 층(112)은 제 1 금속 원소를 함유하는 구조(114), 제 2 금속 원소를 함유하는 구조(116) 및 절연 구조(118)에 직접 접촉된다. 구체적으로, 도 3l에 도시된 바와 같이, p형 또는 n형 층(112)은 제 1 메사 구조(S1)의 제 1 측면(e1), 제 2 측면(e2) 및 상면(e3), 및 제 2 메사 구조(S2)의 상면(e4)을 커버하면서 직접 접촉된다. 일 실시예에 있어서, p형 또는 n형 층(112)은 제 1 반도체 층(104)의 측벽을 커버하지 않는다. p형 또는 n형 층(112)은 제 2 금속 원소를 함유하는 구조(116)에 직접 접촉하고, 수직 방향에서 제 2 금속 원소를 함유하는 구조(116)와 중첩되지 않을 수 있다. 일 실시예에 있어서, p형 또는 n형 층(112)은 수직 방향에서 수평 방향에 비해

더 낮은 접촉 저항률을 가지기 때문에, 반도체 소자(30)의 작동 시, 제 2 금속 원소를 함유하는 구조(116)와 제 1 금속 원소를 함유하는 구조(114) 사이 또는 제 2 금속 원소를 함유하는 구조(116)와 제 1 반도체 층(104) 사이에 전류 경로(current path)를 형성하지 않게 한다. 도 3m은 본 개시의 일 실시예에 따른 반도체 소자(30D)의 단면을 나타내는 도면이다. 도 3m에 도시된 바와 같이, p형 또는 n형 층(112)은 제 2 금속 원소를 함유하는 구조(116)의 상면(e5)의 일부, 제 3 측면(e6) 및 제 4 측면(e7)을 추가로 커버할 수 있고, 이에 의해, 제 2 전극 패드(122)는 제 2 금속 원소를 함유하는 구조(116) 중 p형 또는 n형 층(112)에 의해 커버되지 않은 상면(e5)의 일부에 직접 접촉하게 된다. 도 3m에 도시된 구조를 형성하기 위해, 제조 공정에서, 먼저, 제 1 메사 구조(S1) 상에 제 2 금속 원소를 함유하는 구조(116)를 형성한 다음, 제 1 메사 구조(S1) 및 제 2 금속 원소를 함유하는 구조(116)의 일부에 위치하는 p형 또는 n형 층(112)을 형성하고, 나아가, p형 또는 n형 층(112)에 제 1 금속 원소를 함유하는 구조(114)를 추가로 형성한다.

[0048] 기타 각 층 또는 구조의 위치, 상대 관계 및 재료 구성 등 내용 및 구조 변화에는 전술한 실시예에서 자세하게 설명하였으므로, 여기서, 반복하여 설명하지 않는다.

[0049] 도 4a는 본 개시의 일 실시예에 따른 반도체 장치(400)의 개략적인 단면 구조도이다. 도 4b는 본 개시의 일 실시예에 따른 반도체 장치(400')의 개략적인 단면 구조도이다.

[0050] 도 4a 및 도 4b에 도시된 바와 같이, 반도체 장치(400) 또는 반도체 장치(400')는 복수의 반도체 소자(40)를 포함한다. 도 4a의 각 반도체 소자(40)의 구조는 상술한 반도체 소자(30A)의 구조와 유사하다. 구체적으로, 반도체 소자(40)는 본 개시의 임의의 실시예에서 기재된 반도체 소자(반도체 소자(10, 20, 30B, 30C 또는 30D))일 수 있다.

[0051] 도 4a 및 도 4b에서, 반도체 소자(40)는 성장 기판(101)을 가지지 않는다. 도 4a를 참조하면, 복수의 반도체 소자(40)는 접합 기판(101') 위에 배치된다. 일 실시예에 있어서, 접합 기판(101')은 접합 구조(124)에 의해 커버되는 제 1 영역(A1) 및 접합 구조(124)에 의해 커버되지 않는 제 2 영역(A2)을 포함한다. 구체적으로, 제 1 영역(A1)은 수직 방향에서 반도체 소자(40)와 중첩된다. 즉, 도 4a에서, 접합 구조(124)는 접합 기판(101') 위에 연속적으로 분포되지 않는다. 도 4a에서, 접합 구조(124)는 상부 에지(upper edge)(124e) 및 측벽(Q1)을 가지고, 절연 구조(118)는 측벽(Q1)을 커버하지 않고 상부 에지를 커버한다. 일 실시예에 있어서, 절연 구조(118)는 수직 방향에서 측벽(Q1)과 중첩되는 측벽(Q2)을 갖는다. 측벽(Q1)은 제 1 반도체 층(104)의 측벽(Q3)과 수직 방향에서 중첩되지 않는다. 일 실시예에 있어서, 접합 구조(124)에서 상부 에지 근접하는 상면은 절연 구조(118)에 의해 커버되지 않는다. 일 실시예에서, 접합 구조(124)는 제 1 반도체 층(104)의 폭 이하의 폭을 갖는다.

[0052] 도 4b는 복수의 반도체 소자(40)가 접합 구조(124) 내에 매입되는 다른 배치 방식을 도시한다. 여기서, 접합 구조(124)는 접합 기판(101') 위에 연속적으로 분포되고, 1개 이상의 반도체 소자(40)에 직접 접촉한다. 일부 실시예에 있어서, 운반 과정에서 반도체 소자(40) 내의 반도체 구조(102)를 보호할 수 있도록, 접합 구조(124)는 반도체 소자(40)를 소정의 위치에 고정하는데 유리할 수 있다.

[0053] 일 실시예에 있어서, 반도체 소자(40)와 접합 기판(101') 사이에 청색 테이프(blue tape), 열 방출 시트 또는 열 방출 테이프(thermal release sheet or tape), 또는 (UV)광 박리 막(light release tape)(폴리에틸렌 테레프탈레이트(polyethylene terephthalate, PET)를 설치할 수 있다. 구체적으로, 청색 테이프, 열 방출 시트 또는 열 방출 테이프, 또는 (UV)광 박리 막은 접합 구조(124)와 접합 기판(101') 사이에 설치되거나, 반도체 소자(40)의 제 1 전극 패드(120) 및 제 2 전극 패드(122)에 직접 접촉하여 커버할 수 있다.

[0054] 기타 각 층 또는 구조의 위치, 상대 관계 및 재료 구성 등에 대한 내용 및 구조 변화에는 전술한 실시예에 자세하게 설명되어 있으므로, 여기서, 반복하여 설명하지 않는다.

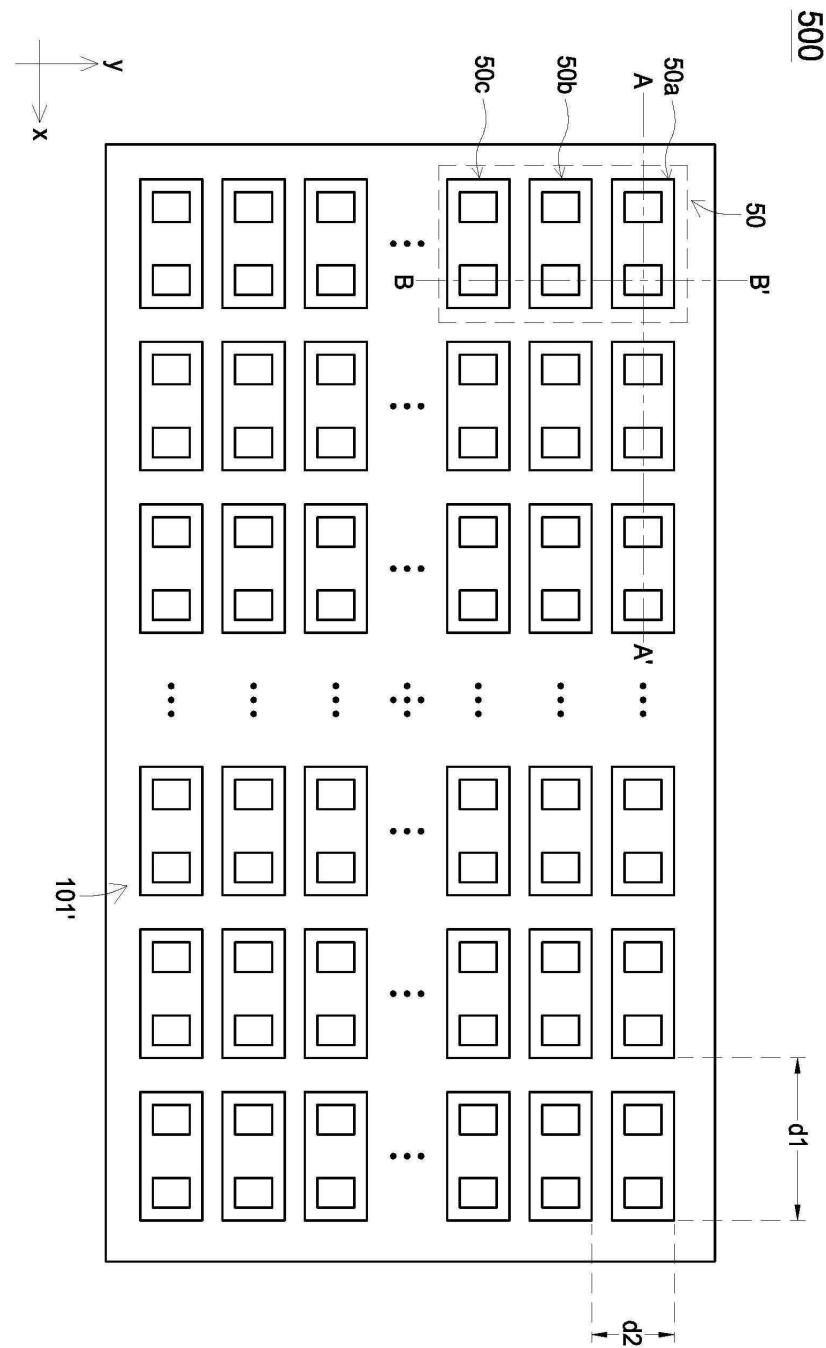

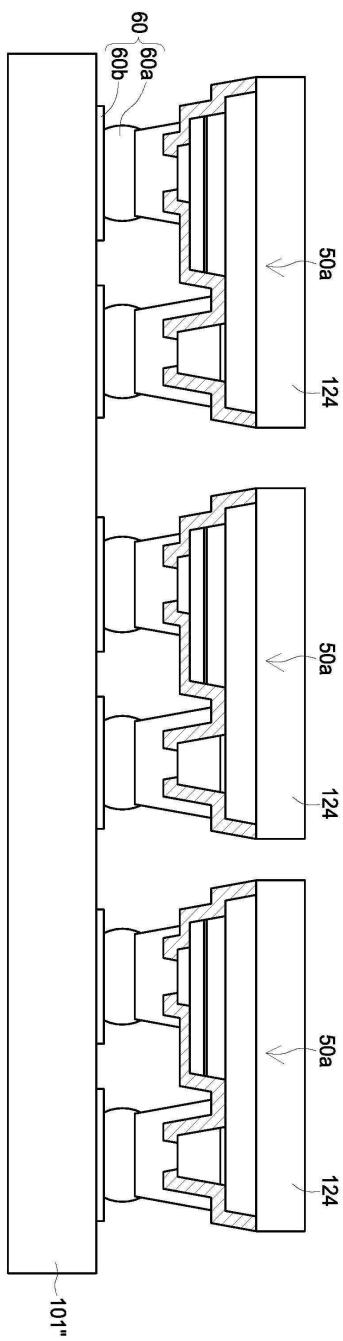

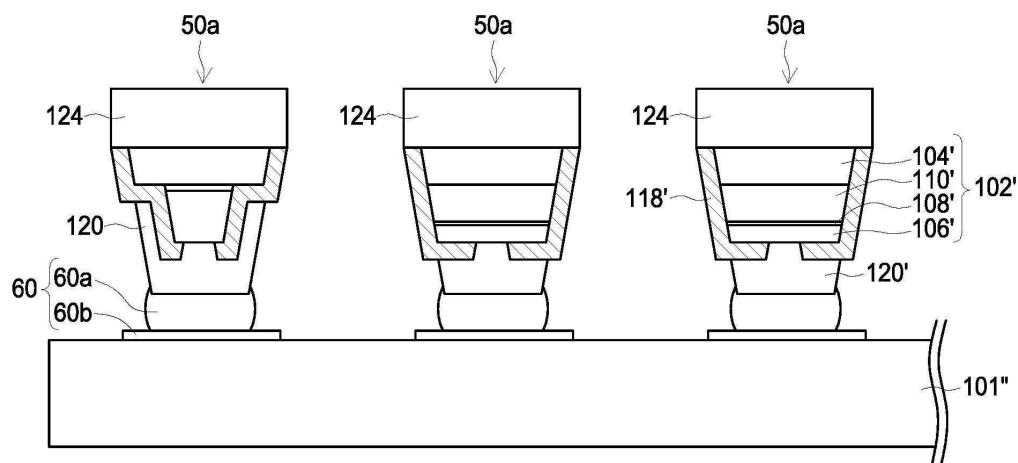

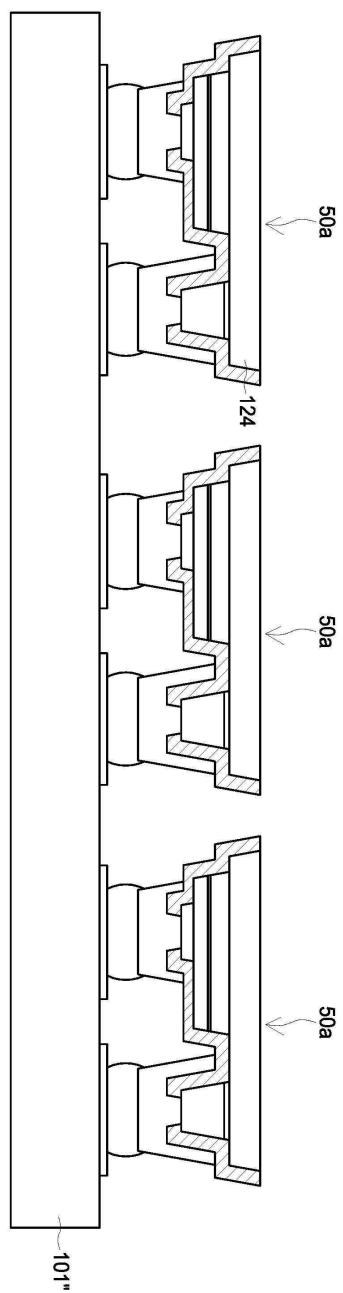

[0055] 도 5a는 본 개시의 일 실시예에 따른 디스플레이 패널(500)의 개략적인 평면도이다. 도 5b 및 도 5c는 본 개시의 일 실시예에 따른 디스플레이 패널(500)의 개략적인 부분 단면 구조도이다. 구체적으로, 도 5b는 도 5a의 A-A'선에 따른 단면을 나타내는 도면이고, 도 5c는 도 5a의 B-B'선에 따른 단면을 나타내는 도면이다.

[0056] 일 실시예에 있어서, 디스플레이 패널(500)은 캐리어 기판(101'') 및 캐리어 기판(101'') 위에 위치하는 복수의 픽셀 유닛(50)을 포함한다. 복수의 픽셀 유닛(50)은 행 방향(row direction)(x) 및 열 방향(column direction)(y)을 따라 배열된다. 복수의 픽셀 유닛(50)은 전사(transfer) 방법으로 캐리어 기판(101'') 위에 형성될 수 있다. 캐리어 기판(101'')은 유리, 플라스틱(plastic), 실리콘 기판(silicon substrate), 또는 인쇄 회로 기판(printed circuit board, PCB)일 수 있다. 각 픽셀 유닛(50)은 복수의 반도체 소자를 포함한다. 일

실시예에 있어서, 각 픽셀 유닛(50)은 3개의 반도체 소자, 즉 반도체 소자(50a), 반도체 소자(50b) 및 반도체 소자(50c)를 포함한다. 구체적으로, 일 실시예에 있어서, 반도체 소자(50a), 반도체 소자(50b) 및 반도체 소자(50c)는, 행 방향(x)에서 제 1 간격(d1) 이격되게 설치되고, 열 방향(y)에서 제 2 간격(d2) 이격되게 설치된다. 일 실시예에 있어서, 제 1 간격(d1)은 100  $\mu\text{m}$  이하이고, 제 2 간격(d2)은 50  $\mu\text{m}$  이하이다. 반도체 소자(50a), 반도체 소자(50b) 및 반도체 소자(50c)는 각각 상이한 파장 범위의 광을 방출할 수 있다. 예를 들어, 반도체 소자(50a), 반도체 소자(50b) 및 반도체 소자(50c)는 각각 적색 광, 녹색 광 및 청색 광을 방출할 수 있다. 캐리어 기판(110<sup>``</sup>) 위에 구동 회로(driving circuit) 및 제어 유닛(control unit)(도시하지 않음)을 더 설치하여 픽셀 유닛(50)을 구동하고 픽셀 유닛(50)의 발광 시간을 제어할 수 있다.

[0057] 도 5b 및 도 5c에 도시된 바와 같이, 각 반도체 소자(50a), 반도체 소자(50b) 및 반도체 소자(50c)는 접촉 구조(60)를 통해 캐리어 기판(101<sup>``</sup>)에 전기적으로 연결된다. 접촉 구조(60)는 연결 층(connection layer)(60a) 및 회로 전극(circuit electrode)(60b)을 포함한다. 일 실시예에 있어서, 반도체 소자(50a)는 본 개시의 임의의 실시예에 기재된 반도체 소자(예를 들어, 반도체 소자(10, 20, 30A, 30B, 30C 또는 30D)일 수 있고, 반도체 소자(50b) 및 반도체 소자(50c)는 반도체 소자(50a)와 상이한 구조를 가질 수 있다.

[0058] 도 5c에 도시된 바와 같이, 각 반도체 소자(50b) 및 반도체 소자(50c)는 반도체 스택(102<sup>``</sup>), 절연 구조(118) 및 전극 패드(120)를 포함한다. 반도체 스택(102<sup>``</sup>)은 제 1 반도체 층(104<sup>``</sup>), 제 2 반도체 층(106<sup>``</sup>), 제 1 반도체 층(104<sup>``</sup>)과 제 2 반도체 층(106<sup>``</sup>) 사이에 위치하는 활성 영역(108<sup>``</sup>), 및 제 1 반도체 층(104<sup>``</sup>)과 활성 영역(108<sup>``</sup>) 사이에 위치하는 제 3 반도체 층(110<sup>``</sup>)을 갖는다. 절연 구조(118)는 반도체 스택(102<sup>``</sup>)의 측벽 및 일부 표면을 커버한다. 전극 패드(120<sup>``</sup>)는 반도체 스택(102<sup>``</sup>)에 전기적으로 연결된다. 일부 실시예에 있어서, 활성 영역(108<sup>``</sup>)은 전극 패드(120<sup>``</sup>)와 중첩되는 반면, 전극 패드(120)는 활성 영역(108<sup>``</sup>)과 중첩되거나 중첩되지 않을 수 있다(도시하지 않음). 일 실시예에 있어서, 활성 영역(108<sup>``</sup>)의 재료는 활성 영역(108<sup>``</sup>)과 상이하다. 예를 들어, 활성 영역(108<sup>``</sup>)은 원소 N를 포함하고, 활성 영역(108<sup>``</sup>)은 원소 As 또는 원소 P를 포함한다. 일 실시예에 있어서, 제 2 반도체 층(106<sup>``</sup>)과 전극 패드(120<sup>``</sup>) 사이에 도전층이 추가로 배치될 수 있다(도시하지 않음). 상기 도전층은 인듐 주석 산화물(ITO)과 같은 도전성 산화물을 포함할 수 있다.

[0059] 도 5d 및 도 5e는 본 개시의 다른 실시예에 따른 디스플레이 패널(500)의 개략적인 부분 단면 구조도이다. 구체적으로, 도 5d는 도 5a의 A-A<sup>``</sup>선에 따른 단면도를 나타내고, 도 5e는 도 5a의 B-B<sup>``</sup>선에 따른 단면도를 나타낸다. 일 실시예에 있어서, 반도체 소자(50a), 반도체 소자(50b) 및 반도체 소자(50c)는 접합 구조(124)를 가지지 않으며, 이에 의해 각 반도체 소자의 두께가 더 감소될 수 있다.

[0060] 기타 각 층 또는 구조의 위치, 상대 관계 및 재료 구성 등에 대한 내용 및 구조 변화에는 전술한 실시예에 자세하게 설명되어 있으므로, 여기서, 반복하여 설명하지 않는다.

[0061] 상술한 내용을 토대로, 본 개시는, 반도체 소자, 반도체 소자의 제조 방법, 반도체 장치 또는 디스플레이 패널을 제공할 수 있다. 본 개시에서 제공되는 반도체 소자는 접촉 저항(contact resistance) 및 제조 공정 안정성(process stability)과 같은 광전 특성이 개선될 수 있다. 구체적으로, 본 개시의 반도체 소자 또는 반도체 장치는 조명, 의료, 디스플레이, 통신, 감지, 전원 시스템과 같은 다양한 분야의 제품에 적용될 수 있으며, 예를 들어, 조명 기구, 모니터, 휴대폰, 태블릿 PC, 자동차 계기판, 텔레비전, 컴퓨터, 웨어러블 장치(예를 들어, 손목시계, 팔찌 또는 목걸이 등), 교통 표지판, 실외 디스플레이, 의료기 등에 사용될 수 있다.

[0062] 이상, 실시예를 통해 본 발명에 대해 설명했지만, 본 발명을 한정하는 것은 아니며, 본 기술분야의 기술자는 본 발명의 사상과 범위를 벗어나지 않는 범위 내에서 다양한 장식 또는 변경을 실시할 수 있으므로, 본 발명의 보호 범위는 첨부한 특허청구 범위에 의해 결정되어야 한다. 또한, 상술한 실시예는 상황에 따라 서로 조합하거나 대체할 수 있으며, 상술한 특정 실시예에 제한되는 것은 아니다. 예를 들어, 일 실시예에 개시된 특정 구성 요소의 관련 변수 또는 특정 구성 요소와 기타 부재의 상관 관계도 기타 실시예에 적용될 수 있으며, 모두 본 발명의 청구범위에 속한다고 해야 할 것이다.

## 부호의 설명

[0063] 10, 20, 30A, 30B, 30C, 30D, 40, 50a, 50b, 50c 반도체 소자

100 베이스

101 성장 기판

101<sup>``</sup> 접합 기판

- 101`` 캐리어 기판

- 102 반도체 구조

- 102` 반도체 스택

- 104 제 1 반도체 층

- 104a 제 1 표면

- 104b 제 2 표면

- 106 제 2 반도체 층

- 108 활성 영역

- 110 제 3 반도체 층

- 112 접촉층

- 114 제 1 금속 원소를 함유하는 구조

- 116 제 2 금속 원소를 함유하는 구조

- 118 절연 구조

- 118a 제 1 개구

- 118b 제 2 개구

- 120 제 1 전극 패드

- 120` 전극 패드

- 120a 제 1 부분

- 120b 제 2 부분

- 122 제 2 전극 패드

- 124 접합 구조

- 124e 상부 에지

- 400, 400` 반도체 장치

- 50 퍽셀 유닛

- 60 접촉 구조

- 60a 연결 층

- 60b 회로 전극

- 500 디스플레이 패널

- A1 제 1 영역

- A2 제 2 영역

- d1 제 1 간격

- d2 제 2 간격

- e1 제 1 측면

- e2 제 2 측면

- e3, e4, e5 상면

- e6 제 3 측면

e7 제 4 측면

h1 제 1 두께

h2 제 2 두께

P1 제 1 부분

P2 제 2 부분

Q1, Q2, Q3 측벽

S1 제 1 메사 구조

S2 제 2 메사 구조

W1 제 1 폭

W2 제 2 폭

t0 총 두께

t1 두께

### 도면

#### 도면1

10

도면2a

20

도면2b

20

도면3a

도면3b

도면3c

도면3d

도면3e

도면3f

도면3g

도면3h

도면3i

도면3j

## 도면3k

## 도면3l

**30C**

## 도면3m

**30D**

도면4a

도면4b

도면5a

도면5b

도면5c

도면5d

도면5e