(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5080132号

(P5080132)

(45) 発行日 平成24年11月21日(2012.11.21)

(24) 登録日 平成24年9月7日(2012.9.7)

(51) Int.Cl.

F 1

G09G 3/36 (2006.01)

G02F 1/133 (2006.01)

G09G 3/20 (2006.01)G09G 3/36

G02F 1/133 550

G02F 1/133 570

G09G 3/20 631B

G09G 3/20 632B

請求項の数 15 (全 18 頁) 最終頁に続く

(21) 出願番号

特願2007-129985 (P2007-129985)

(22) 出願日

平成19年5月16日 (2007.5.16)

(65) 公開番号

特開2007-334321 (P2007-334321A)

(43) 公開日

平成19年12月27日 (2007.12.27)

審査請求日

平成22年4月28日 (2010.4.28)

(31) 優先権主張番号

10-2006-0052607

(32) 優先日

平成18年6月12日 (2006.6.12)

(33) 優先権主張国

韓国 (KR)

(31) 優先権主張番号

10-2006-0073457

(32) 優先日

平成18年8月3日 (2006.8.3)

(33) 優先権主張国

韓国 (KR)

(73) 特許権者 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.大韓民国京畿道水原市靈通区三星路 129

129, Samsung-ro, Yeongtong-gu, Suwon-si, Gyeonggi-do, Republic

of Korea

(74) 代理人 100121382

弁理士 山下 託嗣

(74) 代理人 100094145

弁理士 小野 由己男

(74) 代理人 100106367

弁理士 稲積 朋子

最終頁に続く

(54) 【発明の名称】データ補償回路及びこれを有する表示装置

(57) 【特許請求の範囲】

【請求項 1】

n - 2 番目のフレームデータ(ここで、nは現在フレームを示す)が圧縮されたn - 2 番目の圧縮データをあらかじめ格納する第1メモリと、n - 1 番目のフレームデータが圧縮されたn - 1 番目の圧縮データをあらかじめ格納する第2メモリと、n 番目のフレームの間、前記第1メモリから前記n - 2 番目の圧縮データを読み出して復元し、n - 2 番目の復元データを出力する第1復号部と、前記n 番目のフレームの間、前記第2メモリから前記n - 1 番目の圧縮データを読み出して復元し、n - 1 番目の復元データを出力する第2復号部と、前記n 番目のフレームの間、n 番目のフレームデータをn 番目の圧縮データに圧縮して前記第2メモリに格納し、前記n 番目の圧縮データを復元してn 番目の復元データを出力するコードック部と、

前記n - 2 番目の復元データと前記n 番目の復元データとの第1差分値を出力する第1処理部と、

前記第1差分値と前記n 番目のフレームデータに基づいてn - 2 番目の再復元データを出力する第2処理部と、

前記n - 1 番目の復元データと前記n 番目の復元データとの第2差分値を出力する第3処理部と、

前記第2差分値と前記n 番目のフレームデータとに基いてn - 1 番目の再復元データを

10

20

出力する第4処理部と、

前記n-2番目の再復元データと前記n-1番目の再復元データと前記n番目のフレームデータとに基いて前記n-1番目の再復元データを償って、n-1番目の補償データを出力する補償部とを含むことを特徴とするデータ補償回路。

【請求項2】

前記n-2番目の再復元データは前記n番目のフレームデータと前記第1差分値との和からなり、

前記n-1番目の再復元データは、前記n番目のフレームデータと前記第2差分値との和からなることを特徴とする請求項1に記載のデータ補償回路。

【請求項3】

前記補償部は、前記n-2番目の再復元データと前記n-1番目の再復元データとの第3差分値があらかじめ設定された第1基準値以下であれば、前記n-2番目の再復元データと同一値を有する前記n-1番目の補償データを出力し、前記第1基準値より大きければ、前記n-1番目の再復元データよりあらかじめ設定された補正値だけ増加した前記n-1番目の補償データを出力する請求項2に記載のデータ補償回路。

【請求項4】

前記第1差分値が0になると、前記第2処理部は前記n番目のフレームデータと同一である前記n-2番目の再復元データを出力し、

前記第2差分値が0になると、前記第4処理部は前記n番目のフレームデータと同一である前記n-1番目の再復元データを出力し、

前記n-1番目の補償データは前記n番目のフレームデータと同一である請求項3に記載のデータ補償回路。

【請求項5】

前記第1及び第2メモリは $2^m$ (ここで、mは前記現在フレームデータのビット数)より小さいサイズを有する請求項1に記載のデータ補償回路。

【請求項6】

n-2番目のフレームデータ(ここで、nは現在フレームを示す)が圧縮されたn-2番目の圧縮データをあらかじめ格納する第1メモリと、

n-1番目のフレームデータが圧縮されたn-1番目の圧縮データをあらかじめ格納する第2メモリと、

n番目のフレームの間、n番目のフレームデータをn番目の圧縮データに変換する符号部と、

前記n-2圧縮データ、前記n-1番目の圧縮データ及び前記n番目の圧縮データを比べて選択信号を出力する比較部と、

前記n番目の圧縮データ、前記n-1番目の圧縮データ及び前記n-2番目の圧縮データをn番目の復元データ、n-1番目の復元データ及びn-2番目の復元データにそれぞれ復元する復号部と、

前記n番目の復元データ、前記n-1番目の復元データ及び前記n-2番目の復元データに基いて第1補償データを出力する補償部と、

前記選択信号に応答して前記n番目のフレームデータと前記第1補償データのうちのいずれか1つを出力データとして出力するデータ選択部とを含むことを特徴とするデータ補償回路。

【請求項7】

前記補償部は、

前記n-1番目の復元データ及び前記n-2番目の復元データに基いて第2補償データを出力する第1補償部と、

前記第2補償データと前記n番目の復元データに基いて前記第1補償データを出力する第2補償部とを含むことを特徴とする請求項6に記載のデータ補償回路。

【請求項8】

前記第2補償部は前記第2補償データと前記n番目の復元データの中間値とを前記第1

補償データとして出力することを特徴とする請求項 7 に記載のデータ補償回路。

**【請求項 9】**

前記第1補償部は前記n-2番目の復元データと前記n-1番目の復元データとの差分値があらかじめ設定された基準値以下であれば、前記n-1番目の復元データを出力し、前記基準値以上であれば、前記n-1番目の復元データよりあらかじめ設定された補正值だけ増加した前記第2補償データを出力することを特徴とする請求項7に記載のデータ補償回路。

**【請求項 10】**

前記比較部は、

前記n番目の圧縮データが前記n-2番目の圧縮データ及び前記n-1番目の圧縮データと互いに同一であれば、第1状態を有する前記選択信号を出力し、

10

前記n番目の圧縮データが前記n-2番目の圧縮データ及び前記n-1番目の圧縮データと互いに同一ではなくれば、第2状態を有する前記選択信号を出力することを特徴とする請求項6に記載のデータ補償回路。

**【請求項 11】**

前記データ選択部は、

前記第1状態を有する前記第1選択信号に応答して前記n番目のフレームデータを前記出力データとして出力し、

前記第2状態を有する前記選択信号に応答して前記第1補償データを前記出力データとして出力することを特徴とする請求項10に記載のデータ補償回路。

20

**【請求項 12】**

前記第1及び第2メモリは $2^m$  (ここで、mは前記n番目のフレームデータのビット数)より小さいサイズを有することを特徴とする請求項6に記載のデータ補償回路。

**【請求項 13】**

請求項1乃至12のいずれか1項に記載のデータ補償回路と、

データ制御信号に応答して前記現在補償データに対応するデータ電圧を出力するデータ駆動回路と、

ゲート制御信号に応答してゲート電圧を出力するゲート駆動回路と、

前記データ電圧と前記ゲート電圧に応答して映像を表示する表示部とを含むことを特徴とする表示装置。

30

**【請求項 14】**

外部からの制御信号に応答して前記データ駆動回路に前記データ制御信号を提供し、前記ゲート駆動回路に前記ゲート制御信号を提供するタイミングコントローラをさらに含む請求項13に記載の表示装置。

**【請求項 15】**

前記タイミングコントローラはチップ形態からなり、

前記データ補償回路は前記タイミングコントローラに内蔵している請求項14に記載の表示装置。

**【発明の詳細な説明】**

**【技術分野】**

40

**【0001】**

本発明はデータ補償回路及びこれを有する表示装置に関する。

**【背景技術】**

**【0002】**

一般的に、液晶表示装置は2枚の表示基板とその間に介在された液晶層からなる。液晶表示装置は液晶層に電界を印加し、電界の強さを調節して液晶層を通過する光の透過率を調節することによって、所望の映像を表示する。

**【0003】**

このような液晶表示装置は、最近、コンピュータの表示装置だけでなく、テレビの表示画面において広く用いられていることによって、動画を実現する必要性が高くなっている

50

。しかし、従来の液晶表示装置は液晶の応答速度が遅いので、動画を実現しにくい。

#### 【0004】

具体的に、液晶分子の応答速度が遅いので、液晶キャパシタに充電される電圧が目標電圧(すなわち、所望する輝度を得ることができる電圧)まで到達するのに一定の時間がかかる。特に、直前フレームで液晶キャパシタにあらかじめ充電されている直前電圧と、現在フレームでの目標電圧との差が大きい場合、初期から目標電圧のみを印加すれば、スイッチング素子がターンオンされる1H時間(1水平時間)の間で目標電圧に到達されない可能性がある。ここで、直前フレームは、現在フレームの1つ前のフレームを意味する。

#### 【0005】

したがって、従来の液晶表示装置は液晶の応答速度を高速化するために、DCC(Dynamic Capacitance Compensation)方式を採用している。DCC方式は、現在フレームの目標電圧と直前フレームの直前電圧とを考慮して、補正電圧を現在フレームに印加して液晶の応答速度を高速化させる方式である。

#### 【特許文献1】特開2005-309326号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0006】

しかし、DCC方式を採用する液晶表示装置は、直前フレームの直前電圧を格納するためのフレームメモリを要する。このとき、フレームメモリの個数及びサイズは液晶表示装置の生産性を低下させ、製造コストを上昇させる。

20

#### 【0007】

そこで、本発明の目的は、生産性を向上させることができるデータ補償回路を提供することにある。

#### 【0008】

また、本発明の他の目的は、上記したデータ補償回路を有する表示装置を提供することにある。

#### 【課題を解決するための手段】

#### 【0009】

本発明の実施形態に係るデータ補償回路は、第1及び第2メモリ、第1及び第2復号部、コーデック部、第1乃至第4処理部及び補償部を含む。前記第1メモリはn-1番目のフレーム(ここで、nは現在フレームを示す)の間、n-2番目のフレームデータから圧縮されたn-2番目の圧縮データを格納し、n番目のフレームの間、あらかじめ格納された前記n-2番目の圧縮データを出力し、n-1番目のフレームデータから圧縮されたn-1番目の圧縮データを格納する。前記第2メモリはn-1番目のフレームの間、前記n-1番目の圧縮データを格納し、前記n番目のフレームの間、あらかじめ格納された前記n-1番目の圧縮データを出力する。

30

#### 【0010】

前記第1復号部は前記n番目のフレームの間、前記n-2番目の圧縮データを復元してn-2番目の復元データを出力し、前記第2復号部は前記n番目のフレームの間、前記n-1番目の圧縮データを復元してn-1番目の復元データを出力する。前記コーデック部は前記n番目のフレームの間、n番目のフレームデータを前記n番目の圧縮データに圧縮して前記第2メモリに格納し、前記n番目の圧縮データを復元してn番目の復元データを出力する。

40

#### 【0011】

前記第1処理部は、前記n-2番目の復元データと前記n番目の復元データとの第1差分値を出力し、前記第2処理部は前記第1差分値と前記n番目のフレームデータに基いてn-2番目の再復元データを生成する。前記第3処理部は前記n-1番目の復元データと前記n番目の復元データとの第2差分値を出力し、前記第4処理部は前記第2差分値と前記n番目のフレームデータに基いてn-1番目の再復元データを生成する。前記補償部は前記n-2番目の再復元データ、前記n-1番目の再復元データ及び前記n番目のフレー

50

ムデータに基いて前記 n - 1 番目の再復元データを償って n - 1 番目の補償データを出力する。

【 0 0 1 2 】

このようなデータ補償回路によると、圧縮されたデータが第 1 及び第 2 メモリに格納されるので、第 1 及び第 2 メモリの全体のサイズを減少させることができる。また、第 1 及び第 2 メモリに圧縮されて格納され、さらに DCC 处理の際に読み出されて復元されることでデータが損傷してしまうが、上記の第 1 乃至第 4 处理部により、圧縮及び復元による損傷が抑えられた n - 2 番目の再復元データ及び n - 1 番目の再復元データを求めることが可能。次に、補償部は、第 2 及び第 4 处理部からのデータに基づいて n - 1 番目の補償データを出力する。これにより、各フレームでの目標電圧の到達時間を調整し、液晶の応答速度を高速化することができる。

10

【 0 0 1 3 】

前記 n - 2 番目の再復元データは前記 n 番目のフレームデータと前記第 1 差分値との和からなり、前記 n - 1 番目の再復元データは前記 n 番目のフレームデータと前記第 2 差分値との和からなるとよい。

【 0 0 1 4 】

前記補償部は、前記 n - 2 番目の再復元データと前記 n - 1 番目の再復元データとの第 3 差分値があらかじめ設定された第 1 基準値以下であれば、前記第 n - 2 番目の再復元データと同一値を有する前記 n - 1 番目の補償データを出力し、前記第 1 基準値より大きければ、前記 n - 1 番目の再復元データよりあらかじめ設定された補正值だけ増加した前記 n - 1 番目の補償データを出力するとよい。

20

【 0 0 1 5 】

前記第 1 差分値が 0 になると、前記第 2 处理部は前記 n 番目のフレームデータと同一である前記 n - 2 番目の再復元データを出力し、前記第 2 差分値が 0 になると、前記第 4 处理部は前記 n 番目のフレームデータと同一である前記 n - 1 番目の再復元データを出力し、前記 n - 1 番目の補償データは前記 n 番目のフレームデータと同一であるとよい。

【 0 0 1 6 】

前記第 1 及び第 2 メモリは  $2^m$  (ここで、m は前記 n フレームデータのビット数) より小さいサイズを有するとよい。さらに、前記第 1 及び第 2 メモリは  $2^{m/3}$  のサイズを有するとよい。

30

【 0 0 1 7 】

本発明の別の実施形態に係るデータ補償回路は第 1 メモリ、第 2 メモリ、符号部、比較部、復号部、補償部及びデータ選択部を含んでおり、前記第 1 メモリには n - 2 番目のフレームデータ(ここで、n は現在フレームを示す)から圧縮された n - 2 番目の圧縮データがあらかじめ格納され、前記第 2 メモリには n - 1 番目のフレームデータから圧縮された n - 1 番目の圧縮データがあらかじめ格納される。前記符号部は n 番目のフレームの間、n 番目のフレームデータを n 番目の圧縮データに変換し、前記比較部は前記 n - 2 番目の圧縮データ、前記 n - 1 番目の圧縮データ及び前記 n 番目の圧縮データを比べて選択信号を出力する。

【 0 0 1 8 】

前記復号部は前記 n 番目の圧縮データ、前記 n - 1 番目の圧縮データ及び前記 n - 2 番目の圧縮データを n 番目の復元データ、n - 1 番目の復元データ及び n - 2 番目の復元データにそれぞれ復元する。前記補償部は前記 n 番目の復元データ、前記 n - 1 番目の復元データ及び前記 n - 2 番目の復元データに基いて第 1 補償データを出力し、前記データ選択部は前記選択信号に応答して前記 n 番目のフレームデータと前記第 1 補償データのうちのいずれか 1 つを出力データとして出力する。

40

【 0 0 1 9 】

このようなデータ補償回路によると、圧縮されたデータが第 1 及び第 2 メモリに格納されるので、第 1 及び第 2 メモリの全体のサイズを減少させることができる。また、第 1 及び第 2 メモリに圧縮されて格納され、さらに DCC 处理の際に読み出されて復元されるこ

50

とでデータが損傷してしまうが、補償部により、 $n - 1$ 番目及び $n - 2$ 番目の復元データに基づいて第1補償データを出力するため、圧縮及び復元による損傷を抑えるとともに、各フレームでの目標電圧の到達時間を調整し、液晶の応答速度を高速化することができる。

【0020】

前記補償部は、前記 $n - 1$ 番目の復元データ及び前記 $n - 2$ 番目の復元データに基いて第2補償データを出力する第1補償部と、前記第2補償データと前記 $n$ 番目の復元データに基いて前記第1補償データを出力する第2補償部とを含むとよい。さらに、前記第2補償部は前記第2補償データと前記 $n$ 番目の復元データの中間値とを前記第1補償データとして出力するとよい。

10

【0021】

このデータ駆動回路は連続する3つのフレームに対応する圧縮データを比べた後、その結果によって圧縮される直前状態の現在フレームデータを出力するか、または現在フレームデータと第1補償データの中間値を出力する。したがって、圧縮によるデータの損傷を防止し、かつ応答速度を向上することができる。

【0022】

前記第1補償部は前記 $n - 2$ 番目の復元データと前記 $n - 1$ 番目の復元データとの差分値があらかじめ設定された基準値以下であれば、前記 $n - 1$ 番目の復元データを出力し、前記基準値以上であれば、前記 $n - 1$ 番目の復元データよりあらかじめ設定された補正值だけ増加した前記第2補償データを出力するとよい。

20

【0023】

これにより、各フレームの1H時間内に目標輝度 $L_t$ に到達するようにし、応答速度を向上することができる。

【0024】

前記比較部は、前記 $n$ 番目の圧縮データが前記 $n - 2$ 番目の圧縮データ及び前記 $n - 1$ 番目の圧縮データと互いに同一であれば、第1状態を有する前記選択信号を出力し、前記 $n$ 番目の圧縮データが前記 $n - 2$ 番目の圧縮データ及び前記 $n - 1$ 番目の圧縮データと互いに同一ではなければ、第2状態を有する前記選択信号を出力するとよい。

【0025】

前記データ選択部は、前記第1状態を有する前記第1選択信号に応答して前記 $n$ 番目のフレームデータを前記出力データとして出力し、前記第2状態を有する前記選択信号に応答して前記第1補償データを前記出力データとして出力するとよい。

30

【0026】

前記第1及び第2メモリは $2^m$ (ここで、 $m$ は前記 $n$ 番目のフレームデータのビット数)より小さいサイズを有するとよい。

【0027】

本発明のさらに別の実施形態に係る表示装置は、前述のデータ補償回路と、データ制御信号に応答して前記現在補償データに対応するデータ電圧を出力するデータ駆動回路と、ゲート制御信号に応答してゲート電圧を出力するゲート駆動回路と、前記データ電圧と前記ゲート電圧に応答して映像を表示する表示部とを含む。

40

【0028】

このようなデータ補償回路を有する表示装置によると、フレームデータは圧縮された後メモリに格納され、メモリから読み出された圧縮データは復元過程を経た後、補償部に伝送される。したがって、メモリの全体のサイズを減少させることができ、その結果、メモリをタイミングコントローラに内蔵させることができ、表示装置の製造コストを節減させ、生産性を向上することができる。また、停止画面が表示される場合、圧縮及び復元過程なしに現在フレームデータを利用して映像を表示することによって、停止画面が損傷されることを防止することができる。

【0029】

当該表示装置は、外部からの制御信号に応答して前記データ駆動回路に前記データ制御

50

信号を提供し、前記ゲート駆動回路に前記ゲート制御信号を提供するタイミングコントローラをさらに含むとよい。

【0030】

さらに、前記タイミングコントローラはチップ形態からなり、前記データ補償回路は前記タイミングコントローラに内蔵しているとよい。

【0031】

前記表示部にはマトリックス形態で配置された複数の画素を備え、前記各画素は、前記ゲート電圧に応答して前記データ電圧を出力する薄膜トランジスタと、前記データ電圧とあらかじめ設定された基準電圧との電位差を充電する液晶キャパシタとを含むとよい。

【発明の効果】

10

【0032】

本発明によれば、生産性を向上させることができるデータ補償回路及び前記データ補償回路を有する表示装置を提供することができる。

【発明を実施するための最良の形態】

【0033】

以下、添付した図面を参照して、本発明の望ましい実施形態をさらに詳細に説明する。

【0034】

<第1参考例>

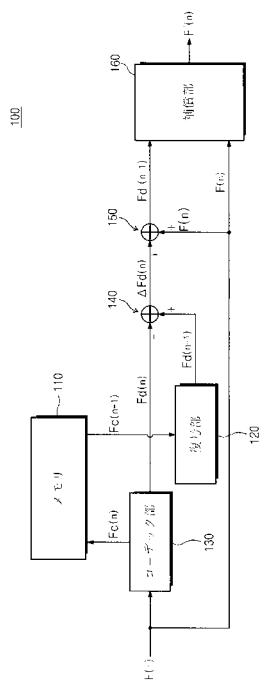

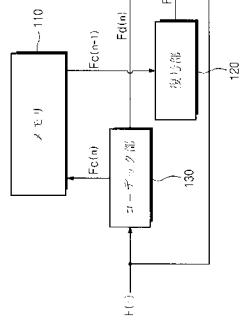

図1は本発明の一参考例に係るデータ補償回路を示すブロック図である。

【0035】

20

図1を参照すると、本発明の一参考例に係るデータ補償回路100はメモリ110、復号部120、コーデック部130、第1処理部140、第2処理部150及び補償部160を含んでいる。以下、直前フレームとは、現在フレームの1つ前のフレームを意味するものとする。

【0036】

前記メモリ110には、直前フレームデータF(n-1)が圧縮された直前圧縮データFc(n-1)があらかじめ格納されている。本発明の一例として、直前フレームデータF(n-1)が24ビットからなると、直前圧縮データFc(n-1)は1/3に圧縮された8ビットからなる。したがって、メモリ110は、 $2^m$ (ここで、mは直前フレームデータF(n-1)のビット数)より小さいサイズを有する。本発明の一例として、直前フレームデータF(n-1)が24ビットからなる場合、メモリ110は $2^8$ のサイズを有する。このように、メモリ110には1フレーム分量より小さい分量の圧縮されたデータが格納されているので、メモリ110のサイズを減少させることができる。

30

【0037】

復号部120は現在フレームの間、メモリ110にあらかじめ格納されている直前圧縮データFc(n-1)を読み出し、直前圧縮データFc(n-1)を復元して直前復元データFd(n-1)を出力する。具体的に、復号部120はm/3ビットからなる直前圧縮データFc(n-1)をmビットからなる直前復元データFd(n-1)に復元する。

【0038】

一方、コーデック部130に現在フレームの間、現在フレームデータF(n)が入力され、現在フレームデータF(n)を現在圧縮データFc(n)に圧縮した後、メモリ110に格納する。本発明の一例として、現在フレームデータF(n)はmビットからなり、現在圧縮データFc(n)はm/3ビットからなる。また、コーデック部130は現在フレームの間、現在圧縮データFc(n)を復元して現在復元データFd(n)を出力する。

40

【0039】

第1処理部140は、直前復元データFd(n-1)と現在復元データFd(n)との第1差分値Fd(n)を出力する。また、第2処理部150は、第1差分値Fd(n)及び現在フレームデータF(n)に基いて、直前再復元データFd'(n-1)を生成する。具体的に、第2処理部150は現在フレームデータF(n)に第1差分値Fd(n)を合算して直前再復元データFd'(n-1)を生成する。例えば、停止画面の場合、現在復元データF

50

$d(n)$  と直前復元データ  $F d(n-1)$  とが同一であるため、第 1 差分値  $F d(n)$  は 0 になる。この場合、第 2 処理部 150 は現在フレームデータ  $F(n)$  と同一である直前再復元データ  $F d'(n-1)$  を出力する。

#### 【0040】

補償部 160 は、直前再復元データ  $F d'(n-1)$  と現在フレームデータ  $F(n)$  に基づいて、現在フレームデータ  $F(n)$  を償って現在補償データ  $F'(n)$  を出力する。具体的に、補償部 160 は、直前再復元データ  $F d'(n-1)$  と現在フレームデータ  $F(n)$  との第 2 差分値があらかじめ設定された第 1 基準値以下であれば、現在フレームデータ  $F(n)$  と同一値を有する現在補償データ  $F'(n)$  を出力する。したがって、停止画面の場合、第 1 差分値  $F d(n)$  は 0 になるため、直前再復元データ  $F d'(n-1)$  は現在フレームデータ  $F(n)$  と同一値を有する。つまり、停止画面の場合、現在フレームでは圧縮または復元されない現在フレームデータ  $F(n)$  がそのまま画像として表示装置に出力される。その結果、加工されない現在フレームデータ  $F(n)$  を利用して映像を表示することによって、停止画面の損傷を防止することができる。

#### 【0041】

一方、補償部 160 は第 2 差分値が第 1 基準値より大きければ、現在フレームデータ  $F(n)$  よりあらかじめ設定された補正值だけオーバードライブされた現在補償データ  $F'(n)$  を出力する。

#### 【0042】

以上のように、メモリ 110 には、メモリ 110 のサイズを小さくするために、直前フレームデータ  $F(n-1)$  を圧縮した直前圧縮データ  $F c(n-1)$  が格納されており、DC C 処理の際に復元される。このようなデータの圧縮及び復元により、データが損傷してしまう。そこで、第 1 処理部 140 では、直前復元データ  $F d(n-1)$  と現在復元データ  $F d(n)$  との第 1 差分値  $F d(n)$  を出力し、直前フレームと現在フレームとの復元データの差分を算出する。そして、第 2 処理部 150 は、現在フレームデータ  $F(n)$  に、直前フレームと現在フレームとの復元データ間の第 1 差分値  $F d(n)$  を合算することで、直前再復元データ  $F d'(n-1)$  を生成する。これにより、圧縮及び復元による損傷が抑えられた直前再復元データ  $F d'(n-1)$  を求めることができる。次に、補償部 160 は、直前再復元データ  $F d'(n-1)$  及び現在フレームデータ  $F(n)$  間の第 2 差分値と、第 1 基準値との比較結果に応じた現在補償データ  $F'(n)$  を出力する。これにより、各フレームでの目標電圧の到達時間を調整し、液晶の応答速度を高速化することができる。

#### 【0043】

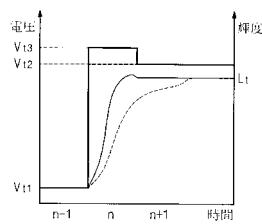

以下、図 2 及び図 3 を参照して補償部 160 によってオーバードライブされる現在補償データ  $F'(n)$  を具体的に説明する。

#### 【0044】

図 2 及び図 3 は、図 1 に示したデータ補償回路によって補償された現在補償データに  $F'(n)$  対応する電圧及び輝度を示したグラフである。図 2 及び図 3 において、x 軸は時間を表しており  $n-1$ 、 $n$ 、 $n+1$  はフレームの順番を示し、y 軸は電圧及び輝度を示す。ここで、電圧はフレーム単位毎に液晶層に印加される電圧を示し、輝度は液晶層を通過した光の輝度を示す。

#### 【0045】

図 2 を参照すると、直前フレームデータ  $F(n-1)$  は第 1 目標電圧  $V t 1$  に対応し、現在フレームデータ  $F(n)$  は第 1 目標電圧  $V t 1$  より高い第 2 目標電圧  $V t 2$  に対応する。第 1 目標電圧  $V t 1$  と第 2 目標電圧  $V t 2$  との電圧差があらかじめ設定された基準値より大きい場合、第 2 目標電圧  $V t 2$  を液晶層に印加しても 1 フレーム内に所望の目標輝度  $L t$  に到達しにくい。現在フレーム内において目標輝度  $L t$  に到達しない場合の様子が、図 2 中の破線の曲線で示されている。

#### 【0046】

このような問題を解決するため、補償部(160、図 1 に示す)は、現在フレーム( $n$ )において第 2 目標電圧  $V t 2$  を第 2 目標電圧  $V t 2$  より高い第 3 目標電圧  $V t 3$  にオーバー

10

20

30

40

50

ドライブさせる。したがって、現在フレーム( $n$ )において液晶層には第3目標電圧 $V_{t3}$ が印加され、その結果、ライジングタイムが減少して1フレーム内に所望の目標輝度 $L_t$ に到達することができる。この様子が図2中の実線の曲線で示されており、現在フレーム内において輝度が目標輝度 $L_t$ に到達しているのがわかる。

【0047】

図3を参照すると、直前フレームデータ $F(n-1)$ は第1目標電圧 $V_{t1}$ に対応し、現在フレームデータは第1目標電圧 $V_{t1}$ より低い第2目標電圧 $V_{t2}$ に対応する。第1目標電圧 $V_{t1}$ と第2目標電圧 $V_{t2}$ との電圧差があらかじめ設定された基準値より大きい場合、第2目標電圧 $V_{t2}$ を液晶層に印加しても1フレーム内に所望の目標輝度 $L_t$ に到達しにくい。現在フレーム内において目標輝度 $L_t$ に到達しない場合の様子が、図3中の破線の曲線で示されている。

10

【0048】

このような問題を解決するため、補償部(160、図1に示す)は現在フレーム( $n$ )において第2目標電圧 $V_{t2}$ を第2目標電圧 $V_{t2}$ より低い第3目標電圧 $V_{t3}$ にオーバードライブさせる。したがって、現在フレーム( $n$ )において液晶層には第3目標電圧 $V_{t3}$ が印加され、その結果、フォーリングタイムが減少して1フレーム内に所望の目標輝度 $L_t$ に到達することができる。この様子が図3中の実線の曲線で示されており、現在フレーム内において輝度が目標輝度 $L_t$ に到達しているのがわかる。

【0049】

このように、オーバードライブされた電圧を液晶層に印加することによって、液晶の応答速度を向上させることができる。

20

【0050】

<第1実施形態>

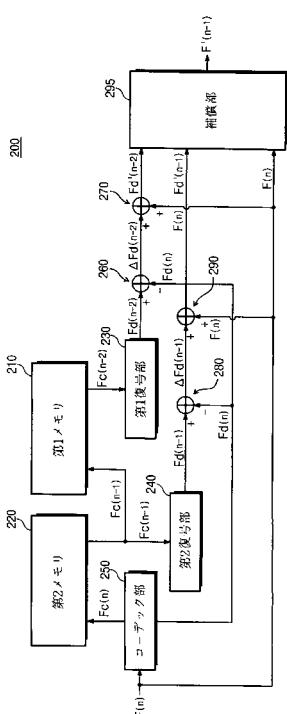

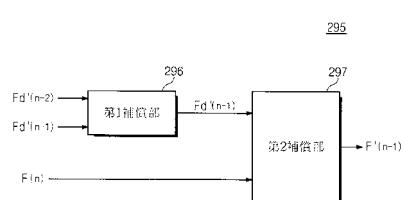

図4は本発明の一実施形態に係るデータ補償回路を示したブロック図であり、図5は図4に示した補償部の内部ブロック図である。

【0051】

図4を参照すると、本発明の他の実施形態に係るデータ補償回路200は第1及び第2メモリ210、220、第1及び第2復号部230、240、コーデック部250、第1、第2、第3及び第4処理部260、270、280、290及び補償部295を含んでいる。

30

【0052】

第1メモリ210には、 $n-2$ 番目のフレームデータ $F(n-2)$ (ここで、 $n$ は現在フレームを示す)が圧縮された $n-2$ 番目の圧縮データ $F_c(n-2)$ があらかじめ格納されており、第2メモリ220には $n-1$ 番目のフレームデータ $F(n-1)$ が圧縮された $n-1$ 番目の圧縮データ $F_c(n-1)$ が格納されている。第1メモリ210は $n$ 番目のフレームの間、あらかじめ格納された $n-2$ 番目の圧縮データ $F_c(n-2)$ を出力し、その後、 $n-1$ 番目の圧縮データ $F_c(n-1)$ を格納する。第2メモリ220は $n$ 番目のフレームの間、あらかじめ格納された $n-1$ 番目の圧縮データ $F_c(n-1)$ を出力する。本発明の一例として、 $n-2$ 番目のフレーム及び $n-1$ 番目のフレームデータが $m$ ビットからなるとき、 $n-2$ 番目及び $n-1$ 番目のフレームデータの圧縮データは $m/3$ ビットからなる。第1及び第2メモリ210、220は $2^m$ より小さいサイズを有する。本発明の一例として、第1及び第2メモリ210、220は $2^{m/3}$ のサイズを有する。このように、第1及び第2メモリ210、220には1フレーム分量より小さい分量の圧縮されたデータが格納されているので、第1及び第2メモリ210、220のサイズを減少させることができる。

40

【0053】

第1復号部230は、 $n$ 番目のフレームの間、 $n-2$ 番目の圧縮データ $F_c(n-2)$ を復元して $n-2$ 番目の復元データ $F_d(n-2)$ を出力し、第2復号部240は、 $n$ 番目のフレームの間、 $n-1$ 番目の圧縮データ $F_c(n-1)$ を復元して $n-1$ 番目の復元データ $F_d(n-1)$ を出力する。本発明の一例として、第1及び第2復号部230、240は、

50

$m/3$  ビットからなる  $n-2$  及び  $n-1$  番目の圧縮データ  $F_c(n-2)$ 、 $F_c(n-1)$  を、 $m$  ビットからなる  $n-2$  番目の及び  $n-1$  番目の復元データ  $F_d(n-2)$ 、 $F_d(n-1)$  にそれぞれ復元する。

#### 【0054】

コーデック部 250 には、 $n$  番目のフレームの間、 $n$  番目のフレームデータ  $F(n)$  が入力され、 $n$  番目のフレームデータ  $F(n)$  を  $n$  番目の圧縮データ  $F_c(n)$  に圧縮して第 2 メモリ 220 に提供する。また、コーデック部 250 は  $n$  番目のフレームの間、 $n$  番目の圧縮データ  $F_c(n)$  を復元して  $n$  番目の復元データ  $F_d(n)$  を出力する。

#### 【0055】

第 1 処理部 260 は  $n-2$  番目の復元データ  $F_d(n-2)$  と  $n$  番目の復元データ  $F_d(n)$  との第 1 差分値  $F_d(n-2)$  を出力し、第 2 処理部 270 は第 1 差分値  $F_d(n-2)$  と  $n$  番目のフレームデータ  $F(n)$  に基いて、 $n-2$  番目の再復元データ  $F_d'(n-2)$  を生成する。ここで、第 2 処理部 270 は、 $n$  番目のフレームデータ  $F(n)$  に第 1 差分値  $F_d(n-2)$  を合算して、 $n-2$  番目の再復元データ  $F_d'(n-2)$  を生成する。

#### 【0056】

第 3 処理部 280 は、 $n-1$  番目の復元データ  $F_d(n-1)$  と  $n$  番目の復元データ  $F_d(n)$  との第 2 差分値  $F_d(n-1)$  を出力し、第 4 処理部 290 は第 2 差分値  $F_d(n-1)$  と  $n$  番目のフレームデータ  $F(n)$  に基いて、 $n-1$  番目の再復元データ  $F_d'(n-1)$  を生成する。ここで、第 4 処理部 290 は  $n$  番目のフレームデータ  $F(n)$  に第 2 差分値  $F_d(n-1)$  を合算して、 $n-1$  番目の再復元データ  $F_d'(n-1)$  を生成する。

#### 【0057】

補償部 295 は  $n-2$  番目の再復元データ  $F_d'(n-2)$ 、 $n-1$  番目の再復元データ  $F_d'(n-1)$  及び  $n$  番目のフレームデータ  $F(n)$  に基いて、 $n-1$  番目の再復元データ  $F_d'(n-1)$  を償って  $n-1$  番目の補償データ  $F'(n-1)$  を出力する。

#### 【0058】

図 5 に示したように、補償部 295 は第 1 及び第 2 補償部 296、297 を含んでいる。第 1 補償部 296 は  $n-2$  番目の再復元データ  $F_d'(n-2)$  及び  $n-1$  番目の再復元データ  $F_d'(n-1)$  に基いて  $n-1$  番目の補償復元データ  $F_d''(n-1)$  を生成し、第 2 補償部 297 は  $n-1$  番目の補償復元データ  $F_d''(n-1)$  及び  $n$  番目のフレームデータ  $F(n)$  に基いて  $n-1$  番目の補償データ  $F'(n-1)$  を生成する。

#### 【0059】

具体的に、第 1 補償部 296 は、 $n-2$  番目の再復元データ  $F_d'(n-2)$  と  $n-1$  番目の再復元データ  $F_d'(n-1)$  の第 3 差分値があらかじめ設定された第 1 基準値以下であれば、 $n-2$  番目の再復元データ  $F_d'(n-2)$  と同一値を有する  $n-1$  番目の補償復元データ  $F_d''(n-1)$  を出力し、第 1 基準値以上であれば、 $n-1$  番目の再復元データ  $F_d'(n-1)$  からオーバードライブされた  $n-1$  番目の補償復元データ  $F_d''(n-1)$  を出力する。

#### 【0060】

例えば、停止画面の場合、第 1 及び第 2 差分値  $F_d(n-2)$ 、 $F_d(n-1)$  が 0 になるので、 $n-2$  及び  $n-1$  番目の再復元データ  $F_d'(n-2)$ 、 $F_d'(n-1)$  は  $n$  フレームデータ  $F(n)$  と同一値を有する。また、第 3 差分値が 0 になるので、第 1 補償部 296 は  $n$  フレームデータ  $F(n)$  と同一値を有する  $n-1$  補償復元データ  $F_d''(n-1)$  を出力する。

#### 【0061】

一方、第 2 補償部 297 は  $n-1$  番目の補償復元データ  $F_d''(n-1)$  が第 2 基準値より小さく、 $n$  番目のフレームデータ  $F(n)$  が第 3 基準値より大きければ、 $n-1$  番目の補償復元データ  $F_d''(n-1)$  より第 2 補正値だけ大きい  $n-1$  補償データ  $F'(n-1)$  を生成し、 $n-1$  番目の補償復元データ  $F_d''(n-1)$  が第 2 基準値以上であるか、または  $n$  番目のフレームデータ  $F(n)$  が第 3 基準値以下であれば、 $n-1$  番目の補償復元データ  $F_d''(n-1)$  と同一である  $n-1$  番目の補償データ  $F'(n-1)$  を生成する。

## 【0062】

停止画面の場合、第2補償部297はn-1番目の補償復元データF d "(n-1)と同一であるn-1番目の補償データF '(n-1)を生成する。ここで、n-1番目の補償復元データF d "(n-1)はn番目のフレームデータF(n)と同一値を有するので、n-1番目の補償データF '(n-1)はn番目のフレームデータF(n)と同一値を有する。

## 【0063】

このように、停止画面を表示する場合、第1及び第2補償部296、297では圧縮または復元されないn番目のフレームデータF(n)がそのまま出力される。その結果、加工されないn番目のフレームデータF(n)を利用して映像を表示することによって、停止画面の損傷を防止することができる。

10

## 【0064】

以上のように、第1メモリ210及び第2メモリ220には、第1メモリ210及び第2メモリ220のサイズを小さくするために、それぞれn-2番目のフレームデータF(n-2)を圧縮したn-2番目の圧縮データF c(n-2)と、n-1番目のフレームデータF(n-1)を圧縮したn-1番目の圧縮データF c(n-1)とが格納されており、DC C処理の際に読み出されて復元される。このようなデータの圧縮及び復元により、データが損傷してしまう。そこで、第1処理部260では、n-2番目の復元データF d(n-2)とn番目の復元データF d(n)との第1差分値F d(n-2)を出力し、n-2番目のフレームとn番目のフレームとの復元データ間の差分を算出する。そして、第2処理部270は、n番目のフレームデータF(n)に、n-2番目のフレーム及びn番目のフレームの復元データ間の第1差分値F d(n-2)を合算することで、n-2番目の再復元データF d'(n-2)を生成する。これにより、圧縮及び復元による損傷が抑えられたn-2番目の再復元データF d'(n-2)を求めることができる。同様にして、第3処理部280及び第4処理部290により、圧縮及び復元による損傷が抑えられたn-1番目の再復元データF d'(n-1)を求めることができる。さらに、次に、補償部295は、n-2番目の再復元データF d'(n-2)、n-1番目の再復元データF d'(n-1)及びn番目の復元データF d(n)に応じたn-1番目の補償データF '(n-1)を出力する。これにより、各フレームでの目標電圧の到達時間を調整し、液晶の応答速度を高速化することができる。

20

## 【0065】

30

## &lt;第2実施形態&gt;

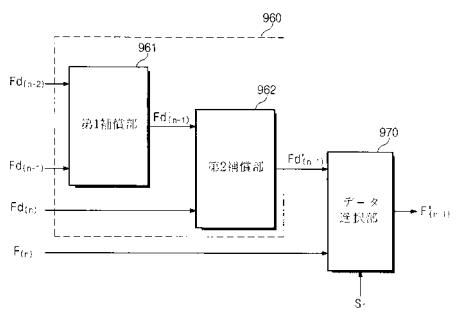

図6は本発明の他の実施形態に係るデータ補償回路のブロック図であり、図7は図6に示した補償部の内部ブロック図である。

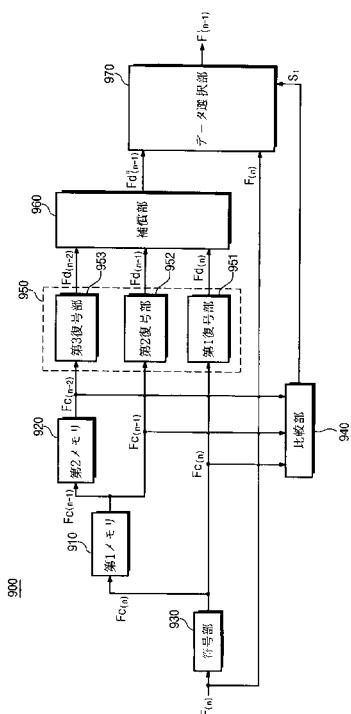

## 【0066】

図6を参照すると、本発明の他の実施形態に係るデータ補償回路900は、第1メモリ910、第2メモリ920、符号部930、比較部940、復号部950、補償部960及びデータ選択部970からなる。

## 【0067】

第1メモリ910にはn-1番目のフレームデータF(n-1)から圧縮されたn-1番目の圧縮データF c(n-1)があらかじめ格納されており、第2メモリ920にはn-2番目のフレームデータF(n-2)から圧縮されたn-2番目の圧縮データF c(n-2)があらかじめ格納されている。第1及び第2メモリ910、920は $2^m / i$ (ここで、mはn-1番目及びn-2番目のフレームデータF(n-1)、F(n-2)のビット数であり、iはmビットを圧縮しようとするビット数で分けた値)より小さいサイズを有する。

40

## 【0068】

本発明の一例として、n-1番目のフレームデータF(n-1)が24ビットからなると、n-1番目の圧縮データF c(n-1)は1/3に圧縮された8ビットからなる。ここで、m=24でi=3である。したがって、第1及び第2メモリ910、920は $2^8$ のサイズを有する。このように、第1及び第2メモリ910、920には1フレーム分量より

50

小さい分量の圧縮されたデータが格納されるので、第1及び第2メモリ910、920のサイズを減少させることができる。

【0069】

符号部930にはn番目のフレームの間、n番目のフレームデータF(n)が入力され、n番目のフレームデータF(n)をn番目の圧縮データF<sub>c</sub>(n)に圧縮する。n番目のフレームの間、第1及び第2メモリ910、920にあらかじめ格納されたn-1番目の圧縮データF<sub>c</sub>(n-1)及びn-2番目の圧縮データF<sub>c</sub>(n-2)がそれぞれ読み出され、以後n-1番目の圧縮データF<sub>c</sub>(n-1)及びn-2番目の圧縮データF<sub>c</sub>(n-2)が第1及び第2メモリ910、920にそれぞれ格納される。

【0070】

比較部940には、符号部930からのn番目の圧縮データF<sub>c</sub>(n)、第1メモリ910からのn-1番目の圧縮データF<sub>c</sub>(n-1)及び第2メモリ920からのn-2番目の圧縮データF<sub>c</sub>(n-2)が入力される。比較部940は、n番目の圧縮データF<sub>c</sub>(n)がn-1番目の圧縮データF<sub>c</sub>(n-1)及びn-2番目の圧縮データF<sub>c</sub>(n-2)と互いに同一であれば、第1状態を有する選択信号S1を出力する。また、比較部940は、n番目の圧縮データF<sub>c</sub>(n)がn-1番目の圧縮データF<sub>c</sub>(n-1)及びn-2番目の圧縮データF<sub>c</sub>(n-2)と互いに同一ではなく異なり、n-1番目の圧縮データF<sub>c</sub>(n-1)とn-2番目の圧縮データF<sub>c</sub>(n-2)が互いに同一であれば、第2状態を有する選択信号S1を出力する。

【0071】

復号部950は第1復号部951、第2復号部952及び第3復号部953からなる。第1復号部951には、符号部930からn番目の圧縮データF<sub>c</sub>(n)が入力され、n番目の圧縮データF<sub>c</sub>(n)をn番目の復元データF<sub>d</sub>(n)に復元して出力する。第2復号部952には、n-1番目の圧縮データF<sub>c</sub>(n-1)が入力され、n-1番目の圧縮データF<sub>c</sub>(n-1)をn-1番目の復元データF<sub>d</sub>(n-1)に復元して出力する。また、第3復号部953には、n-2番目の圧縮データF<sub>c</sub>(n-2)が入力され、n-2番目の圧縮データF<sub>c</sub>(n-2)をn-2番目の復元データF<sub>d</sub>(n-2)に復元して出力する。

【0072】

補償部960には、第1乃至第3復号部951、952、953からn番目乃至n-2番目の復元データF<sub>d</sub>(n)、F<sub>d</sub>(n-1)、F<sub>d</sub>(n-2)がそれぞれ入力される。補償部960はn番目乃至n-2番目の復元データF<sub>d</sub>(n)、F<sub>d</sub>(n-1)、F<sub>d</sub>(n-2)に基いて第1補償データF<sub>d</sub>''(n-1)を出力する。

【0073】

一方、データ選択部970には第1補償データF<sub>d</sub>''(n-1)、n番目のフレームデータF(n)及び比較部940から選択信号S1が入力され、出力データF'(n-1)を出力する。具体的に、データ選択部970には、第1状態を有する選択信号S1が入力されれば、n番目のフレームデータF(n)を出力データF'(n-1)として出力し、第2状態を有する選択信号S1が入力されれば、第1補償データF<sub>d</sub>''(n-1)を出力データF'(n-1)として出力する。

【0074】

図7に示したように、補償部960は第1補償部961及び第2補償部962からなる。

【0075】

第1補償部961はn-1番目の復元データF<sub>d</sub>(n-1)及びn-2番目の復元データF<sub>d</sub>(n-2)に基いて第2補償データF<sub>d</sub>''(n-1)を出力する。第2補償部962は第2補償データF<sub>d</sub>''(n-1)とn番目の復元データF<sub>d</sub>(n)に基いて第1補償データF<sub>d</sub>''(n-1)を出力する。

【0076】

第1補償部961はn-2番目の復元データF<sub>d</sub>(n-2)とn-1番目の復元データF<sub>d</sub>(n-1)との差分値があらかじめ設定された基準値以下であれば、第2補償データF<sub>d</sub>

10

20

30

40

50

' (n - 1)としてn - 1番目の復元データF d (n - 1)を出力し、基準値以上であれば、n - 1番目の復元データF d (n - 1)よりあらかじめ設定された補償値だけ増加した第2補償データF d ' (n - 1)を出力する。

【0077】

第2補償部962には第2補償データF d ' (n - 1)とn番目の復元データF d (n)が入力されて第1補償データF d " (n - 1)を出力する。本発明の一例として、第1補償データF d " (n - 1)は第2補償データF d ' (n - 1)とn番目の復元データF d (n)の中間値を有する。

【0078】

本発明の他の一例として、データ補償回路900は第2補償データF d ' (n - 1)とn番目の復元データF d (n)との値によってあらかじめ設定された補償データからなるルックアップテーブル(Look Up Table: LUT)(図示しない)をさらに含む。したがって、第2補償部962は、第2補償データF d ' (n - 1)とn番目の復元データF d (n)に基いてLUTからデータを抽出し、抽出した補償データを第1補償データF d " (n - 1)として出力する。

【0079】

データ選択部970は、選択信号S1の状態によって、第1補償データF d " (n - 1)及びn番目のフレームデータF (n)のうちのいずれか1つを出力データF ' (n - 1)として出力する。

【0080】

したがって、データ補償回路900は停止映像が表示される場合、圧縮されないn番目のフレームデータF (n)を出力することによって、データの損傷を防止することができる。また、停止映像から動画に変わる場合、変わった直前のデータと変わった直後のデータとの間の値F d " (n - 1)を出力することによって、変わった瞬間のデータ損傷を減少させることができる。

【0081】

<第3実施形態>

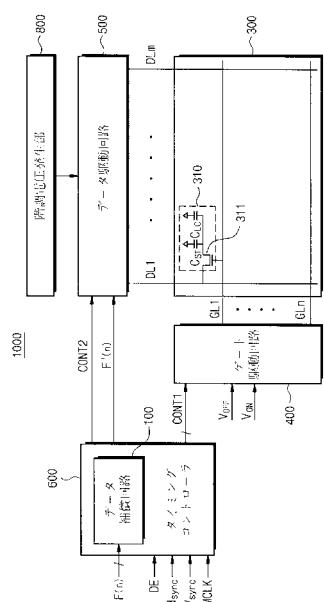

図8は図1に示したデータ駆動回路を備える液晶表示装置のブロック図である。

【0082】

図8を参照すると、液晶表示装置1000は映像を表示する表示部300、表示部300を駆動させるゲート駆動回路400とデータ駆動回路500、データ駆動回路500に接続された階調電圧発生部800及びゲート駆動回路400とデータ駆動回路500の駆動を制御するタイミングコントローラ600を含む。

【0083】

表示部300にはゲート電圧が入力される複数のゲートラインG L 1 ~ G L nとデータ電圧が入力される複数のデータラインD L 1 ~ D L mが備えられている。複数のゲートラインG L 1 ~ G L nと複数のデータラインD L 1 ~ D L mによって表示部300にはマトリックス形態で複数の画素領域が定義され、各画素領域には画素310が備えられている。画素310は薄膜トランジスタ311、液晶キャパシタC<sub>Lc</sub>及びストレージキャパシタC<sub>ST</sub>からなる。

【0084】

図8に示したように、薄膜トランジスタ311のゲート電極は第1ゲートラインG L 1に接続されており、ソース電極は第1データラインD L 1に接続されており、液晶キャパシタC<sub>Lc</sub>とストレージキャパシタC<sub>ST</sub>は薄膜トランジスタ311のドレイン電極に並列接続されている。

【0085】

本発明の一例として、表示部300は下部基板、下部基板と向い合う上部基板及び下部基板と上部基板との間に介在された液晶層からなっている。

【0086】

下部基板には複数のゲートラインG L 1 ~ G L n、複数のデータラインD L 1 ~ D L m

10

20

30

40

50

、薄膜トランジスタ311及び液晶キャパシタ $C_{LC}$ の第1電極である画素電極が形成されている。したがって、薄膜トランジスタ311はゲート電圧に応答してデータ電圧を画素電極に印加する。

【0087】

一方、上部基板には液晶キャパシタ $C_{LC}$ の第2電極である共通電極が形成されており、共通電極には共通電圧が印加される。画素電極と共通電極との間に介在された液晶層は誘電体の役割を実行する。したがって、液晶キャパシタ $C_{LC}$ にはデータ電圧と共通電圧との電位差に対応する電圧が充電される。

【0088】

ゲート駆動回路400は表示部300に備えられた複数のゲートライン $GL_1 \sim GL_n$ と電気的に接続されて、複数のゲートライン $GL_1 \sim GL_n$ にゲート電圧を提供する。データ駆動回路500は表示部300に備えられた複数のデータライン $DL_1 \sim DL_m$ と電気的に接続され、階調電圧発生部800からの階調電圧を選択して複数のデータライン $DL_1 \sim DL_m$ にデータ電圧として提供する。

【0089】

タイミングコントローラ600には各種制御信号、例えば垂直同期信号 $V_{sync}$ 、水平同期信号 $H_{sync}$ 、メインクロック $MCLK$ 、データイネーブル信号 $DE$ などが入力される。タイミングコントローラ600は各種制御信号に基づいてゲート制御信号 $CONT_1$ とデータ制御信号 $CONT_2$ とを出力する。

【0090】

ゲート制御信号 $CONT_1$ はゲート駆動回路400の動作を制御するための信号としてゲート駆動回路400に提供される。ゲート制御信号 $CONT_1$ はゲート駆動回路400の動作を開始する垂直開始信号、ゲート電圧の出力時期を決めるゲートクロック信号及びゲート電圧のオンパルス幅を決める出力イネーブル信号などを含んでいる。

【0091】

ゲート駆動回路400はタイミングコントローラ600からのゲート制御信号 $CONT_1$ に応答してゲートオン電圧 $V_{on}$ とゲートオフ電圧 $V_{off}$ の組合からなるゲート電圧を出力する。

【0092】

データ制御信号 $CONT_2$ はデータ駆動回路500の動作を制御する信号としてデータ駆動回路500として提供される。データ制御信号 $CONT_2$ はデータ駆動回路500の動作を開始する水平開始信号、データ電圧の極性を反転させる反転信号及びデータ駆動部からデータ電圧が出力される時期を決める出力指示信号などを含む。

【0093】

また、タイミングコントローラ600はチップ形態からなり、タイミングコントローラ600には図1に示したデータ補償回路100が内蔵されている。特に、メモリ110(図1に示す)には圧縮されたデータが格納されるので、メモリ110の全体のサイズが減少し、その結果、メモリ110をタイミングコントローラ600に内蔵させることができる。

【0094】

データ補償回路100は、現在フレームにおいて外部のグラフィック制御器(図示しない)から現在フレームデータ $F(n)$ が入力されて、補償された現在補償データ $F'(n)$ を出力する。データ駆動回路500は、タイミングコントローラ600からのデータ制御信号 $CONT_1$ に応答して現在補償データ $F'(n)$ が入力され、階調電圧発生部800からの階調電圧のうち現在補償データ $F'(n)$ に対応する階調電圧を選択してデータ電圧に変換して出力する。

【0095】

これによって、表示部300はデータ電圧とゲート電圧に応答して映像を表示する。特に、停止画面の場合、現在補償データ $F'(n)$ は圧縮または復元の過程なしに現在フレームデータ $F(n)$ に対応するデータ電圧に変換されるので、表示部300は損傷されないデ

10

20

30

40

50

ータを利用して映像を表示することができる。

【0096】

以上、実施形態を参照して説明したが、当業者は特許請求の範囲に記載した本発明の思想及び領域から逸脱しない範囲内で本発明を多様に修正及び変更させることができることを理解することができるであろう。

【産業上の利用可能性】

【0097】

本発明は、メモリを有する表示装置等に適用可能である。

【図面の簡単な説明】

【0098】

10

【図1】本発明の一参考例に係るデータ補償回路を示したブロック図である。

【図2】図1に示したデータ補償回路によって補償された現在フレームに対応する電圧及び輝度を示すグラフである。

【図3】図1に示したデータ補償回路によって補償された現在フレームに対応する電圧及び輝度を示すグラフである。

【図4】本発明の一実施形態に係るデータ補償回路を示すブロック図である。

【図5】図4に示した補償部の内部ブロック図である。

【図6】本発明の他の実施形態に係るデータ補償回路のブロック図である。

【図7】図6に示した補償部の内部ブロック図である。

【図8】図1に示したデータ補償回路を具備する液晶表示装置のブロック図である。

20

【符号の説明】

【0099】

100 データ補償回路

110 メモリ

120 復号部

130 コーデック部

140 第1処理部

150 第2処理部

160 補償部

300 表示部

30

400 ゲート駆動回路

500 データ駆動回路

600 タイミングコントローラ

1000 液晶表示装置

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

(51)Int.Cl.

F I

|         |      |         |

|---------|------|---------|

| G 0 9 G | 3/20 | 6 3 1 D |

| G 0 9 G | 3/20 | 6 1 2 L |

| G 0 9 G | 3/20 | 6 1 2 J |

| G 0 9 G | 3/20 | 6 2 4 B |

| G 0 9 G | 3/20 | 6 1 2 U |

| G 0 9 G | 3/20 | 6 3 2 F |

| G 0 9 G | 3/20 | 6 2 1 F |

(72)発明者 南 亨 植

大韓民国仁川廣域市延壽區玉蓮洞ウソンアパート105 - 605

(72)発明者 朴 東 園

大韓民国忠清南道天安市佛堂洞デンドラスップアパート110 - 1402

審査官 中村 直行

(56)参考文献 特開2005-316369 (JP, A)

特開2006-047993 (JP, A)

特開2006-113359 (JP, A)

特開2005-017484 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 0 9 G 3 / 0 0 - 5 / 4 2

G 0 2 F 1 / 1 3 3