(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-317127

(P2005-317127A)

(43) 公開日 平成17年11月10日(2005.11.10)

(51) Int.Cl.<sup>7</sup>

G 11 C 16/02

F 1

G 11 C 17/00

6 O 1 Q

テーマコード(参考)

5 B 12 5

審査請求 未請求 請求項の数 3 O L (全 8 頁)

(21) 出願番号

特願2004-134486 (P2004-134486)

(22) 出願日

平成16年4月28日 (2004.4.28)

(71) 出願人

000005821

松下電器産業株式会社

大阪府門真市大字門真1006番地

(74) 代理人

100098291

弁理士 小笠原 史朗

(72) 発明者

小宮 学

大阪府門真市大字門真1006番地 松下

電器産業株式会社内

(72) 発明者

諫訪 仁史

大阪府門真市大字門真1006番地 松下

電器産業株式会社内

(72) 発明者

富田 泰弘

大阪府門真市大字門真1006番地 松下

電器産業株式会社内

F ターム(参考) 5B125 BA01 CA11 DE20 EA10

(54) 【発明の名称】不揮発性半導体記憶装置

## (57) 【要約】

**【課題】** 従来のCPU等に搭載あるいは接続されるフラッシュメモリ等の不揮発性半導体記憶装置は、ソフトによるCPUの暴走及びノイズによる誤ったコマンド発行が原因のプロテクトやユーザが入ってはならないモードへの移行といった、誤ったコマンド発行が原因の予期せぬモードへの移行の問題がある。

**【解決手段】** コマンドを受理するコマンドデコーダと、書き換えや読み出し等の各種モードを制御する制御回路と、コマンドデコーダに入力され、外部から入力されたプロテクトやテストモード等の特定のコマンドを受け付けるか受け付けないかを制御する信号を設けることで、ソフトによるCPUの暴走及びノイズによる誤ったコマンド発行が原因のプロテクトやユーザが入ってはならないモードへの移行といった、誤ったコマンド発行が原因の予期せぬモードへの移行を防ぐことが出来る。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

メモリセルと、前記メモリセルをアレイ状にならべ幾つかの消去ブロックをもったメモリセルアレイと、コマンドを受理するコマンドデコーダと、書き換えや読み出し等の各種モードを制御する制御回路と、前記コマンドデコーダに入力され、外部から入力された少なくとも一つ以上の特定のコマンドを受け付けるか受け付けないかを制御する配線層により形成された一つまたは複数の制御信号を備えた不揮発性半導体記憶装置。

**【請求項 2】**

前記コマンドデコーダに入力され、外部から入力された少なくとも一つ以上の特定のコマンドを受け付けるか受け付けないかを制御する、内部に設けられたレジスタにより形成された一つまたは複数の制御信号を備えた請求項 1 の不揮発性半導体記憶装置。 10

**【請求項 3】**

メモリセルと、前記メモリセルをアレイ状にならべ幾つかの消去ブロックをもったメモリセルアレイと、コマンドを受理するコマンドデコーダと、書き換えや読み出し等の各種モードを制御する制御回路と、特別なテストモードでしかアクセスできないコンフィギュレーションデータ格納領域と、前記コマンドデコーダに入力され、外部から入力された少なくとも一つ以上の特定のコマンドを受け付けるか受け付けないかを制御する、内部に設けられた前記レジスタにより形成された一つまたは複数の制御信号を備え、前記レジスタは前記コンフィギュレーションデータにセットされているデータが転送されることを特徴とした請求項 2 の不揮発性半導体記憶装置。 20

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、C P U 等の搭載或いは接続された半導体装置のソフト等による暴走及びノイズによる誤った命令を発行された場合でも、例えば誤ったプロテクション ( P r o t e c t i o n ) やユーザに対して非公開のモードに入ることを防ぐことが出来る不揮発性半導体記憶装置に関する。 30

**【背景技術】****【0002】**

ここでは特定コマンドの例として、プロテクション及びテストモードを説明する。ソフトの多様化や増大によるC P U の暴走やセットの小型化による半導体装置の実装密集化によるノイズにおける不揮発性半導体記憶装置のデータやプログラムの破壊に対しての対策としてプロテクション機能を備えている。しかし、プロテクションのレベルを上げるために一度プロテクションがかかった領域に対してアンプロテクト ( U n p r o t e c t ) が出来ないような構造になっているためC P U の暴走やノイズによる誤ったプロテクション命令発行によりプロテクションがかかってしまうと、そのブロックは書き換えが出来なくなってしまう。従って、プロテクションしたくないブロックに対しての誤ったプロテクション命令の発行に対しての対策は重要である。 40

**【0003】**

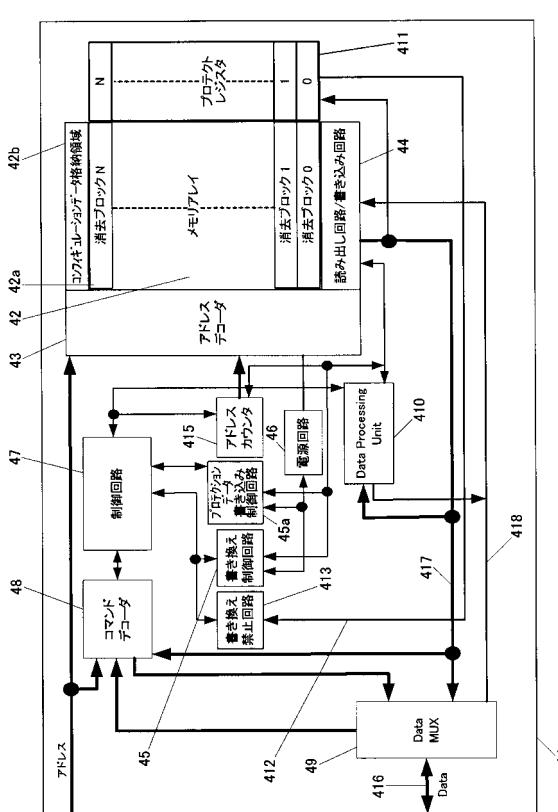

以下、従来の不揮発性半導体記憶装置について説明する。従来の不揮発性半導体記憶装置の構成を図 4 に示す。図 4 において、4 1 はフラッシュメモリ等の不揮発性半導体記憶装置、4 2 はメモリアレイ、4 2 a はメモリアレイ 4 2 内の消去ブロック、4 2 b はプロテクションの情報等を格納するコンフィギュレーションデータ格納領域、4 3 はアドレスデコーダ、4 4 は読み出し及び書き込み時にメモリセルのドレインに対して高電圧を印加する読み出し回路 / 書き込み回路、4 5 は書き換え制御回路、4 5 a はコンフィギュレーションデータ格納領域にプロテクションデータ ( P r o t e c t i o n D a t a ) を書き込むプロテクションデータ書き込み制御回路、4 6 は高電圧を発生させる昇圧回路等の電源回路、4 7 は書き換えアルゴリズムコントローラを含めた制御回路、4 8 はコマンドデコーダ、4 9 はデータ入出力切り替え回路を含めた Data M U X 、4 1 0 は書き込 50

みデータの生成及び書き換え時の期待値を生成する Data Processing Unit (DPU)、411はプロテクトビットプログラムコマンド(Protect Bit Program Command)によりコンフィギュレーションデータ格納領域42bに消去ブロック42aに対応したビット(Bit)が書き込まれた情報を格納する消去ブロック数分あるプロテクトレジスタ(Protect Register)、412はプロテクトレジスタ411のデータを出力するプロテクト情報信号、413はプロテクト情報信号412の情報により書き換え許可するかしないかを制御する書き換え禁止回路、415はアドレスを内部発生するアドレスカウンタ、416は不揮発性半導体記憶装置41の入出力データバス、417は読み出し回路/書き込み回路44から出力される出力バス及び418は書き込みデータ等を入力する入力バスである。

10

## 【0004】

プロテクト(Protect)の実行は、プロテクトコマンド(Protect Command)及びプロテクトする消去ブロックアドレスを入出力データバス416及びアドレス端子に入力する。コマンドデコーダ48によりコマンドが解読され、制御回路47を通じてプロテクションデータ書き込み制御回路45aにプロテクト命令を発行することで、アドレスカウンタ415やDPU410を制御してコンフィギュレーションデータ格納領域42bに消去ブロック番号に対応したビットがセットされる。次に、制御回路47により読み出し回路44を介して消去ブロック番号に対応するプロテクトレジスタ411に転送される。プロテクトレジスタ411がセットされている消去ブロック42aは、書き換え禁止回路413により書き換えが出来なくなる。また、各種テストモードへの移行は、テストモードコマンドをコマンドデコーダ48に入力することで行われる。

20

## 【0005】

なお、コンフィギュレーションデータ格納領域42bは、ユーザに公開しないテストモードに設定しないと、これらの領域に対してRead及び書き換えができないようになっている。更に、プロテクションレベルを上げるためにアンプロテクトコマンド(Unprotect Command)を設けていない或いは通常セットに搭載されるとあり得ない高電圧を有する外部端子に印加しないとアンプロテクトできない不揮発性半導体記憶装置が多くなっている。

30

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0006】

従来のCPU等に搭載或いは接続されるフラッシュメモリ等の不揮発性半導体記憶装置は、ソフトによるCPUの暴走及びノイズによる誤ったコマンド発行が原因のプロテクトやユーザが入ってはならないモードへの移行といった、誤ったコマンド発行が原因の予期せぬモードへの移行が問題であった。本発明は、このような問題を解決する不揮発性半導体記憶装置を提供することを目的とする。

## 【課題を解決するための手段】

## 【0007】

上記の課題を達成するために、本発明の不揮発性半導体記憶装置は、コマンドを受理するコマンドデコーダと、書き換えや読み出し等の各種モードを制御する制御回路と、コマンドデコーダに入力され、外部から入力されたプロテクトやテストモード等の特定のコマンドを受け付けるか受け付けないかを制御する配線層により形成された一つまたは複数の制御信号とを備える。

40

## 【0008】

また、本発明の不揮発性半導体記憶装置は、コマンドデコーダに入力され、外部から入力されたプロテクトやテストモード等の特定のコマンドを受け付けるか受け付けないかを制御する、内部に設けられたレジスタにより形成された一つまたは複数の制御信号を備えていてもよい。

## 【0009】

また、本発明の不揮発性半導体記憶装置は、コマンドを受理するコマンドデコーダと、

50

書き換えや読み出し等の各種モードを制御する制御回路と、特別なテストモードでしかアクセスできないコンフィギュレーションデータ格納領域と、コマンドデコーダに入力され、外部から入力されたプロテクトやテストモード等の特定のコマンドを受け付けるか受け付けないかを制御する、内部に設けられたレジスタにより形成された一つまたは複数の制御信号とを備え、レジスタはコンフィギュレーションデータにセットされているデータが転送されることが好ましい。

【発明の効果】

【0010】

本発明の不揮発性半導体記憶装置は、コマンドを受理するコマンドデコーダと、書き換えや読み出し等の各種モードを制御する制御回路と、コマンドデコーダに入力され、外部から入力されたプロテクトやテストモード等の特定のコマンドを受け付けるか受け付けないかを制御する配線層により形成された一つまたは複数の制御信号とを備える。この構成をとることで、ソフトによるCPUの暴走及びノイズによる誤ったコマンド発行が原因のプロテクトやユーザが入ってはならないモードへの移行といった予期せぬモードへの移行を防ぐことが出来る。また、アンプロテクトコマンドが存在する不揮発性半導体記憶装置においてもアンプロテクトコマンドを禁止する制御信号を設ければ高電圧を使用しなくても不揮発性半導体記憶装置のデータの保護が可能となる。

【0011】

また、本発明の不揮発性半導体記憶装置は、コマンドデコーダに入力され、外部から入力されたプロテクトやテストモード等の特定のコマンドを受け付けるか受け付けないかを制御する、内部に設けられたレジスタにより形成された一つまたは複数の制御信号を備える。この構成をとることで、半導体記憶装置の端子数を増やすことなくソフトによるCPUの暴走及びノイズによる誤ったコマンド発行が原因のプロテクトやユーザが入ってはならないモードへの移行といった予期せぬモードへの移行及び高電圧を使用しなくとも不揮発性半導体記憶装置のデータの破壊を防ぐことが出来る。

【0012】

更に、本発明の不揮発性半導体記憶装置は、コマンドを受理するコマンドデコーダと、書き換えや読み出し等の各種モードを制御する制御回路と、特別なテストモードでしかアクセスできないコンフィギュレーションデータ格納領域と、コマンドデコーダとに入力され、外部から入力されたプロテクトやテストモード等の特定のコマンドを受け付けるか受け付けないかを制御する、内部に設けられたレジスタにより形成された一つまたは複数の制御信号とを備え、レジスタはコンフィギュレーションデータにセットされているデータが転送されることを特徴として、使用しなくなったモードや移行したくないモードに対して毎回レジスタにセットすることなく、ソフトによるCPUの暴走及びノイズによる誤ったコマンド発行が原因のプロテクトやユーザが入ってはならないモードへの移行といった予期せぬモードへの移行及び高電圧を使用しなくとも不揮発性半導体記憶装置のデータの破壊を防ぐことが出来る。

【発明を実施するための最良の形態】

【0013】

以下、本発明の実施の形態について図面を参照しながら説明する。なお、ここで示す実施の形態はあくまで一例であり、必ずしもこの形態に限定されるものではない。

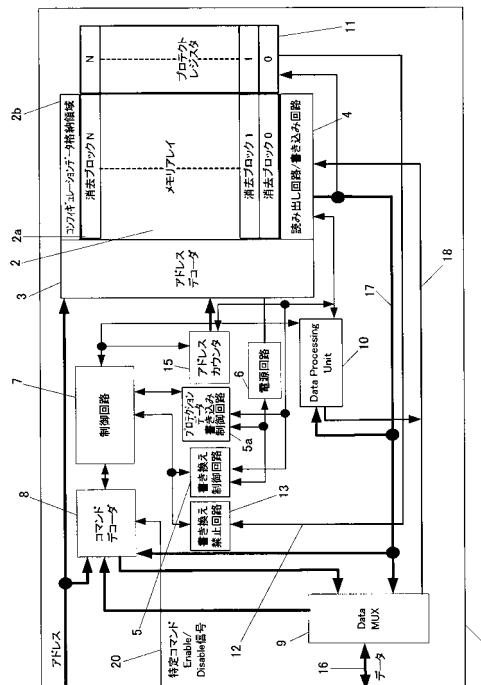

【0014】

(実施の形態1)

図1に本発明の実施の形態1に係る半導体記憶装置の構成を示す。以下に図1を参照しながら本発明の半導体記憶装置の実施の形態1を説明する。

【0015】

図1において、1はフラッシュメモリ等の不揮発性半導体記憶装置、2はメモリアレイ、2aはメモリアレイ2内の消去ブロック、2bはプロテクションの情報等を格納するコンフィギュレーションデータ格納領域、3はアドレスデコーダ、4は読み出し及び書き込み時にメモリセルのドレンに印加する読み出し回路/書き込み回路、5

10

20

30

40

50

は書き換え制御回路、5aはコンフィギュレーションデータ格納領域にプロテクションデータを書き込むプロテクションデータ書き込み制御回路、6は高電圧を発生させる昇圧回路等の電源回路、7は書き換えアルゴリズムコントローラを含めた制御回路、8はコマンドデコーダ、9はデータ入出力切り替え回路を含めたData MUX、10は書き込みデータの生成及び書き換え時の期待値を生成するDPU、11はプロテクトビットプログラムコマンドによりコンフィギュレーションデータ格納領域2bに消去ブロック2aに対応したビットが書き込まれた情報を格納する消去ブロック数分あるプロテクトレジスタ、12はプロテクトレジスタ11のデータを出力するプロテクト情報信号、13はプロテクト情報信号12の情報により書き換え許可するかしないかを制御する書き換え禁止回路、15はアドレスを内部発生するアドレスカウンタ、16は不揮発性半導体記憶装置1の入出力データバス、17は読み出し回路／書き込み回路4から出力される出力バス、18は書き込みデータ等を入力する入力バス及び20はコマンドデコーダ8に入力され、プロテクト／アンプロテクト及びテストモードといった特定のコマンドを受け付けるか受け付けないかを制御する特定コマンドEnable/Disable端子である。

10

20

30

## 【0016】

プロテクトの実行は、プロテクトコマンド及びプロテクトする消去ブロックアドレスを入出力データバス16及びアドレス端子に入力する。コマンドデコーダ8によりコマンドが解読され制御回路7を通じてプロテクションデータ書き込み制御回路5aにプロテクト命令を発行することでアドレスカウンタ15やDPU10を制御してコンフィギュレーションデータ格納領域2bに消去ブロック番号に対応したビットがセットされる。次に、制御回路7により読み出し回路／書き込み回路4を介して消去ブロック番号に対応するプロテクトレジスタ11に転送される。プロテクトレジスタ11がセットされている消去ブロック2aは、書き換え禁止回路13により書き換えが出来なくなる。また、各種テストモードへの移行はテストモードコマンドをコマンドデコーダ8に入力することで行われる。

## 【0017】

ここで特定コマンドEnable/Disable端子20を、プロテクトコマンド及びテストモードコマンドに設けることでブート(Boot)領域へのプロテクト設定やテストモードに設定したいときは、特定コマンドEnable/Disable端子20を”H”に設定する。プロテクト設定を終えたときには、特定コマンドEnable/Disable端子20を”L”にする。テストモードは、トリミングデータ等の設定値を格納しておくコンフィギュレーションデータ格納領域2bを選択する手段も含んでいる。従って、ユーザが使用するとき、誤ってコンフィギュレーションデータ格納領域2bを書き換えてしまっては不揮発性半導体装置1は、誤動作してしまう。また、プロテクションを設定した領域はアンプロテクトする手段が無いため不揮発性半導体記憶装置1は、不良となってしまう。特定コマンドEnable/Disable端子20を設けることにより、ユーザ使用時及びプロテクトをかけたくない状況で、CPUの暴走やノイズでのテストモード及びプロテクトに設定されることを防ぐことが出来る。

30

## 【0018】

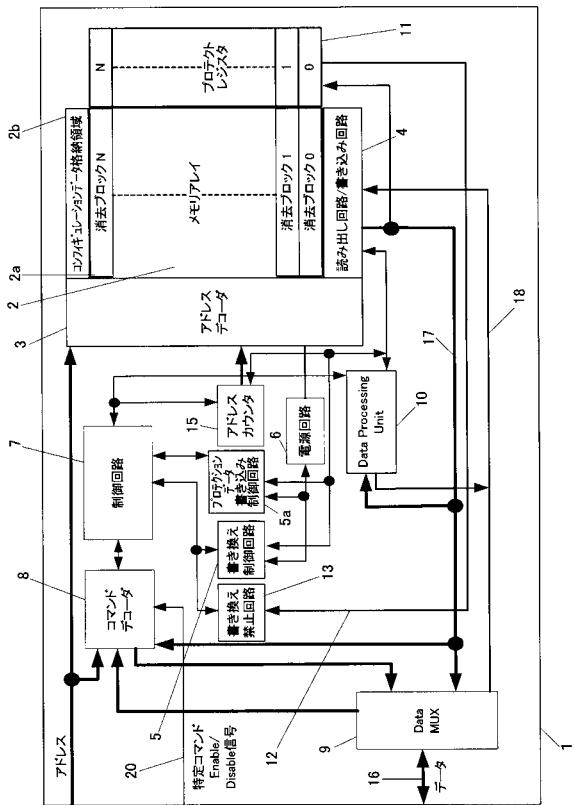

(実施の形態2)

図2に本発明の実施の形態2に係る半導体記憶装置の構成を示す。以下に図2を参照しながら本発明の半導体記憶装置の実施の形態2を説明する。

40

## 【0019】

図2において、21はフラッシュメモリ等の不揮発性半導体記憶装置、22はメモリアレイ、22aはメモリアレイ22内の消去ブロック、22bはプロテクションの情報等を格納するコンフィギュレーションデータ格納領域、23はアドレスデコーダ、24は読み出し及び書き込み時にメモリセルのドレインに対して高電圧を印加する読み出し回路／書き込み回路、25は書き換え制御回路、25aはコンフィギュレーションデータ格納領域にプロテクションデータを書き込むプロテクションデータ書き込み制御回路、26は高電圧を発生させる昇圧回路等の電源回路、27は書き換えアルゴリズムコントローラを含めた制御回路、28はコマンドデコーダ、29はデータ入出力切り替え回路を含めたData t

50

a MUX、210は書き込みデータの生成及び書き換え時の期待値を生成するDPU、211はプロテクトビットプログラムコマンドによりコンフィギュレーションデータ格納領域22bに消去ブロック22aに対応したビットが書き込まれた情報を格納する消去ブロック数分あるプロテクトレジスタ、212はプロテクトレジスタ211のデータを出力するプロテクト情報信号、213はプロテクト情報信号212の情報により書き換え許可するかしないかを制御する書き換え禁止回路、215はアドレスを内部発生するアドレスカウンタ、216は不揮発性半導体記憶装置21の入出力データバス、217は読み出し回路／書き込み回路24から出力される出力バス、218は書き込みデータ等を入力する入力バス、219はテストモードで入出力データバス216からデータをセットできる揮発性レジスタ及び220はコマンドデコーダ28に入力され、プロテクト／アンプロテクト及びテストモードといった特定のコマンドを受け付けるか受け付けないかを制御する特定コマンドEnable/Disable信号である。

10

20

【0020】

プロテクト実行及びテストモードの設定は実施の形態1と同様である。ここで実施の形態1における特定コマンドEnable/Disable端子20は禁止したいコマンドの数だけ必要となり端子数が限られている少ピンの半導体装置には不向きである。そこで内部レジスタ219を設け、入出力データバス216からEnable/Disableするコマンドに対応した内部レジスタ219に設定することで、端子数を増やすことなく、ソフトによるCPUの暴走及びノイズによる誤ったコマンド発行が原因のプロテクトやユーザが入ってはならないモードへの移行といった、誤ったコマンド発行が原因の予期せぬモードへの移行及びアンプロテクトコマンドがある場合でも、揮発性レジスタ219を設けることで高電圧を使用しなくても不揮発性半導体記憶装置のデータの破壊を防止することが出来る。

20

【0021】

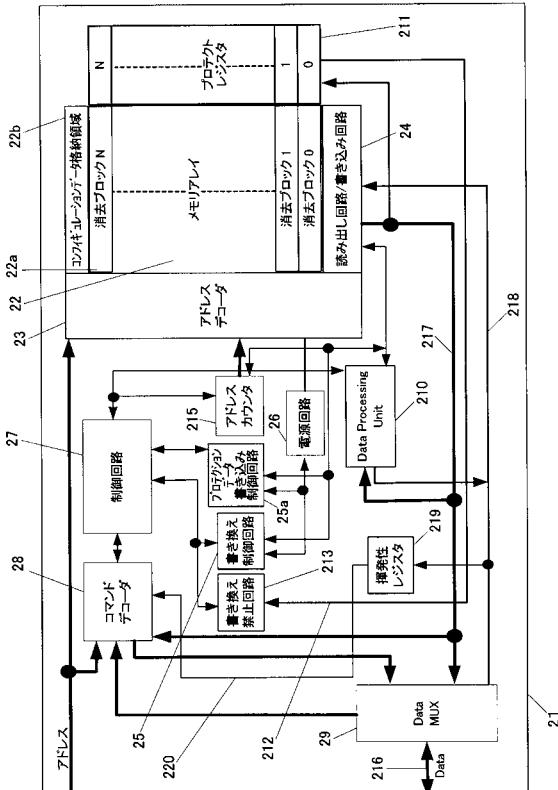

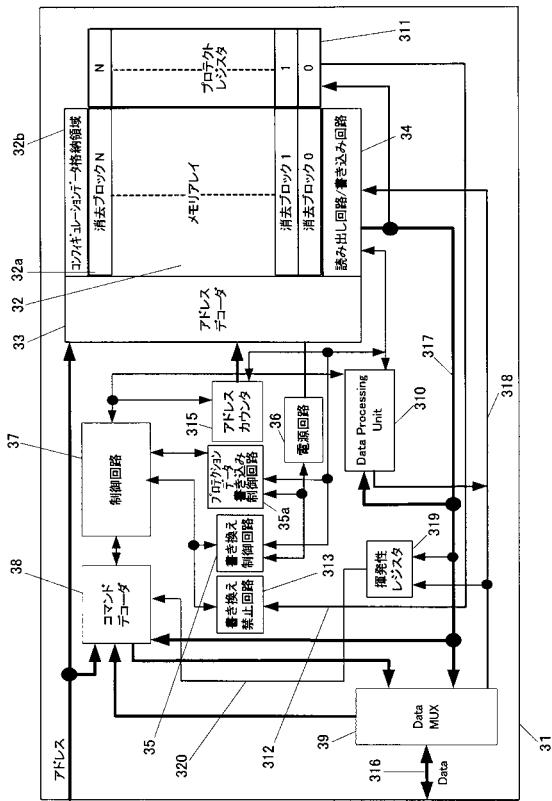

(実施の形態3)

図3に本発明の実施の形態3に係る半導体記憶装置の構成を示す。以下に図3を参照しながら本発明の半導体記憶装置の実施の形態3を説明する。

30

【0022】

図3において、31はフラッシュメモリ等の不揮発性半導体記憶装置、32はメモリアレイ、32aはメモリアレイ32内の消去ブロック、32bはプロテクションの情報等を格納するコンフィギュレーションデータ格納領域、33はアドレスデコーダ、34は読み出し及び書き込み時にメモリセルのドレインに対して高電圧を印加する読み出し回路／書き込み回路、35は書き換え制御回路、35aはコンフィギュレーションデータ格納領域にプロテクションデータを書き込むプロテクションデータ書き込み制御回路、36は高電圧を発生させる昇圧回路等の電源回路、37は書き換えアルゴリズムコントローラを含めた制御回路、38はコマンドデコーダ、39はデータ入出力切り替え回路を含めたData MUX、310は書き込みデータの生成及び書き換え時の期待値を生成するDPU、311はプロテクトビットプログラムコマンドによりコンフィギュレーションデータ格納領域32bに消去ブロック32aに対応したビットが書き込まれた情報を格納する消去ブロック数分あるプロテクトレジスタ、312はプロテクトレジスタ311のデータを出力するプロテクト情報信号、313はプロテクト情報信号312の情報により書き換え許可するかしないかを制御する書き換え禁止回路、315はアドレスを内部発生するアドレスカウンタ、316は不揮発性半導体記憶装置31の入出力データバス、317は読み出し回路／書き込み回路34から出力される出力バス、318は書き込みデータ等を入力する入力バス、319はコンフィギュレーションデータ格納領域32bにセットされているデータが電源立ち上げ時に転送される揮発性レジスタ及び320はコマンドデコーダ38に入力され、プロテクト／アンプロテクト及びテストモードといった特定のコマンドを受け付けるか受け付けないかを制御する特定コマンドEnable/Disable信号である。

40

【0023】

50

プロテクト実行及びテストモードの設定は、実施の形態1と同様である。ここで実施の形態2における揮発性レジスタ219は、毎回セットが必要となってしまう。そこで工場出荷時にユーザが要望する消去ブロック32aにプロテクトを設定し、コンフィギュレーションデータ領域32bに揮発性レジスタ319の禁止したいコマンドに対応したデータをセットする。コンフィギュレーションデータ格納領域32bのデータは、電源を立ち上げるときに制御回路37及びアドレスカウンタ315により、揮発性レジスタ319に転送されるようになっている。この構成により、端子数を増やすことなく、また毎回設定する必要がなくユーザは意識することなく、ソフトによるCPUの暴走及びノイズによる誤ったコマンド発行が原因のプロテクトやユーザが入ってはならないモードへの移行といった、誤ったコマンド発行が原因の予期せぬモードへの移行及びアンプロテクトコマンドがある場合でも、揮発性レジスタ319を設け、コンフィギュレーションデータ格納領域32bに対応させることで、高電圧を使用しなくても不揮発性半導体記憶装置のデータの破壊を防止することが出来る。

10

20

50

## 【産業上の利用可能性】

## 【0024】

本発明は、CPU等の搭載或いは接続された半導体装置のソフト等による暴走及びノイズによる誤った命令を発行された場合でも、例えば誤ったプロテクション(Protection)やユーザに対して非公開のモードに入ることを防ぐことが出来る不揮発性半導体記憶装置であるため、フラッシュメモリ等に利用できる。

## 【図面の簡単な説明】

## 【0025】

【図1】本発明の実施の形態1に係る不揮発性半導体記憶装置の構成図

【図2】本発明の実施の形態2に係る不揮発性半導体記憶装置の構成図

【図3】本発明の実施の形態3に係る不揮発性半導体記憶装置の構成図

【図4】不揮発性半導体記憶装置の従来例を示す構成図

## 【符号の説明】

## 【0026】

1、21、31、41 フラッシュメモリ等の不揮発性半導体記憶装置

2、22、32、42 ユーザ領域メモリアレイ

2a、22a、32a、42a 消去ブロック

30

2b、22b、32b、42b コンフィギュレーションデータ格納領域

3、23、33、43 アドレスデコーダ

4、24、34、44 読み出し回路 / 書き込み回路

5、25、35、45 書き換え制御回路

5a、25a、35a、45a プロテクションデータ書き込み制御回路

6、26、36、46 電源回路

7、27、37、47 制御回路

8、28、38、48 コマンドデコーダ

9、29、39、49 Data MUX

40

10、210、310、410 Data Processing Unit (DPU)

11、211、311、411 プロテクトレジスタ

12、212、312、412 プロテクト情報信号

13、213、313、413 書き換え禁止回路

15、215、315、415 アドレスカウンタ

16、216、316、416 入出力データバス

17、217、317、417 出力バス

18、218、318、418 入力バス

219、319、揮発性レジスタ

20、220、320、特定コマンドEnable/Disable信号

【 図 1 】

【図2】

【 図 3 】

【図4】