(19) 日本国特許庁 (JP)

(12) 公 開 特 許 公 報(A)

(11) 特許出願公開番号

特開2007-207411

(P2007-207411A)

(43) 公開日 平成19年8月16日(2007.8.16)

| (51) Int.Cl.         | F 1              |         |       | テーマコード (参考)   |

|----------------------|------------------|---------|-------|---------------|

| <b>G 1 1 C</b> 19/28 | <b>(2006.01)</b> | G 1 1 C | 19/28 | D 5C006       |

| <b>G 0 9 G</b> 3/20  | <b>(2006.01)</b> | G 0 9 G | 3/20  | 6 2 2 E 5C080 |

| <b>G 0 9 G</b> 3/36  | <b>(2006.01)</b> | G 0 9 G | 3/36  |               |

| <b>G 1 1 C</b> 19/00 | <b>(2006.01)</b> | G 1 1 C | 19/00 | J             |

|                      |                  | G 1 1 C | 19/00 | K             |

審査請求 未請求 請求項の数 16 O.L. (全 24 頁)

|              |                              |          |                                            |

|--------------|------------------------------|----------|--------------------------------------------|

| (21) 出願番号    | 特願2006-351076 (P2006-351076) | (71) 出願人 | 000006013<br>三菱電機株式会社<br>東京都千代田区丸の内二丁目7番3号 |

| (22) 出願日     | 平成18年12月27日 (2006.12.27)     | (74) 代理人 | 100089233<br>弁理士 吉田 茂明                     |

| (31) 優先権主張番号 | 特願2006-390 (P2006-390)       | (74) 代理人 | 100088672<br>弁理士 吉竹 英俊                     |

| (32) 優先日     | 平成18年1月5日 (2006.1.5)         | (74) 代理人 | 100088845<br>弁理士 有田 貴弘                     |

| (33) 優先権主張国  | 日本国 (JP)                     | (72) 発明者 | 飛田 洋一<br>東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内       |

(54) 【発明の名称】 シフトレジスタ回路およびそれを備える画像表示装置

(57) 【要約】

【課題】シフトレジスタ回路の誤動作を防止し、動作信頼性を向上させる。

【解決手段】シフトレジスタ回路は、出力端子OUTと第1クロック端子Aとの間のトランジスタQ1と、出力端子OUTと第1電源端子s1との間のトランジスタQ2と、トランジスタQ1のゲートが接続するノードN1を入力端としてトランジスタQ2のゲートが接続するノードN2を出力端とするインバータとを備える。当該インバータは、ノードN2と第1電源端子s1との間に直列に接続し、ノードN1に接続したゲートをそれぞれ有するトランジスタQ7A, Q7Bと、ノードN2と第3電源端子s3との間に接続し、当第3電源端子s3に接続したゲートを有するトランジスタQ6と、トランジスタQ7AとトランジスタQ7Bとの接続ノードである第3ノードと第4電源端子s4との間に接続し、ノードN2に接続したゲートを有するトランジスタQ8とを備える。

○

### 【選択図】図 7

## 【特許請求の範囲】

## 【請求項 1】

クロック端子および出力端子と、

前記出力端子と前記クロック端子との間に接続する第1トランジスタと、

前記出力端子を放電する第2トランジスタと、

前記第1トランジスタの制御電極が接続するノードである第1ノードを入力端とし、前記第2トランジスタの制御電極が接続するノードである第2ノードを出力端とする第1プルダウン駆動回路とを備え、

前記第1プルダウン駆動回路は、

前記第2ノードと第1電源端子との間に直列接続した第3および第4トランジスタと、

前記第2ノードと第2電源端子との間に接続した第5トランジスタと、

前記第2ノードの電位で制御されて、前記第3トランジスタと前記第4トランジスタとの接続ノードである第3ノードに帰還電流を流す第6トランジスタとを備えることを特徴とするシフトレジスタ回路。

## 【請求項 2】

請求項1記載のシフトレジスタ回路であって、

前記第3および第4トランジスタの制御電極は、前記第1ノードに接続し、

前記第5トランジスタの制御電極は、前記第2電源端子に接続し、

前記第6トランジスタは、前記第3ノードと第3電源端子との間に接続し、その制御電極が前記第2ノードに接続していることを特徴とするシフトレジスタ回路。

## 【請求項 3】

請求項2記載のシフトレジスタ回路であって、

前記第2および前記第3電源端子は、同一の端子により構成されていることを特徴とするシフトレジスタ回路。

## 【請求項 4】

請求項1から請求項3のいずれか記載のシフトレジスタ回路であって、

前記第1ノードを充電するタイミングを規定する信号が入力される入力端子と、

前記入力端子を入力端とし前記第2ノードを出力端とする第2プルダウン駆動回路とをさらに備え、

前記第2プルダウン駆動回路は、

前記第2ノードと前記第1電源端子との間に直列接続した第7および第8トランジスタと、

前記第2ノードと前記第2電源端子との間に接続した第9トランジスタと、

前記第2ノードの電位に制御されて、前記第7トランジスタと第8トランジスタとの接続ノードである第4ノードに帰還電流を流す第10トランジスタとを備えることを特徴とするシフトレジスタ回路。

## 【請求項 5】

請求項4記載のシフトレジスタ回路であって、

前記第7および第8トランジスタの制御電極は、前記入力端子に接続し、

前記第9トランジスタの制御電極は、前記第2電源端子に接続し、

前記第10トランジスタは、前記第4ノードと第4電源端子との間に接続し、その制御電極が前記第2ノードに接続していることを特徴とするシフトレジスタ回路。

## 【請求項 6】

請求項4または請求項5記載のシフトレジスタ回路であって、

前記第5および第9トランジスタは、同一のトランジスタにより構成されており、

前記第6および第10トランジスタは、同一のトランジスタにより構成されていることを特徴とするシフトレジスタ回路。

## 【請求項 7】

10

20

30

40

50

請求項 5 記載のシフトレジスタ回路であって、

前記第 2 および前記第 4 電源端子は、同一の端子により構成されている

ことを特徴とするシフトレジスタ回路。

【請求項 8】

請求項 1 から請求項 7 のいずれか記載のシフトレジスタ回路であって、

前記第 1 ノードと前記出力端子との間に接続する容量素子をさらに備える

ことを特徴とするシフトレジスタ回路。

【請求項 9】

請求項 1 から請求項 8 のいずれか記載のシフトレジスタ回路が複数個従属接続して成る

シフトレジスタ回路。

10

【請求項 10】

請求項 9 記載のシフトレジスタ回路をゲート線駆動回路とする画像表示装置。

【請求項 11】

クロック端子および出力端子と、

前記出力端子と前記クロック端子との間に接続する第 1 トランジスタと、

前記出力端子を放電する第 2 トランジスタと、

前記第 1 トランジスタの制御電極が接続するノードである第 1 ノードを充電するタイミングを規定する信号が入力される入力端子と、

前記入力端子を入力端とし前記第 2 トランジスタの制御電極が接続するノードである第 2 ノードを出力端とするプルダウン駆動回路とを備え、

前記プルダウン駆動回路は、

前記第 2 ノードと第 1 電源端子との間に直列接続した第 3 および第 4 トランジスタと、

前記第 2 ノードと第 2 電源端子との間に接続した第 5 トランジスタと、

前記第 2 ノードの電位で制御されて、前記第 3 トランジスタと第 4 トランジスタとの接続ノードである第 3 ノードに帰還電流を流す第 6 トランジスタとを備える

ことを特徴とするシフトレジスタ回路。

20

【請求項 12】

請求項 11 記載のシフトレジスタ回路であって、

前記第 3 および第 4 トランジスタの制御電極は、前記入力端子に接続し、

前記第 5 トランジスタの制御電極は、前記第 2 電源端子に接続し、

前記第 6 トランジスタは、前記第 3 ノードと第 3 電源端子との間に接続し、その制御端子が前記第 2 ノードに接続している

ことを特徴とするシフトレジスタ回路。

30

【請求項 13】

請求項 12 記載のシフトレジスタ回路であって、

前記第 2 および第 3 電源端子は、同一の端子により構成されている

ことを特徴とするシフトレジスタ回路。

40

【請求項 14】

請求項 11 または請求項 13 記載のシフトレジスタ回路であって、

前記第 1 ノードと前記出力端子との間に接続する容量素子をさらに備える

ことを特徴とするシフトレジスタ回路。

【請求項 15】

請求項 11 から請求項 14 のいずれか記載のシフトレジスタ回路が複数個従属接続して成るシフトレジスタ回路。

【請求項 16】

請求項 15 記載のシフトレジスタ回路をゲート線駆動回路とする画像表示装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、シフトレジスタ回路に関するものであり、特に、例えば画像表示装置の走査

50

線駆動回路などに使用される、同一導電型の電界効果トランジスタのみにより構成されるシフトレジスタ回路に関するものである。

【背景技術】

【0002】

液晶表示装置等の画像表示装置（以下「表示装置」）では、複数の画素が行列状に配列された表示パネルの画素行（画素ライン）ごとにゲート線（走査線）が設けられ、表示信号の1水平期間の周期でそのゲート線を順次選択して駆動することにより表示画像の更新が行なわれる。そのように画素ラインすなわちゲート線を順次選択して駆動するためのゲート線駆動回路（走査線駆動回路）としては、表示信号の1フレーム期間で一巡するシフト動作を行なうシフトレジスタを用いることができる。

10

【0003】

ゲート線駆動回路に使用されるシフトレジスタは、表示装置の製造プロセスにおける工程数を少なくするために、同一導電型の電界効果トランジスタのみで構成されることが望ましい。このため、N型またはP型の電界効果トランジスタのみで構成されたシフトレジスタおよびそれを搭載する表示装置が種々提案されている（例えば特許文献1，2）。電界効果トランジスタとしては、MOS（Metal Oxide Semiconductor）トランジスタや薄膜トランジスタ（TFT：Thin Film Transistor）などが用いられる。

20

【0004】

【特許文献1】特開2004-246358号公報

【特許文献2】特開2001-350438号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

例えば特許文献1の図1に代表されるシフトレジスタ回路は、その出力段に、出力端子（特許文献1における第1ゲート電圧信号端子GOUT）とクロック端子（第1パワークロックCKV）との間に接続する第1トランジスタ（プルアップ用MOSトランジスタQ1）と、出力端子と基準電圧端子（ゲートオフ電圧端子VOFF）との間に接続する第2トランジスタ（プルダウンMOSトランジスタQ2）とを備えている。また、第1トランジスタのゲートのレベルを反転して、第2トランジスタのゲートに出力するインバータ（トランジスタQ6，Q7）を備えている。

30

【0006】

そのようなシフトレジスタ回路では、所定の入力信号（前段の出力信号GOUT[N-1]）によって第1トランジスタがオン、第2トランジスタがオフにされ、その状態でクロック端子に入力されるクロック信号が出力端子に伝達されることによって、出力信号が出力される。逆に、上記入力信号が入力されない期間は、第1トランジスタがオフ、第2トランジスタがオンにされ、クロック信号が出力端子に伝達されないようになる。

【0007】

TFTなどの電界効果トランジスタは、ゲートとドレインとの間にドレイン・ゲート・オーバラップ容量（以下、単に「オーバラップ容量」と称す）を有している。そのため、上記の第1トランジスタがオフの期間であってもドレインに入力されるクロック信号の立ち上がり時に、オーバラップ容量による結合を介して第1トランジスタのゲートのレベルが上昇する場合がある。第1トランジスタのゲートのレベルが上昇すると、インバータの働きにより第2トランジスタのゲートのレベルが下がる。その結果、第1トランジスタの抵抗値が下がり、第2トランジスタの抵抗値が上がる。それによって出力端子のレベルが上昇し、それに接続するゲート線が不要に活性化されてしまうという誤動作が生じることがある。

40

【0008】

また、ゲート線駆動回路のシフトレジスタを非晶質シリコンTFT（a-Si TFT）で構成した表示装置は、大面積化が容易で且つ生産性が高く、例えばノート型PCの画面や、大画面ディスプレイ装置などに広く採用されている。

50

## 【0009】

その反面、a-Si TFTはゲート電極が継続的(直流的)に正バイアスされた場合に、しきい値電圧が正方向にシフトして駆動能力が小さくなる傾向がある。特にゲート線駆動回路のシフトレジスタでは、第2トランジスタのゲートが約1フレーム期間(約16ms)もの間、継続的に正バイアスされるため、第2トランジスタの駆動能力が低下して上記の誤動作が生じやすくなる(詳細は後述する)。

## 【0010】

本発明は上記の課題を解決するためのものであり、シフトレジスタ回路の誤動作を防止し、動作信頼性を向上させることを目的とする。

## 【課題を解決するための手段】

## 【0011】

本発明の第1の局面としてのシフトレジスタ回路は、クロック端子および出力端子と、前記出力端子と前記クロック端子との間に接続する第1トランジスタと、前記出力端子を放電する第2トランジスタと、前記第1トランジスタの制御電極が接続するノードである第1ノードを入力端とし、前記第2トランジスタの制御電極が接続するノードである第2ノードを出力端とする第1プルダウン駆動回路とを備え、前記第1プルダウン駆動回路は、前記第2ノードと第1電源端子との間に直列接続した第3および第4トランジスタと、前記第2ノードと第2ノードと第2電源端子との間に接続した第5トランジスタと、前記第2ノードの電位で制御されて、前記第3トランジスタと前記第4トランジスタとの接続ノードである第3ノードに帰還電流を流す第6トランジスタとを備えるものである。

## 【0012】

本発明の第2の局面としてのシフトレジスタ回路は、クロック端子および出力端子と、前記出力端子と前記クロック端子との間に接続する第1トランジスタと、前記出力端子を放電する第2トランジスタと、前記第1トランジスタの制御電極が接続するノードである第1ノードを充電するタイミングを規定する信号が入力される入力端子と、前記入力端子を入力端とし前記第2トランジスタの制御電極が接続するノードである第2ノードを出力端とするプルダウン駆動回路とを備え、前記プルダウン駆動回路は、前記第2ノードと第1電源端子との間に直列接続した第3および第4トランジスタと、前記第2ノードと第2電源端子との間に接続した第5トランジスタと、前記第2ノードの電位で制御されて、前記第3トランジスタと第4トランジスタとの接続ノードである第3ノードに帰還電流を流す第6トランジスタとを備えるものである。

## 【発明の効果】

## 【0013】

本発明の第1の局面に係るシフトレジスタ回路によれば、当該シフトレジスタ回路が備える第1プルダウン駆動回路は、従来のインバータと比較してしきい値電圧が高い。よって、第1ノードがLレベルであるリセット状態に当該レベルがある程度変動したとしても、第2ノードのレベル低下が生じ難い。よって、第1トランジスタがオフの期間に、そのオーバラップ容量に起因するノイズが第1ノードに生じても第2ノードのレベル低下は防止される。従って、リセット状態における第1ノードのノイズによる誤動作の問題を解決することができる。

## 【0014】

本発明の第2の局面に係るシフトレジスタ回路によれば、当該シフトレジスタ回路が備えるプルダウン駆動回路は従来のインバータと比較してしきい値電圧が高く、入力端子がLレベルのときにそれに加わるノイズの影響を受けにくい。そのため、シフトレジスタ回路のリセット状態に入力端子に加わるノイズに起因して、第2ノードのレベルが低下することが防止される。よって、入力端子に加わるノイズによる誤動作を防止することができる。

## 【発明を実施するための最良の形態】

## 【0015】

以下、本発明の実施の形態を図面を参照しながら説明する。なお、説明が重複して冗長

10

20

30

40

50

になるのを避けるため、各図において同一または相当する機能を有する要素には同一符号を付してある。

【0016】

<実施の形態1>

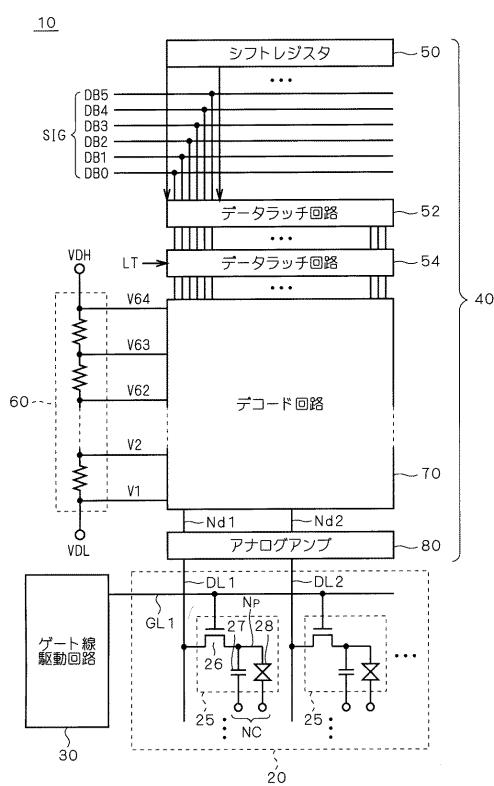

図1は、本発明の実施の形態1に係る表示装置の構成を示す概略ブロック図であり、表示装置の代表例として液晶表示装置10の全体構成を示している。

【0017】

液晶表示装置10は、液晶アレイ部20と、ゲート線駆動回路(走査線駆動回路)30と、ソースドライバ40とを備える。後の説明により明らかになるが、本発明の実施の形態に係るシフトレジスタは、ゲート線駆動回路30に搭載される。

10

【0018】

液晶アレイ部20は、行列状に配設された複数の画素25を含む。画素の行(以下「画素ライン」とも称する)の各々にはそれぞれゲート線GL1, GL2... (総称「ゲート線GL」)が配設され、また、画素の列(以下「画素列」とも称する)の各々にはそれぞれデータ線DL1, DL2... (総称「データ線DL」)がそれぞれ設けられる。図1には、第1行の第1列および第2列の画素25、並びにこれに対応するゲート線GL1およびデータ線DL1, DL2が代表的に示されている。

【0019】

各画素25は、対応するデータ線DLと画素ノードNpとの間に設けられる画素スイッチ素子26と、画素ノードNpおよび共通電極ノードNCの間に並列に接続されるキャパシタ27および液晶表示素子28とを有している。画素ノードNpと共通電極ノードNCとの間の電圧差に応じて、液晶表示素子28中の液晶の配向性が変化し、これに応答して液晶表示素子28の表示輝度が変化する。これにより、データ線DLおよび画素スイッチ素子26を介して画素ノードNpへ伝達される表示電圧によって、各画素の輝度をコントロールすることが可能となる。即ち、最大輝度に対応する電圧差と最小輝度に対応する電圧差との間の中間的な電圧差を、画素ノードNpと共通電極ノードNCとの間に印加することによって、中間的な輝度を得ることができる。従って、上記表示電圧を段階的に設定することにより、階調的な輝度を得ることが可能となる。

20

【0020】

ゲート線駆動回路30は、所定の走査周期に基づき、ゲート線GLを順に選択して駆動する。画素スイッチ素子26のゲート電極は、それぞれ対応するゲート線GLと接続される。特定のゲート線GLが選択されている間は、それに接続する各画素において、画素スイッチ素子26が導通状態になり画素ノードNpが対応するデータ線DLと接続される。そして、画素ノードNpへ伝達された表示電圧がキャパシタ27によって保持される。一般的に、画素スイッチ素子26は、液晶表示素子28と同一の絶縁体基板(ガラス基板、樹脂基板等)上に形成されるTFTで構成される。

30

【0021】

ソースドライバ40は、Nビットのデジタル信号である表示信号SIGによって段階的に設定される表示電圧を、データ線DLへ出力するためのものである。ここでは一例として、表示信号SIGは6ビットの信号であり、表示信号ビットDB0～DB5から構成されるものとする。6ビットの表示信号SIGに基づくと、各画素において、 $2^6 = 64$ 段階の階調表示が可能となる。さらに、R(Red)、G(Green)およびB(Blue)の3つの画素により1つのカラー表示単位を形成すれば、約26万色のカラー表示が可能となる。

40

【0022】

また、図1に示すように、ソースドライバ40は、シフトレジスタ50と、データラッチ回路52, 54と、階調電圧生成回路60と、デコード回路70と、アナログアンプ80とから構成されている。

【0023】

表示信号SIGにおいては、各々の画素25の表示輝度に対応する表示信号ビットDB0～DB5がシリアルに生成される。すなわち、各タイミングにおける表示信号ビットD

50

B 0 ~ D B 5 は、液晶アレイ部 2 0 中のいずれか 1 つの画素 2 5 における表示輝度を示している。

【 0 0 2 4 】

シフトレジスタ 5 0 は、表示信号 S I G の設定が切換わる周期に同期したタイミングで、データラッチ回路 5 2 に対して、表示信号ビット D B 0 ~ D B 5 の取込を指示する。データラッチ回路 5 2 は、シリアルに生成される表示信号 S I G を順に取り込み、1 つの画素ライン分の表示信号 S I G を保持する。

【 0 0 2 5 】

データラッチ回路 5 4 に入力されるラッチ信号 L T は、データラッチ回路 5 2 に1 つの画素ライン分の表示信号 S I G が取込まれるタイミングで活性化する。データラッチ回路 5 4 はそれに応答して、そのときデータラッチ回路 5 2 に保持されている1 つの画素ライン分の表示信号 S I G を取り込む。

【 0 0 2 6 】

階調電圧生成回路 6 0 は、高電圧 V D H および低電圧 V D L の間に直列に接続された6 3 個の分圧抵抗で構成され、6 4 段階の階調電圧 V 1 ~ V 6 4 をそれぞれ生成する。

【 0 0 2 7 】

デコード回路 7 0 は、データラッチ回路 5 4 に保持されている表示信号 S I G をデコードし、当該デコード結果に基づいて各デコード出力ノード N d 1 , N d 2 . . . ( 総称「デコード出力ノード N d 」) に出力する電圧を、階調電圧 V 1 ~ V 6 4 のうちから選択して出力する。

【 0 0 2 8 】

その結果、デコード出力ノード N d には、データラッチ回路 5 4 に保持された1 つの画素ライン分の表示信号 S I G に対応した表示電圧 ( 階調電圧 V 1 ~ V 6 4 のうちの1 つ ) が同時に ( パラレルに ) 出力される。なお、図 1 においては、第1列目および第2列目のデータ線 D L 1 , D L 2 に対応するデコード出力ノード N d 1 , N d 2 が代表的に示されている。

【 0 0 2 9 】

アナログアンプ 8 0 は、デコード回路 7 0 からデコード出力ノード N d 1 , N d 2 . . . に出力された各表示電圧に対応したアナログ電圧を、それぞれデータ線 D L 1 , D L 2 . . . に出力する。

【 0 0 3 0 】

ソースドライバ 4 0 が、所定の走査周期に基づいて、一連の表示信号 S I G に対応する表示電圧を1 画素ライン分ずつデータ線 D L へ繰返し出力し、ゲート線駆動回路 3 0 がその走査周期に同期してゲート線 G L 1 , G L 2 . . . を順に駆動することにより、液晶アレイ部 2 0 に表示信号 S I G に基づいた画像の表示が成される。

【 0 0 3 1 】

なお、図 1 には、ゲート線駆動回路 3 0 およびソースドライバ 4 0 が液晶アレイ部 2 0 と一体的に形成された液晶表示装置 1 0 の構成を例示したが、ゲート線駆動回路 3 0 およびソースドライバ 4 0 については、液晶アレイ部 2 0 の外部回路として設けることも可能である。

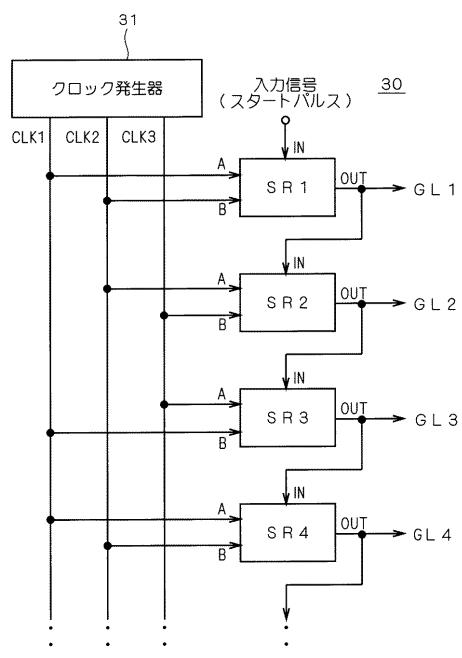

【 0 0 3 2 】

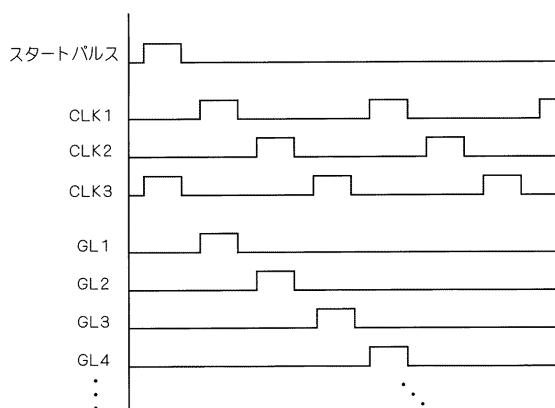

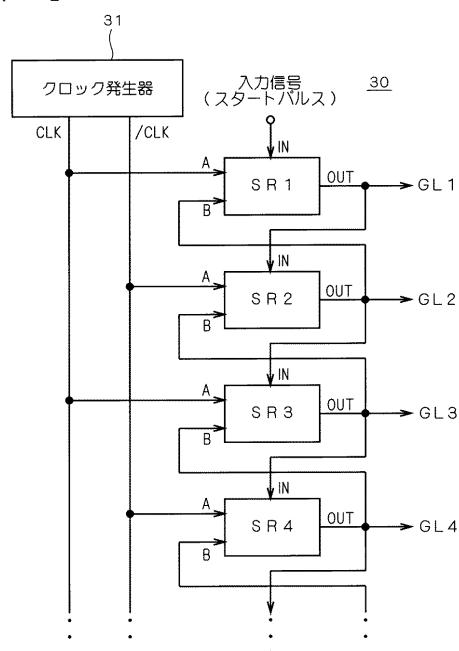

図 2 は、ゲート線駆動回路 3 0 の構成を示す図である。このゲート線駆動回路 3 0 は、縦続接続 ( カスケード接続 ) した複数のシフトレジスタ回路 S R 1 , S R 2 , S R 3 , S R 4 . . . で構成されるシフトレジスタから成っている ( 説明の便宜上、縦続接続するシフトレジスタ回路 S R 1 , S R 2 . . . の各々を「単位シフトレジスタ回路」と称することとし、これらを「単位シフトレジスタ回路 S R 」と総称する ) 。各単位シフトレジスタ回路 S R は、1 つの画素ラインすなわち 1 つのゲート線 G L ごとに設けられる。

【 0 0 3 3 】

また図 2 に示すクロック発生器 3 1 は、各々位相が異なる3 相のクロック信号 C L K 1 , C L K 2 , C L K 3 をゲート線駆動回路 3 0 の単位シフトレジスタ回路 S R に入力する

10

20

30

40

50

ものであり、このクロック信号 CLK1, CLK2, CLK3 は、表示装置の走査周期に同期したタイミングで順番に活性化するよう制御されている。

【0034】

各単位シフトレジスタ回路 SR は、入力端子 IN、出力端子 OUT、第 1 および第 2 クロック端子 A, B を有している。図 2 のように、各単位シフトレジスタ回路 SR のクロック端子 A, B には、クロック発生器 31 が output するクロック信号 CLK1, CLK2, CLK3 のうちの 2 つが供給される。単位シフトレジスタ回路 SR の出力端子 OUT には、それぞれゲート線 GL が接続する。また、第 1 段目（第 1 ステージ）の単位シフトレジスタ回路 SR1 の入力端子 IN には、画像信号の各フレーム期間の先頭に対応するスタートパルスが入力信号として入力され、第 2 段以降の単位シフトレジスタ回路 SR の入力端子 IN には、その前段の出力端子 OUT に出力される出力信号が、入力信号として入力される。各単位シフトレジスタ回路 SR の出力信号は、水平（又は垂直）走査パルスとしてゲート線 GL へと出力される。

【0035】

この構成のゲート線駆動回路 30 によれば、各単位シフトレジスタ回路 SR は、クロック信号 CLK1, CLK2, CLK3 に同期して、前段から入力される入力信号（前段の出力信号）をシフトさせながら、対応するゲート線 GL 並びに自身の次段の単位シフトレジスタ回路 SR へと出力する（単位シフトレジスタ回路 SR の動作の詳細は後述する）。その結果、一連の単位シフトレジスタ回路 SR は、所定の走査周期に基づいたタイミングでゲート線 GL を順に活性化させる、いわゆるゲート線駆動ユニットとして機能する。

【0036】

ここで、本発明の説明を容易にするために従来の単位シフトレジスタについて説明する。図 3 は、従来の単位シフトレジスタ回路 SR の構成を示す回路図である。なおゲート線駆動回路 30 においては、縦続接続された各単位シフトレジスタ回路 SR の構成は実質的にどれも同じであるので、以下では 1 つの単位シフトレジスタ回路 SR の構成についてのみ代表的に説明する。また、この単位シフトレジスタ回路 SR を構成するトランジスタは、全て同一導電型の電界効果トランジスタであるが、本実施の形態においては全て N 型 TFT であるものとする。

【0037】

図 3 の如く、従来の単位シフトレジスタ回路 SR は、図 2 で示した入力端子 IN、出力端子 OUT、第 1 クロック端子 A および第 2 クロック端子 B の他に、低電位側電源電位 VSS が供給される第 1 電源端子 s1、高電位側電源電位 VDD1, VDD2 がそれぞれ供給される第 2 電源端子 s2 および第 3 電源端子 s3 を有している。高電位側電源電位 VDD1, VDD2 は、互いに同一レベルであってもよい。そのようにする場合には、第 2 電源端子 s2 と第 3 電源端子 s3 を同一の端子で構成してもよい。以下の説明では、低電位側電源電位 VSS が回路の基準電位となるが、実使用では画素に書込まれるデータの電圧を基準にして基準電位が設定され、例えば高電位側電源電位 VDD1, VDD2 は 1.7V、低電位側電源電位 VSS は -1.2V などと設定される。

【0038】

単位シフトレジスタ回路 SR の出力段は、出力端子 OUT と第 1 クロック端子 A との間に接続するトランジスタ Q1（第 1 トランジスタ）と、出力端子 OUT と第 1 電源端子 s1 との間に接続するトランジスタ Q2（第 2 トランジスタ）とにより構成されている。以下、単位シフトレジスタ回路 SR の出力段を構成するトランジスタ Q1 のゲート（制御電極）が接続するノードをノード N1（第 1 ノード）、トランジスタ Q2 のゲートノードをノード N2（第 2 ノード）と定義する。

【0039】

トランジスタ Q1 のゲート・ソース間（即ち出力端子 OUT とノード N1 との間）には昇圧容量 C が設けられている。またノード N1 と第 2 電源端子 s2 との間にはトランジスタ Q3 が接続しており、そのゲートは入力端子 IN に接続している。ノード N1 と第 1 電源端子 s1 との間には、トランジスタ Q4 並びにトランジスタ Q5 が接続する。トランジ

10

20

30

40

50

スタQ 4 のゲートは第2クロック端子Bに接続し、トランジスタQ 5 のゲートはノードN 2 に接続する。ノードN 2 と第3電源端子S 3との間には、ダイオード接続されたトランジスタQ 6 が接続し、ノードN 2 と第1電源端子S 1との間にはトランジスタQ 7 が接続する。トランジスタQ 7 のゲートはノードN 1 に接続する。

【0040】

トランジスタQ 7 はトランジスタQ 6 よりも駆動能力（電流を流す能力）が十分大きく設定されている。即ち、トランジスタQ 7 のオン抵抗はトランジスタQ 6 のオン抵抗よりも小さい。よって、トランジスタQ 7 のゲート電位が上昇するとノードN 2 の電位は下降し、トランジスタQ 7 のゲート電位が下降するとノードN 2 の電位は上昇する。即ちトランジスタQ 6 およびトランジスタQ 7 は、ノードN 1 を入力端としノードN 2 を出力端とするインバータを構成している。当該インバータは、トランジスタQ 6 およびトランジスタQ 7 のオン抵抗値の比によってその動作が規定される「レシオ型インバータ」である。当該インバータは、出力端子OUTをプルダウンさせるためにトランジスタQ 2 を駆動する「プルダウン駆動回路」として機能している。

【0041】

図3の単位シフトレジスタ回路SRの具体的な動作を説明する。ゲート線駆動回路30を構成する各単位シフトレジスタ回路SRの動作は実質的にどれも同じであるので、1つの単位シフトレジスタ回路SRの動作を代表的に説明する。簡単のため、当該単位シフトレジスタ回路SRの第1クロック端子Aにクロック信号CLK1が入力され、第2クロック端子Bにクロック信号CLK3が入力されるものとして説明を行う（例えば図2における、単位シフトレジスタ回路SR1, SR4などがこれに該当する）。また、当該単位シフトレジスタ回路SRが出力端子OUTに出力する出力信号をGn、その前段の単位シフトレジスタ回路SRの出力信号をGn-1と定義する。

【0042】

まず初期状態として、ノードN 1 がL（Low）レベル（VSS）、ノードN 2 がH（High）レベル（VDD2 - Vth（Vth：トランジスタのしきい値電圧））であると仮定する（以下、この状態を「リセット状態」と称す）。また、第1クロック端子A（クロック信号CLK1）、第2クロック端子B（クロック信号CLK3）、入力端子IN（前段の出力信号Gn-1）は何れもLレベルであるとする。リセット状態では、トランジスタQ 1 がオフ（遮断状態）、トランジスタQ 2 がオン（導通状態）であるので、第1クロック端子A（クロック信号CLK1）のレベルに関係なく、出力端子OUT（出力信号Gn）はLレベルに保たれる。即ち、この単位シフトレジスタ回路SRが接続するゲート線は非選択状態にある。

【0043】

その状態から、前段の単位シフトレジスタ回路SRの出力信号Gn-1がHレベルになると、それが当該単位シフトレジスタ回路SRの入力端子INに入力されトランジスタQ 3 がオンになる。このときノードN 2 はLレベルなのでトランジスタQ 5 もオンしているが、トランジスタQ 3 はトランジスタQ 5 よりも駆動能力が十分大きく設定されており、トランジスタQ 3 のオン抵抗はトランジスタQ 5 のオン抵抗に比べ十分低いため、ノードN 1 のレベルは上昇する。

【0044】

それによりトランジスタQ 7 が導通し始めノードN 2 のレベルは下降する。そうなるとトランジスタQ 5 の抵抗が高くなり、ノードN 1 のレベルが急速に上昇してトランジスタQ 7 を充分にオンにする。その結果ノードN 2 はLレベル（VSS）になり、トランジスタQ 5 がオフになってノードN 1 がHレベル（VDD1 - Vth）になる。このようにノードN 1 がHレベル、ノードN 2 がLレベルの状態（以下、この状態を「セット状態」と称す）では、トランジスタQ 1 がオン、トランジスタQ 2 がオフになる。なお、前段の出力信号Gn-1がLレベルに戻ってトランジスタQ 3 がオフしても、ノードN 1 はフローティング状態になるのでこのセット状態はその後も維持される。

【0045】

10

20

30

40

50

セット状態では、トランジスタ Q 1 がオン、トランジスタ Q 2 がオフであるので、第 1 クロック端子 A のクロック信号 C L K 1 が H レベルになると、出力端子 O U T のレベルが上昇する。このとき昇圧容量 C およびトランジスタ Q 1 のゲート・チャネル間容量（ゲート容量）による結合により、ノード N 1 のレベルは特定の電圧（以下「昇圧量 V」）だけ昇圧される。そのため出力端子 O U T のレベルが上昇してもトランジスタ Q 1 のゲート・ソース間電圧はしきい値電圧（V<sub>t h</sub>）よりも大きく保たれ、当該トランジスタ Q 1 は低インピーダンスを維持する。従って、出力信号 G<sub>n</sub> のレベルは第 1 クロック端子 A のレベルに追随して変化する。特に、トランジスタ Q 1 のゲート・ソース間電圧が充分大きい場合トランジスタ Q 1 は非飽和動作するので、しきい値電圧分の損失はなく出力端子 O U T はクロック信号 C L K 1 と同レベルになる。よって、第 1 クロック端子 A に入力されるクロック信号 C L K 1 が H レベルの間は、出力信号 G<sub>n</sub> も H レベルになってゲート線の選択状態になる。その後、クロック信号 C L K 1 が L レベルに戻ると出力信号 G<sub>n</sub> も L レベルになってゲート線の非選択状態に戻る。

#### 【 0 0 4 6 】

その後、第 2 クロック端子 B のクロック信号 C L K 3 が H レベルになると、トランジスタ Q 4 がオンになるためノード N 1 が L レベルになり、それに伴ってトランジスタ Q 7 がオフになるためノード N 2 は H レベルになる。即ち、トランジスタ Q 1 がオフ、トランジスタ Q 2 がオンのリセット状態に戻る。

#### 【 0 0 4 7 】

以上の動作をまとめると、単位シフトレジスタ回路 S R においては、入力端子 I N に信号（スタートパルスまたは前段の出力信号 G<sub>n-1</sub>）が入力されない間はリセット状態にあり、その間ノード N 2 が H レベル（V<sub>D D 2</sub> - V<sub>t h</sub>）に保たれることで、出力端子 O U T（ゲート線）は低インピーダンスの L レベル（V<sub>S S</sub>）に維持される。そして入力端子 I N に信号が入力されると、そのタイミングでノード N 2 が L レベル（V<sub>S S</sub>）になると共にノード N 1 が H レベル（V<sub>D D 1</sub> - V<sub>t h</sub>）に充電されてセット状態になる。即ち、単位シフトレジスタ回路 S R では、入力端子 I N に入力される信号により、セット状態になるタイミングが規定される。

#### 【 0 0 4 8 】

セット状態では第 1 クロック端子 A の信号（クロック信号 C L K 1）が H レベルになるとノード N 1 の電位が昇圧量 V だけ高くなり、第 1 クロック端子 A が H レベルである間、出力端子 O U T が H レベルになってゲート線を活性化する（このためノード N 1 は「昇圧ノード」と称されることもある）。その後第 2 クロック端子 B に信号（クロック信号 C L K 3）が入力されると、ノード N 1 が L レベル（V<sub>S S</sub>）、ノード N 2 が H レベル（V<sub>D D 2</sub> - V<sub>t h</sub>）に戻って、元のリセット状態になる（このためノード N 2 は「リセットノード」と称されることもある）。即ち、単位シフトレジスタ回路 S R では、第 2 クロック端子 B に入力される信号により、セット状態になるタイミングが規定される。

#### 【 0 0 4 9 】

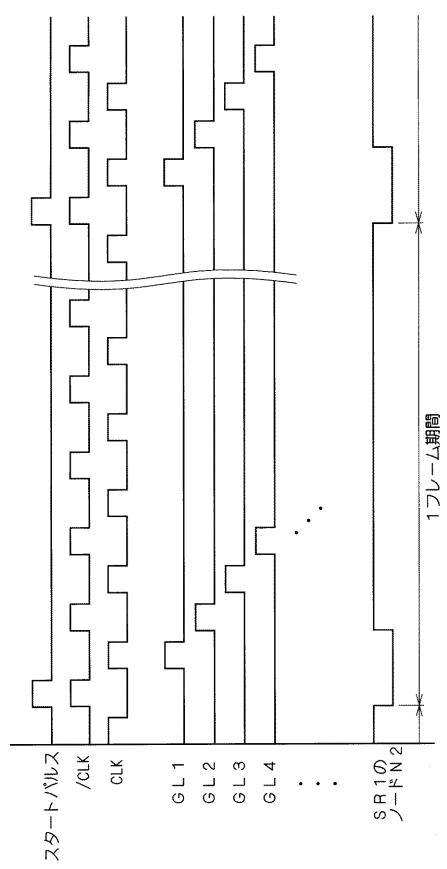

そのように動作する複数の単位シフトレジスタ回路 S R を図 2 のように縦続接続し、ゲート線駆動回路 3 0 を構成すると、第 1 段目の単位シフトレジスタ回路 S R 1 の入力端子 I N に入力された入力信号（スタートパルス）は、図 4 に示すタイミング図のように、クロック信号 C L K 1, C L K 2, C L K 3 に同期したタイミングでシフトされながら、単位シフトレジスタ回路 S R 2, S R 3, … と順番に伝達される。それによって、ゲート線駆動回路 3 0 は、所定の走査周期でゲート線 G L 1, G L 2, G L 3, … を順に駆動することができる。

#### 【 0 0 5 0 】

上の例では、複数の単位シフトレジスタ回路 S R が 3 相クロックに基づいて動作する例を示したが、2 相クロック信号を使用して動作させることも可能である。図 5 はその場合におけるゲート線駆動回路 3 0 の構成を示す図である。

#### 【 0 0 5 1 】

この場合も、ゲート線駆動回路 3 0 は、縦続接続した複数の単位シフトレジスタ回路 S

10

20

30

40

50

R により構成される。即ち、各単位シフトレジスタ回路 S R の入力端子 I N には、その前段の単位シフトレジスタ回路 S R の出力端子 O U T が接続する。但し、第 1 段目の単位シフトレジスタ回路 S R の入力端子 I N には、スタートパルスが入力信号として入力される。

#### 【 0 0 5 2 】

この場合におけるクロック発生器 3 1 は、互いに逆相の 2 相クロックであるクロック信号 C L K , / C L K を出力するものである。それぞれの単位シフトレジスタ回路 S R の第 1 クロック端子 A には、隣接する単位シフトレジスタ回路 S R に互いに逆相のクロック信号が入力されるよう、そのクロック信号 C L K , / C L K の片方が入力される。また図 5 に示すように、各単位シフトレジスタ回路 S R の第 2 クロック端子 B には、その後段（この例では次段）の単位シフトレジスタ回路 S R の出力端子 O U T が接続される。

#### 【 0 0 5 3 】

図 5 のように構成されたゲート線駆動回路 3 0 における単位シフトレジスタ回路 S R の動作を説明する。ここでも、1 つの単位シフトレジスタ回路 S R の動作を代表的に説明する。簡単のため、単位シフトレジスタ回路 S R の第 1 クロック端子 A にクロック信号 C L K が入力されるものとして説明を行う（例えば、図 5 における単位シフトレジスタ回路 S R 1 , S R 3 などがこれに該当する）。また、当該単位シフトレジスタ回路 S R の出力信号を G<sub>n</sub> 、その前段および次段の単位シフトレジスタ回路 S R の出力信号をそれぞれ G<sub>n-1</sub> および G<sub>n+1</sub> と定義する。

#### 【 0 0 5 4 】

まず初期状態として、ノード N 1 が L レベル ( V S S ) 、ノード N 2 が H レベル ( V D D 2 - V t h ) のリセット状態を仮定する。また、第 1 クロック端子 A ( クロック信号 C L K ) 、第 2 クロック端子 B ( 次段の出力信号 G<sub>n+1</sub> ) 、入力端子 I N ( 前段の出力信号 G<sub>n-1</sub> ) は何れも L レベルであるとする。

#### 【 0 0 5 5 】

その状態から、前段の出力信号 G<sub>n-1</sub> が H レベルになると、それが当該単位シフトレジスタ回路 S R の入力端子 I N に入力されトランジスタ Q 3 がオンになり、ノード N 1 のレベルは上昇する。それによりトランジスタ Q 7 が導通し始め、ノード N 2 のレベルは下降する。そうなるとトランジスタ Q 5 の抵抗が高くなり、ノード N 1 のレベルが急速に上昇してトランジスタ Q 7 を充分にオンにする。その結果ノード N 2 は L レベル ( V S S ) になり、トランジスタ Q 5 がオフになってノード N 1 が H レベル ( V D D 1 - V t h ) になる。その結果、トランジスタ Q 1 がオン、トランジスタ Q 2 がオフとなるセット状態になる。

#### 【 0 0 5 6 】

そして、クロック信号 C L K が H レベルになり出力端子 O U T のレベルが上昇すると、昇圧容量 C およびトランジスタ Q 1 のゲート・チャネル間容量による結合によりノード N 1 のレベルは特定の電圧（昇圧量 V ）だけ昇圧される。従って、出力信号 G<sub>n</sub> のレベルは第 1 クロック端子 A のレベルに追随して変化し、クロック信号 C L K が H レベルである間は出力信号 G<sub>n</sub> も H レベルになる。その後、クロック信号 C L K が L レベルに戻ると出力信号 G<sub>n</sub> も L レベルに戻る。

#### 【 0 0 5 7 】

出力信号 G<sub>n</sub> が次段の単位シフトレジスタ回路 S R に伝達された後、次段の出力信号 G<sub>n+1</sub> が H レベルになると、それが第 2 クロック端子 B に入力されてトランジスタ Q 4 がオンになりノード N 1 が L レベルになる。それに伴ってトランジスタ Q 7 がオフになるのでノード N 2 は H レベルになる。即ち、当該単位シフトレジスタ回路 S R はリセット状態に戻り、トランジスタ Q 1 がオフ、トランジスタ Q 2 がオンになる。

#### 【 0 0 5 8 】

このように、ゲート線駆動回路 3 0 が図 5 のように構成されている場合においても、それぞれの単位シフトレジスタ回路 S R の動作は、第 2 クロック端子 B に入力される信号が次段の出力信号 G<sub>n+1</sub> であることを除けば図 2 の場合とほぼ同じである。

10

20

30

40

50

## 【0059】

以上の動作を、図5のように継続接続された単位シフトレジスタ回路SR1, SR2, ...が順に行う。それによって、第1段目の単位シフトレジスタ回路SR1の入力端子INに入力された入力信号(スタートパルス)が、クロック信号CLK, /CLKに同期してシフトされながら、単位シフトレジスタ回路SR2, SR3, ...と順番に伝達される。その結果、ゲート線駆動回路30は図6に示すタイミング図の如く、クロック信号CLK, /CLKに同期して、ゲート線GL1, GL2, GL3, ...を順に駆動することができる。

## 【0060】

但し、図5の構成では、各単位シフトレジスタ回路SRは、第2クロック端子Bに次段の単位シフトレジスタ回路SRの出力信号G<sub>n+1</sub>が入力されるので、次段の単位シフトレジスタ回路SRが少なくとも一度動作した後でなければリセット状態(すなわち上記の初期状態)にならない。各単位シフトレジスタ回路SRは、リセット状態を経なければ図6に示したような通常動作を行うことができない。従って図5の構成の場合には、通常動作に先立って、ダミーの入力信号を単位シフトレジスタ回路SRの第1段目から最終段まで伝達させるダミー動作を行わせる必要がある。あるいは、各単位シフトレジスタ回路SRのノードN2と第3電源端子s3(高電位側電源)との間にリセット用のトランジスタを別途設け、通常動作の前に強制的にノードN2を充電するリセット動作を行なってもよい。但し、その場合はリセット用の信号ラインが別途必要になる。

## 【0061】

ここで、先に述べた従来の単位シフトレジスタ回路SRにおける誤動作の問題を詳細に説明する。以下では、単位シフトレジスタ回路SRを構成する各トランジスタはa-Si TFTであるとする。

## 【0062】

図6の最下段に、図5のゲート線駆動回路30における単位シフトレジスタ回路SR1のノードN2の電圧波形を示す。上記のように、入力端子INの信号(スタートパルスあるいは前段の出力信号G<sub>n-1</sub>)がHレベルに成ると、ノードN2はLレベルに遷移するが、すぐに第2クロック端子Bの信号(次段の出力信号G<sub>n+1</sub>)によってHレベルに戻され、その後約1フレーム期間(約16ms)Hレベルに維持される(図示は省略するが、この振る舞いは図2のケースでも同様である)。つまり各単位シフトレジスタ回路SRにおける、トランジスタQ2およびトランジスタQ5のゲートは、約1フレーム期間継続的(直流的)に正バイアスされる。よって単位シフトレジスタ回路SRがa-Si TFTにより構成されている場合には、トランジスタQ2, Q5はしきい値電圧が正方向にシフトして駆動能力が低下する。

## 【0063】

単位シフトレジスタ回路SRがゲート線の非選択期間にあり、リセット状態(ノードN1がLレベル、ノードN2がHレベル)になっている場合を想定する。この状態ではトランジスタQ1はオフしているが、そのドレインが接続する第1クロック端子Aにはクロック信号CLKが繰り返し入力される。

## 【0064】

このときトランジスタQ1のドレインとゲートとの間のオーバラップ容量による結合により、クロック信号CLKの入力に伴ってノードN1の電圧が変動する。すなわちクロック信号CLKの立上り時にノードN1が充電され、その後トランジスタQ5を介して放電されという振る舞いが繰り返し行われる。従ってノードN1には、鋸歯状の繰り返し波形のノイズが生じる。当該ノイズによりトランジスタQ7がオンすると、ノードN2のレベルが下降してしまう。

## 【0065】

上記のように単位シフトレジスタ回路SRのトランジスタQ2, Q5のゲート・ソース間は直流的に正バイアスされるため、当該トランジスタQ2, Q5は駆動能力が時間と共に低下する。そのような状態でノードN2のレベルが低下すると、トランジスタQ5はノ

10

20

30

40

50

ードN1のノイズによる電荷を素早く放電することができず、ノードN1のレベルがさらに上昇する。応じてトランジスタQ1の抵抗値が下がるため、クロック信号CLKがHレベルになったときに出力端子OUTに電荷が供給されるようになる。またこのときトランジスタQ2の駆動能力も低下しているため、トランジスタQ2は出力端子OUTの電荷を素早く放電できず、出力端子OUTのレベルが上昇してしまう。つまり、非選択状態にあるべきゲート線が選択状態になってしまいうとい誤動作が生じ、液晶表示装置10の表示不具合が発生する。以下、この問題を解決可能な本発明に係るシフトレジスタ回路について説明する。

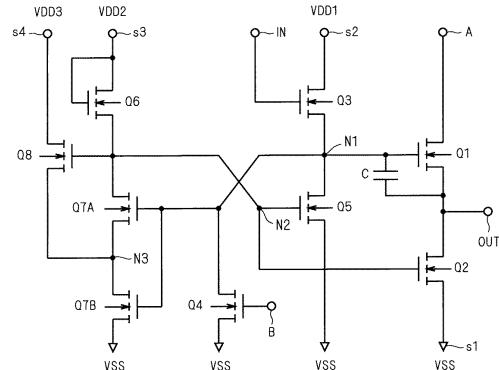

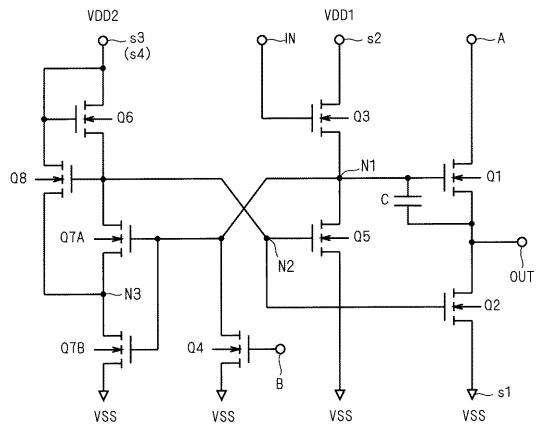

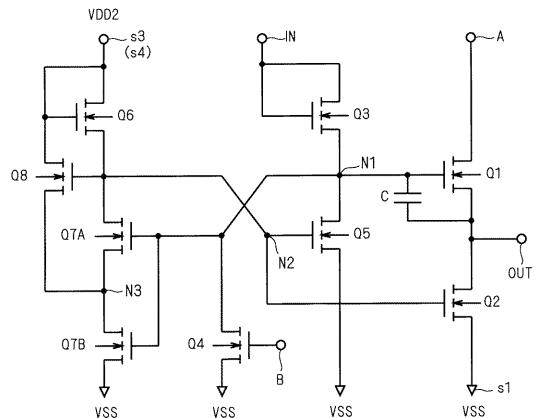

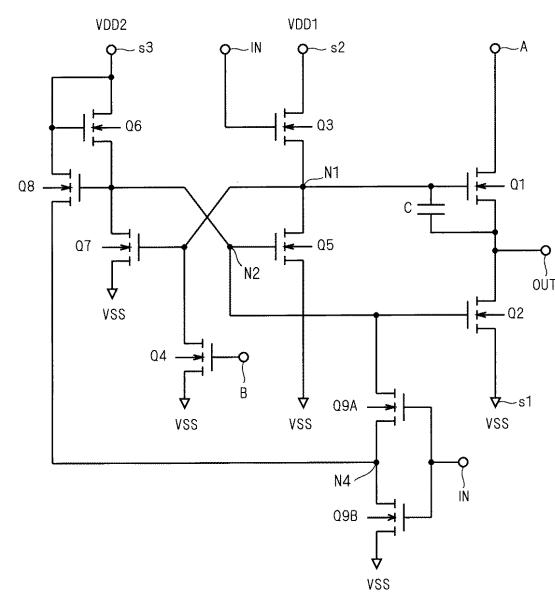

#### 【0066】

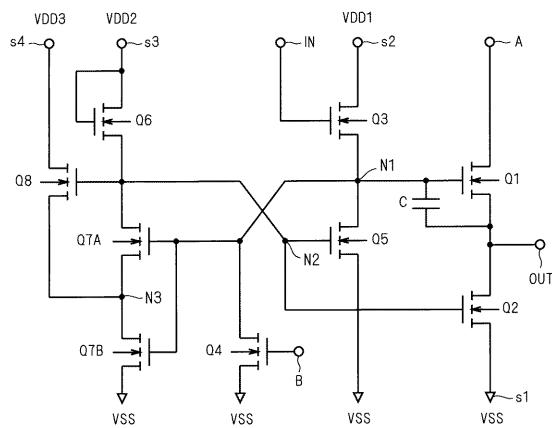

図7は、実施の形態1に係る単位シフトレジスタ回路SRの構成を示す回路図である。

同図のように、当該単位シフトレジスタ回路SRの出力段は、出力端子OUTと第1クロック端子Aとの間に接続するトランジスタQ1(第1トランジスタ)と、出力端子OUTと第1電源端子s1との間に接続するトランジスタQ2(第2トランジスタ)とにより構成されている。また、トランジスタQ1のゲート(制御電極)とソースとの間すなわちノードN1と出力端子OUTとの間には昇圧容量Cが設けられている。ノードN1と第2電源端子s2との間には、ゲートが入力端子INに接続するトランジスタQ3が接続しており、ノードN1と第1電源端子s1との間には、ゲートが第2クロック端子Bに接続するトランジスタQ4と、ゲートがノードN2に接続したトランジスタQ5とが接続している。以上の構成は図3に示した従来の単位シフトレジスタ回路SRと同様である。

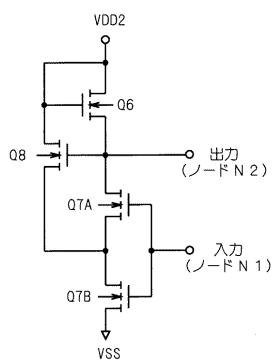

#### 【0067】

本実施の形態に係る単位シフトレジスタ回路SRも、ノードN1を入力端としノードN2を出力端とするインバータ(第1プルダウン駆動回路)を備えている。本実施の形態においては、当該インバータはトランジスタQ6, Q7A, Q7B, Q8により構成される。図7の如く、トランジスタQ6はダイオード接続されており、ノードN2と第3電源端子s3との間に接続している。トランジスタQ7A, Q7BはノードN2と第1電源端子s1との間に直列に接続し、それぞれのゲートはノードN1に接続している。またトランジスタQ7AとトランジスタQ7Bとの接続ノードをN3と定義すると、トランジスタQ8は当該ノードN3と高電位側電源電位VDD3が供給される第4電源端子s4との間に接続されており、そのゲートはノードN2に接続している。トランジスタQ8は、ノードN2の電位で制御されて、第4電源端子s4からノードN3へ帰還電流を流すよう機能する。以上のような構成のインバータは「シュミット・トリガ回路」と呼ばれることもある(例えは特開昭56-96525号公報参照)。

#### 【0068】

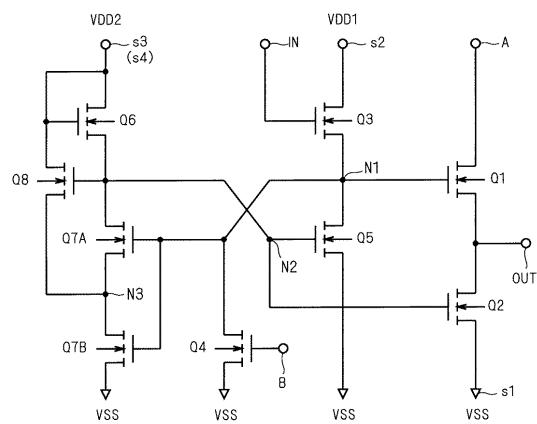

高電位側電源電位VDD3は、ノードN2がHレベルとなってトランジスタQ8がオンしたときにノードN3を所定のレベルに充電することが可能な電位であり、例えば高電位側電源電位VDD1, VDD2と同一レベルであってもよい。例えば高電位側電源電位VDD3を高電位側電源電位VDD2と同一レベルとする場合には、図8に示すが如く、第3電源端子s3と第4電源端子s4とを互いに接続し、両者を同一の端子で構成してもよい(即ち、第3電源端子s3を第4電源端子s4としても機能させる)。そのようにすることで、電源供給のための配線の占有面積は削減される。説明の簡単のため、以下においては図8の回路構成に基づいて説明を行う。

#### 【0069】

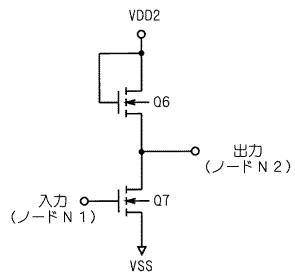

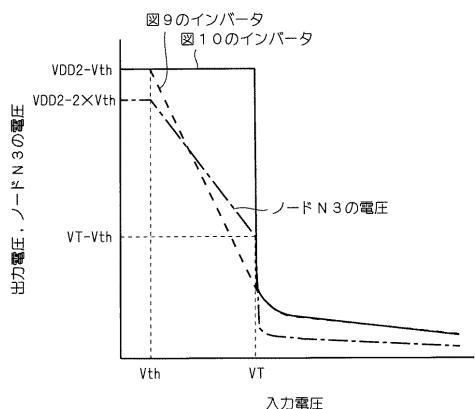

図3と図8とを比較して分かるように、従来の単位シフトレジスタ回路SRが備えるプルダウン駆動回路は図9に示すインバータであり、本実施の形態に係るプルダウン駆動回路は図10に示すインバータである。本実施の形態に係る単位シフトレジスタ回路SRは、このインバータの回路構成が従来のものと異なっているものの、論理的な動作は先に図4あるいは図6を用いて説明した従来のものと同様である。従って、本実施の形態に係る単位シフトレジスタ回路SRの動作についての説明は省略する。

#### 【0070】

図11は、図9および図10に示したインバータの入出力電圧特性を示すグラフである

10

20

30

40

50

。図11のように、図9のインバータでは入力電圧が駆動トランジスタQ7のしきい値電圧 $V_{th}$ を越えると当該トランジスタQ7が導通し始めて出力電圧が下降し始めるが、図10のインバータでは、従来のインバータに比べ出力レベルが下降を始める電圧(インバータのしきい値電圧=  $V_T$ )がそれよりも高い。

#### 【0071】

図10のインバータでは、入力電圧がLレベル、出力電圧がHレベルであるときはトランジスタQ8がオンになるので、トランジスタQ7Aのソース(ノードN3)は正バイアスされる。トランジスタQ7Aはゲートの電位がソースの電位よりもしきい値 $V_{th}$ 以上高くなれば導通しないので、図10のインバータを反転させるためには、入力電位(ノードN1の電位)がバイアスされたノードN3の電位よりもさらにしきい値電圧 $V_{th}$ 以上高くなる必要がある。従って上記のように、図10のインバータのしきい値電圧が、図9のインバータのそれよりも高いことになる。

10

#### 【0072】

図10のインバータの動作原理を説明する。まず、入力電圧がLレベルとあるとする。その状態では、トランジスタQ7A, Q7Bがオフであるので出力電圧はHレベル( $V_{DD2} - V_{th}$ )である。そのためトランジスタQ8はオンしており、ノードN3は $V_{DD2} - 2 \times V_{th}$ のレベルにバイアスされている。

#### 【0073】

そして入力レベルが上昇し始めトランジスタQ7Bのしきい値電圧( $V_{th}$ )を超えると、トランジスタQ7Aが導通し始めノードN3のレベルが低下するが、トランジスタQ7Aは入力レベルがノードN3の電位よりも $V_{th}$ 以上高くなれば導通しないので、それまではHレベルは維持される。そしてさらに入力電圧が上昇してついにノードN3の電位よりも $V_{th}$ 以上高くなると、トランジスタQ7Aが導通し始める。

20

#### 【0074】

すると当該インバータ内で、トランジスタQ7Aの駆動能力上昇 出力電圧のレベル低下 トランジスタQ8の駆動能力低下 ノードN3のレベル低下 トランジスタQ7Aの駆動能力上昇 ・・・という正帰還ループが構成され、図11のグラフのように急激に反転する。

20

#### 【0075】

また、入力電圧がHレベルの状態から下降するときは、入力電圧がインバータのしきい値電圧 $V_T$ にまで下がると、トランジスタQ7Aの駆動能力低下 出力電圧のレベル上昇 トランジスタQ8の駆動能力上昇 ノードN3のレベル上昇 トランジスタQ7Aの駆動能力低下 ・・・という上記と逆のループが構成されて、この場合にも急激に反転する。

30

#### 【0076】

以上のように、図10のインバータは、図9のインバータに比較してしきい値電圧が高い。よって図10のインバータがプルダウン駆動回路として用いられている本実施の形態に係る単位シフトレジスタ回路SRにおいては、ノードN1がLレベルであるリセット状態に当該レベルがある程度変動したとしても、ノードN2のレベル低下が生じ難い。よって、トランジスタQ1がオフの期間に、オーバラップ容量に起因するノイズがノードN1に生じてもノードN2のレベル低下は防止される。従って、リセット状態におけるノードN1のノイズによる誤動作の問題を解決することができる。その結果、本実施の形態に係る単位シフトレジスタ回路SRにより構成されたゲート線駆動回路を有する表示装置における表示不具合を防止できる。

40

#### 【0077】

特に、単位シフトレジスタ回路SRがa-Si TFTで構成されている場合には、ゲートがノードN2に接続したトランジスタQ2, Q5の駆動能力が低下して上記の誤動作の問題が生じやすくなるため、本発明の適用は効果的である。

#### 【0078】

<実施の形態2>

50

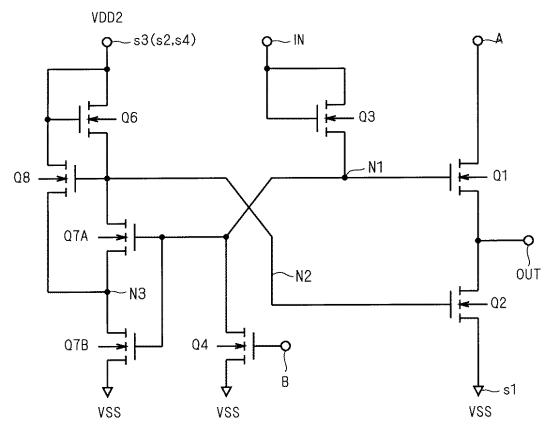

図12は、本発明の実施の形態2に係る単位シフトレジスタ回路SRの構成を示す回路図である。本実施の形態では、トランジスタQ3のドレインを電源ではなく入力端子INに接続させる。それにより電源供給のための配線の占有面積を削減できる。但し、入力端子INにはその前段の出力端子OUTが接続するため、各単位シフトレジスタ回路SRの出力段への負荷が大きくなるので、回路動作の速度が劣化する場合もあることに留意すべきである。

#### 【0079】

##### <実施の形態3>

TFTを含む電界効果トランジスタは、ゲートにしきい値電圧以上の電圧が印加されたときに、ゲート絶縁膜を介したゲート電極の直下に形成される導電性チャネルによりドレイン・ソース間が電気的に接続されることにより導通する素子である。従って、導通状態の電界効果トランジスタは、ゲートとチャネルを両電極とし、ゲート絶縁膜を誘電体層とする容量素子（ゲート容量）としても機能することができる。

#### 【0080】

図13は実施の形態3に係る単位シフトレジスタ回路SRの構成を示す回路図である。実施の形態1では、ノードN1の昇圧を効率よく行うためにトランジスタQ1のドレイン・ソース間に昇圧容量Cを設けていたが、本実施の形態ではそれをトランジスタQ1のゲート容量に置き換えている。その場合、図13の回路図の如く昇圧容量Cは不要になる。

#### 【0081】

通常、半導体集積回路内に形成される容量素子の誘電体層となる絶縁膜の厚さは、トランジスタのゲート絶縁膜の厚さと同じになるので、容量素子をトランジスタのゲート容量に置き換える場合には、その容量素子と同一面積のトランジスタで代替することができる。即ち、図13においてトランジスタQ1のゲート幅を相当分広くすることで、実施の形態1に係る図8の回路と同等の昇圧動作を実現できる。またトランジスタQ1のゲート幅を広くすることによりその駆動能力が高くなるので、結果として出力信号の立上りおよび立下り速度が速くなり、動作の高速化を図ることができるという利点もある。

#### 【0082】

##### <実施の形態4>

例えば図3に示した従来の単位シフトレジスタ回路SRにおいて、ノードN1と第1電源端子S1（低電位側電源電位VSS）との間には、トランジスタQ4, Q5の2つが接続している。そのうちトランジスタQ4は主に、HレベルにあるノードN1の電荷を放電してLレベルに遷移させる働きをしており、トランジスタQ5は主に、LレベルになったノードN1を低電位側電源電位VSSに固定する働きをしている。

#### 【0083】

仮に従来の単位シフトレジスタ回路SRからトランジスタQ5が省略されたとしても、Lレベルになった後のノードN1がフローティング状態になるだけであるので、理論的な動作は可能である。トランジスタQ5を省略すればそれだけ装置の縮小化を図ることができるという利点があるため、トランジスタQ5を有していない構造のレベルシフト回路も提案されている（上記の特許文献2）。

#### 【0084】

但し、トランジスタQ5はLレベルにあるノードN1のノイズの放電経路になるため、それが省略されるとトランジスタQ1のオーバラップ容量に起因するノイズの影響が大きくなり、それによる誤動作の問題が顕著になる。そこで本実施の形態では、本発明をトランジスタQ5を有しない構造の単位シフトレジスタ回路SRへ適用することによって、その問題を解決する。

#### 【0085】

図14は、実施の形態4に係る単位シフトレジスタ回路SRの構成を示す回路図である。同図の如く、当該単位シフトレジスタ回路SRは、図8の回路に対して、トランジスタQ5が省略された構造を有している。また実施の形態2が適用されており、トランジスタQ3のドレインを入力端子INに接続させ、電源供給のための配線の占有面積を削減を図

10

20

30

40

50

っている。さらに実施の形態3が適用されており、昇圧容量Cも省略されている。

【0086】

上記のようにトランジスタQ5はLレベルにあるノードN1のノイズの放電経路であったため、図14のようにそれを有さない単位シフトレジスタ回路SRでは、トランジスタQ1のオーバラップ容量に起因するノイズにより、リセット状態でのノードN1のレベル変動が大きくなりやすい。しかし図14の単位シフトレジスタ回路SRでは、ノードN1を入力端としノードN2を出力端とするインバータ（プルダウン駆動回路）がトランジスタQ6, Q7A, Q7B, Q8によって図10のように構成されており、そのしきい値電圧が高い。従って当該インバータはリセット状態におけるノードN1のノイズの影響を受けにくく、当該ノイズによる誤動作は防止される。このように本発明はトランジスタQ5を有さない構造の単位シフトレジスタ回路SRに対して特に効果的である。

10

【0087】

また図14のように、トランジスタQ5を省略すると共に、実施の形態2を適用して電源配線を省略し、さらに実施の形態3を適用して昇圧容量Cを省略すれば、単位シフトレジスタ回路SRの形成面積をより小さくすることができ表示装置の小型化に効果的である。

【0088】

<実施の形態5>

例えば図3に示した従来の単位シフトレジスタ回路SRにおいて、入力端子INへの入力信号（スタートパルスまたは前段の出力信号G<sub>n-1</sub>）がHレベルになる直前はリセット状態であるのでトランジスタQ5はオン状態にある。

20

【0089】

従って先に述べたように、入力端子INがHレベルになり単位シフトレジスタ回路SRがリセット状態からセット状態へ移行する際には、次のような段階が踏まれる。即ち、入力端子INがHレベルになると、トランジスタQ3とトランジスタQ5のオン抵抗の比に応じてノードN1のレベルが上昇し、それによりトランジスタQ7が導通し始めノードN2のレベルを下降させる。それにより、トランジスタQ5の抵抗がさらに高くなつてノードN1のレベルがさらに上昇し、トランジスタQ7が充分にオンになつてノードN2がLレベル(VSS)になる。応じてトランジスタQ5がオフになるのでノードN1はHレベル(VDD1 - Vth)になる。その結果単位シフトレジスタ回路SRはセット状態になる。

30

【0090】

単位シフトレジスタ回路SRでは、リセット状態からセット状態へ切り替わる際に以上の動作を経るため、その切り替わりに比較的長い時間を要していた。そのことは単位シフトレジスタ回路SRの動作の高速化の妨げとなり、ひいては単位シフトレジスタ回路SRをゲート線駆動回路に用いた表示装置の高解像度化の妨げとなる。

40

【0091】

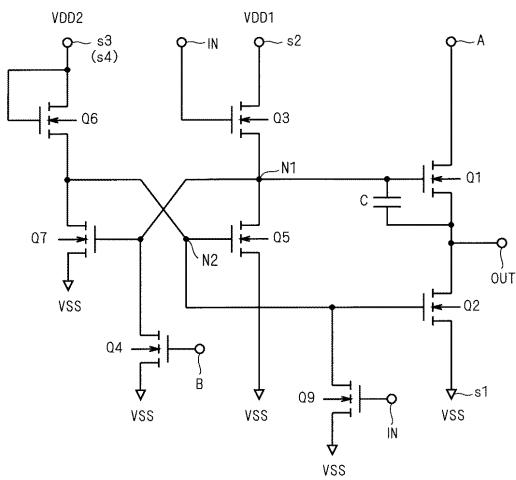

その対策としては、例えば図15に示すようにノードN2と第1電源端子S1（低電位側電源電位VSS）との間に、ゲートが入力端子INに接続したトランジスタQ9を設けることが考えられる。図15の回路によれば、入力端子INがHレベルになったときにトランジスタQ9がオンして、ノードN2を瞬時にLレベルなる。またそれに応じてトランジスタQ5がオフになるので、ノードN1のレベルは高速にHレベルになる。即ち、リセット状態からセット状態への切り替わりが瞬時に行われるため、単位シフトレジスタ回路SRの動作の高速化に寄与できる。

40

【0092】

しかし、図15の単位シフトレジスタ回路SRがゲート線駆動回路回路に用いられた場合には、次のような問題が生じる。即ち、ゲート線は多数のデータ線（図1のデータ線DL1, DL2, ..., ）と交叉しているため、データ線との間の寄生容量による結合によって、データ線へのデータの書き込み時、あるいは対向電極（図1の共通電極ノードNC）の極性反転時において、ゲート線にノイズが加わりやすい。単位シフトレジスタ回路SRが

50

リセット状態のときに、そのノイズがゲート線を介して入力端子INに加わると、トランジスタQ9に電流が流れノードN2のLレベルを低下させる。

【0093】

その結果、トランジスタQ2, Q5は駆動能力が低下するため、単位シフトレジスタ回路SRが、トランジスタQ1のオーバラップ容量に起因するノードN1のノイズの影響を受けやすくなり、実施の形態1で説明した従来のレベルシフト回路の誤動作と同様の問題が生じる。特に単位シフトレジスタ回路SRがa-Si TFTにより構成されている場合には、トランジスタQ2, Q5は駆動能力は時間と共にさらに低下するため、その問題は顕著になる。本実施の形態では、この問題を解決することが可能な単位シフトレジスタ回路SRを提案する。

10

【0094】

再び図15の回路を参照し、トランジスタQ6およびトランジスタQ9に着目すると、それらは入力端子INを入力端としノードN2を出力端とする、図9に示したインバータを構成している。入力端子INに加わるノイズにより、ノードN2のレベルが下がるという上記の問題は、このインバータがノイズに影響を受けやすいことが原因となっている。

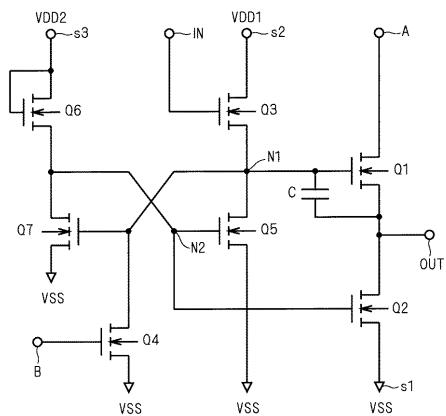

【0095】

図16は、実施の形態5に係る単位シフトレジスタ回路SRの構成を示す回路図である。同図の如く、当該単位シフトレジスタ回路SRは、ノードN2と第1電源端子s1との間に直列に接続し、共にゲートが入力端子INに接続したトランジスタQ9A, Q9Bを有している。またトランジスタQ9AとトランジスタQ9Bとの接続ノードをノードN4と定義すると、トランジスタQ8は当該ノードN4と第3電源端子s3との間に接続されており、そのゲートはノードN2に接続する。つまり本実施の形態のトランジスタQ8は、ノードN2の電位で制御されて、第3電源端子s3からノードN4へ帰還電流を流すよう機能する。従って、トランジスタQ6, Q8, Q9A, Q9Bによって、いわゆる「シミュット・トリガ回路」が構成されている。

20

【0096】

即ち、図16の単位シフトレジスタ回路SRは、トランジスタQ6, Q7から成り、ノードN1の入力端にしノードN2を出力端にする第1のインバータに加え、トランジスタQ6, Q8, Q9A, Q9Bから成り、入力端子INを入力端としノードN2を出力端とする第2のインバータとを備えている（トランジスタQ6は第1のインバータと第2のインバータとで共有されている）。この第2のインバータも、出力端子OUTをプルダウンするためにトランジスタQ2を駆動するプルダウン駆動回路（第2プルダウン駆動回路）である。図16から分かるように、第1のインバータは図9に示した構成のものであり、第2のインバータは図10に示した構成のものである。

30

【0097】

第2のインバータにおいては、ノードN2がHレベルのときトランジスタQ8がオンになるので、トランジスタQ9Aのソース（ノードN4）は正バイアスされる。トランジスタQ9Aは、ゲート電位がソース電位よりもしきい値電圧Vth以上高くなれば導通しないので、第2のインバータを反転させるためには、入力端子INがバイアスされたノードN4の電位よりもさらにしきい値電圧Vth以上高くなる必要がある。従って、第2のインバータのしきい値電圧は高いものとなる。

40

【0098】

従って、トランジスタQ6, Q8, Q9A, Q9Bから成る第2のインバータは、Lレベルの入力端子INに加わるノイズの影響を受けにくい。そのため、単位シフトレジスタ回路SRのリセット状態に入力端子INに加わるノイズに起因して、ノードN2のレベルが低下することが防止される。よって本実施の形態によれば、入力端子INがHレベルになるとノードN2がLレベルが素早く切り替わるようにして単位シフトレジスタ回路SRの動作の高速化を図りつつ、入力端子INに加わるノイズによる誤動作を防止することができる。その結果、本実施の形態に係る単位シフトレジスタ回路SRにより構成され

50

たゲート線駆動回路を有する表示装置における表示不具合を防止できる。

【0099】

特に、単位シフトレジスタ回路S Rがa - S i T F Tで構成されている場合には、ゲートがノードN 2に接続したトランジスタQ 2, Q 5の駆動能力が低下して上記の誤動作の問題が生じやすくなるため、本発明の適用は効果的である。

【0100】

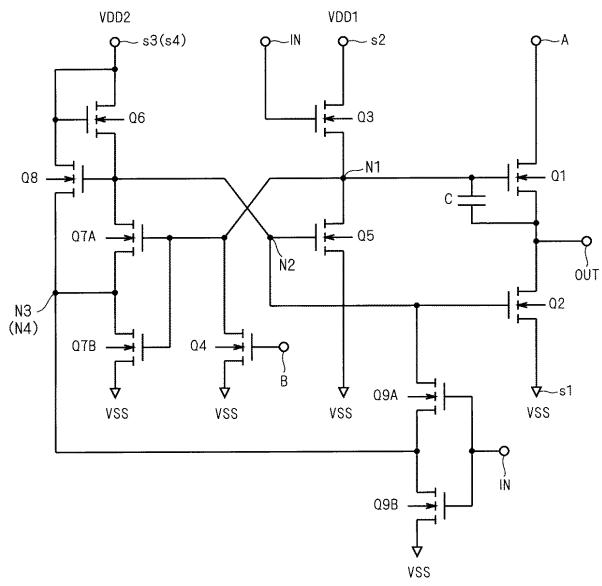

<実施の形態6>

図17は、実施の形態6に係る単位シフトレジスタ回路S Rの構成を示す回路図である。本実施の形態は、上記の実施の形態1と実施の形態5とを組み合わせたものである。即ち、本実施の形態に係る単位シフトレジスタ回路S Rは図17の如く、トランジスタQ 6, Q 7 A, A 7 B, Q 8から成り、ノードN 1を入力端としノードN 2を出力端とする第1のインバータ(第1プルダウン駆動回路)と、トランジスタQ 6, Q 8, Q 9 A, Q 9 Bから成り、入力端子INを入力端としノードN 2を出力端とする第2のインバータ(第2プルダウン駆動回路)とを備えている。トランジスタQ 6, Q 8は第1のインバータと第2のインバータとで共有されており、そのためトランジスタQ 9 A, Q 9 Bは、それぞれトランジスタQ 7 A, Q 7 Bに並列に接続することとなる。つまり本実施の形態では、トランジスタQ 7 AとトランジスタQ 7 Bとの間のノードN 3と、トランジスタQ 9 AとトランジスタQ 9 Bとの間のノードN 4とは同一のノードとなる。

【0101】

本実施の形態によれば、実施の形態1および実施の形態5で得られる両方の効果を得ることができる。即ち、入力端子INがHレベルになったときにノードN 2がLレベルが素早く切り替わるようにして単位シフトレジスタ回路S Rの動作の高速化を図りつつ、トランジスタQ 1のオーバラップ容量に起因するノイズや、ゲート線を介して入力端子INに加わるノイズによる誤動作を防止することができる。

【0102】

また図17の回路のように、第1のインバータと第2のインバータとでトランジスタQ 6, Q 8を共有させることにより、本発明に係る単位シフトレジスタ回路S Rの形成面積の増大を抑制することができる。

【図面の簡単な説明】

【0103】

【図1】本発明の実施の形態に係る表示装置の構成を示す概略ブロック図である。

【図2】単位シフトレジスタ回路を用いたゲート線駆動回路の構成例を示すブロック図である。

【図3】従来の単位シフトレジスタ回路の構成を示す回路図である。

【図4】ゲート線駆動回路の動作を示すタイミング図である。

【図5】単位シフトレジスタ回路を用いたゲート線駆動回路の構成例を示すブロック図である。

【図6】ゲート線駆動回路の動作を示すタイミング図である。

【図7】実施の形態1に係る単位シフトレジスタ回路の構成を示す回路図である。

【図8】実施の形態1に係る単位シフトレジスタ回路の構成を示す回路図である。

【図9】従来の単位シフトレジスタ回路のプルダウン駆動回路の構成を示す回路図である。

【図10】実施の形態1に係る単位シフトレジスタ回路のプルダウン駆動回路の構成を示す回路図である。

【図11】図9および図10のインバータの入出力特性を示すグラフである。

【図12】実施の形態2に係る単位シフトレジスタ回路の構成を示す回路図である。

【図13】実施の形態3に係る単位シフトレジスタ回路の構成を示す回路図である。

【図14】実施の形態4に係る単位シフトレジスタ回路の構成を示す回路図である。

【図15】従来の単位シフトレジスタ回路の変形例を示す図である。

【図16】実施の形態5に係る単位シフトレジスタ回路の構成を示す回路図である。

10

20

30

40

50

【図17】実施の形態6に係る単位シフトレジスタ回路の構成を示す回路図である。

【符号の説明】

【0104】

30 ゲート線駆動回路、SR 単位シフトレジスタ回路、Q1～Q12 トランジスタ、C 昇圧容量、N1～N4 ノード、A 第1クロック端子、B 第2クロック端子、IN 入力端子、OUT 出力端子、s1～s4 電源端子。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

---

フロントページの続き

F ターム(参考) 5C080 AA10 BB05 DD09 DD25 DD28 EE29 FF11 JJ02 JJ03 JJ04

JJ05