(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6829253号

(P6829253)

(45) 発行日 令和3年2月10日(2021.2.10)

(24) 登録日 令和3年1月25日(2021.1.25)

(51) Int.Cl.

F 1

|              |           |              |

|--------------|-----------|--------------|

| HO 1 L 21/66 | (2006.01) | HO 1 L 21/66 |

| GO 1 N 27/00 | (2006.01) | GO 1 N 27/00 |

| GO 1 N 27/22 | (2006.01) | GO 1 N 27/22 |

|   |

|---|

| N |

| Z |

| C |

請求項の数 18 (全 16 頁)

(21) 出願番号 特願2018-515182 (P2018-515182)

(86) (22) 出願日 平成28年6月2日 (2016.6.2)

(65) 公表番号 特表2018-518063 (P2018-518063A)

(43) 公表日 平成30年7月5日 (2018.7.5)

(86) 國際出願番号 PCT/US2016/035545

(87) 國際公開番号 WO2016/196813

(87) 國際公開日 平成28年12月8日 (2016.12.8)

審査請求日 令和1年5月22日 (2019.5.22)

(31) 優先権主張番号 14/731,677

(32) 優先日 平成27年6月5日 (2015.6.5)

(33) 優先権主張国・地域又は機関

米国 (US)

(73) 特許権者 517423763

セミラボ セミコンダクター フィジック

ス ラボラトリー カンパニー リミテッ

ド

SEMI LAB Semiconductor

Physics Laboratory Co., Ltd.

ハンガリー国 H-1117 ブダペスト

プリエレ コーネリア ウツツア 2

(74) 代理人 100105957

弁理士 恩田 誠

(74) 代理人 100068755

弁理士 恩田 博宣

(74) 代理人 100142907

弁理士 本田 淳

最終頁に続く

(54) 【発明の名称】一定の表面電位コロナ帯電を用いた半導体ドーピングの測定

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体試料を特徴付ける方法であつて、

( i ) 前記半導体試料の領域における表面電位の初期値を測定するステップと、

( i i ) 前記半導体試料が 2 ボルト以下の目標表面電位値を有するように、前記半導体試料の表面に電気的に結合された電圧源を介して前記半導体試料にバイアス電圧を印加するステップと、

( i i i ) 前記半導体試料にバイアス電圧を印加しつつ、前記表面の領域上にコロナ電荷量を堆積させるステップと、ここで、コロナ電荷の量は堆積中に監視され、

( i v ) コロナ電荷量を堆積させ、前記バイアス電圧を前記半導体試料から除去した後の領域における表面電位の値をさらに測定するステップと、

( v ) コロナ電荷量を堆積する前と後に測定され、前記半導体試料に印加される前記バイアス電圧なしでの表面電位の値の差に等しい表面電位の増分値を決定するステップと、

( v i ) 表面電位の前記増分値に対するコロナ電荷量の比に等しい前記半導体試料の表面空間電荷容量値を決定するステップと、

( v i i ) ステップ ( i i ) ~ ( v i ) を k 回繰り返して、k 個のコロナ電荷量、k 個の表面電位の増分値、および k 個の表面空間電荷容量値を提供するステップと、ここで、k は、1 より大きく、かつ前記半導体試料の目標ドーピング監視深さに到達するのに十分な整数であり、

( v i i i ) 表面電位の前記初期値、k 個の表面電位のさらなる値、前記 k 個のコロナ

10

20

電荷量、前記  $k$  個の表面電位の増分値、および前記  $k$  個の表面空間電荷容量値に基づいて前記半導体試料を特徴付けるステップとを含む方法。

**【請求項 2】**

表面電位を測定するために使用されるプローブの下で  $k$  個の対応する電荷密度値を得るために、 $k$  個のコロナ電荷量が較正関数  $F(V, I)$  によって補正される、請求項 1 に記載の方法。

**【請求項 3】**

$k$  個の電荷密度値の各々を使用して、表面電位の対応する増分値に対する対応する電荷密度値の比に等しい対応する補正された空間電荷容量を決定する、請求項 2 に記載の方法。

**【請求項 4】**

前記  $k$  個の電荷密度値の合計に等しい補正された正味のコロナ電荷密度値および補正された空間電荷容量を使用して、前記半導体試料のドーピング密度を決定する、請求項 3 に記載の方法。

**【請求項 5】**

補正された空間電荷容量と、対応する補正された正味の電荷密度値との積に等しい静電容量電荷係数を用いて前記較正関数の品質が決定される、請求項 4 に記載の方法。

**【請求項 6】**

半導体較正試料の表面下の距離  $W$  に亘る既知のドーピング密度を有する半導体較正試料を使用して電荷密度較正を行うことをさらに含む、請求項 1 に記載の方法。

**【請求項 7】**

コロナ帯電の極性は、前記半導体試料内に空乏表面空間の電荷領域を生成するような極性である、請求項 1 に記載の方法。

**【請求項 8】**

前記半導体試料が  $n$  型半導体であり、前記コロナ電荷が負の帯電極性を用いて堆積される、請求項 7 に記載の方法。

**【請求項 9】**

前記半導体試料が  $p$  型半導体であり、前記コロナ電荷が正の帯電極性を用いて堆積される、請求項 7 に記載の方法。

**【請求項 10】**

前記半導体試料を特徴付けることは、ドーピング密度および / またはドーピングプロファイルを決定することを含む、請求項 1 に記載の方法。

**【請求項 11】**

前記半導体試料がワイドバンドギャップ半導体を含む、請求項 1 に記載の方法。

**【請求項 12】**

前記半導体試料は、SiC、GaN、ZnO、ZnS、およびZnSe からなる群から選択される半導体を含む、請求項 1 に記載の方法。

**【請求項 13】**

表面電位測定が、非接触振動プローブを使用して行われる、請求項 1 に記載の方法。

**【請求項 14】**

表面電位測定が、容量性電極を使用して行われる、請求項 1 に記載の方法。

**【請求項 15】**

目標表面電位が 0.5 ボルト以下である、請求項 1 に記載の方法。

**【請求項 16】**

目標表面電位が約 0 ボルトである、請求項 1 に記載の方法。

**【請求項 17】**

前記半導体試料中に過剰なキャリアを生成するのに十分な光子エネルギーの光を有する照明を用いて、堆積されたコロナ電荷が光中性化され、半導体表面から除去される、請求項 1 に記載の方法。

**【請求項 18】**

各繰り返しの前に堆積されたコロナ電荷を光中性化した後に前記半導体試料の特徴付けを

10

20

30

40

50

繰り返すことをさらに含む、請求項 1 7 に記載の方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0 0 0 1】**

本開示は、特に一定の表面電位コロナ帯電を用いて、半導体ドーピング濃度を測定するためのシステムおよび方法に関する。

**【背景技術】**

**【0 0 0 2】**

ドナーまたはアクセプタ不純物を有する半導体をドーピングすると、半導体の電気伝導率が変化する。電気伝導率は、一般に、品質管理の目的のために、半導体材料の重要な特性であるので、半導体材料およびデバイスの製造中の半導体ドーピング濃度（例えば、半導体体積当たりのドーピング原子の濃度）を測定または監視することが有益である。例として、製造プロセスは、半導体結晶からスライスされた半導体ウェハのドーピング濃度を監視するステップ、バルクウェハ上に成長または堆積された薄いエピタキシャル層のドーピング濃度を監視するステップ、意図的なドーピングプロセスの実施後（例えば、不純物拡散またはイオン注入プロセスの後）の半導体のドーピング濃度を監視するステップを含むことができる。

10

**【発明の概要】**

**【0 0 0 3】**

一般に、一態様では、半導体試料を特徴付ける方法は、半導体試料の表面領域における表面電位の初期値  $V_{in}$  を測定するステップと、半導体試料を 2 V 以下の目標表面電位値 ( $V_0$ ) を有するようにバイアスするステップと、表面電位を目標値に調整した後に、表面領域上に監視下の量のコロナ電荷 ( $Q_1$ ) を堆積させるステップとを含む。この方法はまた、コロナ電荷を堆積した後の領域における表面電位の第 1 の値  $V_1$  を測定するステップと、表面電位の第 1 の変化 ( $V_1 = V_1 - V_0$ ) を決定するステップと、第 1 の静電容量値  $C_1 = Q_1 / V_1$  を決定するステップと、 $V_0$ 、 $V_1$ 、 $V_1$ 、 $Q_1$  および  $C_1$  に基づいて半導体試料を特徴付けるステップとを含む。

20

**【0 0 0 4】**

この態様の実施形態は、以下の特徴またはより多くの以下の特徴を含むことができる。

いくつかの実施形態では、この方法は、一連の連続的な監視下のコロナ電荷の堆積ステップをさらに含み、該ステップは、各堆積ステップの前に表面電位の目標値 ( $V_0$ ) を調整すること、および各堆積ステップの後の表面電位値を測定し、各ステップの結果を使用して、表面電位 ( $V_k$ )、コロナ電荷 ( $Q_k$ )、静電容量 ( $C_k$ )、表面電圧の累積値 ( $V_k = V_k$ ) および電荷の累積値 ( $Q_k = Q_k$ ) の対応する増分値を決定することを伴う。ここで、 $k$  は  $k$  番目のステップを示し、半導体試料は  $V_0$ 、 $V_k$ 、 $V_k$ 、 $Q_k$  および  $C_k$  の値に基づいて特徴付けられる。表面電位を測定するために使用されるプローブの下で電荷密度 ( $Q_{ck}$ ) を得るために、コロナ電荷  $Q_k$  は、較正関数  $F(V, I)$  によって補正することができる。 $Q_{ck}$  を使用して、補正された空間電荷容量  $C_{ck} = Q_{ck} / V_k$  を決定することができる。補正された正味のコロナ電荷密度  $Q_{ck} = Q_{ck}$  および補正された空間電荷容量  $C_{ck}$  を使用して、 $1 / C_{ck}^2$  対  $V_k$  プロットの傾き、 $Q_{ck}^2$  対  $V_k$  プロットの傾き、または  $C_{ck} Q_{ck}$  静電容量電荷係数から半導体試料のドーピング密度を決定することができる。較正関数の品質は、静電容量電荷係数  $C_{ck} Q_{ck}$  を使用して決定することができる。この方法はさらに、半導体較正試料の表面下の距離  $W$  に亘る既知のドーピング密度を有する半導体較正試料を使用して電荷密度較正を行うことを含むことができる。コロナ電荷の堆積ステップおよび表面電位の調整ステップは、目標のドーピング監視深さに到達するまで繰り返すことができる。

30

**【0 0 0 5】**

いくつかの実施形態では、コロナ帯電の極性は、半導体試料中に空乏表面空間の電荷領域を生成するような極性であり得る。半導体試料は、n 型半導体とすることができます、コロナ電荷は、負の帯電極性を用いて堆積される。半導体試料は、p 型半導体とすることができます

40

50

き、コロナ電荷は、正の帯電極性を用いて堆積される。

#### 【0006】

いくつかの実施形態では、半導体試料を特徴付けることは、ドーピング密度および／またはドーピングプロファイルを決定することを含むことができる。

いくつかの実施形態では、半導体試料は、ワイドバンドギャップ半導体を含むことができる。

#### 【0007】

いくつかの実施形態では、半導体試料は、SiC、GaN、ZnO、ZnS、およびZnSeからなる群から選択される半導体を含むことができる。

いくつかの実施形態では、表面電位測定は非接触振動プローブを使用して行うことができる。 10

#### 【0008】

いくつかの実施形態では、容量性電極を用いて表面電位測定を行うことができる。

いくつかの実施形態では、 $V_0$ は2V以下にすることができる。

いくつかの実施形態では、 $V_0$ は0.5V以下にすることができる。

いくつかの実施形態では、 $V_0$ は約0Vにすることができる。

#### 【0009】

いくつかの実施形態では、半導体試料中に過剰なキャリアを発生させるのに十分な光子エネルギーの光を有する照明を用いて、堆積されたコロナ電荷が光中性化され、半導体表面から除去される。この方法は、各繰り返しの前に堆積したコロナ電荷を光中性化した後に半導体試料の特徴付けを繰り返すことをさらに含むことができる。 20

#### 【0010】

一般に、別の態様では、方法は、試料の表面の領域において目標値と同じとなるように表面電位をバイアスした後、試料の表面の領域にコロナ電荷を繰り返し堆積させることを含む。

#### 【0011】

他の利点の中でも、実施形態を使用して、永久または一時的な金属半導体ダイオードを製造することなく、かつ侵入性の電気的接触を全く伴わずに、半導体試料のドーピング濃度を測定することができる。従って、場合によっては、測定値を比較的迅速に取得することができ、ドーピング測定が行われた後に、半導体ウェハをさらに処理または使用することができる。さらに、いくつかの実施形態では、静電反発力の影響が低減されるか、場合によっては実質的に排除されるように、（例えば、ゼロまたは他の一定の値にバイアスされた）一定の補償された表面電位値に従って増分的に半導体試料の表面上に電荷を堆積させることができる。さらに、一般に、これらの技術の実施形態は、環境規制または他の使用制限の対象となる危険物質である水銀を使用せずに実施することができる。 30

#### 【0012】

1つまたは複数の実施形態の詳細は、添付の図面および以下の説明に記載されている。他の特徴および利点は、説明および図面ならびに特許請求の範囲から明らかになるであろう。

#### 【図面の簡単な説明】

#### 【0013】

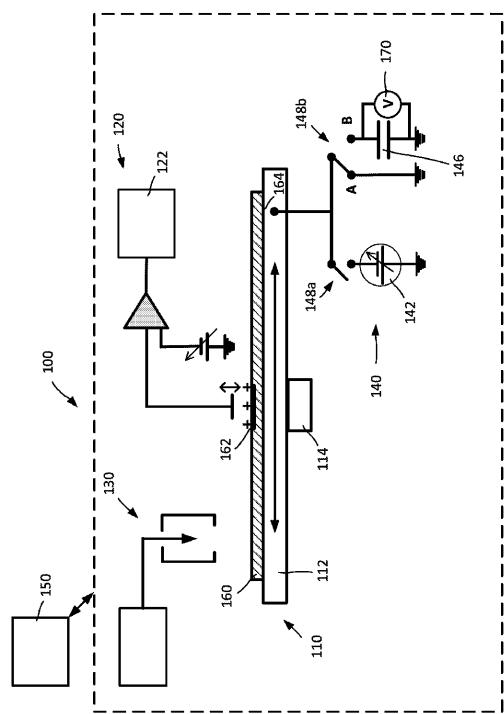

【図1A】半導体試料のドーピング濃度を測定する例示的なシステムの概略図である。

【図1B】半導体試料のドーピング濃度を測定する例示的なシステムの概略図である。

【図1C】半導体試料のドーピング濃度を測定する例示的なシステムの概略図である。

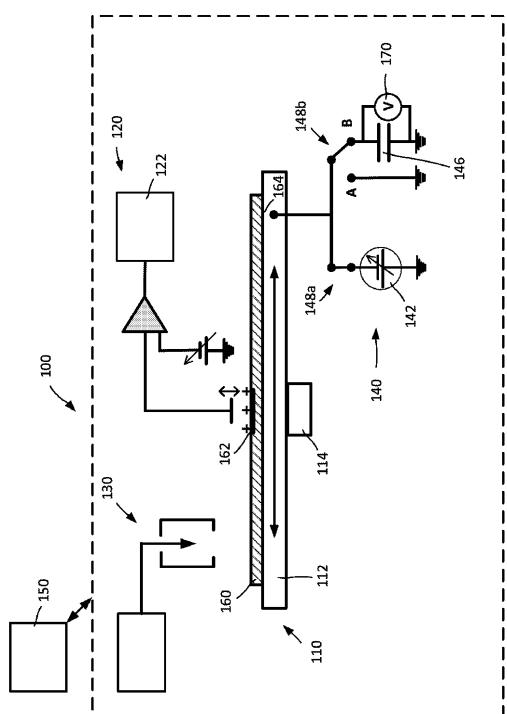

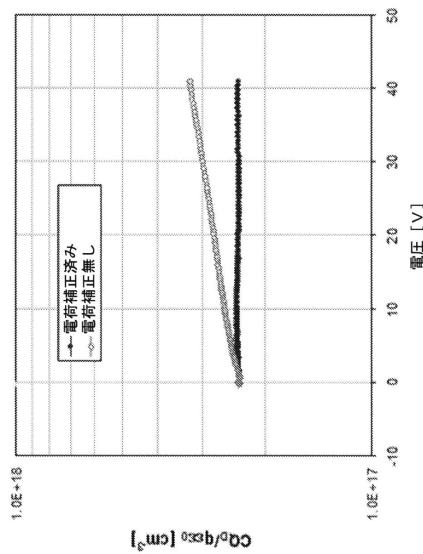

【図2】 $N = 2.37 \times 10^{17} \text{ cm}^{-3}$  の非常に均一にドープされたp型エピタキシャルSiC半導体試料に対するコロナ電荷の面密度補正の有無による $1/C^2$ 対 $V$ のプロットの一例である。

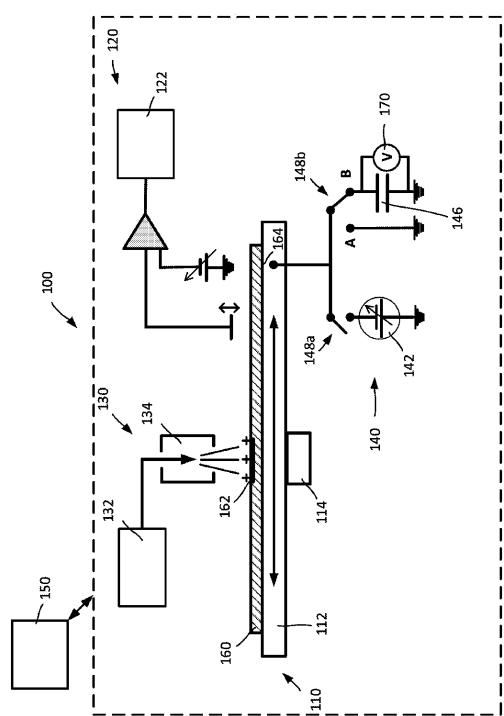

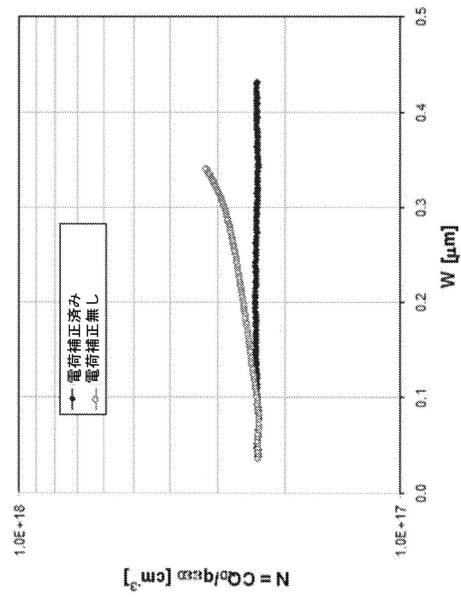

【図3】 $N = 2.37 \times 10^{17} \text{ cm}^{-3}$  の非常に均一にドープされたp型エピタキシャルSiCのコロナ電荷補正の有無による $CQ$ 対 $V$ プロットの一例である。

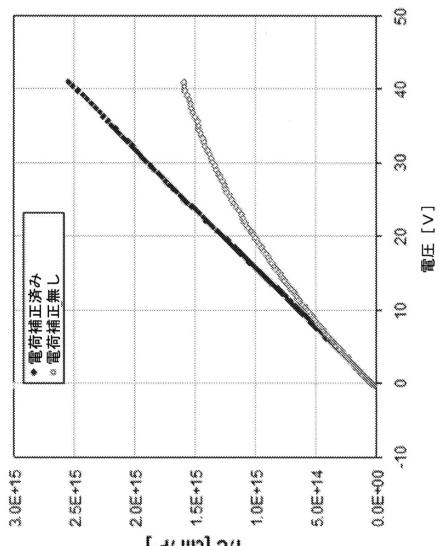

【図4】コロナ電荷補正の有無による $CQ$ 係数を用いて決定された一定のドーピング濃度

$N = 2.37 \times 10^{17} \text{ cm}^{-3}$  を有する例示的な p 型エピタキシャル SiC 半導体試料に関するドーピング深さプロファイルである。

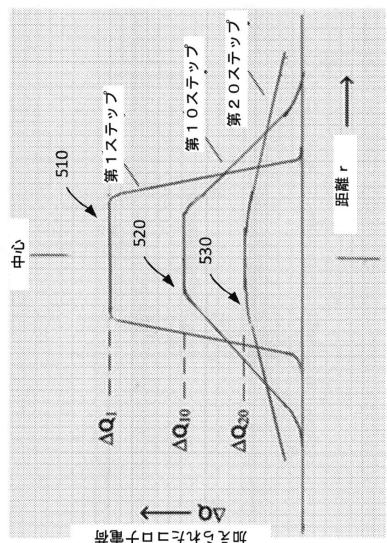

【図 5】電荷の初期堆積後、10 回の電荷の堆積の後、および 20 回の電荷の堆積の後の半導体ウェハに関する電荷プロファイルの例を示す。

【発明を実施するための形態】

【0014】

様々な図面における同様の参照番号は同様の構成を示す。

本開示は、正確で高速なフィードバック、非侵襲的、および非接触技術を用いて半導体のドーピング濃度を測定することに関する。これらの技術の実施形態は、半導体の試験部位における表面電位を測定すること、試験部位での特定の表面電位（例えば、ゼロ、実質的にゼロ、または他の一定の値）を得るために半導体にバイアス電圧を印加すること、（例えば、空気中でのコロナ放電を使用して）半導体表面の試験部位上に電荷を堆積させることを含む。この一連の表面電位測定、表面電位補償、および電荷堆積は、金属コンタクトダイオードにおけるショットキー障壁と同様に、精密に制御された空乏表面空間の電荷層を生成するために複数回繰り返すことができる。次いで、空乏空間の電荷層内の半導体のドーピング濃度を決定して、半導体表面下のドーピング深さプロファイルを得るために、半導体空乏空間電荷容量 C を測定することができる。いくつかの実施形態では、半導体空乏空間電荷容量と試験部位に堆積した全電荷との積 CQ を正確なドーピング深さプロファイルリングのための測定品質係数として使用することができる。

【0015】

電荷の各増分堆積の後に半導体の表面電位が補償されるので、静電反発力の効果は低減され、場合によっては実質的に除去される。さらに、空乏空間の電荷層は、永久または一時的な金属半導体ダイオードを形成することなく、かつ侵入的な電気接点を用いずに形成することができるので、比較的迅速に測定値を得ることができ、ドーピング測定後に半導体ウェハをさらに処理または使用することができる。さらに、一般に、これらの技術の実施形態は、しばしば環境規制または他の使用制限の対象となる危険物質である水銀を使用せずに実施することができる。

【0016】

これらの技術の実施形態は、コロナ堆積の電荷を保持することができる半導体材料のドーピング濃度を測定するために使用することができる。これは、例えば、ワイドバンドギャップ半導体（例えば、短波長照明に曝されない SiC、GaN または ZnO 半導体）を含むことができる。これは、例えば、コロナ電荷の中性化を防止する誘電体膜（例えば、SiO<sub>2</sub> 膜または Si<sub>3</sub>N<sub>4</sub> 膜）で被覆された半導体を含むこともできる。

【0017】

さらに、これらの技術の実施形態は、様々な用途に使用される半導体ウェハの製造を改善するために使用することができる。例えば、これらの技術は、コロナ誘起空乏電圧値の範囲を、比較的高い電圧（例えば、数百ボルト）にまで拡張することができ、高電圧電力デバイス用の SiC および GaN 半導体ウェハのドーピングプロファイルリングを実行するのに有利であり得る。別の例として、これらの技術は、オプトエレクトロニクス用途に使用される半導体ウェハの製造を改善するために使用することができる。

【0018】

ある場合において、記載された技術はまた、誘電体と、ウェハおよびマイクロ試験部位上の界面との測定を含む、他のコロナ電荷に基づく特性決定プロセスにも適用することができる。

【0019】

半導体試料のドーピング濃度を測定するための例示的なシステム 100 を図 1A に示す。システム 100 は、ステージアセンブリ 110、ケルビンプローブ 120、コロナ帯電ステーション 130、電圧補償アセンブリ 140、および処理モジュール 150 を含む。

【0020】

システム 100 の例示的な動作において、半導体試料 160 が、ステージアセンブリ 1

10

20

30

40

50

10 上に配置され、かつケルビンプローブ 120 による検査のために配置される。ケルビンプローブ 120 は、半導体試料 160 の表面上の試験部位 162 の表面電位を測定する。電圧アセンブリ 140 は、半導体試料 160（例えば、半導体試料 160 の裏面 164）にバイアス電圧を印加して、試験部位の表面電位を特定の値（例えば、ゼロボルト、0 . 5 V 以下、2 V 以下、またはその他のいくらかの値）に補償する。次いで、半導体試料 160 は、コロナ帯電ステーション 130 の下方に再配置され、半導体試料 160 の試験部位 162 に電荷が堆積される。電荷が堆積された後、堆積された電荷によって半導体試料 160 上の表面の下に誘導される空乏空間の電荷層を形成するために、表面電位測定、表面電位補償、電荷堆積が 1 回または複数回繰り返される。これらの各繰り返しの後に、半導体空乏空間電荷容量が決定され、これらの決定に基づいて、処理モジュール 150 は、半導体のドーピング濃度および／または半導体表面の下のドーピング深さプロファイルを決定する。このプロセスの間、半導体試料 160 は、（例えば、システム 100 のすべてまたは一部が遮光されたハウジングまたは設備内で包囲されることにより）迷光から遮蔽することができる。

#### 【0021】

ステージアセンブリ 110 は、システム 100 による検査の間に半導体試料 160 を支持し位置決めする。ステージアセンブリ 110 は、半導体試料（例えば、半導体ウェハ）との間で電荷を伝導することができるチャック 112 を含む。場合によっては、チャック 112 は、1 つまたは複数の導電性材料で構成することができる。例えば、チャック 112 は、アルミニウムで構成され、かつ窒化チタンで被覆されていてもよい。実際には、実施形態に応じて、他の導電性材料も可能である。

#### 【0022】

半導体試料 160（例えば、半導体ウェハ）は、半導体試料 160（例えば、裏面 164）とチャック 112 との間に電気的接触が提供されるように、チャック 112 に固定される。半導体試料 160 は、チャック 112 に非侵襲的に固定することができる。例えば、ある場合には、半導体試料 160 は、真空室 114 によって加えられる吸引力によってチャック 112 に固定され得る。図 1A には真空室 114 が示されているが、実際には、実施形態に応じて、他の固定機構（例えば、ピン、ブラケットおよび／または結合部）も可能である。

#### 【0023】

ステージアセンブリ 110 は、半導体試料 160 がケルビンプローブ 120 および帯電ステーション 130 に対して平行移動できるように、1 つまたは複数の軸に沿って移動することができる。例えば、場合によっては、チャック 112 は、システム 100 の他の構成要素に対して 3 つの次元のいずれかに沿って半導体試料 160 を移動させるために、デカルト座標系の y 軸、y 軸、および／または z 軸に沿って移動することができる。

#### 【0024】

図 1A に示すように、ステージアセンブリ 110 は、ケルビンプローブ 120 が試験部位 162 の表面電位を測定できるように、半導体試料 160 を最初にケルビンプローブ 120 の下に位置決めする。ケルビンプローブ 120 によって得られた測定値は、分析のために処理モジュール 150 に送信される。

#### 【0025】

ケルビンプローブ 120 は、半導体試料 160 に接触することなく、試験部位 162 の表面電位を測定することができる。表面電位は、既知の仕事関数を有する基準プローブと未知の仕事関数を有する半導体表面との間の定電位差（C P D : constant potential difference）を測定することにより得ることができる。典型的には、プローブは半導体試験部位の表面の上方に配置され、振動されて、プローブと半導体試験部位との間の静電容量の周期的変動を引き起こし、プローブに時間変化する電流を生じさせる。この電流は、測定され、プローブまたは半導体表面に反対の電圧を印加することによって無効にされ得る。バックинг電位（backing potential）として知られているこの電圧は、プローブと半導体表面との間の C P D に等しいとき、

ゼロ電流が生じる。この電圧は、例えば、測定システム 122 を用いて決定することができる。

#### 【0026】

振動ケルビンプローブ 120 が図 1A に示されているが、実際には、実施形態に応じて他の非接触振動プローブまたは測定システムも使用することができる。例えば、ある場合には、ケルビンプローブの代わりにモンロープローブを使用することができる。

#### 【0027】

いくつかの実施形態では、振動プローブ 120 は、特定の直径（例えば、1 mm、2 mm、または他のいくらかの直径）を有することができる。いくつかの場合では、ケルビンプローブ 120 は、半導体試料上のいくつかの試験部位の表面電位を測定するために、半導体試料に対して移動することができる（例えば、半導体試料を横切って移動する）。10

#### 【0028】

試験部位 162 の表面電位の測定中、電圧補償アセンブリ 140 は、半導体試料 160 の裏面 164 を電気的に接地するように構成される。例えば、図 1A に示すように、電圧補償アセンブリ 140 は、スイッチ 148a を介してチャック 112 に結合された直流（DC）電圧源 142 と、スイッチ 148b を介してチャック 112 に結合された入力コンデンサ 146 とを含む。試験部位 162 の表面電位の測定中、スイッチ 148a は開いており、スイッチ 148b は位置 A にある。その結果、チャック 112 および半導体試料 160 の裏面 164 は、両方とも電気的に接地される。20

#### 【0029】

システム 100 は、半導体試料 160 の裏面 164 にバイアス電圧を印加することによって、試験部位の表面電位を補償する。図 1A に示すように、いくつかの実施形態では、このバイアス電圧は、入力コンデンサ 146 を半導体試料 160 の裏面 164 に電気的に接続し、特定のバイアス電圧が入力コンデンサ 146 の両端に得られるまで入力コンデンサ 146 を充電することによって印加される。図 1B に示すように、これは、スイッチ 148a を閉じ、スイッチ 148b を位置 B に切り替えることによって行うことができる。スイッチ 148a - b がこれらの位置にあるとき、DC 電圧源 142 および入力コンデンサ 146 は、それぞれ共に電気的に接続されるとともに、チャック 112 に電気的に接続される。従って、直流電圧源 142 は、入力コンデンサ 146 を電気的に充電する。さらに、入力コンデンサ 146 がチャック 112 および半導体試料 160 の裏面 164 に電気的に接続されると、入力コンデンサ 146 の両端の電圧は、試験部位の表面電位をバイアスする。30

#### 【0030】

入力コンデンサ 146 のバイアス電圧は、入力コンデンサ 146 と並列の測定システム 170 を用いて監視することができる。測定システム 170 によって得られた測定値は、分析のために処理モジュール 150 に送信することができる。

#### 【0031】

DC 電圧源 142 は、試験部位 162 における表面電位を補償するために、入力コンデンサ 146 を特定のバイアス電圧に充電するように構成することができる。場合によっては、DC 電圧源 142 は、試験部位 162 においてゼロまたは実質的にゼロの表面電位を達成するように構成することができる。例えば、DC 電圧源 142 は、入力コンデンサ 146 の両端のバイアス電圧がケルビンプローブ 120 によって測定された表面電圧と反対になるように入力コンデンサ 146 を充電することができる。すなわち、裏面 164 が電気的に接地されている間（例えば、スイッチ 148a が開いており、スイッチ 148b が位置 A にある間）にケルビンプローブ 120 が  $V_0$  の表面電圧を測定した場合、スイッチ 148b が閉じ、スイッチ 148b が位置 B にあるとき、DC 電圧源 142 は、入力コンデンサ 146 の両端の  $-V_0$  の電圧を印加することができる。従って、試験部位 162 の表面電位は、入力コンデンサ 146 が充電され、入力コンデンサ 146 の両端に  $-V_0$  のバイアス電圧が得られると、ゼロに補償される。40

#### 【0032】

50

入力コンデンサ 146 が充電された後、バイアスされた表面電位の状態に従って試験部位 162 に電荷が堆積される。図 1C に示すように、半導体試料 160 は、試験部位 162 がコロナ帯電ステーション 130 の下に配置されるように、ステージアセンブリ 110 によって再配置される。コロナ帯電ステーション 130 は、試験部位 162 に電荷を堆積させる。電荷の堆積中、スイッチ 148a は開位置にあり、スイッチ 148b は位置 B にある。従って、入力コンデンサ 146 は電荷堆積中に試験部位の表面電位をバイアスし続ける。

#### 【 0033】

場合によっては、コロナ帯電ステーション 130 は、空気中のコロナ放電によって試験部位 162 上に電荷を堆積させる。例えば、図 1C に示すように、コロナ帯電ステーション 130 は、高電圧源 132 と、放電針電極を備えたコロナ帯電ガン 134 とを含む。高電圧によりコロナ放電が生成され、コロナ放電によって生成されたイオンは、帯電ガン 134 から試験部位 162 に向けて導かれ、試験部位 162 の表面に堆積する。電荷堆積の結果、電圧の僅かな変化が入力コンデンサ 146 の両端に誘起される。この電圧変化  $V$  は、堆積された電荷  $Q_{in} = C_{in} V$  の現場測定として使用することができ、ここで、 $C_{in}$  は入力コンデンサ 146 の容量であり、 $Q_{in}$  は堆積した電荷である。この電圧変化は、入力コンデンサ 146 と並列な測定システム 170 を用いて測定することができる。測定システム 170 によって得られた測定値は、分析のために処理モジュール 150 に送信することができる。

#### 【 0034】

いくつかの実施形態では、コロナ帯電ステーション 130 は、特定の領域（例えば、約 8 ~ 10 mm の直径を有する円形領域）内に電荷を堆積するように構成され、ケルビンプローブ 120 は、電荷堆積領域内のより小さなサブ領域（例えば、約 2 mm の直径を有する円形のサブ領域）の表面電位を測定するように構成されている。これは、例えば、ケルビンプローブ 120 によって測定されている領域の全体にわたって電荷が均一に堆積されることを保証するために有益であり得る。

#### 【 0035】

電荷が半導体試料 160 上に堆積された後、図 1A ~ C に示される一連の表面電位測定、表面電位補償および電荷堆積が、試験部位 162 において表面空乏空間の電荷層を正確に制御された態様で変化させるために、1 回または複数回繰り返すことができる。例えば、システム 100 を図 1A に示す形態に戻して、新たな表面電圧測定値  $V_1$  を試験部位 162 に対して決定することができる。同様に、（例えば、入力コンデンサ 146 を  $-V_1$  のバイアス電圧に充電し、入力コンデンサ 146 を半導体試料 160 の裏面 164 に接続することによって）新たな電圧測定値  $V_1$  に従って試験部位 162 の表面電位をバイアスするために、システム 100 を図 1B に示す形態に再び切り替えることができる。さらに、バイアスされた表面電位の状態に応じて試験部位 162 上に電荷を再び堆積させることができるように、システム 100 を図 1C に示す形態に再び切り替えることができる。このようにして、一貫したまたは実質的に一貫性のある表面電位に従って試験部位 162 に電荷を増分的に堆積させることができる。さらに、各電荷堆積ステップの間に誘起される電圧変化を観察することができ、かつ堆積電荷の現場測定として使用することができる。

#### 【 0036】

処理モジュール 150 は、半導体空乏空間電荷容量に基づいて、半導体のドーピング濃度および / または半導体表面下のドーピング深さプロファイルを決定する。例えば、帯電によって生じる電圧差  $V = V_1 - V_0$ 、および堆積電荷の密度  $Q / \text{cm}^2$  を用いて、半導体空乏空間電荷容量  $C = Q / V$  を決定することができる。以下により詳細に説明するように、この関係は、半導体試料のドーピング濃度を推定するために使用することができる。

#### 【 0037】

いくつかの実施形態では、処理モジュール 150 は、デジタル電子回路を使用して、またはコンピュータソフトウェア、ファームウェア、またはハードウェア、またはそれらの

10

20

30

40

50

うちの 1 つまたは複数の組み合わせで実施することができる。例えば、ある場合において、処理モジュール 150 は、少なくとも部分的に、1 つまたは複数のコンピュータプログラム（例えば、データ処理装置によって実行するための、またはデータ処理装置の動作を制御するために実行するためのコンピュータ記憶媒体上に符号化されたコンピュータプログラム命令の 1 つまたは複数のモジュール）として実施することができる。コンピュータ記憶媒体は、コンピュータ可読記憶装置、コンピュータ可読記憶基板、ランダムまたはシリアルアクセスメモリアレイまたはデバイス、またはそれらの 1 つまたは複数の組み合わせとすることができます、またはこれらに含まれ得る。「処理装置」という用語は、例えば、プログラム可能なプロセッサ、コンピュータ、チップ上のシステム、またはそれらの複数のもの、またはそれらの組み合わせを含む、データを処理するためのあらゆる種類の装置、デバイスおよび機械を包含する。装置は、FPGA（フィールドプログラマブルゲートアレイ）またはASIC（特定用途向け集積回路）などの専用論理回路を含むことができる。装置は、ハードウェアに加えて、当該コンピュータプログラムの実行環境を生成するコード、例えば、プロセッサファームウェア、プロトコルスタック、データベース管理システム、オペレーティングシステム、クロスプラットフォームランタイム環境、仮想マシン、またはそれらのうちの 1 つまたは複数の組み合わせを構成するコードを含むことができる。装置および実行環境は、ウェブサービス、分散型コンピュティングインフラストラクチャおよびグリッドコンピュティングインフラストラクチャなど、様々な異なるコンピュティングモデルインフラストラクチャを実現することができる。

## 【0038】

いくつかの実施形態では、処理モジュール 150 は、システム 100 の 1 つまたは複数の他の構成要素の動作をも制御することができる。例えば、いくつかの実施形態では、これらの構成要素の各々を制御するために、処理モジュール 150 は、ステージアセンブリ 110、ケルビンプローブ 120、コロナ帯電ステーション 130 および / または電圧補償アセンブリ 140 と通信可能に接続される。

## 【0039】

特定の表面空乏層を生成するために、表面電位測定、表面電位補償、および電荷堆積のシーケンスを任意の回数繰り返すことができる。例えば、ある場合には、シーケンスは、所定回数だけ（例えば、10 回の繰り返し、20 回の繰り返し、30 回の繰り返し、または他の何回かの繰り返し）、または所望の幅の表面空乏層 W が得られるまで繰り返され得る。場合によっては、ドーピング深さプロファイリングおよびコロナ帯電較正のために、より多くの増分帯電ステップ（例えば、10 ステップ以上、20 ステップ以上）を使用することができる。

## 【0040】

このようにして電荷を増分的に堆積させることにより、静電容量 C は、表面空乏層 W の幅に関する差分空乏空間電荷容量  $C_D$  ( $C_D = \epsilon_s / W$ ) となる。ここで、 $\epsilon_s$  は半導体の誘電率であり、 $\epsilon_0$  は自由空間の誘電率  $\epsilon_0 = 8.854 \times 10^{-12} F/cm^2$  である。一例として、初期表面電位値  $V_0$  は、半導体試料の表面上の試験部位に対して決定され、試験部位の表面電位は、バイアス電圧（例えば、 $-V_0$ ）を半導体試料の裏面に印加することにより補償される。次いで、電荷密度  $Q_1$  を有する電荷量が試験部位に堆積される。電荷堆積後、バイアス電圧が除去され、試験部位の表面電位値  $V_1$  が決定される。次に、 $C_1 = Q_1 / (V_1 - V_0)$  の関係を用いて、半導体試料の差分表面電荷容量  $C_1$  が算出される。試験部位の表面電位は、半導体試料に新たなバイアス電圧（例えば、 $-V_1$ ）を印加することによって補償される。電荷密度  $Q_2$  を有する第 2 の電荷量が試験部位に堆積される。電荷堆積後、バイアス電圧が除去され、試験部位の表面電位値  $V_2$  が決定される。次いで、 $C_2 = Q_2 / (V_2 - V_1)$  の関係を用いて、半導体試料の差分表面電荷容量  $C_2$  が計算される。

## 【0041】

このシーケンスは、k 回（例えば、k = 20 回の繰り返し）、または所望のドーピング監視深さ  $W = \epsilon_s / C_k$  に到達するまで繰り返すことができる。例えば、場合によっ

10

20

30

40

50

ては、一連の連続的に監視されるコロナ電荷堆積ステップを実施することができ、試験部位の表面電位を、各堆積ステップの前に特定の目標値（例えば、ゼロボルト、0.5V以下、2V以下、または他のいくつかの目標値）に調整することができる。表面電位値は各堆積ステップの後に測定することができ、各ステップの測定値の結果を用いて、表面電位（ $V_k$ ）、コロナ電荷（ $Q_k$ ）、静電容量（ $C_k$ ）、表面電圧の累積値（ $V_k = V_0 + \dots + V_k$ ）および電荷の累積値（ $Q_k = Q_0 + \dots + Q_k$ ）の対応する増分値を決定することができる。ここで、 $k$  は  $k$  番目のステップまたは繰り返しを表す。半導体試料は、 $V_0$ 、 $V_k$ 、 $V_k$ 、 $Q_k$  および  $C_k$  の値に基づいて特徴付けられ得る。

#### 【0042】

場合によっては、堆積された電荷密度の線量は、電荷堆積の各繰り返し毎に同じであってもよい（例えば、 $Q_1 = Q_2 = Q_3 = \dots = Q_k$ ）。

いくつかの実施形態では、堆積した電荷は、半導体のドーピング濃度が決定された後に除去することができる。例えば、ある場合には、半導体試料中に過剰なキャリアを発生させるのに十分な光子エネルギーを有する照明（例えば、SiC、GaN、またはZnO半導体に対しては3.3eVを超える光子エネルギーを有する青色光）を使用してコロナ堆積電荷が光中性化されて（photo-neutralized）、半導体表面から除去され得る。場合によっては、各測定の間に堆積した電荷を除去し、電荷の堆積を繰り返すことによって、試験部位のドーピング濃度を複数回測定することができる。

#### 【0043】

半導体のドーピング濃度を測定することは、特定の空乏層電圧（例えば、10V、20V、50V、100V、200Vまたはそれ以上）を必要とすることがある。補償なしでは、表面電位が高いと、堆積したコロナイオンと入射するコロナイオンとの間に存在する静電気力によりコロナ電荷堆積が妨げられることが多い。例えば、ある場合には、堆積されたコロナイオンと入射するコロナイオンとの間の静電反発力は、電荷堆積の密度を制限し得る。加えて、多くの場合、コロナイオンに作用する力は、入射イオンを帯電部位の中心から離れる方向に導き、電荷密度の不均一な横方向分布を引き起こす。これは、試験部位での堆積された電荷線量密度の定量化において誤差が生じる可能性があり、静電容量およびドーピング密度の計算において対応する誤差が生じる可能性がある。これらの制限および誤差は、堆積部位で一定または実質的に一定の表面電位を有する半導体表面上に（例えば、上述したように）電荷を増分的に堆積することによって緩和することができるか、または、場合によっては完全に排除することができる。

#### 【0044】

コロナ帯電に基づく技術を用いて半導体ドーピング濃度を測定する場合、表面空乏層は、半導体表面およびその下の表面空間の電荷領域の正味の電気的中性により形成される。従って、半導体表面上に置かれた電荷は、表面空間の電荷領域内の反対の電荷によってミラーリングされる。空乏型空間電荷を生成するために、負のコロナ電荷がn型半導体上に堆積され、正のコロナ電荷がp型半導体上に堆積される。

#### 【0045】

半導体ドーピング濃度Nの場合、単位面積当たりの空乏層空間電荷は、 $Q_D = q N W$ として表すことができ、Wは空乏層の幅であり、qは素電荷である。空乏層は、単位面積当たりの容量  $C_D$  を有するキャパシタを形成する。

#### 【0046】

##### 【数1】

$$C_D = \frac{\epsilon_S \epsilon_0}{W} = q \frac{\epsilon_S \epsilon_0}{Q_D} N$$

上記の関係に基づいて、静電容量と電荷を乗算した係数  $C_Q$  に基づいてドーピング測定値を得ることができる。これは、i) コロナ堆積電荷密度  $Q$  の較正、および ii) ドーピング濃度  $N$  の決定の2つの目的のために使用することができる。

#### 【0047】

コロナ電荷較正を使用して、試験部位における単位面積当たりに堆積した増分電荷密度

10

20

30

40

50

$Q$  を正確に決定することができる。半導体試験部位の表面電位を補償し、一定の補償された表面電位に従って試験部位に電荷を堆積することにより、半導体の表面をより正確かつ / またはより均一に帯電させることができる。

#### 【 0 0 4 8 】

さらに、場合によっては、試験部位において現場測定された電荷増分値  $Q_{in_k}$  ( 例えれば、 $Q_{in_1}$ 、 $Q_{in_2}$  ) 、または任意の他の値  $Q_{in_k}$  を較正された電荷増分値  $Q_{ck} = Q_{in} F(V, I)$  に変換することができる。ここで、 $F(V, I)$  は表面電位  $V$  に依存する較正関数であり、 $I$  はコロナ帯電電流である。較正された電荷増分値

$Q_{ck}$  は、補正された空間電荷容量  $C_{ck} = Q_{ck} / V_k$  を決定するために使用され、補正されたドーピング濃度を決定するためにも使用され得る。場合によっては、較正関数  $F(V, I)$  は経験的に決定することができる。例えば、表面下の既知の距離  $W$  に亘って一定のドーピング深さプロファイルを有する既知のドーピング密度を有する半導体較正試料を使用して、電荷密度較正を行うことができる。関数  $F(V, I)$  は、関係  $Q_{ck} = Q_{in} F(V, I)$  を満たすのに必要な補正関数を決定することによって決定することができる。この関数は、未知のドーピング密度を有する試料のドーピング密度の決定値を補正するために使用することができる。

#### 【 0 0 4 9 】

いくつかの異なる技術を使用して、補正されたコロナ電荷増分値  $Q_{ck}$  、測定された表面電圧変化  $V_k$  、および補正された空間電荷容量  $C_{ck} = Q_{ck} / V_k$  を使用してドーピング密度を計算することができる。一例として、場合によっては、 $1/C^2 - V$  技法を使用することができる。ショットキーダイオード C - V 測定と同様に、ドーピング濃度  $N$  の計算は、補正された空間電荷容量  $C_{ck}$  を  $C$  の代わりに使用することができる以下の関係に基づいて  $1/C_{ck}^2$  対表面電圧  $V_k$  のプロットを使用して行うことができる。

#### 【 0 0 5 0 】

##### 【 数 2 】

$$\frac{1}{C_{ck}^2} = \frac{2(V_k - V_o)}{q \varepsilon_s \varepsilon_0 N}$$

ドーピング密度が空乏領域を通して一定である場合、プロットは直線であり、ドーピング密度は線の傾きから次のように決定される。

#### 【 0 0 5 1 】

##### 【 数 3 】

$$N = \frac{2}{\varepsilon_s \varepsilon_0} (\text{傾き}^{-1})$$

図 2 は、 $N = 2.37 \times 10^{17} \text{ cm}^{-3}$  の非常に均一にドープされた p 型エピタキシャル SiC 半導体試料に対するコロナ電荷面密度補正の有無による  $1/C^2$  対  $V$  のプロットの例を示す。この例では、補正なしでは、誤差による線の屈曲が観察される。場合によっては、補正されていないコロナ電荷を使用することによって、より高い電圧範囲で 50 %までの  $N$  の非常に大きな過大推定がなされ得る。例えば、場合によっては、約 8 V を超える表面電圧に対して電荷補正の必要性が明らかになり得る。この効果は、表面電位が比較的低い場合でさえ、コロナ帯電における静電気力効果の重要性を実証する。

#### 【 0 0 5 2 】

別の例として、ドーピング濃度  $N$  を評価するために使用することができる別の技術は、 $Q^2 - V$  技法である。例えば、ドーピング濃度  $N$  は、全電荷  $Q_k$  、総表面電圧  $V_k$  、および空乏層の関係に基づいて決定することができ、ここで、補正されたコロナ電荷増分値  $Q_{ck}$  を使用して全電荷  $Q_{ck} = Q_{ck}$  を決定することができる。

#### 【 0 0 5 3 】

## 【数4】

$$Q_{ck}^2 = 2q \varepsilon_s \varepsilon_o N |V_k - V_o|$$

$N$  が一定であれば、この  $Q^2 - V$  方程式は直線が与えられ、この直線の傾きはドーピング濃度  $N$  を与える。

## 【0054】

## 【数5】

$$N = \frac{1}{2q \varepsilon_s \varepsilon_o} \cdot |(\text{傾き})|$$

10

場合によっては、 $Q^2 - V$  技法で使用される累積全電荷は、静電容量測定と  $1/C^2 - V$  技法で使用される単一の電荷増分値  $Q_{ck}$  と比較して、電荷線量誤差および漏れ電流による対応するコロナ電荷の中性化に対してより敏感であり得る。電荷漏れがなく、静電気力効果に関して電荷量を適切に補正する場合、両方の技法が同様の結果をもたらすことができる。

## 【0055】

半導体の静電容量と電荷の積  $CQ$ （または、補正された空間電荷容量および補正されたコロナ電荷増分に従って表される場合は  $C_{ck} Q_{ck}$ ）もドーピング濃度  $N$  を決定するために使用され得る。図3は、 $N = 2.37 \times 10^{17} \text{ cm}^{-3}$  の例示的な一定のドーピング密度の p型エピタキシャル SiC 半導体試料について、コロナ電荷補正の有無による表面電圧の関数としてこの  $CQ$  係数（ $CQ$  は  $N$  に比例する）を示す。この例では、40Vで、補正されたコロナ電荷を使用しないことにより、 $N$  の誤差は約 35% である。 $CQ$  係数は、均一なドーパント深さプロファイル（例えば、図3に示されるような）を有する試料に対する定数とることができ、これらの場合、自己一貫性電荷線量検証メトリック（self-consistent charge dose verification metric）として使用することができる。例えば、不均一なドーパント深さプロファイルを有する半導体は、変化するかまたは一定でない  $CQ$  プロファイルを示す半導体を識別することによって区別することができる。

20

## 【0056】

別の例として、図4は、コロナ電荷補正の有無に応じて  $CQ$  係数を使用して決定された、一定のドーピング密度  $N = 2.37 \times 10^{17} \text{ cm}^{-3}$  を有する例示的な p型エピタキシャル SiC 半導体試料のドーパント深さプロファイルを示している。図4に示すように、試料の均一なドーパント深さプロファイルにより、補正された  $CQ$  係数は実質的に一定である。

30

## 【0057】

表面電位の調整後に電荷を一定値に堆積させることにより、クレーター、傾斜、または他の不均一な電荷堆積パターンの存在のような、同じ部位での複数の帯電ステップにわたって発生する傾向のある望ましくない電荷堆積パターンをなくすか、または低減することができる。比較例として、図5は、表面上の中心位置に公称的に電荷の初期堆積（プロファイル 510）後、同じ場所における電荷の 10 回の堆積のシーケンス（プロファイル 520）の後、同じ場所における電荷の 20 回の堆積のシーケンス（プロファイル 530）の後の半導体ウェハの電荷プロファイルを示す。この例では、半導体ウェハの表面電位は、各電荷の堆積の前に一定の目標値に調整されなかった。その結果、静電反発力は中心部での電荷量の減少を引き起こし、電荷プロファイルの広がりは、連続的な電荷堆積後の堆積部位において観察される。対照的に、各帯電ステップに先立って表面電位を調整（バイアス）することによって、電荷プロファイルの広がりを少なくすることができ、空間電荷プロファイルは、帯電ごとに同様に維持される。従って、電荷の堆積およびコロナ電荷のモニタリングの精度を向上させることができる。

40

## 【0058】

例示的なシステム 100 が図示され説明されているが、これは単なる例示である。実際

50

には、システム 100 は、実施形態に応じて、他の構成を有することができる。

例えば、場合によっては、ドーピング濃度測定中にステージアセンブリ 110 は移動しない。代わりに、ドーピング濃度測定を行うために、システム 100 の 1 つまたは複数の他の構成要素（例えば、ケルビンプローブ 120 および / またはコロナ帯電ステーション 130）が半導体試料 160 に対して移動することができる。

### 【0059】

多数の実施形態が記載されている。それにもかかわらず、本開示の技術思想および範囲から逸脱することなく、様々な変更がなされ得ることが理解されるであろう。従って、他の実施形態は、添付の特許請求の範囲内に含まれる。

【図 1 A】

FIG. 1A

【図 1 B】

FIG. 1B

【図1C】

FIG. 1C

【図2】

【図3】

【図4】

【図5】

---

フロントページの続き

(72)発明者 ラゴウスキー、ヤツエク

アメリカ合衆国 33647 フロリダ州 タンパ バーバドス アイル ドライブ 10852

(72)発明者 ウィルソン、マーシャル

アメリカ合衆国 33647 フロリダ州 タンパ エベンスバーグ ドライブ 4903

(72)発明者 サフチョク、アレクサンダー

アメリカ合衆国 33647 フロリダ州 タンパ ベルフラワー ロード 18909

(72)発明者 アルメイダ、カルロス

アメリカ合衆国 33634 フロリダ州 タンパ モルバーン サークル 8204

(72)発明者 ブダイ、チャバ

ハンガリー国 H - 8220 バラトナルマディ ヴェレシェギー ウツツア 19

審査官 小池 英敏

(56)参考文献 米国特許出願公開第2006/0267622(US, A1)

特開昭64-069024(JP, A)

特開平08-236591(JP, A)

特開平05-206243(JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/66

G01N 27/00

G01N 27/22