(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2007-503659

(P2007-503659A)

(43) 公表日 平成19年2月22日(2007.2.22)

(51) Int.C1.

G06F 17/50

(2006.01)

F 1

G06F 17/50 664A

G06F 17/50 668U

G06F 17/50 668K

テーマコード(参考)

5B046

(43) 公表日 平成19年2月22日(2007.2.22)

審査請求 未請求 予備審査請求 未請求 (全 39 頁)

(21) 出願番号 特願2006-532839 (P2006-532839)

(86) (22) 出願日 平成16年5月6日 (2004.5.6)

(85) 翻訳文提出日 平成18年1月6日 (2006.1.6)

(86) 國際出願番号 PCT/US2004/014225

(87) 國際公開番号 WO2004/102429

(87) 國際公開日 平成16年11月25日 (2004.11.25)

(31) 優先権主張番号 10/435,061

(32) 優先日 平成15年5月9日 (2003.5.9)

(33) 優先権主張国 米国(US)

(71) 出願人 300056440

シンプリシティ・インコーポレーテッド

アメリカ合衆国・94086・カリフォルニア州・サンイベイル・ウェスト・カリフォルニア・アベニュー・600

(74) 代理人 100064621

弁理士 山川 政樹

(74) 代理人 100098394

弁理士 山川 茂樹

(72) 発明者 オクテム、レベント

アメリカ合衆国・94085・カリフォルニア州・サンイベイル・イースト・ドゥア・ン・アベニュー・656

F ターム(参考) 5B046 AA08 BA03 JA01

最終頁に続く

(54) 【発明の名称】回路設計およびリタイミングの方法および装置

## (57) 【要約】

回路を階層的にリタイミングする方法と装置。本発明の少なくとも1つの実施形態では、(例えばモジュール・レベルでのリタイミングを介して)異なる複数の最小クロック周期を有するように異なる複数のレイテンシを備える回路のモジュールが設計される。一例では、モジュールの配置配線の後、詳細なタイミング分析から最小クロック周期が決定され、モジュールを含む回路のリタイミングの際に、回路の目的のクロック周期、とレイテンシと最小クロック周期との間の相関に基づいてモジュールのデータ・フロー・グラフ表現が構築される。本発明の少なくとも1つの実施形態では、階層的なリタイミングが実行される。これは、回路の一部分がリタイミングされて(例えば異なるレイテンシについての)結果が生成され、その結果が目的のクロック周期に基づく回路全体のリタイミングに選択的に使用されるものである。

**【特許請求の範囲】****【請求項 1】**

回路モジュールを設計する方法であって、モジュールの複数の回路設計を生成するステップであって、前記複数の回路設計が異なる複数のレイテンシを備える前記モジュールに対応するステップと、前記複数の回路設計の複数の許容できるクロックを決定するステップであって、前記複数の許容できるクロックのそれぞれが前記複数の回路設計のうちの対応する1つの実行可能なクロック周期を表すステップと、前記複数の許容できるクロックを前記異なる複数のレイテンシに関連付けるための設計データを生成するステップと

を含む方法。

**【請求項 2】**

前記複数の回路設計を生成する前記ステップが配置配線を行って前記複数の回路設計のそれぞれを生成するステップを含む請求項1に記載の方法。

**【請求項 3】**

前記複数の回路設計を生成する前記ステップが前記複数の回路設計のうちの第1のものを生成するステップと、前記複数の回路設計のうちの前記第1のものにパイプライン・レジスタ・セットを挿入して、前記複数の回路設計のうちの第2のものを生成するステップと

を含む請求項1に記載の方法。

**【請求項 4】**

前記複数の回路設計を生成する前記ステップがリタイミングを行って前記複数の回路設計のうちの前記第2のものを生成するステップをさらに含む請求項3に記載の方法。

**【請求項 5】**

前記複数の回路設計のうちの第1のものと前記複数の回路設計のうちの第2のものが異なるアーキテクチャを有する請求項1に記載の方法。

**【請求項 6】**

前記複数の回路設計のうちの第1のものと前記複数の回路設計のうちの第2のものが

a)異なる処理ロジックと

b)異なるロジック処理素子と

のうちの一方を有する請求項5に記載の方法。

**【請求項 7】**

前記実行可能なクロック周期が最小クロック周期を表す請求項1に記載の方法。

**【請求項 8】**

前記設計データがさらに前記異なる複数のレイテンシを前記複数の回路設計のうちの1つまたは複数のデータ・フロー・グラフ表現に関連付ける請求項1に記載の方法。

**【請求項 9】**

前記1つまたは複数のデータ・フロー・グラフ表現が前記複数の許容できるクロックに基づく請求項8に記載の方法。

**【請求項 10】**

前記設計データを生成する前記ステップが前記モジュールの1つまたは複数のデータ・フロー・グラフ表現を生成するステップであって、前記1つまたは複数のデータ・フロー・グラフ表現が前記複数の許容できるクロックに基づくステップ

を含む請求項1に記載の方法。

**【請求項 11】**

前記複数の回路設計のうちの第1のものが非レジスタード入力を含んでおり、前記1つまたは複数のデータ・フロー・グラフ表現が前記複数の回路設計のうちの前記

第1のものの第1のパスにおける信号遅延の少なくとも一部分を表す演算ノードの表現を含んでおり、前記第1のパスがレジスタを含んでおらず、非レジスタード入力に接続される

請求項10に記載の方法。

【請求項12】

前記演算ノードが前記第1のパスにおける前記信号遅延を表し、前記第1のパスにおける前記信号遅延が、レジスタを含んでおらず、かつ前記複数の回路設計のうちの前記第1のものにおける前記非レジスタード入力とレジスタとの間を接続する任意のパスにおける信号遅延以上である

請求項11に記載の方法。

10

【請求項13】

前記複数の回路設計のうちの第1のものが非レジスタード出力を含んでおり、

前記1つまたは複数のデータ・フロー・グラフ表現が前記複数の回路設計のうちの前記第1のものの第1のパスにおける信号遅延の少なくとも一部分を表す演算ノードの表現を含んでおり、前記第1のパスがレジスタを含んでおらず、非レジスタード出力に接続される

請求項10に記載の方法。

【請求項14】

前記演算ノードが前記第1のパスにおける前記信号遅延を表し、前記第1のパスにおける前記信号遅延が、レジスタを含んでおらず、かつ前記複数の回路設計のうちの前記第1のものにおける前記非レジスタード出力とレジスタとの間を接続する任意のパスにおける信号遅延以上である請求項13に記載の方法。

20

【請求項15】

前記演算ノードが前記第1のパスにおける前記信号遅延を表し、前記第1のパスが非レジスタード入力に接続されており、前記第1のパスにおける前記信号遅延が、レジスタを含んでおらず、かつ前記複数の回路設計のうちの前記第1のものにおける前記非レジスタード入力と出力とを接続する任意のパスにおける信号遅延以上である請求項13に記載の方法。

【請求項16】

前記1つまたは複数のデータ・フロー・グラフ表現のうちの第1のグラフ表現が前記複数の回路設計のうちの第1のものに対応しており、前記第1のグラフ表現が、前記複数の回路設計のうちの前記第1のものにおけるレジスタから始まり、前記複数の回路設計のうちの前記第1のものにおけるレジスタで終わるすべての第1のパスを表すエッジを含んでおり、前記エッジにおける遅延が前記複数の回路設計のうちの前記第1のもののレイテンシを表す請求項10に記載の方法。

30

【請求項17】

前記エッジが第1のノードと第2のノードとを接続して前記第1のパスを表し、前記第1のノードおよび前記第2のノードが信号遅延をもたらさない請求項16に記載の方法。

【請求項18】

回路を設計する方法であって、

40

前記回路の設計の目的のクロックを選択するステップと、

前記目的のクロックに基づいて前記回路の一部分のデータ・フロー・グラフの表現を決定するステップと、

前記データ・フロー・グラフの前記表現を使用して前記目的のクロックの前記設計をリタイミングするステップと

を含む方法。

【請求項19】

前記データ・フロー・グラフの前記表現を決定する前記ステップが

前記データ・フロー・グラフのエッジにおいて必要な追加の遅延数を決定するステップを含む請求項18に記載の方法。

50

**【請求項 2 0】**

前記エッジが前記データ・フロー・グラフの第1のノードと第2のノードを接続し、前記エッジによって接続されている前記第1と第2のノードが、前記回路の前記一部分のレジスタから始まり、前記回路の前記一部分のレジスタで終わるパスを表す請求項19に記載の方法。

**【請求項 2 1】**

前記第1のノードが、レジスタを含んでおらず、かつ前記回路の前記一部分の第1の入力と前記回路の前記一部分のレジスタの入力との間にある任意のパスにおける信号遅延以上である信号遅延を表すノードに接続される請求項20に記載の方法。

**【請求項 2 2】**

前記第2のノードが、レジスタを含んでおらず、かつ前記回路の前記一部分の第1の出力と前記回路の前記一部分のレジスタの出力との間にある任意のパスにおける信号遅延以上である信号遅延を表すノードに接続される請求項20に記載の方法。

**【請求項 2 3】**

前記データ・フロー・グラフが、レジスタを含んでおらず、かつ前記回路の前記一部分の第1の入力を前記回路の前記一部分の第1の出力に接続する任意のパスにおける信号遅延以上である信号遅延を表すノードを含む請求項20に記載の方法。

**【請求項 2 4】**

前記追加の遅延数を決定する前記ステップが

前記目的のクロックに従って前記回路の前記一部分に対してリタイミングを実行するステップ

を含む請求項19に記載の方法。

**【請求項 2 5】**

前記追加の遅延数を決定する前記ステップが

追加の遅延数を前記回路の前記一部分の許容できるクロックに相關させる設計データから前記追加の遅延数を決定するステップ

を含む請求項19に記載の方法。

**【請求項 2 6】**

回路を設計する方法であって、

前記回路の設計の目的のクロックを選択するステップと、

前記目的のクロックの前記回路の前記設計の一部分をリタイミングして第1の結果を生成するステップと、

前記第1の結果を使用して前記目的のクロックの前記設計をリタイミングするステップと

を含む方法。

**【請求項 2 7】**

前記回路の前記設計の前記一部分をリタイミングする前記ステップが

前記設計の前記一部分が前記目的のクロックで稼動することができるよう、いくつかのパイプライン・レジスタ・セットを前記設計の前記一部分に追加するステップ

を含む請求項26に記載の方法。

**【請求項 2 8】**

前記回路の前記設計の前記一部分をリタイミングする前記ステップが

前記設計の前記一部分が前記目的のクロックで稼動することができるよう、いくつかのパイプライン・レジスタ・セットを前記設計の前記一部分から削除するステップ

を含む請求項26に記載の方法。

**【請求項 2 9】**

前記目的のクロックの前記設計をリタイミングする前記ステップが

接続を使用して、リタイミングされる前記設計の前記一部分のレジスタ間のすべてのパスを表すステップであって、前記接続が前記設計の前記一部分に追加された前記いくつかのパイプライン・レジスタ・セットを表すいくつかの追加の遅延を必要とするステップ

10

20

30

40

50

を含む請求項 2 7 に記載の方法。

【請求項 3 0】

前記接続が第 1 のノードと第 2 のノードとを接続し、前記第 1 のノードと第 2 のノードが信号遅延をもたらさない請求項 2 9 に記載の方法。

【請求項 3 1】

前記目的のクロックの前記設計をリタイミングする前記ステップが

入力演算ノードを使用して、レジスタを含んでおらず、かつ前記設計の前記一部分の第 1 の入力と前記設計の前記一部分のレジスタとを接続するすべてのパスに沿った最大信号遅延を表すステップであって、前記入力演算ノードが遅延無しの接続を介して前記第 1 のノードに接続されるステップ

をさらに含む請求項 3 0 に記載の方法。

【請求項 3 2】

前記目的のクロックの前記設計をリタイミングする前記ステップが

出力演算ノードを使用して、レジスタを含んでおらず、かつ前記設計の前記一部分の第 1 の出力と前記設計の前記一部分のレジスタとを接続するすべてのパスに沿った最大信号遅延を表すステップであって、前記出力演算ノードが遅延無しの接続を介して前記第 2 のノードに接続されるステップ

をさらに含む請求項 3 1 に記載の方法。

【請求項 3 3】

前記目的のクロックの前記設計をリタイミングする前記ステップが

第 1 の演算ノードを使用して、レジスタを含んでおらず、かつ前記設計の前記一部分の第 2 の入力と前記設計の前記一部分の第 2 の出力とを接続するすべてのパスに沿った最大信号遅延を表すステップ

をさらに含む請求項 3 2 に記載の方法。

【請求項 3 4】

デジタル処理システムによって実行されると、前記システムに、回路モジュールを設計する方法を実行させる実行可能コンピュータ・プログラム命令を含む機械可読媒体であって、前記方法は、

モジュールの複数の回路設計を生成するステップであって、前記複数の回路設計が異なる複数のレイテンシを備える前記モジュールに対応するステップと、

前記複数の回路設計の複数の許容できるクロックを決定するステップであって、前記複数の許容できるクロックのそれぞれが前記複数の回路設計のうちの対応する 1 つの実行可能なクロック周期を表すステップと、

前記複数の許容できるクロックを前記異なる複数のレイテンシに関連付けるための設計データを生成するステップと

を含む機械可読媒体。

【請求項 3 5】

前記複数の回路設計を生成する前記ステップが

配置配線を行って前記複数の回路設計のそれぞれを生成するステップ

を含む請求項 3 4 に記載の媒体。

【請求項 3 6】

前記複数の回路設計を生成する前記ステップが

前記複数の回路設計のうちの第 1 のものを生成するステップと、

前記複数の回路設計のうちの前記第 1 のものにパイプライン・レジスタ・セットを挿入して、前記複数の回路設計のうちの第 2 のものを生成するステップ

を含む請求項 3 4 に記載の媒体。

【請求項 3 7】

前記複数の回路設計を生成する前記ステップが

リタイミングを行って前記複数の回路設計のうちの前記第 2 のものを生成するステップ

をさらに含む請求項 3 6 に記載の媒体。

10

20

30

40

50

**【請求項 3 8】**

前記複数の回路設計のうちの第1のものと前記複数の回路設計のうちの第2のものが異なるアーキテクチャを有する請求項34に記載の媒体。

**【請求項 3 9】**

前記複数の回路設計のうちの第1のものと前記複数の回路設計のうちの第2のものが

a)異なる処理ロジックと

b)異なるロジック処理素子と

のうちの一方を有する請求項38に記載の媒体。

**【請求項 4 0】**

前記実行可能なクロック周期が最小クロック周期を表す請求項34に記載の媒体。 10

**【請求項 4 1】**

前記設計データがさらに前記異なる複数のレイテンシを前記複数の回路設計のうちの1つまたは複数のデータ・フロー・グラフ表現に関連付ける請求項34に記載の媒体。

**【請求項 4 2】**

前記1つまたは複数のデータ・フロー・グラフ表現が前記複数の許容できるクロックに基づく請求項41に記載の媒体。

**【請求項 4 3】**

前記設計データを生成する前記ステップが

前記モジュールの1つまたは複数のデータ・フロー・グラフ表現を生成するステップであって、前記1つまたは複数のデータ・フロー・グラフ表現が前記複数の許容できるクロックに基づくステップ 20

を含む請求項34に記載の媒体。

**【請求項 4 4】**

前記複数の回路設計のうちの第1のものが非レジスタード入力を含んでおり、

前記1つまたは複数のデータ・フロー・グラフ表現が前記複数の回路設計のうちの前記第1のものの第1のパスにおける信号遅延の少なくとも一部分を表す演算ノードの表現を含んでおり、前記第1のパスがレジスタを含んでおらず、非レジスタード入力に接続される

請求項43に記載の媒体。

**【請求項 4 5】**

前記演算ノードが前記第1のパスにおける前記信号遅延を表し、前記第1のパスにおける前記信号遅延が、レジスタを含んでおらず、かつ前記複数の回路設計のうちの前記第1のものにおける前記非レジスタード入力とレジスタとの間を接続する任意のパスにおける信号遅延以上である請求項44に記載の媒体。 30

**【請求項 4 6】**

前記複数の回路設計のうちの第1のものが非レジスタード出力を含んでおり、

前記1つまたは複数のデータ・フロー・グラフ表現が前記複数の回路設計のうちの前記第1のものの第1のパスにおける信号遅延の少なくとも一部分を表す演算ノードの表現を含んでおり、前記第1のパスがレジスタを含んでおらず、非レジスタード出力に接続される 40

請求項43に記載の媒体。

**【請求項 4 7】**

前記演算ノードが前記第1のパスにおける前記信号遅延を表し、前記第1のパスにおける前記信号遅延が、レジスタを含んでおらず、かつ前記複数の回路設計のうちの前記第1のものにおける前記非レジスタード出力とレジスタとの間を接続する任意のパスにおける信号遅延以上である請求項46に記載の媒体。

**【請求項 4 8】**

前記演算ノードが前記第1のパスにおける前記信号遅延を表し、前記第1のパスが非レジスタード入力に接続されており、前記第1のパスにおける前記信号遅延が、レジスタを含んでおらず、かつ前記複数の回路設計のうちの前記第1のものにおける前記非レジスタ 50

ード入力と出力とを接続する任意のパスにおける信号遅延以上である請求項46に記載の媒体。

【請求項49】

前記1つまたは複数のデータ・フロー・グラフ表現のうちの第1のグラフ表現が前記複数の回路設計のうちの第1のものに対応しており、前記第1のグラフ表現が、前記複数の回路設計のうちの前記第1のものにおけるレジスタから始まり、前記複数の回路設計のうちの前記第1のものにおけるレジスタで終わるすべての第1のパスを表すエッジを含んでおり、前記エッジにおける遅延が前記複数の回路設計のうちの前記第1のもののレイテンシを表す請求項43に記載の媒体。

【請求項50】

前記エッジが第1のノードと第2のノードとを接続して前記第1のパスを表し、前記第1のノードと前記第2のノードが信号遅延をもたらさない請求項49に記載の媒体。

【請求項51】

デジタル処理システムによって実行されると、前記システムに、回路を設計する方法を実行させる実行可能コンピュータ・プログラム命令を含む機械可読媒体であって、前記方法は、

前記回路の設計の目的のクロックを選択するステップと、

前記目的のクロックに基づいて前記回路の一部分のデータ・フロー・グラフの表現を決定するステップと、

前記データ・フロー・グラフの前記表現を使用して前記目的のクロックの前記設計をリタイミングするステップと

を含む機械可読媒体。

【請求項52】

前記データ・フロー・グラフの前記表現を決定する前記ステップが

前記データ・フロー・グラフのエッジにおいて必要な追加の遅延数を決定するステップを含む請求項51に記載の媒体。

【請求項53】

前記エッジが前記データ・フロー・グラフの第1のノードと第2のノードを接続し、前記エッジによって接続されている前記第1と第2のノードが、前記回路の前記一部分のレジスタから始まり、前記一部分のレジスタで終わるパスを表す請求項52に記載の媒体。

【請求項54】

前記第1のノードが、レジスタを含んでおらず、かつ前記回路の前記一部分の第1の入力と前記回路の前記一部分のレジスタの入力との間に任意のパスにおける信号遅延以上である信号遅延を表すノードに接続される請求項53に記載の媒体。

【請求項55】

前記第2のノードが、レジスタを含んでおらず、かつ前記回路の前記一部分の第1の出力と前記回路の前記一部分のレジスタの出力との間に任意のパスにおける信号遅延以上である信号遅延を表すノードに接続される請求項53に記載の媒体。

【請求項56】

前記データ・フロー・グラフが、レジスタを含んでおらず、かつ前記回路の前記一部分の第1の入力を前記回路の前記一部分の第1の出力に接続する任意のパスにおける信号遅延以上である信号遅延を表すノードを含む請求項53に記載の媒体。

【請求項57】

前記追加の遅延数を決定する前記ステップが

前記目的のクロックに従って前記回路の前記一部分に対してリタイミングを実行するステップ

を含む請求項52に記載の媒体。

【請求項58】

前記追加の遅延数を決定する前記ステップが

追加の遅延数を前記回路の前記一部分の許容できるクロックに相關させる設計データか

10

20

30

40

50

ら前記追加の遅延数を決定するステップ

を含む請求項 5 2 に記載の媒体。

【請求項 5 9】

デジタル処理システムによって実行されると、前記システムに、回路を設計する方法を実行させる実行可能コンピュータ・プログラム命令を含む機械可読媒体であって、前記方法は、

前記回路の設計の目的のクロックを選択するステップと、

前記目的のクロックの前記回路の前記設計の一部分をリタイミングして第 1 の結果を生成するステップと、

前記第 1 の結果を使用して前記目的のクロックの前記設計をリタイミングするステップ

と

を含む機械可読媒体。

【請求項 6 0】

前記回路の前記設計の前記一部分をリタイミングする前記ステップが

前記設計の前記一部分が前記目的のクロックで稼動することができるよう、いくつかのパイプライン・レジスタ・セットを前記設計の前記一部分に追加するステップ

を含む請求項 5 9 に記載の媒体。

【請求項 6 1】

前記回路の前記設計の前記一部分をリタイミングする前記ステップが

前記設計の前記一部分が前記目的のクロックで稼動することができるよう、いくつかのパイプライン・レジスタ・セットを前記設計の前記一部分から削除するステップ

を含む請求項 5 9 に記載の媒体。

【請求項 6 2】

前記目的のクロックの前記設計をリタイミングする前記ステップが

接続を使用して、リタイミングされる前記設計の前記一部分のレジスタ間のすべてのパスを表すステップであって、前記接続が前記設計の前記一部分に追加された前記いくつかのパイプライン・レジスタ・セットを表すいくつかの追加の遅延を必要とするステップ

を含む請求項 6 0 に記載の媒体。

【請求項 6 3】

前記接続が第 1 のノードと第 2 のノードとを接続し、前記第 1 のノードと第 2 のノード

が信号遅延をもたらさない請求項 6 2 に記載の媒体。

【請求項 6 4】

前記目的のクロックの前記設計をリタイミングする前記ステップが

入力演算ノードを使用して、レジスタを含んでおらず、かつ前記設計の前記一部分の第 1 の入力と前記設計の前記一部分のレジスタとを接続するすべてのパスに沿った最大信号遅延を表すステップであって、前記入力演算ノードが遅延無しの接続を介して前記第 1 のノードに接続されるステップ

をさらに含む請求項 6 3 に記載の媒体。

【請求項 6 5】

前記目的のクロックの前記設計をリタイミングする前記ステップが

出力演算ノードを使用して、レジスタを含んでおらず、かつ前記設計の前記一部分の第 1 の出力と前記設計の前記一部分のレジスタとを接続するすべてのパスに沿った最大信号遅延を表すステップであって、前記出力演算ノードが遅延無しの接続を介して前記第 2 のノードに接続されるステップ

をさらに含む請求項 6 4 に記載の媒体。

【請求項 6 6】

前記目的のクロックの前記設計をリタイミングする前記ステップが

第 1 の演算ノードを使用して、レジスタを含んでおらず、かつ前記設計の前記一部分の第 2 の入力と前記設計の前記一部分の第 2 の出力とを接続するすべてのパスに沿った最大信号遅延を表すステップ

をさらに含む請求項 6 5 に記載の媒体。

10

20

30

40

50

をさらに含む請求項 6 5 に記載の媒体。

【請求項 6 7】

回路モジュールを設計するデータ処理システムであって、

モジュールの複数の回路設計を生成する手段であって、前記複数の回路設計が異なる複数のレイテンシを備える前記モジュールに対応する手段と、

前記複数の回路設計の複数の許容できるクロックを決定する手段であって、前記複数の許容できるクロックのそれぞれが前記複数の回路設計のうちの対応する 1 つの実行可能なクロック周期を表す手段と、

前記複数の許容できるクロックを前記異なる複数のレイテンシに関連付けるための設計データを生成する手段と

を含むデータ処理システム。

【請求項 6 8】

前記複数の回路設計を生成する前記手段が

配置配線を行って前記複数の回路設計のそれぞれを生成する手段

を含む請求項 6 7 に記載のデータ処理システム。

【請求項 6 9】

前記複数の回路設計を生成する前記手段が

前記複数の回路設計のうちの第 1 のものを生成する手段と、

前記複数の回路設計のうちの前記第 1 のものにパイプライン・レジスタ・セットを挿入して、前記複数の回路設計のうちの第 2 のものを生成する手段と

を含む請求項 6 7 に記載のデータ処理システム。

【請求項 7 0】

前記複数の回路設計を生成する前記手段が

リタイミングを行って前記複数の回路設計のうちの前記第 2 のものを生成する手段

をさらに含む請求項 6 9 に記載のデータ処理システム。

【請求項 7 1】

前記複数の回路設計のうちの第 1 のものと前記複数の回路設計のうちの第 2 のものが異なるアーキテクチャを有する請求項 6 7 に記載のデータ処理システム。

【請求項 7 2】

前記複数の回路設計のうちの第 1 のものと前記複数の回路設計のうちの第 2 のものが

a ) 異なる処理ロジックと

b ) 異なるロジック処理素子と

のうちの一方を有する請求項 7 1 に記載のデータ処理システム。

【請求項 7 3】

前記実行可能なクロック周期が最小クロック周期を表す請求項 6 7 に記載のデータ処理システム。

【請求項 7 4】

前記設計データがさらに前記異なる複数のレイテンシを前記複数の回路設計のうちの 1 つまたは複数のデータ・フロー・グラフ表現に関連付ける請求項 6 7 に記載のデータ処理システム。

【請求項 7 5】

前記 1 つまたは複数のデータ・フロー・グラフ表現が前記複数の許容できるクロックに基づく請求項 7 4 に記載のデータ処理システム。

【請求項 7 6】

前記設計データを生成する前記手段が

前記モジュールの 1 つまたは複数のデータ・フロー・グラフ表現を生成する手段であって、前記 1 つまたは複数のデータ・フロー・グラフ表現が前記複数の許容できるクロックに基づく手段

を含む請求項 6 7 に記載のデータ処理システム。

【請求項 7 7】

10

20

40

50

前記複数の回路設計のうちの第1のものが非レジスタード入力を含み、

前記1つまたは複数のデータ・フロー・グラフ表現が前記複数の回路設計のうちの前記第1のものの第1のパスにおける信号遅延の少なくとも一部分を表す演算ノードの表現を含んでおり、前記第1のパスがレジスタを含んでおらず、非レジスタード入力に接続される

請求項76に記載のデータ処理システム。

【請求項78】

前記演算ノードが前記第1のパスにおける前記信号遅延を表し、前記第1のパスにおける前記信号遅延が、レジスタを含んでおらず、かつ前記複数の回路設計のうちの前記第1のものにおける前記非レジスタード入力とレジスタとの間を接続する任意のパスにおける信号遅延以上である請求項77に記載のデータ処理システム。

10

【請求項79】

前記複数の回路設計のうちの第1のものが非レジスタード出力を含み、

前記1つまたは複数のデータ・フロー・グラフ表現が前記複数の回路設計のうちの前記第1のものの第1のパスにおける信号遅延の少なくとも一部分を表す演算ノードの表現を含んでおり、前記第1のパスがレジスタを含んでおらず、非レジスタード出力に接続される

請求項76に記載のデータ処理システム。

【請求項80】

前記演算ノードが前記第1のパスにおける前記信号遅延を表し、前記第1のパスにおける前記信号遅延が、レジスタを含んでおらず、かつ前記複数の回路設計のうちの前記第1のものにおける前記非レジスタード出力とレジスタとの間を接続する任意のパスにおける信号遅延以上である請求項79に記載のデータ処理システム。

20

【請求項81】

前記演算ノードが前記第1のパスにおける前記信号遅延を表し、前記第1のパスが非レジスタード入力に接続されており、前記第1のパスにおける前記信号遅延が、レジスタを含んでおらず、かつ前記複数の回路設計のうちの前記第1のものにおける前記非レジスタード入力と出力とを接続する任意のパスにおける信号遅延以上である請求項79に記載のデータ処理システム。

30

【請求項82】

前記1つまたは複数のデータ・フロー・グラフ表現のうちの第1のグラフ表現が前記複数の回路設計のうちの第1のものに対応しており、前記第1のグラフ表現が、前記複数の回路設計のうちの前記第1のものにおけるレジスタから始まり、前記複数の回路設計のうちの前記第1のものにおけるレジスタで終わるすべての第1のパスを表すエッジを含んでおり、前記エッジにおける遅延が前記複数の回路設計のうちの前記第1のもののレイテンシを表す請求項76に記載のデータ処理システム。

40

【請求項83】

前記エッジが第1のノードと第2のノードとを接続して前記第1のパスを表し、前記第1のノードと前記第2のノードが信号遅延をもたらさない請求項82に記載のデータ処理システム。

40

【請求項84】

回路を設計するデータ処理システムであって、

前記回路の設計の目的のクロックを選択する手段と、

前記目的のクロックに基づいて前記回路の一部分のデータ・フロー・グラフの表現を決定する手段と、

前記データ・フロー・グラフの前記表現を使用して前記目的のクロックの前記設計をリタイミングする手段と

を含むデータ処理システム。

【請求項85】

前記データ・フロー・グラフの前記表現を決定する前記手段が

50

前記データ・フロー・グラフのエッジにおいて必要な追加の遅延数を決定する手段を含む請求項84に記載のデータ処理システム。

【請求項86】

前記エッジが前記データ・フロー・グラフの第1のノードと第2のノードを接続し、前記エッジによって接続されている前記第1と第2のノードが、前記回路の前記一部分のレジスタから始まり、前記回路の前記一部分のレジスタで終わるパスを表す請求項85に記載のデータ処理システム。

【請求項87】

前記第1のノードが、レジスタを含んでおらず、かつ前記回路の前記一部分の第1の入力と前記回路の前記一部分のレジスタの入力との間にある任意のパスにおける信号遅延以上である信号遅延を表すノードに接続される請求項86に記載のデータ処理システム。

10

【請求項88】

前記第2のノードが、レジスタを含んでおらず、かつ前記回路の前記一部分の第1の出力と前記回路の前記一部分のレジスタの出力との間にある任意のパスにおける信号遅延以上である信号遅延を表すノードに接続される請求項86に記載のデータ処理システム。

【請求項89】

前記データ・フロー・グラフが、レジスタを含んでおらず、かつ前記回路の前記一部分の第1の入力を前記回路の前記一部分の第1の出力に接続する任意のパスにおける信号遅延以上である信号遅延を表すノードを含む請求項86に記載のデータ処理システム。

【請求項90】

前記追加の遅延数を決定する前記手段が

前記目的のクロックに従って前記回路の前記一部分に対してリタイミングを実行する手段

20

を含む請求項85に記載のデータ処理システム。

【請求項91】

前記追加の遅延数を決定する前記手段が

追加の遅延数を前記回路の前記一部分の許容できるクロックに相關させる設計データから前記追加の遅延数を決定する手段

を含む請求項85に記載のデータ処理システム。

30

【請求項92】

回路を設計するデータ処理システムであって、

前記回路の設計の目的のクロックを選択する手段と、

前記目的のクロックの前記回路の前記設計の一部分をリタイミングして第1の結果を生成する手段と、

前記第1の結果を使用して前記目的のクロックの前記設計をリタイミングする手段とを含むデータ処理システム。

【請求項93】

前記回路の前記設計の前記一部分をリタイミングする前記手段が

前記設計の前記一部分が前記目的のクロックで稼動することができるよう、いくつかのパイプライン・レジスタ・セットを前記設計の前記一部分に追加する手段

を含む請求項92に記載のデータ処理システム。

40

【請求項94】

前記回路の前記設計の前記一部分をリタイミングする前記手段が

前記設計の前記一部分が前記目的のクロックで稼動することができるよう、いくつかのパイプライン・レジスタ・セットを前記設計の前記一部分から削除する手段

を含む請求項92に記載のデータ処理システム。

【請求項95】

前記目的のクロックの前記設計をリタイミングする前記手段が

接続を使用して、リタイミングされる前記設計の前記一部分のレジスタ間のすべてのパスを表す手段であって、前記接続が前記設計の前記一部分に追加された前記いくつかのパ

50

イプライン・レジスタ・セットを表すいくつかの追加の遅延を必要とする手段を含む請求項 9 3 に記載のデータ処理システム。

【請求項 9 6】

前記接続が第 1 のノードと第 2 のノードとを接続し、前記第 1 のノードと第 2 のノードが信号遅延をもたらさない請求項 9 5 に記載のデータ処理システム。

【請求項 9 7】

前記目的のクロックの前記設計をリタイミングする前記手段が

10

入力演算ノードを使用して、レジスタを含んでおらず、かつ前記設計の前記一部分の第 1 の入力と前記設計の前記一部分のレジスタとを接続するすべてのパスに沿った最大信号遅延を表す手段であって、前記入力演算ノードが遅延無しの接続を介して前記第 1 のノードに接続される手段

をさらに含む請求項 9 6 に記載のデータ処理システム。

【請求項 9 8】

前記目的のクロックの前記設計をリタイミングする前記手段が

出力演算ノードを使用して、レジスタを含んでおらず、かつ前記設計の前記一部分の第 1 の出力と前記設計の前記一部分のレジスタとを接続するすべてのパスに沿った最大信号遅延を表す手段であって、前記出力演算ノードが遅延無しの接続を介して前記第 2 のノードに接続される手段

をさらに含む請求項 9 7 に記載のデータ処理システム。

【請求項 9 9】

前記目的のクロックの前記設計をリタイミングする前記手段が

20

第 1 の演算ノードを使用して、レジスタを含んでおらず、かつ前記設計の前記一部分の第 2 の入力と前記設計の前記一部分の第 2 の出力とを接続するすべてのパスに沿った最大信号遅延を表す手段

をさらに含む請求項 9 8 に記載のデータ処理システム。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、回路設計に関し、より詳細には回路設計における回路モデルのタイミング動作のモデリングに関する。

30

【背景技術】

【0 0 0 2】

デジタル回路の設計（例えば超大規模集積回路（VLSI）技術の規模など）では、設計者はコンピュータ支援技術を使用することが多い。複雑なデジタル回路の設計やシミュレーションを助けるためにデジタル回路を記述するハードウェア記述言語（HDL）などの標準言語が開発されている。VHDLやVerilogなどいくつかのハードウェア記述言語は、業界標準として発展している。VHDLとVerilogは、抽象データ型を使用して、ゲート・レベル、レジスタ転送レベル（RTL）、または動作レベルでハードウェア・モデルを定義する汎用ハードウェア記述言語である。デバイス技術の継続的な進歩に伴い、HDLをより新しいデバイスや設計様式とともに使用できるようにするための様々な製品設計ツールが開発されている。

40

【0 0 0 3】

HDLコードによる集積回路の設計の際、コードは、まず書き込まれ、次にHDLコンパイラによってコンパイルされる。HDLソース・コードは、何らかのレベルで回路素子を記述し、コンパイラは、このコンパイルからRTLネットリストを生成する。RTLネットリストは、一般に、フィールド・プログラマブル・ゲート・アレイ（FPGA）や特定用途向け集積回路（ASIC）など、特定のベンダーの集積回路の技術／アーキテクチャに依存しないという点で、技術非依存型ネットリストである。RTLネットリストは、（動作表現に対して）回路素子の概略図に対応している。次いで、技術非依存型RTLネットリストから、ベンダーの技術／アーキテクチャでの回路の作成に使用できる技術固有

50

のネットリストに変換されるように、マッピング・オペレーションが行われる。FPGAベンダーが異なる技術／アーキテクチャを使用して集積回路内に論理回路を実装することはよく知られている。したがって、技術非依存型RTLネットリストがマッピングされて、特定のベンダーの技術／アーキテクチャに固有のネットリストが作成される。

#### 【0004】

このプロセスにおいてしばしば望ましい1つのオペレーションは、特定の集積回路のレイアウトを計画し、タイミング問題を制御し、集積回路の領域間の相互接続を管理することである。これは、時として「フロア・プランニング」と呼ばれることがある。一般的のフロア・プランニング・オペレーションは、集積回路の回路エリアを時として「ブロック」と呼ばれる領域に分割し、ロジックをブロック内に存在するよう割り当てる。これらの領域は、四角形でも四角形でなくてもよい。このオペレーションには、ロジックの位置の推定誤差が集積回路のサイズからブロックのサイズに低減される（タイミング推定値(timing estimates)の誤差を低減する傾向がある）、また、配置配線が非常に大きい問題からより簡単な一連の問題に軽減されているので一般により早く稼動するという2つの効果がある。

#### 【0005】

リタイミング・アルゴリズムは、回路の設計を最適化するために使用されている。一般に、同期回路は、信号が、指定された数のブロック・サイクル以内（例えば1クロック周期内など）に、組み合わせバス、すなわちメモリ・セル、フリップフロップ、遅延素子などのレジスタを含まないバスに沿って、あるレジスタから別のレジスタに伝わるときのみ、適切に動作する。したがって、レジスタ間のバスにおける最大信号遅延（例えばバス上の組み合わせ演算素子の演算時間や配線遅延のためなど）は、回路が適切に働くことができる最小クロック周期を決定する。レジスタは、回路のバスに配置または再配置されて、バスにおける最大信号遅延を低減し、回路のクロック周期を低減させる。一般的リタイミング・アルゴリズムを使用して、回路のタイミング・モデルに基づいて回路内のレジスタのうちのいくつかを分配し直して、クロック周期を最低限に抑えることができる。

#### 【0006】

一般に、回路のタイミング・モデルは、組み合わせ演算ユニットと、遅延（レジスタによるなど）と、回路を構成する相互接続とのタイミング・モデルをひとまとめにすることによって取得される。相互接続遅延は、モデル化するのが難しく、したがってしばしば無視される。1つまたは複数の回路モジュールを含む回路システムの一般的タイミング・モデルは、モジュールの組み合わせ演算ユニットのタイミング・モデルの集約から生成される。

#### 【0007】

一般的リタイミング・アルゴリズム（例えば「VLSI Digital Signal Processing Systems: Design and Implementation」by Keshab K. Parhi, pp. 91-118, Wiley-Interscience, 1999に記載）は、データ・フロー・グラフに基づいて策定される。データ・フロー・グラフは、組み合わせ演算ユニットを表すノードと、それらを相互接続するエッジから成る。遅延（レジスタなど）は、エッジの重さとして表される。各ノードには、それに関連付けられている実行時間がある。

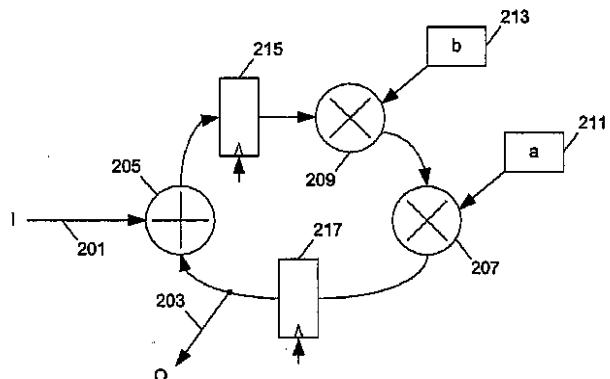

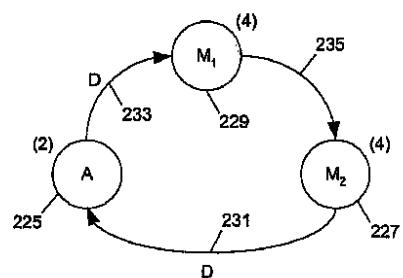

#### 【0008】

例えば、図2～3は、リタイミング用のデータ・フロー・グラフを構築する従来技術の方法を示している。図2の組み合わせ演算ユニット（加算器205、乗算器207、209）は、演算ノード（例えば図3のノード225、227、229）として表される。組み合わせ演算ユニットでの実行時間は、ノードの演算時間によって表される。例えば、ノード225は2nsの演算時間を有しており、この演算時間は加算器205によって必要とされ、ノード227、229のそれぞれは4nsの演算時間を有しており、この演算時間は1つの乗算器（例えば209または207）によって必要とされる。エッジ231は、乗算器207と加算器205との間の接続を表す。エッジ231は、1の重さを有し、

10

20

30

40

40

50

この重さはレジスタ 217（またはレジスタ 217による1クロック・サイクルのレイテンシ）を表す。同様に、エッジ 233は、レジスタ 215を表す1遅延を有する。エッジ 235は、乗算器 209と 207との間の接続を表し、エッジ 235に関連付けられている遅延はない。

#### 【0009】

データ・フロー・グラフにおけるクリティカル・パスとは、ゼロ遅延エッジ（組み合わせパス）を含むすべてのパスの中で最長の演算時間を有するパスである。例えば、図3で、ノード 229からノード 227へのパスは、ゼロ遅延を有するエッジ 235を含み、ノード 229からノード 227へのパスは、演算時間が最も長くかかる（例えば 8 ns など）。そのうちの 4 ns はノード 229、4 ns はノード 227）。したがって、図2の回路の最小クロック周期は 8 ns である。図3で、エッジ 233における遅延をエッジ 235に移動し、したがってクリティカル・パスがノード 225と 229との間のパスになり、演算時間がわずか 6 ns で済むようにすることができる。したがって、遅延をエッジ 233からエッジ 235に移動させることは、レジスタ 215を加算器 205と乗算器 209との間から乗算器 209と 207との間に移動させることによって実施することができ、これによって、変更された（リタイミングされた）回路は、低減されたクロック周期 6 ns で動作することができる。

#### 【0010】

回路モジュールのタイミング・モデルを取得するための従来の手法は、モジュールを実際に構成するレジスタと組み合わせ演算素子とにモジュールを分解し、1つのノードを各組み合わせ演算素子に割り当てることである。一般に、ある設計における回路モジュールは、モジュールにおける組み合わせユニットと、それを接続するネットに対応する1組のノードとエッジに変換される。言い換えれば、各ハードウェア・モジュールのタイミング・モデルは、一般に、組み合わせ演算ユニットと、遅延と、ハードウェア・モジュールを構成する相互接続とのタイミング・モデルをひとまとめにすることによって構築される。特定のハードウェア・モジュールの変換で使用されるノードとエッジとの組の集約が、事実上そのハードウェア・モジュールのタイミング・モデル（データ・フロー・グラフ）となる。

#### 【0011】

リタイミング・アルゴリズムは、カットセットのリタイミングとパイプライニングを含む。さらに、データ・フロー・グラフを使用したクロック周期最小化のためのリタイミング・アルゴリズムが存在する。カットセットのリタイミング、パイプライニング、クロック周期最小化のためのリタイミングについてのこれ以上の詳細については、文献（“VLSI Digital Signal Processing Systems: Design and Implementation” by Keshab K. Parhi, pp. 97 - 106, Wiley-Interscience, 1999など）に記載されている。

#### 【発明の開示】

##### 【課題を解決するための手段】

#### 【0012】

ここでは、回路の階層的なリタイミングを行うための方法と装置について説明する。このセクションでは、本発明の一部の実施態様の要約について述べる。

#### 【0013】

本発明の少なくとも1つの実施態様では、（例えばモジュール・レベルでのリタイミングを介して）異なる複数の最小クロック周期を有するように異なる複数のレイテンシを備える回路のモジュールが設計される。一例では、モジュールの配置配線の後、詳細なタイミング分析から最小クロック周期が決定され、モジュールを含む回路のリタイミングの際に、回路の目的のクロック周期、および、レイテンシと最小クロック周期との間の相関に基づいてモジュールのデータ・フロー・グラフ表現が構築される。本発明の少なくとも1つの実施態様では、階層的なリタイミングが実行される。これは、回路の一部分がリタイ

10

20

30

40

50

ミングされて（例えば異なるレイテンシについての）結果が生成され、その結果が目的のクロック周期に基づく回路全体のリタイミングに選択的に使用されるものである。

#### 【0014】

本発明の一実施態様では、回路モジュールを設計する方法は、異なる複数のレイテンシを備えるモジュールに対応する、モジュールの複数の回路設計を生成するステップと、複数の回路設計の実行可能なクロック周期を表すように、複数の回路設計の複数の許容できるクロック（例えば最小クロック周期など）を決定するステップと、複数の許容できるクロックを異なる複数のレイテンシに関連付けるための設計データを生成するステップとを含む。一例では、複数の回路設計のそれぞれを生成するために配置配線が実行され、設計レイアウトに基づく詳細なタイミング分析から、許容できるクロックが決定される。一例では、複数の回路設計のうちの第1のものが生成された後、パイプライン・レジスタ・セットが複数の回路設計のうちの第1のものに挿入されて、複数の回路設計のうちの第2のものが生成され、さらに、複数の回路設計の第2のものを生成するためにリタイミングが実行される。一例では、複数の回路設計のうちの第1のものと複数の回路設計のうちの第2のものは（例えば異なる処理ロジックまたは異なるロジック処理要素を有するなど）異なるアーキテクチャを有する。一例では、設計データは、さらに、複数の許容できるクロックに基づいて、異なる複数のレイテンシを、複数の回路設計の1つまたは複数のデータ・フロー・グラフ表現に関連付ける。一例では、モジュールの1つまたは複数のデータ・フロー・グラフ表現は、複数の許容できるクロックに基づいて、複数の回路設計を表すように生成される。例えば、複数の回路設計のうちの第1のものが非レジスタード入力(non-registered input)を含んでいる場合、1つまたは複数のデータ・フロー・グラフ表現は、複数の回路設計のうちの第1のものの第1のパスにおける信号遅延の少なくとも一部分を表す演算ノードの表現を含んでおり、この場合第1のパスは、レジスタを含んでおらず、非レジスタード入力に接続されており、例えば、演算ノードは、レジスタを含んでおらず、複数の回路設計のうちの第1のものの非レジスタード入力とレジスタとの間を接続する任意のパスにおける信号遅延以上である第1のパスにおける信号遅延を表す。同様に、例えば、複数の回路設計のうちの第1のものが非レジスタード出力を含んでいる場合、1つまたは複数のデータ・フロー・グラフ表現は、複数の回路設計のうちの第1のものの第1のパスにおける信号遅延の少なくとも一部分を表す演算ノードの表現を含んでおり、この場合第1のパスは、レジスタを含んでおらず、非レジスタード出力に接続されており、例えば、演算ノードは、レジスタを含んでおらず、複数の回路設計のうちの第1のものにおける非レジスタード入力と出力との間を接続する任意のパスにおける信号遅延以上である第1のパスにおける信号遅延を表す。また、演算ノードは、レジスタを含んでおらず、複数の回路設計のうちの第1のものにおける非レジスタード入力と出力との間を接続する任意のパスにおける信号遅延以上である第1のパスにおける信号遅延を表すために使用することもできる。一例では、1つまたは複数のデータ・フロー・グラフ表現のうちの第1のグラフ表現は、複数の回路設計のうちの第1のものに対応しており、第1のグラフ表現は、複数の回路設計のうちの第1のもののレジスタから始まり、第1のもののレジスタで終わるすべての第1のパスを表すエッジを含んでおり、そのエッジにおける遅延は、複数の回路設計のうちの第1のもののレイテンシに関連する。一例では、エッジは、第1のノードと第2のノードとを接続して第1のパスを表す。この場合第1のノードと第2のノードは信号遅延をもたらさない。

#### 【0015】

本発明の一実施態様では、回路を設計する方法は、回路の設計の目的のクロックを選択するステップと、目的のクロックに基づいて、回路の一部分のデータ・フロー・グラフの表現を決定するステップと、データ・フロー・グラフの表現を使用して目的のクロックの設計をリタイミングするステップとを含む。一例では、データ・フロー・グラフの表現を決定する際に、目的のクロックに基づいて、データ・フロー・グラフのエッジにおいて必要な追加の遅延数が決定される。一例では、エッジは、データ・フロー・グラフの第1のノードと第2のノードとを接続し、エッジによって接続されている第1と第2のノードは

10

20

30

40

50

、回路の一部分のレジスタから始まり、回路の一部分のレジスタで終了するパスを表す。第1のノードは、レジスタを含んでおらず、回路の一部分の第1の入力と回路の一部分のレジスタの入力との間にある任意のパスにおける信号遅延以上である信号遅延を表すノードに接続され、第2のノードは、レジスタを含んでおらず、回路の一部分の第1の出力と回路の一部分のレジスタの出力との間にある任意のパスにおける信号遅延以上である信号遅延を表すノードに接続され、データ・フロー・グラフは、レジスタを含んでおらず、回路の一部分の1つの入力を回路の一部分の1つの出力に接続する任意のパスにおける信号遅延以上である信号遅延を表すノードを含む。一例では、追加の遅延数を決定する際に、目的のクロックに従って回路の一部分に対しリタイミングが実行される。一例では、追加の遅延数は、追加の遅延数を回路の一部分の許容できるクロックに相關させる設計データから決定される。

10

#### 【0016】

本発明の一実施態様では、回路を設計する方法は、回路の設計の目的のクロックを選択するステップと、目的のクロックの回路の設計の一部分をリタイミングして第1の結果を生成するステップと、第1の結果を使用して目的のクロックの設計をリタイミングするステップとを含む。一例では、回路の設計の一部分をリタイミングするステップは、設計の一部分が目的のクロックで稼働できるように、いくつかのパイプライン・レジスタ・セットを設計の一部分に追加する（または削除する）ステップを含み、目的のクロックの設計をリタイミングするステップは、接続を使用して、リタイミングされる設計の一部分のレジスタ間のすべてのパスを表すステップを含む。この場合接続は、設計の一部分に追加されたパイプライン・レジスタ・セットの数を表すいくつかの追加の遅延を必要とする。一例では、接続は、第1のノードと第2のノードとを接続する。この場合第1のノードと第2のノードは信号遅延をもたらさない。一例では、目的のクロックの設計をリタイミングするステップは、入力演算ノードを使用して、レジスタを含んでおらず、設計の一部分の第1の入力と設計の一部分のレジスタとを接続するすべてのパスに沿った最大信号遅延を表すステップであって、入力演算ノードが遅延のない接続を介して第1のノードに接続されるステップと、出力演算ノードを使用して、レジスタを含んでおらず、設計の一部分の第1の出力と設計の一部分のレジスタとを接続するすべてのパスに沿った最大信号遅延を表すステップであって、出力演算ノードが遅延のない接続を介して第2のノードに接続されるステップと、第1の演算ノードを使用して、レジスタを含んでおらず、設計の一部分の第2の入力と設計の一部分の第2の出力とを接続するすべてのパスに沿った最大信号遅延を表すステップとをさらに含む。

20

30

#### 【0017】

本発明は、これらの方法を実行するデータ処理システムや、データ処理システム上で実行されるとシステムにこれらの方法を実行させるコンピュータ可読媒体を含めて、これらの方法を実行する方法と装置を含む。

#### 【0018】

本発明の他の特徴は、添付の図面や以下の詳細な説明から明らかになるであろう。

#### 【発明を実施するための最良の形態】

#### 【0019】

本発明は、例示として示されており、添付の図面に限定されるものではない。図中、同様の参照番号は同様の要素を示す。

40

#### 【0020】

以下の説明と図面は、本発明の実例であり、本発明を限定するものと解釈されるべきではない。本発明を完全に理解できるようにするために、特定の詳細が多数記述されている。しかし、いくつかの場合、本発明の説明を不明瞭にするのを避けるために、よく知られている詳細、または従来の詳細は記述していない。本開示において一実施形態への言及は、必ずしも同じ実施形態を指すのではなく、こうした言及は少なくとも1つを意味する。

#### 【0021】

本発明の少なくとも1つの実施形態は、回路の一部分（例えば回路モジュールまたは回路

50

ブロック)がクロック周期最小化のためにリタイミングされ、回路の一部分のリタイミングの結果に基づいて回路全体がリタイミングされる階層的方法を使用して回路設計のリタイミングを行おうとするものである。本発明の一実施形態では、モジュールのパラメトリック設計を取得してモジュールのタイミング・モデルを確立し、タイミング・モデルを使用して回路全体のリタイミングを行う。

#### 【0022】

本説明および特許請求の範囲では、レジスタとは、一般に順次素子(遅延素子、メモリ・セル、フリップフロップなど)を指す。レジスタは、回路のクロックとの同期の際に出力することができるよう、入力信号をサンプリングし、保持(格納)する。さらに、データ・フロー・グラフのエッジにおける1遅延は、一般に対応するバス上のレジスタの存在によってもたらされるレイテンシの単位を表すことを理解されたい。しかし、レイテンシの単位は、メモリ・セルを読み取るための様々な制御信号など、他の手段を介して実装することもできる。

#### 【0023】

本発明の方法の多くは、従来の汎用コンピュータ・システムなど、デジタル処理システムで実行することができる。1つの機能のみを実行するように設計され、またはプログラムされている専用コンピュータを使用することもできる。

#### 【0024】

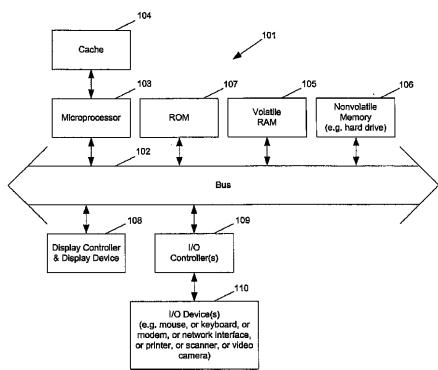

図1は、本発明とともに使用することができる一般のコンピュータ・システムの一例を示している。図1は、コンピュータ・システムの様々な構成要素を示しているが、こうした詳細は本発明と密接な関係はないので、構成要素を相互接続する任意のアーキテクチャまたは方法を表すためのものではないことに留意されたい。また、構成要素が少ない、または場合によっては多いネットワーク・コンピュータや他のデータ処理システムも本発明とともに使用できることを理解されたい。図1のコンピュータ・システムは、例えば、Sunワークステーション、あるいはWindows(登録商標)オペレーティング・システムまたはApple Macintoshコンピュータを稼働させるパーソナル・コンピュータ(PC)とすることができる。

#### 【0025】

図1に示すように、データ処理システムの形態をしているコンピュータ・システム101はバス102を含んでいる。バスは、マイクロプロセッサ103、ROM107、揮発性RAM105、不揮発性メモリ106に結合されている。マイクロプロセッサ103は、図1の例に示すように、キャッシュ・メモリ104に結合されている。バス102は、これらの様々な構成要素をいっしょに相互接続し、また、これらの構成要素103、107、105、106は、表示コントローラと表示デバイス108に接続され、かつ、マウス、キーボード、モデム、ネットワーク・インターフェイス、プリンタ、スキャナ、ビデオ・カメラ、当分野でよく知られている他のデバイスなどの入力/出力(I/O)デバイスなどの周辺デバイスに相互接続される。一般に、入力/出力デバイス110は、入力/出力コントローラ109を介してシステムに結合される。揮発性RAM105は、一般に、メモリ内のデータを最新の状態したり維持したりするために連続的に電力を必要とする動的RAM(DRAM)として実装される。不揮発性メモリ106は、一般に磁気ハード・ドライブ、磁気光ドライブ、光ドライブ、DVD RAM、または電力がシステムから取り除かれた後もデータを維持する他のタイプのメモリ・システムである。また、一般に、不揮発性メモリは、ランダム・アクセス・メモリであるが、これは必須ではない。図1は、不揮発性メモリがデータ処理システムの構成要素の残りに直接結合されているローカル・デバイスであることを示しているが、本発明では、例えばモデムやEthernet(登録商標)インターフェイスなどのネットワーク・インターフェイスを介してデータ処理システムに結合されているネットワーク記憶デバイスなどのシステムから離れている不揮発性メモリを使用してもよいことを理解されたい。バス102は、当分野で知られている様々な様々なブリッジ、コントローラ、および/またはアダプタを介して互いに接続されている1つまたは複数のバスをも含む。一実施形態では、I/Oコントローラ109は

、 U S B 周辺装置を制御する U S B (ユニバーサル・シリアル・バス) アダプタ、および / または I E E E - 1 3 9 4 周辺装置を制御する I E E E - 1 3 9 4 バス・アダプタを含む。

【 0 0 2 6 】

本発明の形態を少なくとも一部にはソフトウェアに組み込むことができる事がこの説明から明らかである。つまり、技術は、R O M 1 0 7、揮発性R A M 1 0 5、不揮発性メモリ1 0 6、キャッシュ1 0 4、またはリモート記憶デバイスなどのメモリに含まれる命令のシーケンスを実行するマイクロプロセッサなどのプロセッサに応答してコンピュータ・システムまたは他のデータ処理システムで実行することができる。様々な実施形態では、配線回路を、本発明を実施するためのソフトウェア命令との組み合わせで使用することができる。したがって、技術は、ハードウェア回路とソフトウェアとの任意の特定の組み合わせに限定されるものではなく、また、データ処理システムによって実行される命令の任意の特定のソースに限定されるものでもない。さらに、説明を簡潔にするために、この説明を通じて、様々な機能およびオペレーションは、ソフトウェア・コードによって実行される、またはソフトウェア・コードによってもたらされるものとして説明される。しかし、こうした表現が意味することは、こうした機能はマイクロプロセッサ1 0 3などのプロセッサによるコードの実行から生まれるということであることを当業者は理解されよう。

【 0 0 2 7 】

機械可読媒体を使用して、データ処理システムによって実行されるとシステムに本発明の様々な方法を実行させるソフトウェアとデータを格納することができる。この実行可能ソフトウェアとデータは、図1に示すように、例えばR O M 1 0 7、揮発性R A M 1 0 5、不揮発性メモリ1 0 6、および / またはキャッシュ1 0 4を含む様々な場所に格納することができる。このソフトウェアおよび / またはデータの一部分は、これらの記憶デバイスのうちの任意のものに格納することができる。

【 0 0 2 8 】

したがって、機械可読媒体は、機械（コンピュータ、ネットワーク・デバイス、P D A、製造ツール、1組の1つまたは複数のプロセッサを備える任意のデバイスなど）によってアクセス可能な形式で情報を提供（すなわち格納および / または送信）する任意の機構を含む。例えば、機械可読媒体は、書き込み可能 / 書き込み禁止媒体（読み取り専用メモリ（R O M）、ランダム・アクセス・メモリ（R A M）、磁気ディスク記憶媒体、光記憶媒体、フラッシュ・メモリ・デバイスなど）、および電気、光、音響または他の形式の伝搬信号（搬送波、赤外線信号、デジタル信号など）などを含む。

【 0 0 2 9 】

回路の一般的タイミング・モデルは、組み合わせ演算素子のタイミング・モデルの集合である。組み合わせ演算素子のタイミング・モデルは回路のクロック周期に依存しない。従来の方法は、回路モジュールの組み合わせ演算素子のタイミング・モデルを集約して、回路のクロック周期に依存しない回路のタイミング・モデルを生成する。

【 0 0 3 0 】

タイミング・モデルが組み合わせ演算素子のタイミング・モデルの集約から構築されるとき、結果として得られたデータ・フロー・グラフにおける組み合わせ演算素子を表すノードの数は非常に多い。また、この種のタイミング・モデルは不正確であることが多い。というのは、モジュール内相互接続遅延（配線遅延など）は一般に無視されるからである。また、組み合わせ演算素子のタイミング・モデルは遅延の実装前推定値を使用するため、不正確である。

【 0 0 3 1 】

一般的なリタイミング・アルゴリズムは、O ( n <sup>3</sup> ) の複雑さを有している。この場合、nは、従来の方法における組み合わせ演算素子の数に対応するデータ・フロー・グラフでのノードの数である。したがって、ゲート・レベルのタイミング・モデルの使用によって、システム・レベルのリタイミングでの演算の法外な複雑さがもたらされることが多く、

一方で、モジュール内相互接続遅延などが無視されるため、また実装前推定値を使用するため、依然として回路のタイミング動作の不正確なモデルが生み出される可能性がある。

### 【0032】

本発明の一実施形態では、事前に設計されたハードウェア・モジュールの結合によってシステム・レベルの回路を生成し、リタイミングを改善し、加速するために、タイミング・モデルをこうしたモジュールごとに構成する。本発明の実施形態によるタイミング・モデルは、リタイミングの目的でモジュールのタイミング動作を正確に表しながら、データ・フロー・グラフで使用されるノードの数を最低限に抑える。所与のハードウェア・モジュールの簡単だが有効なタイミング・モデルがシステムチックな方法で構築される。一般に、回路（サブ回路、または回路の1ブロックなど）の一部分を、類似のやり方で回路モジュールとして扱うこともでき、その簡略化されたタイミング・モデルを、本発明の実施形態に従って構成することができる。したがって、クロック周期最小化のための回路のリタイミングは、本発明の実施形態に従って、階層的なやり方で実行することができる。従来の手法では、回路システムのクロック周期最小化は、予め定められている設計とロジック（例えば予め定められているレイテンシおよび予め定められている最大遅延など）をそれぞれ有する組み合わせ演算素子に対応するノードを備えるデータ・フロー・グラフを使用する。本発明の少なくとも1つの実施形態による階層的な手法では、クロック周期最小化は、回路システムの1つまたは複数のモジュール（またはサブ回路）のタイミング・モデルに基づいて実行され、モジュールの各タイミング・モデルは、複数の設計パラメータ（様々なレイテンシ、様々な設計アーキテクチャ、モジュールの様々な最小クロック周期など）を備えるモジュールのクロック周期最小化から取得され、モジュールのタイミング・モデルは、複数の設計パラメータを反映する。一実施形態では、モジュールのタイミング・モデルにおける少なくとも1つのパラメータ（例えば最小レイテンシ）は、回路システムの目的のクロック周期に従って決定される。以下で、本発明の実施形態の詳細についてさらに説明する。

### 【0033】

一部のハードウェア・モジュール（FIRフィルタなど）とサブ回路は一般に、レイテンシを速度と交換することができる。言い換えれば、レジスタをモジュールに「投入」することによってハードウェア・モジュールを加速させ、クロック周期を低減させることができる。

### 【0034】

本発明の一実施形態では、ハードウェア・モジュールのタイミング・モデルは、モデルの詳細な実装からデータを使用して構築される。このデータは、モジュールに供給するレジスタの数を増やしていく、ハードウェア・モジュールをリタイミング（および最適化）し、新しいレジスタが追加されるとモジュール内のクリティカル・パスを検出してモジュールの最小クロック周期を決定することによって取得される。本発明の一実施形態では、モジュールの最小クロック周期は、（例えば配置配線後のタイミング分析を使用して）詳細な設計レイアウトから取得される。

### 【0035】

出力設計のクロック速度は、例えばクロック周期最小化の既知のリタイミング・アルゴリズムを適用することによって最大化することができる（“VLSI Digital Signal Processing Systems: Design and Implementation” by Keshab K. Parhi, pp. 100-106, Wiley-Interscience, 1999）。これらのリタイミング・アルゴリズムは、データ・フロー・グラフ上で策定される。ハードウェア・モジュールは、しばしばレジスタやメモリを含んでおり、単一のノードとして直接適しない。したがって、これらは、そのタイミング動作を十分に表すように、ノードとエッジとの組み合わせに変換される。ノードとエッジが多すぎて最適化アルゴリズムに負担をかけることがないようにするために、本発明の一実施形態による変換／モデリングは、ノードとエッジをできるだけ少なくし、非常に簡単だが十分なタイミング・モデルを提供する。以下で、ハードウェ

10

20

30

40

50

ア・モジュール設計からノードとエッジとの組み合わせにシステムチックに変換するための方法を示す詳細な例について説明する。

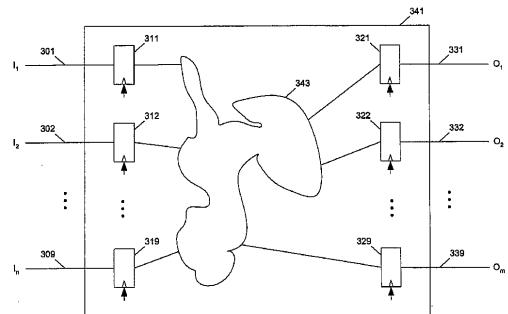

【0036】

図4～図5は、本発明の一実施形態によるレジスタードI/Oを備える回路モジュールのデータ・フロー・グラフを構築する例を示す図である。図4は、n個のレジスタード入力とm個のレジスタード出力を備えるハードウェア・モジュールを示しており、入力 $I_1$  (301)、 $I_2$  (302)、...、 $I_n$  (309)は、それぞれレジスタ311、312、...、319の直接入力であり、出力 $O_1$  (331)、 $O_2$  (332)、...、 $O_m$  (339)は、レジスタ321、322、...、329からの直接出力である。ロジック343は、モジュール341の入力301～309から出力331～339を算出するためのロジック素子のネットワークを表す。追加のi組のパイプライン・レジスタが（例えは既知の任意のアルゴリズムを使用してパイプラインニングを行う、または設計者によりレジスタを挿入する、またはモジュールの変更された仕様に従って設計者によりモジュールの代替の設計を使用するなど）、ハードウェア・モジュールに「投入」されているとき、 $c_i$ は、モジュール内のクリティカル・パスに沿った遅延を示すと仮定する。1組のパイプライン・レジスタは、モジュールの正方向送りカットセットにある1組のレジスタである。従来のパイプラインニング・アルゴリズムを使用して、1組または複数組のパイプライン・レジスタを挿入することができる。値 $\{c_0, c_1, \dots, c_L\}$ は、任意の既知の方法によって算出することができ、Lは、挿入されたパイプライン・レジスタの組の最大数である。パイプライン・レジスタが挿入された後でクリティカル・パス遅延を最低限に抑えるためにリタイミングまたは最適化が行われるため、一般に $c_0 > c_1 > \dots > c_L$ であると理解されたい。本発明の一実施形態では、クリティカル・パスに沿った遅延は、モジュールが配置され、配線された後でタイミング分析から算出することができる。しかし、遅延は、合成ツールの一般的な方法を使用して推定することもできるが、こうした遅延推定は、一般に、配置配線後のタイミング分析から取得されるものほど正確ではない。本発明の一実施形態によるタイミング・モデルは、1組の値 $\{c_0, c_1, \dots, c_L\}$ と図5に示すようなデータ・フロー・グラフ表現を含む。

【0037】

図5では、演算ノード $B_i$  (353)と $B_0$  (355)は、ゼロ演算時間有する。エッジ351では少なくとも1つの遅延があり、したがってエッジ351は、クリティカル・パスの一部ではあり得ない。この説明から、実行可能性条件(feasibility condition)がシステムの目的のクロックに従って適切に設定されており、エッジ351がクリティカル・パスの一部として含まれていない場合、エッジ351での遅延回数を任意の数に設定することは明らかである。パイプライン・レジスタの追加の組がないモジュールが回路で使用されており、回路のクロックが $\{c_0, c_1, \dots, c_L\}$ の値の組から $c_{(i-1)} > c > c_i$ となるような場合、少なくともi組のパイプライン・レジスタがモジュールに挿入される場合はモジュールが適切に働くことを理解されたい。したがって、図5のグラフの実行可能性の制約(feasibility constraint)では、エッジ351は、適切に働くようにするために、リタイミング・オペレーションに遅延をもうi個求めることを示している。こうした制約は、エッジから移動させることができる遅延の最大数を示すデータ・フロー・グラフの一般的なエッジに対する実行可能性の制約に非常に似ている。一般的なリタイミング・アルゴリズムを使用するには、 $c_{(i-1)} > c > c_i$ である場合、エッジ351の実行可能性の制約を、エッジから移動させることができる遅延の最大数が $-i$ であることをとして表すことができる。

【0038】

したがって、レジスタードI/Oを備えるモジュール(341)データ・フロー・グラフ表現は、2つのノード $B_i$  (353)、 $B_0$  (355)と、これらの2つのノードを接続するエッジ(351)を有する。これらのノードの演算時間は0である。エッジの実行可能性の制約は、回路のクロック周期に依存する。モジュールがより大きい設計の構成要素として使用されるとき、タイミング・モデルは、次のようにリタイミングに使用すること

10

20

30

40

50

ができる。

【0039】

1. 図5のデータ・フロー・グラフを使用して、設計全体のデータ・フロー・グラフを作成する際のモジュールを表す。

【0040】

2.  $c$  は設計全体を対象としたクロック周期と仮定する。 $(L + 1)$  組のパイプライン・レジスタをモジュールに追加することでは、 $c_L$  未満のモジュールの最小クロック周期を低減することができないことを前提として、 $c < c_L$  である場合、目的のクロック周期  $c$  は設計に適していないという結論に達する。

【0041】

3.  $c = c_L$  の場合、エッジ351の実行可能条件を決定する。例えば、 $i = 1, 2, \dots, L$  であるときに  $c_i < c < c_{(i-1)}$  の場合、エッジには追加の遅延が少なくとも  $i$  個必要である。 $c > c_0$  である場合、エッジには追加の遅延は必要ない。次いで既知のアルゴリズムを使用して、データ・フロー・グラフを使用した設計全体のリタイミングを行うことができる。例えば、“VLSI Digital Signal Processing Systems: Design and Implementation” by Keshab K. Parhi, pp. 91-118, Wiley-Interscience, 1999 のリタイミング・アルゴリズムでは、値  $r(B_i)$  と  $r(B_0)$  は、ノード  $B_i$ 、 $B_0$  について解かれ、したがってリタイミングした後、エッジ351での遅延数が  $w$  から  $w_r = w + r(B_0) - r(B_i)$  に変わる。したがって、エッジ351の実行可能条件は、 $c_i < c < c_{(i-1)}$  の場合は  $r(B_i) - r(B_0) < -i$ 、 $c > c_0$  の場合は  $r(B_i) - r(B_0) < 0$  となり、また  $c < c_L$  の場合は実行できない。

【0042】

4. 実行可能なリタイミングの解が見つかった場合、モジュールのインスタンス化の間に  $r(B_0) - r(B_i)$  組のパイプライン・レジスタをモジュールに追加する。

【0043】

図4、図5に示した例は、モジュールのすべての入力ライン（またはすべての出力ライン）を介して1組または複数組のパイプライン・レジスタがモジュールに「投入」される状況を示している。しかし、モジュールのクロック周期は、モジュールの入力（または出力）ラインのうちの1つまたは一部分を介してレジスタに「投入」することによって最低限に抑えることを理解されたい。例えば、図4のモジュールのクロック周期は、1つのレジスタを入力  $I_1$  (301) に追加し、変更されたモジュールをリタイミングしてクロック周期を最低限に抑えることによって低減させることができる。入力および/または出力ラインの一部分のリタイミングによるこうしたレイテンシの変化を反映させるために、レジスター・ド  $I/O$  を備えるモジュールのより全体的なデータ・フロー・グラフは、入力  $I_1, I_2, \dots, I_n$  と  $B_i$  との間、および出力  $O_1, O_2, \dots, O_m$  と  $B_0$  との間を接続するゼロ処理時間ノードを含むことができる。これらのゼロ処理時間ノードを  $B_i, B_0$  に接続する各エッジは、少なくとも1つの遅延を有しており、モジュールの対応する入力ラインまたは出力ラインを介して「投入」されたレジスタに対応する数を示すために、追加の遅延をいくつか必要とする。あるいは、同じ数のレジスタが入力ラインの一部分に「投入」されるとき、これらの入力ラインは、単一のゼロ処理時間ノードに接続される。これは次いで、システム全体のリタイミングの際に少なくとも同じ数の遅延を必要とするエッジを介してノード  $B_i$  に接続される。独立してリタイミングすることができる入力と出力の部分は、タイミング・モデル・トポロジを決定する。さらに独立性を許容することによって、結果的に複雑なモデルが得られる。さらに、同じ数のレジスタに「投入」するために、様々なモデルを構築することができる。この説明から、異なるレイテンシを備えるモジュールのリタイミングに基づいて、簡略化されたデータ・フロー・グラフの多くの変形を構築することができることを理解されたい。実行可能性条件は、回路システムの目的のクロックに従って設定される。

【0044】

10

20

30

40

50

モジュールの入力および／または出力がレジスタードではないとき、本発明の一実施形態によるリタイミング・モデルは、1) 非レジスタード入力ごとの入力から任意のモジュール内レジスタへの最大遅延、2) 非レジスタード出力ごとの任意のモジュール内レジスタから出力への最大遅延、3) 入力・出力対ごとの任意の純粋な組み合わせパスにおける最大入力対出力遅延を考慮に入れる。純粋な組み合わせパスは、クロックト・レジスタ(*locked register*)を含まないことを理解されたい。

#### 【0045】

これらの最大遅延値は、パイプライン・レジスタの追加の組の数に依存する可能性があり、したがって、実行可能性条件がそうであると同様に、目的のクロック周期に依存する可能性があることに留意されたい。

10

#### 【0046】

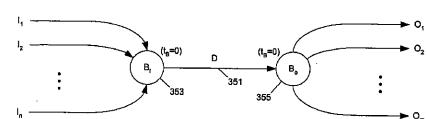

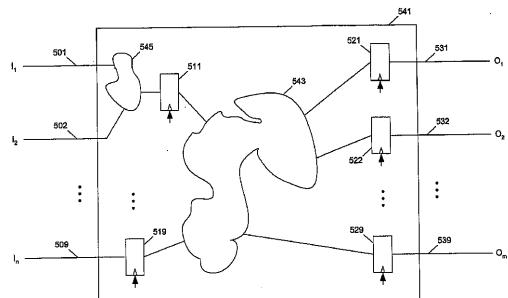

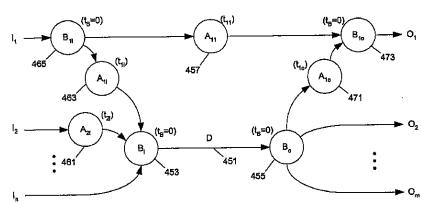

図6～図7は、本発明の一実施形態による非レジスタードI/Oを備える回路モジュールのデータ・フロー・グラフを構築する例を示す図である。図6では、入力401、402はレジスタードではなく、出力431はレジスタードではなく、入力401から出力431への少なくとも1つの純粋な組み合わせパスがある。ネットワーク445、447、449は、レジスタを有していない純粋な組み合わせネットワークを表す。

#### 【0047】

図7は、本発明の一実施形態によるモジュール441のデータ・フロー・グラフの一例を示している。図7では、ノード453、455とエッジ451は、モジュール441のレジスタード部分を表しており、これには、ネットワーク443を介したレジスタ411～419、およびレジスタ421～429の間のすべてのパスが含まれている。ノードA<sub>2i</sub>(461)は、入力I<sub>2</sub>(402)とレジスタ412との間のパスを表し、ノードA<sub>1i</sub>(463)は、入力I<sub>1</sub>(401)とレジスタ411との間のパスを表し、ノードA<sub>1o</sub>(471)は、レジスタ421と出力O<sub>1</sub>(431)との間のパスを表し、ノードA<sub>1i</sub>(457)は、ネット440を介した入力I<sub>1</sub>(401)と出力O<sub>1</sub>(431)との間のパスを表す。ノードB<sub>1i</sub>(465)は、ノードA<sub>1i</sub>(463)とA<sub>1i</sub>(457)の入力I<sub>1</sub>への適切な接続を容易にする。同様に、ノードB<sub>1o</sub>(473)は、ノードA<sub>1i</sub>(457)とA<sub>1o</sub>(471)を出力O<sub>1</sub>に接続する。図7では、ノードB<sub>1i</sub>、B<sub>1o</sub>、B<sub>1</sub>、B<sub>0</sub>は、接続を容易にするために使用されるため、ゼロの処理時間を有し、ノードA<sub>2i</sub>、A<sub>1i</sub>、A<sub>11</sub>、A<sub>1o</sub>は純粋な組み合わせパスを表すため、ノードによって表されるすべてのパスの中の最大遅延に等しい処理時間を有する。例えば、A<sub>1i</sub>(463)は、入力I<sub>1</sub>(401)からレジスタ411への最大遅延に等しい処理時間を有し、A<sub>2i</sub>(461)は、入力I<sub>2</sub>(402)からレジスタ412への最大遅延に等しい処理時間を有し、A<sub>1o</sub>(471)は、レジスタ421から出力O<sub>1</sub>(431)への最大遅延に等しい処理時間を有し、A<sub>1i</sub>(457)は、(ネットワーク440を介して)入力I<sub>1</sub>(401)から出力O<sub>1</sub>(431)への最大組み合わせ遅延に等しい処理時間を有する。

20

30

30

#### 【0048】

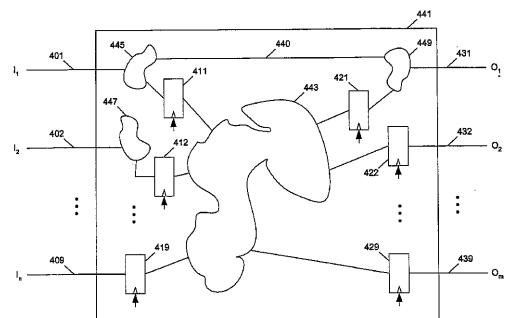

一般に、モジュールのレジスタへの入力は、モジュールの1つまたは複数の入力からの結果とすることを理解されたい。同様に、モジュールのレジスタからの出力は、モジュールの複数の出力に関与し得る。図8～図9は、本発明の一実施形態による非レジスタードI/Oを備える回路モジュールのデータ・フロー・グラフを構築する別の例を示す図である。図8では、入力I<sub>1</sub>(501)とI<sub>2</sub>(502)は、レジスタ511に至る1つまたは複数の純粋な組み合わせパスを有している。ネットワーク545は、レジスタを含んでいない。入力I<sub>1</sub>(501)とレジスタ511との間のすべての組み合わせパスは、図9のノードA<sub>1i</sub>(563)によって表されており、入力I<sub>2</sub>(502)とレジスタ511との間のすべての組み合わせパスは、図9のノードA<sub>2i</sub>(561)によって示されている。図9では、A<sub>1i</sub>(563) A<sub>2i</sub>(561)の処理時間は、組み合わせネットワーク545を介したそれぞれ入力I<sub>1</sub>(501)とI<sub>2</sub>(502)からレジスタ511への最大遅延である。

40

#### 【0049】

50

レジスタード I/O を備えるモジュールと同様に、非レジスタード I/O を備えるモジュールのクロック周期を、入力ラインと出力ラインの一部分を介してレジスタに「投入」することによって低減することもできる。入力ラインと出力ラインの一部分のこうしたレイテンシの追加は、レジスタード I/O を備えるモジュールについて上述したものに似た方法で、モジュールのレジスタード部分（例えばノード B<sub>i</sub> 533 と B<sub>o</sub> 555）を表すノードに接続されているエッジ上で指定することができる。

#### 【0050】

さらに、一般に、モジュールの入力は、異なるレジスタへの組み合わせパスを有していてもよく、モジュールの出力は、純粋な組み合わせパスを介して複数のレジスタからの関与を得ることができることを理解されたい。一般に、單一ノードを使用して、レジスタを有しておらず、モジュールの1つの入力からモジュールの任意のレジスタにそれぞれ向かうすべてのパスを表すことができ、單一ノードの演算時間は、ノードによって表されるすべてのパスの中の最大遅延である。同様に、單一ノードを使用して、レジスタを有しておらず、モジュールの任意のレジスタからモジュールの1つの出力にそれぞれ向かうすべてのパスを表すことができる。さらに、單一ノードを使用して、レジスタを有しておらず、モジュールの1つの入力からモジュールの1つの出力にそれぞれ向かうすべてのパスを表すことができる。

#### 【0051】

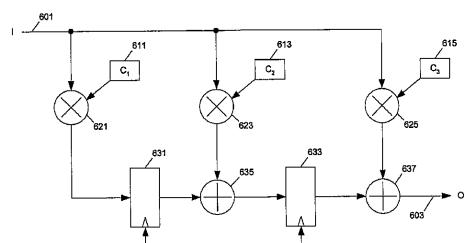

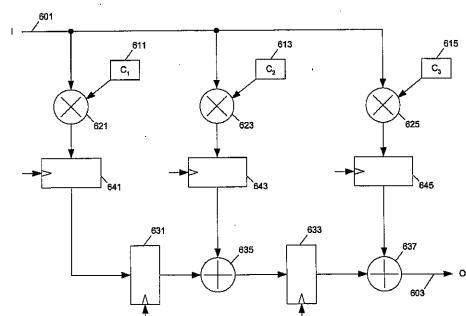

図10～16は、本発明の一実施形態による回路モジュールを設計する詳細な例を示す図である。

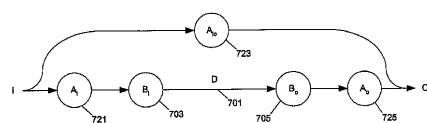

#### 【0052】

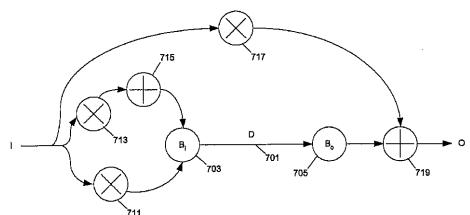

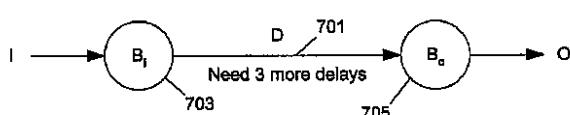

図10は、最小レイテンシを有するモジュールを示す図であり、図11は、本発明の一実施形態による図10のモジュールのデータ・フロー・グラフを示している。図11では、ノード B<sub>i</sub> (703)、エッジ701、ノード B<sub>o</sub> (705)は、図10のレジスタ間のすべてのパス（例えば加算器635を経由する図10のレジスタ631からレジスタ633まで）を表している。ノード711は乗算器621を表し、ノード713、715は乗算器623と加算器635を表し、ノード717、719は乗算器625と加算器637を表す。図11では、入力Iからノード703への2つのパスがあり、これは、図10の入力I (601)から内部レジスタ631、633のモジュールへの異なる組み合わせパスを表していることに留意されたい。これらのパスは、パスにおける最長遅延に等しい処理時間を有する單一ノードによって表すことができる。図12は、データ・フロー・グラフのこうした表現を示しており、ノード A<sub>i</sub> (721)は、図10における入力Iから任意の内部レジスタのモジュールへの最長の組み合わせ遅延を表している。一実施形態例では、データ・フロー・グラフの表現は、ノード（ロジックを表す）と、ノード間のリンクを含む。さらに、ノード723は、乗算器625と加算器637を通るパスにおける遅延である、任意の組み合わせパスを通る入力I (601)から出力O (603)への最長遅延を表す。ノード A<sub>o</sub> (725)は、加算器637を通るレジスタ633から出力O (603)へのパスを表す。ノード703、705は、ゼロ処理時間を有し、ノード721と703との間と、ノード705、725との間のエッジは遅延がなく、したがってノード703、705は、ノード721、725にそれぞれマージされる（この例では図12におけるノード B<sub>i</sub> (703)と B<sub>o</sub> (705)が冗長であるため）ことに留意されたい。図10のモジュールのクリティカル・パスを識別した後、モジュールの最小クロック周期C<sub>o</sub>が決定される。

#### 【0053】

図10のモジュールにもう1つ分のクロック・サイクルのレイテンシが許可されているとき、パイプライン・レジスタ・セット（例えば図13のレジスタ641、643、645など）を追加することができる。（例えば図13の設計を生成するために）もう1つ分のクロック・サイクルのレイテンシを備えるモジュールのクロック周期を最低限に抑えるために、リタイミングや最適化を実行することができる。次いで図14に示したようなデータ・フロー・グラフを、図13のモジュールのために構築することができる。図14で

は、ノード 731 は、入力 601 から乗算器 621、623、625 を通るパスを表し、ノード 735 は、加算器 637 を通るレジスタ 633、645 から出力 603 へのパスを表している。図 10 のモジュールに対して、図 13 のモジュールは、もう 1 組のパイプライン・レジスタ（もう 1 つ分のクロック・サイクルの遅延時間）を必要とし、したがって、図 14 のデータ・フロー・グラフにおけるエッジ 701 は、図 12 のデータ・フロー・グラフにおけるエッジ 701 に対して 1 つ多くの遅延を必要とする。図 13 のモジュールのクリティカル・パスを識別した後、もう 1 つ分のクロック・サイクルのレイテンシを含むモジュールの最小クロック周期  $C_1$  が決定される。図 14 のノード  $B_i$  (703)、 $B_o$  (705) は、この例では冗長であり、取り除くこともできることに留意されたい。

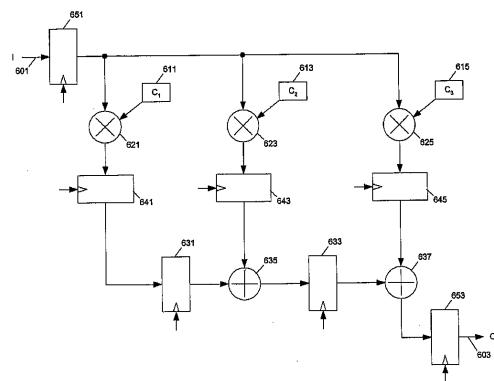

## 【0054】

レジスタ 651、653 とレジスタ 641、643、645 が図 15 のようにモジュールに追加されると、モジュールは、レジスタード I/O を備えるモジュールになる。したがって、図 15 のモジュールは、図 16 のデータ・フロー・グラフによって表すことができる。図 16 のエッジ 701 は、図 12 のエッジ 701 に対して 3 つ多い遅延を必要とする。同様に、図 15 のモジュールのクリティカル・パスを識別した後、もう 3 つ分のクロック・サイクルのレイテンシを含むモジュールの最小クロック周期  $C_3$  が決定される。

## 【0055】

図 12、図 14、図 16 のデータ・フロー・グラフは、モジュールを含む回路のリタイミングの際に、目的のクロック周期  $C$  に従って選択的に使用することができる。例えば、ある回路で図 10 のモジュールが使用されており、 $C_1 < C < C_0$  であるとき、少なくとももう 1 つ分のクロック・サイクルのレイテンシがモジュールに「投入」されることが求められ、したがって、図 14 のデータ・フロー・グラフは、回路全体のクロック最小化のためのリタイミングに使用され、図 14 のエッジ 701 の実行可能性条件は、エッジ 701 には 1 つ多い遅延が必要（またはエッジ 701 から取り除くことができる最大遅延は -1）であることを理解されたい。しかし、この回路で図 13 のモジュールが使用されており、 $C > C_0$  である場合、追加の 1 つ分のレイテンシをモジュールから移動させることができ、したがって図 12 のデータ・フロー・グラフを使用することができ、図 12 のエッジ 701 の実行可能性条件は、最大 1 つの遅延をエッジ 701 から移動させることができることを理解されたい。

## 【0056】

IP モジュールが設計で使用されるとき、ユーザは、IP モジュールで使用すべきレイテンシの量を指定することができる。したがって、リタイミング最適化エンジンに入力される設計は、その IP モジュールの最低必要レイテンシより長いレイテンシを有する IP モジュールを有することができる。例えば、入力された設計が 2 つのパイプライン・レジスタを有する FIR フィルタ・モジュールを含んでいてもよい。モジュールの元の指定されたレイテンシが考え得る最小レイテンシより長いとき、モジュールのデータ・フロー・グラフの制約の構築で、追加のレイテンシが考慮される。例えば、実行可能性条件は、必要に応じて回路の別の部分に移すことができる追加のレイテンシを示すように調整することができる。代替の手法を使用することもできることに留意されたい。例えば、追加のレイテンシは、モジュールの出力（または入力）ポートから始まるエッジにおける移動可能な重さ（遅延）として指定することができる。

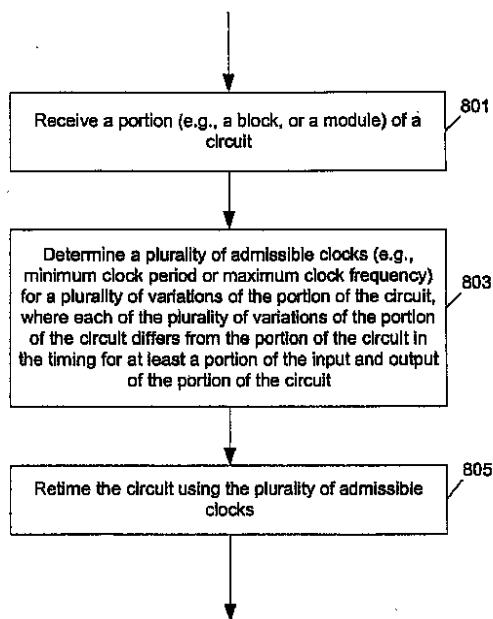

## 【0057】

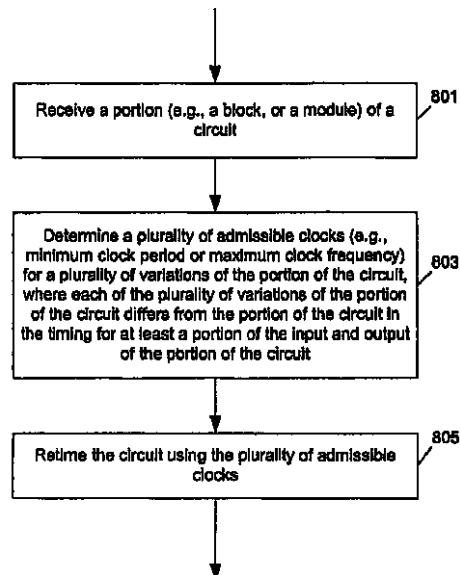

図 17 は、本発明の一実施形態による回路をリタイミングする方法を示す図である。オペレーション 801 が回路の一部分（ブロックやモジュールなど）を受信した後、オペレーション 803 は、回路の一部分の複数の変形の複数の許容できるクロック（例えば最小クロック周期または最大クロック周波数など）を決定する。回路の一部分の複数の変形のそれぞれは、その回路の一部分の少なくとも一部の入力と出力のタイミングがその回路の一部分とは異なる。例えば、回路の一部分の 1 つの変形は、1 つまたは複数のレジスタ（正または負のレイテンシを備える）を、回路の一部分の入力ラインと出力ラインの少なくとも一部分に追加し、回路の一部分のリタイミングを実行することに等しい。オペレーション 805 は、オペレーション 803 によって決定された回路の一部分の変形を実行する。

10

20

30

40

50

ヨン 8 0 5 は、複数の許容できるクロックを使用して回路をリタイミングする。例えば、（例えば入力ラインと出力ラインの一部分を介して）モジュールに「投入」する必要のある最低数のレイテンシ（遅延）は、複数の許容できるクロックと、回路の目的のクロックから決定される。

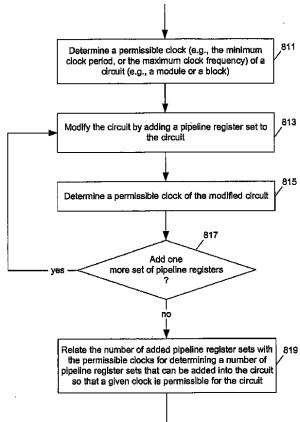

【 0 0 5 8 】

図 1 8 は、本発明の一実施形態による回路モジュールを設計する方法を示す図である。オペレーション 8 1 1 は、回路（モジュールまたはブロックなど）の許容クロック（最小クロック周期または最大クロック周波数など）を決定する。オペレーション 8 1 3 は、パイプライン・レジスタ・セットを回路に追加することによって回路を変更する。代わりに、1組のレジスタは、モジュールの入力ラインと出力ラインの一部分を介してモジュールに「投入」することができる（例えば入力ラインと出力ラインの一部分にレジスタを追加し、追加されたレジスタを備えるモジュールを最適化するようリタイミングする）。オペレーション 8 1 5 は、変更された回路の許容クロックを決定する。オペレーション 8 1 7 が、モジュールのクロックを低減するためにパイプライン・レジスタをもう1組追加すべきである（または、モジュールのクロック周期を最低限に抑えるためにより多くのレジスタをモジュールに「投入」することができる）と決定すると、オペレーション 8 1 3 、8 1 5 は、モジュールの異なる変形を得るために繰り返される。オペレーション 8 1 9 は、所与のクロックが回路に許容可能になるように回路に追加することができるパイプライン・レジスタ・セットの数を決定するために、追加されたパイプライン・レジスタ・セットの数を許容クロックに関連付ける。したがって、モデルが設計に使用されているとき、目的のクロックを実行可能にするために回路に追加することができる最低数のパイプライン・レジスタ・セットを決定することができる。あるいは、モジュールの入力ラインと出力ラインの一部分を介してモジュールに「投入」することができるレジスタの最低数は、モジュールの変形と対応する最小クロック周期との間の関係から決定することができる。クロック最小化のために、異なる数のレジスタを、モジュールの入力ラインと出力ラインの異なる部分を介してモジュールに「投入」することができ、次いで、回路の目的のクロックを達成するためにモジュールに「投入」することができる最低数のレジスタを、モジュールに「投入」されたレジスタの数と対応する最小クロック周期との間の相関から決定することができる。

【 0 0 5 9 】

図 1 9 は、本発明の一実施形態によるレジスタード I / O を備えるモジュールを備える回路をリタイミングする方法を示す図である。オペレーション 8 3 1 は、レジスタード入力と出力を備える回路の一部分を決定する。回路の一部分への各入力は、レジスタに対する直接入力であり、回路の一部分の各出力は、レジスタからの直接出力である。オペレーション 8 3 3 は、回路のデータ・フロー・グラフにおけるエッジによって接続された2つのノードを備える回路の一部分を表し、2つのノードのそれぞれは、ゼロ演算時間を必要とし、エッジにおいて必要な追加の遅延数は、回路の様々な許容クロックと回路に挿入された様々な遅延数との間の関係に従って、回路の目的のクロックによって決定される。回路の様々な許容クロックと様々な遅延数との間の関係は、システム・レベルでの回路のリタイミングの開始前、またはシステム・レベルでの回路のリタイミングのプロセス中に決定することができる。オペレーション 8 3 5 は、データ・フロー・グラフを使用して回路をリタイミングする。

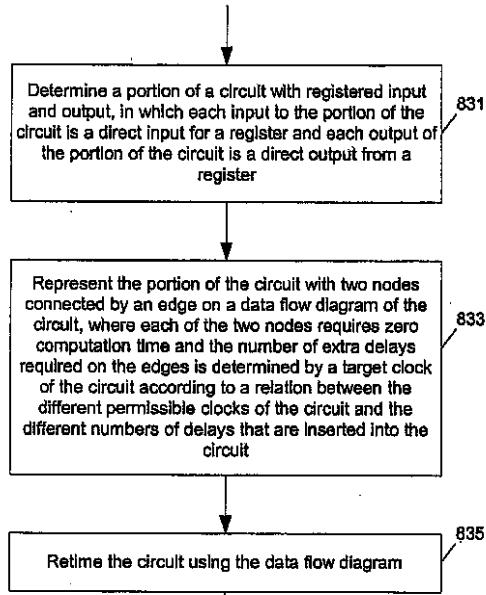

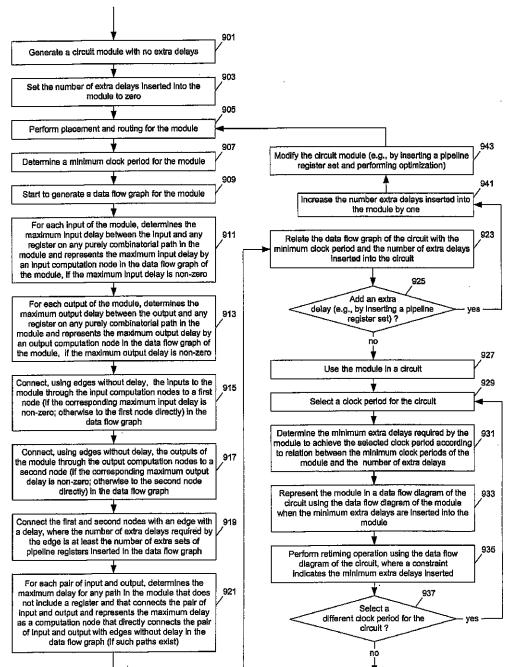

【 0 0 6 0 】

図 2 0 は、本発明の一実施形態による回路を設計する詳細な方法を示す図である。オペレーション 9 0 1 は、追加の遅延のない回路モジュールを生成する。オペレーション 9 0 3 は、モジュールに挿入される追加の遅延数をゼロに設定する。オペレーション 9 0 5 は、モジュールの配置配線を行う。オペレーション 9 0 7 は、（例えば静的タイミング分析またはタイミング・シミュレーションなどから）モジュールの最小クロック周期を決定する。オペレーション 9 0 9 は、モジュールのデータ・フロー・グラフの生成を開始する。モジュールの入力ごとに、オペレーション 9 1 1 は、モジュールの任意の純粹な組み合わ

10

20

30

40

50

セパスにおける入力と任意のレジスタとの間の最大入力遅延を決定し、（最大入力遅延がゼロでない場合）最大入力遅延に等しい演算時間を有する入力演算ノードによる最大入力遅延をモジュールのデータ・フロー・グラフに表す。モジュールの出力ごとに、オペレーション913は、モジュールの任意の純粹な組み合わせパスにおける出力と任意のレジスタとの間の最大出力遅延を決定し、（最大出力遅延がゼロでない場合）最大出力遅延に等しい演算時間を有する出力演算ノードによる最大出力遅延をデータ・フロー・グラフに表す。オペレーション915は、遅延無しのエッジを使用して、モジュールへの入力を、入力演算ノードを介してデータ・フロー・グラフにおける第1のノードに接続する（対応する最大入力遅延がゼロではない場合。そうでない場合は、第1のノードに直接接続する）。オペレーション917は、遅延無しのエッジを使用して、モジュールの出力を、出力演算ノードを介してデータ・フロー・グラフにおける第2のノードに接続する（対応する最大出力遅延がゼロではない場合。そうでない場合は、第2のノードに直接接続する）。オペレーション919は、第1と第2のノードを、遅延のあるエッジに接続する。エッジが必要とする追加の遅延数は、データ・フロー・グラフに挿入されるパイプライン・レジスタの少なくとも追加の組の数である。オペレーション921は、入力と出力の対ごとに、レジスタを含んでおらず、入力と出力の対を接続するモジュールにおける任意のパスの最大遅延を決定し、（こうしたパスが存在する場合）入力と出力の対を、データ・フロー・グラフにおける遅延のないエッジに直接接続する演算ノードとして最大遅延を表す。オペレーション923は、回路のデータ・フロー・グラフを最小クロック周期と、回路に挿入された追加の遅延数に関連付ける。オペレーション925が（例えばパイプライン・レジスタ・セットを挿入することによって）追加の遅延を追加することを決定した場合、オペレーション941は、モジュールに挿入される追加の遅延数を1つずつ増やし、オペレーション943は、（例えばパイプライン・レジスタ・セットを挿入し、最適化を実行することによって）回路モジュールを変更する。追加のレイテンシ（または遅延）は、入力ラインと出力ラインの一部分を介してモジュールに「投入」することもできるこに留意されたい。

#### 【0061】

異なるレイテンシを備えるモジュールの変形の様々な設計が取得された後、オペレーション927は、回路においてモジュールを使用する。オペレーション929は、回路のクロック周期を選択する。オペレーション931は、モジュールの最小クロック周期と追加の遅延数との間の関係に従って、選択されたクロック周期を達成するために、モジュールによって必要とされる最小余分遅延を決定する。オペレーション933は、最小余分遅延がモジュールに挿入されたとき、モジュールのデータ・フロー・グラフを使用して回路のデータ・フロー・グラフにモジュールを表す。オペレーション935は、回路のデータ・フロー・グラフを使用して、リタイミング・オペレーションを実行する。この場合、制約は、挿入された最小余分遅延を示す。モジュールの最小余分遅延数は、制約の形式で、リタイミング・オペレーション全体に組み込まれる。例えば、データ・フロー・グラフのエッジの実行可能性の制約は、少なくとも最小余分遅延がリタイミング・オペレーションでエッジに移動されることを求める（またはエッジのリタイミング・オペレーションで移動させることができる遅延の数は、挿入された最小余分遅延に等しい大きさの負の数である）。オペレーション937は、回路に異なるクロック周期を選択するかどうかを決定する。例えば、選択されたクロック周期がリタイミングの後に実行可能である場合、クロック周期の低減を選択することができ、回路に選択されたクロック周期に使用できる実行可能な解がない場合、目的のクロック周期は増える。オペレーション929～935は、回路のクロックが最低になるまで繰り返すことができる。

#### 【0062】

本発明の一実施形態において、モジュールは、異なるレイテンシと最小クロック周期（異なるレイテンシと速度）を備える複数の設計を有する。異なるレイテンシと速度を備えるモジュール設計を取得するために、レジスタが1つのモジュール設計の入力（または出力）ラインの少なくとも一部分に追加された後、リタイミングと最適化を実行することが

10

20

30

40

50

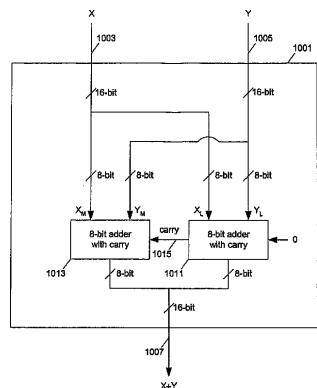

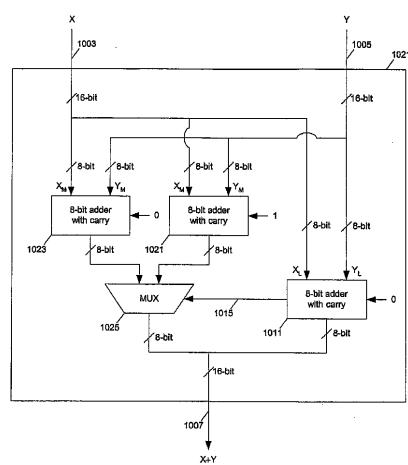

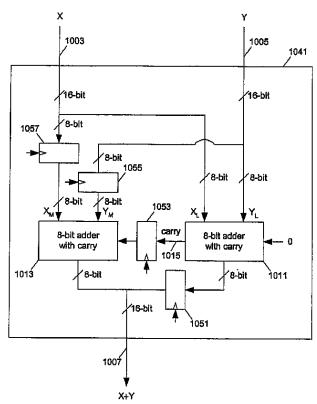

できる。一般に、リタイミングと最適化は、モジュール設計のアーキテクチャを変更しないことを理解されたい。しかし、異なる設計アーキテクチャを使用して異なる方法でモジュールを実施して、異なるレイテンシと速度を備えるモジュール設計を生成することができ、必要な速度とレイテンシ（および存在する場合は他の要件）に基づいて、システム・レベル・アルゴリズムを、異なるアーキテクチャのこれらの異なる設計の中から選択することができる。異なるアーキテクチャが使用される場合、異なる設計は、異なるロジック・オペレーション素子を含み、異なる設計は、異なる処理ロジックを有し得る。例えば、図21は、8ビットの加算器（1011、1013）を含む16ビットの加算器（1001）の設計例を示している。入力X（1003）とY（1005）の最下位8ビット（ $X_L$ および $Y_L$ ）の合計の桁上げ出力ビット（carry out bit）は、ライン1015を介して加算器1013に入力され、加算器1013は、入力X（1003）とY（1005）の最上位8ビット（ $X_M$ 、 $Y_M$ ）と加算器1011からの桁上げ出力ビットを合計する。図22は、加算器1011の桁上げ出力ビットが加算器1021、1023の結果から1つを選択する桁上げ選択（carry-select）と呼ばれる異なるアーキテクチャを備える16ビット加算器の異なる設計を示している。加算器1021は、加算器1011の桁上げ出力ビットが1であると仮定して最上位8ビット（ $X_M$ 、 $Y_M$ ）を合計し、加算器1023は、加算器1011の桁上げ出力ビットがゼロであると仮定して最上位8ビット（ $X_M$ 、 $Y_M$ ）を合計する。桁上げ選択アーキテクチャは、追加の8ビット加算器桁上げ付き、および乗算器（1025）を使用することによってクリティカル・パスを速める。図21と図22の設計は、同じレイテンシを有しているが、異なる速度を有している。図23は、図21の設計のパイプライン式バージョンを示している。パイプライン・レジスタ1051～1057では、図21の設計に対して、図23の設計のレイテンシが1ずつ増える。しかし、図23の設計（1041）は、図21と図22の設計（1001、1021）より速い。本発明の一実施形態では、システム・レベルの最適化は、目的のクロック周期に従って、設計1001、1041（同じアーキテクチャを有する）から1つを選択するステップ、または設計1021、1041（異なるアーキテクチャを有する）から1つを選択するステップ、または設計1001、1021、1041から1つを選択するステップを伴う。代替の設計が選択されると、本発明の様々な方法を使用して選択された設計のタイミング・モデルを構築して、モジュールのタイミング動作を簡略化し、レジスタ可用性条件を提示することができる。

10

20

30

40

#### 【0063】

本発明の一実施形態では、（例えばレジスタの前または後ろの組み合わせパス、またはクリティカル・パスにおける）信号遅延は、（例えば配置配線後）モジュールの全実装から取得される。したがって、モジュール内の接続遅延は、簡略化されたタイミング・モデルに含まれる。これは、モジュールのタイミング動作を正確に反映する。これらのタイミング・モデルは、最低限の複雑さで最適なリタイミングの解決策をもたらし得る。こうしたモデルは、実際の組み合わせ構成要素モデルよりかなり簡単であるが、タイミング動作をより現実的に表している。というのは、モジュール内タイミング動作の正確な遅延データ（例えば相互接続の遅延などのモジュール内遅延など）が考慮に入れられるからである。結果として、こうしたタイミング・モデルは、あまり複雑ではなく、より高い精度をもたらす。タイミングにおけるよりよいモデリング精度は、より質の高い最終解決策をもたらす。

40

50

#### 【0064】

従来の方法とは異なり、本発明の実施形態によるタイミング・モデルは、単純、有効、かつ正確にシステム・レベルの回路をリタイミングすることができる。単純なタイミング・モデルでは、データ・フロー・グラフにおいて使用するノードがより少ないので、システム・レベルのリタイミングの演算の複雑さがより低減される。したがって、本発明の実施形態による単純なタイミング・モデルは、より高質の結果をもたらしながら、システム・レベルのリタイミングの演算の複雑さを大幅に低減することができる。

#### 【0065】

さらに、本発明の一実施形態では、レジスタの「投入」は、特定のハードウェア・モジュール向けのアルゴリズムで実行することができる。こうしたカスタム・アルゴリズムを使用すると、ハードウェア・モジュールのアーキテクチャは、レイテンシによって劇的に変わり、既存の一般的なアルゴリズムを介して達成することができるものよりはるかによい結果を生成することができる。特性値(characterization value) {  $c_0, c_1, \dots, c_L$  } は、カスタム・アルゴリズムのこの挙動を捕捉する。

【0066】

回路モジュールを表す簡略化されたモデルの上記の例は、クロック周期を最低限に抑えるためのシステム・レベルのリタイミングについて示されているが、この手法は、システムのエリアと消費電力（または他の設計の目的）を伴う最適化のために使用することもできることを理解されたい。例えば、回路の消費電力またはエリアなどの他の属性を、回路モジュールの簡略化されたモデルに追加して、回路モジュールの対応する特性（例えば回路モジュールの設計の変更による消費電力の変化）を表すことができ、システム・レベルの最適化は、（タイミングの制約に加えて）これらの属性を伴う。例えば、図21～23の設計1001、1021、1041の消費電力とモジュール・エリアを決定することができる。したがって、設計の変更による消費電力とモジュール・エリアの変化を評価することができ、これは、消費電力、回路エリア、クロック速度の制約、これらの制約の組み合わせを伴うシステム・レベルの最適化に使用することができる。

【0067】

上記の明細書では、本発明は、その特定の実施形態例を参照して説明してきた。頭記の特許請求の範囲に記載した本発明の意図および範囲から逸脱することなく、様々な変更をそれに加えることができることは明らかである。したがって本明細書および図面は、制約の意味ではなく例示の意味と見なされるものとする。

【図面の簡単な説明】

【0068】

【図1】本発明とともに使用することができるデータ処理システムを示すブロック図例である。

【図2】リタイミング用のデータ・フロー・グラフを構築する従来技術の方法を示す図である。

【図3】リタイミング用のデータ・フロー・グラフを構築する従来技術の方法を示す図である。

【図4】本発明の一実施形態によるレジスタードI/Oを備える回路モジュールのデータ・フロー・グラフを構築する例を示す図である。

【図5】本発明の一実施形態によるレジスタードI/Oを備える回路モジュールのデータ・フロー・グラフを構築する例を示す図である。

【図6】本発明の一実施形態による非レジスタードI/Oを備える回路モジュールのデータ・フロー・グラフを構築する例を示す図である。

【図7】本発明の一実施形態による非レジスタードI/Oを備える回路モジュールのデータ・フロー・グラフを構築する例を示す図である。

【図8】本発明の一実施形態による非レジスタードI/Oを備える回路モジュールのデータ・フロー・グラフを構築する別の例を示す図である。

【図9】本発明の一実施形態による非レジスタードI/Oを備える回路モジュールのデータ・フロー・グラフを構築する別の例を示す図である。

【図10】本発明の一実施形態による回路モジュールを設計する詳細な例を示す図である。

【図11】本発明の一実施形態による回路モジュールを設計する詳細な例を示す図である。

【図12】本発明の一実施形態による回路モジュールを設計する詳細な例を示す図である。

【図13】本発明の一実施形態による回路モジュールを設計する詳細な例を示す図である。

10

20

30

40

50

【図14】本発明の一実施形態による回路モジュールを設計する詳細な例を示す図である。

【図15】本発明の一実施形態による回路モジュールを設計する詳細な例を示す図である。

【図16】本発明の一実施形態による回路モジュールを設計する詳細な例を示す図である。

【図17】本発明の一実施形態による回路をリタイミングする方法を示す図である。

【図18】本発明の一実施形態による回路モジュールを設計する方法を示す図である。

【図19】本発明の一実施形態によるレジスタードI/Oを備えるモジュールを備える回路をリタイミングする方法を示す図である。 10

【図20】本発明の一実施形態による回路を設計する詳細な方法を示す図である。

【図21】本発明の一実施形態に従って使用することができる、異なるレイテンシおよび最小クロック周期についての異なる設計を備えるモジュールの例を示す図である。

【図22】本発明の一実施形態に従って使用することができる、異なるレイテンシおよび最小クロック周期についての異なる設計を備えるモジュールの例を示す図である。

【図23】本発明の一実施形態に従って使用することができる、異なるレイテンシおよび最小クロック周期についての異なる設計を備えるモジュールの例を示す図である。

【図1】

【図2】

Fig. 1

Fig. 2

【図3】

Fig. 3

【図4】

Fig. 4

【図5】

Fig. 5

【図6】

Fig. 6

【図8】

Fig. 8

【図7】

Fig. 7

【図 1 0】

Fig. 10

【図 1 1】

Fig. 11

【図 1 2】

Fig. 12

【図 1 3】

Fig. 13

【図 1 4】

Fig. 14

【図 1 6】

Fig. 16

【図 1 5】

Fig. 15

【図17】

Fig. 17

【図18】

Fig. 18

【図19】

Fig. 19

【図20】

Fig. 20

【図2-1】

Fig. 21

【図2-2】

Fig. 22

【図2-3】

Fig. 23

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                    | International Application No<br>PCT/US2004/014225                  |          |                                                                                    |                       |   |                                                                                                               |                          |   |                                                                                                                                                                                    |                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|----------|------------------------------------------------------------------------------------|-----------------------|---|---------------------------------------------------------------------------------------------------------------|--------------------------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| <b>A. CLASSIFICATION OF SUBJECT MATTER</b><br>IPC 7 G06F17/50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                    |                                                                    |          |                                                                                    |                       |   |                                                                                                               |                          |   |                                                                                                                                                                                    |                          |

| According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                    |                                                                    |          |                                                                                    |                       |   |                                                                                                               |                          |   |                                                                                                                                                                                    |                          |

| <b>B. FIELDS SEARCHED</b><br>Minimum documentation searched (classification system followed by classification symbols)<br>IPC 7 G06F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                    |                                                                    |          |                                                                                    |                       |   |                                                                                                               |                          |   |                                                                                                                                                                                    |                          |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                    |                                                                    |          |                                                                                    |                       |   |                                                                                                               |                          |   |                                                                                                                                                                                    |                          |

| Electronic data base consulted during the international search (name of data base and, where practical, search terms used)<br>EPO-Internal, WPI Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                    |                                                                    |          |                                                                                    |                       |   |                                                                                                               |                          |   |                                                                                                                                                                                    |                          |

| <b>C. DOCUMENTS CONSIDERED TO BE RELEVANT</b> <table border="1" style="width: 100%; border-collapse: collapse;"> <thead> <tr> <th style="text-align: left; padding: 2px;">Category</th> <th style="text-align: left; padding: 2px;">Citation of document, with indication, where appropriate, of the relevant passages</th> <th style="text-align: left; padding: 2px;">Relevant to claim No.</th> </tr> </thead> <tbody> <tr> <td style="text-align: center; padding: 2px;">X</td> <td style="padding: 2px;">US 5 898 742 A (VAN DER WERF ET AL)<br/>27 April 1999 (1999-04-27)<br/><br/>column 1, line 7 - column 4, line 38</td> <td style="text-align: center; padding: 2px;">1-17,<br/>34-50,<br/>67-83</td> </tr> <tr> <td style="text-align: center; padding: 2px;">X</td> <td style="padding: 2px;">EP 0 769 738 A (KABUSHIKI KAISHA TOSHIBA)<br/>23 April 1997 (1997-04-23)<br/><br/>column 1, line 5 - column 7, line 25<br/>column 11, line 50 - column 13, line 49<br/><br/>-----<br/>-/-</td> <td style="text-align: center; padding: 2px;">1-17,<br/>34-50,<br/>67-83</td> </tr> </tbody> </table> |                                                                                                                                                                                    |                                                                    | Category | Citation of document, with indication, where appropriate, of the relevant passages | Relevant to claim No. | X | US 5 898 742 A (VAN DER WERF ET AL)<br>27 April 1999 (1999-04-27)<br><br>column 1, line 7 - column 4, line 38 | 1-17,<br>34-50,<br>67-83 | X | EP 0 769 738 A (KABUSHIKI KAISHA TOSHIBA)<br>23 April 1997 (1997-04-23)<br><br>column 1, line 5 - column 7, line 25<br>column 11, line 50 - column 13, line 49<br><br>-----<br>-/- | 1-17,<br>34-50,<br>67-83 |

| Category                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                 | Relevant to claim No.                                              |          |                                                                                    |                       |   |                                                                                                               |                          |   |                                                                                                                                                                                    |                          |

| X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | US 5 898 742 A (VAN DER WERF ET AL)<br>27 April 1999 (1999-04-27)<br><br>column 1, line 7 - column 4, line 38                                                                      | 1-17,<br>34-50,<br>67-83                                           |          |                                                                                    |                       |   |                                                                                                               |                          |   |                                                                                                                                                                                    |                          |

| X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | EP 0 769 738 A (KABUSHIKI KAISHA TOSHIBA)<br>23 April 1997 (1997-04-23)<br><br>column 1, line 5 - column 7, line 25<br>column 11, line 50 - column 13, line 49<br><br>-----<br>-/- | 1-17,<br>34-50,<br>67-83                                           |          |                                                                                    |                       |   |                                                                                                               |                          |   |                                                                                                                                                                                    |                          |

| <input checked="" type="checkbox"/> Further documents are listed in the continuation of box C. <input checked="" type="checkbox"/> Patent family members are listed in annex.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                    |                                                                    |          |                                                                                    |                       |   |                                                                                                               |                          |   |                                                                                                                                                                                    |                          |

| ° Special categories of cited documents :<br>"A" document defining the general state of the art which is not considered to be of particular relevance<br>"E" earlier document but published on or after the international filing date<br>"L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)<br>"O" document referring to an oral disclosure, use, exhibition or other means<br>"P" document published prior to the international filing date but later than the priority date claimed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                    |                                                                    |          |                                                                                    |                       |   |                                                                                                               |                          |   |                                                                                                                                                                                    |                          |

| "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention<br>"X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone<br>"Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art<br>"&" document member of the same patent family                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                    |                                                                    |          |                                                                                    |                       |   |                                                                                                               |                          |   |                                                                                                                                                                                    |                          |

| Date of the actual completion of the international search<br><br>22 July 2005                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                    | Date of mailing of the international search report<br><br>10.10.05 |          |                                                                                    |                       |   |                                                                                                               |                          |   |                                                                                                                                                                                    |                          |