# (19) World Intellectual Property Organization

International Bureau

(43) International Publication Date 18 May 2007 (18.05.2007)

(10) International Publication Number WO 2007/054405 A1

(51) International Patent Classification: *H01L 21/762* (2006.01)

(21) International Application Number:

PCT/EP2006/066992

(22) International Filing Date: 3 October 2006 (03.10.2006)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

11/164,179 14 November 2005 (14.11.2005) US

(71) Applicant (for all designated States except US): INTER-NATIONAL BUSINESS MACHINES CORPORA-TION [US/US]; New Orchard Road, Armonk, New York 10504 (US).

(71) Applicant (for MG only): IBM UNITED KINGDOM LIMITED [GB/GB]; PO Box 41, Portsmouth Hampshire PO6 3AU (GB).

(72) Inventor; and

(75) Inventor/Applicant (for US only): CHIDAMBARRAO, Dureseti [US/US]; 29 Old Mill Road, Weston, Connecticut 06883 (US).

- (74) Agent: WILLIAMS, Julian, David; IBM United Kingdom Limited, Intellectual Property Law, Hursley Park, Winchester Hampshire SO21 2JN (GB).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LV, LY, MA, MD, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, SV, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IS, IT, LT, LU, LV, MC, NL, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### **Published:**

with international search report

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

(54) Title: ROTATIONAL SHEAR STRESS FOR CHARGE CARRIER MOBILITY MODIFICATION

(57) Abstract: A semiconductor structure and its method of fabrication utilize a semiconductor substrate having an active region (11) mesa surrounded by an isolation trench. A first isolation region (12) having a first stress is located in the isolation trench. A second isolation region (16a, 16b) having a second stress different than the first stress is also located in the isolation trench. The first isolation region and the second isolation region are sized and positioned to rotationally shear stress the active region mesa.

#### ROTATIONAL SHEAR STRESS FOR CHARGE CARRIER MOBILITY MODIFICATION

#### DESCRIPTION

#### Field of the Invention

The invention relates generally to physical stress within semiconductor structures. More particularly, the invention relates to physical stress induced charge carrier mobility modification within semiconductor structures.

#### Description of Related Art

Recent advances in semiconductor device design and development have involved the introduction of applied physical stress into semiconductor device components. Applied physical stress often leads to charge carrier mobility modification. In particular, enhanced charge carrier mobility generally leads to enhanced semiconductor device performance.

There are various examples of stress induced performance enhancement within semiconductor devices. For example, Doris et al., in U.S. Patent No. 6,717,216 teaches a silicon-on-insulator (SOI) field effect transistor (FET) having a compressive stress in an undercut area to provide increased charge carrier mobility in the device.

Other examples of compressive stress or tensile stress within various locations within semiconductor structures are alternatively known to provide charge carrier mobility modification. Typically, n-FET and p-FET devices respond differently to compressive and tensile stresses since piezoresistance coefficients will typically differ as a function of several variables, including, for example, semiconductor substrate doping and crystallographic orientation. Thus, stressed components within n-FET and p-FET devices often need to be specifically engineered and optimized.

A trend within semiconductor device design and development is for continued enhanced performance at smaller dimensions. Thus, a need will continue to exist for novel structures and methods that, in turn, provide semiconductor devices with enhanced performance. To that end, the use of physically stressed semiconductor structures is likely to continue. Desirable are alternative semiconductor structures and methods for fabrication that advantageously use physical stress for semiconductor device performance enhancement.

#### SUMMARY OF THE INVENTION

The present invention provides a semiconductor structure having enhanced performance, as well as a method for fabricating such a semiconductor structure. Specifically, the present invention provides a semiconductor structure and a method for fabricating the semiconductor structure in which rotational shear stress is introduced into the structure to enhance performance thereof. The introduction of the rotational shear stress applies to both the inventive structure and the inventive method.

In accordance with the invention, the semiconductor structure comprises a semiconductor substrate having an isolation trench surrounding an active region mesa. The semiconductor structure also comprises a first isolation region having a first stress located in the isolation trench. The semiconductor structure also comprises a second isolation region having a second stress, which is different than the first stress, also located in the isolation trench. The first isolation region and the second isolation region are sized and positioned to rotationally shear stress the active region mesa.

The method for fabricating the inventive semiconductor structure derives from and is correlated with the semiconductor structure itself. To that end, the inventive method first provides a semiconductor substrate having an active region mesa surrounded by an isolation trench. The method also provides for forming a first isolation region having a first stress into the isolation trench. Finally, the method also provides for forming a second isolation region having a second stress different than the first stress into the isolation trench. Within the method, the first isolation region and the second isolation region are sized and positioned to rotationally shear stress the active region mesa.

The inventive structure and inventive method also provide that the first isolation region and the second isolation region may comprise a single chemical material, such as a silicon oxide material. The method further provides a specific silicon oxidation process for forming the silicon oxide material.

By "rotationally shear stress" within the invention it is meant that an active region mesa is subjected to a rotational force that if the active region mesa was unattached to a semiconductor substrate the rotational force would rotate the active region mesa with respect to the semiconductor substrate. The rotation would be along an axis that perpendicularly penetrates an exposed surface of the active region mesa.

Since the active region mesa is integral to and nominally non-separable from a semiconductor substrate, it may not freely rotate to relieve such a rotational force. Rather, the active region mesa experiences a rotational shear stress due to an unrelieved rotational force. The shear within the rotational shear stress results from differing ability of an active region mesa to deform as a result of a rotational force as a function of height intervals of the active region mesa above a semiconductor substrate.

The invention is predicated upon the observation that a piezoresistance coefficient for rotational shear stress may be particularly high for certain semiconductor substrate compositions and orientations. For example, p-silicon in a normal orientation of x=(110), y=(-110) and z=(001) has a particularly high piezoresistance coefficient of 138.1 e-11/Pa for rotational shear stress in the xy plane. Thus, for that semiconductor substrate material and crystallographic orientation, the invention provides for considerable charge carrier mobility enhancement incident to rotational shear stress. The invention is also applicable to other semiconductor substrates, but will provide differing levels of performance enhancement as measured in terms of charge carrier mobility.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The objects, features and advantages of the invention are understood within the context of the Description of the Preferred Embodiments, as set forth below. The Description of the Preferred Embodiments is understood within the context of the accompanying drawings, which form a material part of this disclosure, wherein:

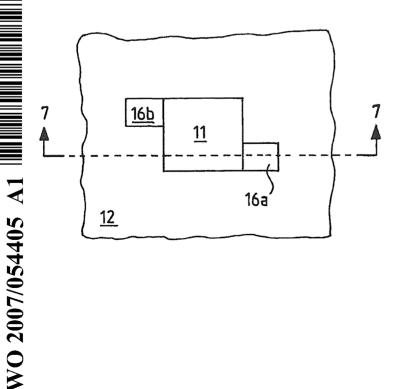

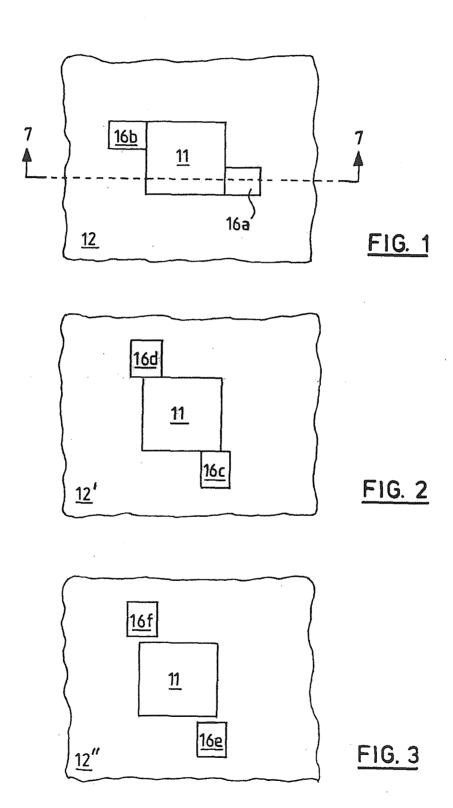

FIG. 1, FIG. 2 and FIG. 3 show a series of schematic plan-view diagrams illustrating three separate embodiments of the invention.

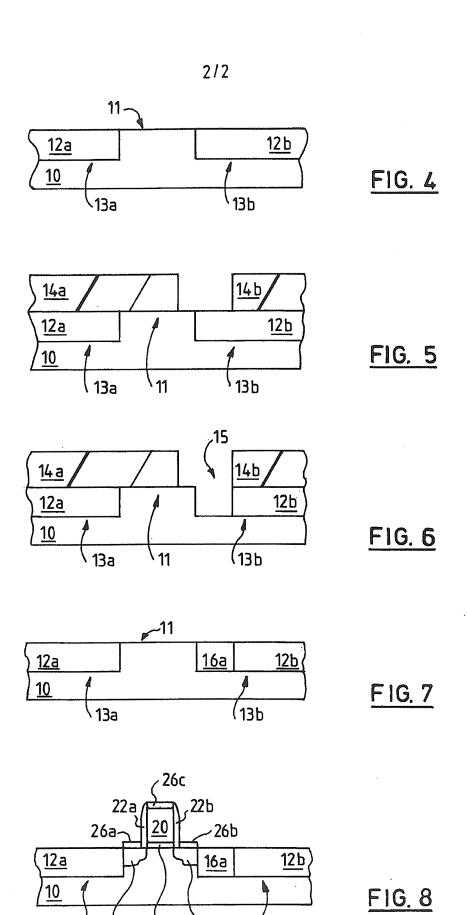

FIG. 4 to FIG. 8 show a series of schematic cross-sectional diagrams illustrating the results of progressive stages in fabricating a semiconductor structure in accordance with a first embodiment of the invention.

### DESCRIPTION OF THE PREFERRED EMBODIMENTS

The invention provides a semiconductor structure and a method for fabricating the semiconductor structure. The semiconductor structure may be fabricated with enhanced performance with respect to charge carrier mobility by using a minimum of a two component isolation region located within an isolation trench that surrounds an active region mesa within the semiconductor structure. The two component isolation region includes a

first isolation region having a first stress and a second isolation region having a second stress different than the first stress. The first isolation region and the second isolation region are sized and positioned to rotationally shear stress the active region mesa. The rotational shear stress influences charge carrier mobility within the active region mesa.

FIG. 1 shows a schematic plan-view diagram of a semiconductor structure in accordance with a first embodiment of the invention.

FIG. 1 shows an active region mesa 11. The active region mesa 11 is completely surrounded by a first isolation region 12. A pair of second isolation regions 16a and 16b adjoins the active region mesa 11 at a pair of opposite corners thereof. They do not completely surround the active region mesa 11 as does the first isolation region 12. Typically, the active region mesa 11 is sized in area to accommodate submicron devices, although such is not a requirement or a limitation of the invention. Typically, the pair of second isolation regions 16a and 16b is sized in area or volume to be from about 5% to about 10% the area or volume of the first isolation region 12. The invention is not so limited. Greater comparative area or volume ratios of isolation regions such as the first isolation region 12 and the pair of second isolation regions 16a and 16b are also within the context of the invention.

When the second isolation regions 16a and 16b comprise an isolation material having a compressive stress, these isolation regions impart a rotational shear stress in a clockwise direction into the active region mesa 11. The second isolation regions 16a and 16b when comprised of a material having a tensile stress impart a counter clockwise rotational shear stress into the active region mesa 11. A rotational shear stress in a clockwise direction is preferred in the first embodiment. In turn, this stress provides for enhanced hole carrier mobility when the active region mesa comprises a p silicon material of the crystallographic orientation described above. The enhanced hole carrier mobility is desirable since it, in turn, provides for enhanced performance of p channel devices such as p-FETs.

As will be illustrated in further detail below (see, e.g. FIG. 7 and FIG. 8) a channel region when located vertically centered within the active region mesa 11 as illustrated in FIG. 1 further benefits from a clockwise rotational shear stress since the clockwise rotation shear stress also imparts a longitudinal compressive stress and a transverse tensile stress into the channel region. Both of these additional stresses are also

beneficial for charge carrier mobility enhancement within p-FET devices.

FIG. 2 shows a schematic plan-view diagram of a second embodiment of the invention. The second embodiment also shows the active region mesa 11 completely surrounded by a first isolation region 12'. The first isolation region 12' has slightly differing dimensions than the first isolation region 12 illustrated in FIG. 1. A pair of second isolation regions 16c and 16d is located contacting the active region mesa 11, but at a different location and with a different offset in comparison with the second isolation regions 16a and 16b as illustrated in FIG. 1.

In the second embodiment, the pair of second isolation regions 16c and 16d may also be comprised of a second isolation material having a tensile stress or a compressive stress. A tensile stress is preferred. This yields the preferred clockwise rotational shear stress within the active region mesa 11. Thus, an enhanced hole carrier mobility is still realized in the second embodiment when the active region mesa 11 comprises a p silicon material of the above described crystallographic orientation.

FIG. 3 shows a schematic plan-view diagram of a third embodiment of the invention. The third embodiment is similar to the second embodiment. However, the third embodiment comprises a pair of second isolation regions 16e and 16f that is separated from the active region mesa 11. Thus, within the third embodiment only one of a first isolation region 12'' and the pair of second isolation regions 16e and 16f contacts the active region mesa 11. In comparison, within the first embodiment and the second embodiment both of the first isolation region 12 or 12', and the pertinent second isolation regions 16a and 16b or 16c and 16d, contact the active region mesa 11 at a sidewall thereof.

The third embodiment provides a semiconductor structure where the second isolation regions 16e and 16f do not contact the active region mesa 11. Under these circumstances, a rotational shear stress is still imparted to the active region mesa 11, but it is diminished in magnitude in comparison with the semiconductor structure of FIG. 2. The reduction results from some intervening first insulator material of different stress between the active region mesa 11 and the pair of second isolation regions 16e and 16f.

FIGS. 4-8 show a series of schematic cross-sectional diagrams illustrating the results of progressive stages in fabricating a semiconductor structure in accordance with the first embodiment of the invention. While FIGS. 4-8

are directed towards fabrication of the semiconductor structure in accordance with the first embodiment, an analogous fabrication sequence may be used for semiconductor structures in accordance with the second embodiment and the third embodiment.

The schematic cross-sectional diagrams of FIGS. 4-8 illustrate longitudinal cross-sections. A transverse cross-section is normal to the longitudinal cross-section and it also includes a cross-section through a substrate plane. A vertical direction is perpendicular to the substrate plane.

FIG. 4 shows a semiconductor substrate 10. It has an active region mesa 11 located therein. The active region mesa 11 separates a pair of isolation trenches 13a and 13b that adjoin the active region mesa 11. A pair of first isolation regions 12a and 12b (corresponding with the first isolation region 12 as illustrated in FIG. 1) is located in the corresponding pair of isolation trenches 13a and 13b. Each of the foregoing structures may comprise materials and have dimensions that are conventional in the semiconductor fabrication art. In addition, each of the foregoing structures may be formed using methods that are conventional in the semiconductor fabrication art.

The semiconductor substrate 10 may comprise any of several semiconductor materials, including but not limited to: silicon, germanium, silicon germanium alloy, silicon carbide, silicon germanium carbide alloy and compound (e.g., III-V and II-VI) semiconductor materials. Non-limiting examples of compound semiconductor materials include gallium arsenide, indium arsenide and indium phosphide semiconductor materials. Typically, the semiconductor substrate 10 comprises a silicon or silicon-germanium alloy semiconductor material.

Also, the semiconductor substrate 10 may comprise, but is not limited to: a bulk semiconductor substrate, a semiconductor-on-insulator substrate or a hybrid orientation technology (HOT) semiconductor substrate having multiple crystallographic orientation regions. Typically, the semiconductor substrate 10 is intended for complementary metal oxide semiconductor (CMOS) device fabrication, and it includes appropriate complementary doped semiconductor regions not otherwise illustrated in FIG. 4. Typically, the semiconductor substrate 10 has a thickness from about 0.5 to about 3 millimeters.

As noted above, the invention is preferably practiced using a p silicon semiconductor substrate having crystallographic orientation planes of x=(110), y=(-110) and z=(001). With these orientations, a piezoresistance coefficient for rotational shear stress in the xy plane of the p silicon semiconductor substrate is particularly high at 138.1 e-11/Pa for p-silicon. It is lower for rotational shear stress for other planes of the above p-silicon semiconductor substrate (66.3 e-11/Pa for xz and yz planes), and for all planes of n-silicon (-13.6 e-11/Pa for xy plane and 18 e-11/Pa for xz and yz planes). The invention is not limited to the foregoing p silicon semiconductor substrate with its particularly high piezoresistance coefficient for rotational shear stress in the xy plane. A relative advantage of the invention for particular semiconductor substrates (i.e., materials compositions, doping and crystallographic orientations) is readily determined by a person skilled in the art incident to evaluation of piezoresistance coefficients.

The pair of isolation trenches 13a and 13b is typically formed while using an appropriate masking and etching of the semiconductor substrate 10. The masked semiconductor substrate 10 is preferably etched using an anisotropic etchant that preserves a straight sidewall contour of the active region mesa 11. Such anisotropic etchants are typically plasma etchants, reactive ion etchants or ion beam etchants that include a directional component, and optionally a chemical etching component. The invention may alternatively use crystallographically specific chemical etchants and, in some circumstances, also isotropic etchants. Although isotropic etchants may yield a non-planar active region mesa 11 sidewall contour, such a sidewall contour is not necessarily detrimental within the invention. Thus, such a sidewall contour is also included within the context of the invention.

Typically, each of the isolation trenches 13a and 13b has a depth from about 500 to about 2000 angstroms within the semiconductor substrate 10. At such a depth, each of the pair of isolation trenches 13a and 13b may be regarded as a "shallow" isolation trench. The embodiment and the invention are, however, not limited to shallow isolation trenches. Rather the embodiment and the invention are also applicable to deeper isolation trenches having depths of several thousand angstroms within a semiconductor substrate.

The pair of first isolation regions 12a and 12b typically comprises isolation materials that are generally conventional in the semiconductor fabrication art. Such isolation materials will typically include, but are

not limited to: oxides, nitrides and oxynitrides typically of silicon, but other materials are not excluded. The embodiment and invention also contemplate laminates and composites of the foregoing materials. The pair of first isolation regions 12a and 12b may have either tensile stress, compressive stress or neutral stress. Factors that influence stress within the pair of first isolation regions 12a and 12b include, but are not limited to: deposition rate and temperature, deposited film crystallinity and deposition source material compositions.

The pair of first isolation regions 12a and 12b is typically formed using at least in part a blanket dielectric layer formation method, typically followed by a planarizing method. The blanket dielectric layer may be formed using methods including, but not limited to: thermal oxidation methods, chemical vapor deposition methods and physical vapor deposition methods. High density plasma chemical vapor deposition methods are desirable insofar as they provide generally dense dielectric layers that, in turn, are desirable for isolation purposes. Planarization may be effected using methods including, but not limited to: purely mechanical methods and chemical mechanical polish (CMP) methods. Chemical mechanical polish methods are generally preferred, but the neither the instant embodiment nor the invention is so limited.

FIG. 5 shows a pair of patterned photoresist layers 14a and 14b located upon the semiconductor structure of FIG. 4. The pair of patterned photoresist layers 14a and 14b leaves exposed a portion of the active region mesa 11 and an adjoining portion of the isolation region 12b. Although not illustrated, in plan-view the pair of patterned photoresist layers 14a and 14b is intended to represent a single photoresist layer having apertures therein corresponding with locations wherein the pair of second isolation regions 16a and 16b is desired to be located. The pair of patterned photoresist layers 14a and 14b may comprise photoresist materials as are conventional in the art. Non-limiting examples of photoresist materials include: positive photoresist materials, negative photoresist materials and hybrid photoresist materials. Typically, the pair of patterned photoresist layers 14a and 14b is formed using coating, photoexposure and development methods that are similarly also conventional in the semiconductor fabrication art. Typically, each of the pair of patterned photoresist layers 14a and 14b has a thickness from about 5000 to about 15000 angstroms.

FIG. 6 shows an etched isolation region 12b' that results of etching a portion of the isolation region 12b exposed by the pair of patterned

Ç

photoresist layers 14a and 14b. The etching may be accomplished using conventional dry etching techniques such as reactive-ion etching, while employing the pair of patterned photoresist layers 14a and 14b as a mask. Other etch methods such as physical etch methods and wet chemical etch methods may also advantageously be used. The etching leaves exposed sidewall portions of the active region mesa 11 and adjoining floor portions of the isolation trench 13b. Thus, a void 15 is formed.

FIG. 7 first shows the results of stripping the pair of patterned photoresist layers 14a and 14b from the semiconductor structure of FIG. 6. They may be stripped using methods and materials that are conventional in the semiconductor fabrication art. Non-limiting examples include: wet chemical methods, dry plasma methods and combinations thereof.

FIG. 7 also shows a second isolation region 16a located in the void 15 as illustrated in FIG. 6. As noted above, the first embodiment provides that the first isolation regions 12a and 12b (which correspond with the first isolation region 12 illustrated in plan-view FIG. 1), comprise a first isolation material having a first stress. The second isolation region 16a comprises a second isolation material having a second stress different than the first stress. As further discussed above, the first isolation material is typically a silicon oxide material, although the invention is not so limited. The first isolation regions 12a and 12b may have either tensile stress, compressive stress or neutral stress. Most generally within the invention, an isolation region such as the second isolation region 16a may also have either tensile stress, compressive stress or neutral stress provided that the desired rotational shear stress limitations of the invention are met (incident to proper sizing and positioning of the first isolation regions 12a and 12b, and the second isolation region 16a). More typically within the first embodiment, the second isolation region 16a may have either tensile stress or compressive stress. Preferably the second isolation region 16a has compressive stress since in accordance with description corresponding with FIG. 1 the same provides for a desirable clockwise rotational shear stress in the active region mesa 11.

The second isolation region 16a may comprise dielectric materials including, but not limited to: oxide, nitride and oxynitride dielectric materials, as well as laminates thereof and composites thereof. Silicon oxide materials may be formed using a different method than used for forming the first isolation regions 12a and 12b, when they also comprise silicon oxide materials. For example, a silicon oxide material may be

formed using a thermal oxidation of a deposited amorphous silicon material or polycrystalline silicon material. The oxidation is undertaken to not substantially oxidize the active region mesa 11. A silicon oxide material resulting from such a thermal oxidation may have a particularly high compressive stress since upon oxidation to yield a silicon oxide material, either an amorphous silicon material or a polysilicon material has an increase in volume. When forming the second isolation region 16a from such a silicon oxide material, a planarizing method will also typically be needed (but may not necessarily be required), since the thermally grown silicon oxide will often cover in part the active region mesa 11 and the etched first isolation region 12b'. For this reason, a planarizing stop liner layer may also optionally first be formed and located upon the semiconductor structure as illustrated in FIG. 6 absent the pair of patterned photoresist layers 14a and 14b, prior to forming the second isolation region 16a within the void 15. A nitride or oxynitride material is typically appropriate for the planarizing stop layer.

FIG. 8 shows a field effect transistor located upon the active region mesa 11. The field effect transistor comprises a gate dielectric layer 18 located upon the active region mesa 11. A gate electrode 20 is located aligned upon the gate dielectric layer 18 although such an alignment is not a limitation of the embodiment or the invention. A pair of spacer layers 22a and 22b is located adjacent and adjoining a pair of opposite sidewalls of the gate dielectric layer 18 and the gate electrode 20. A pair of source/drain regions 22a and 22b is located within the active region mesa 11 and separated by the gate electrode 20. Finally, a series of silicide layers 26a, 26b and 26c is located one each upon the pair of source/drain regions 24a and 24b, and the gate electrode 20.

Each of the foregoing structures that comprise the field effect transistor may comprise materials, and have dimensions, that are conventional in the semiconductor fabrication art. Each of the foregoing structures may also be formed using methods that are conventional in the semiconductor fabrication art.

For example, the gate dielectric layer 18 may comprise oxide, nitride or oxynitride dielectric materials that typically have a dielectric constant from about 4 to about 20, measured in vacuum. Alternatively, the gate dielectric layer 18 may comprise generally higher dielectric constant dielectric materials having a dielectric constant greater than 20, and perhaps up to about 100. These generally higher dielectric constant dielectric materials may include, but are not limited to: hafnium oxides,

WO 2007/054405 PCT/EP2006/066992

11

hafnium silicates, aluminum oxides, titanium oxides, lanthanum oxides, barium strontium titanates (BSTs) and lead zirconate titanates (PZTs). The foregoing materials may be formed using methods including, but not limited to: thermal oxidation methods, chemical vapor deposition methods, physical vapor deposition methods and atomic layer chemical vapor deposition methods. The gate dielectric layer 18 when comprising a conventional thermal silicon oxide material typically has a thickness from about 10 to about 70 angstroms.

The gate electrode 20 typically comprises a highly doped (e.g., 1e20 to 1e22 dopant atoms per cubic centimeter) polysilicon material that may be deposited employing chemical vapor deposition or physical vapor deposition methods. Alternate methods may also be used. Alternative gate electrode conductor materials may also be used. Alternative gate electrode conductor materials may include, but are not limited to: metals, metal alloys, metal nitrides and metal silicides, as well as laminates thereof and composites thereof. Typically, the gate electrode 20 has a thickness from about 500 to about 1500 angstroms.

The pair of spacers 22a and 22b generally comprise a dielectric material or a multilayer laminate of several dielectric materials. Typical but not limiting dielectric materials include oxides, nitrides and oxynitrides, typically of silicon, but other materials are not excluded. The pair of spacers 22a and 22b is typically formed utilizing a blanket layer deposition and anisotropic etch method that provides their characteristically tapered spacer shape.

The pair of source/drain regions 24a and 24b typically comprises an appropriate dopant material incorporated into the active region mesa at a concentration of up to about 1e21 dopant atoms per cubic centimeter. The dopant is selected in accordance with the type of field effect transistor desired to be fabricated within the active region mesa 11. The dopant is typically ion implanted using a two step method. The two step method uses the gate electrode 20 as a mask, both with or without the pair of spacers 22a and 22b. Thus, the pair of source/drain regions 24a and 24b has a pair of extension regions located primarily beneath the pair of spacer layers 22a and 22b.

Finally, the series of metal silicide layers 26a, 26b and 26c may comprise metal silicides of any of several metal silicide forming metals. Non-limiting examples of metal silicide forming metals include tungsten, titanium, cobalt, nickel and platinum. The metal silicide layers 26a, 26b and 26c are generally formed utilizing a blanket metal silicide forming metal layer deposition, thermal annealing and regioselective unreacted metal etch. The regioselective unreacted metal etch generally uses a wet chemical etchant specific to a particular metal silicide forming metal desired to be regioselectively removed. Alternative methods may also be used. Typically, each of the metal silicide layers 26a, 26b and 26c has a thickness from about 50 to about 200 angstroms.

FIG. 8 shows a schematic cross-sectional diagram of a field effect transistor located upon an active region mesa 11 that is rotationally shear stressed (by properly sized and positioned first isolation regions 12a and 12b corresponding with isolation region 12 in FIG. 1, and second isolation regions 16a and 16b as also illustrated in FIG. 1) in accordance with the first embodiment of the invention. The rotational shear stress provides an enhanced hole charge carrier mobility when the active region mesa comprises a particular p silicon crystallographic orientation. Thus, thus a p-FET located upon such an active region mesa has enhanced performance. In addition, rotational shear stress in a particular clockwise direction also imparts a longitudinal compressive stress and a transverse tensile stress into the channel region. Both of these additional stresses are also beneficial for charge carrier mobility enhancement within p-FET devices.

Although the instant embodiment illustrates the invention most particularly with respect to a p-FET upon an active region mesa comprising a p silicon material of particular crystallographic orientation, clearly the invention is not intended to be so limited. Rather, as noted above, a person of skill in the art can easily evaluate piezoresistance coefficients to readily determine applicability of the invention to a particular semiconductor material crystallographic orientation and doping. In addition, the invention is also clearly operative with any of several semiconductor devices that might benefit from enhanced charge carrier mobility within an active region mesa. Such devices may include, but are not limited to: field effect devices other than field effect transistors, bipolar transistors, bi-CMOS transistors, diodes and other active devices. In addition, performance enhancements are also not precluded within passive devices, including but not limited to: resistors and capacitors.

In summary, the invention provides for a modified charge carrier mobility within a semiconductor structure by imparting a rotational shear stress into an active region mesa within the semiconductor structure. The rotational shear stress is imparted by use of a two component isolation

13

region surrounding the active region mesa. The two components include:

(1) a first isolation region having a first stress; and (2) a second isolation region having a second stress different than the first stress. The first isolation region and the second isolation region are sized and positioned to rotationally shear stress the active region mesa.

The preferred embodiments illustrate the invention within the contest of a single first isolation region 12, 12' or 12' and a pair of second isolation regions 16a and 16b, 16c and 16d or 16e and 16f. However, an operative invention may be realized with at least one each of a first isolation region and a second isolation region of different stress properly sized and positioned to rotationally shear stress an active region mesa within a semiconductor structure. Multiple first isolation regions and second isolation regions may also be employed within the context of the above rotational shear stress limitations to provide an operative invention.

The preferred embodiments of the invention are illustrative of the invention rather than limiting of the invention. Revisions and modifications may be made to methods, materials, structures and dimensions in accordance with the preferred embodiments of the invention while still providing an embodiment in accordance with the invention, further in accordance with the accompanying claims.

#### **CLAIMS**

1. A semiconductor structure comprising:

a semiconductor substrate having an active region mesa surrounded by an isolation trench;

at least one first isolation region having a first stress located in the isolation trench; and

at least one second isolation region having a second stress different than the first stress also located in the isolation trench, where the first isolation region and the second isolation region are sized and positioned to rotationally shear stress the active region mesa.

- 2. The semiconductor structure of claim 1 wherein both the first isolation region and the second isolation region contact the active region mesa.

- 3. The semiconductor structure of claim 1 wherein only one of the first isolation region and the second isolation region contacts the active region meas.

- 4. The semiconductor structure of claim 1 wherein the isolation trench is a shallow isolation trench.

- 5. The semiconductor structure of claim 1 wherein the rotational shear stress is in a clockwise direction.

- 6. The semiconductor structure of claim 1 wherein the rotational shear stress is in a counter clockwise direction.

- 7. The semiconductor structure of claim 1 further comprising a semiconductor device located upon the active region mesa.

- 8. The semiconductor structure of claim 7 wherein the semiconductor device is a field effect transistor.

- 9. A semiconductor structure comprising:

a semiconductor substrate having an active region mesa surrounded by an isolation trench;

at least one first isolation region having a first stress located in the isolation trench; and

at least one second isolation region having a second stress different than the first stress also located in the isolation trench, where:

the first isolation region and the second isolation region are sized and positioned to rotationally shear stress the active region mesa; and

the first isolation region and the second isolation region are comprised of a same chemical composition.

- 10. The semiconductor structure of claim 9 wherein the first isolation region and the second isolation region comprise silicon oxide.

- 11. The semiconductor structure of claim 9 wherein the rotational shear stress is in a clockwise direction.

- 12. The semiconductor structure of claim 9 wherein the rotational shear stress is in a counter clockwise direction.

- 13. A method for forming a semiconductor structure comprising:

providing a semiconductor substrate having an active region mesa surrounded by an isolation trench;

forming a first isolation region having a first stress into the isolation trench;

forming a second isolation region having a second stress different than the first stress into the isolation trench, where the first isolation region and the second isolation region are sized and positioned to rotationally shear stress the active region mesa.

- 14. The method of claim 13 wherein only one of the first isolation region and the second isolation region contacts the active region mesa.

- 15. The method of claim 13 wherein both of the first isolation region and the second isolation region contact the active region mesa.

- 16. The method of claim 13 wherein the rotational shear stress is in a clockwise direction.

- 17. The method of claim 13 wherein the rotational shear stress is in a counter clockwise direction.

- 18. The method of claim 13 wherein when forming the first isolation region and the second isolation region:

the isolation trench is completely filled with a first isolation material;

a portion of the first isolation material is removed to form a void and the first isolation region; and

the second isolation region is formed into the void.

19. The method of claim 18 wherein the second isolation region is formed by:

filling the void with a silicon material; and oxidizing the silicon material to form a silicon oxide material.

20. The method of claim 19 wherein the silicon material is selected from the group consisting of amorphous silicon materials and polysilicon materials.

24a

13a

18

24b

<sup>(</sup>13b

## INTERNATIONAL SEARCH REPORT

International application No PCT/EP2006/066992

| A. CLASSIFICATION OF SUBJECT MATTER INV. H01L21/762                                                                                                                                                                                                                                                                                                         |                                                                                                       |                                                                                                  |                       |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------|--|--|--|--|--|

| According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                                                                                           |                                                                                                       |                                                                                                  |                       |  |  |  |  |  |

| B. FIELDS                                                                                                                                                                                                                                                                                                                                                   | SEARCHED                                                                                              |                                                                                                  |                       |  |  |  |  |  |

| <u> </u>                                                                                                                                                                                                                                                                                                                                                    | ocumentation searched (classification system followed by classification                               | on symbols)                                                                                      |                       |  |  |  |  |  |

| H01L                                                                                                                                                                                                                                                                                                                                                        |                                                                                                       |                                                                                                  |                       |  |  |  |  |  |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                                                                                                                                                                                               |                                                                                                       |                                                                                                  |                       |  |  |  |  |  |

| Electronic d                                                                                                                                                                                                                                                                                                                                                | ata base consulted during the international search (name of data ba                                   | se and, where practical, search terms used                                                       | 1)                    |  |  |  |  |  |

| 1                                                                                                                                                                                                                                                                                                                                                           |                                                                                                       |                                                                                                  |                       |  |  |  |  |  |

| EPO-Internal, INSPEC, COMPENDEX                                                                                                                                                                                                                                                                                                                             |                                                                                                       |                                                                                                  |                       |  |  |  |  |  |

| C. DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                                                                                                                                                                      |                                                                                                       |                                                                                                  |                       |  |  |  |  |  |

| Category*                                                                                                                                                                                                                                                                                                                                                   | Citation of document, with indication, where appropriate, of the rele                                 | evant passages                                                                                   | Relevant to claim No. |  |  |  |  |  |

| A                                                                                                                                                                                                                                                                                                                                                           | US 2004/113174 A1 (CHIDAMBARRAO DE LOS ET AL) 17 June 2004 (2004-06 paragraphs [0008] - [0045]; figur | 1-20                                                                                             |                       |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                             | ——————————————————————————————————————                                                                |                                                                                                  |                       |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                             |                                                                                                       |                                                                                                  |                       |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                             |                                                                                                       |                                                                                                  |                       |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                             |                                                                                                       |                                                                                                  |                       |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                             |                                                                                                       |                                                                                                  |                       |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                             |                                                                                                       |                                                                                                  |                       |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                             | [                                                                                                     |                                                                                                  |                       |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                             |                                                                                                       |                                                                                                  |                       |  |  |  |  |  |

| ,                                                                                                                                                                                                                                                                                                                                                           |                                                                                                       |                                                                                                  |                       |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                             |                                                                                                       |                                                                                                  |                       |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                             |                                                                                                       |                                                                                                  |                       |  |  |  |  |  |

| Forth                                                                                                                                                                                                                                                                                                                                                       | ner documents are listed in the continuation of Box C.                                                | X See patent family annex.                                                                       |                       |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                             |                                                                                                       | X See patent family annex.                                                                       |                       |  |  |  |  |  |

| * Special categories of cited documents :  "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory, underlying the                                                                                                                       |                                                                                                       |                                                                                                  |                       |  |  |  |  |  |

| considered to be of particular relevance  "E" earlier document but published on or after the international  "X" document of particular relevance: the claimed invention                                                                                                                                                                                     |                                                                                                       |                                                                                                  |                       |  |  |  |  |  |

| "L" document which may throw doubts on priority claim(s) or involve an inventive step when the document is taken alone                                                                                                                                                                                                                                      |                                                                                                       |                                                                                                  |                       |  |  |  |  |  |

| which is cited to establish the publication date of another citation or other special reason (as specified)  "O" document referring to an oral disclosure, use, exhibition or "Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such docu— |                                                                                                       |                                                                                                  |                       |  |  |  |  |  |

| other means ments, such combination being obvious to a person skilled in the art.                                                                                                                                                                                                                                                                           |                                                                                                       |                                                                                                  |                       |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                             | an the priority date claimed                                                                          | &* document member of the same patent family  Date of mailing of the international search report |                       |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                             | 6 January 2007                                                                                        | 23/01/2007                                                                                       |                       |  |  |  |  |  |

| Name and mailing address of the ISA/                                                                                                                                                                                                                                                                                                                        |                                                                                                       | Authorized officer                                                                               |                       |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                             | European Patent Office, P.B. 5818 Patentlaan 2<br>NL – 2280 HV Rijswijk                               |                                                                                                  |                       |  |  |  |  |  |

| Tel. (+31–70) 340–2040, Tx. 31 651 epo nl,<br>Fax: (+31–70) 340–3016                                                                                                                                                                                                                                                                                        |                                                                                                       | Ott, André                                                                                       |                       |  |  |  |  |  |

### INTERNATIONAL SEARCH REPORT

Information on patent family members

International application No

PCT/EP2006/066992

| Patent document cited in search report |    | Publication<br>date |                | Patent family member(s)                | Publication<br>date                    |

|----------------------------------------|----|---------------------|----------------|----------------------------------------|----------------------------------------|

| . US 2004113174                        | A1 | 17-06-2004          | CN<br>TW<br>US | 1507032 A<br>230433 B<br>2005280051 A1 | 23-06-2004<br>01-04-2005<br>22-12-2005 |