(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5778688号

(P5778688)

(45) 発行日 平成27年9月16日(2015.9.16)

(24) 登録日 平成27年7月17日(2015.7.17)

(51) Int.Cl.

H02M 3/07 (2006.01)

F 1

H02M 3/07

請求項の数 11 (全 16 頁)

(21) 出願番号 特願2012-543628 (P2012-543628)

(86) (22) 出願日 平成22年12月10日 (2010.12.10)

(65) 公表番号 特表2013-532458 (P2013-532458A)

(43) 公表日 平成25年8月15日 (2013.8.15)

(86) 國際出願番号 PCT/EP2010/069373

(87) 國際公開番号 WO2011/073095

(87) 國際公開日 平成23年6月23日 (2011.6.23)

審査請求日 平成25年12月6日 (2013.12.6)

(31) 優先権主張番号 2629/DEL/2009

(32) 優先日 平成21年12月16日 (2009.12.16)

(33) 優先権主張国 インド (IN)

(31) 優先権主張番号 2629/DEL/2009

(32) 優先日 平成22年5月14日 (2010.5.14)

(33) 優先権主張国 インド (IN)

(73) 特許権者 510000633

エスティー・エリクソン、ソシエテ、アノニム

スイス国プラン-レ-ズアト、シュマン、デュ、シャン-デ-フィーユ、39

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

最終頁に続く

(54) 【発明の名称】高耐圧反転型チャージポンプ

## (57) 【特許請求の範囲】

## 【請求項 1】

負電圧を生成する反転型チャージポンプであって、

直流入力電圧を受信する第1の端子と、

フライングコンデンサを接続する第2の端子及び第3の端子と、

出力として前記負電圧を供給する第4の端子と、

充電経路であって、

前記第1の端子に接続されており、前記第2の端子に接続された第1のスイッチング装置を駆動する第1のプリドライバ回路と、

前記第1のスイッチング装置と接続され、当該第1のスイッチング装置のピーク電流を制限する第1の電流制限金属酸化物半導体(MOS)トランジスタデバイスと、 10

前記第1の端子に接続されており、第1のカスコードデバイスを介して前記第3の端子に接続された第2のスイッチング装置を駆動する第2のプリドライバ回路とを備える、前記充電経路と、

ダンピング経路であって、

前記第1の端子に接続されており、前記第2の端子及び前記第4の端子に接続された第3のスイッチング装置を駆動する第3のプリドライバ回路と、

負帰還制御装置と、前記第3の端子に接続された第2のカスコードデバイスとに対し直列に接続され、当該負帰還制御装置のピーク電流を制限する第2の電流制限金属酸化物半導体(MOS)トランジスタデバイスと、

前記第4の端子に接続され、出力の前記負電圧を調整する前記負帰還制御装置とを備える、前記ダンピング経路とを備えることを特徴とする反転型チャージポンプ。

【請求項2】

前記第1、第2及び第3のスイッチング装置は、1つ以上の金属酸化物半導体(MOS)トランジスタを備えることを特徴とする請求項1に記載の反転型チャージポンプ。

【請求項3】

前記第1のスイッチング装置及び前記第3のスイッチング装置の前記1つ以上のMOSトランジスタは、少なくとも1つの高オン抵抗金属酸化物半導体(MOS)トランジスタと、少なくとも1つの低オン抵抗金属酸化物半導体(MOS)トランジスタとを備えることを特徴とする請求項2に記載の反転型チャージポンプ。10

【請求項4】

前記第1のスイッチング装置に含まれる前記金属酸化物半導体(MOS)トランジスタのソース端子は、前記反転型チャージポンプの前記第2の端子に接続されていることを特徴とする請求項2に記載の反転型チャージポンプ。

【請求項5】

前記第3のスイッチング装置に含まれる前記金属酸化物半導体(MOS)トランジスタのドレイン端子は、前記反転型チャージポンプの前記第2の端子に接続されていることを特徴とする請求項2に記載の反転型チャージポンプ。20

【請求項6】

単一の入力クロック信号から4相クロック信号を生成するクロック生成器を更に備えることを特徴とする請求項1に記載の反転型チャージポンプ。

【請求項7】

前記4相クロック信号は、前記第1、第2及び第3のプリドライバ回路と、前記負帰還制御装置とをそれぞれ駆動することを特徴とする請求項6に記載の反転型チャージポンプ。30

【請求項8】

バイアス電圧を、前記1つ以上の金属酸化物半導体(MOS)トランジスタに供給するバイアス生成器ブロックを更に備えることを特徴とする請求項2に記載の反転型チャージポンプ。30

【請求項9】

前記負帰還制御装置は、帰還ネットワーク、誤差増幅器、及び負帰還ループ補償器を備えることを特徴とする請求項1に記載の反転型チャージポンプ。

【請求項10】

前記第1、第2及び第3のプリドライバ回路は、1つ以上のクロックレベルシフタと、高電圧保護回路とを備えることを特徴とする請求項1に記載の反転型チャージポンプ。

【請求項11】

前記第1及び第2のカスコードデバイスは、金属酸化物半導体(MOS)トランジスタに対応していることを特徴とする請求項1に記載の反転型チャージポンプ。

【発明の詳細な説明】

40

【技術分野】

【0001】

本発明は、全体として、反転型チャージポンプに関するものである。本発明は、特に、低電圧MOSトランジスタデバイスを使用する高耐圧反転型チャージポンプに関するものである。

【背景技術】

【0002】

D C - D C 変換器は、直流電流(DC)の電源を、ある電圧レベルから別の電圧レベルに変換する電子回路である。ある種のD C - D C 変換器は、所与の入力D C 電圧源から、より高い電圧又はより低い電圧を生成するために、エネルギー蓄積及びエネルギー伝達素50

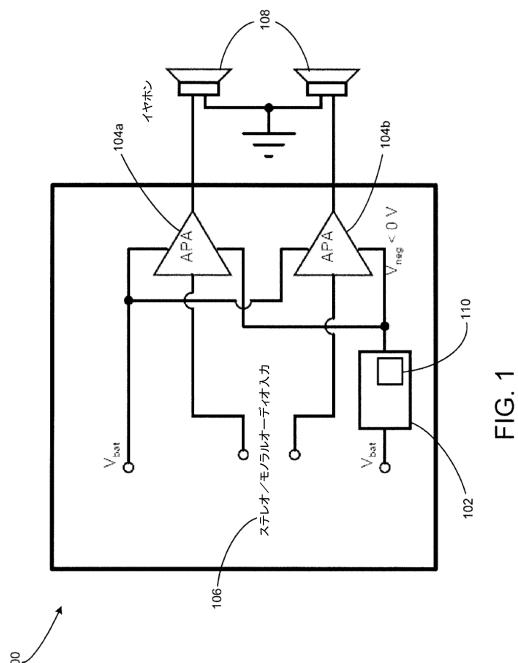

子である複数のコンデンサを備えるチャージポンプを使用する。チャージポンプを用いたDC - DC変換器は、単一の電源レール（例えば、正電圧を提供するバッテリ）から正電圧及び負電圧を得るために使用される。一般に、負電圧を生成するチャージポンプを「反転型チャージポンプ（inverting charge pumps）」と称する。反転型チャージポンプは、単一の電圧から正電圧及び負電圧の双方を生成する必要があるポータブルICにおいて、いくつかの用途に供される。図1においてそのような一実現例を示す。図1は、反転型チャージポンプ110を利用するモバイルハンドセットのオーディオサブシステム100を示す。

#### 【0003】

一般にオーディオサブシステム100は、バッテリ駆動の1つ以上のオーディオ電力増幅器（APA）104a及び104bを有する。APA104a及び104bの出力コモンモードレベルは、一般に、標準的な外部コネクタとのインターフェースを容易にするために接地（0ボルト）であることが考えられる。APAの正のレールは、一般に、バッテリ電圧（ $V_{bat}$ ）から得られた正電圧である。APAの負のレール（ $V_{neg}$ ）は、一般に、チャージポンプ110を用いたDC - DC変換器102を使用して、バッテリ電圧（ $V_{bat}$ ）から得られた負電圧である。APA104a及び104bは、ステレオ／モノラルオーディオ入力106を受信し、標準的なコネクタを介してオーディオサブシステム100（及びモバイルハンドセット）に接続されたスピーカ108に供給される出力信号を提供する。DC - DC変換器102は、一般に、誘導性DC - DC変換器と比較して減少した外部構成要素コスト及びエリアによって、 $V_{bat}$ から $V_{neg}$ を生成する、容量性チャージポンプを用いた変換器である。

#### 【0004】

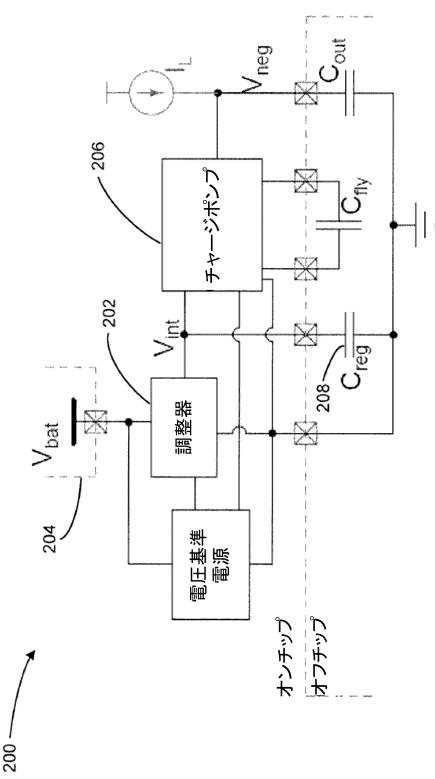

そのような容量性チャージポンプを用いた、1つのDC - DC変換器200を、図2に示す。DC - DC変換器200は、バッテリ204からの電圧 $V_{bat}$ に対して、より低い中間正電圧を生成する調整器202を使用する。調整器202は、チャージポンプ206の外側のオンチップエリア及びコンデンサC<sub>reg</sub>208を調整する追加のICピンを必要とする。ICにおけるオンチップエリアは非常に高価となり、追加のピン及び追加の外部コンデンサは、非常に大きなエリアとなり、小型移動デバイス及び最近のプリント回路基板（PCB）にはコストがかかる。

#### 【0005】

また、チャージポンプ206の出力は、例えばチャージポンプ102をトリガするクロック信号をスキップする等の既知の方法によって、又は電流制御による線形調整によって調整される。クロックスキップによる調整の結果、負荷電流における変化に基づいて、チャージポンプ出力の可変周波数スペクトルが得られる。そのような可変周波数スペクトルは、高忠実度のオーディオ・アプリケーションにおいては非常に望ましくない。（非特許文献1において公開されているような）電流モード制御による線形調整は、限られた負荷電流範囲（ $I_{max} / I_{min} \sim 40$ ）を有する。しかし、高効率のオーディオ・アプリケーションの場合、より高い負荷電流比（例えば、 $I_{max} / I_{min} \sim 1000$ ）が望ましい。

#### 【0006】

当技術分野において使用可能な別の解決方法は、高価な高電圧（HV : High Voltage）処理技術において設計された反転型チャージポンプである。しかし、チャージポンプのみに対してHV処理技術を使用することは、システムオンチップ（SoC）環境上での集積に適さない。

#### 【先行技術文献】

#### 【非特許文献】

#### 【0007】

【非特許文献1】Gerhard Thiele, Erich Bayer著, 論文「Current Mode Charge Pump: Topology, Modeling and Control（電流モード・チャージポンプ：テクノロジ、モデリング、及び制御」

#### 【発明の概要】

10

20

30

40

50

**【0008】**

開示された本発明の目的は、1つ以上の上述した欠点を排除し、1つ以上のオンチップ・プリドライバを用いて高電圧源から負電圧を生成する、反転型チャージポンプ及び回路を提供することであり、それにより、容量性チャージポンプを用いたDC-D C変換器において、追加のピン、コンデンサ及び調整器の必要性を除去することである。

**【0009】**

本発明の更なる目的は、出力において定周波数スペクトルを含む広い負荷電流範囲にわたる動作をサポートするように、出力電圧調整方式によるチャージポンプを提供することである。

**【0010】**

高耐圧反転型チャージポンプの実施形態を開示する。一実施形態において、負電圧を生成するチャージポンプは、直流(DC)入力電圧を受信する第1の端子を備える。チャージポンプは、フライングコンデンサを接続する第2の端子及び第3の端子を更に備える。更に、チャージポンプは、負電圧を出力として供給する第4の端子を備える。チャージポンプは、充電経路及びダンピング経路を更に備える。充電経路は、第1のスイッチング装置を駆動するための、第1の端子に接続された第1のプリドライバ回路を備える。第1のスイッチング装置は第2の端子に接続される。

**【0011】**

第1の電流制限デバイスは、第1のスイッチング装置と接続される。第2のプリドライバ回路は、第1の端子に接続され、第2のスイッチング装置を駆動する。第2のスイッチング装置は、第1のカスコードデバイスを介して第3の端子に接続される。

**【0012】**

ダンピング経路は、第1の端子に接続された第3のプリドライバ回路を備え、第3のスイッチング装置を駆動する。第3のスイッチング装置は、第2の端子及び第4の端子に接続される。第2の電流制限デバイスは、負帰還(ネガティブ・フィードバック)制御装置及び第2のカスコードデバイスに直列接続される。第2のカスコードデバイスは、第3の端子に接続されてもよい。また、負帰還制御装置は、第4の端子に接続される。

**【0013】**

本発明の更に別の実施形態によれば、高電圧源から負電圧を生成する回路が開示される。本回路は、高電圧源(例えば、DCバッテリ)に接続された1つ以上の高耐圧プリドライバ回路を備える。フライング容量性素子は、1つ以上の低電圧半導体デバイスを介して高電圧源に接続する。1つ以上のプリドライバ回路は、高電圧源から電圧を得るとともに、低電圧半導体デバイスを駆動する。

**【0014】**

本回路は、1つ以上の低電圧半導体デバイスを介してフライングコンデンサに接続する出力コンデンサを更に備える。また、負帰還制御装置は、出力コンデンサに接続することで、出力電圧を調整する。

**【図面の簡単な説明】****【0015】**

本発明の上述の利点及び特徴、並びに他の利点及び特徴を更に明らかにするために、添付の図面に示される本発明の特定の実施形態を参照して本発明のより具体的な説明を示す。これらの図面は、本発明の典型的な実施形態を示すにすぎず、本発明の範囲を限定するものとして考えられないことが理解される。添付の図面を用いて本発明を更に具体的かつ詳細に示し、説明する。

**【0016】**

【図1】モバイルハンドセットにおける典型的なオーディオサブシステムを示す図。

【図2】既存の反転型チャージポンプを示す回路図。

【図3】本発明の一実施形態に係る反転型チャージポンプ回路を示す図。

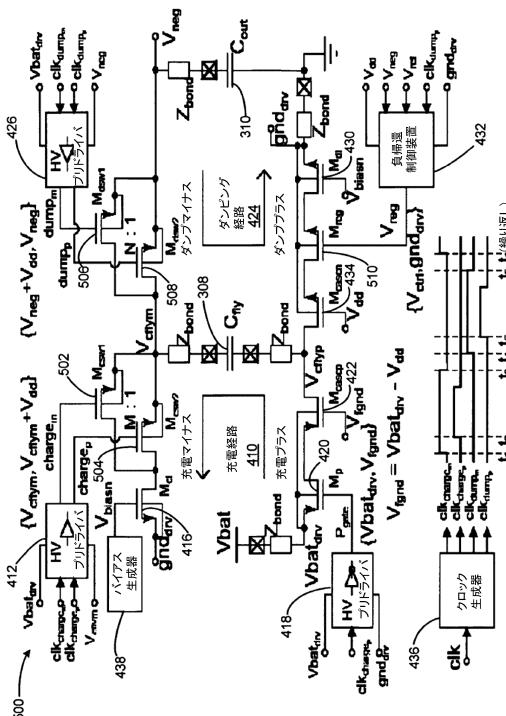

【図4】本発明の一実施形態に係る反転型チャージポンプ回路を示すブロック図。

【図5】本発明の例示的な一実施形態に係る反転型チャージポンプを示す詳細な回路図。

10

20

30

40

50

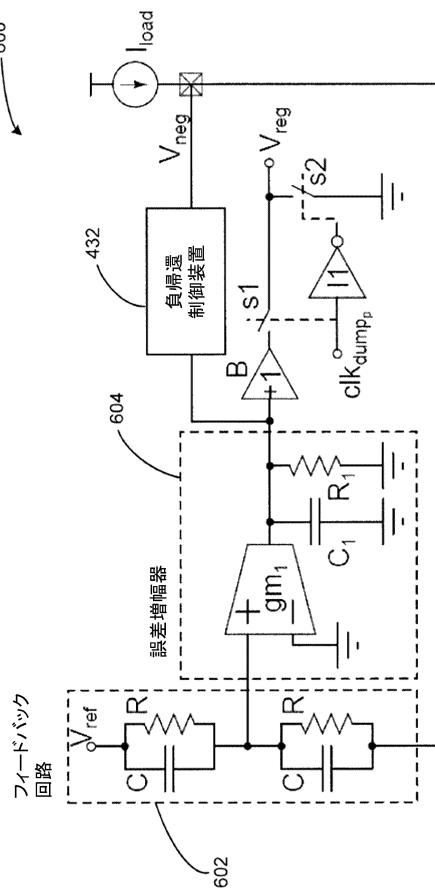

【図6】本発明の一実施形態の例に係る負帰還制御装置を示す図。

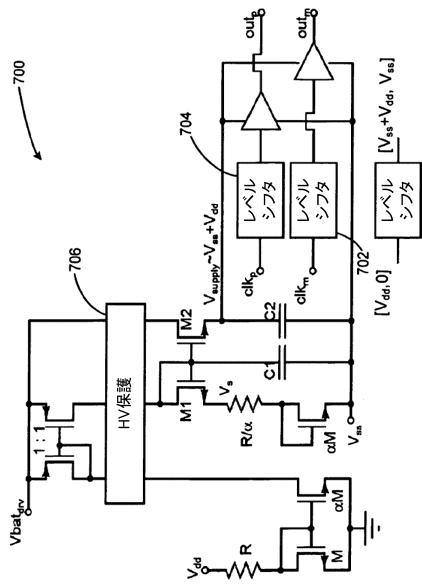

【図7】本発明の一実施形態の例に係るダンプマイナス／充電マイナス経路を示す耐HVプリドライバ回路図。

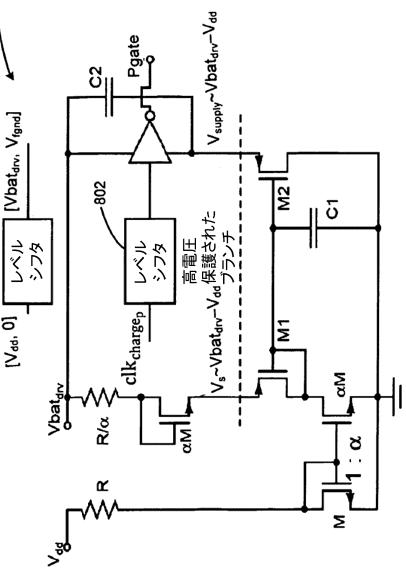

【図8】本発明の別の実施形態の例に係る充電プラス経路を示す耐HVプリドライバ回路図。

**【発明を実施するための形態】**

**【0017】**

高耐圧(HV)調整反転型チャージポンプ回路の実施形態を開示する。既存の反転型チャージポンプは、より低い範囲の出力電流、可変出力電圧周波数スペクトル、並びにオンチップエリア及びオフチップエリアの双方についての望ましくない消費という、固有の制限を有する。以下の説明から明らかとなるように、開示された反転型チャージポンプは、中間電圧調整器(例えば、202)を有さずにDCバッテリから直接入力電圧を得る。開示された反転型チャージポンプは、追加のコンデンサ(例えば、調整コンデンサC<sub>reg2</sub>08)の必要性を更に除去することにより、外部ピン、部品数及びオンチップエリアを最小限に抑える。10

**【0018】**

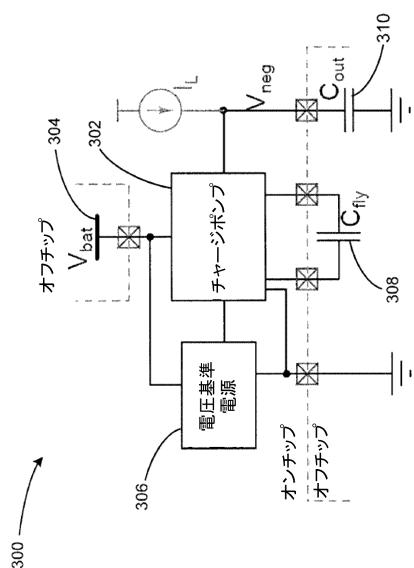

図3は、本発明の一実施形態に係る反転型チャージポンプ回路300を示す。図3に示されるように、回路300は、バッテリ又はDC電圧源304に直接接続された反転型チャージポンプ302を備える。反転型チャージポンプ302は、高電圧源(DCバッテリ)からの操作を可能にする高電圧回路を備える。当該回路は、高電圧DC電源の望ましくない影響からの保護をもたらす。また、高速のスイッチング速度を有しつつ小型であり、それにより所与の構成に対してオンチップエリアを最小限に抑える低電圧半導体デバイスを使用して、チャージポンプ302は実現される。20

**【0019】**

バッテリ304は、任意の標準的なDC電圧源であり、例えば金属イオン電池、金属ポリ電池、鉛蓄電池、金属イオンポリ電池等であるが、それらに限定されない。なお、バッテリ304は、MP3プレーヤ、移動電話、携帯用無線電話機等のポータブルデバイスにおいて、及びバッテリ電源が正のレール電圧を提供し、反転型チャージポンプが正のレールから負電圧を提供する必要がある他の同様の演算装置において使用されるタイプのものであることが好ましい。30

**【0020】**

回路300は、チャージポンプ302が必要とする種々の内部電圧(V<sub>dd</sub>、V<sub>ref</sub>、V<sub>f</sub><sub>gnd</sub>及びV<sub>biasn</sub>等)を提供する電圧基準電源306を更に備える。内部電圧は、反転型チャージポンプ302のブロックのうちの1つ以上を駆動する。なお、チャージポンプ302及び電圧基準電源306はオンチップ構成要素である。

**【0021】**

回路300は、オンチップ構成要素に加え、オフチップ構成要素を更に備える。例えば、フライングコンデンサ(C<sub>fly</sub>)308は、チャージポンプ302の2つの端子に接続され、出力コンデンサ(C<sub>out</sub>)310は、チャージポンプ302の更に別の端子に接続される。40

**【0022】**

フライングコンデンサ308は、制御された方法で、充電期間(charging phase)において予め定義された電圧まで充電され、ダンピング期間(dumping phase)において放電する。放電中のフライングコンデンサ308は、ダンピング期間中に出力コンデンサ310を充電し、このようにして出力コンデンサの両端間に形成された(developed across)電圧は、出力負電圧になる。

**【0023】**

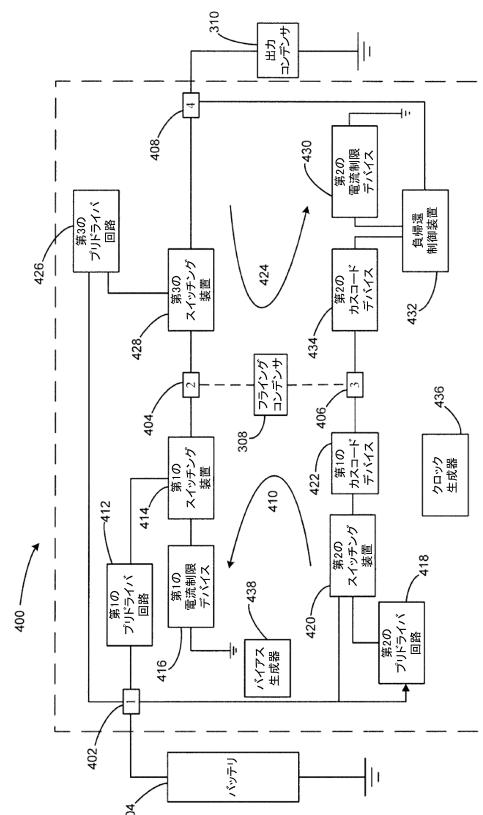

図4は、本発明の一実施形態に係る反転型チャージポンプ400を示す例示的なプロック図である。反転型チャージポンプ400は、少なくとも4つの端子402、404、406及び408を備える。チャージポンプ400の第1の端子402は、バッテリ30450

から直流( d c )入力電圧を受信するように構成される。チャージポンプ 400 の第 2 の端子 404 及び第 3 の端子 406 は、フライングコンデンサ 308 を接続するように構成される。チャージポンプ 400 の第 4 の端子 408 は、出力コンデンサ 310 を接続するように構成される。

#### 【 0024 】

上述したように、フライングコンデンサ 308 は、充電期間中に、予め定義された電圧まで充電される。この目的のために、反転型チャージポンプ 400 は、フライングコンデンサ 308 を充電するための回路素子を有する充電経路 410 を備える。例えば、充電経路 410 は、第 1 のスイッチング装置 414 を駆動する第 1 のプリドライバ回路 412 を備える。第 1 のプリドライバ回路 412 は、図 4 に示されるように、反転型チャージポンプ 400 をバッテリ 304 に直接接続できるようにする高耐圧回路である。第 1 のプリドライバ回路 412 の構成要素については、図 7 及び図 8 を参照して詳細に説明する。

10

#### 【 0025 】

第 1 のスイッチング装置 414 は、一端において第 2 の端子 404 に接続し、他端において第 1 の電流制限デバイス 416 に接続する。第 1 の電流制限デバイス 416 は、一端において第 1 のスイッチング装置 414 に接続し、他端において接地される。

#### 【 0026 】

充電経路 410 は、第 2 のスイッチング装置 420 を駆動する第 2 のプリドライバ回路 418 を更に備える。第 2 のスイッチング装置 420 は、一端において第 1 のカスコードデバイス 422 を介して第 3 の端子 406 に接続し、他端において第 1 の端子 402 に接続する。

20

#### 【 0027 】

チャージポンプ 400 は、フライングコンデンサ 308 の放電及び出力コンデンサ 310 の充電を容易にするダンピング経路 424 を更に備える。ダンピング経路は、第 3 のスイッチング装置 428 を駆動する第 3 のプリドライバ回路 426 を備える。第 3 のスイッチング装置 428 は、一端において第 2 の端子 404 に接続し、他端において第 4 の端子 408 に接続する。

#### 【 0028 】

ダンピング経路 424 は、一端において負帰還制御装置 432 及び第 2 のカスコードデバイス 434 に直列接続し、他端において接地される第 2 の電流制限デバイス 430 を更に備える。第 2 のカスコードデバイス 434 は、一端において第 3 の端子 406 に接続し、他端において負帰還制御装置 432 に接続する。

30

#### 【 0029 】

例示的な実施形態において、第 1 のスイッチング装置 414 、第 2 のスイッチング装置 420 及び第 3 のスイッチング装置 428 は、それぞれ、第 1 のプリドライバ回路 412 、第 2 のプリドライバ回路 418 及び第 3 のプリドライバ回路 426 によって駆動される 1 つ以上の金属酸化物半導体 (MOS) ツランジスタを備える。

#### 【 0030 】

また、第 1 のスイッチング装置 414 及び第 3 のスイッチング装置 428 は、少なくとも 1 つの高オン抵抗金属酸化物半導体 (MOS) ツランジスタ及び少なくとも 1 つの低オン抵抗金属酸化物半導体 (MOS) ツランジスタを備える。

40

#### 【 0031 】

本発明の一実施形態に係る反転型チャージポンプ 400 は、第 1 のプリドライバ回路、第 2 のプリドライバ回路及び第 3 のプリドライバ回路 (412 、 418 及び 426) を駆動するためのクロック信号を生成するように構成されたクロック生成器 436 を備える。クロック信号は、充電期間中に充電経路 410 における構成要素が導通 (conduct) し、ダンピング期間中にダンピング経路 424 における構成要素が導通するように、提供される。また、生成されたクロック信号のうちの少なくとも 1 つは、出力負電圧を調整するように構成された負帰還制御装置 432 を駆動する。クロック生成器 436 は、4 相信号を生成して反転型チャージポンプ 400 の構成要素を駆動することによって、チャージポン

50

プの出力における可変周波数スペクトルを防止する。

#### 【0032】

更に別の実施形態において、第1のプリドライバ回路、第2のプリドライバ回路及び第3のプリドライバ回路(412、418及び426)は、1つ以上のクロックレベルシフタ及び高電圧保護回路を備える。

#### 【0033】

また、チャージポンプ400は、1つ以上の金属酸化物半導体(MOS)トランジスタデバイスにバイアス電圧を提供するBiasn生成器438を更に備える。第1のカスコードデバイス422及び第2のカスコードデバイス434は、金属酸化物半導体(MOS)トランジスタに相当する。Biasn生成器438は、チャージポンプ400に含まれた別個のブロックとして示されているが、別の一実施形態において、バイアス生成器438は、単一のモジュールとして電圧基準電源306と統合されてもよい。10

#### 【0034】

例示的な一実現例において、負帰還制御装置432は、帰還回路(feedback network)、誤差增幅器及び負帰還ループ補償器を備える。負帰還制御装置432の構成要素については、図6を参照して詳細に説明している。

#### 【0035】

図5は、例示的な一実施形態に係る反転型チャージポンプ500を示す詳細な回路図である。図4のブロック図は図5に対応し、図5に示された回路素子は、図3及び図4に示されたチャージポンプの一例として示されている。本明細書の説明の範囲から逸脱せずに他の構成が可能であることは、当業者により理解されるであろう。20

#### 【0036】

一実施形態によれば、反転型チャージポンプ回路500は充電経路410を備える。当該充電経路によって、フライングコンデンサ308を、予め定義された電圧まで充電できる。予め定義された電圧は、反転型チャージポンプの出力において生成される必要のある負電圧の大きさに依存し、一実施形態ではチャージポンプへの高電圧直流(d.c.)入力と同一である。出力電圧は、出力コンデンサ310の両端間の電圧に相当する。

#### 【0037】

充電経路410は、それぞれM<sub>csw1</sub>502及びM<sub>csw2</sub>504等の2つの金属酸化物半導体(MOS)トランジスタデバイス(例えば、NMOSトランジスタ)を駆動する第1の高電圧プリドライバ回路412を備える。2つのMOSデバイス502及び504は、図4の第1のスイッチング装置414を形成する。30

充電経路410は、Biasn生成器438によって駆動される(図4の)第1の電流制限デバイス416として実装された電流制限MOSトランジスタデバイスM<sub>c1</sub>416を更に備える。例示的な一実施形態において、Biasn生成器438は、電流制限MOSトランジスタデバイスM<sub>c1</sub>416として実装されるうるNMOSトランジスタに対するバイアス回路に相当する。

充電経路410は、図4の第2のスイッチング装置420に対応するMOSトランジスタデバイスM<sub>p</sub>420(例えば、PMOSトランジスタ)を駆動する第2の高電圧プリドライバ418を更に備える。MOSトランジスタデバイスM<sub>p</sub>420は、一端においてV<sub>b</sub><sub>a</sub>tに接続され、他端において第1のカスコードデバイス422として実装された別のMOSトランジスタデバイスM<sub>cascp</sub>422(例えば、PMOSトランジスタ)に接続される。40

#### 【0038】

反転型チャージポンプ回路500は、出力コンデンサ310を充電するために、フライングコンデンサ308からの充電のダンピングを容易にするダンピング経路424を更に備える。一実施形態によれば、ダンピング経路424は、図4の第3のスイッチング装置428を形成する2つのMOSトランジスタデバイス(例えば、NMOSトランジスタ)M<sub>dsw1</sub>506及びM<sub>dsw2</sub>508を駆動する第3の高電圧プリドライバ426を備える。ダンピング経路424は、図4の第2の電流制限デバイス430として実装された電流制限50

MOSトランジスタ $M_{d1}$ 430を更に備える。電流制限MOSトランジスタ $M_{d1}$ 430は、負帰還制御装置432から誤差フィードバック信号を導入する電圧調整トランジスタ(例えば、PMOSトランジスタ) $M_{reg}$ 510に直列接続する。電圧調整トランジスタ $M_{reg}$ 510は、図4の第2のカスコードデバイス434として実装されるカスコードMOSトランジスタデバイス(PMOSトランジスタ)434に接続する。

#### 【0039】

反転型チャージポンプ回路500は、第1のプリドライバ412、第2のプリドライバ418、第3のプリドライバ426及び負帰還制御装置432を駆動するために必要なクロック信号を提供するクロック生成器436を更に備える。

#### 【0040】

図5に示されたような高耐圧(HV)調整反転型チャージポンプ回路500は、低電圧MOSトランジスタを利用する。高耐圧プリドライバにより、チャージポンプは、バッテリ又はHV DC電圧源 $V_{bat}$ 304から直接操作される。また、開示された出力電圧調整方式による反転型チャージポンプ500は、広い負荷電流範囲(例えば、 $I_{max}/I_{min} \sim 1000$ )にわたって操作されうる。それぞれ充電経路410及びダンピング経路424に含まれた2つのピーク電流制限トランジスタ416及び430は、ボンドワイヤ寄生( $Z_{bond}$ )が存在する状態で信頼性の高い動作を確保し、更に、充電経路ドライバデバイス及びダンプ経路ドライバデバイスにおけるジュール加熱を制限し、関連する金属が相互接続する。

#### 【0041】

電流制限トランジスタ430は、ダンプ期間誤差フィードバック調整ループの一部を更に形成する。第4の端子408が負帰還制御装置432に接続され、出力負電圧を調整する場合、ダンプ期間誤差フィードバック調整ループが形成される。ダンプ期間誤差フィードバック調整ループは、広範囲の負荷電流にわたりチャージポンプ出力電圧を調整するようダンプ期間電流を制御する合成制御素子である調整制御トランジスタ $M_{reg}$ 510とともに、電流制限トランジスタ430を直列で利用する。

#### 【0042】

第1のスイッチング装置502、504及び第3のスイッチング装置506、508を形成する2つのMOSトランジスタデバイス(例えば、NMOSトランジスタ)は、高オン抵抗スイッチ及び低オン抵抗スイッチの2つの部分に分割される。例えば、NMOSトランジスタ502及び504は、トランジスタ特性の線形領域において動作する場合にM:1の比率の抵抗を有する。MOSトランジスタデバイス502及び504のゲート端子は、第1のプリドライバ412と接続され、MOSトランジスタデバイス506及び508のゲート端子は、第3のプリドライバ426と接続される。第1のスイッチング装置414の金属酸化物半導体(MOS)トランジスタ502、504のソース端子は、充電経路410において第2の端子404に接続される。また、第3のスイッチング装置428の金属酸化物半導体(MOS)トランジスタ506、508のドレイン端子は、ダンピング経路424において第2の端子404に接続される。

#### 【0043】

動作:

例示的な実施形態によれば、反転型チャージポンプ回路500の充電経路/期間は、それぞれ、第1のプリドライバ412及び第2のプリドライバ418と関連付けられた「充電マイナス」及び「充電プラス」経路/期間に分割される。同様に、チャージポンプ回路500のダンピング経路/期間は、それぞれ、負帰還制御装置432及び第3のプリドライバ426と関連付けられた「ダンププラス」及び「ダンプマイナス」経路/期間に分割される。例示的な実施形態について、プリドライバ出力における所望の電圧レベルを図5に示す。

#### 【0044】

クロック生成器436は、プリドライバブロック(412、418及び426)、並びに負帰還制御装置432への入力としてそれぞれ供給される4相クロックを、入力クロック

10

20

30

40

50

クから生成する。図5には、一実施形態に従ってクロック生成器436によって生成されたクロック信号及び波形が示されている。その波形において示されるように、クロック生成器436は、充電経路とダンピング経路との非オーバラップ時間( $t_3 - t_4$ ,  $t_6 - t_1$ )を確保することで、( $gnd_{drv}$ ,  $V_{neg}$ )と( $V_{bat_{drv}}$ ,  $gnd_{drv}$ )との間の直接経路を除去する。

#### 【0045】

例示的な一実装例において、図5に示されたようなクロック信号 $CLK_{charge_m}$ 及び $CLK_{dump_m}$ は、典型的には、クロック信号 $CLK_{charge_p}$ 及び $CLK_{dump_p}$ と比較してより長い期間にわたって高い(デジタル「1」又は「on」)。また、クロック信号 $CLK_{charge_m}$ 及び $CLK_{dump_m}$ の期間は、それぞれクロック信号 $CLK_{charge_p}$ 及び $CLK_{dump_p}$ の前に開始する。<sup>10</sup> 実施形態のうちの1つにおいて、クロック信号 $CLK_{charge_m}$ 及び $CLK_{dump_m}$ は、クロック信号 $CLK_{charge_p}$ 及び $CLK_{dump_p}$ がそれぞれ図5に示されたように低くなつた後で終了する(又は低くなる)。クロック信号 $CLK_{charge_m}$ 及びクロック信号 $CLK_{charge_p}$ 、並びにクロック信号 $CLK_{dump_m}$ 及び $CLK_{dump_p}$ は、異なる時刻において終了するように示されているが、当然ながら、同一の時間において終了してもよい。

#### 【0046】

クロック信号 $CLK_{charge_m}$ 及びクロック信号 $CLK_{charge_p}$ は、チャージポンプ500の充電期間中にそれぞれMOSトランジスタデバイス502及び504をonにするように耐HVプリドライバを制御する。同様に、クロック信号 $CLK_{dump_m}$ 及びクロック信号 $CLK_{dump_p}$ は、チャージポンプ500のダンピング期間中にそれぞれMOSトランジスタデバイス506及び508をonにするように耐HVプリドライバを制御する。<sup>20</sup>

#### 【0047】

##### 充電プラス経路:

充電プラス経路は、ゲート酸化膜耐圧(GOI)ストレスがないようにそれぞれ[ $V_{fgnd}$ 、 $V_{bat_{drv}}$ ]電圧レベルでon及びoffされるPMOSスイッチデバイス $M_{p420}$ を備える。充電プラス経路はPMOSカスコードデバイス $M_{cascp422}$ を更に備え、そのゲートは、 $M_{cascp422}$ のソース端子が $V_{fgnd} + V_t$ ( $M_{cascp}$ の閾値電圧)を決して下回らないことを保証する高電圧保護のために、 $V_{fgnd}$ (= $V_{bat} - V_{dd}$ )にバイアスされている。カスコードデバイス $M_{cascp422}$ は、 $V_{cfltyp}$ が「0」ボルトになる場合でもスイッチングMOSデバイス $M_{p420}$ がGOIストレス及びホットキャリア注入(HCI)ストレスから保護されることを保証する。また、 $M_{cascp}$ は、[0,  $V_{bat}$ ]の範囲にある $V_{cfltyp}$ に対して更に保護される。<sup>30</sup>

#### 【0048】

##### 充電マイナス経路:

充電マイナス経路は、NMOSピーク電流制限デバイスである電流制限MOSトランジスタ「 $M_{c1}$ 」416を備え、そのゲートは、 $gnd_{drv}$ に対して $V_{bias_n}$ においてバイアスをかけられる。 $V_{bias_n}$ は、ピーク電流を所望のレベルに制限する「バイアス生成器」438において生成された適切なバイアス電圧である。同一の $V_{bias_n}$ 電圧は、更に「ダンププラス」経路において電流制限トランジスタ「 $M_{d1}$ 」430をバイアスするために使用される。ピーク電流制限は、ボンドワイヤ寄生 $Z_{bond}$ が存在する状態で充電経路及びダンプ経路において高周波数電圧のリンクギング振幅を最小限にするために実現される。また、ピーク電流を制限することにより、チャージポンプ動作中のドライバにおけるジュール加熱が限度内であることを更に確保する。<sup>40</sup>

#### 【0049】

スイッチングデバイス502、504は、 $M_{cs_w1}$ : $M_{cs_w2} = 1 : M$ の比率に分割される。Mは、 $M_{cs_w2}$ に対する $M_{cs_w1}$ のオン抵抗の比率に相当する。2つのスイッチングデバイス502、504は、それぞれ高オン抵抗スイッチ及び低オン抵抗スイッチとして動作する。従って、MOSトランジスタ502を「弱スイッチ」と呼び、MOSトランジスタデバイス504を「強スイッチ」と呼ぶ。

#### 【0050】

スイッチングデバイス 502 のバックゲートは、ダンピング期間中に  $M_{c1416}$  と関連付けられた寄生 PN ウエル・ダイオードを介して、 $gnd_{drv}$  と  $V_{neg}$  との間の導電経路を除去するように  $V_{cflym}$  に接続される。非オーバラップ時間間隔から充電期間 ( $t_6 \sim t_1$ ) に遷移する間、弱スイッチングデバイス  $M_{cs w1}$  は、 $c1k_{charge}$  相によって時間  $t_1$  において最初に on にされるため、 $V_{neg}$  から  $gnd_{drv}$  への  $V_{cflym}$  の遷移は、ボンドワイヤ寄生  $Z_{bond}$  が存在する状態で高周波数振動、高振幅振動を除去するのに十分低速である。時間  $t_2$  において、 $V_{cflym}$  が  $gnd_{drv}$  に落ち着いた後、強スイッチングデバイス  $M_{cs w2}$  は、フライングコンデンサ  $C_{fly308}$  の充電を開始する  $c1k_{charge}$  相によって on にされる。

## 【0051】

10

ダンプマイナス経路：

ダンプマイナス経路において、スイッチングデバイス 506、508 は、 $M_{ds w1} : M_{ds w2} = 1 : N$  の比率に分割される。N は、 $M_{ds w2}$  に対する  $M_{ds w1}$  のオン抵抗の比率を示す。非オーバラップ時間間隔からダンプ期間 ( $t_3 \sim t_4$ ) に遷移する間、弱スイッチングデバイス  $M_{ds w1}$  は、 $c1k_{dump}$  相によって時間  $t_4$  において最初に on にされるため、 $gnd_{drv}$  から  $V_{neg}$  への  $V_{cflym}$  の遷移は、ボンドワイヤ寄生  $Z_{bond}$  が存在する状態で高周波数振動、高振幅振動を除去するのに十分低速である。時間  $t_5$  において、 $V_{cflym}$  が  $V_{neg}$  に定着した後、強スイッチングデバイス  $M_{ds w2}$  は、フライングコンデンサ  $C_{fly308}$  から出力  $C_{out}$  コンデンサ 310 のへの充電のダンピングを開始する  $c1k_{dump}$  相によって on にされる。

20

## 【0052】

ダンププラス経路：

ダンププラス経路において、 $V_{neg}$  は、 $c1k_{dump}$  ダンプ期間において「 $-V_{ref}$ 」に調整するために、 $V_{ref}$  と比較される。負帰還制御装置 432 は、アナログ誤差型デバイスである。ピーク電流制限デバイス「 $M_{d1}$ 」430 は、 $gnd_{drv}$  に対して  $V_{biasn}$  にバイアスされたゲートを有する。 $V_{biasn}$  は、所望のレベル内にピーク電流を制限するための適切な電圧であり、 $Biasn$  生成器 438 によって生成される。

## 【0053】

30

ダンププラス経路は、ゲート端子に対して調整制御電圧  $V_{reg}$  が供給される MOS トランジスタデバイス  $M_{reg}$  を更に備える。 $M_{d1}$  とともに  $M_{reg}$  は、ダンプ期間の負帰還制御ループにおいて合成制御素子及び最終段を直列形成する。提案された合成制御素子により、広範囲の負荷電流（例えば、 $I_{max} / I_{min} \sim 1000$ ）にわたる出力電圧調整が可能になる。そのような大きな比率が可能であるのは、既存の解決方法のように、誤差増幅器出力と電源デバイス（ダンピング経路における回路部品）との間ににおいて大きな比率の電流ミラーリング・ブロック等を間接的に操作することなく、制御（電圧）が電源デバイス上で直接的に動作するためである。

## 【0054】

カスコードデバイス  $M_{cascn434}$  は、適切な電圧 ( $V_{dd}$ ) にバイアスされたゲートを有する。 $V_{cflyp}$  が  $V_{bat}$  レベルの電圧になる場合、 $M_{cascn}$  は、HCl 及び GOI ストレスから  $M_{reg}$  及び  $M_{d1}$  を保護するように構成される。

40

## 【0055】

なお、動作中の既存のチャージポンプ（例えば、図 2 の 206）は、最新技術の回路素子により形成された充電プラス経路、充電マイナス経路、ダンププラス経路及びダンプマイナス経路を備えうる。また、チャージポンプ 206 は、フライングコンデンサ  $C_{fly}$  を充電及び放電するための適切なクロック信号を生成するように構成されたクロック生成器を更に備える。しかし、開示されたチャージポンプ 302 は、少なくとも高耐圧プリドライバ回路と、プリドライバ回路及び負帰還制御装置 432 を駆動する 4 相クロック信号の使用とに起因して、既存の反転型チャージポンプ回路（例えば、206）とは異なる。

## 【0056】

負帰還制御装置

50

図6は、負帰還制御装置600の一実施形態の例を示す。なお、負帰還制御装置600は、(図4及び図5に示されたような)負帰還制御装置432の実施形態のうちの1つである。負帰還制御装置600は、図6に示されるように、一端が $V_{ref}$ に接続され、他端が $V_{neg}$ に接続される、抵抗器コンデンサ(RC)を用いたフィードバック回路602を備える。誤差増幅器604において、中点電圧を「0」ボルトと比較する。誤差増幅器604は、単一利得( $gm_1, R_1, C_1$ )段を備える。誤差増幅器の出力は、調整MOSトランジスタデバイス $M_{reg}$ のゲートを制御する前に単位利得段でバッファリングされる。

#### 【0057】

負帰還ループ補償器432は、ダンプ期間制御ループを安定させて、チャージポンプ500の過渡的ループダイナミクスが制御されることを保証するために、 $V_{neg}$ ノードと誤差増幅器604の出力との間で使用される。 $c1k_{dump}$ が「ハイ」ロジックの場合、スイッチs1は閉じ、s2は開き、制御ループが有効化される。 $V_{reg}$ ノードは、 $V_{neg}$ から「- $V_{reg}$ 」までの電圧を調整するように制御される。 $c1k_{dump}$ が「ロー」ロジックの場合、スイッチs1が開き、s2が閉じ、 $V_{reg}$ が「0」Vに接続され、それにより、ダンプ期間制御ループが無効化される。

#### 【0058】

ダンプマイナス/充電マイナス経路に対する耐HVプリドライバ:

図7は、一実施形態に係るダンプマイナス/充電マイナス経路に対する耐HVプリドライバ700の一実施形態の例を示す。例示的な一実装例において、プリドライバ412及び426(充電マイナス及びダンプマイナス)のトポロジは同一であり、高電圧プリドライバ700は、高電圧プリドライバブロック412、418、426等の一例を示す。なお、トポロジは、種々の回路設計要求に適合するよう異なってもよい。高耐圧プリドライバ回路は、1つ以上のレベルシフタ702、704及び高電圧保護回路706を有する。

#### 【0059】

充電マイナスプリドライバ412の場合、 $V_{ss}$ は、チャージポンプ動作中に、スイッチング波形である $V_{cflym}$ に接続される。 $V_{ss}$ は、充電マイナス経路に対して交互に $V_{neg}$ か $gnd_{drv}$ になる。また、ダンプマイナス経路において、 $V_{ss}$ は $V_{neg}$ に対応する。双方の場合において、それぞれの経路をon/offにするために、対応するプリドライバの出力は( $V_{ss} + V_{dd}$ )/ $V_{ss}$ に等しい必要がある。出力電圧は、それぞれ、充電マイナス経路及びダンプマイナス経路において対応するN MOSスイッチングデバイス[ $M_{csw1}, M_{csw2}$ ]及び[ $M_{dsw1}, M_{dsw2}$ ]をon/offにする。予歪基準電流(pre-distorted reference current)は、 $V_{dd}$ が抵抗器「R」及び直列N MOSトランジスタにわたって印加され、ドレイン端子及びゲート端子が共に短くなり、ユニットサイズが「M」の状態で、生成される。このようにして生成された電流は、「」だけ増加され、HV保護ブロックを通過した後に $V_{bat_{drv}}$ レベルに転送される。

#### 【0060】

HV保護ブロックを通過した後の $V_{bat_{drv}}$ レベルからのミラー電流は、ドレイン端子及びゲート端子が短くなり、ユニットサイズが「M」及びM1の状態で、抵抗器R/直列N MOSトランジスタの直列結合を流れる。

#### 【0061】

ダンプマイナス/充電マイナス経路に対するプリドライバ回路700において、バイアス電圧 $V_s$ 電圧は( $V_{ss} + V_{dd}$ )に等しい。高インピーダンス基準電圧である $V_s$ は、ドレイン端子及びゲート端子が共に短くなる状態でMOSトランジスタM1を用いて実現されるクラスBソーシング段によって、バッファリングされる。MOSトランジスタM2のドレインは、HV保護ブロックを介して $V_{bat}$ に接続され、ソース端子は、局所的に示された供給電圧 $V_{supply}$ (~ $V_{ss} + V_{dd}$ )をプリドライバに対して提供する。

#### 【0062】

コンデンサC1は、プリドライバが動作可能であり、かつ、切り替わっている場合に、スイッチング過渡的キックバックを処理するように、M1、M2のゲートにおいて、 $V_{ss}$

10

20

30

40

50

についての基準電圧に対して低インピーダンスを提供する。コンデンサC2は、 $V_{\text{supply}}$ において低インピーダンスを提供することで、高周波数スイッチング電流を提供する。2つのレベルシフタは、[ $V_{dd}$ , 0]電圧領域における2つのクロック位相を、[ $V_{ss} + V_{dd}$ ,  $V_{ss}$ ]電圧領域に変換するために使用される。

#### 【0063】

レベルシフタ702及び704は、それぞれ充電マイナス経路及びダンプマイナス経路において、電源デバイス [ $M_{csw1}$ ,  $M_{csw2}$ ] 及び [ $M_{dsw1}$ ,  $M_{dsw2}$ ] を更に駆動する局所供給電圧  $V_{\text{supply}}$  上で動作する、図7においてバッファとして示された、適切な大きさのプリドライバを駆動するために使用される、レベルシフトクロック信号を提供する。

#### 【0064】

充電プラス経路に対する耐HVプリドライバ：

図8は、充電プラス経路に対する耐HVプリドライバ800の一実施形態の例を示す。プリドライバ回路800に示されるように、PMOSスイッチデバイス  $M_p420$  をon/offにするために、 $P_{\text{gate}}$  が ( $V_{fgnd}/V_{bat}$ ) 間を変動するようとする。 $V_{fgnd} = (V_{bat} - V_{dd})$  は、Biasn生成器438によって内部で生成されたバイアス電圧である。

#### 【0065】

予歪基準電流は、 $V_{dd}$ が抵抗器「R」及び直列NMOSトランジスタにわたって印加され、ドレイン端子及びゲート端子が共に短くなり、ユニットサイズが「M」の状態で、生成される。生成された電流は「」だけ増加される。ミラー電流は、ドレイン端子及びゲート端子が共に短くなり、ユニットサイズが  $V_{bat_{drv}}$  に接続された「M」及びM1の状態で、抵抗器 R / 、直列NMOSトランジスタの直列結合を流される。

#### 【0066】

提案されたバイアス  $V_s$  電圧は、 $V_{bat_{drv}} - V_{dd}$  である。この高インピーダンス基準電圧は、ドレイン端子及びゲート端子が共に短くなった状態のM1と、 $gnd_{drv}$  に接続されたドレイン、及び局所的に示された供給電圧  $V_{\text{supply}}$  ( $\sim V_{bat_{drv}} - V_{dd}$ ) をプリドライバに対して提供するソース端子を有するM2とによって実現された、クラスBシンキング段によってバッファリングされる。クラスBシンキング段の2つのブランチは、 $V_{bat_{drv}}$  と  $gnd_{drv}$  との間で直接動作するために保護される。

#### 【0067】

また、充電プラス経路に対する耐HVプリドライバ800は、プリドライバが動作可能であり、かつ、切り替わっている場合に、スイッチング過渡的キックバックを処理するように、M1及びM2のゲートにおいて基準電圧に対して低インピーダンスを提供するコンデンサC1を備える。コンデンサC2は、 $V_{\text{supply}}$ において低インピーダンスを提供することで、高周波数スイッチング電流を提供する。

#### 【0068】

レベルシフタ（例えば、802）は、[ $V_{dd}$ , 0]電圧領域におけるクロック位相  $c1_{k_{chargep}}$  を [ $V_{bat_{drv}}$ ,  $V_{fgnd}$ ] 電圧領域に変換するために使用される。レベルシフトクロック信号は、充電プラス経路において、電源デバイス  $M_p$  の  $P_{\text{gate}}$  を更に駆動する局所供給電圧  $V_{\text{supply}}$  上で動作する、図8においてインバータとして示された、適切な大きさのプリドライバを駆動するために使用される。

#### 【0069】

当然ながら、以下の特許請求の範囲の主題は、種々の例及び本発明の原理を記述するために使用された文言に限定されず、その範囲から逸脱することなく特許請求の範囲を実施するため変形例が考えられうる。むしろ、本発明の実施形態は、本発明の構造的な均等物及び機能的な均等物の双方を包含する。

#### 【0070】

本明細書では、本発明のある特定の好適な実施形態、並びに同様のものを実施するある特定の好適な方法及び回路について説明しつつ例示したが、当然ながら、本発明は、それらに限定されず、以下の特許請求の範囲の範囲内で種々に具体化されかつ実施されること

は明らかである。

【図1】

FIG. 1

【図2】

FIG. 2

【図3】

【図4】

FIG. 3

FIG. 4

【 四 5 】

FIG. 5

【 6 】

FIG. 6

【図7】

FIG. 7

【図8】

FIG. 8

---

フロントページの続き

(74)代理人 100166660

弁理士 吉田 晴人

(72)発明者 プラブー, ジェイ. ラジャ

インド国 チエンナイ 600 073, セライユ, チェリナガル, ヴァララー ストリー

ト, プロット 45

(72)発明者 ソマヤジュラ, シャム

インド国 パンガロール 560 037, ドッダナンクンディ, フェーンズ シティ, 8

2

審査官 今井 貞雄

(56)参考文献 特開2009-011121(JP, A)

特開2002-136105(JP, A)

特開2005-348561(JP, A)

特開2005-192350(JP, A)

特開平10-248240(JP, A)

特開2001-186754(JP, A)

(58)調査した分野(Int.Cl., DB名)

H02M 3/07