(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6757289号

(P6757289)

(45) 発行日 令和2年9月16日(2020.9.16)

(24) 登録日 令和2年9月1日(2020.9.1)

(51) Int.Cl.

F 1

G06F 12/02 (2006.01)

G06F 12/02 570H

G06F 12/1081 (2016.01)

G06F 12/02 550B

G06F 12/109 (2016.01)

G06F 12/1081

G06F 12/109 100

請求項の数 10 (全 10 頁)

|                    |                               |           |                                                                                                                                                                        |

|--------------------|-------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号          | 特願2017-81927 (P2017-81927)    | (73) 特許権者 | 390019839<br>三星電子株式会社<br>Samsung Electronics<br>Co., Ltd.<br>大韓民国京畿道水原市靈通区三星路 129<br>129, Samsung-ro, Yeon<br>gton-gu, Suwon-si, G<br>yeonggi-do, Republic<br>of Korea |

| (22) 出願日           | 平成29年4月18日(2017.4.18)         |           |                                                                                                                                                                        |

| (65) 公開番号          | 特開2017-194964 (P2017-194964A) |           |                                                                                                                                                                        |

| (43) 公開日           | 平成29年10月26日(2017.10.26)       |           |                                                                                                                                                                        |

| 審査請求日              | 令和2年4月14日(2020.4.14)          |           |                                                                                                                                                                        |

| (31) 優先権主張番号       | 62/326,537                    | (74) 代理人  | 110000051<br>特許業務法人共生国際特許事務所                                                                                                                                           |

| (32) 優先日           | 平成28年4月22日(2016.4.22)         | (72) 発明者  | グースラ, マノイ ケイ<br>アメリカ合衆国 カリフォルニア州 94<br>022, ロス アルトス, ユニット 7,<br>ティンダル ストリート 575<br>最終頁に続く                                                                              |

| (33) 優先権主張国・地域又は機関 | 米国(US)                        |           |                                                                                                                                                                        |

| (31) 優先権主張番号       | 15/333,010                    |           |                                                                                                                                                                        |

| (32) 優先日           | 平成28年10月24日(2016.10.24)       |           |                                                                                                                                                                        |

| (33) 優先権主張国・地域又は機関 | 米国(US)                        |           |                                                                                                                                                                        |

| 早期審査対象出願           |                               |           |                                                                                                                                                                        |

(54) 【発明の名称】メモリの事前割当と関連されたバッファマッピング方式

## (57) 【特許請求の範囲】

## 【請求項 1】

第1のアプリケーション及び第2のアプリケーションと通信するオペレーティングシステムを利用したコンピュータ具現方法であって、

前記第1のアプリケーションから第1の物理的アドレスを受信する段階と、

前記第2のアプリケーションが、アプリケーションのオフセットを用いて前記第1のアプリケーションと通信する段階と、

データ伝達を実現するために前記第1の物理的アドレスに基づいてオペレーティングシステムレベルの仮想アドレスを決定する段階と、を含み、

前記第1のアプリケーションは、第1のページテーブル有し、前記第1のページテーブルを使用して前記第1のアプリケーションの仮想ページをメモリの物理的ページにマッピングし、前記第1のアプリケーションに対応する前記第1の物理的アドレスを決定するために第1の物理的ページフレームナンバー及び第1のオフセットを使用することによって、前記第1の物理的アドレスは決定され、

前記アプリケーションのオフセットは、前記第2のアプリケーションに対応する第2の物理的アドレスを決定するために前記第1の物理的アドレスに適用され、

前記オペレーティングシステムレベルの仮想アドレスは、前記第1の物理的アドレスのみに基づいたカーネル変換テーブルによって決定され、前記オペレーティングシステムは、前記第1の物理的アドレスのみを介して前記第1のアプリケーション及び前記第2のアプリケーションと通信することを特徴とする方法。

## 【請求項 2】

前記第1のアプリケーション又は前記第2のアプリケーションが使用者入力を受信する前にメモリの割当を遂行し、前記第1のアプリケーション及び前記第2のアプリケーションと前記割当を共有する段階をさらに含むことを特徴とする請求項1に記載の方法。

## 【請求項 3】

前記オペレーティングシステム内に多数のモジュールがあり、前記モジュールの各々は、自分のオペレーティングシステムレベルの仮想メモリを有し、

前記モジュールの全てが前記第1の物理的アドレスを使用して前記第1のアプリケーションと直接通信することを許容する段階をさらに含むことを特徴とする請求項1に記載の方法。 10

## 【請求項 4】

バッファを利用して互いに通信する單一ノードの第1のアプリケーション、第2のアプリケーション、オペレーティングシステム、及びハードウェアを利用したコンピュータ具現方法であって、

前記第1のアプリケーションが、第1のアプリケーションレベルの仮想アドレスを前記第1のアプリケーションに対応する第1の物理的アドレスに変換し、前記オペレーティングシステムに前記第1の物理的アドレスを通信する段階と、

前記第2のアプリケーションに対応する第2の物理的アドレスを決定するために、前記第1の物理的アドレスに適用されるアプリケーションのオフセットを用いて前記第1のアプリケーションと前記第2のアプリケーションとが互いに通信する段階と、 20

前記オペレーティングシステムが、前記第1の物理的アドレスを使用してオペレーティングシステムレベルの仮想アドレスを決定する段階と、を含み、

前記オペレーティングシステムレベルの仮想アドレスは、前記第1の物理的アドレスのみに基づいたカーネル変換テーブルによって決定され、前記オペレーティングシステムは、前記第1の物理的アドレスのみを介して前記第1のアプリケーション及び前記第2のアプリケーションと通信することを特徴とする方法。 25

## 【請求項 5】

前記第1のアプリケーションは、前記オペレーティングシステムの介入無しでハードウェアのオフセットを使用して計算された直接メモリアクセス(Direct Memory Access、以下、DMA)アドレスを使用して、前記ハードウェアと通信することを特徴とする請求項4に記載の方法。 30

## 【請求項 6】

前記オペレーティングシステムは、メモリバッファを事前割当し、使用者入力を受信する前に、物理的アドレスをアプリケーションにマッピングする方法を提供することを特徴とする請求項4に記載の方法。

## 【請求項 7】

前記第1のアプリケーションは、前記第1のアプリケーション、前記第2のアプリケーション、前記オペレーティングシステム、及び前記ハードウェアの間で前記バッファを使用してデータを伝達する前に、前記第1の物理的アドレス及びメモリのDMAアドレスを獲得することを特徴とする請求項4に記載の方法。 40

## 【請求項 8】

前記オペレーティングシステム内に複数のモジュールがあり、前記複数のモジュールの各々は、前記第1のアプリケーションと直接通信し、前記第1の物理的アドレスを利用して自分のオペレーティングシステムレベルの仮想アドレスを決定することを特徴とする請求項4に記載の方法。

## 【請求項 9】

データ伝達を制御する装置であって、

第1のアプリケーションが、第1のアプリケーションレベルの仮想アドレスを前記第1のアプリケーションに対応する第1の物理的アドレスに変換し、オペレーティングシステムに前記第1の物理的アドレスを通信することを許容し、第2のアプリケーションが、ア 50

プリケーションのオフセットを用いて前記第1のアプリケーションと通信することを許容するメモリマッパーを備え、

前記アプリケーションのオフセットは、前記第2のアプリケーションに対応する第2の物理的アドレスを決定するために、前記第1の物理的アドレスに適用され、

カーネル変換テーブルは、前記第1の物理的アドレスのみに基づいたオペレーティングシステムレベルの仮想アドレスを決定するために使用され、

前記オペレーティングシステムは、前記第1の物理的アドレスのみを介して前記第1のアプリケーション及び前記第2のアプリケーションと通信することを特徴とする装置。

**【請求項10】**

前記メモリマッパーは、前記第1のアプリケーションがDMAアドレス及びハードウェアのオフセットを使用して、ハードウェアと直接通信することを許容することを特徴とする請求項9に記載の装置。 10

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は一般的にメモリバッファに係り、具体的にはメモリの事前割当と関連されたバッファマッピング方式に係る。

**【背景技術】**

**【0002】**

UNIX(登録商標)基盤のストレージ/サーバーシステム内には各々が特定作業を遂行する多様なアプリケーション及び装置ドライバがある。アプリケーション、オペレーティングシステム/カーネル(*operating system(OS)/kernel*)、及びハードウェアは、効果的に通信するために、しばしばメモリバッファに順にアクセス(*pass-around*)する。通常、このような通信をする間に、アプリケーションはそのアプリケーションレベル仮想アドレス(*application-level virtual address*)をオペレーティングシステム/カーネルに伝達する。メモリバッファはアプリケーションレベル仮想アドレスを使用してドライバを呼び出し、ドライバはアプリケーションレベル仮想アドレスをオペレーティングシステム/カーネルレベル仮想アドレス(*operating system/kernel-level virtual address*)にマッピング(*mapping*)する。 30

**【0003】**

このような変換を容易にするために、仮想及び物理的メモリはページと称される扱い易いサイズのチャンク(*chunk*)に分割される。このページドモデル(*paged model*)において、仮想アドレスはオフセット(*offset*)及び仮想ページフレームナンバー(*virtual page frame number*)から構成される。プロセッサが仮想アドレスに出会う毎に、プロセッサは仮想アドレスからオフセット及び仮想ページフレームナンバーを抽出する。プロセッサはその後、仮想ページフレームナンバーを物理的ページフレームナンバーに変換してその物理的ページ内の正しいオフセットの位置にアクセスする。 40

**【0004】**

仮想アドレスを物理的アドレスに変換するために、プロセッサは第1に仮想アドレスページフレームナンバーとその仮想ページ内のオフセットを算出する。プロセッサは仮想ページフレームナンバーをプロセスページテーブルへのインデックスとして使用してそのページテーブルエントリを検索する。そのオフセットにおけるページテーブルエントリが有効であれば、プロセッサはこのエントリから物理的ページフレームナンバーを持って来る。プロセッサが仮想ページフレームナンバーを物理的フレームナンバーに変換するのに使用するテーブルはページテーブル(*page table*)と称される。

**【0005】**

仮想アドレスはオフセットを仮想ページナンバーに加算することによって計算される。

10

20

30

40

50

保護機能を強化するために、使用者領域（空間、スペース）アプリケーション及びカーネルのために別途分離されたページテーブルがある。使用者領域仮想アドレスにアクセスするために、カーネルレベルソフトウェアは使用者領域アドレスをカーネルアドレス領域にマッピングする。このプロセスは使用者領域アドレスのためにカーネルページテーブルエントリを生成することを含む。

#### 【0006】

ハードウェアに対しては、オペレーティングシステム／カーネルとハードウェアとの間のコネクションは、直接メモリアクセス（direct memory access、以下、DMA）として発生する。DMAを使用して、ハードウェア装置はCPUが介入しなくとも、コンピュータのメーンメモリから、又はコンピュータのメーンメモリへ、データを伝達できる。DMAが作動するために、メモリバッファはハードウェア装置に認識されるアドレス範囲に頻繁にマッピングされる。このアドレス範囲はI/O仮想アドレスと称される。このマッピングはアーキテクチャにも依存するが、I/O仮想アドレスとコンピュータメーンメモリの物理的アドレスとの間の変換を設定（set-up）することを含む。一般的に、これは入出力メモリ管理装置（Input/Output Memory Management Unit、IOMMU）ハードウェアを使用して発生する。幾つかのアーキテクチャにおいて、I/O仮想アドレスはコンピュータメーンメモリの物理的アドレスと同一である。

#### 【0007】

上述したマッピング方式は、ページテーブルエントリを設定することによってアプリケーションレベル仮想アドレスをオペレーティングシステムレベル仮想アドレスに最初に変換することを要求するので、オペレーティングシステム／カーネルに重い負担を与える。同様に、DMAマッピングはすべてのDMA伝送のためにその都度設定されなければならない。そこで、OS、アプリケーション、及びハードウェア間の通信がさらに効率的にできる方法が要求される。

#### 【先行技術文献】

##### 【特許文献】

##### 【0008】

【特許文献1】米国特許第8,909,727号公報

【特許文献2】米国特許第6,405,237号公報

【特許文献3】米国特許第8,504,744号公報

【特許文献4】米国特許第8,166,194号公報

【特許文献5】米国特許第7,590,777号公報

【特許文献6】米国特許第8,868,867号公報

【特許文献7】米国特許第9,092,426号公報

【特許文献8】米国特許公開第2007/0255866号明細書

#### 【発明の概要】

#### 【発明が解決しようとする課題】

##### 【0009】

上記の要求に応じるためになされた本発明は、アプリケーションレベル仮想アドレスをオペレーティングシステムレベル仮想アドレスに最初に変換する必要が無く、オペレーティングシステム／カーネルに重い負担を与えない、同様に、すべてのDMA伝送のためにDMAマッピングをその都度設定する必要が無い、ような、アプリケーション、オペレーティングシステム、及びハードウェア間の効率的な通信を可能にするコンピュータ具現方法を提供する。

#### 【課題を解決するための手段】

##### 【0010】

本発明の一実施形態による発明の概念は、オペレーティングシステムがアプリケーションと通信するために利用するコンピュータ具現方法に係る。この方法では、オペレーティングシステムがアプリケーションから直接物理的アドレスを受信し、データ伝達を実現す

10

20

30

40

50

るためにメモリの物理的アドレスに基づいてオペレーティングシステムレベル仮想アドレスを決定する。

#### 【0011】

本発明の他の一実施形態による発明の概念は、アプリケーション、オペレーティングシステム、及びハードウェアが、バッファを利用して互いに單一ノードにおいて通信するために利用するコンピュータ具現方法に係る。この方法では、アプリケーションが、アプリケーションレベル仮想アドレスを物理的アドレスに変換し、その物理的アドレスをオペレーティングシステムに対して通信する。そうすると、オペレーティングシステムは、その物理的アドレスを使用してオペレーティングシステムレベル仮想アドレスを決定する。

#### 【0012】

本発明の他の一実施形態による発明の概念は、データ伝達制御装置に係り、前記装置は、アプリケーションが自分のアプリケーションレベル仮想アドレスを物理的アドレスに変換し、その物理的アドレスをオペレーティングシステムに通信することを可能にするメモリマッパーを含む。

#### 【発明の効果】

#### 【0013】

本発明の実施形態によれば、オペレーティングシステムがアプリケーションから直接物理的アドレスを受信し、データ伝達を実現するためにメモリの物理的アドレスに基づいてオペレーティングシステムレベル仮想アドレスを決定するので、例えば、アプリケーションは単純にオフセットをバッファの開始点のDMAアドレスに加算してオフセットのDMAアドレスを決定できる。このように、アプリケーションレベル仮想アドレスをオペレーティングシステムレベル仮想アドレスに最初に変換する必要が無く、オペレーティングシステム／カーネルに重い負担を与えない、同様に、すべてのDMA伝達のためにDMAマッピングをその都度設定する必要が無い。よって、アプリケーションはカーネルの介入無しでバッファアドレスをハードウェア装置に直接伝達でき、アプリケーション、オペレーティングシステム、及びハードウェア間の効率的な通信が可能になる。

#### 【図面の簡単な説明】

#### 【0014】

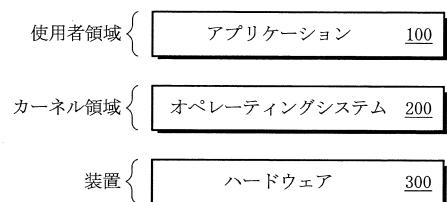

【図1】本発明の一実施形態に係る1つの可能な環境を提供する、單一ノードにおける使用者領域、カーネル領域、及びハードウェアを概念的に示した図である。

【図2】本発明の一実施形態に係るアプリケーション、オペレーティングシステム、及びハードウェアの間の通信方法を示した概略図である。

【図3】本発明の一実施形態に係る使用者領域における多様なアプリケーション、及び同一の物理的アドレスをポインティングし、バッファ共有を可能にするカーネル内の相異なる仮想アドレスを示した概略図である。

【図4】本発明の一実施形態に係るアプリケーション、オペレーティングシステム、及びハードウェアの間の通信方法を示した概略図である。

#### 【発明を実施するための形態】

#### 【0015】

本発明に係るシステムでは、オペレーティングシステムが、メモリバッファが通過される毎にカーネルレベルページテーブル基盤の変換を設定する必要がない。本開示では、アプリケーションは物理的アドレスをカーネルに伝達する。本発明の一実施形態によれば、カーネルはこのようなバッファのために要求されるマッピングを有している。従って、カーネルは仮想アドレスを計算でき、その度にマッピング動作を遂行しなくともよい。すべてのカーネルモジュールが同一の仮想アドレス領域を共有するので、どのオペレーティングシステムモジュール（メモリに割当されたオペレーティングシステムモジュールのみならず）も、物理的アドレスを使用して仮想アドレスを獲得し、バッファ上で動作できる。

#### 【0016】

相異なるアプリケーションの間で、通信がバッファオフセットを使用して発生する。アプリケーションは仮想アドレスを使用してバッファ上で動作する。アプリケーションは、

単純にオフセットをバッファの開始点の仮想アドレスに加算して自分の仮想アドレスを計算できる。

#### 【0017】

アプリケーションは、単純にオフセットをバッファの開始点のDMAアドレスに加算してオフセットのDMAアドレスを決定できる。アプリケーションはカーネル介入無しでバッファアドレスをハードウェア装置に直接伝達できる。

#### 【0018】

本開示は單一ノードの状況に対して開示しているが、本発明はこれに制限されない。

#### 【0019】

図1は本発明の一実施形態に係る1つの可能な環境を提供する、單一ノード(sing 10 le node)における使用者領域(user space)、カーネル領域(kernel space)、及びハードウェアを概念的に示す。図示されたように、使用者領域を形成するアプリケーション100、オペレーティングシステム/カーネル200、及びハードウェア300は互いに通信して、使用者の要請を受信し、実行する。ハードウェア300は多様な装置、中央処理装置、及びシステムメモリを含む。

オペレーティングシステム200は、使用者領域を形成するアプリケーション100及びハードウェア300の間のインターフェイスを担い、且つ、中でもアプリケーション100にシステムメモリへのアクセスを可能にする。装置ドライバは一般的にオペレーティングシステム200の一部である。メモリマッパーはイメージ及びデータファイルを使用者領域のアプリケーション内にマッピングする。メモリマッピングにおいて、ファイルのコンテンツは仮想アドレスと連結(link)される。

#### 【0020】

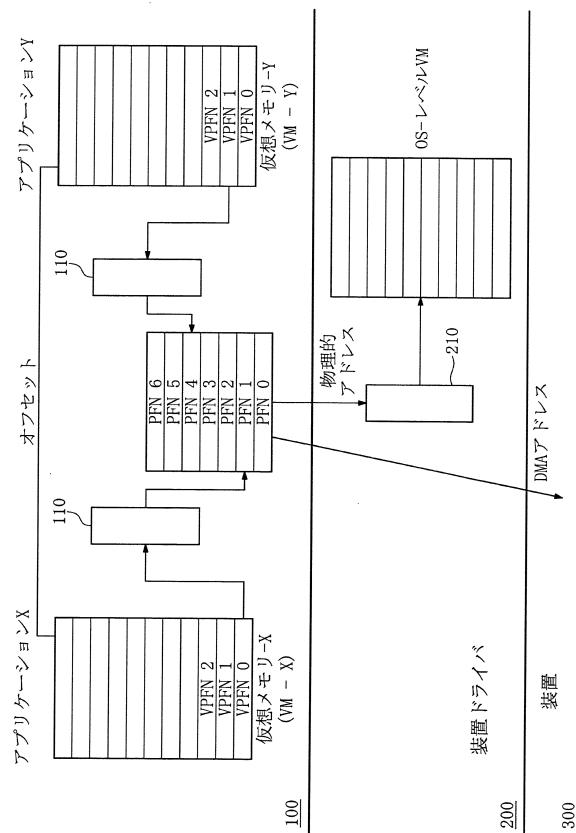

図2は本発明の一実施形態に係るアプリケーション、オペレーティングシステム、及びハードウェアの間の通信方法を示した概略図である。アプリケーション100に関しては、2つのアプリケーション、アプリケーションX及びアプリケーションYが例示される。2つのアプリケーションの各々は自分の仮想アドレスのセットと共に自分の仮想メモリVMを有し、これは図2のVM-X及びVM-Yで示されている。

また、各アプリケーションは自分の各々の仮想ページをメモリの物理的ページにマッピングする自分のページテーブル110を有する。例えば、図示されたように、アプリケーションXの仮想ページフレームナンバー0(VPFN0)は物理的ページフレームナンバー1(PFN1)のメモリにマッピングされ、アプリケーションYの仮想ページフレームナンバー1(VPFN1)は物理的ページフレームナンバー4(PFN4)のメモリにマッピングされる。

#### 【0021】

ページテーブル110は仮想ページフレームナンバーをオフセットとして使用してアクセスされる。仮想アドレスを物理的アドレスに変換するために、仮想アドレスページフレームナンバー及びその仮想ページ内のオフセットが先に決定される。仮に仮想メモリアドレスが有効であり、テーブルエントリが有効であれば、プロセッサは物理的ページフレームナンバーを取り上げ、これにページサイズを乗じて、物理的メモリのページのベース(base)アドレスを獲得する。その後、オフセットが加えられる。

#### 【0022】

例えば、図2に示されたように、ページサイズが $0 \times 2000$ であると仮定する。VM-Yの $0 \times 2194$ のアドレスに対して、プロセッサは前記アドレスを仮想ページフレームナンバー1内の $0 \times 194$ のオフセットに変換する。この仮想ページフレームナンバー1は物理的ページフレームナンバー4にマッピングされ、これは $0 \times 8000$ ( $4 \times 2000$ )から開始する。 $0 \times 194$ のオフセットを物理的ページフレームナンバーに加えて、最終物理的アドレス $0 \times 8194$ を生成する。

従来のアプリケーションは仮想アドレスと仮想アドレスのベースアドレスに対するオフセットと、のみを使用して互いに通信するが、本システムは、アプリケーションが物理的アドレスを使用してカーネルと通信できるようにする。図示されたように、カーネル変換

10

20

30

40

50

テーブル210は物理的アドレスをオペレーティングシステムレベル仮想アドレスに変換するのに使用される。カーネル変換テーブル210は物理的アドレスの仮想アドレスへの変換を可能にし、各オペレーティングシステムに特有(OS-specific)であり得る。

【0023】

本発明の一実施形態によれば、メモリは、アプリケーション100と事前割当(Pre-allocation)及び共有され、従って、アプリケーション100及びオペレーティングシステム200は共に物理的アドレステーブルにアクセスできる。ここで使用された“事前割当(Pre-allocation)”は、アプリケーション/カーネル/ハードウェアの各ドメイン間のデータを伝達するためにバッファが使用される前に割当されることを意味する。また、オペレーティングシステム200内の相異なるモジュールは、すべてのモジュールが同一の仮想アドレス領域を共有する場合、物理的アドレスを自分のオペレーティングシステムレベル仮想アドレスに変換する。

各オペレーティングシステムが物理的アドレスを仮想アドレスに変換するのに使用する方法は、各オペレーティングシステムのアーキテクチャに依存する。例えば、リナックス(登録商標)オペレーティングシステムは、アドレスの或る特定範囲に対する単純な算術演算を使用して物理的アドレスを仮想アドレスに変換する。リナックス(登録商標)で具現される場合、本システムの事前割当されたバッファは、物理的アドレスに到達するために単純な算術が使用されたこのようなアドレス範囲に属する。一部の他のオペレーティングシステムは相異なるメカニズムを通じてこの作業を遂行される。

【0024】

この場合アプリケーションは、オフセットのDMAアドレスを単純にバッファの開始点のDMAアドレスにオフセットを加えて計算できる。このように、アプリケーションはオペレーティングシステム200の介入無しでハードウェア300装置にバッファアドレスを直接伝達できる。

【0025】

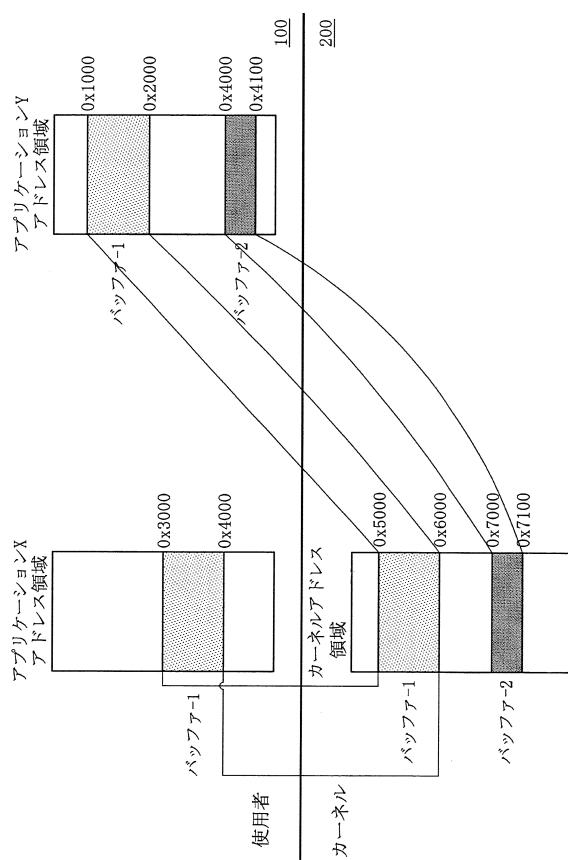

図3は本発明の一実施形態に係る、使用者領域における多重アプリケーション、及び、同一の物理的アドレスをポインティングし、バッファ共有を可能にするカーネル内の相異なる仮想アドレスを示した概略図である。図3ではアプリケーション使用者領域100のアプリケーションX及びアプリケーションYが例示されている。アプリケーションXにおいて“バッファ-1”とラベルされたデータはアプリケーションXのアドレス領域0×3000に格納される。このデータは、例えば図2に示されたプロセスを使用してカーネルアドレス領域0×5000に変換される。

同一のデータ(バッファ-1)は、アプリケーションYのアドレス領域アドレス0×1000のデータに対応するが、2つのアプリケーションX及びYは物理的アドレスを使用して同一のデータを指し示すことができる。“バッファ-2”とラベルされたデータはアプリケーションYの仮想アドレス0×4000に格納され、これはカーネルアドレス領域0×7000に対応する。カーネルモジュールが同一の仮想アドレス領域を共有するという事実のため、如何なるオペレーティングシステムモジュールも図3に示されたカーネルアドレスを使用して仮想アドレスを得る。

【0026】

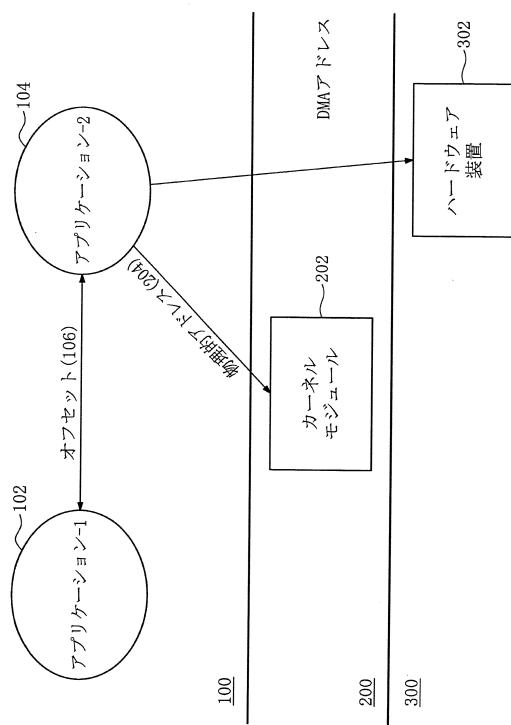

図4は本発明の一実施形態に係るアプリケーション、オペレーティングシステム、及びハードウェアの間の通信方法を示した概略図である。具体的には、図4の実施形態は使用者領域(アプリケーション100)のアプリケーション-1(102)及びアプリケーション-2(104)がオフセット106を使用して互いに通信し、アプリケーション-2(104)は物理的アドレス204を使用してカーネルモジュール202と通信することを示す。アプリケーション(例えば、アプリケーション-2(104))はオフセットを利用して生成されたDMAアドレスを使用してハードウェア装置302と直接的に通信できる。

【0027】

10

20

30

40

50

本発明の一実施形態によれば本システムは、機械によって実行可能な少なくとも1つのコードセクションを有するコンピュータプログラムが格納されたコンピュータ読出し可能な格納媒体を含み、これによって上述したような段階を機械に遂行させる。

【0028】

本発明の一実施形態によれば、本システムはハードウェア、ソフトウェア、又は、ハードウェアとソフトウェアの組合せにより具現できる。本開示は単1のコンピュータシステムを含む單一ノード具現に中心に説明しているが、これは互いに異なる要素が複数個の相互連結されたコンピュータシステムに亘って散在している分散方式において使用するよう適応できよう。任意の種類のコンピュータシステム又は装置は、本願に記載された方法を遂行するように適応するのに適合できる。典型的なハードウェアとソフトウェアの組合せは、ローディングされて実行される時、ここに記述された方法を遂行するようにコンピュータシステムを制御するコンピュータプログラムを有する汎用コンピュータシステムである。

【0029】

本システムは、上述した方法の具現を可能にするすべての機能を含み、且つコンピュータシステムにローディングされる時、この方法を遂行できる、コンピュータプログラム製品に組込み可能である。本文脈で“コンピュータプログラム”とは、情報処理能力を有するシステムが特定の機能を、(a)直接遂行するように意図された、若しくは、(b)1)別の言語、コード、又は表記法に変換、2)相異なる材質形態に再生、の中でいずれか1つ、或いは双方を行った後に遂行するように意図された命令のセットの、何らかの言語、コード、又は表記法による何らかの表現を意味する。

【0030】

本発明が特定な実施形態を参照して説明されたが、当業者ならば本発明の範囲を逸脱しない範囲内で多様な変更をなし、等価物で置換できることを理解できよう。また、本発明の範囲を逸脱せずに本発明の教示に特定状況又は特定材料を適応させる多くの変形が可能であろう。従って、本発明の開示は、本開示が開示された特定実施形態に限定されず、本発明が添付された請求の範囲内に属するすべての実施形態を含むことを意図している。

【符号の説明】

【0031】

|                  |                  |    |

|------------------|------------------|----|

| 100              | アプリケーション         | 30 |

| 102              | アプリケーション-1       |    |

| 104              | アプリケーション-2       |    |

| 106              | オフセット            |    |

| 110              | ページテーブル          |    |

| 200              | オペレーティングシステム     |    |

| 202              | カーネルモジュール        |    |

| 204              | 物理的アドレス          |    |

| 210              | カーネル変換テーブル       |    |

| 300              | ハードウェア           |    |

| 302              | ハードウェア装置         | 40 |

| P F N n          | 物理的ページレームナンバー-n  |    |

| V M              | 仮想メモリ            |    |

| V M - X, V M - Y | 仮想メモリ-X, 仮想メモリ-Y |    |

| V P F N n        | 仮想ページフレームナンバー-n  |    |

【図1】

【図2】

【図3】

【図4】

---

フロントページの続き

(72)発明者 ゴルラプディ, ヴェンカタ バース プラカシュ

アメリカ合衆国 カリフォルニア州 95051, サンタ クララ, #60, ホームステッド ロ

ード 3455

審査官 後藤 彰

(56)参考文献 特開2003-248626 (JP, A)

特開2001-22640 (JP, A)

米国特許第9092426 (US, B1)

米国特許出願公開第2015/0095610 (US, A1)

(58)調査した分野(Int.Cl., DB名)

G 06 F 12/02

G 06 F 12/1081

G 06 F 12/109