**(19) 대한민국특허청(KR)**

**(12) 특허공보(B1)**

(51) Int. Cl.<sup>5</sup>

G11C 11/34

(45) 공고일자 1991년 11월 21일

(11) 공고번호 특 1991-0009552

(21) 출원번호 특 1989-0000744 (65) 공개번호 특 1990-0012269

(22) 출원일자 1989년 01월 25일 (43) 공개일자 1990년 08월 03일

(71) 출원인 현대전자산업 주식회사 정몽현

서울특별시 종로구 계동 140-2

(72) 발명자 한광마

경기도 성남시 태평2동 3307-123

(74) 대리인 이병호

**심사관 : 김영길 (책자공보 제2572호)**

**(54) 듀얼 포트 램의 종재회로**

**요약**

내용 없음.

**대표도**

**도1**

**영세서**

[발명의 명칭]

듀얼 포트 램의 종재회로

[도면의 간단한 설명]

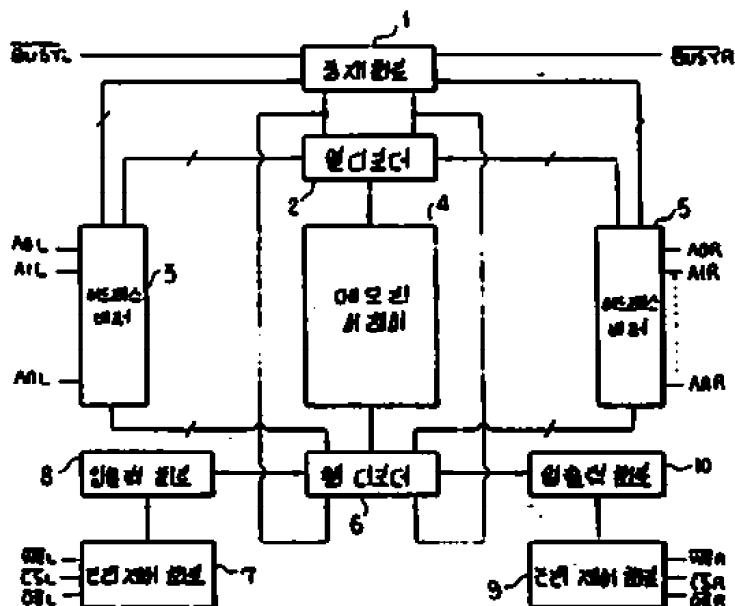

제1도는 듀얼 포트 램의 블럭도.

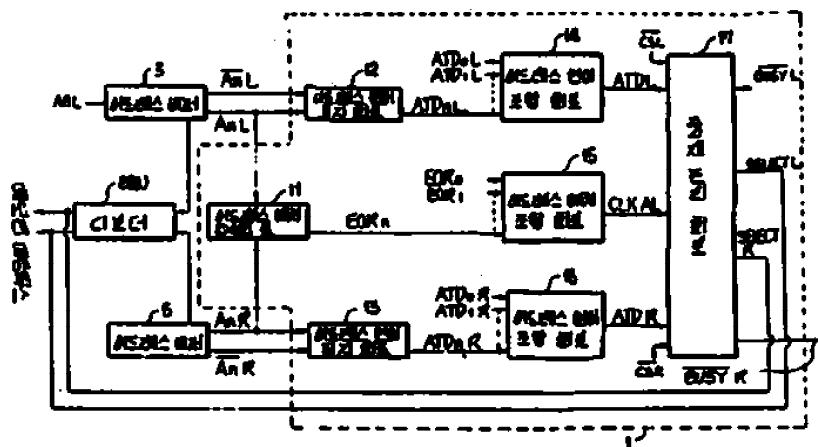

제2도는 본 발명에 따른 종재회로의 블럭도.

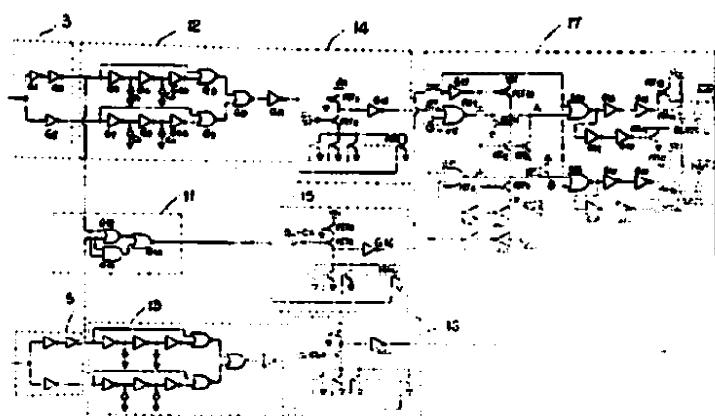

제3도는 제3도의 상세회로도.

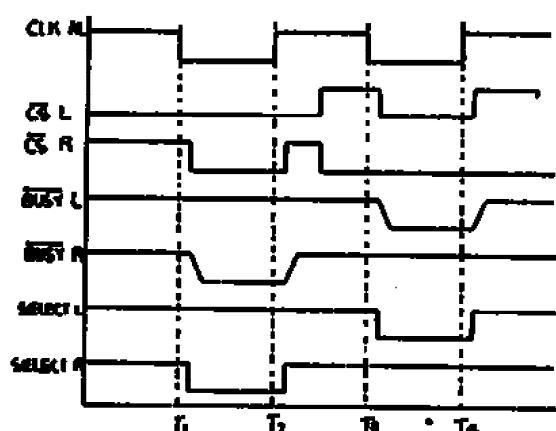

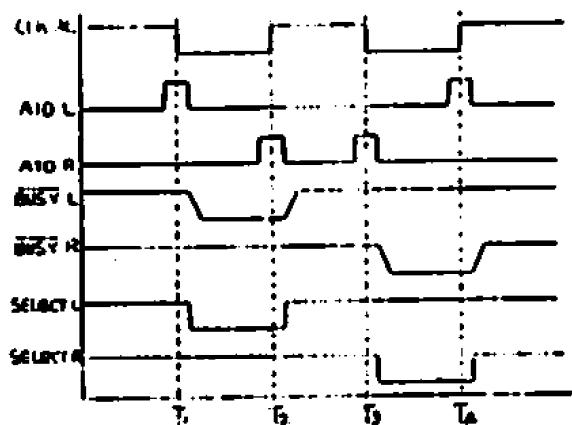

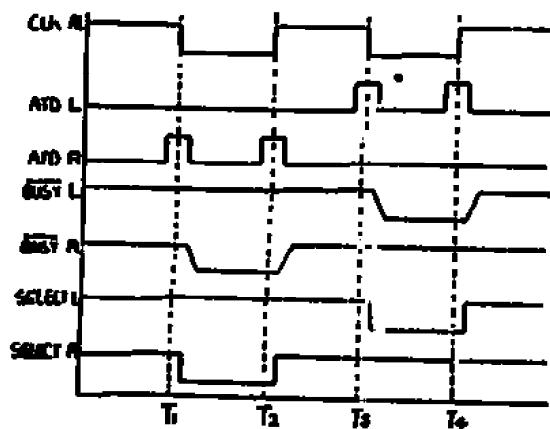

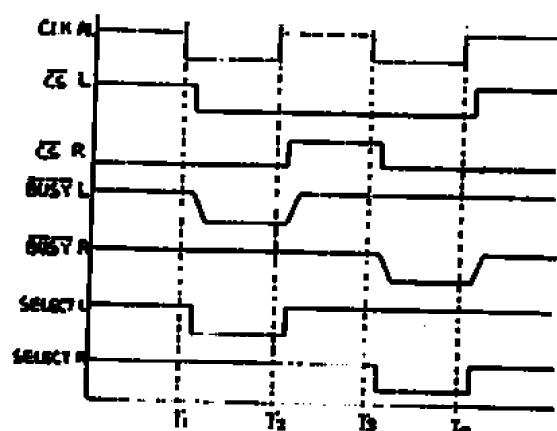

제4a도 내지 제4d도는 본 발명에 따른 종재회로의 동작설명을 위한 타이밍도.

\* 도면의 주요부분에 대한 부호의 설명

1 : 종재회로 2 : 열디코더

3 및 5 : 어드레스버퍼 4 : 메모리 어레이

6 : 행디코더 7 및 9 : 논리제어회로

8 및 10 : 입출력회로 11 : 어드레스 매치 감지회로

12 및 13 : 어드레스 천이 감지회로 15 : 어드레스 매치 조합회로

14 및 16 : 어드레스 천이 조합회로 17 : 종재논리회로

[발명의 상세한 설명]

본 발명은 듀얼 포트 램(DUAL PORT RAM)이 종재(ARBITRATION)회로에 관한 것으로, 특히 램 동작중 우측포트와 좌측포트, 즉 양포트가 동일위치의 동일 메모리 셀을 선택하여 동시에 서입 또는 판독하려고 할때, 어느 한쪽 포트의 램동작을 허용하고 다른쪽 포트는 그 기간 동안 동일 셀에 대한 램동작이 금지되도록 구성한 신규의 듀얼 포트 램의 종재회로에 관한 것이다.

일반적으로 듀얼 포트 램(DUAL PORT RAM)은 같은 메모리 용량을 놓고 좌측포트와 우측포트, 즉 듀얼 포트에서 서입(WRITE) 및 판독(READ) 동작이 동시에 가능하도록 하자는 견지에서 설계되고 개발되었다. 이러한 듀얼 포트에서의 램동작은 각 포트가 메모리 어레이(MEMORY ARRAY)중에서 서로 다른 메모리 셀(MEMORY CELL)을 선택했을 때 가능한 것으로 만약에 램동작중 양포트가 같은 위치의 동일 메모리 셀을 선택하여 동시에 서입 또는 판독을 하려고 하는 경우 일정한 원칙에 의해 한쪽 포트만이

램동작이 허용되고 다른쪽 포트는 그 기간동안 동일셀에 대한 램동작이 금지되는 종재회로(ARBITRATION CIRCUITS)가 필요하다.

본 발명은 듀얼 포트 램의 종재회로에 관한 것으로서 다음의 세가지 논리원칙에 의해 동일셀에 대한 듀얼 포트의 램동작을 조정 종재한다.

첫번째 논리 원칙은 일정셀에 대한 어드레스(ADDRESS)선택이 먼저 이루어진 포트를 동작이 허용되도록 하고, 동작이 허용된 포트가 일정셀에 대해 램동작을 하고 있는 시간동안은 다른쪽 포트로부터의 동일셀에 대한 램동작을 금지하는 어드레스 종재논리회로이다.

둘째는 칩 셀렉트(CHIP SELECT)종재논리로서 듀얼 포트의 어드레스가 이미 동일 셀 선택을 위해 매치(MATCH)가 된 상태(양 포트의 어드레스가 같은 상태)에서 양포트의 칩 셀렉트 신호가 먼저 인에이블(ENABLE)된 포트가 동작이 허용되고 다른쪽 포트는 그 시간동안 동일셀에 대한 동작이 금지되는 논리원칙이다.

셋째는 양포트로부터의 어드레스 또는 칩 셀렉트 신호가 상기 어드레스 종재논리와 칩 셀렉트 종재논리, 두 논리에 의해 구별될 수 없는 동시신호로 입력되었을 때 항상 좌측포트의 동작을 허용하고 우측포트는 그 시간동안 동일 셀에 대한 동작을 금지하는 동시신호 종재논리이다.

따라서, 본 발명은 듀얼 포트 램의 종재회로가 상기 세가지 종재논리원칙을 구현하면서 종재논리가 성립 또는 해제되었을때의 프래그(FLAG) 신호인 **BUSY**의 응답시간을 신속하게 하여 CPU가 이를 감지하는 시간을 종전보다 빠르게 개선하였고 안정된 동작을 제공하는데 그 목적이 있다.

본 발명의 듀얼 포트 램의 종재회로에 의하면 상기 종재논리원칙과 **BUSY**의 빠른 응답시간, 안정된 종재회로 동작을 구현하기 위해 다음과 같은 특징적인 논리회로 및 구성으로 설계된다. 즉 동일 셀에 대한 어드레스의 선택이 어느쪽 포트부터 일어났는지를 판별하기 위해서 각 포트의 모든 어드레스 버퍼(ADDRESS BUFFER)에 어드레스 천이감지회로(ADDRESS TRANSITION DETECTION CIRCUIT)를 연결 사용하고, 모든 어드레스 천이감지회로의 출력들은 어드레스 천이조합회로를 통해 각 포트별로 조합되어 하나의 클럭(CK, ATDL, ATDR)을 만들고 이를 종재논리회로에 인가한다. 또한 양포트의 어드레스가 동일셀 선택을 위해서 같은 논리신호가 되었는지를 판별하기 위해 양포트의 어드레스 버퍼의 정신호 출력들을(An L, An R) 입력으로 하는 어드레스 매치감지회로(EXCLUSIVE OR FUNCTION)를 채택하고, 각 어드레스 매치감지회로의 출력들을 입력으로 하는 어드레스 매치조합회로를 통해 모든 어드레스가 동일한지 여부를 클럭(CLK AL)으로 만들어 종재논리회로에 인가한다. 각포트의 어드레스 천이 조합회로의 출력들과 어드레스 매치조합회로의 출력, 각포트의 칩 셀렉트 신호의 출력(CS L, CS R)들을 입력으로 하는 종재논리회로는 상기 세가지 종재 논리원칙에 따라 동일셀에 대한 듀얼포트의 램동작을 종재하며 **BUSY** L와 **BUSY** R 신호를 출력으로 하여 CPU가 이를 감지할 수 있도록 한다.

이하, 첨부된 도면을 참조하여 본 발명을 상세히 설명하기로 한다.

제1도는 일반적인 듀얼 포트 램을 설명하기 위한 블록도로서, Ao L 내지 An L의 좌측 포트 어드레스 신호 및 Ao R 내지 An R의 우측포트 어드레스 신호가 어드레스 버퍼(3 및 5)에 각기 인가되어, 이 인가된 신호들을 정신호 및 부신호(예를 들어 Ao 및 **Ao**)로 변환시키는 상기 어드레스 버퍼(3 및 5)는 메모리 어레이(4)를 선택하기 위한 열디코더(2)와 행디코더(6) 그리고 이 열, 행디코더(2 및 6)를 인에이블(ENABLE)하기 위한 종재회로(1)에 각각 접속된다. 이 종재회로(1)는 다시 상기 열, 행디코더(2 및 6)를 통해 상기 메모리 어레이에 접속된다.

또한 논리제어회로(7 및 9)는 칩의 동작 또는 정지 상태를 제어하는 **CS** 신호, 칩의 판독 또는 서입 상태를 제어하는 **WE** 신호, 판독된 데이터를 출력시키는 상태를 조정하는 **OE** 신호로 구성되어, 각 포트의 논리제어 회로는 입출력회로(8 및 10)를 제어한다. 동일셀에 대한 양포트의 선택이 이루어지 는 경우와 보통 상태의 칩 동작의 경우는 종재회로(1)의 출력인 **BUSY** L 및 **BUSY** R 신호상태로 판별할 수 있다.

제2도는 상술한 **BUSY** 제어신호 처리를 신속 정확하게 하기 위해 본 발명에 따라 새로이 구성된 상기 듀얼 포트 램의 종재회로(1)의 블록도로서, Ao 내지 An까지의 어드레스 신호중 An신호만을 발췌하여 설명하기로 한다. 여기서 첨자 L은 좌측 포트 그리고 R은 우측 포트를 의미한다.

먼저, 좌,우측 포트의 어드레스 신호 An L 및 An R 신호가 양포트의 어드레스 버퍼(3 및 5)에 인가되면 이 어드레스 버퍼(3 및 5)는 **An** L, An L 및 **An** R, An R 신호를 생성하여, 이를 신호들을 어드레스 천이 감지회로(12 및 13) 및 열, 행디코더(2 및 6)에 인가시킨다. 또한, 상기 An L 및 An R 신호는 어드레스 매치 감지회로(11)에 인가되어 이 회로(11)에서 An L  $\oplus$  An R 신호인 EoRn 신호(실제로는 EoRo, EoR1, EoR2...EoR7임)를 생성하여 어드레스 매치 조합회로(15)에 인가시킨다. 그리하여, 상기 어드레스 매치 조합회로(15)에서는 상기 EOR 신호들을 조합하여 한 개의 클럭펄스 CLK AL 신호를 생성하여 종재논리회로(17)에 인가시킨다.

한편, 상기 어드레스 천이 감지회로(12 및 13)에서는 상기 어드레스 버퍼(3 및 5)에서 각각 출력되는 2개의 신호를 일정시간지연, 변환하여 ATD 신호(실제로는 ATD0, ATD1, ATD2...TDn)를 생성하고, 이 신호들(ATDn L 및 ATDn R)을 어드레스 천이 조합회로(14 및 16)에 인가시키면, 이 회로(14 및 16)에서는 인가된 신호들을 조합하여 ATD L 및 ATD R 신호를 생성한다음, 이 신호들(ATD L 및 ATD R)을 상기 종재 논리회로(17)에 인가시킨다.

상기 종재 논리회로(17)에서는 상술한 신호들의 인가에 따라 SELECT 및 **BUSY** 출력단자에 논리적

“고” 또는 “저” 신호가 출력되는데, **BUSY** 출력은 마이크로 프로세서의 CPU 동작을 제어하는 데 이용되고, 셀렉트 단자 출력은 상기 열, 행디코더(2 및 6)에 접속되어, 이 디코더(2 및 6)의 동작을 제어하게 된다.

제3도는 제2도의 상세 회로로서, 좌측 포트의 어드레스 신호  $A_n L$ 은 NOT 논리게이트 G1 및 G2를 경유한  $A_n L$  신호와 NOT 논리게이트 G6를 경유한  $\overline{A_n} L$  신호로 분리되는데, 전자인 상기  $A_n L$  신호는 직접 그리고 NOT 논리게이트 G3, G4 및 G33 그리고 이들 사이에 접지된 캐패시터 C1 및 C2로 구성된 지연회로를 경유해 NOR 게이트 G5에 입력되고, 후자인  $\overline{A_n} L$  신호는 직접 그리고 NOT 논리게이트 G7, G8 및 G34 그리고 이들 사이에 접지된 캐패시터 C3 및 C4로 구성된 지연회로를 경유해 NOR 게이트 G9에 각각 입력된다.

따라서, 상기 NOR 게이트 G5 및 G9의 각각의 출력은 NOR 게이트 G10을 경유해 NOT 게이트 G11에서 반전되어 ATDn 펄스가 생성된다(본 명세서에서는 편의상 하나의 ATDn 펄스 생성과정만 세술하고 있지만, 실제로는 상술한 회로가 여러개 나열되어 ATD1, ATD2, ATD3…ATDn 펄스가 생성된다). 상기 ATDn 펄스신호가 FET1의 게이트 단자에 인가되는데, 이 펄스신호가 High 상태(즉 어드레스 천이가 일어난 상태)이면 FET1이 ON되고 칩 셀렉터 신호의 CSL.CSR가 논리적으로 High 상태에서 FET2와 FET3의 접속점은 노리적으로 LOW 상태가 된다. 이 상태가 NOT 게이트 G15에서 반전되어 NOR 게이트 G18의 한 입력단자에 인가된다.

한편, 우측 포트의 어드레스 신호  $A_n R$  또한 상술한 좌측 포트의 어드레스 신호  $A_n L$  전달과정과 동일한 동작으로, 어드레스 버퍼(5), 어드레스 천이 감지회로(13)를 거쳐 어드레스 천이 조합회로(16)에서의 NOT 게이트 G35의 출력이 시간지연을 위한 NOT 게이트 G22 및 G23을 경유해 NOR 게이트 G19의 한입력 단자에 인가된다. 여기서 상술한 우측 포트의 어드레스 버퍼(5), 어드레스 천이 감지회로(13) 및 어드레스 천이 조합회로(16)의 구성은 좌측 포트 측의 회로와 구성이 동일하므로 그 설명은 생략키로 한다.

상술한 양측의 어드레스 버퍼(3 및 5)에서 출력되는 신호중  $A_n L$  및  $A_n R$  신호를 게이트 G12, G13 및 G14로 구성된 배타 논리합(EXCLUSIVE OR)(11)회로에 인가시켜, 이 두 개의 신호가 다를때만 NOR 게이트 G14에서 High 신호가 출력되는 EoRn(실제로는 상기 배타 논리합 회로가 수개로 구성되어 EoR1, EoR2, EoR3…EoRn의 펄스신호가 된다) 펄스신호를 생성하여, EoRn 펄스 신호를 FET4의 게이트에 인가시키면 이펄스신호에 따라 상기 FET4가 ON 또는 OFF 되고 칩 셀렉터 신호를 조합한

**CSL + CSR** 신호에 따라 FET6과 FET5의 접속점의 상태가 변환된다음, NOT 논리게이트 G16를 거쳐 CLK AL 펄스 신호를 생성하여 역시 NOT 논리게이트 G17를 거쳐 중재논리회로(17)의 FET10, FET7, FET8, FET9의 게이트 단자에 인가되고 또한 CLK AL 신호는 직접 NOR 게이트 G24, G35에 연결된다.

상술한 바와 같이, 중재논리회로(17)에 인가된 상기 신호들에 따라 좌측 포트 또는 우측 포트가 선택되는데, 이 동작 설명은 제4a도 내지 제4d도에 도시된 타이밍도를 참조하여 상세히 설명하면 다음과 같다.

CLK AL 신호가 HIGH 상태인 경우, 즉 각 포트의 어드레스들이 동일 논리신호가 아닌 상태여서 동일 셀에 대한 각 포트의 동작이 이루어지지 않는 보통상태의 듀얼 포트 램동작에서는 제3도의 중재논리회로(17)의 G24와 G35의 출력들은 다른쪽 입력(점 A와 점 B)의 상태와는 관계없이 CLK AL에 의해 결정되므로 NOR 게이트 G24와 G35의 출력신호는 LOW이다. 두단의 NOT 논리게이트를 거친 신호 역시 LOW이므로 FET16, FET17, FET19, FET20은 OFF 상태이고 FET15, FET18은 ON 상태이다. 따라서

**BUSY** L, **BUSY** R은 HIGH 상태로 있으며 디코더의 출력인 SELECT L 및 SELECT R도 변화가 없이 각 포트별로 보통 램동작을 계속하게 된다. 이와 같이 중재논리회로의 중재가 필요하지 않아 보통상태를 유지하고 있는 시간은 타이밍도(제4a도 내지 제4d도)에서 T1 이전 구간과 T2부터 T3까지 구간, T4이후의 구간을 가리킨다. 제4a도와 제4b도는 상기에서 기술한 어드레스 중재논리에 의한 타이밍도로서 좌측포트와 우측포트의 우선순위에 따른 경우의 수를 도시한 것이다. 제4c도와 제4d도는 칩 셀렉트 중재논리에 의한 타이밍도를 역시 나타낸 것이다.

먼저, 제4a도의 경우를 제3도의 회로와 함께 설명하여 보기로 한다.

CLK AL T1에서 LOW 상태로 바뀌면, 즉 각 포트의 어드레스들이 동일셀 선택을 위해 동일 논리신호가 되면 어드레스 매치회로와 어드레스 매치조합회로를 거쳐 G24와 G35의 CLK AL 입력은 LOW 상태가 되므로 앞단의 ATD 신호와 **CS** 신호에 의해 결정되는 G24와 G35의 다른쪽 입력(점 A와 점 B)에 의해 출력의 상태가 좌우된다. ATD L 신호는 상기에서 기술한 어드레스 버퍼, 어드레스 감지회로, 어드레스 감지조합회로를 거쳐 T1에서 CLK AL의 변환점과 앞뒤로 겹치는 클럭을 생성한다. CLK AL G17를 거쳐 HIGH 상태가 되어 FET10, FET9는 OFF되고 FET7, FET8, FET8, FET12, FET13은 ON된다.

T1시점에서 볼 때 ATD L은 HIGH 상태이므로 G18과 FET17을 거쳐 점 A의 상태는 LOW이고, ATD R과 **CS** R이 모두 LOW인 상태에서 G19의 출력은 HIGH이므로 FET8을 거친 점 B의 HIGH 상태, FET12와 FET11을 거쳐 점 A를 계속 LOW 상태로 유지시킨다. 따라서 G24의 출력은 HIGH 상태, G25와 G26, G27과 G28을 거친 출력 역시 HIGH이므로 FET16은 ON, FET15는 OFF되어 **BUSY** L이 LOW상태로 바뀐다. 또한 FET17이 ON되어 디코더의 출력인 SELECT L을 LOW로 바꾸어 결국 좌측 포트는 우측포트가 먼저 선택한 동일 메모리셀을 선택하지 못한다. 반면 점 B의 상태는 계속 HIGH이므로 좌측 포트와는 관계없이 우측포트는 선택한 메모리셀에 대한 램동작을 계속할 수 있다.

상기의 중재논리에 의해 이루어진 신호들의 상태는 T2시점에서 우측포트의 어드레스가 바뀌어 CLK AL이 HIGH 상태로 되면 해제된다. 즉 **BUSY** L과 SELECT L이 HIGH 상태로 돌아오고 우측포트가 선택했던 메모리 셀에 대해 좌측포트가 램동작을 수행할 수 있으며 우측포트는 다른 위치의 메모리셀을 선택, 동작을 한다.

T3에서 T4 구간의 타이밍도는 T1에서 T2구간에서 발생한 경우를 좌측, 우측포트끼리 서로 바꿔어 놓은 상황과 같다. 즉 T3시점에서 볼 때 ATD R은 HIGH 상태이므로 G19와 FET8을 거친 점 B의 상태는 LOW이고 ATD L과 **CS** L이 모두 LOW인 상태에서 G18의 출력은 HIGH이므로 FET7을 거친 점 A의 HIGH 상태는 FET13과 FET14를 거쳐 점 B를 계속 LOW 상태로 유지시킨다. 따라서 G35의 출력은 HIGH 상태, G29와 G30, G31과 G32를 거친 출력 역시 HIGH이므로 FET19는 ON, FET18은 OFF되어 **BUSY** ROI LOW 상태로 바뀐다. 또한 FET20이 ON되어 디코더의 출력인 SELECT R을 LOW로 바꿔어 결국 우측포트는 좌측포트가 먼저 선택한 동일 메모리셀을 선택하지 못한다. 반면 점 A의 상태는 계속 HIGH이므로 우측포트와는 관계없이 좌측포트는 선택한 메모리셀에 대한 램동작을 계속하고 T4시점에서 중재논리가 해제되어 양포트는 서로 다른 메모리셀을 선택하게 되므로 보통의 듀얼 포트 램 동작 상태로 넘어오게 된다.

제4b도 역시 어드레스 중재논리의 또 다른 경우의 타이밍도를 나타낸 것으로 제4a도의 경우에서 설명한 바와 같은 중재논리회로의 동작으로 실행되며 중재논리가 성립되는 경우의 차이점을 설명하여 보면 다음과 같다.

제4a도의 경우 T1이전 구간에서 우측포트가 일정셀에 대해 동작을 하고 있는 상황에서 우측포트가 선택하고 있는 동일셀에 대해 좌측포트가 동작을 하기 위한 상태로 바꿔어 각 포트의 어드레스들이 동일논리신호가 되면 어드레스 매치회로와 어드레스 매치회로와 어드레스 매치조합회로를 거쳐 T1 시점에서 CLK AL HIGH에서 LOW로 바뀌고, 좌측포트의 어드레스 신호의 변화는 어드레스 천이감지회로와 어드레스 천이조합회로를 통해 ATD 신호가 클럭으로 나타나 T1 시점의 앞뒤로 CLK AL과 겹치게 된다.

제4b도의 경우 먼저 동일셀을 T1이전 구간에서 선택하고 있는 포트는 좌측포트이며, T2에서 중재논리의 해제가 우측포트의 어드레스가 바뀜으로써 일어나는 경우는 제4a도와 제4b도가 동일하다. T3부터 T4구간의 경우도 위와 같이 설명할 수 있으며 이는 중재논리가 여러 가지 경우의 수에 대해서도 예외 없이 동작하는 것을 검증하고 설명하기 위해 도시한 것이다.

칩 셀렉트 중재논리의 타이밍도인 제4c도 및 제4d도의 경우 ATD 신호를 **CS** 신호로 대체하여 상기한 동작원리와 동일하게 설명될 수 있으므로 여기에 대한 내용은 생략하기로 한다. 동시신호중재논리의 경우 양포트의 **CS** 신호 또는 어드레스신호가 동시에 입력되더라도 제3도의 G20 및 G21, G22 및 G23에 의해 **CS** R 신호 및 ATD R 신호가 지연되어 지연시간만큼 늦게 G19에 입력되므로 위에서 설명한 중재논리회로의 동작에 따라 좌측포트가 우선적으로 동작할 수 있도록 설계되어 있다. 제4a도 내지 제4d도에서 T1시점, T3시점은 중재논리가 시작된 점으로 CLK AL과 ATD 신호, CLK AL과 **CS** 신호는 T1 전후 어느 시간동안 중첩되어야 하는 조건을 가지며 이는 각신호들의 전달회로에 의해 조정될 수 있다.

상술한 바와 같이 본 발명에 의한 듀얼 포트 램의 중재회로에 의하면 중재논리가 성립 또는 해제되었을 시 **BUSY** 응답시간을 신속하게 하여 CPU가 이를 감지하는 시간을 더욱 빠르게 개선하고 보다 안정된 중재회로의 동작을 제공하게 된다.

### (57) 청구의 범위

#### 청구항 1

듀얼 포트 램의 중재회로에 있어서, 양측 포트의 어드레스 신호로부터 각각 2개의 정, 부 논리신호를 출력하여 어드레스 천이 감지회로(12 및 13)에 입력시키는 2개의 어드레스 버퍼(3 및 5)와, 상기 각각의 정, 부 논리신호중 정논리신호로부터 양측 어드레스 신호의 동일성을 판별하여, 소정수의 신호를 출력하는 소정수의 어드레스 매치 감지회로(11)와, 상기 어드레스 버퍼(3 및 5)의 출력신호로부터 일정시간 지연시켜 각 어드레스 신호에 대응되는 수의 신호를 각각 출력하여 어드레스 천이 조합회로(14 및 16)에 입력시키는 다수의 어드레스 천이 감지회로(12 및 13)와, 상기 어드레스 매치 감지회로(11)의 출력신호를 조합하여 한 개의 출력신호를 생성하여 중재 논리회로(17)에 입력시키는 어드레스 매치 조합회로(15)와, 상기 어드레스 천이 감지회로(12 및 13)의 출력신호를 조합하여 각각 한 개의 출력신호를 생성, 중재논리회로(17)에 입력시키는 어드레스 천이 조합회로(14 및 16)와,

상기 각각의 출력신호로부터 출력을 중재하는 SELECT 신호와 프레그(FLAG) 신호인 **BUSY** 신호를 출력하는 중재논리회로(17)를 구비하는 것을 특징으로 하는 듀얼 포트 램의 중재회로.

#### 청구항 2

제1항에 있어서, 상기 어드레스 매치 감지회로(11)는, 어드레스 신호의 동일성을 판별하기 위하여 배타논리합(EXCLUSIVE OR)회로(G12, G13 및 G14)를 조합하여 조정수로 구성된 것을 특징으로 하는 듀얼 포트 램의 중재회로.

#### 청구항 3

제1항에 있어서, 상기 어드레스 천이 감지회로(12 및 13)는, 상기 정, 부 어드레스 버퍼 신호로부터의 출력 신호를 직접 그리고 소정수의 NOT 논리게이트(G3, G4 및 G33) 및 캐페시터(C1 및 C2)로 구성된 지연회로로부터 생성된 지연신호로하여 2개의 NOR게이트(G5 및 G9)에 의해 각각 합성하고 이들 각각의 출력을 한 개의 NOR 게이트(G10)로 합성, NOT 논리게이트(G11)로 반전시켜, 새로운 필스를 생성함에 의해 어드레스 천이를 감지할 수 있도록 구성한 것을 특징으로 하는 듀얼 포트 램의 중재회로.

## 청구항 4

제1 또는 2항에 있어서, 상기 어드레스 매치 조합회로(15)는, 병렬 접속된 다수의 FET(FET4...)에 종속 접속된 2개의 FET(FET5 및 FET6)들로 구성되어, 상기 소정수의 어드레스 매치 감지회로(11)의 출력으로부터 상기 병렬 접속된 다수의 FET들중의 하나 이상의 게이트를 트리거 시킴으로써 상기 종속 접속된 FET 접속점에서 정 또는 부 논리 신호가 생성되도록 구성한 것을 특징으로 하는 듀얼 포트 램의 종재회로.

## 청구항 5

제1 또는 3항에 있어서, 상기 어드레스 천이 조합회로(14 및 16)는, 병렬 접속된 다수의 FET(FET1...)들에 종속 접속된 2개의 FET(FET2 및 FET3)들로 구성되어, 상기 어드레스 천이 감지회로(12 및 13)의 출력으로부터 상기 병렬접속된 다수의 FET들중의 하나 이상의 게이트를 트리거시킴으로써 상기 종속접속된 FET 접속점에서 정 또는 부 논리신호가 생성되도록 구성한 것을 특징으로 하는 듀얼 포트 램의 종재회로.

## 청구항 6

제1 또는 5항에 있어서, 상기 종재논리회로(17)에서 우측포트의 어드레스 천이 조합회로(16)의 출력(ATDR) 및 칩셀렉트신호( $\overline{CS}$  R)가 2단의 NOT 게이트(G20 및 G21, G22 및 G23)에 의해 각각 지연되도록 구성하여 동시 신호로 듀얼 포트의 어드레스 및 칩셀렉트 신호들이 입력되었을 때 항상 좌측포트부처 동작이 허용되는 것을 특징으로하는 듀얼 포트 램의 종재회로.

## 도면

## 도면1

## 도면2

### 도면3

#### 도면4A

도면4B

도면4C

도면4D