## (12) 按照专利合作条约所公布的国际申请

(19) 世界知识产权组织

国际局

(43) 国际公布日

2014年5月8日 (08.05.2014)

(10) 国际公布号

WO 2014/067463 A1

(51) 国转 利分类号 :

H01L 29/786 (2006.01) H01L 21/28 (2006.01)

H01L 29/06 (2006.01) G09F 9/33 (2006.01)

H01L 21/336 (2006.01) G09F 9/35 (2006.01)

H01L 27/12 (2006.01)

(21) 国际申请号 : PCT/CN20 13/086250

(22) 国际申请日 : 2013年10月30日 (30.10.2013)

(25) 申请语言 : 中文

(26) 公布语言 : 中文

(30) 优先权 :

2012 10434914.X 2012年11月2日 (02.11.2012) CN

201220575529.2 2012年11月2日 (02.11.2012) CN

(71) 申请人 : 京东方科技股份有限公司 (BOE

TECHNOLOGY GROUP CO., LTD.) [CN/CN]; 中国

北京市朝阳区酒仙桥路10号, Beijing 100015 (CN)。

(72) 发明人 刘翔 (LIU, Xiang); 中国北京市经济技术开

发区地泽路9号, Beijing 100176 (CN)。王刚

(WANG, Gang); 中国北京市经济技术开发区地泽路

9号, Beijing 100176 (CN)。

(74) 代理人 : 北京市柳沈律师事务所 (LIU, SHEN &

ASSOCIATES); 中国北京市朝阳区北辰东路8号汇

宾大厦 A0601, Beijing 100101 (CN)。

(81) 指定国 (除另有指明, 要求每一种可提供的国家保

护) : AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG,

BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR,

CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB,

GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS,

JP, KE, KG, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT,

LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY,

MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT,

QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM,

ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US,

UZ, VC, VN, ZA, ZM, ZW。

(84) 指定国 (除另有指明, 要求每一种可提供的地区保

护) : ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA,

RW, SD, SL, SZ, TZ, UG, ZM, ZW), 印度 (AM, AZ,

BY, KG, KZ, RU, TJ, TM), 欧洲 (AL, AT, BE, BG, CH,

CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE,

IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO,

RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM,

GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG)。

[见续页]

(54) Title: THIN FILM TRANSISTOR AND MANUFACTURING METHOD, ARRAY SUBSTRATE, DISPLAY DEVICE AND BARRIER LAYER THEREOF

(54) 发明名称 薄膜晶体管及其制作方法、阵列基板、显示装置和阻挡层

图 2 /Fig.2

(57) Abstract: Provided are a thin film transistor and manufacturing method, array substrate and display device thereof, for improving the electrical performance of the thin film transistor and the quality of an image displayed on the display device. The thin film transistor of the present invention comprises a gate electrode (2) located on a substrate (1), a source electrode (8), a drain electrode (9), a semiconductor layer (4), a gate insulation layer (3), and a first metal barrier layer (5); the gate insulation layer (3) is located between the gate electrode (2) and the semiconductor layer (4); the first metal barrier layer (5) is located among the source electrode (8), the drain electrode (9) and the gate insulation layer (3); the first metal barrier layer (5) and the semiconductor layer (4) are disposed on the same layer; the first metal barrier layer (5) prevents mutual diffusion between the materials forming the source electrode (8) and the drain electrode (9), and the material forming the gate electrode (2).

(57) 摘要: 提供了一种薄膜晶体管及其制作方法、阵列基板及显示装置, 用以提高薄膜晶体管的电学性能, 提高显示装置显示图像的画质。本发明提供的薄膜晶体管包括: 位于基板(1)上的栅极(2)、源极(8)、漏极(9)、半导体层(4)、栅极绝缘层(3)以及第一金属阻挡层(5); 所述栅极绝缘层(3)位于所述栅极(2)和所述半导体层(4)之间; 所述第一金属阻挡层(5)位于所述源极(8)、漏极(9)与栅极绝缘层(3)之间; 其中, 所述第一金属阻挡层(5)与所述半导体层(4)同层设置, 所述第一金属阻挡层(5)阻止形成源极(8)和漏极(9)的材料与形成栅极(2)的材料的相互扩散。

W 2 14/06 63 A1

---

本 国际公布 :

- 包括 国际检索报告(条约第 21 条(3))。

# 薄膜晶体管及其制作方法、阵列基板、显示装置和阻挡层

## 技术领域

本发明涉及显示技术领域，尤其涉及一种薄膜晶体管及其制作方法、阵列基板、显示装置和阻挡层。

5

## 背景技术

在显示技术领域，平板显示装置，如液晶显示器 (Liquid Crystal Display, LCD) 和有机电致发光显示器 (Organic Light Emitting Display, OLED)，因其具有轻、薄、低功耗、高亮度，以及高画质等优点，在平板显示领域占据 10 重要的地位。尤其是大尺寸、高分辨率，以及高画质的平板显示装置，如液晶电视，在当前的平板显示器市场已经占据了主导地位。

目前，图像信号的延迟成为制约大尺寸、高分辨率及高画质平板显示装置的关键因素之一。具体地，图像信号的延迟主要由基板上的栅极、栅极线，或数据线等信号电阻  $R$  和相关电容  $C$  决定。随着显示装置尺寸的不断增大， 15 分辨率不断提高，驱动电路施加的信号频率也不断提高，图像信号的延迟越来越严重。在图像显示阶段，栅极线打开，像素充电，由于图像信号的延迟，某些像素充电不充分，导致图像显示画面的亮度不均匀，严重影响图像的显示质量。降低栅极、栅极线，数据线等的电阻可以减小图像信号的延迟，改善图像的画质。

20 目前，降低栅极线和数据线的电阻的方法主要采用电阻较低的金属铜 (Cu) 制作栅极线和数据线。但是存在以下缺点：

铜 (Cu) 金属离子易扩散，尤其是在较高温度下很容易扩散到栅极保护层、半导体层、或钝化层中，严重影响薄膜晶体管 (Thin Film Transistor, TFT) 的性能。尤其是在 TFT 后续高温加热工艺中，铜 (Cu) 离子的活性增加，可 25 以穿越绝缘阻挡层渗透到半导体层，严重影响 TFT 性能，使得图像的画质更差，甚至破坏 TFT 的正常工作。

现有基板上的 TFT 以及制作方法会引起 TFT 性能下降，图像画质较差的问题。

## 发明内容

本发明实施例提供一种薄膜晶体管及其制作方法、阵列基板、显示装置和阻挡层，用以提高TFT的性能，提高图像的画质。

为实现上述目的，本发明实施例提供的薄膜晶体管，包括：

5 位于基板上的栅极、源极、漏极、半导体层、栅极绝缘层以及第一金属阻挡层；所述栅极绝缘层位于所述栅极和所述半导体层之间；所述第一金属阻挡层位于所述源极、漏极与栅极绝缘层之间；其中，所述第一金属阻挡层与所述半导体层同层设置，所述第一金属阻挡层阻止形成源极和漏极的材料与形成栅极的材料的相互扩散，提高TFT的性能，提高图像的画质。

10 例如，较佳地，还包括位于所述源极、漏极与所述半导体层之间的刻蚀阻挡层，具有刻蚀阻挡层的TFT可以防止刻蚀源极和漏极时对半导体层的影响。

例如，较佳地，所述第一金属阻挡层与所述半导体层绝缘设置。

15 例如，较佳地，所述形成源极和漏极的材料和形成栅极的材料中的至少之一为铜或铜合金，铜或铜合金的电阻率较低，可以减小图像信号的延迟，改善图像的画质。

例如，较佳地，当所述TFT为金属氧化物TFT时，所述半导体层为金属氧化物半导体层。

20 例如，较佳地，所述第一金属阻挡层采用与所述半导体层相同的材料制作而成，首先所述金属氧化物半导体层具有阻止形成源极和漏极的材料与形成栅极的材料的相互扩散功能，其次同种材料形成第一金属阻挡层和半导体层可以简化TFT的结构，节约制作工艺流程。

例如，较佳地，所述第一金属阻挡层为具有阻止形成源极和漏极的材料与形成栅极的材料的相互扩散功能的氧化铜、氮化铜或氮氧化铜膜层。

25 例如，较佳地，所述第一金属阻挡层还可以采用与所述半导体层不相同的金属氧化物半导体材料制作而成，由于金属氧化物半导体材料可以阻止形成源极和漏极的材料与形成栅极的材料的相互扩散，可以实现提高TFT的性能，提高图像的画质。

例如，较佳地，所述薄膜晶体管还包括：第二金属阻挡层，所述第二金属阻挡层位于所述第一金属阻挡层与所述源极、漏极之间，所述第二金属阻挡层阻止形成源极和漏极的材料与形成栅极的材料的相互扩散，可以更进一

步提高 TFT 的性能，提高图像的画质。

例如，较佳地，所述形成源极和漏极的材料为铜或铜合金，铜或铜合金的电阻率较低，可以减小图像信号的延迟，改善图像的画质。

例如，较佳地，所述第二金属阻挡层为具有阻止形成源极和漏极的材料与形成栅极的材料的相互扩散功能的氧化铜、氮化铜，或氮氧化铜膜层。

例如，较佳地，所述第二金属阻挡层采用具有阻止形成源极和漏极的材料与形成栅极的材料的相互扩散功能的金属氧化物半导体材料制作而成。

例如，较佳地，所述薄膜晶体管的结构为：

所述栅极位于所述基板上；

10 所述栅极绝缘层位于所述栅极上；

所述半导体层和第一金属阻挡层位于所述栅极绝缘层上；

所述刻蚀阻挡层位于所述半导体层上；

所述第二金属阻挡层位于所述半导体层和第一金属阻挡层上；

所述源漏极层位于所述第二金属阻挡层上；

15 或者所述薄膜晶体管的结构为：

所述源漏极层位于所述基板上；

所述第二金属阻挡层位于所述源漏极层上；

所述刻蚀阻挡层位于所述第二金属阻挡层上；

所述半导体层和第一金属阻挡层位于所述刻蚀阻挡层上；

20 所述栅极绝缘层位于所述半导体层上；

所述栅极位于所述栅极绝缘层上。

例如，较佳地，所述薄膜晶体管的结构为：

所述栅极位于所述基板上；

所述栅极绝缘层位于所述栅极上；

25 所述半导体层和第一金属阻挡层位于所述栅极绝缘层上；

所述源极和漏极位于所述第一金属阻挡层上；

或者所述薄膜晶体管的结构为：

所述源极和漏极位于所述基板上；

所述半导体层和第一金属阻挡层位于所述源极和漏极上；

30 所述栅极绝缘层位于所述半导体层和第一金属阻挡层上；

所述栅极位于所述栅极绝缘层上。

例如，较佳地，所述薄膜晶体管的结构为：

所述栅极位于所述基板上；

所述栅极绝缘层位于所述栅极上；

所述半导体层和第一金属阻挡层位于所述栅极绝缘层上；

所述第二金属阻挡层位于所述半导体层和第一金属阻挡层上；

所述源极和漏极位于所述第一金属阻挡层上；

或者所述薄膜晶体管的结构为：

所述源极和漏极位于所述基板上；

所述第二金属阻挡层位于所述源极和漏极上；

所述半导体层和第一金属阻挡层位于所述第二金属阻挡层上；

所述栅极绝缘层位于所述半导体层和第一金属阻挡层上；

所述栅极位于所述栅极绝缘层上。

例如，较佳地，所述第一金属阻挡层位于与所述源极和漏极相对应的位置，尽可能地简化 TFT 的结构。

例如，较佳地，所述第二金属阻挡层位于与所述源极和漏极相对应的位置，尽可能地简化 TFT 的结构。

本发明实施例提供一种阵列基板，其特征在于，包括上述仅设置有第一金属阻挡层的薄膜晶体管，所述第一金属阻挡层阻止形成源极和漏极的材料与形成栅极的材料的相互扩散，提高 TFT 的性能，提高图像的画质。

例如，较佳地，所述阵列基板还包括：数据线和栅极线，所述数据线与所述薄膜晶体管的源极相连，所述栅极线与薄膜晶体管的栅极相连；

所述第一金属阻挡层位于与所述源极、漏极及数据线相对应的位置；或者

所述第一金属阻挡层位于与所述源极、漏极及栅极线相对应的位置；或者

25

所述第一金属阻挡层位于与所述源极、漏极、栅极线和数据线相对应的位置，所述第一金属阻挡层阻止形成源极和漏极的材料与形成栅极的材料的相互扩散，提高 TFT 的性能，提高图像的画质，同时还阻止形成栅极线和数据线的材料的相互扩散，提高 TFT 的性能，提高图像的画质。

30 本发明实施例提供一种阵列基板，包括上述设置有第一金属阻挡层和第二金属阻挡层的薄膜晶体管，进一步提高 TFT 的性能，提高图像的画质。

例如，较佳地，所述阵列基板还包括：数据线和栅极线，所述数据线与所述薄膜晶体管的源极相连，所述栅极线与薄膜晶体管的栅极相连；

所述第一金属阻挡层位于与所述源极、漏极及数据线相对应的位置，或者位于与所述源极、漏极及栅极线相对应的位置，或者位于与所述源极、漏极、栅极线和数据线相对应的位置；和/或

所述第二金属阻挡层位于与所述源极、漏极及数据线相对应的位置，或者位于与所述源极、漏极及栅极线相对应的位置，或者位于与所述源极、漏极、栅极线和数据线相对应的位置，第二金属阻挡层的设置可以进一步避免形成源极、漏极、栅极线、和数据线的材料的相互扩散，进一步提高 TFT 的性能，提高图像的画质。

本发明实施例提供一种显示装置，包括上述阵列基板，该阵列基板为仅设置有第一金属阻挡层的薄膜晶体管，可以实现一种信号延迟较小且图像的画质较佳的显示器件。

本发明实施例提供一种显示装置，包括上述阵列基板，该阵列基板为同时设置有第一金属阻挡层和第二金属阻挡层的薄膜晶体管。

本发明实施例提供一种薄膜晶体管的制作方法，包括：

形成包括栅极、源极、漏极和半导体层的图形；形成包括栅极绝缘层以及第一金属阻挡层的图形；

所述栅极绝缘层位于所述栅极和半导体层之间，所述第一金属阻挡层位于所述源极、漏极与栅极绝缘层之间，其中，所述第一金属阻挡层与所述半导体层同层设置。所述第一金属阻挡层阻止形成源极和漏极的材料与形成栅极的材料的相互扩散，提高 TFT 的性能，提高图像的画质。

例如，较佳地，还包括形成刻蚀阻挡层的图形，所述刻蚀阻挡层位于所述半导体层与源极、漏极之间，具有刻蚀阻挡层的 TFT 可以防止刻蚀源极和漏极时对半导体层的影响。

例如，较佳地，所述第一金属阻挡层与所述半导体层绝缘设置。

例如，较佳地，当所述 TFT 为金属氧化物 TFT 时，所述半导体层由金属氧化物半导体材料制作而成。

例如，较佳地，还包括形成第二金属阻挡层的图形，所述第二金属阻挡层位于所述第一金属阻挡层与所述源极、漏极之间，可以更进一步提高 TFT 的性能，提高图像的画质。

例如，较佳地，所述形成包括栅极、源极、漏极、半导体层、栅极绝缘层、第一金属阻挡层的图形，为：

采用构图工艺在基板上形成包括栅极的图形；

5 采用构图工艺在形成有所述栅极图形的基板上形成包括栅极绝缘层的图

形；

采用同一次构图工艺在形成有所述栅极绝缘层图形的基板上形成包括半

导体层和第一金属阻挡层的图形；

采用同一次构图工艺在形成有半导体层和第一金属阻挡层的基板上形成

包括源极、漏极的图形；

10 或者所述形成包括栅极、源极、漏极、半导体层、栅极绝缘层、第一金

属阻挡层的图形，为：

采用同一次构图工艺在基板上形成包括源极、漏极的图形；

采用同一次构图工艺在形成有所述源极、漏极的基板上形成包括半导

体层和第一金属阻挡层的图形；

15 采用构图工艺在形成有所述半导体层和第一金属阻挡层图形的基板上形

成包括栅极绝缘层的图形；

采用构图工艺在形成有所述栅极绝缘层图形的基板上形成包括栅极的图

形。

例如，较佳地，所述形成包括栅极、源极、漏极、半导体层、栅极绝缘

20 层、刻蚀阻挡层、第一金属阻挡层和第二金属阻挡层的图形，为：

采用构图工艺在基板上形成包括栅极的图形；

采用构图工艺在形成有所述栅极图形的基板上形成包括栅极绝缘层的图

形；

25 采用同一次构图工艺在形成有所述栅极绝缘层图形的基板上形成包括半

导体层和第一金属阻挡层的图形；

采用构图工艺在形成有半导体层和第一金属阻挡层图形的基板上形成包

括刻蚀阻挡层的图形；

采用同一次构图工艺在形成有刻蚀阻挡层图形的基板上形成包括源极、

漏极以及第二金属阻挡层的图形；

30 或者所述形成包括栅极、源极、漏极、半导体层、栅极绝缘层、刻蚀阻

挡层、第一金属阻挡层和第二金属阻挡层的图形，为：

采用同一次构图工艺在基板上形成包括源极、漏极以及第二金属阻挡层的图形；

采用构图工艺在形成有所述源极、漏极和第二金属阻挡层图形的基板上形成包括刻蚀阻挡层的图形；

5 采用同一次构图工艺在形成有所述刻蚀阻挡层图形的基板上形成包括半导体层和第一金属阻挡层的图形；

采用构图工艺在形成有所述半导体层和第一金属阻挡层图形的基板上形成包括栅极绝缘层的图形；

10 采用构图工艺在形成有所述栅极绝缘层图形的基板上形成包括栅极的图

例如，较佳地，所述形成包括栅极、源极、漏极、半导体层、栅极绝缘层、第一金属阻挡层和第二金属阻挡层的图形，为：

采用构图工艺在基板上形成包括栅极的图形；

15 采用构图工艺在形成有所述栅极图形的基板上形成包括栅极绝缘层的图

采用构图工艺在形成有所述栅极绝缘层图形的基板上形成包括半导体层的图形；

采用构图工艺在形成有所述半导体层图形的基板上形成第一金属阻挡层的图形；

20 采用同一次构图工艺在形成有第一金属阻挡层图形的基板上形成包括源极、漏极以及第二金属阻挡层的图形；

或者所述形成包括栅极、源极、漏极、半导体层、栅极绝缘层、第一金属阻挡层和第二金属阻挡层的图形，为：

25 采用同一次构图工艺在基板上形成包括源极、漏极以及第二金属阻挡层的图形；

采用构图工艺在形成有所述源极、漏极以及第二金属阻挡层图形的基板上形成包括半导体层的图形；

采用构图工艺在形成有所述半导体层图形的基板上形成第一金属阻挡层的图形；

30 采用构图工艺在形成有所述第一金属阻挡层图形的基板上形成包括栅极绝缘层的图形；

采用构图工艺在形成有所述栅极绝缘层图形的基板上形成包括栅极的图形。

例如，较佳地，所述形成源极和漏极的材料为电阻率较低的铜或铜合金。

例如，较佳地，所述采用同一次构图工艺在形成有刻蚀阻挡层图形的基板上形成包括源极、漏极以及第二金属阻挡层的图形为：

采用镀膜工艺在形成有所述刻蚀阻挡层图形或第一金属阻挡层图形的基板上形成所述铜金属或铜合金膜层；在形成所述铜金属或铜合金膜层的初始时间段内，向腔体内通入预设比例的氧气、氮气或氧气和氮气的混合气体形成铜或铜合金的氧化物、氮化物或氮氧化物用于形成第二金属阻挡层，除所述第二金属阻挡层之外的铜金属或铜合金膜层用于形成源极和漏极；采用一次曝光、显影、光刻刻蚀步骤形成所述源极、漏极以及第二金属阻挡层的图形；

所述采用同一次构图工艺在形成有第一金属阻挡层图形的基板上形成包括源极、漏极以及第二金属阻挡层的图形为：

采用镀膜工艺在形成有所述刻蚀阻挡层图形或第一金属阻挡层图形的基板上形成所述铜金属或铜合金膜层；在形成所述铜金属或铜合金膜层的初始时间段内，向腔体内通入预设比例的氧气、氮气或氧气和氮气的混合气体形成铜或铜合金的氧化物、氮化物或氮氧化物用于形成第二金属阻挡层，除所述第二金属阻挡层之外的铜金属或铜合金膜层用于形成源极和漏极；采用一次曝光、显影、光刻刻蚀步骤形成所述源极、漏极以及第二金属阻挡层的图形。

例如，较佳地，所述采用同一次构图工艺在基板上形成包括源极、漏极以及第二金属阻挡层的图形为：

采用镀膜工艺在基板上形成所述铜或铜合金膜层；在形成所述铜或铜合金膜层的结束时间段内，向腔体内通入预设比例的氧气、氮气或氧气和氮气的混合气体形成铜或铜合金的氧化物、氮化物或氮氧化物用于形成第二金属阻挡层，除所述第二金属阻挡层之外的铜金属或铜合金膜层用于形成源极和漏极；采用一次曝光、显影、光刻刻蚀步骤形成所述源极、漏极以及第二金属阻挡层的图形。

本发明实施例提供一种阻挡层，用于所述仅设置有第一金属阻挡层的阵列基板中阻止铜或铜合金的扩散的第一金属阻挡层。

例如，较佳地，所述阻挡层的材质为具有阻止形成源极和漏极的材料与形成栅极的材料的相互扩散功能的金属氧化物、金属氮化物或金属氮氧化物。

例如，较佳地，所述金属氧化物为具有阻止形成源极和漏极的材料与形成栅极的材料的相互扩散功能的铟镓辞氧化物或氧化铜。

5 例如，较佳地，所述金属氮化物为具有阻止形成源极和漏极的材料与形成栅极的材料的相互扩散功能的铜金属氮化物。

例如，较佳地，所述金属氮氧化物为具有阻止形成源极和漏极的材料与形成栅极的材料的相互扩散功能的铜金属氮氧化物。

本发明实施例提供一种阻挡层，用于所述同时设置有第一金属阻挡层和10 第二金属阻挡层的阵列基板中阻止铜或铜合金的扩散的第一金属阻挡层和/或第二金属阻挡层。

例如，较佳地，所述阻挡层的材质为具有阻止形成源极和漏极的材料与形成栅极的材料的相互扩散功能的金属氧化物、金属氮化物或金属氮氧化物。

15 例如，较佳地，所述金属氧化物为具有阻止形成源极和漏极的材料与形成栅极的材料的相互扩散功能的铟镓辞氧化物或氧化铜。

例如，较佳地，所述金属氮化物为具有阻止形成源极和漏极的材料与形成栅极的材料的相互扩散功能的铜金属氮化物。

例如，较佳地，所述金属氮氧化物为具有阻止形成源极和漏极的材料与形成栅极的材料的相互扩散功能的铜金属氮氧化物。

20 本发明实施例提供的薄膜晶体管，在源极、漏极与栅极绝缘层之间设置有第一金属阻挡层，所述第一金属阻挡层阻止形成源极和漏极的材料与形成栅极的材料的相互扩散，提高TFT的性能，提高图像的画质。进一步地，在源极、漏极与第一金属阻挡层之间设置第二金属阻挡层，所述第二金属阻挡层进一步阻止形成源极和漏极的材料与形成栅极的材料的相互扩散，提高25 TFT的性能，提高图像的画质。

### 附图说明

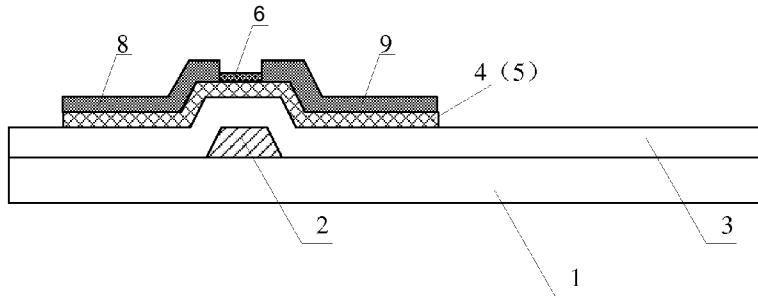

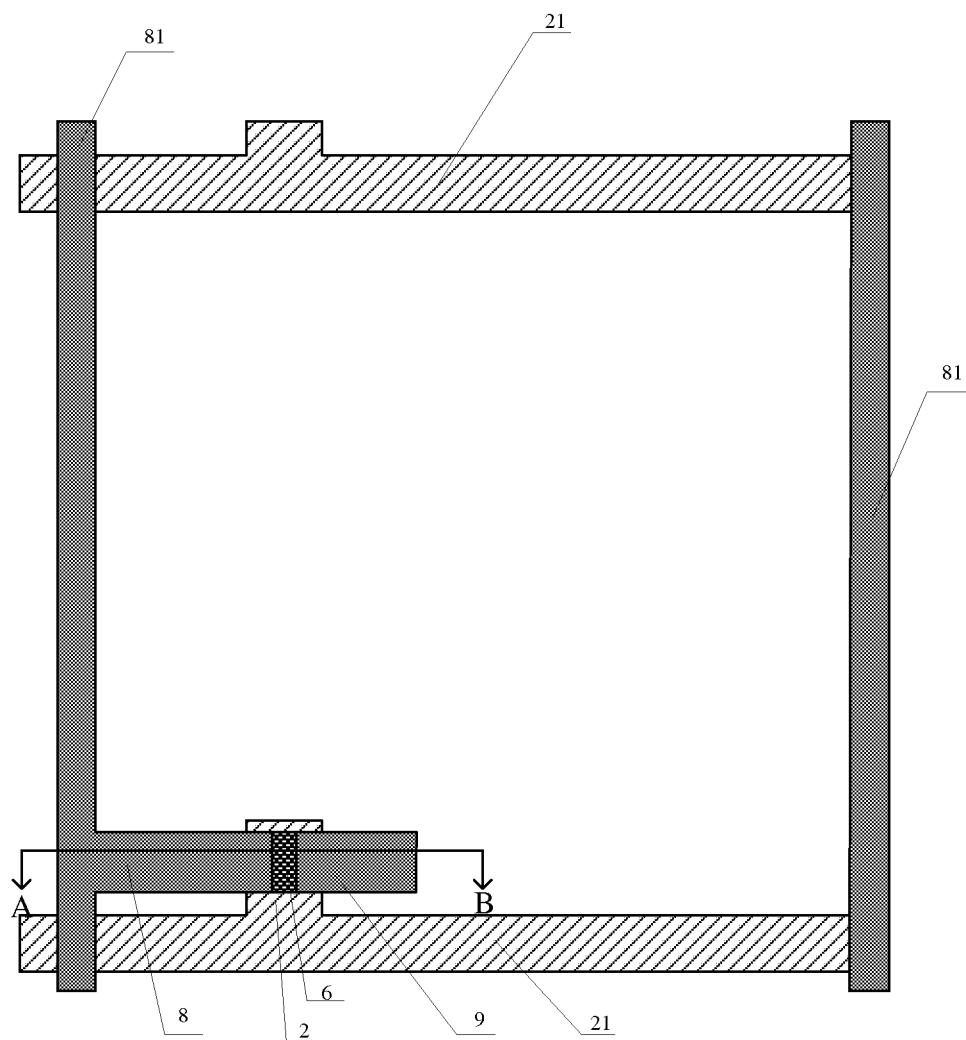

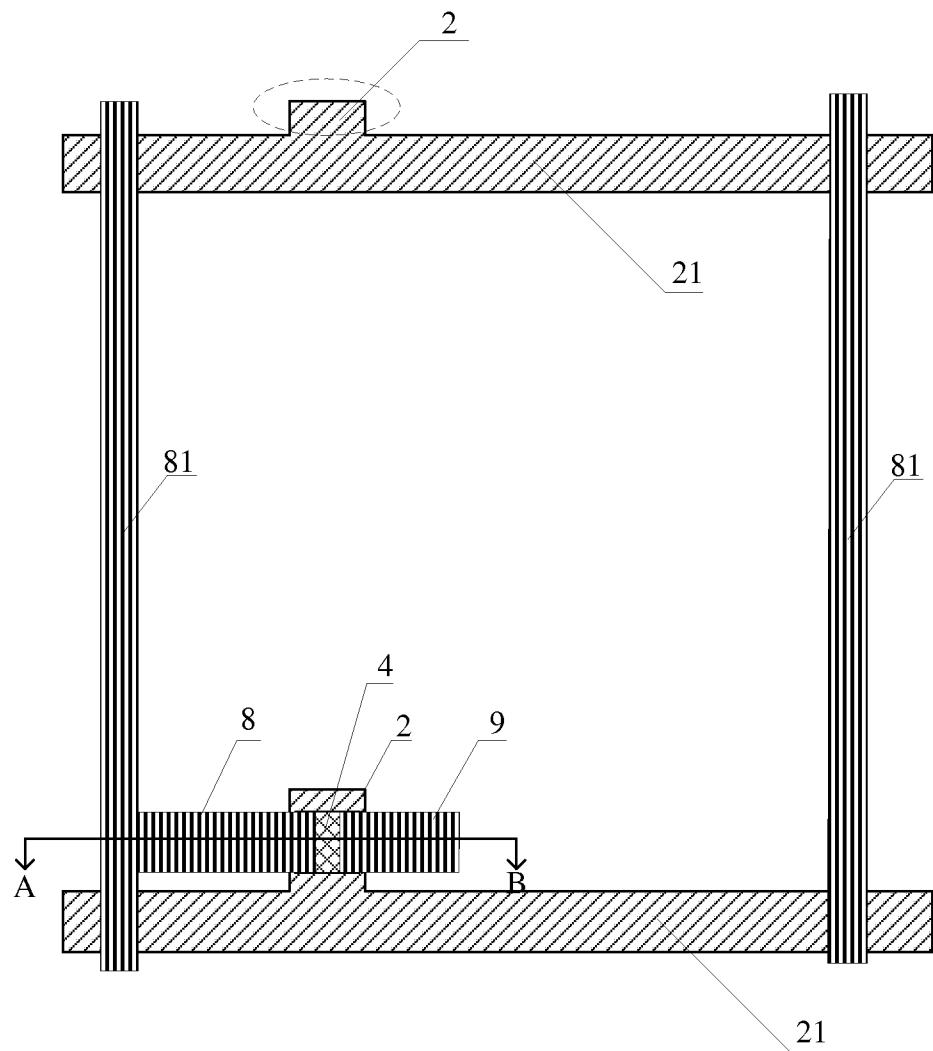

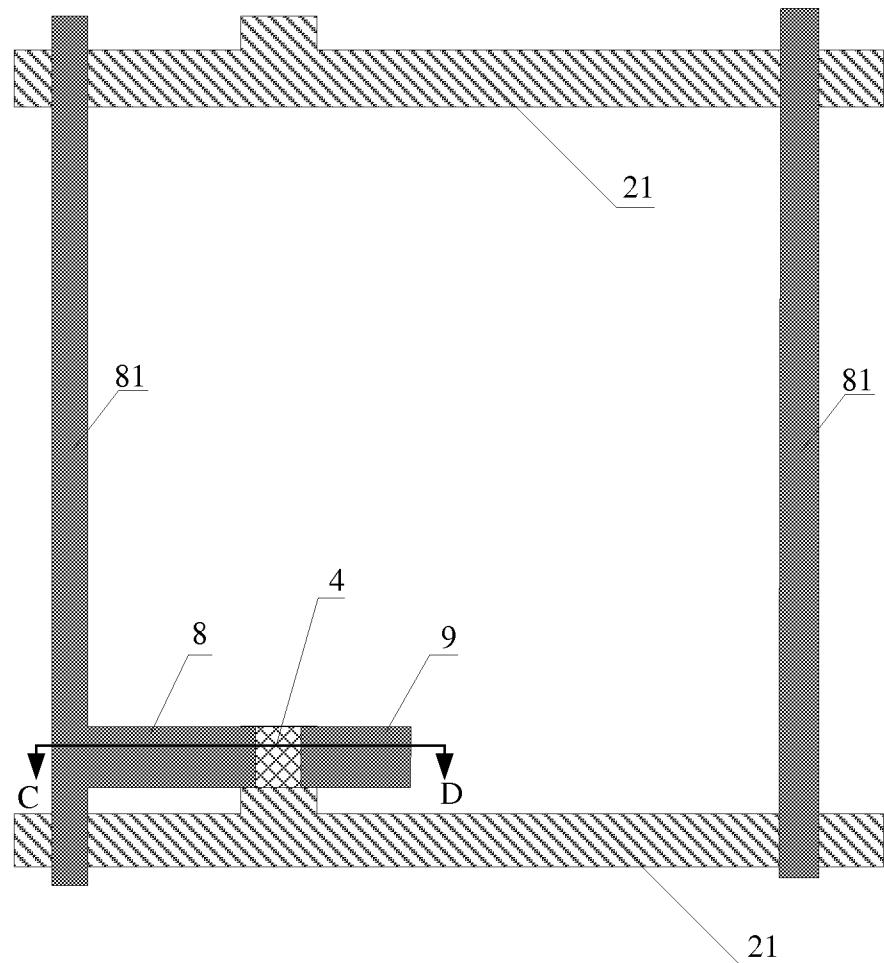

图1为本发明实施例一提供的阵列基板结构俯视示意图；

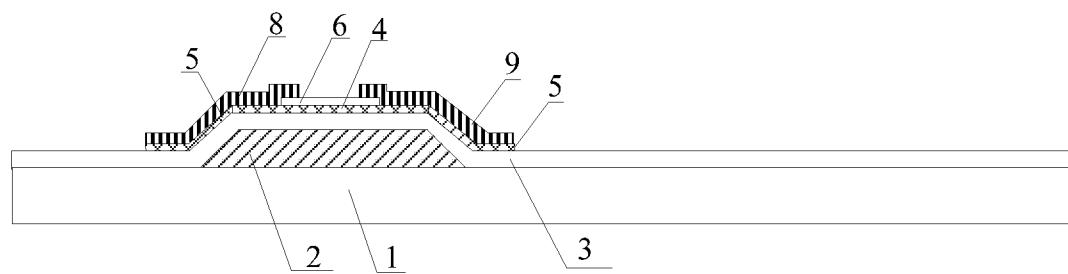

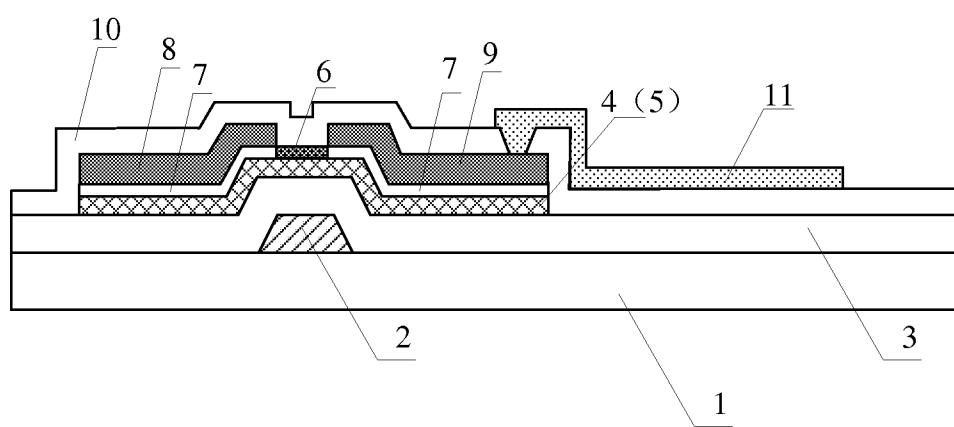

图2为图1所示的TFT在A-B向的截面示意图；

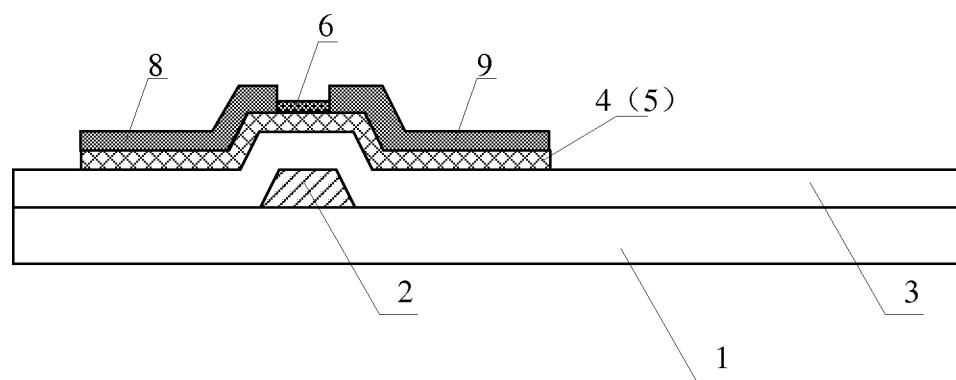

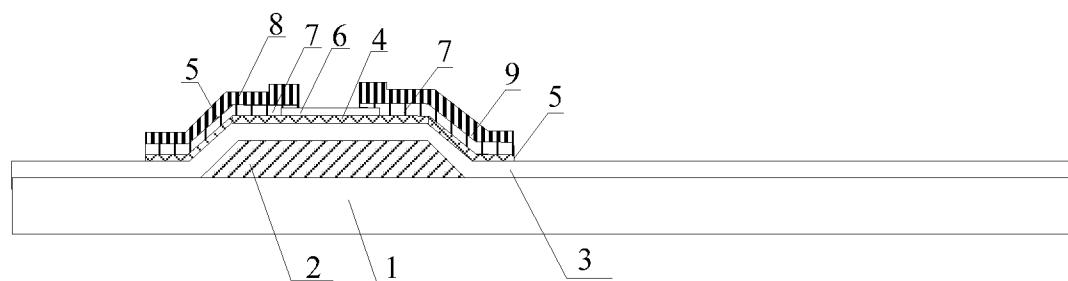

30 图3为图2所示的具有第二金属阻挡层的TFT结构示意图；

图4为本发明实施例二提供的阵列基板结构俯视示意图；

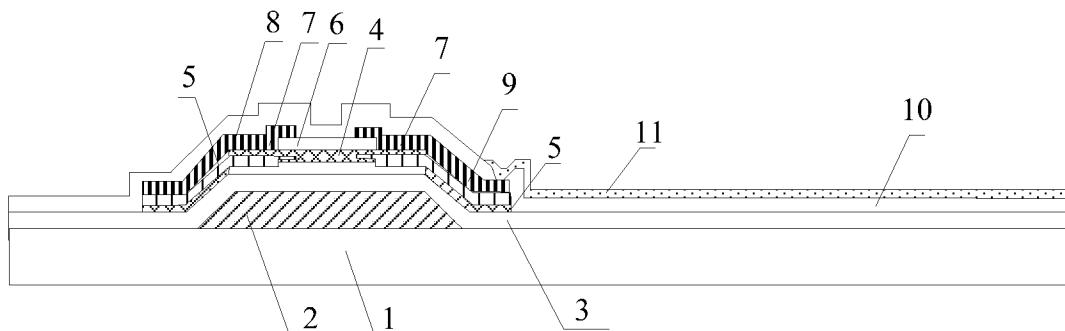

图 5 为图 4 所示的 TFT 在 A-B 向的截面图；

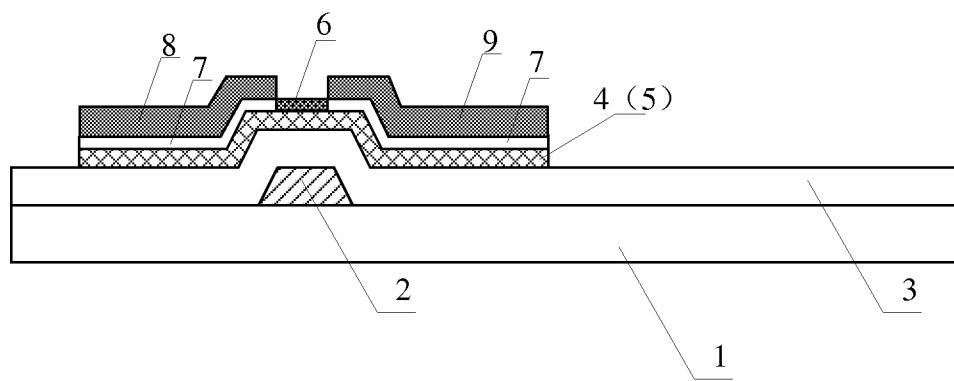

图 6 为图 5 所示的 TFT 具有第二金属阻挡层的 TFT 结构示意图；

图 7 为实施例二提供的 TFT 结构示意图；

图 8 为本发明实施例四提供的阵列基板俯视示意图；

5 图 9 为图 8 所示的阵列基板在 C-D 方向的截面示意图；

图 10 为本发明实施例四提供的阵列基板截面示意图；

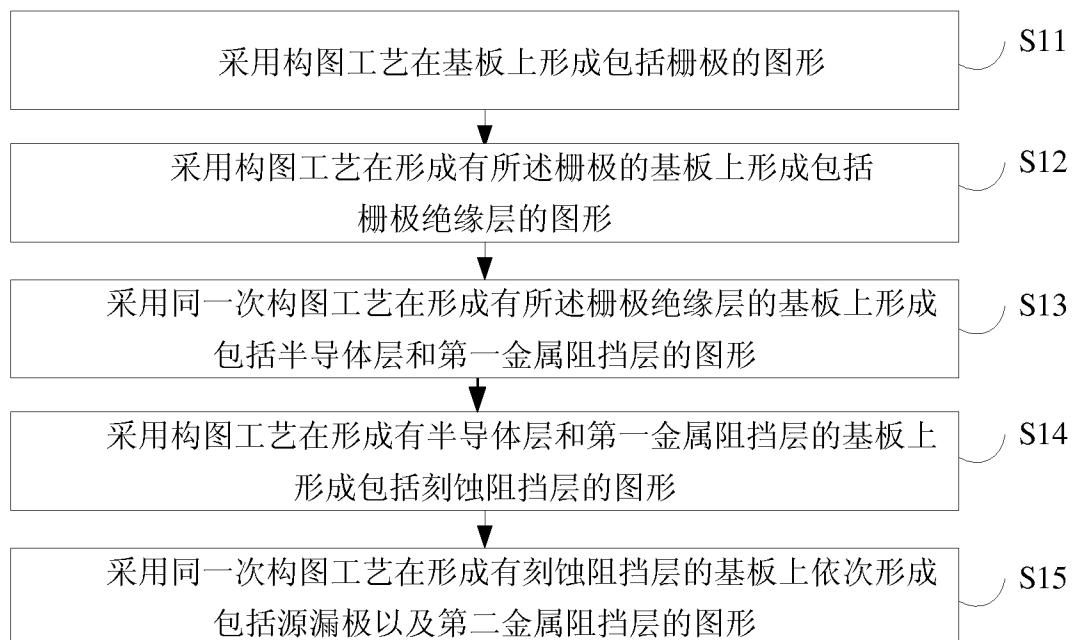

图 11 为本发明实施例六提供的底栅型 TFT 的制作方法流程示意图；

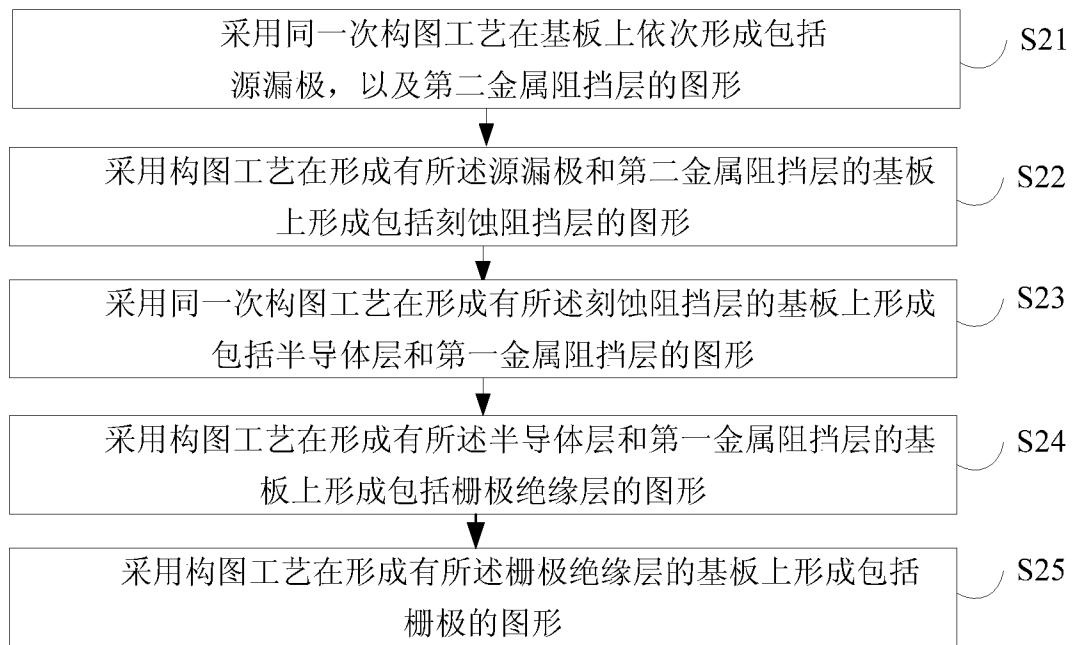

图 12 为本发明提供的顶栅型 TFT 的制作方法流程示意图。

## 10 具体实施方式

本发明实施例提供了一种薄膜晶体管及其制作方法、阵列基板、显示装置及一种阻挡层，用以提高 TFT 的性能，提高图像的画质。

一般地，TFT 至少包括位于基板上的栅极、源极、漏极、半导体层，以及位于所述栅极和半导体层之间的栅极绝缘层。源极和漏极可以称为源漏极层，源漏极层所在 TFT 的膜层称为 SD 层。进一步地，TFT 还包括位于半导体层与源极和漏极之间的刻蚀阻挡层。一般地 对于非晶硅 TFT 和多晶硅 TFT 中无需设置刻蚀阻挡层。对于金属氧化物 TFT，为了防止刻蚀源极和漏极图形对由金属氧化物形成的半导体层造成影响，可以设置刻蚀阻挡层，但是也不排除某些类型的金属氧化物作为半导体层不需要设置刻蚀阻挡层。本发明实施例提供的 TFT 还包括位于所述源极和漏极与栅极绝缘层之间的具有阻止形成源极和漏极的材料与形成栅极的材料的相互扩散功能的阻挡层，所述阻挡层为第一金属阻挡层，所述第一金属阻挡层阻止形成源极和漏极的材料与形成栅极的材料的相互扩散，提高 TFT 的性能，提高图像的画质。

本发明实施例提供的 TFT，源极、漏极、栅极至少之一的材质为电阻率较低的铜或铜合金。当然并不限于此，本发明实施例的目的在于采用第一金属阻挡层阻止形成源极、漏极的材料与形成栅极的材料的相互扩散，其他形成栅极、源极、漏极的材料具备很强的扩散性时也适用于本发明，例如金、银等。

以下简单介绍本发明实施例提供的薄膜晶体管。

30 根据 TFT 中是否设置刻蚀阻挡层，TFT 分为以下两类：

第一类 TFT 结构为：位于基板上的栅极、源极、漏极、半导体层、位于

所述栅极和半导体层之间的栅极绝缘层、位于半导体层与源极、漏极之间的刻蚀阻挡层，以及位于所述源漏极层与栅极绝缘层之间的第一金属阻挡层；其中，所述第一金属阻挡层与所述半导体层同层设置，所述第一金属阻挡层阻止形成源极、漏极的材料与形成栅极的材料的相互扩散。

5 需要说明的是，所述“源极、漏极”表示同层设置的源极和漏极，也可以称为源漏极层，即本发明提到的“源极、漏极”和“源漏极层”均表示同层设置的源极和漏极，同层设置的源极和漏极为源漏极层。

第二类 TFT 结构为：位于基板上的栅极、源极、漏极、半导体层、位于所述栅极和半导体层之间的栅极绝缘层、位于栅极绝缘层与源极和漏极之间10的第一金属阻挡层；所述第一金属阻挡层位于源极、漏极与栅极绝缘层之间；其中，所述第一金属阻挡层与所述半导体层同层设置，所述第一金属阻挡层阻止形成源极、漏极的材料与形成栅极的材料的相互扩散。

本发明上述两类 TFT 中的第一金属阻挡层用于阻止形成源极、漏极的材料扩散至栅极绝缘层和/或栅极中，以及用于阻止形成栅极的材料扩散至半导体层和/或源漏极层中。

为了进一步阻止或避免本发明上述两类 TFT 中形成源极、漏极的材料与形成栅极的材料的相互扩散，例如，优选地，在第一金属阻挡层与源漏极层之间设置第二金属阻挡层。该第二金属阻挡层不仅可以阻挡形成源极、漏极的材料与形成栅极的材料扩散到半导体层，还可以进一步阻挡形成源极、漏极的材料扩散到栅极绝缘层和栅极。

第一类 TFT 的其中一种优选实施方式为：薄膜晶体管包括基板、形成在所述基板上的栅极、源漏极层、半导体层；以及形成在所述基板上位于所述栅极和半导体层之间的栅极绝缘层、位于半导体层与源漏极层之间的刻蚀阻挡层，以及位于所述源漏极层与栅极绝缘层之间的第一金属阻挡层；其中，25 所述第一金属阻挡层与所述半导体层同层设置。

所述源极和漏极由铜金属制作而成，为了避免铜金属离子扩散到栅极绝缘层、栅极，对栅极和栅极绝缘层造成污染，导致 TFT 性能下降，本发明在源漏极层和栅极绝缘层之间形成第一金属阻挡层，阻挡源漏极层金属离子扩散。

30 为了防止源漏极层金属铜离子扩散到半导体层，在半导体层和源漏极层之间设置具有阻止形成源极和漏极的材料与形成栅极的材料的相互扩散功能

的阻挡层，所述阻挡层为第二金属阻挡层，该第二金属阻挡层不仅可以阻挡形成源漏极层的材料扩散到半导体层，还可以进一步阻挡金属铜离子扩散到栅极绝缘层和栅极。

以下将结合附图以及不同的实施例具体说明本发明提供的上述薄膜晶体管 TFT 及其制作方法、阵列基板、显示装置和阻挡层。

本发明实施例提供的薄膜晶体管 TFT 可以是底栅型或顶栅型结构，以下将通过附图具体说明本发明实施例提供的底栅型和顶栅型 TFT。

实施例一：对应上述第一类 TFT。

实施例一提供的底栅型 TFT，结构为：

10 栅极位于基板上；

栅极绝缘层位于所述栅极上；

半导体层和第一金属阻挡层位于所述栅极绝缘层上；

刻蚀阻挡层位于所述半导体层上；

源极和漏极位于所述刻蚀阻挡层上；

15 实施例一提供的顶栅型 TFT，结构为：

源极和漏极位于所述基板上；

刻蚀阻挡层位于所述源极和漏极上；

所述半导体层和第一金属阻挡层位于所述刻蚀阻挡层上；

所述栅极绝缘层位于所述半导体层和第一金属阻挡层上；

20 所述栅极位于所述栅极绝缘层上。

所述半导体层与所述第一金属阻挡层可以同层设置也可以不同层设置，为了尽可能降低 TFT 的整体厚度，例如，较佳地，半导体层与所述第一金属阻挡层同层设置。

需要说明的是，本发明提供的所有 TFT 的结构，各膜层之间的上下位置关系除特别说明之外仅表示膜层之间同层或不同层，并不表示膜层的具体结构以及与其他膜层的具体相对位置。例如刻蚀阻挡层位于所述源极和漏极上，仅表示刻蚀阻挡层与源极和漏极不同层，相对于基板刻蚀阻挡层位于源极和漏极上，即刻蚀阻挡层相比较源极和漏极远离基板。

例如，较佳地，所述第一金属阻挡层与所述半导体层绝缘设置或不相绝缘设置。

该实施例中，半导体层与第一金属阻挡层不相绝缘设置。

进一步地，所述形成源极和漏极的材料和形成栅极的材料中的至少之一为低电阻率的铜或铜合金。

以下将通过附图具体说明，图1为实施例一提供的包括TFT的阵列基板俯视示意图，图2为图1所示的TFT在A-B向的截面图。

5 图1中所示的TFT，包括栅极2、源极8、漏极9，刻蚀阻挡层6以及半导体层。图1所示的阵列基板还包括与源极8相连的数据线81，与栅极2相连的栅极线21。源极8和漏极9可以称为源漏极层，源漏极层所在TFT的膜层称为SD层。

10 以底栅型TFT为例说明，图2所示的底栅型TFT包括：基板1、基板1上的栅极2；

基板1上位于栅极2上的栅极绝缘层3；

基板1上位于栅极绝缘层3上的半导体层4和第一金属阻挡层5，半导体层4和第一金属阻挡层5位于同一层；

15 基板1上位于半导体层4上的刻蚀阻挡层6，刻蚀阻挡层6位于半导体层4沟道的上方，用于保护刻蚀时沟道不受影响。

基板1上位于第一金属阻挡层5上的源极8和漏极9。

通过在源漏极层(SD层)以及栅极绝缘层3之间设置有第一金属阻挡层5，阻挡源漏极层的金属离子进入栅极绝缘层和栅极层。同理，也阻挡栅极层的金属离子进入半导体层和源漏极层，提高了TFT性能。

20 图2所示的TFT，半导体层4和第一金属阻挡层5位于同一层为一种优选的实施例，半导体层4和第一金属阻挡层5也可以位于不同层，这里不做具体限制。

例如，优选地，所述形成源极和漏极的材料和形成栅极的材料中的至少之一为铜或铜合金。

25 形成源极和漏极的材料和形成栅极的材料中的至少之一为铜或铜合金时，为了进一步避免形成源极和漏极的材料与形成栅极的材料的相互扩散。例如，较佳地，实施例一提供的TFT还包括：第二金属阻挡层，所述第二金属阻挡层位于所述第一金属阻挡层与所述源极、漏极之间，所述第二金属阻挡层阻止形成源极和漏极的材料与形成栅极的材料的相互扩散。

30 例如，底栅型TFT结构为：

所述栅极位于所述基板上；

所述栅极绝缘层位于所述栅极上；

所述半导体层和第一金属阻挡层位于所述栅极绝缘层上；

所述刻蚀阻挡层位于所述半导体层上；

所述第二金属阻挡层位于所述半导体层和第一金属阻挡层上；

5 所述源漏极层位于所述第二金属阻挡层上；

顶栅型 TFT 结构为：

所述源漏极层位于所述基板上；

所述第二金属阻挡层位于所述源漏极层上；

所述刻蚀阻挡层位于所述第二金属阻挡层上；

10 所述半导体层和第一金属阻挡层位于所述刻蚀阻挡层上；

所述栅极绝缘层位于所述半导体层上；

所述栅极位于所述栅极绝缘层上。

以下将通过附图具体说明，如图 3 所示，本发明实施例一提供的 TFT，

还包括：第二金属阻挡层 7，位于源漏极层和第一金属阻挡层 5 之间。

15 所述 TFT 结构为：

位于基板 1 上的栅极 2；

位于栅极 2 上的栅极绝缘层 3；

位于栅极绝缘层 3 上的半导体层 4 和第一金属阻挡层 5；

位于半导体层 4 上方的刻蚀阻挡层 6；

20 位于半导体层 4 和第一金属阻挡层 5 上的第二金属阻挡层 7；

位于第二金属阻挡层 7 上的源极 8 和漏极 9。

图 3 所示的 TFT，第二金属阻挡层 7 位于源漏极层和第一金属阻挡层 5 之间，更进一步阻挡了 SD 层的金属离子向栅极绝缘层和/或栅极扩散，更进一步提高了 TFT 的性能。

25 上述图 2 和图 3 提供的 TFT，源漏极层和栅极至少之一的材质为金属铜 (Cu) 或铜合金。例如，优选地，所述形成源极和漏极的材料为铜或铜合金。

例如，优选地，栅极可以为金属铜 (Cu)、金属铬 (Cr)、金属钨 (W)、金属钛 (Ti)、金属钽 (Ta)、金属钼 (Mo) 等，或者是上述至少两种金属的合金。

30 所述源极和漏极由铜金属制作而成，为了避免铜金属离子扩散到栅极绝缘层、栅极，对栅极和栅极绝缘层造成污染，导致 TFT 性能下降，本发明在

源漏极层和栅极绝缘层之间形成第一金属阻挡层，阻挡源漏极层金属离子扩散。

为了防止源漏极层金属铜离子扩散到半导体层，在半导体层和源漏极层之间设置第二金属阻挡层，该第二金属阻挡层不仅可以阻挡金属铜离子扩散到半导体层，还可以进一步阻挡金属铜离子扩散到栅极绝缘层和栅极。

上述任一方式的 TFT 同层设置的第一金属阻挡层和半导体层可以采用同一种材料制备而成，或采用不同种材料制备而成。

例如，较佳地，所述半导体层为金属氧化物半导体层。

所述第一金属阻挡层采用金属氧化物半导体材料制作而成。

更进一步地，所述第一金属阻挡层采用与所述半导体层相同的材料制作而成。

例如，同层设置的第一金属阻挡层和半导体层采用同一种材料制备而成。第一金属阻挡层可以采用制备金属氧化物半导体层的材料，例如：可以是铟镓辞氧化物 (IGZO)、铪铟辞氧化物 (HIZO)、铟辞氧化物 (IZO)、非晶铟辞氧化物 (a-InZnO)、非晶氧化辞掺杂氟氧化物 (ZnO:F)、氧化铟掺杂锡氧化物 (In<sub>2</sub>O<sub>3</sub>:Sn)、非晶氧化铟掺杂钼氧化物 (In<sub>2</sub>O<sub>3</sub>:Mo)、铬锡氧化物 (Cd<sub>2</sub>SnO<sub>4</sub>)、非晶氧化辞掺杂铝氧化物 (ZnO:Al)、非晶氧化钛掺杂铌氧化物 (TiO<sub>2</sub>:Nb)、铬锡氧化物 (Cd-Sn-O) 或其他金属氧化物。同层设置的第一金属阻挡层和半导体层可以采用同一种材料制备而成时，第一金属阻挡层与半导体层为同一膜层，在实施过程中，半导体层和第一金属阻挡层通过同一次构图工艺制作而成，相对于现有制作 TFT，没有增加工艺流程。

针对同层设置的第一金属阻挡层和半导体层采用不同种材料制备而成。例如，较佳地，第一金属阻挡层可以采用氧化铜 (CuO<sub>x</sub>)、氮化铜 (CuNy) 或氮氧化铜 (CuN<sub>y</sub>O<sub>x</sub>) 等膜层，或者例如，较佳地，所述第一金属阻挡层采用与所述半导体层不相同的金属氧化物半导体材料制作而成。

上述两种优选方式的 TFT (对应图 2 和图 3 所示的 TFT) 同层设置的第一金属阻挡层和半导体层可以绝缘或不绝缘设置，只要不影响 TFT 功能的实现即可，在此不作限定。所述绝缘设置的方法可以为多种，例如直接采用激光切割方式、掺杂工艺或构图工艺的方式使两者相绝缘。

当同层设置的第一金属阻挡层和半导体层采用同一种材料制备而成时，半导体层和第一金属阻挡层相绝缘设置的情况下，同层形成的半导体层与第

一金属阻挡层可以通过构图工艺、直接采用激光切割方式、掺杂工艺或构图工艺的方式使两者相绝缘，当然只要可以使两者保持绝缘即可，并不限定具体的形成方法。所述绝缘设置的方法可以为多种，例如直接采用激光切割方式、掺杂工艺或构图工艺的方式使两者相绝缘。

5 例如，优选地，同层设置的第一金属阻挡层和半导体层采用同一种材料制备而成，二者不绝缘设置。在具体实施过程中，半导体层和第一金属阻挡层通过同一膜层，同一次构图工艺制作而成，相对于现有制作 TFT，没有增加工艺流程。

例如，优选地，上述图 2 和图 3 提供的 TFT，源漏极层和栅极至少之一的材质为金属铜 (Cu) 或铜合金。例如，优选地，所述形成源极和漏极的材料为铜或铜合金。

例如，优选地，栅极可以为金属铜 (Cu)、金属铬 (Cr)、金属钨 (W)、金属钛 (Ti)、金属钽 (Ta)、金属钼 (Mo) 等，或者是上述至少两种金属的合金。

15 进一步地，第二金属阻挡层可以采用氧化铜 ( $CuO_x$ )、氮化铜 ( $CuN_y$ ) 或氮氧化铜 ( $CuN_yO_x$ ) 等膜层；或者所述第二金属阻挡层采用金属氧化物半导体材料制作而成。例如：可以是铟镓辞氧化物 (IGZO)、铪铟辞氧化物 (HIZO)、铟辞氧化物 (IZO)、非晶铟辞氧化物 (a-InZnO)、非晶氧化辞掺杂氟氧化物 ( $ZnO:F$ )、氧化铟掺杂锡氧化物 ( $In_2O_3:Sn$ )、非晶氧化铟掺杂钼氧化物 ( $In_2O_3:Mo$ )、铬锡氧化物 ( $Cd_2SnO_4$ )、非晶氧化辞掺杂铝氧化物 ( $ZnO:A1$ )、非晶氧化钛掺杂铌氧化物 ( $TiO_2:Nb$ )、铬锡氧化物 (Cd-Sn-O) 或其他金属氧化物。

上述任一方式的 TFT，源极、漏极、栅极至少之一的材质为电阻率较低的铜或铜合金。例如，优选地，源漏极层为金属铜或铜合金，第二金属阻挡层为氧化铜 ( $CuO_x$ )、氮化铜 ( $CuNy$ ) 或氮氧化铜 ( $CuNyO_x$ ) 等。在实施过程中，第二金属阻挡层和 SD 层可以采用同一次构图工艺制作而成。可以理解的是，第二金属阻挡层和 SD 层的形成方式不限于此。

首先，氧化铜 ( $CuO_x$ )、氮化铜 ( $CuNy$ ) 或氮氧化铜 ( $CuNyO_x$ ) 可以与半导体层和第一金属阻挡层形成稳定的界面，其次，氧化铜 ( $CuO_x$ )、氮化铜 ( $CuN_y$ ) 或氮氧化铜 ( $CuNyO_x$ ) 的刻蚀性能与金属铜或铜合金形成的源漏极层的刻蚀性能类似，在同时对源漏极层、以及位于其下方的第一金属阻挡层

进行湿法刻蚀时，由于二者之间存在第二金属阻挡层（氧化铜（ $\text{CuO}_x$ ）、氮化铜（ $\text{CuNy}$ ）或氮氧化铜（ $\text{CuNyO}_x$ ）），解决了金属铜或铜合金直接与第一金属阻挡层结合湿法刻蚀比较难的问题，或者湿法刻蚀出的截面形貌不理想的问题。

5 基于上述任一方式的 TFT，为了更好的阻止形成源极、漏极的材料与形成栅极的材料的相互扩散，第一金属阻挡层在基板上的投影面积应至少完全覆盖源漏极层在基板上的投影面积，但是应保证相互的位置关系不影响 TFT 性能的实现。

为了更好的阻止形成源极、漏极的材料与形成栅极的材料的相互扩散，

10 本发明上述实施例中第二金属阻挡层在基板上的投影面积应至少完全覆盖源漏极层在基板上的投影面积，只要不影响 TFT 功能的实现即可，对具体的位置不作限定。

本发明上述实施例中，第一金属阻挡层与第二金属阻挡层在基板上的投影面积及相互的位置关系不作过多限定，只要不影响 TFT 功能的实现即可。

15 例如，优选地，为了提高氧化物 TFT 的性能，栅极绝缘层可设计为两层，第一层为氮化硅（ $\text{SiN}_x$ ）层，其与栅极相接触，第二层为氧化硅（ $\text{SiO}_x$ ）层，其直接与半导体层和第一金属阻挡层接触。双层绝缘层的设计一方面可以阻挡 TFT 中的各电极中的金属离子的扩散，另一方面可以避免外界的水、氧气等杂质的进入，提高 TFT 的性能。

20 例如，优选地，为了提高半导体层的导电性能，上述任一方式的 TFT 还包括：位于半导体层的上下两侧的第一欧姆接触层和第二欧姆接触层。第一欧姆接触层位于栅极绝缘层和半导体层之间，第二欧姆接触层位于半导体层和源极、漏极之间。该第一欧姆接触层和第二欧姆接触层可以是导电性能更好的掺杂半导体层。

25 例如，优选地，本发明实施例提供的基板可以是玻璃基板、石英或者柔性塑料。

需要说明的是，本发明中例举的结构没有具体阐明显示区域周边的引线区域的结构，各个膜层都是在进行显示区域制作时同时在周边形成的。而显示区域的膜层顺序可以有很多种变化，只要制作出面板驱动必要的元素（比如栅极、源极、漏极和像素电极等），确保面板正常驱动即可。所以周边的膜层结构也相应的有很多变化，比如栅极不一定就直接制作在基板上，有可

能在其下方有别的膜层，为了提高基板与基板上金属膜层的附着性，还可以在基板与栅极之间设置缓冲层，所述缓冲层可以为铟锡氧化物(ITO)膜层或铟锌氧化物(IZO)膜层；比如绝缘层也不一定必须有2层，栅极和半导体层之间也有可能不止一层绝缘层。本发明实施例的结构中，只要确保各金属层彼此绝缘，且具有连接到外部的可导电部件(比如ITO材料制作的连接电极)即可。

上述实施例一与底栅型TFT为例说明，以下将简单介绍本发明实施例一提供的顶栅型TFT。

顶栅型TFT的结构与上述实施例一提供的任一种方式的底栅型TFT的结构类似，也就是说，实施例一上述提供的TFT中的第一金属阻挡层、第二金属阻挡层、栅极绝缘层、基板、欧姆接触层和缓冲层等相关技术特征均适用于顶栅型TFT。不同之处在于，源极、漏极、栅极、栅极绝缘层和半导体层与基板的相对位置发生变化。缓冲层位于基板和源漏极层之间，半导体部分结构与基板之间也有缓冲层。本发明实施例提供的顶栅型TFT中，除TFT结构与上述底栅型TFT结构不同外，其他说明均适用。

实施例二：对应实施例一的其中一种实施方式，即对应上述第一类TFT的其中一种实施方式。

以底栅型TFT为例。

图4为TFT俯视示意图，图5为图4所示的TFT在A-B向的截面图。

该实施例一提供的TFT，包括栅极2(如图4中的虚线内所示的结构)和与栅极2相连的栅极线21、源极8、漏极9，与源极8相连的数据线81，以及半导体层4。

源极8和漏极9可以称为源漏极层，源漏极层所在TFT的膜层称为SD层。

参见图5，本发明实施例提供的TFT，包括：

基板1、形成在基板1上的栅极2；

形成在基板1上位于栅极2上的栅极绝缘层3；

形成在基板1上位于栅极绝缘层3上的半导体层4和第一金属阻挡层5，半导体层4和第一金属阻挡层5位于同一层；

形成在基板1上位于半导体层4和第一金属阻挡层5上的刻蚀阻挡层6，刻蚀阻挡层6位于半导体层4的上方；

形成在基板 1 上位于刻蚀阻挡层 6 上的源极 8 和漏极 9。

例如，较佳地，所述形成源极和漏极的材料和形成栅极的材料中的至少之一为铜或铜合金。

例如，较佳地，参见图 5，第一金属阻挡层 5 位于与源漏极层（即源极 8 和漏极 9）相对应的位置。即，源漏极层的垂直投影位于第一金属阻挡层 5 内以及半导体层 4 内，以保证源漏极层金属离子不会扩散到位于第一金属阻挡层 5 下方的栅极绝缘层 3 和栅极 2 中。

例如，较佳地，图 5 所示的第一金属阻挡层 5 由与半导体层 4 相同的材料制作而成。

在实施过程中，半导体层 4 和第一金属阻挡层 5 通过同一膜层，同一次构图工艺制作而成，相对于现有制作 TFT，没有增加工艺流程。半导体层 4 和第一金属阻挡层 5 相绝缘，同层形成的半导体层 4 与第一金属阻挡层 5 可以通过构图工艺使其之间存在一定的间隙，当然只要可以使两者保持绝缘即可，并不限定具体的形成方法。

所述半导体层可以是金属氧化物，例如：可以是铟镓辞氧化物 (IGZO)、铪铟辞氧化物 (HIZO)、铟辞氧化物 (IZO)、非晶铟辞氧化物 (a-InZnO)、非晶氧化辞掺杂氟氧化物 (ZnO:F)、氧化铟掺杂锡氧化物 (In<sub>2</sub>O<sub>3</sub>:Sn)、非晶氧化铟掺杂钼氧化物 (In<sub>2</sub>O<sub>3</sub>:Mo)、铬锡氧化物 (Cd<sub>2</sub>SnO<sub>4</sub>)、非晶氧化辞掺杂铝氧化物 (ZnO:A1)、非晶氧化钛掺杂铌氧化物 (TiO<sub>2</sub>:Nb)、铬锡氧化物 (Cd-Sn-O) 或其他金属氧化物。

本发明所述第一金属阻挡层为金属氧化物膜层，该金属氧化物膜层可有效阻挡金属离子，提高了 TFT 的性能。

图 4 和图 5 所示的 TFT，通过在源漏极层 (SD 层) 以及栅极绝缘层 3 之间设置有第一金属阻挡层 5，阻挡源漏极层的金属离子进入栅极绝缘层和栅极层。同理，也阻挡栅极层的金属离子进入半导体层和源漏极层，提高了 TFT 性能。

例如，较佳地，参见图 6，本发明实施例提供的 TFT，还包括：第二金属阻挡层 7；位于源漏极层和第一金属阻挡层 5 之间。

例如，较佳地，第二金属阻挡层 7，位于与源漏极层相对应的位置，位于第一金属阻挡层 5 和源漏极层之间。例如，较佳地，第一金属阻挡层 5 和第二金属阻挡层 7 在垂直方向的投影可以重叠。

图 6 所示的 TFT，第二金属阻挡层 7 位于源漏极层和第一金属阻挡层 5 之间，更进一步阻挡了 SD 层的金属离子向栅极绝缘层或栅极扩散，也阻挡了栅极的金属离子向半导体层和 SD 层扩散，更进一步提高了 TFT 的性能。在实施过程中，第二金属阻挡层和 SD 层在同一次构图工艺中制作而成。

5 例如，较佳地，第二金属阻挡层 7 为氧化铜 (CuO)、氮化铜 (CuN)，或

氮氧化铜 (CuNO) 等。氧化铜 (CuO)、氮化铜 (CuN)，或氮氧化铜 (CuNO)

可以与半导体层 4 和第一金属阻挡层 5 形成稳定的界面，在同时对源漏极层、

数据线以及位于其下方的第一金属阻挡层 5 进行湿法刻蚀时，由于二者之间

10 存在第二金属阻挡层 7，例如氧化铜 (CuO)、氮化铜 (CuN)，或氮氧化铜

(CuNO)，解决了金属铜直接与第一金属阻挡层 5 结合湿法刻蚀比较难的问

题，或者湿法刻蚀出的截面形貌不理想的问题。

例如，较佳地，为了提高氧化物 TFT 的性能，栅极绝缘层可设计为两层，

第一层为氮化硅 (SiN<sub>x</sub>)，与栅极相接触，第二层为氧化硅 (SiO<sub>x</sub>) 直接与半

导体层和第一金属阻挡层接触。

15 例如，较佳地，为了提高半导体层的导电性能，所述 TFT 还包括：位于

半导体层的上下两侧的第一欧姆接触层和第二欧姆接触层。第一欧姆接触层

位于栅极绝缘层和半导体层之间，第二欧姆接触层位于半导体层和源极漏极

之间。该第一欧姆接触层和第二欧姆接触层可以是导电性能更好的掺杂半导

体层。

20 例如，较佳地，本发明实施例提供的基板可以是玻璃基板、石英，或者

柔性塑料等。

需要说明的是，本发明中例举的结构没有具体阐明显示区域周边的引线

区域的结构，各个膜层都是在进行显示区域制作时同时在周边形成的。而显示

区域的膜层顺序可以有很多种变化，只要制作出面板驱动必要的元素（比

25 例如栅极、源极、漏极和像素电极等），确保面板正常驱动即可。所以周边的

膜层结构也相应的有很多变化，比如栅极不一定就直接制作在基板上，有可

能在其下方有别的膜层，为了提高基板与基板上金属膜层的附着性，还可以

在基板与栅极之间设置缓冲层，所述缓冲层可以为铟锡氧化物 (ITO) 膜层或

30 铟锌氧化物 (IZO) 膜层；比如绝缘层也不一定必须有两层，栅极和半导体层

之间也有可能不止一层绝缘层。本发明实施例的结构中，只要确保各金属层

彼此绝缘，且具有连接到外部的可导电部件（比如 ITO 材料制作的连接电极）

即可。

以上实施例二提供的 TFT 为底栅型 TFT，以下将简单介绍顶栅型 TFT。

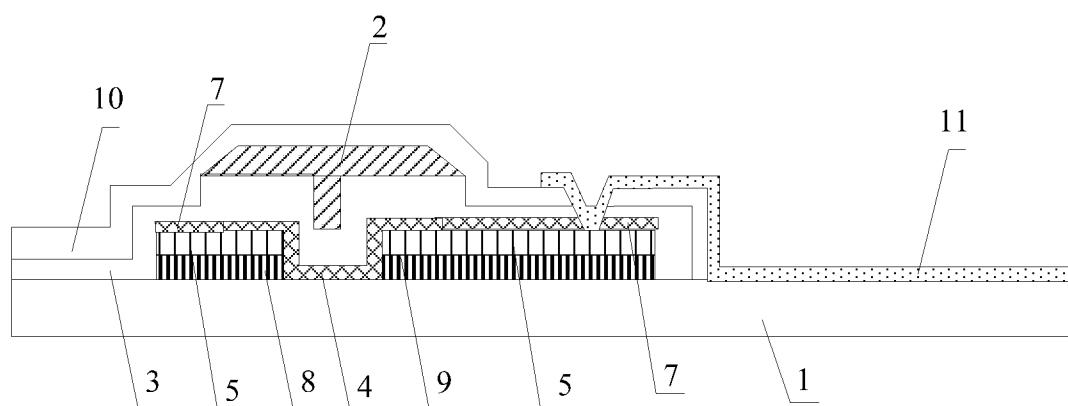

参见图 7，与上述底栅型 TFT 结构类似，不同之处在于，栅极和半导体层所处的位置不同，所述 TFT 包括：

5 基板 1、形成在基板 1 上的源极 8 和漏极 9；

形成在基板 1 上位于源极 8 和漏极 9 上的刻蚀阻挡层 6；

形成在基板 1 上位于刻蚀阻挡层 6 上的半导体层 4 和第一金属阻挡层 5；

形成在基板 1 上位于半导体层 4 和第一金属阻挡层 5 上的栅极绝缘层 3；

形成在基板 1 上位于栅极绝缘层 3 上的栅极 2。

10 所述刻蚀阻挡层实际上是保护源极和漏极不受刻蚀的影响。

例如，较佳地，所述 TFT 还包括：形成在第一金属阻挡层 5 和源极 8 和漏极 9 之间的第二金属阻挡层 7。

例如，较佳地，所述 TFT 还包括：形成在栅极 2 上覆盖整个 TFT 的钝化层 10。

15 与实施例一类似，包括所述顶栅型 TFT 的阵列基板还包括像素电极 11。

像素电极 11 通过过孔与 TFT 的漏极 9 相连。

其他结构与底栅型 TFT 的阵列基板结构类似，这里不再赘述。

实施例三：第二类 TFT（至少包括非晶硅或多晶硅 TFT）。

实施例三提供的第二类 TFT 与上述实施例一提供的 TFT 类似，例如实施例一提供的第一金属阻挡层、第二金属阻挡层、栅极绝缘层、基板、欧姆接触层和缓冲层等的膜层的材质、设置位置等相关技术特征均适用于实施例三提供的第二类 TFT。不同之处包括以下几方面：

(1) 半导体层的材质不同，非晶硅 TFT 和多晶硅 TFT 的半导体层为非晶硅或多晶硅。

25 (2) 无刻蚀阻挡层。

(3) 第一金属阻挡层与半导体层采用不同材料制作而成。

以下简单说明实施例三提供的 TFT 的结构。

例如，较佳地，对于仅设置第一金属阻挡层的底栅型 TFT，为：

所述栅极位于所述基板上；

30 所述栅极绝缘层位于所述栅极上；

所述半导体层和第一金属阻挡层位于所述栅极绝缘层上；

所述源极和漏极位于所述第一金属阻挡层上；

例如，较佳地，对于仅设置第一金属阻挡层的顶栅型 TFT，为：

所述源极和漏极位于所述基板上；

所述半导体层和第一金属阻挡层位于所述源极和漏极上；

5 所述栅极绝缘层位于所述半导体层和第一金属阻挡层上；

所述栅极位于所述栅极绝缘层上。

例如，较佳地，对于同时设置第一金属阻挡层和第二金属阻挡层的底栅型 TFT，为：

10 栅极位于所述基板上；

栅极绝缘层位于所述栅极上；

半导体层和第一金属阻挡层位于所述栅极绝缘层上；

第二金属阻挡层位于所述半导体层和第一金属阻挡层上；

所述源漏极层位于所述第一金属阻挡层上。

例如，较佳地，对于同时设置第一金属阻挡层和第二金属阻挡层的顶栅

15 型 TFT，为：

所述源极和漏极位于所述基板上；

所述第二金属阻挡层位于所述源极和漏极上；

所述半导体层和第一金属阻挡层位于所述第二金属阻挡层上；

所述栅极绝缘层位于所述半导体层和第一金属阻挡层上；

20 所述栅极位于所述栅极绝缘层上。

实施例三提供的顶栅型 TFT 与底栅型 TFT 结构类似，例如第一金属阻挡层、第二金属阻挡层、栅极绝缘层、基板、欧姆接触层和缓冲层等的膜层材质、设置位置等相关技术特征均适用于顶栅型 TFT。实施例三提供的 TFT 至少包括非晶硅或多晶硅 TFT。

25 以上通过实施例一至实施例三说明本发明提供的 TFT。本发明提供的 TFT 不限于为实施例一至实施例三提供的实施方式，任何包括实施例一至实施例三提供的第一金属阻挡层和第二金属阻挡层均包含在本发明范围之内。

实施例四：阵列基板。

本发明实施例三提供的阵列基板，包括实施例一至实施例三提供的任一 30 方式的 TFT，以下所述的 TFT 至少包括金属氧化物 TFT、非晶硅 TFT 和多晶硅 TFT。以下所述的 TFT，至少包括第一金属阻挡层，所述 TFT 例如，优选

地还包括第二金属阻挡层。

所述阵列基板包括上述任一方式的仅包括第一金属阻挡层的 TFT。

所述阵列基板还包括：数据线和栅极线，所述数据线与所述薄膜晶体管的源极相连，所述栅极线与薄膜晶体管的栅极相连；

5 所述第一金属阻挡层位于与所述源极、漏极及数据线相对应的位置；或者

所述第一金属阻挡层位于与所述源极、漏极及栅极线相对应的位置；或者

10 所述第一金属阻挡层位于与所述源极、漏极、栅极线和数据线相对应的位置。

所述阵列基板包括上述任一方式的同时包括第一金属阻挡层和第二金属阻挡层的 TFT。

所述阵列基板还包括：数据线和栅极线，所述数据线与所述薄膜晶体管的源极相连，所述栅极线与薄膜晶体管的栅极相连；

15 所述第一金属阻挡层位于与所述源极、漏极及数据线相对应的位置，或者位于与所述源极、漏极及栅极线相对应的位置，或者位于与所述源极、漏极、栅极线和数据线相对应的位置；和/或

所述第二金属阻挡层位于与所述源极、漏极及数据线相对应的位置，或者位于与所述源极、漏极及栅极线相对应的位置，或者位于与所述源极、漏极、栅极线和数据线相对应的位置。

以下通过附图具体说明，参见图 1，阵列基板还包括：与所述 TFT 中栅极 2 相连的栅极线 21，以及与源极 8 相连的数据线 81。

一般地，数据线 81 和/或栅极线 21 的材质与源漏极层或栅极相同。

在上述 TFT 的基础上，为了更好的防止数据线和/或栅极线向 TFT 中的膜层扩散，或者阻止数据线和栅极线的材料相互扩散，包括上述 TFT 的阵列基板还包括：位于数据线对应区域的第一金属阻挡层，和/或位于栅极线对应区域的第一金属阻挡层。

为了更进一步防止数据线和/或栅极线向 TFT 中的膜层扩散，或者阻止数据线和栅极线的材料相互扩散，在数据线和/或栅极线对应区域设置第一金属阻挡层的基础上，阵列基板还包括：位于数据线对应区域的第二金属阻挡层，和/或位于栅极线对应区域的第二金属阻挡层。

第一金属阻挡层在基板上的投影面积不小于对应位置的源极、漏极、数据线和/或栅极的面积。第二金属阻挡层在基板上的投影面积不小于对应位置的源极、漏极、数据线和/或栅极的面积。数据线和/或栅极在基板上的投影位于第一金属阻挡层在基板上的投影内，但是应保证相互的位置关系不影响 5 TFT 性能的实现。数据线和/或栅极在基板上的投影位于第二金属阻挡层在基板上的投影内，但是应保证相互的位置关系不影响 TFT 性能的实现。

一种优选的实施方式为：参见图 8 和图 9（图 9 为图 8 所示的阵列基板在 C-D 向的截面图），在数据线 81 和栅极线 21 相对应区域均设置第一金属阻挡层 5 和第二金属阻挡层 7。例如，第一金属阻挡层 5 设置于源极 8 和漏极 9 10 相对应的区域，还设置在栅极线 21 和数据线 81 相对应的区域。

第二金属阻挡层也可以设置在与所述源极、漏极以及数据线或所述源极、漏极以及栅极线或所述源极、漏极、栅极线及数据线相对应的位置，这里不再赘述。

例如，优选地，第一金属阻挡层和/或第二金属阻挡层在垂直方向的投影， 15 与数据线、源极和漏极在基板上的投影完全重合。

对于底栅型 TFT，一种实施方式为：先制作栅极和栅极线，后制作第一金属阻挡层，最后制作数据线；第一金属阻挡层可以设置在栅极线上方和/或数据线下方。另一种实施方式为：栅极线和数据线同一次构图工艺形成，在形成栅极时形成栅极线和数据线，或者形成源漏极层时形成栅极线和数据线； 20 第一金属阻挡层可以设置在栅极线和/或数据线的上方，或者设置在栅极线和/或数据线的下方。主要目的是避免栅极线和数据线的金属离子扩散到半导体层对 TFT 性能造成影响。

图 8 中所示的 TFT，在栅极线 21 和数据线 81 对应的区域都设置有第一金属阻挡层。在形成栅极线 21 之后，形成半导体层的同时，形成与栅极线 21 25 区域对应的第一金属阻挡层（图 8 中未示出）。

由于数据线 81 和源极 8 在同一次构图工艺中制作而成，材料相同。在形成数据线 81 之前，形成半导体层 4 的同时，形成位于数据线 81 下方的第一金属阻挡层。

第一阻挡层可以阻挡数据线金属离子扩散到 TFT 的栅极或栅极线或其他 30 膜层结构，进一步提高 TFT 的性能，更进一步提高了显示装置的图像显示效果。

例如，较佳地，该阵列基板还包括位于与基板较近的导电膜层和基板之间的缓冲层，提高导电膜层与基板之间的附着力。例如在栅极线与基板之间，以及第一阻挡层与基板之间设置缓冲层，提高栅极线和第一阻挡层分别与基板的附着力。

5 当然，本发明实施例一、实施例二和实施例三提供的 TFT 和阵列基板结构同样适用于源漏极层、栅极、数据线和栅极线至少之一由其他电阻率较低且金属离子扩散性较高的金属或合金制成的 TFT 和阵列基板。例如金、银、金合金或银合金等用作源漏极层、栅极、数据线和栅极线至少之一时，采用本发明实施例提供的 TFT 和阵列基板同样可以解决金属离子扩散导致的半导体性能下降的问题。

10

参见图 9，本发明实施例提供的阵列基板还包括：位于 TFT 源漏极层上的钝化层 10，以及与 TFT 的漏极 9 相连的像素电极 11。像素电极 11 与漏极 9 通过过孔连接。

例如，优选地，本发明实施例提供的钝化层，由有机树脂材料制作而成。

15 有机树脂可以是苯并环丁烯 (BCB)，也可以是其他有机感光材料。有机树脂相比较无机材料硬度较小，更有利于对阵列基板最外层起到平坦作用，有利于彩膜基板和阵列基板之间的液晶分子的理想排列。

在本发明中，构图工艺，可只包括光刻工艺，或，包括光刻工艺以及刻蚀步骤，同时还可以包括打印、喷墨等其他用于形成预定图形的工艺；光刻工艺，是指包括成膜、曝光、显影等工艺过程的利用光刻胶、掩模板、曝光机等形成图形的工艺。可根据本发明中所形成的结构选择相应的构图工艺。

20

形成膜层的方式通常有沉积、涂敷、溅射等多种方式，下面均以其中的一种或几种方式举例进行说明。举例来说，采用构图工艺在基板上形成包括栅极的图形，为：首先在基板上沉积栅极膜层，然后涂布光刻胶，利用掩模板对光刻胶进行曝光和显影处理来形成光刻胶图案，接着利用该光刻胶图案作为蚀刻掩模，通过刻蚀等工艺去除相应的膜层，并且去除剩余的光刻胶，最终在基板上形成栅极图形。

25

以实施例二提供的 TFT 为例具体介绍所述阵列基板。

图 1 为本发明实施例提供的阵列基板。其中，包括实施例二所述的的 TFT。

30 还包括：与 TFT 中栅极 2 相连的栅极线 21，以及与源极 8 相连的数据线 81。

参见图10, 本发明实施例提供的阵列基板, 第一金属阻挡层5还可以设置在与栅极线和数据线(图10中栅极线和数据线位于第一金属阻挡层5的正下方, 未在图10中体现出)相对应的区域。

对于底栅型TFT, 可以设置在栅极线上方和/或数据线下方。

5 图10中所示的TFT, 在栅极线和数据线(栅极线和数据线在图10中未示出)对应的区域都设置有第一金属阻挡层5。也就是说, 第一金属阻挡层5和/或第二金属阻挡层7在垂直方向的投影, 与数据线、源极8和漏极9在基板1上的投影重叠。

10 在形成栅极线之后, 形成半导体层的同时, 形成与栅极线区域对应的第10 —金属阻挡层。

由于数据线和源极在同一次构图工艺中制作而成, 材料相同。在形成数据线之前, 形成半导体层的同时, 形成第一金属阻挡层。

15 第一金属阻挡层可以阻挡数据线金属离子扩散到TFT的栅极或栅极线或其他膜层结构, 同时也可以阻挡栅极线或数据线的金属离子扩散到半导体层, 进一步提高TFT的性能, 更进一步提高了显示装置的图像显示效果。

同理, 第二金属阻挡层也可以设置在与栅极线和数据线相对应的区域, 这里不再赘述。

例如, 较佳地, 该阵列基板还包括位于栅极线和第一金属阻挡层与基板之间的缓冲层, 提高栅极线和第一金属阻挡层与基板的附着力。

20 参见图9, 本发明实施例提供的阵列基板还包括: 位于TFT源漏极层上的钝化层10, 以及与TFT的漏极8相连的像素电极11。像素电极11与漏极9通过过孔连接, 这属于现有技术, 不再赘述。

25 例如, 较佳地, 本发明实施例提供的钝化层, 由有机树脂材料制作而成。有机树脂可以是苯并环丁烯(BCB), 也可以是其他有机感光材料。有机树脂相比较无机材料硬度较小, 更有利于对阵列基板最外层起到平坦作用, 有利于彩膜基板和阵列基板之间的液晶分子的理想排列。

本发明实施例提供的TFT以及阵列基板, 源漏极层以及数据线可以但不限于由金属铜(Cu)制作而成。

30 本发明实施例提供的栅极可以是金属膜层, 例如可以为金属铬(Cr)、金属钨(W)、金属钛(Ti)、金属钽(Ta)、金属钼(Mo)等, 或者是上述至少两种金属的合金。

### 实施例五：一种显示装置。

本发明实施例提供的显示装置为上述实施例一至实施例三提供的任一方式的 TFT；或者所述显示装置为上述实施例四提供的任一方式的阵列基板。

所述显示装置可以为液晶面板、液晶显示器、液晶电视、OLED 面板、

5 OLED 显示器、OLED 电视或电子纸等显示装置。

该显示装置的一个示例为液晶显示装置，其中，阵列基板与对置基板彼此对置以形成液晶盒，在液晶盒中填充有液晶材料。该对置基板例如为彩膜基板。阵列基板的每个像素单元的像素电极用于施加电场对液晶材料的旋转的程度进行控制从而进行显示操作。在一些示例中，该液晶显示器

10 还包括为阵列基板提供背光的背光源。

该显示装置的另一个示例为有机电致发光 (OLED) 显示装置，其中，阵列基板的每个像素单元的薄膜晶体管连接有机电致发光装置的阳极或阴极，用于驱动有机发光材料发光以进行显示操作。

以下将从工艺流程方面说明本发明实施例提供的薄膜晶体管 TFT 和阵列

15 基板的制作方法。

### 实施例六：薄膜晶体管 TFT 及阵列基板的制作方法。

以上述实施例一至实施例三提供的 TFT 为例说明本发明提供的 TFT 的制作方法。

所述 TFT 的制作方法整体包括：

20 形成包括栅极、源漏极层和半导体层的图形；形成包括栅极绝缘层以及第一金属阻挡层的图形；所述栅极绝缘层位于所述栅极和半导体层之间，所述第一金属阻挡层位于所述源漏极层与栅极绝缘层之间，所述第一金属阻挡层与所述半导体层同层绝缘设置。

针对仅设置有第一金属阻挡层的 TFT，所述形成包括栅极、源漏极层和

25 半导体层的图形；形成包括栅极绝缘层以及第一金属阻挡层的图形，为：

针对底栅型 TFT，所述方法为：

采用构图工艺在基板上形成包括栅极的图形；

采用构图工艺在形成有所述栅极图形的基板上形成包括栅极绝缘层的图

形；

30 采用同一次构图工艺在形成有所述栅极绝缘层图形的基板上形成包括半

导体层和第一金属阻挡层的图形；

采用同一次构图工艺在形成有半导体层和第一金属阻挡层的基板上形成包括源极、漏极的图形；

针对顶栅型 TFT，所述方法为：

采用同一次构图工艺在基板上形成包括源极、漏极的图形；

5 采用同一次构图工艺在形成有所述源极、漏极的基板上形成包括半导体层和第一金属阻挡层的图形；

采用构图工艺在形成有所述半导体层和第一金属阻挡层图形的基板上形成包括栅极绝缘层的图形；

10 采用构图工艺在形成有所述栅极绝缘层图形的基板上形成包括栅极的图

进一步的，在形成有上述第一金属阻挡层的 TFT 的基础上，还包括形成第二金属阻挡层的图形，所述第二金属阻挡层位于所述第一金属阻挡层与所述源极、漏极之间。

15 针对实施例一或实施例二提供的任一方式的 TFT，即具有刻蚀阻挡层的 TFT，还包括形成刻蚀阻挡层的图形，所述刻蚀阻挡层位于所述半导体层与所述源极和漏极之间。

进一步地，所述形成包括栅极、源极、漏极、半导体层、栅极绝缘层、刻蚀阻挡层、第一金属阻挡层和第二金属阻挡层的图形，为：

针对底栅型 TFT，所述方法为：

20 采用构图工艺在基板上形成包括栅极的图形；

采用构图工艺在形成有所述栅极图形的基板上形成包括栅极绝缘层的图

形；

采用同一次构图工艺在形成有所述栅极绝缘层图形的基板上形成包括半

25 导体层和第一金属阻挡层的图形；

采用构图工艺在形成有半导体层和第一金属阻挡层图形的基板上形成包

括刻蚀阻挡层的图形；

采用同一次构图工艺在形成有刻蚀阻挡层图形的基板上形成包括源极、

漏极以及第二金属阻挡层的图形；

针对顶栅型 TFT，所述方法为：

30 采用同一次构图工艺在基板上形成包括源极、漏极以及第二金属阻挡层

的图形；

采用构图工艺在形成有所述源极、漏极和第二金属阻挡层图形的基板上形成包括刻蚀阻挡层的图形；

采用同一次构图工艺在形成有所述刻蚀阻挡层图形的基板上形成包括半导体层和第一金属阻挡层的图形；

5 采用构图工艺在形成有所述半导体层和第一金属阻挡层图形的基板上形成包括栅极绝缘层的图形；

采用构图工艺在形成有所述栅极绝缘层图形的基板上形成包括栅极的图形。

例如，较佳地，所述采用同一次构图工艺在形成有刻蚀阻挡层图形的基10 板上形成包括源极、漏极以及第二金属阻挡层的图形为：

采用镀膜工艺在形成有所述刻蚀阻挡层图形或第一金属阻挡层图形的基板上形成所述铜金属或铜合金膜层；在形成所述铜金属或铜合金膜层的初始时间段内，向腔体内通入预设比例的氧气、氮气或氧气和氮气的混合气体形成铜或铜合金的氧化物、氮化物或氮氧化物用于形成第二金属阻挡层，除所述第二金属阻挡层之外的铜金属或铜合金膜层用于形成源极和漏极；采用一次曝光、显影、光刻刻蚀步骤形成所述源极、漏极以及第二金属阻挡层的图形。

例如，较佳地，所述采用同一次构图工艺在基板上形成包括源极、漏极以及第二金属阻挡层的图形为：

20 采用镀膜工艺在基板上形成所述铜或铜合金膜层；在形成所述铜或铜合金膜层的结束时间段内，向腔体内通入预设比例的氧气、氮气或氧气和氮气的混合气体形成铜或铜合金的氧化物、氮化物或氮氧化物用于形成第二金属阻挡层，除所述第二金属阻挡层之外的铜金属或铜合金膜层用于形成源极和漏极；采用一次曝光、显影、光刻刻蚀步骤形成所述源极、漏极以及第二金属阻挡层的图形。

其中一种较具体的与实施例二对应的实施方式，在上述实施方式（具有第一金属阻挡层、第二金属阻挡层）的基础上，进一步地，所述第一金属阻挡层与所述半导体层绝缘设置。所述半导体层由金属氧化物半导体材料制作而成，进一步地，所述第一金属阻挡层与所述半导体层采用相同的材料制作而成。

30 针对实施例三提供的 TFT，即无刻蚀阻挡层的 TFT，所述形成包括栅极、

源极、漏极、半导体层、栅极绝缘层、刻蚀阻挡层、第一金属阻挡层和第二金属阻挡层的图形，为：

针对底栅型 TFT，所述方法为：

所述形成包括栅极、源极、漏极、半导体层、栅极绝缘层、第一金属阻挡层和第二金属阻挡层的图形，为：

采用构图工艺在基板上形成包括栅极的图形；

采用构图工艺在形成有所述栅极图形的基板上形成包括栅极绝缘层的图形；

采用构图工艺在形成有所述栅极绝缘层图形的基板上形成包括半导体层的图形；

采用构图工艺在形成有所述半导体层图形的基板上形成第一金属阻挡层的图形；

采用同一次构图工艺在形成有第一金属阻挡层图形的基板上形成包括源极、漏极以及第二金属阻挡层的图形；

针对顶栅型 TFT，所述方法为：

采用同一次构图工艺在基板上形成包括源极、漏极以及第二金属阻挡层的图形；

采用构图工艺在形成有所述源极、漏极以及第二金属阻挡层图形的基板上形成包括半导体层的图形；

采用构图工艺在形成有所述半导体层图形的基板上形成第一金属阻挡层的图形；

采用构图工艺在形成有所述第一金属阻挡层图形的基板上形成包括栅极绝缘层的图形；

采用构图工艺在形成有所述栅极绝缘层图形的基板上形成包括栅极的图形。

例如，较佳地，所述采用同一次构图工艺在形成有第一金属阻挡层图形的基板上形成包括源极、漏极以及第二金属阻挡层的图形为：

采用镀膜工艺在形成有所述刻蚀阻挡层图形或第一金属阻挡层图形的基板上形成所述铜金属或铜合金膜层；在形成所述铜金属或铜合金膜层的初始时间段内，向腔体内通入预设比例的氧气、氮气或氧气和氮气的混合气体形成铜或铜合金的氧化物、氮化物或氮氧化物用于形成第二金属阻挡层，除所

述第二金属阻挡层之外的铜金属或铜合金膜层用于形成源极和漏极；采用一次曝光、显影、光刻刻蚀步骤形成所述源极、漏极以及第二金属阻挡层的图形。

5 例如，较佳地，所述采用同一次构图工艺在基板上形成包括源极、漏极以及第二金属阻挡层的图形为：

采用镀膜工艺在基板上形成所述铜或铜合金膜层；在形成所述铜或铜合金膜层的结束时间段内，向腔体内通入预设比例的氧气、氮气或氧气和氮气的混合气体形成铜或铜合金的氧化物、氮化物或氮氧化物用于形成第二金属阻挡层，除所述第二金属阻挡层之外的铜金属或铜合金膜层用于形成源极和漏极；采用一次曝光、显影、光刻刻蚀步骤形成所述源极、漏极以及第二金属阻挡层的图形。

以下将以实施例二提供的 TFT 为例说明本发明提供的 TFT 的制作方法，下面从工艺流程方面说明本发明实施例提供的薄膜晶体管的制作方法。

本发明实施例提供的薄膜晶体管的制作方法整体包括：

15 形成包括栅极、源漏极层和半导体层的图形；以及形成包括栅极绝缘层、刻蚀阻挡层，以及第一金属阻挡层的图形；

所述栅极绝缘层位于所述栅极和半导体层之间，所述刻蚀阻挡层位于所述半导体层与源漏极层之间，所述第一金属阻挡层位于所述源漏极层与栅极绝缘层之间，其中，所述第一金属阻挡层与所述半导体层同层绝缘设置。

20 参见图 11，制作底栅型 TFT 的阵列基板的方法具体包括以下步骤：

S11、采用构图工艺在基板上形成包括栅极的图形；

S12、采用构图工艺在形成有所述栅极图形的基板上形成包括栅极绝缘层的图形；

25 513、采用同一次构图工艺在形成有所述栅极绝缘层图形的基板上形成包括半导体层和第一金属阻挡层的图形；

514、采用构图工艺在形成有半导体层和第一金属阻挡层图形的基板上形成包括刻蚀阻挡层的图形；

S15、采用同一次构图工艺在形成有刻蚀阻挡层图形的基板上依次形成包括源漏极层以及第二金属阻挡层的图形。

30 更进一步的，可以通过溅射或热蒸发的方法在形成有刻蚀阻挡层的基板上沉积一层金属膜层，沉积金属膜层的初始时间段内，向溅射或热蒸发腔体

内通入预设比例的氧气  $O_2$  和/或氮气  $N_2$ 。

如果不包括形成刻蚀阻挡层的步骤时，所述形成包括源漏极层，以及第二金属阻挡层的图形，为：

在形成有包括半导体层和第一金属阻挡层的图形的基板上形成一层金属膜层；

采用一次构图工艺形成所述包括源漏极层，以及第二金属阻挡层的图形；

其中，在形成金属膜层的初始时间段内，向腔体内通入预设比例的氧气或氮气或者氧气和氮气的混合气体。

例如，优选地，参见图 12，制作顶栅型 TFT 的阵列基板的方法具体包括

以下步骤：

S21、采用同一次构图工艺在基板上依次形成包括源漏极层，以及第二金属阻挡层的图形；

S22、采用构图工艺在形成有所述源漏极层和第二金属阻挡层图形的基板上形成包括刻蚀阻挡层的图形；

S23、采用同一次构图工艺在形成有所述刻蚀阻挡层图形的基板上形成包括半导体层和第一金属阻挡层的图形；

S24、采用构图工艺在形成有所述半导体层和第一金属阻挡层图形的基板上形成包括栅极绝缘层的图形；

S25、采用构图工艺在形成有所述栅极绝缘层图形的基板上形成包括栅极的图形。

例如，优选地，图 12 所示的 TFT 的阵列基板的制作方法，所述形成包括源漏极层，以及第二金属阻挡层的图形，为：

在基板上形成一层金属膜层；采用一次构图工艺形成包括源漏极层，以及第二金属阻挡层图形；

其中，在形成金属膜层的结束时间段内，向腔体内通入预设比例的氧气或氮气或者氧气和氮气的混合气体。

更进一步的，可以通过溅射或热蒸发的方法在形成有刻蚀阻挡层的基板上沉积一层金属膜层，沉积金属膜层的结束时间段内，向溅射或热蒸发腔体内通入预设比例的氧气或氮气或者氧气和氮气的混合气体。

本发明的上述方法的实施例中，所述形成源极和漏极的材料及形成栅极的材料中的至少一个为铜或铜合金，当然并不限于此，本发明实施例的目的

在于采用第一金属阻挡层阻止形成源极、漏极的材料与形成栅极的材料的相互扩散，其他形成栅极、源极、漏极的材料具备很强的扩散性时也适用于本发明，例如金、银等。下述均以形成源极和漏极的材料及形成栅极的材料为金属铜举例说明。

5 本发明上述实施例中同层设置的第一金属阻挡层和半导体层可以采用同一种材料制备而成，当半导体层为金属氧化物半导体层时，第一金属阻挡层可以采用制备金属氧化物半导体层的材料，例如：可以是铟镓辞氧化物 (IGZO)、铪铟辞氧化物 (HIZO)、铟辞氧化物 (IZO)、非晶铟辞氧化物 (a-InZnO)、非晶氧化辞掺杂氟氧化物 (ZnO:F)、氧化铟掺杂锡氧化物 (In<sub>2</sub>O<sub>3</sub>:Sn)、非晶氧化铟掺杂钼氧化物 (In<sub>2</sub>O<sub>3</sub>:Mo)、铬锡氧化物 (Cd<sub>2</sub>SnO<sub>4</sub>)、非晶氧化辞掺杂铝氧化物 (ZnO:A1)、非晶氧化钛掺杂铌氧化物 (TiO<sub>2</sub>:Nb)、铬锡氧化物 (Cd-Sn-O) 或其他金属氧化物。

10 本发明上述实施例中同层设置的第一金属阻挡层和半导体层可以采用不同种材料制备而成，当半导体层为金属氧化物半导体层时，第一金属阻挡层可以采用氧化铜 (CuO<sub>x</sub>)、氮化铜 (CuNy) 或氮氧化铜 (CuNyO<sub>x</sub>) 等，或，采用与形成半导体层的金属氧化物不同的其他金属氧化物；当半导体层为非晶硅或多晶硅半导体层时，第一金属阻挡层可以采用制备金属氧化物半导体层的材料，也可以采用氧化铜 (CuO<sub>x</sub>)、氮化铜 (CuNy) 或氮氧化铜 (CuNyO<sub>x</sub>) 等。

15 20 本发明上述实施例中同层设置的第一金属阻挡层和半导体层可以绝缘或不绝缘设置，只要不影响 TFT 功能的实现即可，在此不作限定。所述绝缘设置的方法可以为多种，例如直接采用激光切割方式、掺杂工艺或构图工艺的方式使两者相绝缘。

25 为了更好的阻止形成源极、漏极的材料与形成栅极的材料的相互扩散，本发明上述实施例中，第一金属阻挡层在正投影方向上的面积应至少完全覆盖源漏极层的面积，但是应保证相互的位置关系不影响 TFT 性能的实现。

为了更好的阻止形成源极、漏极的材料与形成栅极的材料的相互扩散，本发明上述实施例中第二金属阻挡层在正投影方向上的面积应至少完全覆盖源漏极层的面积，只要不影响 TFT 功能的实现即可，对具体的位置不作限定。

30 本发明上述实施例中，所述第二金属阻挡层可以采用氧化铜 (CuO<sub>x</sub>)、氮化铜 (CuNy) 或氮氧化铜 (CuN<sub>y</sub>O<sub>x</sub>) 等；也可以采用形成金属氧化物半导体

层的材料，例如：可以是铟镓锌氧化物 (IGZO)、铪铟锌氧化物 (HIZO)、铟

5 锌氧化物 (IZO)、非晶铟锌氧化物 (a-InZnO)、非晶氧化锌掺杂氟氧化物

(ZnO:F)、氧化铟掺杂锡氧化物 (In<sub>2</sub>O<sub>3</sub>:Sn)、非晶氧化铟掺杂钼氧化物

(In<sub>2</sub>O<sub>3</sub>:Mo)、铬锡氧化物 (Cd<sub>2</sub>SnO<sub>4</sub>)、非晶氧化锌掺杂铝氧化物 (ZnO:Al)、

10 非晶氧化钛掺杂铌氧化物 (TiO<sub>2</sub>:Nb)、铬锡氧化物 (Cd-Sn-O) 或其他金属氧化物。

本发明上述实施例中，第一金属阻挡层与第二金属阻挡层在正投影方向上的面积及相互的位置关系不作过多限定，只要不影响 TFT 功能的实现即可。

10 下面以制作图 9 或图 10 所示的阵列基板为例，说明制作 TFT 或阵列基板的优选的工艺流程。

需要说明的是，下述以金属氧化物 TFT 为例说明，所述第一金属阻挡层

5 采用与半导体层 4 相同的金属氧化物制备形成，所述形成源极 8 和漏极 9

的材料为铜，所述第二金属阻挡层 7 为氧化铜 (CuO<sub>x</sub>)、氮化铜 (CuN<sub>y</sub>) 或

氮氧化铜 (CuNyO<sub>x</sub>) 等。

15 阵列基板制作方法包括：

步骤一：栅极 2 和栅极线 21 图形的形成过程。

在基板上采用溅射或热蒸发的方法，沉积栅极金属膜层，厚度优选为

4000 Å ~ 15000 Å。通过一次曝光显影、光刻和刻蚀工艺形成栅极 2 和栅极线

21 图形。形成的栅极 2 和栅极线 21 的图形和位置与现有技术相同这里不再赘

20 述。

所述形成栅极 2 和栅极线 21 图形的金属膜层可以为金属铜 (Cu)、金属

铬 (Cr)、金属钨 (W)、金属钛 (Ti)、金属钽 (Ta)、金属钼 (Mo) 等，或

者是上述至少两种金属的合金。

步骤二：栅极绝缘层 3 图形的形成过程。

25 在完成步骤一的基板上通过化学气相沉积法 (PECVD) 连续沉积绝缘层，

厚度优选为 2000 Å ~ 5000 Å，该绝缘层为待形成栅极绝缘层 2 图形的绝缘层；

具体地，该绝缘层可以为氧化硅或者氮化硅层。氧化硅或者氮化硅层可以是

氧化物、氮化物或者氧氮化合物与反应气体通过化学气相沉积法形成。所述

30 反应气体可以是硅烷 (SiH<sub>4</sub>)、氨气 (NH<sub>3</sub>) 和氮气 (N<sub>2</sub>) 的混合物，或者为

二氯化硅 (SiH<sub>2</sub>Cl<sub>2</sub>)、氨气 (NH<sub>3</sub>) 和氮气 (N<sub>2</sub>) 的混合物。

为了提高氧化物 TFT 的性能，栅极绝缘层 2 图形可通过两层材料不同的

绝缘层形成，第一层为氮化硅 ( $\text{SiN}_x$ )，第二层为氧化硅 ( $\text{SiO}_x$ )，第一层氮化硅 ( $\text{SiN}_x$ ) 形成的栅极绝缘层直接与栅极相接触，第二层氧化硅 ( $\text{SiO}_x$ ) 直接与半导体层和第一金属阻挡层接触。双层栅极绝缘层图形是由双层绝缘层通过一次曝光显影、光刻和刻蚀工艺形成。

5 步骤三：半导体层 4 和第一金属阻挡层 5 图形的形成过程。

在形成有栅极绝缘层 3 的基板上，通过溅射方法连续沉积金属氧化物膜层，厚度优选为 50A ~ 1000A。通过一次曝光显影、光刻和刻蚀工艺形成半导体层 4 和第一金属阻挡层 5 的图形。

所述金属氧化物可以是铟镓辞氧化物 (IGZO)、铪铟辞氧化物 (HIZO)、10 钨辞氧化物 (IZO)、非晶铟辞氧化物 (a-InZnO)、非晶氧化辞掺杂氟氧化物 (ZnO:F)、氧化铟掺杂锡氧化物 ( $\text{In}_2\text{O}_3:\text{Sn}$ )、非晶氧化铟掺杂钼氧化物 ( $\text{In}_2\text{O}_3:\text{Mo}$ )、铬锡氧化物 ( $\text{Cd}_2\text{SnO}_4$ )、非晶氧化辞掺杂铝氧化物 (ZnO:A1)、非晶氧化钛掺杂铌氧化物 ( $\text{TiO}_2:\text{Nb}$ )、铬锡氧化物 (Cd-Sn-O) 或其他金属氧化物。

15 第一金属阻挡层 5 位于与待形成源漏极层和数据线 81 相对应的位置，以及与栅极 2 相对应的位置。

半导体层 4 和第一金属阻挡层 5 同层设置，没有增加工艺流程。该步骤通过一次图形化工艺形成第一金属阻挡层 5 图形，相对于现有技术没有增加工艺流程，但实现了源漏极层和数据线的金属离子的隔离功能，该结构可以20 很好地阻止金属离子的扩散，尤其是高温工艺下金属离子的扩散，提高了 TFT 的性能。

步骤四：刻蚀阻挡层图形 6 的形成过程。

在完成步骤三的基板上通过 PECVD 方法连续沉积绝缘层，厚度优选为 1000A ~ 3000A，绝缘层为刻蚀阻挡层 6，刻蚀阻挡层 6 可以选用氧化物、氮化物或者氧氮化合物，对应的反应气体可以为硅烷 ( $\text{SiH}_4$ )、氨气 ( $\text{NH}_3$ )、氮气 ( $\text{N}_2$ ) 或二氯化硅 ( $\text{SiH}_2\text{Cl}_2$ )、氨气 ( $\text{NH}_3$ )、氮气 ( $\text{N}_2$ )，与形成栅极绝缘层类似，为了提高氧化物 TFT 的性能，刻蚀阻挡层可设计为两层，第一层为氮化硅 ( $\text{SiN}_x$ )，第二层为氧化硅 ( $\text{SiO}_x$ )，氧化硅 ( $\text{SiO}_x$ ) 层直接与金属氧化物接触。双层刻蚀阻挡层 6 图形是由双层绝缘层通过一次曝光显影、光刻和30 刻蚀工艺形成。

步骤五：第二金属阻挡层图形 7 和源漏极层（即源极 8 和漏极 9）图形的

形成过程。

通过溅射或热蒸发的方法，在基板上沉积金属铜薄膜，厚度优选为1000A ~ 6000A。以形成铜 (Cu) 金属膜层为例：具体地，在沉积金属 (Cu) 膜层的初始时间 At 内，向溅射或热蒸发腔体内通入预设比例的氧气 (O<sub>2</sub>)、5 氮气 (N<sub>2</sub>) 或者二者的混合气体，形成一层氮化铜 (CuN<sub>y</sub>) (通过氮气 N<sub>2</sub> 的情况)、氧化铜 (CuO<sub>x</sub>) (通过氧气 O<sub>2</sub> 的情况) 或氮氧化铜 (CuN<sub>y</sub>O<sub>x</sub>) (通过 O<sub>2</sub> 和 N<sub>2</sub> 的混合气体)，厚度优选为 10A ~ 400A。形成的氮化铜 (CuNy)、氧化铜 (CuO<sub>x</sub>)、或氮氧化铜 (CuNyO<sub>x</sub>) 为第二金属阻挡层 7。

所述初始时间 At 可以根据经验值设置。氮化铜 (CuN<sub>y</sub>)、氧化铜 (CuO<sub>x</sub>)、10 或氮氧化铜 (CuN<sub>y</sub>O<sub>x</sub>) 很稳定，与氧化物半导体层可以形成稳定的界面，该物质具有阻止铜 (Cu) 离子的扩散能力，其下的金属氧化物半导体层 (第一金属阻挡层 5) 具有进一步阻止铜 (Cu) 离子的扩散能力，可以有效地阻止穿透氮化铜薄膜的铜 (Cu) 离子，这种设计可以有效地阻止铜 (Cu) 离子的扩散，同时还简化了生产工艺，同时解决了铜 (Cu) 和阻挡层金属结合刻蚀15 工艺难的问题。

在 t-At 时间段内，停止向腔体内通入预设比例的氧气 (O<sub>2</sub>)、氮气 (N<sub>2</sub>) 或者二者的混合气体。此阶段形成的金属膜层为铜 (Cu) 金属膜层，也即源极和漏极，以及数据线。其中，t 可以理解为形成第二金属阻挡层图形和源漏极层图形所需要的总时间。

20 通过一次曝光显影、光刻和刻蚀工艺形成第二金属阻挡层 7、源漏极层，以及数据线 81 的图形。

例如，优选地，第二金属阻挡层 7 的图形与源极 8 和漏极 9，以及数据线 81 的图形相同，且二者完全重合。

步骤六：钝化层 10 图形的形成过程。

25 在完成步骤五的基板上通过 PECVD 方法沉积钝化层 10，厚度优选为 2000A ~ 10000A。钝化层 10 可以选用氧化物、氮化物或者氧氮化合物，硅的氧化对应的反应气体可以为硅烷 (SiH<sub>4</sub>)、氮的氧化物 (N<sub>2</sub>O)；氮化物或者氧氮化合物对应反应气体是硅烷 (SiH<sub>4</sub>)、氨气 (NH<sub>3</sub>)、氮气 (N<sub>2</sub>) 或二氯化硅 (SiH<sub>2</sub>Cl<sub>2</sub>)、氨气 (NH<sub>3</sub>)、氮气 (N<sub>2</sub>)；钝化层 10 可以使用氧化铝 (Al<sub>2</sub>O<sub>3</sub>) 30 膜层，或者双层或多层的阻挡结构。

此外，在该过程中还可以通过曝光显影、光刻和刻蚀工艺形成栅极焊接

区域 (Gate PAD) 和源漏极层 焊接 区域 (SD PAD )，便 于后 续 电 路 板 与 栅 极 线 和 数据 线 相 连 。

具 体 地 ， 钝 化 层 10 的 形 成 过 程 为：通 过 在 形 成 有 源 漏 极 层 以 及 数据 线 图 形 的 基 板 上 涂 覆 一 层 有 机 树 脂 ， 厚 度 优 选 为 4000A ~ 30000A 。 有 机 树 脂 可 以 是 苯 并 环 丁 烯 (BCB )，也 可 以 是 其 他 的 有 机 感 光 材 料 。

涂 覆 一 层 有 机 树 脂 ， 通 过 一 次 曝 光 显 影 、 光 刻 和 刻 蚀 工 艺 后 ， 形 成 阵 列 基 板 上 外 围 区 域 的 Gate PAD 和 SD PAD 。

步 骤 七：像 素 电 极 图 形 11 的 形 成 过 程 。

在 完 成 步 骤 六 的 基 板 上 通 过 溅 射 或 热 蒸 发 的 方 法 沉 积 透 明 导 电 层 膜 层 ， 10 厚 度 优 选 为 300A ~ 1500A 。

通 过 一 次 曝 光 显 影 、 光 刻 和 刻 蚀 工 艺 后 形 成 像 素 电 极 11。 所 述 像 素 电 极 11 可 以 是 ITO 或 者 IZO，或 者 其 他 的 透 明 金 属 氧 化 物 。

形 成 顶 栅 型 金 属 氧 化 物 TFT 的 阵 列 基 板 工 艺 流 程 和 上 述 步 骤 一 至 步 骤 七 形 成 底 栅 型 金 属 氧 化 物 TFT 的 阵 列 基 板 工 艺 流 程 类 似 ， 这 里 不 再 费 述 。

15 但 是 形 成 第 二 金 属 阻 挡 层 和 7 源 极 8、漏 极 9 的 过 程 有 所 不 同 ， 这 是 因 为 ， 第 二 金 属 阻 挡 层 7 是 后 形 成 在 源 漏 极 层 上 方 的 ， 形 成 过 程 如 下 ：

通 过 溅 射 或 热 蒸 发 的 方 法 在 基 板 上 沉 积 一 层 金 属 膜 层 ；

其 中 ， 在 沉 积 金 属 膜 层 的 结 束 时 间 段 内 ， 向 溅 射 或 热 蒸 发 腔 体 内 通 入 预 设 比 例 的 氧 气 (O<sub>2</sub>) 和 / 或 氮 气 (N<sub>2</sub>) 。

20 其 中 ， 本 发 明 所 述 的 通 入 预 设 比 例 的 气 体 与 形 成 膜 层 的 厚 度 以 及 各 工 艺 参 数 相 关 ， 在 此 并 不 做 限 定 。

实 施 例 七：一 种 阻 挡 层 。

本 发 明 实 施 例 提 供 一 种 阻 挡 层 ， 用 于 上 述 实 施 例 仅 设 置 有 第 一 金 属 阻 挡 层 的 薄 膜 晶 体 管 或 阵 列 基 板 中 阻 止 铜 或 铜 合 金 的 扩 散 的 第 一 金 属 阻 挡 层 。

25 例 如 ， 较 佳 地 ， 所 述 阻 挡 层 的 材 质 为 具 有 阻 止 形 成 源 极 和 漏 极 的 材 质 与 形 成 栅 极 的 材 质 的 相 互 扩 散 功 能 的 金 属 氧 化 物 、 金 属 氮 化 物 或 金 属 氮 氧 化 物 。

例 如 ， 较 佳 地 ， 所 述 金 属 氧 化 物 为 具 有 阻 止 形 成 源 极 和 漏 极 的 材 质 与 形 成 栅 极 的 材 质 的 相 互 扩 散 功 能 的 氧 化 铜 (CuO<sub>x</sub>) 、 所 述 金 属 氧 化 物 可 以 为 具 有 半 导 体 性 质 的 铟 镍 辜 氧 化 物 (IGZO) 、 铟 镍 辜 氧 化 物 (HIZO) 、 铟 辜 氧 化 物 30 (IZO) 、 非 晶 铟 辜 氧 化 物 (a-InZnO) 、 非 晶 氧 化 铟 辜 氧 化 物 (ZnO:F) 、 氧 化 铟 辜 氧 化 物 (In<sub>2</sub>O<sub>3</sub>:Sn) 、 非 晶 氧 化 铟 辜 氧 化 物 (In<sub>2</sub>O<sub>3</sub>:Mo) 、 铬

锡 氧化 物 ( $\text{Cd}_2\text{SnO}_4$ )、非 晶 氧化 锌 摻 杂 铝 氧化 物 ( $\text{ZnO:Al}$ )、非 晶 氧化 钛 摻 杂 铌 氧化 物 ( $\text{TiO}_2:\text{Nb}$ )、铬 锡 氧化 物 ( $\text{Cd-Sn-O}$ ) 或 其 他 金 属 氧化 物 等。

例 如，较 佳 地，所 述 金 属 氮化 物 为 具 有 阻 止 形 成 源 极 和 漏 极 的 材 料 与 形 成 栅 极 的 材 料 的 相 互 扩 散 功 能 的 铜 金 属 氮化 物，例 如 氮化 铜 ( $\text{CuN}_y$ ) 等。

5 例 如，较 佳 地，所 述 金 属 氮化 物 为 具 有 阻 止 形 成 源 极 和 漏 极 的 材 料 与 形 成 栅 极 的 材 料 的 相 互 扩 散 功 能 的 铜 金 属 氮化 物，例 如 为 氮化 铜 ( $\text{CuNyO}_x$ ) 等。

本 发 明 实 施 例 提 供 另 一 种 阻 挡 层，用 于 所 述 同 时 设 置 有 第 一 金 属 阻 挡 层 和 第 二 金 属 阻 挡 层 的 薄 膜 晶 体 管 或 阵 列 基 板 中 阻 止 铜 或 铜 合 金 的 扩 散 的 第 一 金 属 阻 挡 层 和 / 或 第 二 金 属 阻 挡 层。

例 如，较 佳 地，所 述 阻 挡 层 的 材 质 为 具 有 阻 止 形 成 源 极 和 漏 极 的 材 料 与 形 成 栅 极 的 材 料 的 相 互 扩 散 功 能 的 金 属 氧化 物、金 属 氮化 物 或 金 属 氮化 物。

例 如，较 佳 地，所 述 金 属 氧化 物 为 具 有 阻 止 形 成 源 极 和 漏 极 的 材 料 与 形 成 栅 极 的 材 料 的 相 互 扩 散 功 能 的 氧化 铜 ( $\text{CuO}_x$ )、所 述 金 属 氧化 物 可 以 为 具 有 15 半 导 体 性 质 的 铜 镍 锌 氧化 物 ( $\text{IGZO}$ )、镓 镍 锌 氧化 物 ( $\text{HIZO}$ )、铟 锌 氧化 物 ( $\text{IZO}$ )、非 晶 镍 锌 氧化 物 ( $\text{a-InZnO}$ )、非 晶 氧化 锌 摻 杂 氟 氧化 物 ( $\text{ZnO:F}$ )、 氧化 铜 摻 杂 锡 氧化 物 ( $\text{In}_2\text{O}_3:\text{Sn}$ )、非 晶 氧化 铜 摻 杂 钼 氧化 物 ( $\text{In}_2\text{O}_3:\text{Mo}$ )、铬 锡 氧化 物 ( $\text{Cd}_2\text{SnO}_4$ )、非 晶 氧化 锌 摻 杂 铝 氧化 物 ( $\text{ZnO:Al}$ )、非 晶 氧化 钛 摻 杂 铌 氧化 物 ( $\text{TiO}_2:\text{Nb}$ )、铬 锡 氧化 物 ( $\text{Cd-Sn-O}$ ) 或 其 他 金 属 氧化 物 等。

20 例 如，较 佳 地，所 述 金 属 氮化 物 为 具 有 阻 止 形 成 源 极 和 漏 极 的 材 料 与 形 成 栅 极 的 材 料 的 相 互 扩 散 功 能 的 铜 金 属 氮化 物，例 如 氮化 铜 ( $\text{CuN}_y$ ) 等。

例 如，较 佳 地，所 述 金 属 氮化 物 为 具 有 阻 止 形 成 源 极 和 漏 极 的 材 料 与 形 成 栅 极 的 材 料 的 相 互 扩 散 功 能 的 铜 金 属 氮化 物，例 如 为 氮化 铜 ( $\text{CuNyO}_x$ ) 等。

25 所 述 阻 挡 层 不 限 于 用 于 TFT 或 阵 列 基 板 中，可 以 用 于 任 何 需 要 阻 挡 高 扩 散 性 金 属 离 子 的 结 构，这 里 就 不 一 一 列 举。

综 上 所 述，本 发 明 实 施 例 提 供 了 一 种 薄 膜 晶 体 管，在 源 漏 极 层 与 栅 极 绝 缘 层 之 间 设 置 有 第 一 金 属 阻 挡 层，该 第 一 金 属 阻 挡 层 有 效 阻 止 源 漏 极 层 金 属 离 子 向 栅 极 绝 缘 层 和 栅 极 扩 散。提 高 TFT 的 性 能，提 高 图 像 的 画 质。此 外，30 所 述 薄 膜 晶 体 管 在 源 漏 极 层 以 及 第 一 金 属 阻 挡 层 之 间 还 设 置 了 第 二 金 属 阻 挡 层，更 进 一 步 阻 止 源 漏 极 层 金 属 离 子 向 栅 极 绝 缘 层 和 栅 极 扩 散，提 高 TFT 的

性能，提高图像的画质。本发明实施例提供的阵列基板和显示装置，分别包括上述薄膜晶体管，实现图像画质较佳，信号延迟较小的显示装置。阻挡层为具有阻止形成源极和漏极的材料与形成栅极的材料的相互扩散功能的金属氧化物、金属氮化物或金属氮氧化物，且金属氧化物、金属氮化物或金属氮氧化物为较常见的材料。

5

显然，本领域的技术人员可以对本发明进行各种改动和变型而不脱离本发明的精神和范围。这样，倘若本发明的这些修改和变型属于本发明权利要求及其等同技术的范围之内，则本发明也意图包含这些改动和变型在内。

## 权 利 要 求 书

1、一种薄膜晶体管，包括：

位于基板上的栅极、源极、漏极、半导体层、栅极绝缘层以及第一金属阻挡层；所述栅极绝缘层位于所述栅极和所述半导体层之间；所述第一金属阻挡层位于所述源极、漏极与栅极绝缘层之间；其中，所述第一金属阻挡层与所述半导体层同层设置，所述第一金属阻挡层阻止形成源极和漏极的材料与形成栅极的材料的相互扩散。

2、根据权利要求1所述的薄膜晶体管，还包括位于所述源极、漏极与所述半导体层之间的刻蚀阻挡层。

3、根据权利要求2所述的薄膜晶体管，其中所述第一金属阻挡层与所述半导体层绝缘设置。

4、根据权利要求1或3所述的薄膜晶体管，其中所述形成源极和漏极的材料和形成栅极的材料中的至少之一为铜或铜合金。

5、根据权利要求4所述的薄膜晶体管，其中所述半导体层为金属氧化物半导体层。

6、根据权利要求5所述的薄膜晶体管，其中所述第一金属阻挡层采用与所述半导体层相同的材料制作而成。

7、根据权利要求5所述的薄膜晶体管，其中所述第一金属阻挡层为氧化铜、氮化铜或氮氧化铜膜层。

8、根据权利要求5所述的薄膜晶体管，其中所述第一金属阻挡层采用与所述半导体层不相同的金属氧化物半导体材料制作而成。

9、根据权利要求4所述的薄膜晶体管，其中所述薄膜晶体管还包括：第二金属阻挡层，所述第二金属阻挡层位于所述第一金属阻挡层与所述源极、漏极之间，所述第二金属阻挡层阻止形成源极和漏极的材料与形成栅极的材料的相互扩散。

10、根据权利要求9所述的薄膜晶体管，其中所述形成源极和漏极的材料为铜或铜合金。

11、根据权利要求10所述的薄膜晶体管，其中所述第二金属阻挡层为氧化铜、氮化铜，或氮氧化铜膜层。

12、根据权利要求10所述的薄膜晶体管，其中所述第二金属阻挡层采用

金属氧化物半导体材料制作而成。

13、根据权利要求 9 所述的薄膜晶体管，其中所述薄膜晶体管的结构为：

所述栅极位于所述基板上；

所述栅极绝缘层位于所述栅极上；

5 所述半导体层和第一金属阻挡层位于所述栅极绝缘层上；

所述刻蚀阻挡层位于所述半导体层上；

所述第二金属阻挡层位于所述半导体层和第一金属阻挡层上；

所述源漏极层位于所述第二金属阻挡层上；

或者所述薄膜晶体管的结构为：

10 所述源漏极层位于所述基板上；

所述第二金属阻挡层位于所述源漏极层上；

所述刻蚀阻挡层位于所述第二金属阻挡层上；

所述半导体层和第一金属阻挡层位于所述刻蚀阻挡层上；

所述栅极绝缘层位于所述半导体层上；

15 所述栅极位于所述栅极绝缘层上。

14、根据权利要求 1 所述的薄膜晶体管，其中所述薄膜晶体管的结构为：

所述栅极位于所述基板上；

所述栅极绝缘层位于所述栅极上；

所述半导体层和第一金属阻挡层位于所述栅极绝缘层上；

20 所述源极和漏极位于所述第一金属阻挡层上；

或者所述薄膜晶体管的结构为：

所述源极和漏极位于所述基板上；

所述半导体层和第一金属阻挡层位于所述源极和漏极上；

所述栅极绝缘层位于所述半导体层和第一金属阻挡层上；

25 所述栅极位于所述栅极绝缘层上。

15、根据权利要求 9 所述的薄膜晶体管，其中所述薄膜晶体管的结构为：

所述栅极位于所述基板上；

所述栅极绝缘层位于所述栅极上；

所述半导体层和第一金属阻挡层位于所述栅极绝缘层上；

30 所述第二金属阻挡层位于所述半导体层和第一金属阻挡层上；

所述源极和漏极位于所述第一金属阻挡层上；

或者所述薄膜晶体管的结构为：

所述源极和漏极位于所述基板上；

所述第二金属阻挡层位于所述源极和漏极上；

所述半导体层和第一金属阻挡层位于所述第二金属阻挡层上；

5 所述栅极绝缘层位于所述半导体层和第一金属阻挡层上；

所述栅极位于所述栅极绝缘层上。

16、根据权利要求4所述的薄膜晶体管，其中所述第一金属阻挡层位于与所述源极和漏极相对应的位置。

17、根据权利要求9所述的薄膜晶体管，其中所述第二金属阻挡层位于10与所述源极和漏极相对应的位置。

18、一种阵列基板，包括权利要求1-8、14、16任一权项所述的薄膜晶体管。

19、根据权利要求18所述的阵列基板，其中所述阵列基板还包括：数据线和栅极线，所述数据线与所述薄膜晶体管的源极相连，所述栅极线与薄膜15晶体管的栅极相连；

所述第一金属阻挡层位于与所述源极、漏极及数据线相对应的位置；或者

所述第一金属阻挡层位于与所述源极、漏极及栅极线相对应的位置；或者

20 所述第一金属阻挡层位于与所述源极、漏极、栅极线和数据线相对应的位置。

20、一种阵列基板，包括权利要求9-13、15、17任一权项所述的薄膜晶体管。

21、根据权利要求20所述的阵列基板，其中所述阵列基板还包括：数据25线和栅极线，所述数据线与所述薄膜晶体管的源极相连，所述栅极线与薄膜晶体管的栅极相连；

所述第一金属阻挡层位于与所述源极、漏极及数据线相对应的位置，或者位于与所述源极、漏极及栅极线相对应的位置，或者位于与所述源极、漏极、栅极线和数据线相对应的位置；和/或

30 所述第二金属阻挡层位于与所述源极、漏极及数据线相对应的位置，或者位于与所述源极、漏极及栅极线相对应的位置，或者位于与所述源极、漏

极、栅极线和数据线相对应的位置。

22、一种显示装置，包括权利要求 18 或 19 所述的阵列基板。

23、一种显示装置，包括权利要求 20 或 21 所述的阵列基板。

24、一种薄膜晶体管的制作方法，包括：

5 形成包括栅极、源极、漏极和半导体层的图形；形成包括栅极绝缘层以及第一金属阻挡层的图形；

所述栅极绝缘层位于所述栅极和半导体层之间，所述第一金属阻挡层位于所述源极、漏极与栅极绝缘层之间，其中，所述第一金属阻挡层与所述半导体层同层设置。

10 25、根据权利要求 24 所述的方法，还包括形成刻蚀阻挡层的图形，所述刻蚀阻挡层位于所述半导体层与源极、漏极之间。

26、根据权利要求 25 所述的薄膜晶体管，其中所述第一金属阻挡层与所述半导体层绝缘设置。

15 27、根据权利要求 26 所述的方法，其中所述半导体层由金属氧化物半导体材料制作而成。

28、根据权利要求 24 或 27 所述的薄膜晶体管，还包括形成第二金属阻挡层的图形，所述第二金属阻挡层位于所述第一金属阻挡层与所述源极、漏极之间。

29、根据权利要求 24 所述的方法，其中所述形成包括栅极、源极、漏极、20 半导体层、栅极绝缘层、第一金属阻挡层的图形，为：

采用构图工艺在基板上形成包括栅极的图形；

采用构图工艺在形成有所述栅极图形的基板上形成包括栅极绝缘层的图形；

25 采用同一次构图工艺在形成有所述栅极绝缘层图形的基板上形成包括半导体层和第一金属阻挡层的图形；

采用同一次构图工艺在形成有半导体层和第一金属阻挡层的基板上形成包括源极、漏极的图形；

或者所述形成包括栅极、源极、漏极、半导体层、栅极绝缘层、第一金属阻挡层的图形，为：

30 采用同一次构图工艺在基板上形成包括源极、漏极的图形；

采用同一次构图工艺在形成有所述源极、漏极的基板上形成包括半导体层和第一金属阻挡层的图形；

采用构图工艺在形成有所述半导体层和第一金属阻挡层图形的基板上形成包括栅极绝缘层的图形；

5 采用构图工艺在形成有所述栅极绝缘层图形的基板上形成包括栅极的图形。

30、根据权利要求 28 所述的方法，其中所述形成包括栅极、源极、漏极、半导体层、栅极绝缘层、刻蚀阻挡层、第一金属阻挡层和第二金属阻挡层的图形，为：

10 采用构图工艺在基板上形成包括栅极的图形；

采用构图工艺在形成有所述栅极图形的基板上形成包括栅极绝缘层的图形；

采用同一次构图工艺在形成有所述栅极绝缘层图形的基板上形成包括半导体层和第一金属阻挡层的图形；

15 采用构图工艺在形成有半导体层和第一金属阻挡层图形的基板上形成包括刻蚀阻挡层的图形；

采用同一次构图工艺在形成有刻蚀阻挡层图形的基板上形成包括源极、漏极以及第二金属阻挡层的图形；

20 或者所述形成包括栅极、源极、漏极、半导体层、栅极绝缘层、刻蚀阻挡层、第一金属阻挡层和第二金属阻挡层的图形，为：

采用同一次构图工艺在基板上形成包括源极、漏极以及第二金属阻挡层的图形；

采用构图工艺在形成有所述源极、漏极和第二金属阻挡层图形的基板上形成包括刻蚀阻挡层的图形；

25 采用同一次构图工艺在形成有所述刻蚀阻挡层图形的基板上形成包括半导体层和第一金属阻挡层的图形；

采用构图工艺在形成有所述半导体层和第一金属阻挡层图形的基板上形成包括栅极绝缘层的图形；

30 采用构图工艺在形成有所述栅极绝缘层图形的基板上形成包括栅极的图形。

31、根据权利要求 28 所述的方法，其中所述形成包括栅极、源极、漏极、

半导体层、栅极绝缘层、第一金属阻挡层和第二金属阻挡层的图形，为：

采用构图工艺在基板上形成包括栅极的图形；

采用构图工艺在形成有所述栅极图形的基板上形成包括栅极绝缘层的图形；

5 采用构图工艺在形成有所述栅极绝缘层图形的基板上形成包括半导体层的图形；

采用构图工艺在形成有所述半导体层图形的基板上形成第一金属阻挡层的图形；

采用同一次构图工艺在形成有第一金属阻挡层图形的基板上形成包括源10 极、漏极以及第二金属阻挡层的图形；

或者所述形成包括栅极、源极、漏极、半导体层、栅极绝缘层、第一金属阻挡层和第二金属阻挡层的图形，为：

采用同一次构图工艺在基板上形成包括源极、漏极以及第二金属阻挡层的图形；

15 采用构图工艺在形成有所述源极、漏极以及第二金属阻挡层图形的基板上形成包括半导体层的图形；

采用构图工艺在形成有所述半导体层图形的基板上形成第一金属阻挡层的图形；

采用构图工艺在形成有所述第一金属阻挡层图形的基板上形成包括栅极20 绝缘层的图形；

采用构图工艺在形成有所述栅极绝缘层图形的基板上形成包括栅极的图形。

32、根据权利要求 30 或 31 所述的方法，其中所述形成源极和漏极的材料为铜或铜合金。

25 33、根据权利要求 32 所述的方法，其中所述采用同一次构图工艺在形成有刻蚀阻挡层图形的基板上形成包括源极、漏极以及第二金属阻挡层的图形为：

采用镀膜工艺在形成有所述刻蚀阻挡层图形或第一金属阻挡层图形的基板上形成所述铜金属或铜合金膜层；在形成所述铜金属或铜合金膜层的初始30 时间段内，向腔体内通入预设比例的氧气、氮气或氧气和氮气的混合气体形成铜或铜合金的氧化物、氮化物或氮氧化物用于形成第二金属阻挡层，除所

述第二金属阻挡层之外的铜金属或铜合金膜层用于形成源极和漏极；采用一次曝光、显影、光刻刻蚀步骤形成所述源极、漏极以及第二金属阻挡层的图形；

5 所述采用同一次构图工艺在形成有第一金属阻挡层图形的基板上形成包括源极、漏极以及第二金属阻挡层的图形为：

采用镀膜工艺在形成有所述刻蚀阻挡层图形或第一金属阻挡层图形的基板上形成所述铜金属或铜合金膜层；在形成所述铜金属或铜合金膜层的初始时间段内，向腔体内通入预设比例的氧气、氮气或氧气和氮气的混合气体形成铜或铜合金的氧化物、氮化物或氮氧化物用于形成第二金属阻挡层，除所述第二金属阻挡层之外的铜金属或铜合金膜层用于形成源极和漏极；采用一次曝光、显影、光刻刻蚀步骤形成所述源极、漏极以及第二金属阻挡层的图形。

34、根据权利要求32所述的方法，其中所述采用同一次构图工艺在基板上形成包括源极、漏极以及第二金属阻挡层的图形为：

15 采用镀膜工艺在基板上形成所述铜或铜合金膜层；在形成所述铜或铜合金膜层的结束时间段内，向腔体内通入预设比例的氧气、氮气或氧气和氮气的混合气体形成铜或铜合金的氧化物、氮化物或氮氧化物用于形成第二金属阻挡层，除所述第二金属阻挡层之外的铜金属或铜合金膜层用于形成源极和漏极；采用一次曝光、显影、光刻刻蚀步骤形成所述源极、漏极以及第二金属阻挡层的图形。

20 35、一种阻挡层，包括用于权利要求18或19任一权项所述的阵列基板中阻止铜或铜合金的扩散的第一金属阻挡层。

36、根据权利要求35所述的阻挡层，其中所述阻挡层的材质为金属氧化物、金属氮化物或金属氮氧化物。

25 37、根据权利要求35所述的阻挡层，其中所述金属氧化物为铟镓锗氧化物或氧化铜。

38、根据权利要求35所述的阻挡层，其中所述金属氮化物为铜金属氮化物。

39、根据权利要求35所述的阻挡层，其中所述金属氮氧化物为铜金属氮氧化物。

40、一种阻挡层，包括用于权利要求20或21任一权项所述的阵列基板

中阻止铜或铜合金的扩散的第一金属阻挡层和/或第二金属阻挡层。

41、根据权利要求40所述的阻挡层，其中所述阻挡层的材质为金属氧化物、金属氮化物或金属氮氧化物。

42、根据权利要求40所述的阻挡层，其中所述金属氧化物为铟镓锗氧化物或氧化铜。

43、根据权利要求40所述的阻挡层，其中所述金属氮化物为铜金属氮化物。

44、根据权利要求40所述的阻挡层，其中所述金属氮氧化物为铜金属氮氧化物。

图 1

图 2

图 3

图 4

图 5

图 6

图 7

图 8

图 9

图 10

图 11

图 12

## INTERNATIONAL SEARCH REPORT

International application No.

PCT/CN2013/086250

## A. CLASSIFICATION OF SUBJECT MATTER

See the extra sheet

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

IPC: H01L 29/-; H01L 21/-; H01L 27-; G09F 91-

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

CNTXT, DWPI, USTXT: thin film transistor, semiconductor layer, active layer, active area, barrier layer, peer, same degree, tft, thin, film, transistor, semiconductor, layer, active, channel, barrier, simultaneity, one, once, metal, copper, cuprum, drift, diffusion, moving

## C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category * | Citation of document, with indication, where appropriate, of the relevant passages                                                        | Relevant to claim No. |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| PX         | CN 102956715 A (BOE TECHNOLOGY GROUP CO., LTD.), 06 March 2013 (06.03.2013), the whole document                                           | 1-44                  |

| PX         | CN 202855742 U (BOE TECHNOLOGY GROUP CO., LTD.), 03 April 2013 (03.04.2013), the whole document                                           | 1-44                  |

| A          | TW 200928531 A (AU OPTRONICS CORP.), 01 July 2009 (01.07.2009), description, page 16, line 6 to page 22, line 2, and figures 2A and 5A-5E | 1-44                  |

| A          | JP 2003-086798 A (NEC CORP.), 20 March 2003 (20.03.2003), the whole document                                                              | 1-44                  |

| A          | CN 102683593 A (BOE TECHNOLOGY GROUP CO., LTD.), 19 September 2012 (19.09.2012), the whole document                                       | 1-44                  |

II Further documents are listed in the continuation of Box C.

See patent family annex.

|                                                                                                                                                                         |                                                                                                                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| * Special categories of cited documents:                                                                                                                                | "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention                                              |

| "A" document defining the general state of the art which is not considered to be of particular relevance                                                                | "X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone                                                                     |

| "E" earlier application or patent but published on or after the international filing date                                                                               | "Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art |

| "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified) | "&" document member of the same patent family                                                                                                                                                                                                    |

| "O" document referring to an oral disclosure, use, exhibition or other means                                                                                            |                                                                                                                                                                                                                                                  |

| "P" document published prior to the international filing date but later than the priority date claimed                                                                  |                                                                                                                                                                                                                                                  |

Date of the actual completion of the international search

26 January 2014 (26.01.2014)Date of mailing of the international search report

20 February 2014 (20.02.2014)Name and mailing address of the ISA/CN:

State Intellectual Property Office of the P.R.China

No. 6, Xitucheng Road, Jimenqiao

Haidian District, Beijing 100088, China

Facsimile No.: (86-10) 62019451Authorized officer

WANG, Yibing

Telephone No.: (86-10) 62411584

INTERNATIONAL SEARCH REPORT

Information on patent family members

International application No.

PCT/CN2013/086250

| Patent Documents referred in the Report | Publication Date | Patent Family                                                           | Publication Date                                     |

|-----------------------------------------|------------------|-------------------------------------------------------------------------|------------------------------------------------------|

| CN 102956715 A                          | 06.03.2013       | None                                                                    |                                                      |

| CN 202855742 U                          | 03.04.2013       | None                                                                    |                                                      |

| TW 200928531 A                          | 01.07.2009       | TWI 360708 B<br>US 2009153056 A I<br>US 8212256 B2<br>US 2012261755 A I | 21.03.2012<br>18.06.2009<br>03.07.2012<br>18.10.2012 |

| JP 2003-086798 A                        | 20.03.2003       | US 2003049919 A I                                                       | 13.03.2003                                           |

|                                         |                  | US 6710407 B2                                                           | 23.03.2004                                           |

| CN 102683593 A                          | 19.09.2012       | W O 2013143280 A I                                                      | 03.10.2013                                           |

## INTERNATIONAL

## SEARCH REPORT

International application No.

PCT/CN2013/086250

CONTINUATION: CLASSIFICATION OF SUBJECT MATTER

HOIL 29/786 (2006.01) i

HOIL 29/06 (2006.01) i

H01L 21/336 (2006.01) i

H01L 27/12 (2006.01) i

H01L 21/28 (2006.01) i

G09F 9/33 (2006.01) i

G09F 9/35 (2006.01) i

## A. 主题的分类

参见附加页

按照国际专利分类(IPC)或者同时按照国家分类和IPC两种分类

## B. 检索领域

检索的最低限度文献(标明分类系统和分类号)

IPC:H01L 29/-;H01L 21/-;H01L 27;-G09F 91-

包含在检索领域中的除最低限度文献以外的检索文献

在国际检索时查阅的电子数据库(数据库的名称,和使用的检索词(如使用))

CNTXT, DWPI, USTXT: 薄膜晶体管, 半导体层, 有源层, 沟道, 有源区, 阻挡层, 一次, 同时, 同层, 同次, 金属, 铜, 扩散, tft, thin, film, transistor, semiconductor, layer, active, channel, barrier, simultaneity, one, once, metal, copper, cuprum, drift, diffusion, moving

## C. 相关文件

| 类型* | 引用文件, 必要时, 指明相关段落                                                                | 相关的权利要求 |

|-----|----------------------------------------------------------------------------------|---------|

| PX  | CN102956715 A (京东方科技股份有限公司)06.3月2013 (06.03.2013)<br>全文                          | 1-44    |

| PX  | CN202855742 U (京东方科技股份有限公司)03.4月2013 (03.04.2013)<br>全文                          | 1-44    |

| A   | TW20092853 1A (友达光电股份有限公司)01.7月2009 (01.07.2009) 说明书第16页第6行至第22页第2行, 附图2A, 5A-5E | 1-44    |

| A   | JP特开2003-086798 A (日本电气株式会社)20.3月2003 (20.03.2003)<br>全文                         | 1-44    |

| A   | CN102683593 A (京东方科技股份有限公司)19.9月2012 (19.09.2012)<br>全文                          | 1-44    |

其余文件在C栏的续页中列出。 见同族专利附件。

## \* 引用文件的具体类型:

"A" 认为不特别相关的表示了现有技术一般状态的文件

"E" 在国际申请日的当天或之后公布的在先申请J3/4/4

"L" 可能对优先权要求构成怀疑的文件, 或为确定另一篇引用文件的公布日而引用的或者因其他特殊理由而引用的文件(如具体说明的)

"O" 涉及口头公开、使用、展览或其他方式公开的文件

"P" 公布日先于国际申请日但迟于所要求的优先权日的文件

"T" 在申请日或优先权日之后公布, 与申请不相抵触, 但为了理解发明之理论或原理的在后文件

"X" 特别相关的文件, 单独考虑该文件, 认定要求保护的发明不是新颖的或不具有创造性

"Y" 特别相关的文件, 当该文件与另一篇或者多篇该类文件结合并且这种结合对于本领域技术人员为显而易见时, 要求保护的发明不具有创造性

"&amp;" 同族专利的文件

## 国际检索实际完成的日期

26.1月2014 (26.01.2014)

## 国际检索报告邮寄日期

20.2月2014 (20.02.2014)

## ISA/CN的名称和邮寄地址:

中华人民共和国国家知识产权局

中国北京市海淀区蓟门桥西土城路6号100088

传真号: (86-10)62019451

## 受权官员

王毅冰

电话号码: (86-10) 62411584

国际检索报告

关于同族专利的信息

国际申请号

PCT/CN2013/086250

| 检索报告中引用的专利文件        | 公布日期       | 同族专利                                                                | 公布日期                                                 |

|---------------------|------------|---------------------------------------------------------------------|------------------------------------------------------|

| CN102956715 A       | 06.03.2013 | 无                                                                   |                                                      |

| CN202855742 U       | 03.04.2013 | 无                                                                   |                                                      |

| TW200928531 A       | 01.07.2009 | TWI360708 B<br>US2009153056 A 1<br>US8212256 B2<br>US2012261755 A 1 | 21.03.2012<br>18.06.2009<br>03.07.2012<br>18.10.2012 |

| JP 特开 2003-086798 A | 20.03.2003 | US2003049919 A 1<br>US67 10407 B2                                   | 13.03.2003<br>23.03.2004                             |

| CN102683593 A       | 19.09.2012 | WO2013 143280 A 1                                                   | 03.10.2013                                           |

续: 主题的分类

GO9F 9/36 (2006.01) †

609J 9111 (2006.01) †

HO1L 21/28 (2006.01) †

HO1L 771Z (2006.01) †

HO1L 21336 (2006.01) †

HO1L 29/06 (2006.01) †

HO1L 29/786 (2006.01) †