(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2006-525750

(P2006-525750A)

(43) 公表日 平成18年11月9日(2006.11.9)

| (51) Int.C1.                 | F 1       | テーマコード (参考) |         |  |

|------------------------------|-----------|-------------|---------|--|

| <b>H03K 5/1252 (2006.01)</b> | H03K 5/01 | G           | 5 J 001 |  |

| <b>H03K 5/06 (2006.01)</b>   | H03K 5/06 |             | 5 J 039 |  |

| <b>G06F 1/04 (2006.01)</b>   | G06F 1/04 | A           |         |  |

審査請求 未請求 予備審査請求 未請求 (全 8 頁)

|               |                              |          |                                                           |

|---------------|------------------------------|----------|-----------------------------------------------------------|

| (21) 出願番号     | 特願2006-509997 (P2006-509997) | (71) 出願人 | 590000846<br>イーストマン コダック カンパニー                            |

| (86) (22) 出願日 | 平成16年4月14日 (2004.4.14)       |          | アメリカ合衆国、ニューヨーク14650<br>ロチェスター、ステイトストリート3<br>43            |

| (85) 翻訳文提出日   | 平成17年10月26日 (2005.10.26)     | (74) 代理人 | 100075258<br>弁理士 吉田 研二                                    |

| (86) 國際出願番号   | PCT/US2004/011415            | (74) 代理人 | 100096976<br>弁理士 石田 純                                     |

| (87) 國際公開番号   | W02004/100373                | (72) 発明者 | ローラー エドワード ポール<br>アメリカ合衆国 ニューヨーク フィアポート ヒーサウッド ロード 61     |

| (87) 國際公開日    | 平成16年11月18日 (2004.11.18)     | (72) 発明者 | チャーネスキー デービッド マイケル<br>アメリカ合衆国 ニューヨーク ヒルトン<br>マジョリー レーン 12 |

| (31) 優先権主張番号  | 10/426,263                   |          |                                                           |

| (32) 優先日      | 平成15年4月30日 (2003.4.30)       |          |                                                           |

| (33) 優先権主張国   | 米国(US)                       |          | 最終頁に続く                                                    |

(54) 【発明の名称】波形グリッチ防止方法

## (57) 【要約】

本発明におけるシステム開発目的は、発止させるパルス列の位相をグリッチやスプリアスパルスやデューティサイクルのスプリアス的変化なしで任意に変化させられるようになることがある。この目的を達成すべく、本ゲート済周期波形発生システムにおいては、可調位相周期波形を発生させる発生器と、この周期波形の位相に基づき遅延イネーブル信号を提供するデバイスと、遅延イネーブル信号及び可調位相周期波形に基づきゲート済周期波形を発生させる論理素子と、を設け、遅延イネーブル信号によりゲート済周期波形をその不要変化なしで発止可能としている。

**【特許請求の範囲】****【請求項 1】**

( a ) 可調位相周期波形を発生させる発生器と、

( b ) この周期波形の位相に基づき遅延イネーブル信号を提供するデバイスと、

( c ) 遅延イネーブル信号及び可調位相周期波形に基づきゲート済周期波形を発生させる論理素子と、

を備え、遅延イネーブル信号によりゲート済周期波形をその不要変化なしで発止可能としたゲート済周期波形発生システム。

**【請求項 2】**

請求項 1 記載のシステムにおいて、上記発生器が可調位相周期波形について複数通りの位相を発生させ、上記遅延イネーブル信号提供デバイスが上記発生器から位相情報を受け取り受け取った位相情報に基づき遅延イネーブル信号を発生させるシステム。 10

**【請求項 3】**

請求項 1 記載のシステムにおいて、更に、複数通りの波形のうち何れかを選択するセレクタを備えるシステム。

**【請求項 4】**

請求項 3 記載のシステムにおいて、上記セレクタがマルチプレクサであるシステム。

**【請求項 5】**

請求項 1 記載のシステムにおいて、上記遅延イネーブル信号提供デバイスが複数個のイネーブリング論理素子を有し、これらイネーブリング論理素子によって複数通りの遅延経路のうち何れかをイネーブルにするシステム。 20

**【請求項 6】**

請求項 5 記載のシステムにおいて、本来のイネーブル信号を基準としてその位相が定められている複数通りのクロック用に上記複数通りの遅延経路を用いるシステム。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は電子的画像形成システムに関し、特に、グリッチやスプリアスパルスを発生させることなく厳正なシステムクロックを発止させる技術に関する。 30

**【背景技術】****【0002】**

一連の論理レベルパルスを発生させるには、普通、連続的パルス列と正論理イネーブル信号との論理 AND 演算を行えばよい。ターンオン時やターンオフ時におけるパルス短縮やグリッチの発生を防止するには、ローレベルからハイレベルへまたハイレベルからローレベルへのイネーブル信号の遷移を、パルス列がローレベルであるときに行わせるべきである。

**【0003】**

ここに、連続的パルス列の位相が変化したならそれに応じてイネーブル信号の位相を変化させねばならないが、イネーブル信号を発生させる論理回路は、通常は、固定位相非可調システムクロックに従い動作している。そのため、パルス短縮やグリッチが発生しないようイネーブル信号の位相を変化させる機構が、必要とされている。 40

**【発明の開示】****【0004】**

本発明はイネーブル信号の位相を変化させる機構を指向している。簡潔にまとめると、本発明の一実施形態に係るゲート済周期波形発生システムにおいては、( a ) 可調位相周期波形を発生させる発生器と、( b ) この周期波形の位相に基づき遅延イネーブル信号を提供するデバイスと、( c ) 遅延イネーブル信号及び可調位相周期波形に基づきゲート済周期波形を発生させる論理素子と、を設け、遅延イネーブル信号によりゲート済周期波形をその不要変化なしで発止可能としている。

**【0005】**

10

20

30

40

50

なお、好適な実施形態に関する以下の詳細な説明及び別紙特許請求の範囲の記載を検討しました別紙図面を参照することによって、ここに述べたものも述べていないものも含め、本発明の実施形態、目的、構成要素及び利点をより明瞭に理解認識できよう。

#### 【発明を実施するための最良の形態】

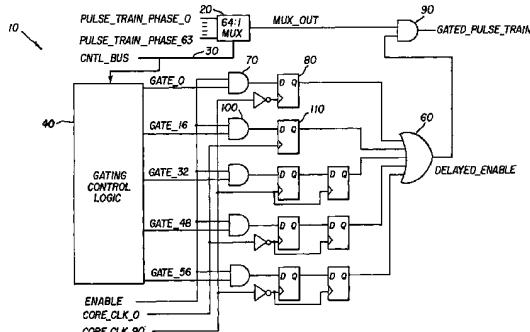

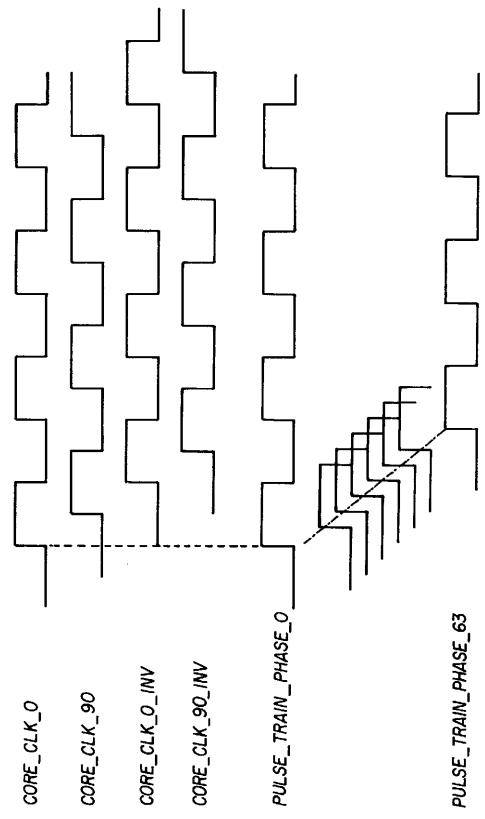

##### 【0006】

図1に、それぞれ90°ずつその位相が異なり図2に示すイネーブル遅延用論理回路10に入力される4通りのコアクロックと、64通りの自走クロック位相PULSE\_TRAIN\_AIN\_PHASE\_0～PULSE\_TRAIN\_PHASE\_63とを示す。PULSE\_TRAIN\_PHASE\_0はCORE\_CLK\_0と同相である。一連の位相PULSE\_TRAIN\_PHASE\_0～PULSE\_TRAIN\_PHASE\_63は、それぞれその前の位相に対して、クロック1/64周期分ずれている。これらの位相は図2に示すマルチプレクサ20に入力される。10

##### 【0007】

図2に、外部で発生させたENABLE信号を遅延させGATED\_PULSE\_TRAIN信号を提供する遅延用論理回路10を示す。コントロールバス30からの信号は、どの位相のパルス列を通過させるかを選択するためマルチプレクサ20にて使用されており、また、GATE\_0、GATE\_16、GATE\_32、GATE\_48、GATE\_56それに係る遅延経路のうち1個をイネーブルにするためゲート制御用論理回路40にて使用されている。注記すべきことに、イネーブルになるのはこれらの経路のうち1個だけで残りの経路はディスエーブルとなり、ディスエーブルにされた経路からORゲート60への論理出力値は0になる。また、信号GATE\_0に係る遅延経路に設けられているANDゲート70によって許可されるとシステムイネーブル信号はこれを通り抜けフリップフロップ80に達する。フリップフロップ80にてクロックとして用いられているのはCORE\_CLK\_90の立ち下がりエッジであるから、この遅延経路ではシステムイネーブル信号がクロック3/4周期分だけ遅延されることになる。フリップフロップ80の出力はORゲート60更にはANDゲート90に供給され、選択した位相に係るパルス列に対するイネーブル/ディスエーブル制御に用いられる。20

##### 【0008】

信号GATE\_16に係る遅延経路に設けられているANDゲート100によって許可されるとシステムイネーブル信号はこれを通り抜けフリップフロップ110に達する。フリップフロップ110にてクロックとして用いられているのはCORE\_CLK\_0の立ち上がりエッジであるから、この遅延経路ではシステムイネーブル信号がクロック1周期分まるまる遅延され、選択した位相に係るパルス列に対しANDゲート90が実行するイネーブル/ディスエーブル制御がこれに応じて遅延される。GATE\_32、GATE\_48、GATE\_56それに係る遅延経路について以上と同様の分析を行うと、ANDゲート90によるイネーブル/ディスエーブル制御の遅延時間が順にクロック周期の1.25倍、1.5倍、1.75倍となることがわかる。これらの遅延経路に係るフリップフロップもフリップフロップ80、110と実質同様の遅延発生機能を有しているのであるが、ここでは仔細部分に立ち入らないことを了承されたい。注記すべきことに、これらの経路それぞれに2個のフリップフロップが設けられているのは遅延時間を増やすためである。この点については本件技術分野における習熟者（いわゆる当業者）であれば即座に理解されるであろう。3040

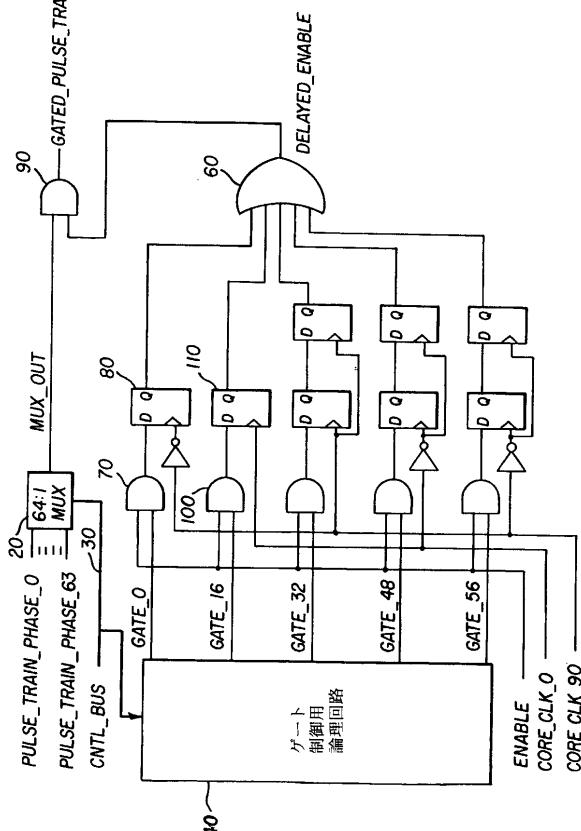

##### 【0009】

図3に、外部で発生したENABLE信号を遅延させGATED\_PULSE\_TRAIN信号を提供する別の遅延用論理回路120を示す。この図に示した論理回路は図2に示したものと類似した構成を有しているが、その遅延経路には相違点がある。即ち、GATE\_0、GATE\_16、GATE\_32、GATE\_48、GATE\_56に係る信号経路における遅延時間が、順にクロック周期の1.25倍、1.5倍、1.75倍、2倍、2.25倍になっている。明瞭化のため、論理回路コンポーネント20、30、60及び90としては図3でも図2と同様のコンポーネントを用いている。他の部品について50

も、当業者であれば、図示されているフリップフロップを用いこの新たな遅延時間がどのように実現されているかを即座に認識できるであろうから、ここでは詳細には説明しないこととする。

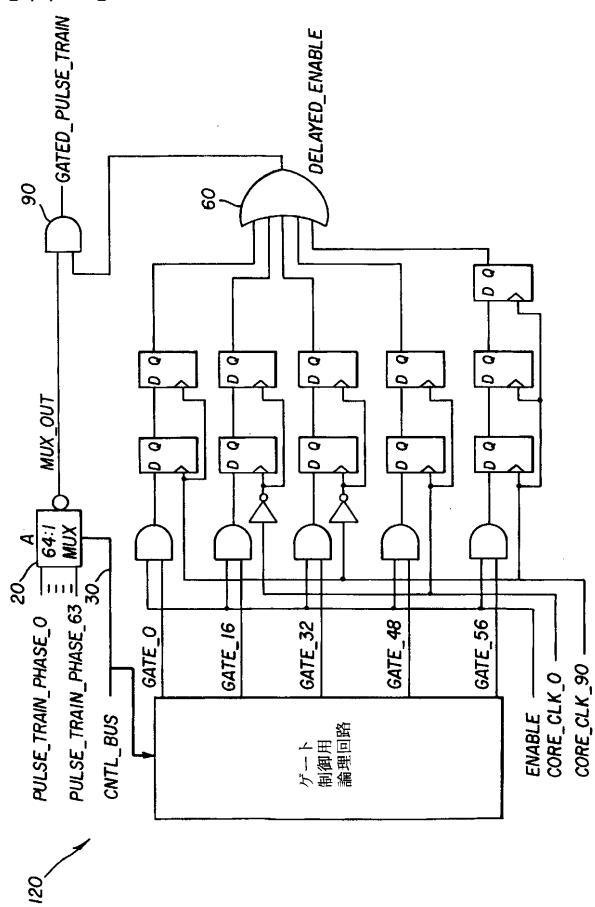

【0010】

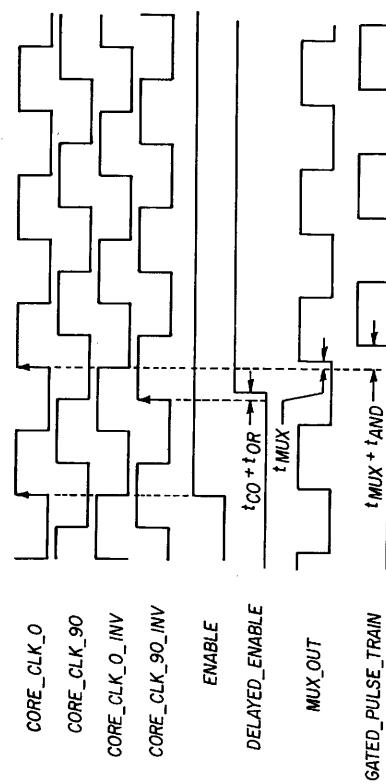

図4に図2におけるタイミングを示す。この例では、ENABLE信号を外部発生させる論理回路(図示せず)にてCORE\_CLK\_0をクロックとして用いており、また、ゲート制御用論理回路40がGATE\_0に係る信号経路を選択するようCNTL\_BUSの値を定めてある。この場合に発生するDELAYED\_ENABLE信号はCORE\_CLK\_0に対しクロック3/4周期分遅延した信号となる。そのため、DELAYED\_ENABLEに応じたANDゲート90出力値遷移が発生するのは信号MUX\_OUTがローであるときであるから、信号GATED\_PULSE\_TRAINを発止させる際のパルス短縮やグリッチの発生を事々に妨ぐことができる。10

【0011】

以上、ある特定の好適な実施形態を参照しつつ本発明について詳細に説明したが、本発明の技術的範囲及びその神髄から逸脱することなく変形や変更を施すことが可能であることを、理解されたい。

【図面の簡単な説明】

【0012】

【図1】本発明にて使用される各種クロック及び位相を示すタイミングチャートである。

【図2】本発明にてゲート済パルス列の発生に使用される論理回路を示す論理回路図である。20

【図3】図2に示したものに代わる実施形態を示す図である。

【図4】図2に示した論理回路におけるタイミングチャートである。

【符号の説明】

【0013】

10, 120 イネーブル遅延用論理回路、20 マルチプレクサ、30 コントロールバス、40 ゲート制御用論理回路、60 ORゲート、70, 90, 100 ANDゲート、80, 110 フリップフロップ。

【図1】

FIG. 1

【図2】

【図4】

FIG. 4

## 【国際調査報告】

## INTERNATIONAL SEARCH REPORT

International Application No

PCT/US2004/011415

A. CLASSIFICATION OF SUBJECT MATTER

IPC 7 H03K7/04

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

IPC 7 H03K

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

EPO-Internal, WPI Data, PAJ

## C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category * | Citation of document, with indication, where appropriate, of the relevant passages           | Relevant to claim No. |

|------------|----------------------------------------------------------------------------------------------|-----------------------|

| X          | EP 1 077 529 A (TEKTRONIX INC)<br>21 February 2001 (2001-02-21)<br>figures 12,14-16<br>----- | 1-4,6                 |

Further documents are listed in the continuation of box C.

Patent family members are listed in annex.

## \* Special categories of cited documents:

- \*A\* document defining the general state of the art which is not considered to be of particular relevance

- \*E\* earlier document but published on or after the International filing date

- \*L\* document which may throw doubts on priority, claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- \*O\* document referring to an oral disclosure, use, exhibition or other means

- \*P\* document published prior to the international filing date but later than the priority date claimed

- \*T\* later document published after the International filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

- \*X\* document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

- \*Y\* document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.

- \*Z\* document member of the same patent family

|                                                                                                                                                                                        |                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| Date of the actual completion of the international search<br><br>27 September 2004                                                                                                     | Date of mailing of the international search report<br><br>04/10/2004 |

| Name and mailing address of the ISA<br>European Patent Office, P.B. 5818 Patentlaan 2<br>NL - 2280 HV Rijswijk<br>Tel. (+31-70) 340-2040, Tx. 31 651 epo nl.<br>Fax: (+31-70) 340-3016 | Authorized officer<br><br>Brown, J                                   |

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

International Application No

PCT/US2004/011415

| Patent document cited in search report | Publication date | Patent family member(s) | Publication date |

|----------------------------------------|------------------|-------------------------|------------------|

| EP 1077529                             | A 21-02-2001     | US 5481230 A            | 02-01-1996       |

|                                        |                  | EP 1077529 A1           | 21-02-2001       |

|                                        |                  | DE 69522779 D1          | 25-10-2001       |

|                                        |                  | DE 69522779 T2          | 04-07-2002       |

|                                        |                  | DE 69526383 D1          | 16-05-2002       |

|                                        |                  | DE 69526383 T2          | 12-12-2002       |

|                                        |                  | EP 0712211 A2           | 15-05-1996       |

---

## フロントページの続き

(81)指定国 AP(BW,GH,GM,KE,LS,MW,MZ,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HU,IE,IT,LU,MC,NL,PL,PT,RO,SE,SI,SK,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AT,AU,AZ,BA,BB,BG,BR,BW,BY,BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,HR,HU,ID,IL,IN,IS,JP,KE,KG,KP,KR,KZ,LC,LK,LR,LS,LT,LU,LV,MA,M,D,MG,MK,MN,MW,MX,MZ,NA,NI,NO,NZ,OM,PG,PH,PL,PT,RO,RU,SC,SD,SE,SG,SK,SL,SY,TJ,TM,TN,TR,TT,TZ,UA,UG,US,UZ,VC,VN,YU,ZA,ZM,ZW

F ターム(参考) 5J001 BB00 BB05 BB08 BB09 BB12 BB19 DD09

5J039 BB04 EE25 KK09 KK10 KK13 KK22 KK29