(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2018-61058

(P2018-61058A)

(43) 公開日 平成30年4月12日(2018.4.12)

| (51) Int.Cl.           | F 1    | HO 1 G | 4/30    | 301 E | 5 E 001 | テーマコード (参考) |

|------------------------|--------|--------|---------|-------|---------|-------------|

| HO 1 G 4/12 (2006.01)  | HO 1 G | 4/12   | 3 4 9   |       | 5 E 082 |             |

| HO 1 G 2/06 (2006.01)  | HO 1 G | 1/035  |         | C     |         |             |

| HO 1 G 2/24 (2006.01)  | HO 1 G | 1/04   |         |       |         |             |

| HO 1 G 13/00 (2013.01) | HO 1 G | 13/00  | 3 2 1 B |       |         |             |

審査請求 有 請求項の数 31 O L (全 24 頁) 最終頁に続く

|              |                                     |          |                                                                                                |

|--------------|-------------------------------------|----------|------------------------------------------------------------------------------------------------|

| (21) 出願番号    | 特願2017-237547 (P2017-237547)        | (71) 出願人 | 594023722<br>サムソン エレクトローメカニックス カンパニーリミテッド<br>大韓民国、キョンギード、スウォンーシ、ヨントンギ、(マエタンードン) マエヨンニード<br>150 |

| (22) 出願日     | 平成29年12月12日 (2017.12.12)            | (74) 代理人 | 100088605<br>弁理士 加藤 公延                                                                         |

| (62) 分割の表示   | 特願2012-274325 (P2012-274325)<br>の分割 | (72) 発明者 | イ・スン・チョル<br>大韓民国、キョンギード、スウォン、ヨントンギ、マエタン3ードン 314、サムソン エレクトローメカニックス カンパニーリミテッド                   |

| 原出願日         | 平成24年12月17日 (2012.12.17)            |          |                                                                                                |

| (31) 優先権主張番号 | 10-2012-0108328                     |          |                                                                                                |

| (32) 優先日     | 平成24年9月27日 (2012.9.27)              |          |                                                                                                |

| (33) 優先権主張国  | 韓国 (KR)                             |          |                                                                                                |

最終頁に続く

(54) 【発明の名称】積層チップ電子部品、その実装基板及び包装体

## (57) 【要約】

【課題】積層チップ電子部品、その実装基板及び包装体に関する。

【解決手段】本発明の電子部品は、内部電極及び誘電体層を含むセラミック本体と、前記セラミック本体の長さ方向の両端部を覆うように形成される外部電極と、前記誘電体層を挟んで前記内部電極が対向して配置され、容量が形成される活性層と、前記活性層の厚さ方向の上部または下部に形成され、厚さ方向の下部が厚さ方向の上部より大きい厚さを有する上部及び下部カバー層と、を含み、前記下部カバー層は前記上部カバー層と区別される色を有する識別層を含み、前記識別層の厚さは 30  $\mu$ m 以上前記下部カバー層の厚さ以下であり、前記下部カバー層は印刷回路基板の上面と隣接する。

【選択図】図 6

## 【特許請求の範囲】

## 【請求項 1】

内部電極及び誘電体層を含むセラミック本体と、

前記セラミック本体の長さ方向の両端部を覆うように形成される外部電極と、

前記誘電体層を挟んで前記内部電極が対向して配置され、容量が形成される活性層と、

前記活性層の厚さ方向の上部または下部に形成され、厚さ方向の下部が厚さ方向の上部より大きい厚さを有する上部及び下部カバー層と、を含み、

前記下部カバー層は前記上部カバー層と区別される色を有する識別層を含み、前記識別層の厚さは  $30 \mu m$  以上前記下部カバー層の厚さ以下であり、前記下部カバー層は印刷回路基板の上面と隣接する、積層セラミックキャパシタ。

10

## 【請求項 2】

前記上部カバー層の厚さ D と下部カバー層の厚さ B との比率  $D / B$  は  $0.021 \sim 0.422$  の範囲を満たす、請求項 1 に記載の積層セラミックキャパシタ。

10

## 【請求項 3】

前記セラミック本体の厚さの  $1/2$  である A に対する前記下部カバー層の厚さ B の比率  $B / A$  は  $0.329 \sim 1.522$  の範囲を満たす、請求項 1 に記載の積層セラミックキャパシタ。

10

## 【請求項 4】

前記下部カバー層の厚さ B に対する前記活性層の厚さの  $1/2$  である C の比率  $C / B$  は  $0.146 \sim 2.458$  の範囲を満たす、請求項 1 に記載の積層セラミックキャパシタ。

20

## 【請求項 5】

前記識別層は白色である、請求項 1 に記載の積層セラミックキャパシタ。

10

## 【請求項 6】

前記識別層の色は前記上部カバー層の色より明るい、請求項 1 に記載の積層セラミックキャパシタ。

10

## 【請求項 7】

前記識別層は主成分として  $ABO_3$  で表される化合物を含み、A は Ba または Ba と Ca 、 Zr 及び Sr のうち少なくとも一つを含み、B は Ti または Ti と Zr 及び Hf のうち少なくとも一つを含み、

30

前記主成分 100 モルに対し、 $0.1 \sim 30$  モルの Si 及び Al を副成分として含む、請求項 1 に記載の積層セラミックキャパシタ。

30

## 【請求項 8】

前記主成分 100 モルに対し、 $1.0 \sim 1.5$  モルの Si 及び  $0.2 \sim 0.8$  モルの Al を副成分として含む、請求項 7 に記載の積層セラミックキャパシタ。

30

## 【請求項 9】

前記主成分 100 モルに対し、 $0 \sim 2$  モルの Mg 及び  $0 \sim 0.09$  モルの Mn を含む、請求項 7 に記載の積層セラミックキャパシタ。

30

## 【請求項 10】

前記主成分 100 モルに対し、Mg 及び Mn の含量はそれぞれ  $0.001$  モル未満である、請求項 7 に記載の積層セラミックキャパシタ。

40

## 【請求項 11】

前記識別層は前記主成分 100 モルに対し、1 モル以下の Ca 及び Zr から選択された一つの添加剤を含む、請求項 7 に記載の積層セラミックキャパシタ。

40

## 【請求項 12】

請求項 1 に記載の積層セラミックキャパシタと、

前記外部電極と半田によって連結される電極パッドと、

前記電極パッドが形成されており、前記内部電極が水平となるように、また前記下部カバー層が前記上部カバー層より厚さ方向下側に配置されるように、前記積層セラミックキャパシタが前記電極パッドに実装される印刷回路基板と、を含む、積層セラミックキャパシ

50

タの実装基板。

【請求項 1 3】

電圧が印加されて前記活性層の中心部で発生する変形率と前記下部カバー層で発生する変形率との差により、前記セラミック本体の長さ方向の両端部に形成される変曲点が前記半田の高さ以下に形成される、請求項 1 2 に記載の積層セラミックキャパシタ品の実装基板。

【請求項 1 4】

請求項 1 に記載の積層セラミックキャパシタと、

前記積層セラミックキャパシタが収納される収納部が形成された包装シートと、を含み、前記収納部内に収納される前記積層セラミックキャパシタの前記内部電極の全ては、前記収納部の底面と水平に配置され、

前記収納部内に収納される前記積層セラミックキャパシタの前記下部カバー層の全ては、収納部の底面に向かう、積層セラミックキャパシタの包装体。

【請求項 1 5】

前記積層セラミックキャパシタが収納された包装シートはリール状に巻線されて形成される、請求項 1 4 に記載の積層セラミックキャパシタの包装体。

【請求項 1 6】

六面体形状のセラミック本体の長さ方向の両端部に形成される外部電極と、

前記セラミック本体内に形成され、容量を形成するように誘電体層を挟んで対向して配置される多数の内部電極からなる活性層と、

前記活性層の最上側の内部電極の上部に形成される上部カバー層と、

前記活性層の最下側の内部電極の下部に形成され、前記上部カバー層の厚さより大きい厚さを有する下部カバー層と、を含み、

前記下部カバー層は前記上部カバー層と区別される色を有する識別層を含み、前記識別層の厚さは  $30 \mu m$  以上前記下部カバー層の厚さ以下であり、前記下部カバー層は印刷回路基板の上面と隣接する、積層セラミックキャパシタ。

【請求項 1 7】

電圧が印加されて前記活性層の中心部で発生する変形率と前記下部カバー層で発生する変形率との差により、前記セラミック本体の厚さ方向の中心部より下側の前記セラミック本体の長さ方向の両端部に変曲点が形成される、請求項 1 6 に記載の積層セラミックキャパシタ。

【請求項 1 8】

前記上部カバー層の厚さを D と規定したときに、前記上部カバー層の厚さ D と下部カバー層の厚さ B との比率  $D / B$  は  $0.021 \leq D / B \leq 0.422$  の範囲を満たす、請求項 1 6 に記載の積層セラミックキャパシタ。

【請求項 1 9】

前記セラミック本体の厚さの  $1/2$  である A に対する前記下部カバー層の厚さ B の比率  $B / A$  は  $0.329 \leq B / A \leq 1.522$  の範囲を満たす、請求項 1 6 に記載の積層セラミックキャパシタ。

【請求項 2 0】

前記下部カバー層の厚さ B に対する前記活性層の  $1/2$  である C の比率  $C / B$  は  $0.146 \leq C / B \leq 2.458$  の範囲を満たす、請求項 1 6 に記載の積層セラミックキャパシタ。

【請求項 2 1】

前記識別層は白色である、請求項 1 6 に記載の積層セラミックキャパシタ。

【請求項 2 2】

前記識別層の色は前記上部カバー層の色より明るい、請求項 1 6 に記載の積層セラミックキャパシタ。

【請求項 2 3】

前記識別層は主成分として  $ABO_3$  で表される化合物を含み、A は Ba または Ca

10

20

30

40

50

、 $Z_r$  及び  $S_r$  のうち少なくとも一つを含み、 $B$  は  $T_i$  または  $T_i$  と  $Z_r$  及び  $H_f$  のうち少なくとも一つを含み、

前記主成分 100 モルに対し、0.1～30 モルの  $S_i$  及び  $A_1$  を副成分として含む請求項 16 に記載の積層セラミックキャパシタ。

【請求項 24】

前記主成分 100 モルに対し、1.0～1.5 モルの  $S_i$  及び 0.2～0.8 モルの  $A_1$  を副成分として含む、請求項 23 に記載の積層セラミックキャパシタ。

【請求項 25】

前記主成分 100 モルに対し、0～2 モルの  $Mg$  及び 0～0.09 モルの  $Mn$  を含む、請求項 23 に記載の積層セラミックキャパシタ。

10

【請求項 26】

前記主成分 100 モルに対し、 $Mg$  及び  $Mn$  の含量はそれぞれ 0.001 モル未満である、請求項 23 に記載の積層セラミックキャパシタ。

【請求項 27】

前記識別層は前記主成分 100 モルに対し、1 モル以下の  $Ca$  及び  $Zr$  から選択された少なくとも一つ及び 0.2 モル以下の  $K$ 、 $B$  及び  $Li$  から選択された少なくとも一つの添加剤を含む、請求項 23 に記載の積層セラミックキャパシタ。

【請求項 28】

請求項 16 に記載の積層セラミックキャパシタと、

前記外部電極と半田によって連結される電極パッドと、

20

前記電極パッドが形成されており、前記内部電極が水平となるように、また前記下部カバー層が前記上部カバー層より厚さ方向下側に配置されるように、前記積層電子部品が前記電極パッドに実装される印刷回路基板と、を含む、積層セラミックキャパシタの実装基板。

【請求項 29】

電圧が印加されて前記活性層の中心部で発生する変形率と前記下部カバー層で発生する変形率との差により、前記セラミック本体の長さ方向の両端部に形成される変曲点が前記半田の高さ以下に形成される、請求項 28 に記載の積層セラミックキャパシタの実装基板。

【請求項 30】

請求項 16 に記載の積層セラミックキャパシタと、

30

前記積層セラミックキャパシタが収納される収納部が形成された包装シートと、を含み、前記収納部内に収納される前記積層セラミックキャパシタの前記内部電極の全ては、前記収納部の底面と水平に配置され、

前記収納部内に収納される前記積層セラミックキャパシタの前記下部カバー層の全ては、収納部の底面に向かう、積層セラミックキャパシタの包装体。

【請求項 31】

前記積層セラミックキャパシタが収納された包装シートはリール状に巻線されて形成される請求項 30 に記載の積層セラミックキャパシタの包装体。

【発明の詳細な説明】

【技術分野】

40

【0001】

本発明は、電圧が印加される際に積層チップ電子部品によって発生するアコースティックノイズを低減することができる積層チップ電子部品、その実装基板及び包装体に関する。

【背景技術】

【0002】

積層チップ電子部品の一つである積層キャパシタは、多数の誘電体層の間に内部電極が形成される。

【0003】

誘電体層を挟んで重なる内部電極が形成された積層キャパシタに直流電圧及び交流電圧を印加する場合、内部電極の間で圧電現象が起こり、振動が発生する。

50

## 【0004】

上記振動は、誘電体層の誘電率が高いほど、同一の静電容量を基準としてチップの形状が相対的に大きい場合に顕著になる傾向がある。上記振動は、上記積層キャパシタの外部電極から上記積層キャパシタが実装された印刷回路基板に伝達される。この際、上記印刷回路基板が振動して騒音が発生する。

## 【0005】

即ち、上記印刷回路基板の振動により発生する騒音が可聴周波数(20~20000Hz)領域に含まれると、その振動音が人に不快感を与える。このような音をアコースティックノイズ(acoustic noise)と言う。

## 【0006】

本特許の発明者は、上記アコースティックノイズを低減するために、積層キャパシタ内の内部電極を印刷回路基板に実装する方向に関する研究を行ったことがある。その結果、内部電極が上記印刷回路基板に対して水平な方向性を有するように上記積層キャパシタを印刷回路基板に実装すると、内部電極が上記印刷回路基板に対して垂直な方向性を有するように実装する場合より、アコースティックノイズが低減することを確認できた。

10

## 【0007】

しかし、内部電極が印刷回路基板に対して水平な方向性を有するように上記積層キャパシタを印刷回路基板に実装してアコースティックノイズを測定しても、騒音レベルが一定レベル以上になるため、アコースティックノイズをさらに低減することができる研究が必要であった。

20

## 【0008】

また、積層キャパシタの外部色は濃い褐色を帯びるが、外部で区分することが困難であり、上記内部電極が印刷回路基板に対して水平な方向性を有するように実装するための研究も必要である。

## 【0009】

下記先行技術文献の特許文献1には、内部電極が印刷回路基板に対して水平な方向性を有するように実装されているが、高周波ノイズを減らすために信号線路間のピッチを狭くした技術的特徴が開示されている。また、特許文献2及び特許文献3には、積層キャパシタの上部カバー層と下部カバー層の厚さが異なることが記載されているが、アコースティックノイズの改善または低減という課題を解決するための方案は提案されていない。さらに、アコースティックノイズを低減するために、本特許の請求項及び本発明の実施例が提案する活性層の中心部が積層チップキャパシタの中心部から外れる程度の範囲や上部カバー層と下部カバー層との間の比率、セラミック本体の厚さに対する下部カバー層が占める比率、活性層の厚さに対して下部カバー層が占める比率等を開示または予想していない。

30

## 【0010】

また、特許文献4及び5は、積層チップキャパシタの上部と下部を区分するために、積層チップキャパシタの上部面にマークを形成する技術が開示されているが、本特許の請求項及び本発明の実施例が提案する半透明の識別層がセラミック本体内のカバー層に形成される内容などを開示又は予想していない。

40

## 【先行技術文献】

## 【特許文献】

## 【0011】

【特許文献1】日本特許公開公報第1994 268464号

【特許文献2】日本特許公開公報第1994 215978号

【特許文献3】日本特許公開公報第1996 130160号

【特許文献4】日本特許公開公報第2006-203165号

【特許文献5】日本特許公開公報第1996-330174号

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0012】

50

本発明の目的は、積層チップキャパシタの上部カバー層より下部カバー層の厚さを大きくし、活性層の中心部がセラミック本体の中心部を外れる範囲を設定した積層チップキャパシタを提供することにある。

【0013】

また、本発明の目的は、厚さがより大きい下部カバー層に半透明の識別層が形成され、上部カバー層と下部カバー層を識別することができる積層キャパシタを提供することにある。

【0014】

また、本発明の他の目的は、内部電極が印刷回路基板に水平となるように、また上記下部カバー層が印刷回路基板と隣接するように、積層チップキャパシタを印刷回路基板に実装して、アコースティックノイズが低減された積層チップ電子部品の実装基板を提供することにある。

10

【0015】

また、本発明のさらに他の目的は、包装シートの収納部の底面を基準として内部電極が水平に配置されて整列される積層チップ電子部品の包装体を提供することにある。

【課題を解決するための手段】

【0016】

本発明の第1実施例による積層チップ電子部品は、内部電極及び誘電体層を含むセラミック本体と、上記セラミック本体の長さ方向の両端部を覆うように形成される外部電極と、上記誘電体層を挟んで上記内部電極が対向して配置され、容量が形成される活性層と、上記活性層の厚さ方向の上部または下部に形成され、厚さ方向の下部が厚さ方向の上部より大きい厚さを有する上部及び下部カバー層と、を含み、上記セラミック本体の全体厚さの $1/2$ をA、上記下部カバー層の厚さをB、上記活性層の全体厚さの $1/2$ をC、上記上部カバー層の厚さをDと規定したときに、上記上部カバー層の厚さDはD $4\mu\text{m}$ の範囲を満たし、上記活性層の中心部が上記セラミック本体の中心部から外れる比率(B+C)/Aは1.063(B+C)/A 1.745の範囲を満たし、上記下部カバー層は上記上部カバー層と区別される色を有する識別層を含み、上記識別層の厚さは30 $\mu\text{m}$ 以上上記下部カバー層の厚さ以下であることができる。

20

【0017】

上記上部カバー層の厚さDと下部カバー層の厚さBとの比率D/Bは0.021 D/B 0.422の範囲を満たすことができる。

30

【0018】

上記セラミック本体の厚さの $1/2$ であるAに対する上記下部カバー層の厚さBの比率B/Aは0.329 B/A 1.522の範囲を満たすことができる。

【0019】

上記下部カバー層の厚さBに対する上記活性層の厚さの $1/2$ であるCの比率C/Bは0.146 C/B 2.458の範囲を満たすことができる。

【0020】

上記識別層は白色であることができる。

40

【0021】

上記識別層の色は上記上部カバー層の色より明るいことができる。

【0022】

上記識別層は主成分として $\text{ABO}_3$ で表される化合物を含み、AはBaまたはCa、Zr及びSrのうち少なくとも一つを含み、BはTiまたはTiとZr及びHfのうち少なくとも一つを含み、上記主成分100モルに対し、0.1~30モルのSi及びAlを副成分として含むことができる。

【0023】

上記主成分100モルに対し、1.0~1.5モルのSi及び0.2~0.8モルのAlを副成分として含むことができる。

【0024】

50

上記主成分 100 モルに対し、0 ~ 2 モルの Mg 及び 0 ~ 0.09 モルの Mn を含むことができる。

【0025】

上記主成分 100 モルに対し、Mg 及び Mn の含量はそれぞれ 0.001 モル未満であることができる。

【0026】

上記識別層は上記主成分 100 モルに対し、1 モル以下の Ca 及び Zr から選択された一つの添加剤を含むことができる。

【0027】

他の側面において、積層チップ電子部品の実装基板は、上記第 1 実施例の積層チップ電子部品と、上記外部電極と半田によって連結される電極パッドと、上記電極パッドが形成されており、上記内部電極が水平となるように、また上記下部カバー層が上記上部カバー層より厚さ方向下側に配置されるように、上記積層電子部品が上記電極パッドに実装される印刷回路基板と、を含むことができる。

【0028】

電圧が印加されて上記活性層の中心部で発生する変形率と上記下部カバー層で発生する変形率との差により、上記セラミック本体の長さ方向の両端部に形成される変曲点が上記半田の高さ以下に形成されることができる。

【0029】

さらに他の側面において、積層チップ電子部品の包装体は、上記第 1 実施例の積層チップ電子部品と、上記積層チップ電子部品が収納される収納部が形成された包装シートと、を含み、上記収納部内に収納される上記積層チップ電子部品の上記内部電極の全ては、上記収納部の底面と水平に配置され、上記収納部内に収納される上記積層チップ電子部品の上記下部カバー層の全ては、収納部の底面に向かうことができる。

【0030】

上記積層チップ電子部品が収納された包装シートはリール状に巻線されて形成されることができる。

【0031】

本発明の第 2 実施例による積層チップ電子部品は、六面体形状のセラミック本体の長さ方向の両端部に形成される外部電極と、上記セラミック本体内に形成され、容量を形成するように誘電体層を挟んで対向して配置される多数の内部電極からなる活性層と、上記活性層の最上側の内部電極の上部に形成される上部カバー層と、上記活性層の最下側の内部電極の下部に形成され、上記上部カバー層の厚さより大きい厚さを有する下部カバー層と、を含み、上記下部カバー層は上記上部カバー層と区別される色を有する識別層を含み、上記識別層の厚さは 30  $\mu$ m 以上上記下部カバー層の厚さ以下であることができる。

【0032】

電圧が印加されて上記活性層の中心部で発生する変形率と上記下部カバー層で発生する変形率との差により、上記セラミック本体の厚さ方向の中心部より下側の上記セラミック本体の長さ方向の両端部に変曲点が形成され、上記セラミック本体の全体厚さの 1/2 を A 、上記下部カバー層の厚さを B 、上記活性層の全体厚さの 1/2 を C と規定したときに、上記活性層の中心部が上記セラミック本体の中心部から外れる比率 (B + C) / A は 1.063 (B + C) / A 1.745 の範囲を満たすことができる。

【0033】

上記上部カバー層の厚さを D と規定したときに、上記上部カバー層の厚さ D と下部カバー層の厚さ B との比率 D / B は 0.021 D / B 0.422 の範囲を満たすことができる。

【0034】

上記セラミック本体の厚さの 1/2 である A に対する上記下部カバー層の厚さ B の比率 B / A は 0.329 B / A 1.522 の範囲を満たすことができる。

【0035】

10

20

30

40

50

上記下部カバー層の厚さ B に対する上記活性層の 1 / 2 である C の比率 C / B は 0 . 1 4 6 C / B 2 . 4 5 8 の範囲を満たすことができる。

【 0 0 3 6 】

上記識別層は白色であることができる。

【 0 0 3 7 】

上記識別層の色は上記上部カバー層の色より明るいことができる。

【 0 0 3 8 】

上記識別層は主成分として A B O<sub>3</sub> で表される化合物を含み、 A は B a または B a と C a 、 Z r 及び S r のうち少なくとも一つを含み、 B は T i または T i と Z r 及び H f のうち少なくとも一つを含み、上記主成分 1 0 0 モルに対し、 0 . 1 ~ 3 0 モルの S i 及び A l を副成分として含むことができる。

【 0 0 3 9 】

上記主成分 1 0 0 モルに対し、 1 . 0 ~ 1 . 5 モルの S i 及び 0 . 2 ~ 0 . 8 モルの A l を副成分として含むことができる。

【 0 0 4 0 】

上記主成分 1 0 0 モルに対し、 0 ~ 2 モルの M g 及び 0 ~ 0 . 0 9 モルの M n を含むことができる。

【 0 0 4 1 】

上記主成分 1 0 0 モルに対し、 M g 及び M n の含量はそれぞれ 0 . 0 0 1 モル未満であることができる。

【 0 0 4 2 】

上記識別層は上記主成分 1 0 0 モルに対し、 1 モル以下の C a 及び Z r から選択された少なくとも一つ及び 0 . 2 モル以下の K 、 B 及び L i から選択された少なくとも一つの添加剤を含むことができる。

【 0 0 4 3 】

他の側面において、積層チップ電子部品の実装基板は、上記第 2 実施例の積層チップ電子部品と、上記外部電極と半田によって連結される電極パッドと、上記電極パッドが形成されており、上記内部電極が水平となるように、また上記下部カバー層が上記上部カバー層より厚さ方向下側に配置されるように、上記積層電子部品が上記電極パッドに実装される印刷回路基板と、を含むことができる。

【 0 0 4 4 】

電圧が印加されて上記活性層の中心部で発生する変形率と上記下部カバー層で発生する変形率との差により、上記セラミック本体の長さ方向の両端部に形成される変曲点が上記半田の高さ以下に形成されることができる。

【 0 0 4 5 】

さらに他の側面において、積層チップ電子部品の包装体は、上記第 2 実施例の積層チップ電子部品と、上記積層チップ電子部品が収納される収納部が形成された包装シートと、を含み、上記収納部内に収納される上記積層チップ電子部品の上記内部電極の全ては、上記収納部の底面と水平に配置され、上記収納部内に収納される上記積層チップ電子部品の上記下部カバー層の全ては、収納部の底面に向かうことができる。

【 0 0 4 6 】

上記積層チップ電子部品が収納された包装シートはリール状に巻線されて形成されることがある。

【 発明の効果 】

【 0 0 4 7 】

本発明の一実施例による積層チップキャパシタ及びその実装基板によると、アコースティックノイズを著しく低減させることができる。

【 図面の簡単な説明 】

【 0 0 4 8 】

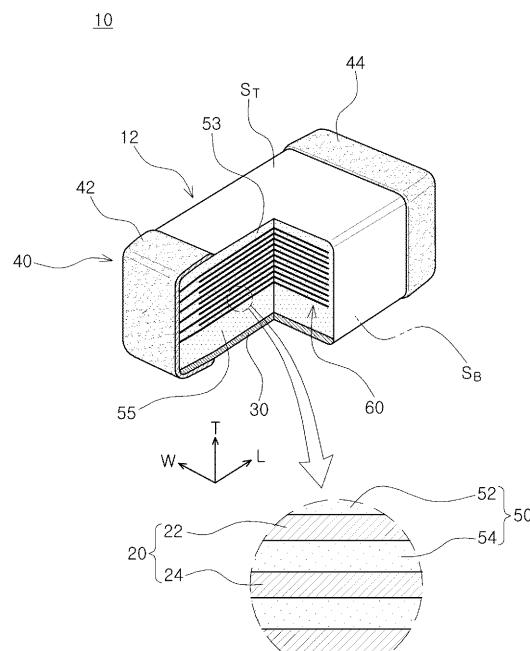

【 図 1 】本発明の一実施例による積層チップキャパシタを一部切開して図示した概略切開

10

20

30

40

50

斜視図である。

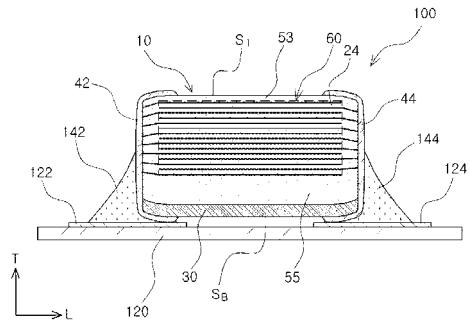

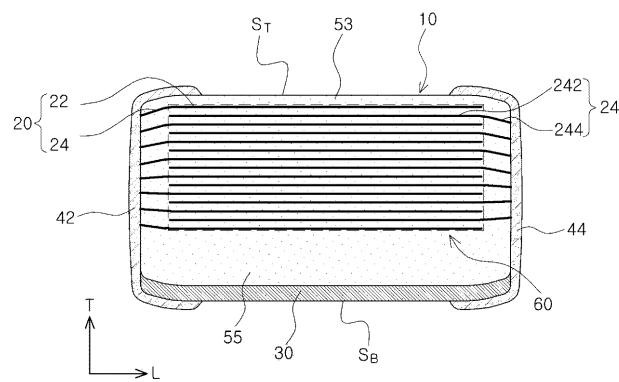

【図2】図1の積層チップキャパシタを長さ方向及び厚さ方向に切断して図示した断面図である。

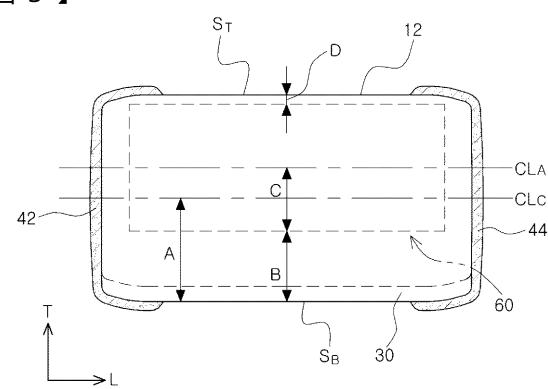

【図3】図1の積層チップキャパシタの寸法関係を説明するための長さ方向及び厚さ方向の概略断面図である。

【図4】図1の積層チップキャパシタが印刷回路基板に実装された状態を概略的に図示した概略斜視図である。

【図5】図4の積層チップキャパシタが印刷回路基板に実装された状態を図示した概略平面図である。

【図6】図4の積層チップキャパシタが印刷回路基板に実装された状態を長さ方向及び厚さ方向に切断して図示した断面図である。

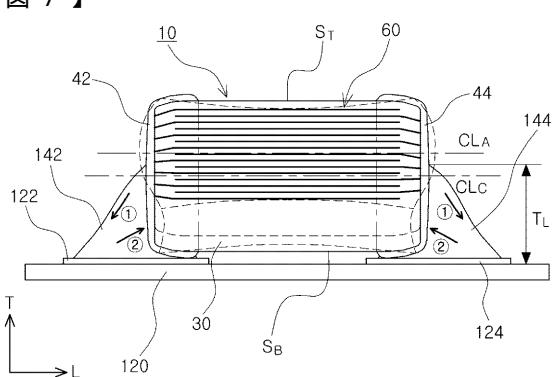

【図7】図4の積層チップキャパシタが印刷回路基板に実装された状態で、電圧が印加されて積層チップキャパシタが変形される様子を概略的に図示した断面図である。

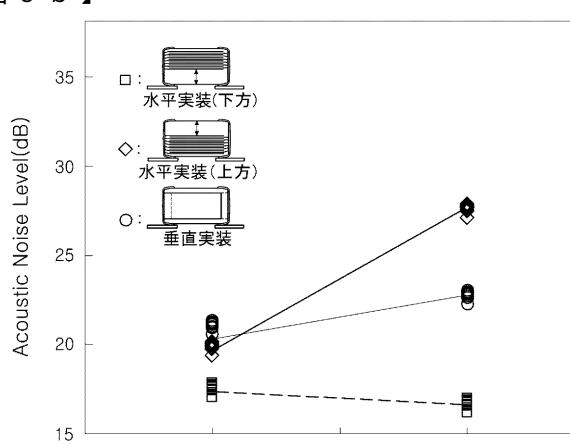

【図8a】従来の積層チップキャパシタの内部電極が印刷回路基板に垂直に実装された場合と水平に実装された場合において、電極パッドのサイズに応じたアコースティックノイズの変化を示したグラフである。

【図8b】本発明の実施例による内部電極が印刷回路基板に水平である状態で、下部カバー層が印刷回路基板と隣接するように積層チップキャパシタを印刷回路基板に実装した場合において、電極パッドのサイズに応じたアコースティックノイズの変化を従来技術と対比して示したグラフである。

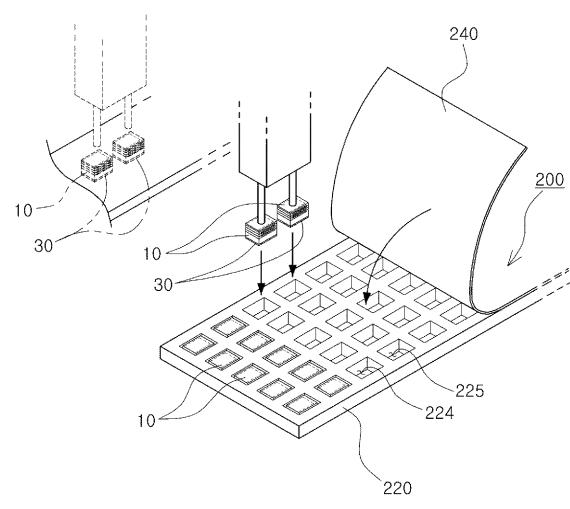

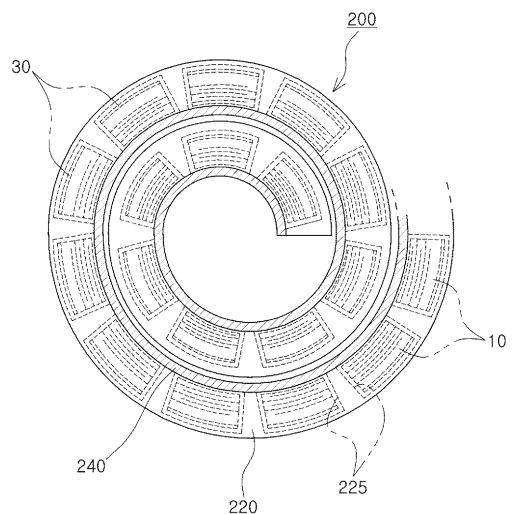

【図9】本発明の一実施例による積層チップキャパシタが包装体に実装される様子を図示した概略斜視図である。

【発明を実施するための形態】

【0049】

以下、図面を参照して本発明の具体的な実施例を詳細に説明する。但し、本発明の思想は提示される実施例に制限されず、本発明の思想を理解する当業者は同一の思想の範囲内で他の構成要素の追加、変更、削除等によって、退歩的な他の発明や本発明の思想の範囲内に含まれる他の実施例を容易に提案することができ、これも本発明の思想の範囲内に含まれる。

【0050】

本発明の一実施例による積層チップ電子部品は、誘電体層を用いて、上記誘電体層を挟んで内部電極が互いに対向する構造を有する積層セラミックキャパシタ、積層バリスタ、サーミスター、圧電素子、多層基板などにも適切に用いられることができる。

【0051】

また、各実施例の図面に示す同一の思想の範囲内における機能が同一の構成要素は、同一の参照符号を用いて説明する。

【0052】

積層チップキャパシタ

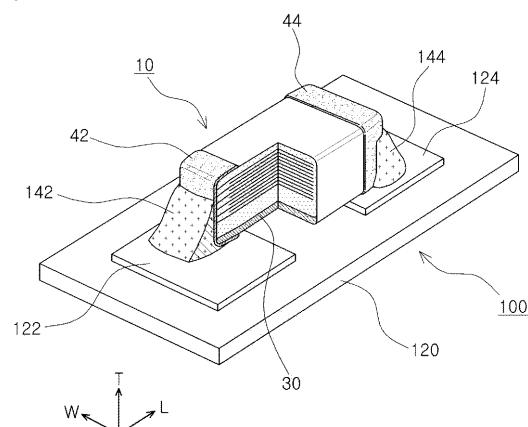

図1は本発明の一実施例による積層チップキャパシタを一部切開して図示した概略切開斜視図であり、図2は図1の積層チップキャパシタを長さ方向及び厚さ方向に切断して図示した断面図であり、図3は図1の積層チップキャパシタの寸法関係を説明するための長さ方向及び厚さ方向の概略断面図である。

【0053】

図1から図3を参照すると、積層チップキャパシタ10は、セラミック本体12と、外部電極40と、活性層60と、上部及び下部カバー層53、55と、を含むことができる。

【0054】

上記セラミック本体12は、セラミックグリーンシート上に内部電極20を形成するために導電性ペーストを塗布し、上記内部電極20が形成されたセラミックグリーンシートを積層した後、焼成することにより製造することができる。上記セラミック本体12は、多

10

20

30

40

50

数の誘電体層 5 2、 5 4 と内部電極 2 2、 2 4 とを繰り返して積層して形成することができる。

【 0 0 5 5 】

上記セラミック本体 1 2 は六面体形状からなることができる。チップ焼成時のセラミック粉末の焼成収縮により、セラミック本体 1 2 は完全な直線を有する六面体形状ではないが、実質的に六面体形状を有することができる。

【 0 0 5 6 】

本発明の実施例を明確に説明するために六面体の方向を定義すると、図 1 に表示された L、W 及び T はそれぞれ、長さ方向、幅方向、厚さ方向を示す。ここで、厚さ方向は誘電体層が積層された積層方向と同一の概念で用いられることができる。

10

【 0 0 5 7 】

図 1 の実施例は、長さ方向が幅方向または厚さ方向より大きい直方体状を有する積層チップキャパシタ 1 0 である。

【 0 0 5 8 】

上記誘電体層 5 0 をなす材料としては、高容量化のために高誘電率を有するセラミック粉末を用いることができる。上記セラミック粉末としては、例えば、チタン酸バリウム ( BaTiO<sub>3</sub> ) 系粉末またはチタン酸ストロンチウム ( SrTiO<sub>3</sub> ) 系粉末などを用いることができ、これに制限されるものではない。

【 0 0 5 9 】

上記第 1 及び第 2 外部電極 4 2、 4 4 は、金属粉末を含む導電性ペーストで形成されることができる。上記導電性ペーストに含まれる金属粉末としては、Cu、Ni、またはこれらの合金を用いることができ、特にこれらに制限されるものではない。

20

【 0 0 6 0 】

上記内部電極 2 0 は第 1 内部電極 2 2 及び第 2 内部電極 2 4 を含むことができ、上記第 1 及び第 2 内部電極 2 2、 2 4 はそれぞれ、第 1 及び第 2 外部電極 4 2、 4 4 を介して電気的に連結されることができる。

【 0 0 6 1 】

ここで、上記第 1 内部電極 2 2 及び第 2 内部電極 2 4 は、誘電体層 5 4 ( 図 1 参照 ) を挟んで対向して重なる第 1 及び第 2 電極パターン部 2 2 2、 2 4 2 と、それぞれの第 1 及び第 2 外部電極 4 2、 4 4 に引き出される第 1 及び第 2 リード部 2 2 4、 2 4 4 と、を含むことができる。

30

【 0 0 6 2 】

上記第 1 及び第 2 電極パターン部 2 2 2、 2 4 2 は、厚さ方向に連続して積層され、セラミック本体 1 2 内で静電容量を形成する活性層 6 0 を構成することができる。

【 0 0 6 3 】

積層チップキャパシタの長さ方向及び厚さ方向の断面において、上記活性層 6 0 を除いた部分をマージン部と定義することができる。上記マージン部のうち厚さ方向に上記活性層 6 0 の上部マージン部及び下部マージン部を特に、上部カバー層 5 3 及び下部カバー層 5 5 と定義することができる。

40

【 0 0 6 4 】

上記上部カバー層 5 3 及び下部カバー層 5 5 は、上記第 1 内部電極 2 2 と第 2 内部電極 2 4 との間に形成される誘電体層 5 2、 5 4 と同様に、セラミックグリーンシートを焼結して形成することができる。

【 0 0 6 5 】

上記上部カバー層 5 3 及び下部カバー層 5 5 を含む複数の誘電体層 5 0 は焼結された状態であり、隣接する誘電体層 5 0 の間の境界は走査型電子顕微鏡 ( SEM、 Scanning Electron Microscope ) を利用せずにには確認することが困難であるほど一体化されることができる。

【 0 0 6 6 】

本実施例において、上記下部カバー層 5 5 は上記上部カバー層 5 3 より大きい厚さを有す

50

ることができる。即ち、上記下部カバー層55は、上記上部カバー層53よりセラミックグリーンシートの積層数を増やすことにより、上記上部カバー層53より大きい厚さを有することができる。

【0067】

上記下部カバー層55は、上記セラミック本体12において、上記上部カバー層と区別される色を有する識別層30を含むことができる。

【0068】

上記識別層30は焼成後の厚さが30μm以上、上記下部カバー層の厚さ以下であることができる。上記識別層30は、例えば、4μm以下のセラミックグリーンシートが少なくとも8枚以上積層されて形成されることができる。

10

【0069】

上記識別層30は主成分として $ABO_3$ で表される化合物を含むことができる。ここで、AはBaまたはBaとCa、Zr及びSrのうち少なくとも一つを含むことができる。付け加えると、AはBaであるか、BaにCa、Zr及びSrのうち少なくとも一つを含むことができる。また、BはTiまたはTiとZr及びHfのうち少なくとも一つを含むことができる。即ち、BはTiであるか、TiとZr、TiとHf、Ti、Zr及びHrであることができる。

【0070】

ここで、上記主成分100モルに対し、0.1~30モルのSi及びAlを副成分として含むことができる。

20

【0071】

より詳細には、Ba、Si及びAlを含む副成分のうちSiの含量は上記主成分100モルに対し、1.0~1.5モル、Alの含量は上記主成分100モルに対し、0.2~0.8モルであることができる。また、本発明の他の一実施例によるアコースティックノイズ低減効果のある低誘電率製品の場合は、上記Ba、Si及びAlを含む副成分のうちSi及びAlの含量が主成分100モルに対し、30モルまで含むこともできる。

【0072】

また、本発明の一実施例によると、上記識別層30は上記主成分100モルに対し、0~2モルのMg及び0~0.09モルのMnを含むことができる。

30

【0073】

ここで、MgとMnのような添加剤は、収縮率が他の誘電体層50と類似するようにして、他の誘電体層50との成分の差異によるクラックやデラミネーションの発生を減らすことができる。

【0074】

BaTiO<sub>3</sub>の母材粉末にSi及びAlを含む副成分を含み、添加剤としてMgまたはMnを微量添加して製造したセラミックグリーンシートを1150で焼成する場合、焼成されたセラミックグリーンシートは白色系の色を有することができる。

【0075】

特に、白色系の色がより目立つようにMgとMnの量を減らすことができ、上記識別層30は上記主成分100モルに対し、Mg及びMnの含量はそれぞれ0.001モル未満含まれることができる。

40

【0076】

本発明の実施例のような副成分と添加剤の組成を有さない一般的なセラミックグリーンシートは、焼成後濃い褐色系の色を有する。上記白色系の識別層30は、焼成後濃い褐色系の色の活性層60や上部カバー層53と色の差異により区分されることができる。即ち、上記識別層30の色は上記活性層60や上部カバー層53の色より明るいことができる。

【0077】

このような色の差異は、下部カバー層55が印刷回路基板の上面と隣接するように実装されるようにし、アコースティックノイズを減らす重要な役割をする。

【0078】

50

また、上記識別層30は上記主成分100モルに対し、1モル以下のCa及びZrから少なくとも一つと、0.2モル以下のK、B及びLiから選択された少なくとも一つの添加剤を含むことができる。ここで、該添加剤は無色の添加剤で、ガラスの形成に寄与することができる。

【0079】

下記表1には下部カバー層に識別層を形成し、上記識別層の厚さを調節しながら、下部カバー層55を印刷回路基板の上面と隣接するように実装する実験例を示した。

【0080】

【表1】

| 下部カバー層の全<br>体厚さ (μm) | 識別層の厚さ (μ<br>m) | 識別層の厚さ／下<br>部カバー層の全体<br>厚さ (%) | 上下区別不良率<br>(%) |

|----------------------|-----------------|--------------------------------|----------------|

| 330                  | 10              | 3.0                            | 47             |

|                      | 20              | 6.1                            | 23             |

|                      | 30              | 9.1                            | 0              |

|                      | 40              | 12.1                           | 0              |

|                      | 50              | 15.2                           | 0              |

|                      | 70              | 21.2                           | 0              |

|                      | 100             | 30.3                           | 0              |

|                      | 150             | 45.5                           | 0              |

|                      | 200             | 60.6                           | 0              |

|                      | 250             | 75.8                           | 0              |

|                      | 270             | 81.8                           | 0              |

|                      | 300             | 90.9                           | 0              |

|                      | 310             | 93.9                           | 0              |

|                      | 330             | 100                            | 0              |

【0081】

識別層30の厚さに従って、印刷回路基板に下部カバー層55が隣接するように実装されない場合を不良と判定した。表1を参照すると、識別層30の厚さは少なくとも30μm以上でなければ、外部で確実に認識できない。

【0082】

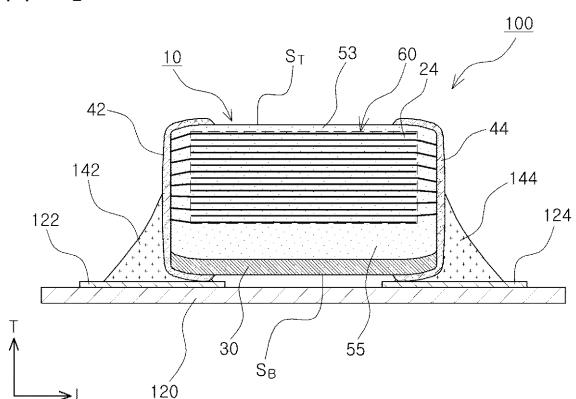

図3を参照すると、本実施例の積層チップキャパシタをより明確に規定することができる。

【0083】

まず、上記セラミック本体の全体厚さの1/2をA、上記下部カバー層の厚さをB、上記活性層の全体厚さの1/2をC、上記上部カバー層の厚さをDと規定することができる。

【0084】

上記セラミック本体12の全体厚さは、外部電極40が上記セラミック本体の上面S<sub>T</sub>と下面S<sub>B</sub>に塗布されて形成される部分だけの厚さを含まない。本実施例では、セラミック

10

20

30

40

50

本体 1 2 の上面  $S_T$  と下面  $S_B$  の 1 / 2 を A と規定する。

【 0 0 8 5 】

上記下部カバー層 5 5 の厚さ B は、活性層 6 0 の厚さ方向の最下側に形成される内部電極の下面からセラミック本体 1 2 の下面  $S_B$  までの距離を規定するものである。また、上記上部カバー層 5 3 の厚さ D は、活性層 6 0 の厚さ方向の最上側に形成される内部電極の上面からセラミック本体 1 2 の上面  $S_T$  までの距離を規定するものである。

【 0 0 8 6 】

ここで、上記活性層 6 0 の全体厚さは、活性層 6 0 の最上側に形成される内部電極の上面から活性層 6 0 の最下側に形成される内部電極の下面までの距離を意味する。C は、上記活性層 6 0 の 1 / 2 を規定するものである。

10

【 0 0 8 7 】

本実施例によると、上記上部カバー層 5 3 の厚さ D は、D 4  $\mu m$  の範囲を満たすことができる。D が 4  $\mu m$  より小さい場合には、内部電極がセラミック本体 1 2 の上面  $S_T$  に露出される不良が発生する恐れがある。

【 0 0 8 8 】

また、本実施例によると、上記活性層 6 0 の中心部が上記セラミック本体 1 2 の中心部から外れる比率  $(B + C) / A$  は、1.063  $(B + C) / A$  1.745 の範囲を満たすことができる。

20

【 0 0 8 9 】

ここで、上記活性層 6 0 の中心部は、上記活性層 6 0 の最上側に形成される内部電極の上面から活性層 6 0 の最下側に形成される内部電極の下面までの距離の中間地点である活性層センターライン  $CL_A$  から上部及び下部に 1  $\mu m$  の範囲内であると規定することができる。

【 0 0 9 0 】

また、上記セラミック本体 1 2 の中心部は、セラミック本体 1 2 の上面  $S_T$  と下面  $S_B$  との間の中間地点であるセラミック本体のセンターライン  $CL_c$  から上部及び下部に 1  $\mu m$  の範囲内であると規定することができる。

30

【 0 0 9 1 】

積層チップキャパシタ 1 0 の両端部に形成される第 1 及び第 2 外部電極 4 2、4 4 に異なる極性の電圧が印加されると、誘電体層 5 0 の逆圧電効果 (Inverse piezoelectric effect) によってセラミック本体 1 2 は厚さ方向に膨脹及び収縮するようになり、第 1 及び第 2 外部電極 4 2、4 4 の長さ方向の両端部は、ポアソン効果 (Poisson effect) によってセラミック本体 1 2 の厚さ方向の膨脹及び収縮とは反対に収縮及び膨脹するようになる。

【 0 0 9 2 】

ここで、上記活性層 6 0 の中心部は、第 1 及び第 2 外部電極 4 2、4 4 の長さ方向の両端部で最大に膨脹及び収縮される部分であり、アコースティックノイズが発生する原因となる。

【 0 0 9 3 】

本実施例では、アコースティックノイズを低減するために、上記活性層 6 0 の中心部がセラミック本体 1 2 の中心部から外れる比率を規定した。

40

【 0 0 9 4 】

一方、本実施例では、電圧が印加されて上記活性層 6 0 の中心部で発生する変形率と上記下部カバー層 5 5 で発生する変形率との差により、上記セラミック本体 1 2 の厚さ方向の中心部より下側の上記セラミック本体 1 2 の長さ方向の両端部に変曲点が形成されることがある。

【 0 0 9 5 】

アコースティックノイズを低減するために、本実施例によると、上記上部カバー層 5 3 の厚さ D と下部カバー層 5 5 の厚さ B の比率  $D / B$  は、0.021  $D / B$  0.422 の範囲を満たすことができる。

50

## 【0096】

また、上記セラミック本体12の厚さの1/2であるAに対する上記下部カバー層55の厚さBの比率B/Aは、0.329 B/A 1.522の範囲を満たすことができる。

## 【0097】

また、上記下部カバー層55の厚さBに対する上記活性層60の厚さの1/2であるCの比率C/Bは、0.146 C/B 2.458の範囲を満たすことができる。

## 【0098】

一方、本発明によると、上部カバー層53より大きい厚さの下部カバー層55を印刷回路基板の上面と隣接するように実装するために、上記下部カバー層55の白色の識別層30が印刷回路基板の上面に向かうようにすることができる。

10

## 【0099】

## 積層チップキャパシタの実装基板

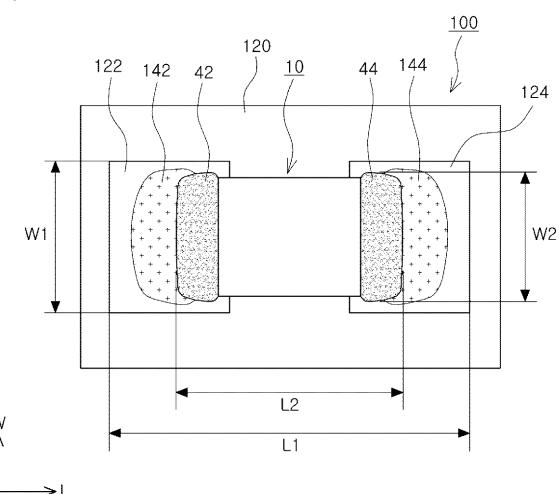

図4は図1の積層チップキャパシタが印刷回路基板に実装された状態を概略的に図示した概略斜視図であり、図5は図4の積層チップキャパシタが印刷回路基板に実装された状態を図示した概略平面図であり、図6は図4の積層チップキャパシタが印刷回路基板に実装された状態を長さ方向及び厚さ方向に切断して図示した断面図である。

## 【0100】

本実施例による積層チップキャパシタの実装基板100は、積層チップ電子部品10と、電極パッド122、124と、印刷回路基板120と、を含むことができる。

20

## 【0101】

上記積層チップ電子部品10は、上記で既に説明した積層チップキャパシタであることができ、内部電極22、24が上記印刷回路基板120に水平となるように積層チップキャパシタ10が印刷回路基板120に実装されることができる。

## 【0102】

また、上記積層チップキャパシタ10のセラミック本体12内の上部カバー層53より大きい厚さの下部カバー層55が上記上部カバー層53より厚さ方向下側に配置されるように、上記積層チップキャパシタ10が上記印刷回路基板120上に実装されることができる。

## 【0103】

上記積層チップキャパシタ10が印刷回路基板120に実装され、電圧が印加されると、アコースティックノイズが発生する。この際、電極パッド122、124のサイズにより、上記積層チップキャパシタ10の第1及び第2外部電極42、44と上記電極パッド122、124とを連結する半田の量が決まり、アコースティックノイズを低減することができる。

30

## 【0104】

図7は図4の積層チップキャパシタが印刷回路基板に実装された状態で、電圧が印加されて積層チップキャパシタが変形される様子を概略的に図示した断面図である。

## 【0105】

図7を参照すると、上記積層チップキャパシタ10が印刷回路基板120に実装され、積層チップキャパシタ10の両端部に形成される第1及び第2外部電極42、44に異なる極性の電圧が印加されると、誘電体層50の逆圧電効果(Reverse piezoelectric effect)によってセラミック本体12は厚さ方向に膨脹及び収縮するようになり、第1及び第2外部電極42、44の長さ方向の両端部は、ポアソン効果(Poisson effect)によってセラミック本体12の厚さ方向の膨脹及び収縮とは反対に収縮及び膨脹するようになる。

40

## 【0106】

一方、本実施例では、電圧が印加されて上記活性層60の中心部で発生する変形率と上記下部カバー層55で発生する変形率との差により、上記セラミック本体12の厚さ方向の中心部より下側の上記セラミック本体12の長さ方向の両端部に変曲点(PI, point of inflection)が形成されることがある。

50

## 【0107】

また、上記変曲点P Iは、セラミック本体1 2の外部面の位相が変化される地点であり、電極パッド1 2 2、1 2 4で上記積層チップキャパシタ1 0の外部電極4 2、4 4に形成される半田1 4 2、1 4 4の高さ以下に形成されることができる。

## 【0108】

ここで、上記活性層6 0の中心部は、電圧の印加によって、第1及び第2外部電極4 2、4 4の長さ方向の両端部で最大に膨脹及び収縮される部分になる。

## 【0109】

図7は積層チップキャパシタ1 0の長さ方向の両端部が最大に膨脹された部分を示しており、積層チップキャパシタ1 0の長さ方向の両端部が最大に膨脹されると、半田1 4 2、1 4 4の上部には膨脹によって外部に押し出される力((1))が生じ、半田1 4 2、1 4 4の下部には膨脹によって外部に押し出される力によって外部電極の方に押す、収縮される力((2))が生じる。

## 【0110】

これにより、変曲点P Iが半田の高さ以下に形成されることができる。

## 【0111】

図5を参照すると、第1電極パッド1 2 2と第2電極パッド1 2 4の長さ方向の両端部の間の距離をL 1、積層チップキャパシタ1 0の第1外部電極4 2と第2外部電極4 4の長さ方向の外部面の間の距離をL 2と規定している。また、第1電極パッド1 2 2と第2電極パッド1 2 4の幅方向の両端部の間の距離をW 1、積層チップキャパシタ1 0の第1外部電極4 2と第2外部電極4 4の幅方向の外部面の間の距離をW 2と規定している。

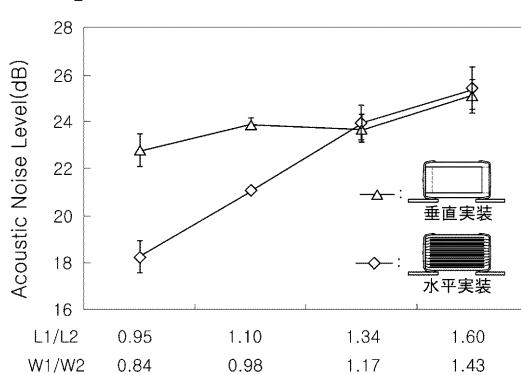

## 【0112】

図8 aは、従来の積層チップキャパシタの内部電極が印刷回路基板に垂直に実装された場合と水平に実装された場合において、電極パッドのサイズに応じたアコースティックノイズの変化を図示したグラフである。

## 【0113】

図8 aを参照すると、電極パッドのサイズ、即ち、L 1 / L 2が1.34及び1.17以下に小さくなる時、積層チップキャパシタの内部電極が印刷回路基板に水平に実装された場合にアコースティックノイズが低減されることが分かる。

## 【0114】

しかし、積層チップキャパシタの内部電極が印刷回路基板に垂直に実装された場合には、アコースティックノイズの低減が大きくないことが分かる。

## 【0115】

即ち、電極パッドのサイズは、積層チップキャパシタの内部電極が印刷回路基板に水平に実装されるかまたは垂直に実装されるかによって、アコースティックノイズの低減において異なる傾向性を示す。

## 【0116】

図8 bは、本発明の実施例による内部電極が印刷回路基板に水平である状態で、下部カバー層が印刷回路基板と隣接するように積層チップキャパシタを印刷回路基板に実装した場合において、電極パッドのサイズに応じたアコースティックノイズの変化を、従来技術と対比して図示したグラフである。

## 【0117】

図8 bを参照すると、積層チップキャパシタの内部電極が印刷回路基板に水平に実装される場合にも、下部カバーまたは上部カバーの厚さによってアコースティックノイズのサイズが異なることが分かる。従って、アコースティックノイズをさらに減少するためには、さらに他のパラメータを要することが分かる。

## 【0118】

本発明の実施例によると、活性層の中心部が積層チップキャパシタの中心部から外れる程度の範囲や上部カバー層と下部カバー層との間の比率、セラミック本体の厚さに対する下部カバー層が占める比率、活性層の厚さに対して下部カバー層が占める比率を調節してア

コースティックノイズをさらに低減させることができる。

【0119】

本発明の一実施例によると、活性層60の中心部が上記セラミック本体12の中心部から外れる比率 $(B+C)/A$ が1.063~ $(B+C)/A$ 1.745の範囲を満たすと、電極パッドが小さいため、半田の量が少ない場合にもアコースティックノイズが十分に低減され、電極パッドが大きい場合には、却ってアコースティックノイズがさらに低減することができる。

【0120】

即ち、活性層60の中心部が上記セラミック本体12の中心部から外れる比率 $(B+C)/A$ が1.06~ $(B+C)/A$ 1.8の範囲を満たすと、電極パッドのサイズに関らず、アコースティックノイズが著しく低減される。ここで、Aは上記セラミック本体の全体厚さの1/2、Bは上記下部カバー層の厚さ、Cは上記活性層の全体厚さの1/2、Dは上記上部カバー層の厚さをそれぞれ示す。

10

【0121】

活性層60の中心部が上記セラミック本体12の中心部から外れる比率 $(B+C)/A$ が1.063~ $(B+C)/A$ 1.745の範囲を満たすと、積層チップキャパシタの最大変位は活性層60の中心で、セラミック本体12の中心部の上部となるため、半田によって印刷回路基板120に伝達される変位量が減ることにより、アコースティックノイズが低減すると解釈することができる。

20

【0122】

積層チップキャパシタの包装体

図9は本発明の一実施例による積層チップキャパシタが包装体に実装される様子を図示した概略斜視図であり、図10は図9の包装体をリール状に巻取したことを図示した概略断面図である。

【0123】

図9を参照すると、本実施例による積層チップキャパシタの包装体200は、積層チップキャパシタ10が収納される収納部224が形成された包装シート220を含むことができる。

30

【0124】

上記包装シート220の収納部224は電子部品10と対応する形状を有しており、上記収納部224の底面225を基準として内部電極が水平に配置されることができる。

【0125】

上記積層チップキャパシタ10は、電子部品整列装置150により内部電極が水平に整列された状態を維持し、移送装置170により包装シート220に移動される。従って、包装シート220の収納部224の底面225を基準として内部電極が水平に配置されることができる。このような方法により、包装シート220内の多数の積層チップキャパシタ10が上記包装シート220内で同一の方向性を有するように配置されることができる。

【0126】

上記収納部224内に収納される上記積層チップキャパシタ10それぞれは、上記下部カバー層55が上記収納部224の底面に向かうように配置されることができる。ここで、上記下部カバー層55内の識別層30があると、上記セラミック本体12の上部及び下部を容易に区分することができる。このとき、上記収納部224内に収納される上記積層チップ電子部品の全ての上記下部カバー層55を上記収納部224の底面に向かうようにすることができる。このように、収納部224に収納されると、後に上記下部カバー層55が印刷回路基板に向かうように実装するのに有利である。

40

【0127】

上記積層チップキャパシタの包装体200は、上記収納部224の底面を基準として上記内部電極が水平に配置された電子部品10が収納された上記包装シート220を覆う包装膜240をさらに含むことができる。

【0128】

50

図10はリール状に巻取された形状の積層チップキャパシタの包装体200であり、連続的に巻取されて形成されることができる。

【0129】

実験例

本発明の実施例と比較例による積層セラミックキャパシタは、下記のように製作された。

【0130】

チタン酸バリウム(  $BaTiO_3$  )などの粉末を含んで形成されたスラリーをキャリアフィルム( carrier film )上に塗布及び乾燥して、 $1.8 \mu m$  の厚さに製造された複数個のセラミックグリーンシートを準備する。

【0131】

次に、上記セラミックグリーンシート上に、スクリーンを利用してニッケル内部電極用の導電性ペーストを塗布することにより、内部電極を形成する。

【0132】

上記セラミックグリーンシートを約370層に積層する。この際、内部電極が形成されていないセラミックグリーンシートを、内部電極が形成されたセラミックグリーンシートの下部に、上部より多く積層する。この積層体を85で $1000 \text{ kgf/cm}^2$ 圧力条件で等方圧縮( isostatic pressing )成形した。圧着が完了したセラミック積層体を個別チップの形態に切断し、切断されたチップは大気雰囲気で230、60時間維持して脱バインダを行った。

【0133】

その後、1200で内部電極が酸化されないように、 $Ni/NiO$ 平衡酸素分圧より低い $10^{-11} \text{ atm} \sim 10^{-10} \text{ atm}$ の酸素分圧下の還元雰囲気で焼成した。焼成後の積層チップキャパシタのチップサイズは、長さ×幅(  $L \times W$  )が約 $1.64 \text{ mm} \times 0.88 \text{ mm}$ (  $L \times W$ 、1608サイズ)であった。ここで、製作公差を長さ×幅(  $L \times W$  )が $\pm 0.1 \text{ mm}$ 内の範囲に定め、これを満たすものに対してアコースティックノイズの測定を行った。

【0134】

次に、外部電極、メッキなどの工程を経て、積層セラミックキャパシタに製作した。

【0135】

10

20

【表2-1】

| サン<br>プル<br>番号 | A<br>( $\mu$ m) | B<br>( $\mu$ m) | C<br>( $\mu$ m) | D<br>( $\mu$ m) | (B+C)/A | B/A   | D/B    | C/B    | Acoustic<br>Noise<br>(dB) | 容量<br>具現率 |

|----------------|-----------------|-----------------|-----------------|-----------------|---------|-------|--------|--------|---------------------------|-----------|

| 1*             | 405.5           | 40.2            | 365.4           | 39.9            | 1.000   | 0.099 | 0.993  | 9.090  | 29.5                      | OK        |

| 2*             | 436.0           | 70.4            | 365.9           | 69.7            | 1.001   | 0.161 | 0.990  | 5.197  | 25.7                      | OK        |

| 3*             | 455.5           | 90.8            | 364.3           | 91.5            | 0.999   | 0.199 | 1.008  | 4.012  | 23.1                      | OK        |

| 4*             | 508.1           | 24.9            | 361.1           | 269.1           | 0.760   | 0.049 | 10.807 | 14.502 | 31.2                      | OK        |

| 5*             | 456.6           | 25.2            | 360.1           | 167.8           | 0.844   | 0.055 | 6.659  | 14.290 | 32.5                      | OK        |

| 6*             | 527.3           | 30.2            | 191.0           | 642.4           | 0.419   | 0.057 | 21.272 | 6.325  | 30.3                      | OK        |

| 7*             | 414.5           | 30.9            | 188.8           | 420.4           | 0.530   | 0.075 | 13.605 | 6.110  | 30.5                      | OK        |

| 8*             | 516.2           | 39.4            | 360.7           | 271.5           | 0.775   | 0.076 | 6.891  | 9.155  | 28.2                      | OK        |

| 9*             | 446.0           | 39.8            | 365.5           | 121.2           | 0.909   | 0.089 | 3.045  | 9.183  | 29.1                      | OK        |

| 10*            | 469.1           | 40.6            | 364.2           | 169.1           | 0.863   | 0.087 | 4.165  | 8.970  | 27.9                      | OK        |

| 11*            | 416.2           | 40.7            | 360.7           | 70.3            | 0.964   | 0.098 | 1.727  | 8.862  | 28.4                      | OK        |

| 12*            | 428.3           | 40.8            | 360.0           | 95.7            | 0.936   | 0.095 | 2.346  | 8.824  | 28.9                      | OK        |

| 13*            | 495.9           | 40.9            | 364.9           | 221.0           | 0.818   | 0.082 | 5.403  | 8.922  | 28.1                      | OK        |

| 14*            | 435.9           | 25.0            | 421.3           | 4.2             | 1.024   | 0.057 | 0.168  | 16.852 | 31.6                      | OK        |

| 15*            | 420.7           | 70.4            | 365.9           | 39.1            | 1.037   | 0.167 | 0.555  | 5.197  | 25.7                      | OK        |

| 16             | 431.7           | 94.8            | 364.3           | 40.0            | 1.063   | 0.220 | 0.422  | 3.843  | 19.9                      | OK        |

| 17             | 443.0           | 103.8           | 389.1           | 4.0             | 1.113   | 0.234 | 0.039  | 3.749  | 19.3                      | OK        |

| 18             | 443.7           | 119.8           | 363.2           | 41.1            | 1.089   | 0.270 | 0.343  | 3.032  | 18.7                      | OK        |

| 19             | 447.1           | 147.3           | 362.1           | 22.7            | 1.139   | 0.329 | 0.154  | 2.458  | 17.9                      | OK        |

| 20             | 452.8           | 164.7           | 360.2           | 20.4            | 1.159   | 0.364 | 0.124  | 2.187  | 17.3                      | OK        |

| 21             | 448.7           | 170.3           | 361.0           | 5.1             | 1.184   | 0.380 | 0.030  | 2.120  | 17.2                      | OK        |

| 22             | 470.7           | 170.4           | 365.4           | 40.2            | 1.138   | 0.362 | 0.236  | 2.144  | 17.4                      | OK        |

| 23             | 491.9           | 220.3           | 360.8           | 41.8            | 1.181   | 0.448 | 0.190  | 1.638  | 16.9                      | OK        |

| 24             | 500.6           | 270.2           | 360.5           | 9.9             | 1.260   | 0.540 | 0.037  | 1.334  | 16.8                      | OK        |

10

20

30

40

【表2-2】

|     |       |       |       |      |       |       |       |       |      |    |

|-----|-------|-------|-------|------|-------|-------|-------|-------|------|----|

| 25  | 516.9 | 270.4 | 361.8 | 39.7 | 1.223 | 0.523 | 0.147 | 1.338 | 16.7 | OK |

| 26  | 502.1 | 364.9 | 312.3 | 14.7 | 1.349 | 0.727 | 0.040 | 0.856 | 16.6 | OK |

| 27  | 407.5 | 421.8 | 189.1 | 14.9 | 1.499 | 1.035 | 0.035 | 0.448 | 16.6 | OK |

| 28  | 445.8 | 493.3 | 179.3 | 39.7 | 1.509 | 1.107 | 0.080 | 0.363 | 16.5 | OK |

| 29  | 483.7 | 632.0 | 160.1 | 15.2 | 1.638 | 1.307 | 0.024 | 0.253 | 16.4 | OK |

| 30  | 520.0 | 643.4 | 190.7 | 15.2 | 1.604 | 1.237 | 0.024 | 0.296 | 16.4 | OK |

| 31  | 486.4 | 685.3 | 121.1 | 45.3 | 1.658 | 1.409 | 0.066 | 0.177 | 16.4 | OK |

| 32  | 507.2 | 742.7 | 120.8 | 30.1 | 1.702 | 1.464 | 0.041 | 0.163 | 16.4 | OK |

| 33  | 515.2 | 773.9 | 118.2 | 20.1 | 1.732 | 1.502 | 0.026 | 0.153 | 16.4 | OK |

| 34  | 524.5 | 798.2 | 116.9 | 16.9 | 1.745 | 1.522 | 0.021 | 0.146 | 16.3 | OK |

| 35* | 533.4 | 832.4 | 109.8 | 14.8 | 1.766 | 1.561 | 0.018 | 0.132 | 16.3 | NG |

| 36* | 533.3 | 841.1 | 105.3 | 14.9 | 1.775 | 1.577 | 0.018 | 0.125 | 16.3 | NG |

| 37* | 534.1 | 849.7 | 101.2 | 16.1 | 1.780 | 1.591 | 0.019 | 0.119 | 16.3 | NG |

\*は比較例

## 【0136】

表2のデータは、図3に示すように、積層チップキャパシタ10のセラミック本体12の幅方向(W)の中心部で長さ方向(L)及び厚さ方向(T)に切開した断面を走査型電子顕微鏡(SEM、Scanning Electron Microscope)で撮った写真を基準として、それぞれの寸法を測定したものである。

## 【0137】

ここで、A、B、C及びDは、上記で説明したように、上記セラミック本体の全体厚さの1/2をA、上記下部カバー層の厚さをB、上記活性層の全体厚さの1/2をC、上記上部カバー層の厚さをDと規定した。

## 【0138】

アコースティックノイズを測定するために、アコースティックノイズ測定用基板当り1個の試料(積層チップキャパシタ)を上下方向に区分して印刷回路基板に実装した後、その基板を測定用治具(Jig)に装着した。そして、DCパワーサプライ(Power supply)及び信号発生器(function generator)を用いて、測定治具に装着された試料の両端子にDC電圧及び電圧変動を印加した。上記印刷回路基板の真上に設けられたマイクを用いて、アコースティックノイズを測定した。

## 【0139】

表2において、試料1～3は、下部カバー層の厚さB及び上部カバー層の厚さDがほとんど類似したカバー対称構造を有する比較例であり、試料4～13は、上部カバー層の厚さDが下部カバー層の厚さBより厚い構造を有する比較例である。また、試料14～15及び35～37は、下部カバー層の厚さBが上部カバー層の厚さDより厚い構造を有する比較例である。試料16～34は、本発明による実施例である。

## 【0140】

本発明の実施例は、上記上部カバー層53の厚さDがD4μmの範囲を満たすことができる。Dが4μmより短いと、内部電極がセラミック本体12の上面STに露出するという不良が発生する可能性がある。

## 【0141】

10

20

30

40

50

(B + C) / A の値がほとんど 1 に近いと、上記活性層の中心部が上記セラミック本体の中心部から大きく外れないことを意味する。下部カバー層の厚さ B 及び上部カバー層の厚さ D がほとんど類似したカバー対称構造を有する試料 1 ~ 3 の (B + C) / A の値はほとんど 1 である。

【0142】

(B + C) / A の値が 1 より大きいと、上記活性層の中心部が上記セラミック本体の中心部から上部方向に外れていることを意味し、(B + C) / A の値が 1 より小さいと、上記活性層の中心部が上記セラミック本体の中心部から下部方向に外れていることを意味する。

【0143】

まず、上記活性層の中心部が上記セラミック本体の中心部から外れる比率 (B + C) / A が 1.063 (B + C) / A 1.745 の範囲を満たす実施例である試料 16 ~ 34 は、アコースティックノイズが 20 dB 未満に著しく低減されることが分かる。

【0144】

上記活性層の中心部が上記セラミック本体の中心部から外れる比率 (B + C) / A が 1.063 未満である試料 1 ~ 15 は、上記活性層の中心部が上記セラミック本体の中心部からほとんど外れていないか、上記活性層の中心部が上記セラミック本体の中心部から下部方向に外れている構造を有する。また、(B + C) / A が 1.063 未満である試料 1 ~ 15 は、アコースティックノイズが 25 dB ~ 32.5 dB であることから、アコースティックノイズの低減効果がないことが分かる。

10

20

30

40

【0145】

上記活性層の中心部が上記セラミック本体の中心部から外れる比率 (B + C) / A が 1.745 を超過する試料 35 ~ 37 の場合には、目標容量に対する静電容量が低くて容量不良が発生した。表 2 において、容量具現率（即ち、目標容量に対する静電容量の比率）が「NG」である場合とは、目標容量値を 100 % とするとき、目標容量に対する静電容量の値が 80 % 未満であることを意味する。

【0146】

また、上記上部カバー層の厚さ D と下部カバー層の厚さ B との比率 D / B が 0.021 D / B 0.422 の範囲を満たす実施例は、アコースティックノイズが著しく低減されることが分かる。

30

【0147】

上記上部カバー層の厚さ D と下部カバー層の厚さ B との比率 D / B が 0.422 以上である比較例は、アコースティックノイズの低減効果がないことを確認できる。上記上部カバー層の厚さ D と下部カバー層の厚さ B との比率 D / B が 0.021 未満である場合には、上記上部カバー層の厚さ D に比べて下部カバー層の厚さ B が大きすぎてクラックまたはデラミネーションが発生する可能性があり、目標容量に対する静電容量が低くて容量不良が発生する恐れもある。

【0148】

実施例において、上記セラミック本体の厚さ A に対する上記下部カバー層の厚 B の比率 B / A と上記下部カバー層の厚さ B に対する活性層の厚さ C の比率 C / B それぞれが 0.329 B / A 1.522 及び 0.146 C / B 2.458 の範囲を満たす実施例である試料 19 ~ 34 は、アコースティックノイズが 18 dB 未満とさらに著しく低減されることが分かる。

【0149】

上記セラミック本体の厚さ A に対する上記下部カバー層の厚さ B の比率 B / A が 1.522 を超過するか、上記下部カバー層の厚さ B に対する活性層の厚さ C の比率 C / B が 0.146 未満である試料 35 ~ 37 の場合は、目標容量に対する静電容量が低くて容量不良が発生する。

【符号の説明】

【0150】

50

- 10 積層チップキャパシタ

42、44 第1及び第2外部電極

20 内部電極

50 誘電体層

53 上部カバー層

55 下部カバー層

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図8 a】

【図7】

【図8 b】

【図 9】

【図 10】

## フロントページの続き

|              |               |            |

|--------------|---------------|------------|

| (51) Int.CI. | F I           | テーマコード(参考) |

|              | H 0 1 G 13/00 | 3 2 1 J    |

|              | H 0 1 G 13/00 | 3 2 1 D    |

(72)発明者 キム・ウ・スブ

大韓民国、キョンギ - ド、スウォン、ヨントン - グ、マエタン3 - ドン 314、サムソン エレクトロ - メカニックス カンパニーリミテッド

(72)発明者 キム・トン・グン

大韓民国、キョンギ - ド、スウォン、ヨントン - グ、マエタン3 - ドン 314、サムソン エレクトロ - メカニックス カンパニーリミテッド

(72)発明者 キム・キョン・ジュン

大韓民国、キョンギ - ド、スウォン、ヨントン - グ、マエタン3 - ドン 314、サムソン エレクトロ - メカニックス カンパニーリミテッド

(72)発明者 イ・キュ・ホ

大韓民国、キョンギ - ド、スウォン、ヨントン - グ、マエタン3 - ドン 314、サムソン エレクトロ - メカニックス カンパニーリミテッド

F ターム(参考) 5E001 AB03 AD03 AE01 AE02 AE03 AE04 AG02

5E082 AA01 AB03 BC38 BC40 EE04 EE23 FF05 FG04 FG26 FG46

GG10 HH22 PP09