(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6298249号

(P6298249)

(45) 発行日 平成30年3月20日(2018.3.20)

(24) 登録日 平成30年3月2日(2018.3.2)

(51) Int.Cl.

F 1

G 11 C 16/14 (2006.01)

G 11 C 11/56 (2006.01)G 11 C 16/14 100

G 11 C 11/56 215

請求項の数 10 (全 25 頁)

(21) 出願番号 特願2013-144492 (P2013-144492)

(22) 出願日 平成25年7月10日 (2013.7.10)

(65) 公開番号 特開2014-22031 (P2014-22031A)

(43) 公開日 平成26年2月3日 (2014.2.3)

審査請求日 平成28年6月29日 (2016.6.29)

(31) 優先権主張番号 10-2012-0075596

(32) 優先日 平成24年7月11日 (2012.7.11)

(33) 優先権主張国 韓国 (KR)

前置審査

(73) 特許権者 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区三星路 129

129, Samsung-ro, Yeon

gton-gu, Suwon-si, G

yeonggi-do, Republic

of Korea

(74) 代理人 110000051

特許業務法人共生国際特許事務所

(72) 発明者 吳 銀 珠

大韓民国京畿道華城市盤松洞 ナルマウル

ワールドメリディアンアパート 652 棟 7

04号

最終頁に続く

(54) 【発明の名称】不揮発性メモリ装置とそれを含むメモリシステム及びそれらのメモリブロック管理、消去、及びプログラム方法

## (57) 【特許請求の範囲】

## 【請求項 1】

不揮発性メモリ装置の消去方法において、

消去モードを設定する段階と、

前記設定された消去モードにしたがって正常消去動作及び緊急消去動作の中でいずれか

1つを実行する段階と、を含み、

前記正常消去動作は、メモリブロックに含まれるメモリセルの閾値電圧を第1消去検証

レベルより低い消去状態にセットし、

前記緊急消去動作は、前記メモリブロックに含まれるメモリセルの閾値電圧を第2消去

検証レベルより低い擬似消去状態にセットし、

前記第2消去検証レベルは前記第1消去検証レベルより高く、

ここで前記緊急消去動作は、消去動作、プログラム動作、又は読み出し動作のいずれかの

成功率に基づいて選択され、

前記緊急消去動作を実行する時、前記第2消去検証レベルに対応する緊急消去マージン

を前記成功率に基づいて決定する段階をさらに含む消去方法。

## 【請求項 2】

前記消去モードは外部から入力された命令に応答して設定される請求項1に記載の消去

方法。

## 【請求項 3】

前記消去モードは前記不揮発性メモリ装置の使用者により設定される請求項1に記載の

消去方法。

【請求項 4】

前記正常消去動作は増加形ステップパルス消去方式による複数のサイクルを実行する請求項 1 に記載の消去方法。

【請求項 5】

前記複数のサイクルの各々は、

消去されるメモリブロックのワードラインにバイアスを設定する段階と、

消去されるメモリブロックのビットライン及び消去されないワードラインをフローティングさせるバイアスの設定段階と、

前記メモリブロックのウェルへ消去電圧を印加する実行段階と、

前記ビットラインの電圧、前記ワードラインの電圧、及び前記ウェルの電圧を放電するリカバリ段階と、

前記メモリブロックのメモリセルの閾値電圧が前記消去状態に存在するか否かを判別する検証段階と、を含む請求項 4 に記載の消去方法。

【請求項 6】

前記緊急消去動作は、前記複数のサイクル全てにおいて、前記複数のサイクルの中で一部のサイクルにおいて、或いは前記複数のサイクルの中でいずれか 1 つのサイクルにおいて、前記実行段階を実行する請求項 5 に記載の消去方法。

【請求項 7】

前記緊急消去動作は、前記正常消去動作の前記消去電圧より低いレベルを有する消去電圧を印加し、前記複数のサイクルにおいて、前記複数のサイクルの中で一部のサイクルにおいて、或いは前記複数のサイクルの中でいずれか 1 つのサイクルにおいて、前記実行段階を実行する請求項 5 に記載の消去方法。

【請求項 8】

前記緊急消去動作は、前記複数のサイクル各々の区間より短い区間を有する少なくとも 1 つのサイクル、或いは前記少なくとも 1 つのサイクルの一部を実行する請求項 5 に記載の消去方法。

【請求項 9】

前記緊急消去動作は、前記正常消去動作の前記消去電圧より低いレベルを有する消去電圧を印加し、前記複数のサイクル各々の区間より短い区間を有する少なくとも 1 つのサイクル或いは前記少なくとも 1 つのサイクルの一部を実行する請求項 5 に記載の消去方法。

【請求項 10】

少なくとも 1 つの不揮発性メモリ装置と、

前記少なくとも 1 つの不揮発性メモリ装置を制御するメモリ制御器と、を含み、

前記少なくとも 1 つの不揮発性メモリ装置は、

ページデータをメモリセル当たり 1 - ビットプログラムする複数の第 1 メモリセルを有する第 1 メモリブロックを含む第 1 メモリセルアレイと、

前記第 1 メモリセルアレイの複数のページデータをいずれか 1 つのページにマルチ - ビットプログラムする複数の第 2 メモリセルを有する第 2 メモリブロックを含む第 2 メモリセルアレイと、

前記第 1 メモリブロックを第 1 消去モード及び第 2 消去モードの中のいずれか 1 つで消去し、前記第 2 メモリブロックを前記第 1 消去モードで消去する制御ロジックと、を含み、

前記第 1 消去モードは前記第 1 メモリセル或いは前記第 2 メモリセルを消去状態にセットし、

前記第 2 消去モードは前記第 1 メモリセルを擬似消去状態にセットし、

前記消去状態は第 1 消去検証レベルより低く、

前記擬似消去状態は第 2 消去検証レベルより低く、

前記第 2 消去検証レベルは前記第 1 消去検証レベルより高く、

前記第 1 及び第 2 消去モードは前記第 1 及び第 2 メモリブロックの状態にしたがって決

10

20

30

40

50

定され、

ここで前記第2消去モードは前記第1メモリブロックの消去動作、プログラム動作、又は読み出し動作のいずれかの成功率に基づいて選択され、前記第1メモリセルの各々は前記消去状態又は前記擬似消去状態に基づいて1-ビットプログラムされるメモリシステム。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は不揮発性メモリ装置とそれを含むメモリシステム及びそれらのメモリブロック管理、消去、プログラム方法に関する。 10

【背景技術】

【0002】

半導体メモリ装置は大きく揮発性半導体メモリ装置と不揮発性半導体メモリ装置とに分けられる。不揮発性半導体メモリ装置は電源が遮断されてもデータを保存できる。不揮発性メモリに格納されるデータはメモリ製造技術によって、永久的であるか、或いは再プログラムできる。不揮発性半導体メモリ装置はコンピュータ、航空電子工学、通信、及び消費者電子技術産業のような広い範囲の応用で使用者データの格納、プログラム及びマイクロコードの格納のために使用される。

【先行技術文献】

20

【特許文献】

【0003】

【特許文献1】米国特許公開第2012/268、988号公報

【特許文献2】米国特許第7、802、054号公報

【特許文献3】米国特許第8、027、194号公報

【特許文献4】米国特許第8、122、193号公報

【特許文献5】米国特許公開第2007/0、106、836号公報

【特許文献6】米国特許公開第2010/0、082、890号公報

【特許文献7】米国特許第8、274、840号公報

【発明の概要】

30

【発明が解決しようとする課題】

【0004】

本発明の目的は、より速い消去動作を実行する不揮発性メモリ装置及びそれを含むメモリシステムを提供することにある。

本発明の更に他の目的は、より速いプログラム動作を実行する不揮発性メモリ装置及びそれを含むメモリシステムを提供することにある。

【課題を解決するための手段】

【0005】

本発明の実施形態による不揮発性メモリ装置の消去方法は、消去モードを設定する段階と、前記設定された消去モードにしたがって正常消去動作及び緊急消去動作の中でいずれか1つを実行する段階と、を含み、前記正常消去動作はメモリセルの閾値電圧を第1消去検証レベルより低い消去状態にセットし、前記緊急消去動作はメモリセルの閾値電圧を第2消去検証レベルより低い擬似消去状態にセットする。 40

【0006】

本発明の実施形態による複数のメモリブロックを有する少なくとも1つの不揮発性メモリ装置及び前記少なくとも1つの不揮発性メモリ装置を制御するメモリ制御器を含むメモリシステムのブロック管理方法は、メモリブロックにM(Mは自然数)-ビットプログラム動作を実行する段階と、前記M-ビットプログラム動作以後に前記メモリブロックに消去動作が必要である時、前記メモリブロックのメモリセルの閾値電圧を擬似消去状態にセットする緊急消去動作を実行する段階と、前記メモリブロックに前記擬似消去状態を利用

50

するN（Nは正の整数）-ビットプログラム動作を実行する段階と、前記N-ビットプログラム動作以後に前記メモリブロックに消去動作が必要である時、前記メモリブロックのメモリセルの閾値電圧を消去状態にセットする正常消去動作を実行する段階と、を含み、前記消去状態は第1消去検証レベルより低く、前記擬似消去状態は第2消去検証レベルより低く、前記第2消去検証レベルは前記第1消去検証レベルより高い。

【0007】

本発明の実施形態による不揮発性メモリ装置及び前記不揮発性メモリ装置を制御するメモリ制御器を含むメモリシステムのプログラム方法は、データ及びアドレスが入力される段階と、消去動作が必要であるか否かを判別する段階と、前記消去動作が必要である時、緊急消去動作が必要であるか否かを判別する段階と、前記緊急消去動作が必要である時擬似消去状態にセットする前記緊急消去動作を実行する段階と、前記緊急消去動作が必要でない時、消去状態にセットする正常消去動作を実行する段階と、前記消去動作の以後に前記入力されたデータに対して前記アドレスに対応する前記不揮発性メモリ装置のメモリブロックにプログラム動作を実行する段階と、を含み、前記消去状態は第1消去検証レベルより低く、前記擬似消去状態は第2消去検証レベルより低く、前記第2消去検証レベルは前記第1消去検証レベルより高い。

10

【0008】

本発明の実施形態によるメモリシステムは、少なくとも1つの不揮発性メモリ装置と、前記少なくとも1つの不揮発性メモリ装置を制御するメモリ制御器と、を含み、前記少なくとも1つの不揮発性メモリ装置は、ページデータをメモリセル当たり1-ビットプログラムする複数の第1メモリセルを有する第1メモリブロックを含む第1メモリセルアレイと、前記第1メモリセルアレイの複数のページデータをいずれか1つのページにマルチ-ビットプログラムする複数の第2メモリセルを有する第2メモリブロックを含む第2メモリセルアレイと、前記第1メモリブロックを第1消去モード及び第2消去モードの中のいずれか1つで消去し、前記第2メモリブロックを前記第1消去モードで消去する制御ロジックと、を含み、前記第1消去モードは前記第1メモリセル或いは前記第2メモリセルを消去状態にセットし、前記第2消去モードは前記第1メモリセルを擬似消去状態にセットし、前記消去状態は第1消去検証レベルより低く、前記擬似消去状態は第2消去検証レベルより低く、前記第2消去検証レベルは前記第1消去検証レベルより高い。

20

【発明の効果】

30

【0009】

上述したように本発明による不揮発性メモリ装置及びそれを含むメモリシステムは、設定された消去モードにしたがって、正常消去動作及び緊急消去動作の中でいずれか1つを実行できる。

【図面の簡単な説明】

【0010】

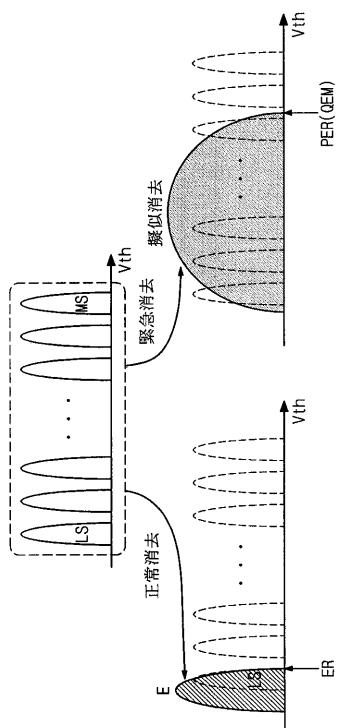

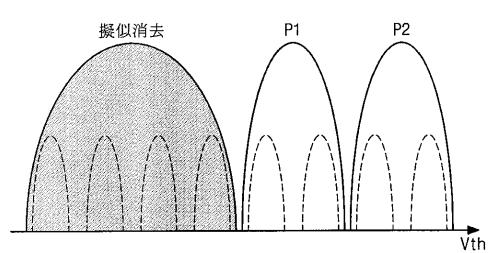

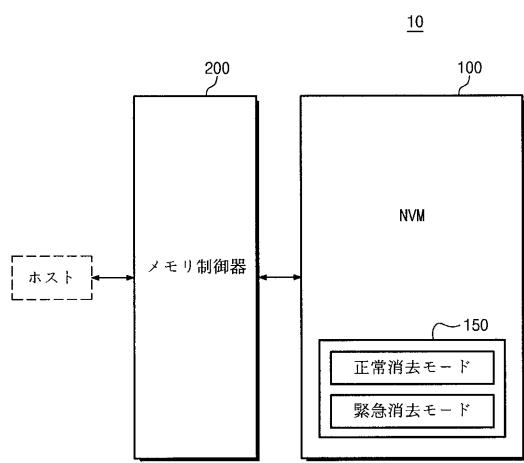

【図1】本発明の概念を説明するための図。

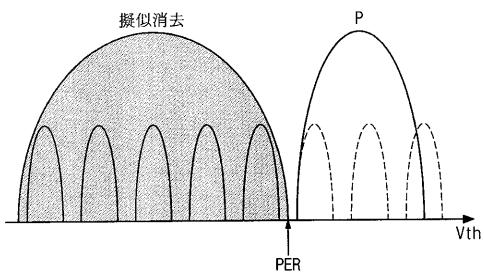

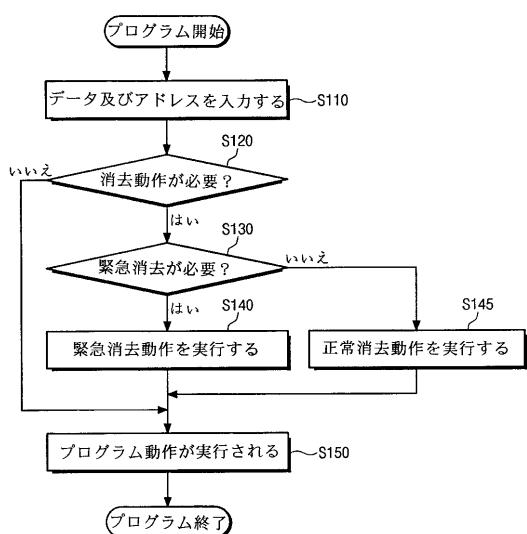

【図2】擬似消去状態（Pseudo E）を利用するプログラム動作に対する第1実施形態を示す図。

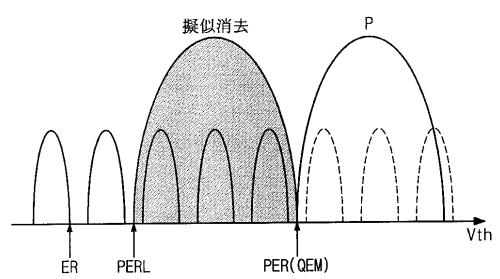

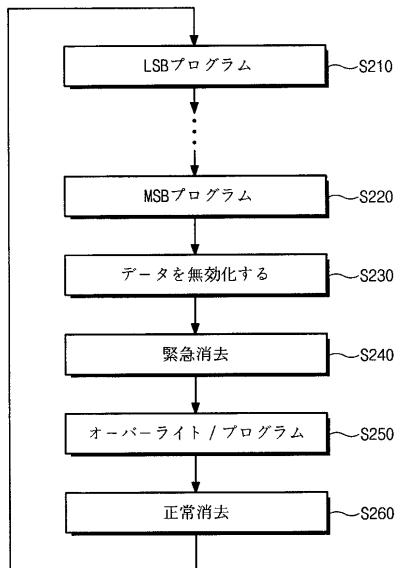

【図3】擬似消去状態（Pseudo E）を利用するプログラム動作に対する第2実施形態を示す図。

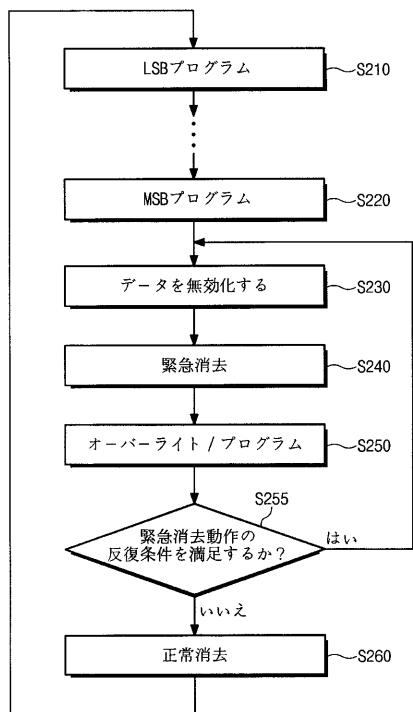

40

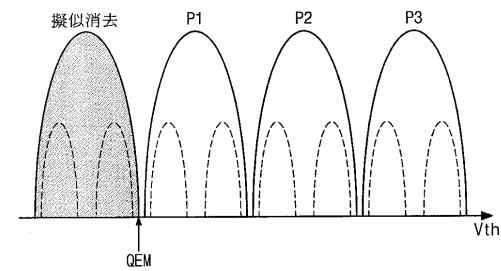

【図4】擬似消去状態（Pseudo E）を利用するプログラム動作に対する第3実施形態を示す図。

【図5】擬似消去状態（Pseudo E）を利用するプログラム動作に対する第4実施形態を示す図。

【図6】本発明の擬似消去状態（Pseudo E）を利用するプログラム動作に対する第5実施形態を示す図。

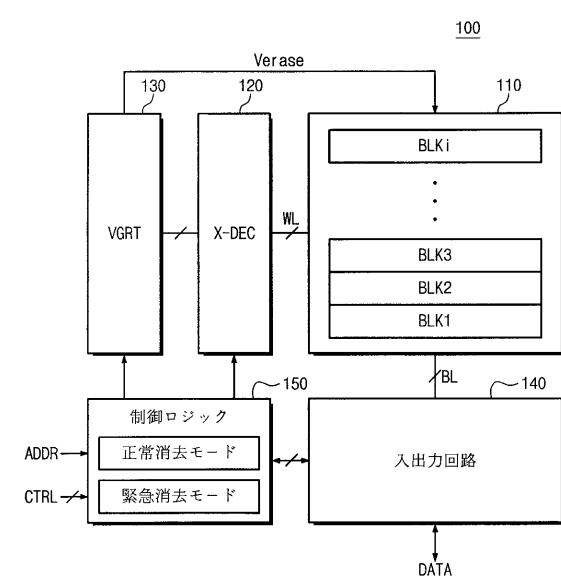

【図7】本発明の実施形態による不揮発性メモリ装置を例示的に示すブロック図。

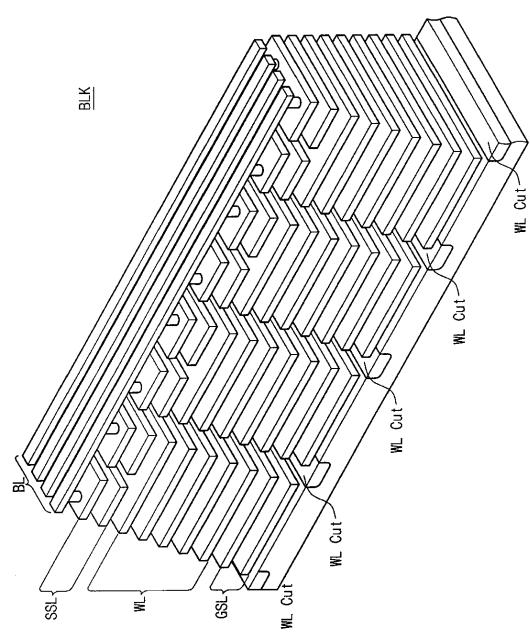

【図8】図7に図示されたメモリブロックBLK1～BLKiの中でのいずれか1つのブロックBLKを例示的に示す図。

50

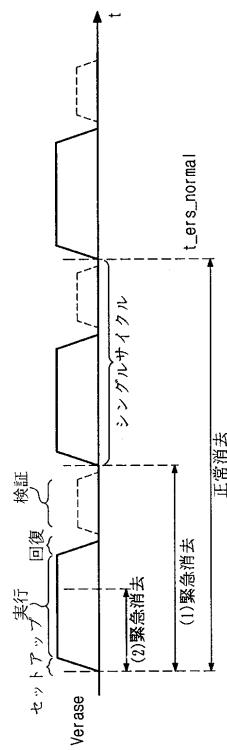

【図9】本発明の実施形態による緊急消去方法に対する第1実施形態を示すタイミング図。

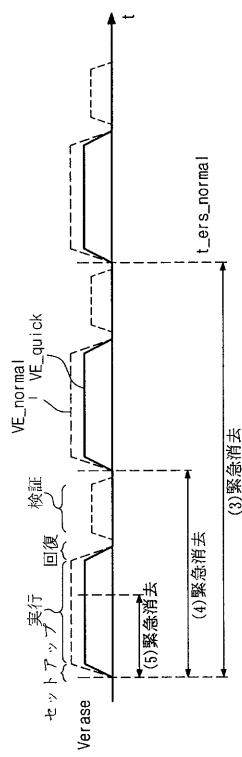

【図10】本発明の実施形態による緊急消去方法に対する第2実施形態を示すタイミング図。

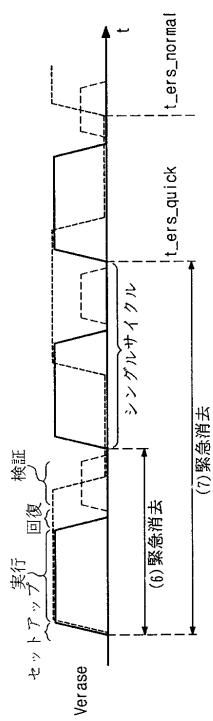

【図11】本発明の実施形態による緊急消去方法に対する第3実施形態を示すタイミング図。

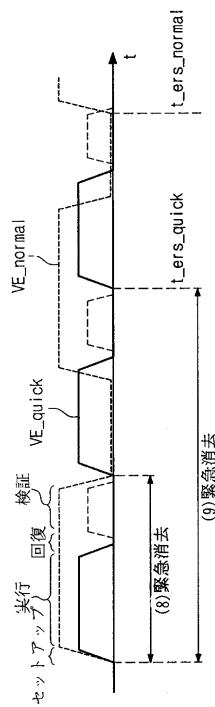

【図12】本発明の実施形態による緊急消去方法に対する第4実施形態を示すタイミング図。

【図13】本発明の実施形態によるメモリシステムを示すロック図。

【図14】本発明の実施形態によるメモリシステムのプログラム方法を例示的に示すフローチャート。 10

【図15】本発明の実施形態によるメモリシステムのロック管理方法に対する第1実施形態を示す図。

【図16】本発明の実施形態によるメモリシステムのロック管理方法に対する第2実施形態を示す図。

【図17】本発明の実施形態によるメモリシステムのロック管理方法に対する第3実施形態を示す図。

【図18】本発明の実施形態によるO B Pを使用するメモリシステムを例示的に示すロック図。 20

【図19】図18に図示されたシングルレベルセル領域のメモリブロックの閾値電圧変化過程を例示的に示す図。

【図20】図18に図示されたメモリシステム20のメモリブロック管理方法を例示的に示す図。

【図21】本発明のその他の実施形態によるO B Pを使用するメモリシステムを例示的に示すロック図。

【図22】本発明の実施形態によるメモリシステムの書き込み動作を例示的に示すフローチャート。

【図23】応用例を示す図。

【図24】応用例を示す図。

【図25】応用例を示す図。 30

【図26】応用例を示す図。

【図27】応用例を示す図。

【図28】応用例を示す図。

【発明を実施するための形態】

【0011】

以下、本発明が属する技術分野で通常の知識を有する者が本発明の技術的思想を容易に実施できるように、本発明の実施形態を添付された図面を参照して説明する。

【0012】

図1は本発明の概念を説明するための図である。図1を参照すれば、プログラム動作によってメモリセルは複数の閾値電圧状態、即ち、最下位状態 (l e a s t s t a t e ; L S ) から最上位状態 (m o s t s t a t e ; M S ) の中でいずれか1つの閾値電圧分布を有する。以後、メモリセルに次のプログラム動作が要求される時、正常消去 (n o r m a l e r a s e ) 動作及び緊急消去 (q u i c k / w e a k / l i g h t / P s u e d o / r o u g h e r a s e ) 動作の中でいずれか1つが選択的に実行できる。 40

【0013】

正常消去動作はプログラムされた状態を最下位状態 L S 或いはそれ以下の閾値電圧を有する消去状態 E にセットする。例えば、正常消去動作はメモリセルの閾値電圧を第1消去検証レベル E R より大きくなないようにする。ここで、第1消去検証レベル E R は最下位状態 L S を検証するレベルであり得る。

緊急消去動作はプログラム状態を第2消去検証レベル P E R より大きくなれない閾値電圧を 50

有する擬似消去状態 (P s u e d o E) にセットする。ここで、第 2 消去検証レベル P E R は第 1 消去検証レベル E R より大きい。第 2 消去検証レベル P E R は緊急消去マージン (quick erase margin; Q E M) と称され得る。ここで、緊急消去マージン Q E M は、緊急消去動作以後に格納できるプログラム状態の個数を多くするか、或いは上書き (o v e r w r i t e) をする場合、データの信頼性を向上させるために調節可能である。

【0014】

本発明はメモリセルの閾値電圧を擬似消去状態 (P s u e d o E) にセットする緊急消去動作を実行するか、或いは消去状態 E にセットする正常消去動作を実行することができる。

10

図 2 は擬似消去状態 (P s u e d o E) を利用するプログラム動作に対する第 1 実施形態を示す図である。説明を簡単にするために、以前に 8 つの状態が存在する 3 - ビットプログラム動作が実行されたと仮定する。

緊急消去動作によって、メモリセルは次のプログラム動作のための擬似消去状態 (P s u e d o E) になる。以後、擬似消去状態 (P s u e d o E) を利用する 1 - ビットプログラム動作が実行される。即ち、メモリセルは擬似消去状態 (P s u e d o E) 及びプログラム状態 P の中でいずれか 1 つにプログラムされる。ここで、プログラム状態 P は第 2 消去検証レベル P E R より高い閾値電圧分布を有する。

【0015】

本発明は擬似消去状態 (P s u e d o E) を利用して 1 - ビットプログラム動作を実行できる。

20

図 2 で擬似消去状態 (P s u e d o E) は以前プログラム動作の状態が第 2 消去検証レベル P E R より大きくない閾値電圧分布を有する。しかし、本発明が必ずしもこれに制限される必要はない。本発明の擬似消去状態 (P s u e d o E) はプログラム動作で所定の区間に集まつた閾値電圧分布を有することができる。

【0016】

図 3 は擬似消去状態 (P s u e d o E) を利用するプログラム動作に対する第 2 実施形態を示す図である。図 3 を参照すれば、擬似消去状態 (P s u e d o E) を利用するプログラム動作で、擬似消去状態 (P s u e d o E) は第 2 消去検証レベル P E R より大きくなく、第 3 消去検証レベル P E R L より小さくない閾値電圧を有する。ここで、第 3 消去検証レベル P E R L は第 1 消去検証レベル E R より大きく、第 2 消去検証レベル P E R より小さい。

30

図 2 乃至図 3 は擬似消去状態 (P s u e d o E) を利用して 1 - ビットプログラム動作が実行される例を示す。しかし、本発明が必ずこれに制限される必要はない。本発明は擬似消去状態 (P s u e d o E) を利用して 2 - ビットプログラム動作を実行することができる。このために、緊急消去マージン Q E M は 1 - ビットプログラム動作の時のそれよりさらに低くなる。

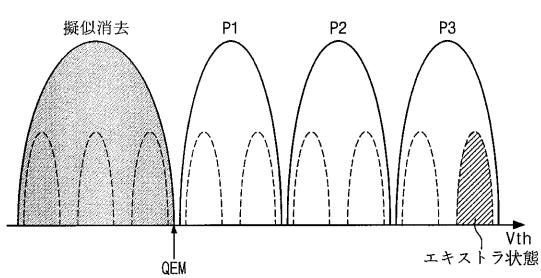

【0017】

図 4 は擬似消去状態 (P s u e d o E) を利用するプログラム動作に対する第 3 実施形態を示す図である。図 4 を参照すれば、擬似消去状態 (P s u e d o E) を利用するプログラム動作でメモリセルは、擬似消去状態 (P s u e d o E)、第 1 プログラム状態 P 1、第 2 プログラム状態 P 2、及び第 3 プログラム状態 P 3 の中でいずれか 1 つにプログラムされる。

40

また、本発明の擬似消去状態 (P s u e d o E) を利用するプログラム動作はエキストラ状態 (extra state) を利用することもあり得る。ここで、エキストラ状態は以前プログラム動作で利用されなかった状態として、以前プログラム動作のプログラム状態より高い状態である。一方、エキストラ状態に対する詳細は、この出願の先行技術文献として記載された特許文献 1 で説明される。

【0018】

図 5 は擬似消去状態 (P s u e d o E) を利用するプログラム動作に対する第 4 実施

50

形態を示す図である。図5を参照すれば、擬似消去状態 (Psuedo E) を利用するプログラム動作でメモリセルは、擬似消去状態 (Psuedo E) 、第1プログラム状態 P1、第2プログラム状態 P2、及び第3プログラム状態 P3 の中でいずれか1つにプログラムされる。ここで、第3プログラム状態 P3 はエキストラ状態を含む。

図5では1つのエキストラ状態が第3プログラム状態に包含されるが、本発明はこれに制限されない。本発明の擬似消去状態 (Psuedo E) を利用するプログラム動作は少なくとも1つのエキストラ状態が少なくとも1つのプログラム状態に包含され得る。

#### 【0019】

また、本発明の擬似消去状態 (Psuedo E) を利用するプログラム動作は多次元変調方式 (multi dimension modulation scheme) のプログラム動作にも適用可能である。ここで、多次元変調方式は、格納されるデータ値をエンコーディングして連続した所定の個数のメモリセルにプログラムすることを言う。一方、多次元変調方式に対する詳細は本出願の出願人である三星電子から出願され、この出願の先行技術文献として記載された特許文献1で説明される。

#### 【0020】

図6は本発明の擬似消去状態 (Psuedo E) を利用するプログラム動作に対する第5実施形態を示す図である。図6を参照すれば、擬似消去状態 (Psuedo E) を利用するプログラム動作でメモリセルは、多次元変調方式にしたがって擬似消去状態 (Psuedo E) 、第1プログラム状態 P1、及び第2プログラム状態 P2 の中でいずれか1つにプログラムされる。

10

20

#### 【0021】

図7は本発明の実施形態による不揮発性メモリ装置100を例示的に示すブロック図である。図7を参照すれば、不揮発性メモリ装置100はメモリセルアレイ110、アドレスコード120、電圧発生回路130、入出力回路140、及び制御ロジック150を含む。

20

#### 【0022】

本発明による不揮発性メモリ装置はNANDフラッシュメモリ (NAND Flash Memory)、垂直形NANDフラッシュメモリ (Vertical NAND、以下、「VNAND」と称する)、NORフラッシュメモリ (NOR Flash Memory)、抵抗性RAM (Resistive Random Access Memory : RRAM (登録商標))、相変化メモリ (Phase-Change Memory : PRAM)、磁気抵抗メモリ (Magnetoresistive Random Access Memory : MRAM)、強誘電体メモリ (Ferroelectric Random Access Memory : FRAM (登録商標))、スピノ注入磁化反転メモリ (Spin Transfer Torque Random Access Memory : STT-RAM) 等であり得る。また、本発明の不揮発性メモリ装置100は3次元アレイ構造 (three-dimensional array structure) で具現され得る。本発明の不揮発性メモリ装置100は電荷格納層が伝導性浮遊ゲートで構成されたフラッシュメモリ装置を含めて、電荷格納層が絶縁膜で構成されたチャージトラップ形フラッシュ (charge trap flash ; CTF) にも全て適用できる。

30

40

#### 【0023】

メモリセルアレイ110は複数のメモリブロック (BLK1 ~ BLKi、iは1より大きい整数) を含む。メモリブロックの各々は、ビットラインBLの各々に連結されたストリングを含む。ここで、ストリングは少なくとも1つのストリング選択トランジスタ、複数のメモリセル、少なくとも1つの接地選択トランジスタを含む。ストリング選択トランジスタはストリング選択ラインを通じて伝送される電圧によって駆動される。接地選択トランジスタは接地選択ラインを通じて伝送される電圧によって駆動される。メモリセルの各々は少なくとも1つのビットのデータを格納し、対応するワードラインWLへ伝送される電圧によって駆動される。

50

## 【0024】

アドレスデコーダ120はアドレスに応答して複数のメモリブロックの中でいずれか1つを選択し、駆動に必要であるワードライン電圧（例えば、プログラム電圧、バス電圧、消去電圧、検証電圧、読み出し電圧、読み出しバス電圧等）を対応するワードラインへ伝送する。

電圧発生回路130は駆動に必要であるワードライン電圧を発生する。電圧発生回路130は高電圧発生器、低電圧発生器、及び／或いは負電圧発生器を含む。また、電圧発生回路130は消去動作のための消去電圧V<sub>erase</sub>を発生する。消去電圧V<sub>erase</sub>はメモリブロックB<sub>L</sub>K<sub>1</sub>～B<sub>L</sub>K<sub>i</sub>の中で選択されたブロックのウェルへ印加される。

入出力回路140はプログラム動作で外部から入力されたデータを臨時に格納した後に、選択されたページにプログラムし、読み出し動作で読み出されるページからデータを読み出して臨時に格納した後に外部へ出力する。入出力回路140はビットラインB<sub>L</sub>の各々に対応するページバッファを含む。

## 【0025】

制御ロジック150は不揮発性メモリ装置100の全般的な動作を制御する。制御ロジック150は外部のメモリ制御器から提供される制御信号及び命令語を解釈し、解釈結果に応答してアドレスデコーダ120、電圧発生回路130及び入出力回路140を制御する。即ち、制御ロジック150は、駆動（例えば、プログラム／読み出し／消去動作）に必要である電圧を発生するように電圧発生回路130を制御し、発生された電圧を対応するワードラインW<sub>L</sub>へ伝送するようにアドレスデコーダ120を制御し、プログラムされるページデータ及び読み出されたページデータを入出力するために入出力回路140を制御する。

## 【0026】

また、制御ロジック150は正常消去モード（normal erase mode）にしたがって、消去動作を実行するか、或いは緊急消去モード（quick erase mode）にしたがって消去動作を実行する。正常消去モードではメモリセルの閾値電圧を消去状態Eにセットする。ここで、消去状態Eは最下位状態（図1参照、LS）或いはそれ以下である。また、緊急消去モードではメモリセルの閾値電圧を擬似消去状態（Pseudo E）にセットする。ここで、擬似消去状態（Pseudo E）は最上位状態（図1参照、MS）以下であり、第2消去検証レベル（図1参照、PER）以下である。

実施形態において、正常消去モード及び緊急消去モードの選択は外部のメモリ制御器から入力された消去モード選択命令によって決定され得る。他の実施形態において、正常消去モード及び緊急消去モードの選択は、不揮発性メモリ装置100で内部的に決定され得る。その他の実施形態において、正常消去モード及び緊急消去モードの選択は、製造者によって固定され得る。

## 【0027】

本発明の不揮発性メモリ装置100では必要に応じて正常消去モード及び緊急消去モードの中のいずれか1つで消去動作を実行できる。

図8は図7に図示されたメモリブロックB<sub>L</sub>K<sub>1</sub>～B<sub>L</sub>K<sub>i</sub>の中でいずれか1つのブロックB<sub>L</sub>Kを例示的に示す図である。図8に図示されたメモリブロックB<sub>L</sub>Kは基板上に垂直方向に形成される。図8を参照すれば、基板上に複数のワードラインカットの間には少なくとも1つの接地ストリングラインG<sub>SL</sub>、複数のワードラインW<sub>L</sub>、少なくとも1つのストリング選択ラインS<sub>SL</sub>が積層される。ここで、少なくとも1つのストリング選択ラインS<sub>SL</sub>はストリング選択ラインカットによって分離される。複数のピラーが少なくとも1つの接地ストリングライン基板G<sub>SL</sub>、複数のワードラインW<sub>L</sub>、少なくとも1つのストリング選択ラインS<sub>SL</sub>を貫通する。ここで、少なくとも1つの接地ストリングラインG<sub>SL</sub>、複数のワードラインW<sub>L</sub>、少なくとも1つのストリング選択ラインS<sub>SL</sub>は基板形態に具現される。また、複数のピラーの上部面には複数のビットラインB<sub>L</sub>が連結される。図8でメモリブロックはワードライン併合構造であるが、本発明がこれに制限

10

20

30

40

50

される必要はない。

【0028】

一般的に3次元メモリ装置、電荷トラップフラッシュメモリ装置、或いはV N A N Dでは物性的/構造的特性のため、消去動作の時間（以下、消去時間）が長い。例えば、V N A N Dは大きいブロック/サブブロック単位に消去動作を実行するので、プラナメモリ装置と比較して長い消去時間を有する。このような長い消去時間は長くなった応答時間（r e s p o n s e t i m e）によって、システム性能（s y s t e m p e r f o r m a n c e）を低下させ得る。例えば、書き込み動作の中で消去動作が実行される場合、長い消去時間のため、書き込み動作の応答時間がタイムアウト（t i m e - o u t）される可能性がある。

10

一方、本発明の不揮発性メモリ装置は、正常消去モード及び緊急消去モードの中のいずれか1つを選択して消去動作を実行できる。従って、本発明の不揮発性メモリ装置は応答時間が長くなることが予想される場合には緊急消去モードを通じて消去動作を実行することによって、消去時間を減少させ得る。その結果として、書き込み動作の応答時間がタイムアウトされる可能性が減る。

【0029】

本発明による不揮発性メモリ装置の緊急消去方法は正常消去動作で時間（或いは、サイクル）を変更することによって、具現され得る。

図9は本発明の実施形態による緊急消去方法に対する第1実施形態を示すタイミング図である。説明を簡単にするために図9では正常消去動作は2つのサイクルで構成されたとする。各サイクルはセットアップ区間、実行区間、回復区間、検証区間に区分される。実線はウェルへ印加される電圧、点線はワードラインへ印加される電圧を示す。図9を参照すれば、正常消去動作は2つのサイクルで構成され、セットアップ区間では消去動作のためにワードラインは接地電圧に、ビットラインとソースラインはフローティングされ、実行区間ではウェルへ消去電圧V e r a s eが印加され、回復区間ではウェル電圧とビットライン電圧が放電され、検証区間では消去動作が正しく実行されたか否かを判別するために第1検証レベル（図1参照、E R）で検証読み出し動作が実行される。図9に図示しないが、サイクルが増加することによって、消去電圧V e r a s eは増加され得る。

20

【0030】

実施形態において、緊急消去動作は正常消去動作の中で一部サイクル（例えば、1つのサイクル）を実行する（(1)）。

30

他の実施形態において、緊急消去動作は正常消去動作の1つのサイクルの中で一部であり得る（(2)）。

整理すれば、本発明の緊急消去動作は、正常消去動作でサイクルの中で一部であるか、或いはいずれか1つのサイクルの一部であり得る。即ち、緊急消去動作は、正常消去動作の消去時間t \_ e r s \_ n o r m a lより短い時間t \_ e r s \_ q u i c kの間に消去電圧V e r a s eをウェルへ印加することによって実行することができる。

【0031】

本発明の緊急消去方法は正常消去動作で消去電圧V e r a s eのレベルを変更することによって具現され得る。

40

図10は本発明の実施形態による緊急消去方法に対する第2実施形態を示すタイミング図である。図10を参照すれば、緊急消去方法は、正常消去動作のレベルV E \_ n o r m a lより低いレベルV E \_ q u i c kを有する消去電圧V e r a s eを印加する。

実施形態において、緊急消去動作は低いレベルV E \_ q u i c kを有する消去電圧V e r a s eを印加し、正常消去動作のようにすべてのサイクルを実行することであり得る（(3)）。

他の実施形態において、緊急消去動作は低いレベルV E \_ q u i c kを有する消去電圧V e r a s eを印加し、一部サイクルを実行することであり得る（(4)）。

他の実施形態において、緊急消去動作は低いレベルV E \_ q u i c kを有する消去電圧V e r a s eを印加し、1つのサイクルの中で一部を実行することであり得る（(5)）。

50

## 【0032】

本発明の緊急消去方法は正常消去動作で消去電圧  $V_{erase}$  が印加される実行区間を減らすことによって具現され得る。

図 11 は本発明の実施形態による緊急消去方法に対する第 3 実施形態を示すタイミング図である。図 11 を参照すれば、緊急消去方法は、図 9 に図示された緊急消去方法と比較して消去電圧  $V_{erase}$  を印加する実行区間を減らす。即ち、緊急消去動作の 1 つのサイクルは正常消去動作の 1 つのサイクルより短い。

実施形態において、緊急消去動作は正常消去動作のように同一の回数のサイクルを実行する (6)。

他の実施形態において、緊急消去動作は正常消去動作のサイクル回数より少ない回数のサイクルを実行する (7)。

## 【0033】

本発明の緊急消去方法は、正常消去動作と比較して消去電圧  $V_{erase}$  のレベルを低くしながら、短いサイクルを実行することによって具現される。

図 12 は本発明の実施形態による緊急消去方法に対する第 4 実施形態を示すタイミング図である。図 12 を参照すれば、緊急消去動作は正常消去動作のレベル  $V_{normal}$  と比較して低いレベル  $V_{quick}$  を有する消去電圧  $V_{erase}$  を印加し、正常消去動作のサイクルより短いサイクルを実行する。

実施形態において、緊急消去動作は正常消去動作と同一な回数のサイクルを実行する (8)。

他の実施形態において、緊急消去動作は正常消去動作のサイクル回数より少ない回数のサイクルを実行する (9)。

## 【0034】

図 9 乃至図 12 を参照すれば、本発明による緊急消去動作は、メモリセルを擬似消去状態 (Pseudo E) にセットするために正常消去動作の時間、或いはレベルの多様な組合せによって決定され得る。

図 13 は本発明の実施形態によるメモリシステムを示すブロック図である。図 13 を参照すれば、メモリシステム 10 は少なくとも 1 つの不揮発性メモリ装置 100 及びそれを制御するメモリ制御器 200 を含む。不揮発性メモリ装置 100 は図 7 で説明したのと同一である。メモリ制御器 200 は必要によって、不揮発性メモリ装置 100 の制御ロジック 150 を正常消去モードで動作させるか、或いは緊急消去モードで動作させるかを決定することができる。

## 【0035】

実施形態において、メモリ制御器 200 はホストの書き込み要請に対する応答時間を予測し、予測された結果に基づいて緊急消去モードを選択することができる。例えば、メモリ制御器 200 は書き込み要請の時、応答時間が長くなるマージ動作が必要であると判別される時、すぐに不揮発性メモリ装置 100 を緊急消去モードに動作するよう制御することができる。

実施形態において、メモリ制御器 200 はホストの使用者の要請に応答して緊急消去モードを選択することができる。例えば、使用者がより速い書き込み動作を望む場合には、メモリ制御器 200 はこのようない要請に応答して不揮発性メモリ装置 100 が緊急消去モードで動作するように制御することができる。

図 14 は本発明の実施形態によるメモリシステム 10 のプログラム方法を例示的に示すフローチャートである。図 7 乃至図 14 を参照すれば、プログラム方法は次の通りである。

## 【0036】

メモリシステム 10 には外部のホストから書き込まれるデータ及びアドレス (例えば、論理アドレス) が入力される (S110)。メモリ制御器 200 は消去動作が必要であるか否かを判別する。例えば、データを書き込むプリブロックが存在しない時、データブロックを消去してプリブロックにセットする必要があり、このためにデータブロックに対す

10

20

30

40

50

る消去動作が実行されなければならない。例えば、メモリブロックの間にマージ動作の後、無効データ、或いはガーベッジ (garbage) を有するメモリブロックがプリブロックを必要とする時、消去動作が必要である (S120)。データブロックが消去される必要がなければ、S150段階が進行される。

【0037】

データブロックが消去される必要があれば、メモリ制御器200は緊急消去動作が必要であるか否かを判別する (S130)。もし、緊急消去動作が必要であれば、データブロックに対する緊急消去動作が実行される (S140)。これに対し、緊急消去動作が必要でなければ、データブロックに対する正常消去動作が実行される (S145)。データブロックに対する消去動作が完了した後に、アドレスに対応するメモリブロックに書き込まれるデータを格納するためのプログラム動作が実行される (S150)。したがって、本発明のプログラム動作が完了する。

【0038】

本発明のプログラム方法は、緊急消去動作が必要であるか否かを判別し、その結果にしたがって緊急消去動作を実行することによって、一般的なそれと比較してプログラム動作時間を短縮させ得る。

図15は本発明の実施形態によるメモリシステムのブロック管理方法に対する第1実施形態を示す図である。図15を参照すれば、メモリシステム10のメモリ制御器200は次の順序でメモリブロックを管理する。

【0039】

処女状態のメモリブロックのページに最下位ビット (least significant bit; LSB) プログラム動作が実行される (S210)。以後、最下位ビットプログラムされたページに次のビットプログラム動作が実行され、このような方式で最上位ビット (most significant bit; MSB) プログラム動作が実行される (S220)。図15ではメモリブロックのページに最下位ビット LSB プログラム動作が先ず実行され、最上位ビット MSB プログラム動作が後に実行される。しかし、本発明がこれに制限される必要はない。反対に、メモリブロックのページに最上位ビット MSB プログラム動作が先に実行され、その後、最下位ビット LSB プログラム動作が実行されることもあり得る。

【0040】

図15でマルチビットプログラム動作は1ビットずつ順に実行される。しかし、本発明のマルチビットプログラム動作は必ずしもこれに制限されない。本発明のマルチビットプログラム動作はマルチビットが一度に或いは同時にプログラムされることもある。

メモリブロックの複数のページが上述したようにプログラム動作が実行された後に、メモリブロックに格納されたデータが無効であると判別され得る。例えば、外部のホストに要請にしたがって格納されたデータが無効処理され得る。また、格納されたデータが物理的に他の位置に複写された後に、以前データを無効化処理することができる (S230)。

【0041】

この時、メモリ制御器200は無効化データを格納するメモリブロックに次のプログラム動作を実行するために緊急消去動作を実行する。ここで、緊急消去動作が実行されたメモリブロックに存在するメモリセルは擬似消去状態 (Pseudo E) に位置する (S240)。擬似消去状態 (Pseudo E) を利用してオーバーライト (overwrite) 或いはプログラム動作が実行される (S250)。その後、メモリ制御器200は消去状態 E を利用する正常的なプログラム動作を実行するためにオーバーライト / プログラムされたメモリブロックに対して正常消去動作を実行し、S210段階へ進入する (S260)。

【0042】

本発明によるメモリブロック管理方法は正常消去動作を実行する前に緊急消去動作を実行し、この時、発生した擬似消去状態 (Pseudo E) を利用してオーバーライト /

10

20

30

40

50

プログラム動作を実行できる。

本発明によるメモリブロック管理方法は、いずれか1つのメモリブロックに対する緊急消去動作を反復することもあり得る。

#### 【0043】

図16は本発明の実施形態によるメモリシステムのブロック管理方法に対する第2実施形態を示す図である。図16を参照すれば、メモリブロック管理方法は、図15に図示されたメモリブロック管理方法と比較してS255段階が追加される。

S255段階では、メモリ制御器200はメモリブロックに緊急消去動作を反復するための条件を満足するか否かを判別する。このような反復条件は、メモリブロックに関連した情報であり得る。例えば、反復条件はメモリブロックのプログラム／消去サイクル回数、ブロック消去比率等であり得る。緊急消去動作の反復条件を満足すれば、例えば、プログラム／消去サイクル回数或いはブロック消去比率が所定の値より小さければ、メモリブロックに対する緊急消去動作を反復するためにS230段階へ進入する。

#### 【0044】

実施形態において、消去動作、プログラム動作、或いは読み出し動作が成功的に実行された比率にしたがって、緊急消去動作の可否が決定され得る。例えば、このような比率が所定の値以上である時、緊急消去動作が実行できる。また、このような比率が所定の値以上である時、オーバーライト動作でメモリセル当たり幾つのビットがプログラムされるかが決定され得る。

実施形態において、緊急消去動作が反復される毎に、緊急消去マージンQEMは段々と低くなり得る。他の実施形態において、緊急消去動作が反復される毎に緊急消去マージンQEMは一定であり得る。

一方、緊急消去動作の反復条件を満足しなければ、正常的なプログラム動作のためにS260段階へ进入する。

#### 【0045】

本発明によるメモリブロック管理方法は、メモリブロックの状態にしたがって反復的に緊急消去動作を実行できる。

図15及び図16では正常消去動作の前に緊急消去動作が実行される。しかし、本発明がこれに制限される必要はない。本発明の緊急消去動作は選択的に実行されることもできる。

#### 【0046】

図17は本発明の実施形態によるメモリシステムのブロック管理方法に対する第3実施形態を示す図である。図17を参照すれば、メモリブロックの管理方法は次の通りである。

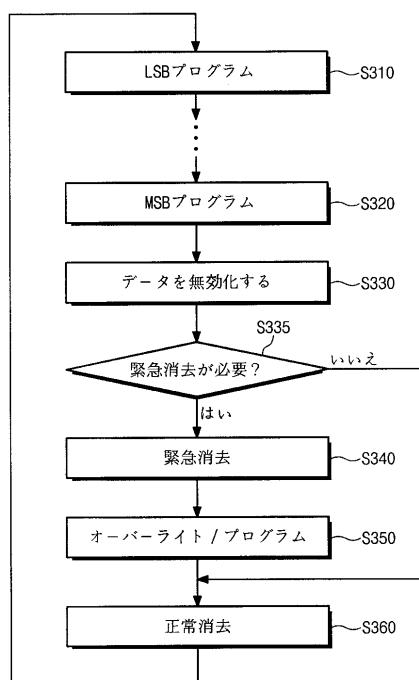

メモリブロックのページに最下位ビットLSBプログラム動作が先に実行され(S310)、以後に最上位ビットMSBプログラム動作が実行される(S320)。メモリブロックの複数のページに上述したようにプログラム動作が実行された後に、メモリブロックに格納されたデータが無効であると判別され得る(S330)。この時、メモリ制御器200は無効化されたデータを格納するメモリブロックに対して緊急消去動作を実行するか否かを判別する(S335)。例えば、ホストの要請が速い消去動作を要求する時、メモリ制御器200は緊急消去動作が実行されるように不揮発性メモリ装置100を制御することができる。

#### 【0047】

もし、緊急消去動作を必要としなければ、S360段階へ进入する。一方、緊急消去動作が必要であれば、無効化データを格納するメモリブロックに次のプログラム動作を実行するために緊急消去動作を実行する。ここで、緊急消去動作が実行されたメモリブロックに存在するメモリセルは擬似消去状態(Pseudoe)に位置する(S340)。例えば、ホストから書き込み要請が入力される時、データを不揮発性メモリ装置100の物理的位置に書き込むまでの時間(以下、書き込み応答時間)が所定の値を超過したと予測される時、メモリ制御器200は緊急消去動作を実行するように不揮発性メモリ装置100を

10

20

30

40

50

制御する。ここで、書き込み応答時間にはマージ動作時間或いは消去時間が含まれる。

【0048】

実施形態において、消去時間は、プリブロックの個数、ブロック消去比率 B E R、プログラム / 消去サイクル、データリテンション時間 (data retention time)、動作温度の中で少なくとも 1 つを利用して予測することができる。ここで、ブロック消去比率 B E R が所定の値以上である時、消去時間が長くなるので、緊急消去動作が実行される。また、ブロック消去比率 B E R が所定の値以上である時、マルチビットオーバーライトが難しいことがあり得るので、オーバーライト動作の時、幾つかのビットにプログラム動作が実行されるかが決定されなければならない。

【0049】

10

以後、擬似消去状態 (pseudo E) を利用してオーバーライト (overwrite) 或いはプログラム動作が実行される (S350)。その後、メモリ制御器 200 は消去状態 E を利用する正常的なプログラム動作を実行するためにメモリブロックに対して正常消去動作を実行し、S310 段階へ進入する (S360)。

本発明のメモリブロック管理方法は予測された書き込み応答時間によって、メモリブロックに緊急消去動作を実行できる。

図 15 乃至図 17 では 1 つの物理ページに複数の論理ページが順次的にプログラムされる場合を開示する。しかし、本発明がこれのみに制限されない。本発明は 1 つの物理ページに複数の論理ページが一度にプログラムされる場合にも適用可能である。即ち、本発明はオンチップバッファプログラム (on-chip buffered program ; 以下、「OBP」) にも適用可能である。

【0050】

20

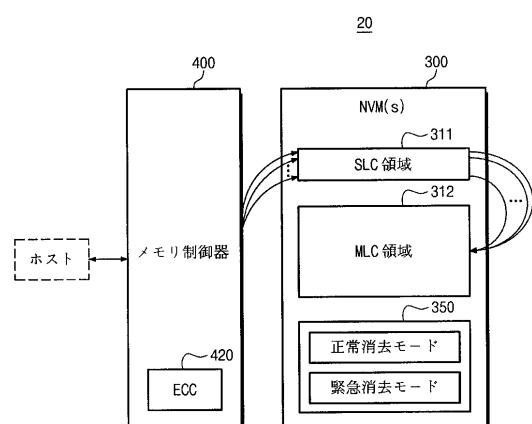

図 18 は本発明の実施形態による OBP を使用するメモリシステムを例示的に示すブロック図である。図 18 を参照すれば、メモリシステム 20 は少なくとも 1 つの不揮発性メモリ装置 300 及びそれを制御するメモリ制御器 400 を含む。

不揮発性メモリ装置 300 はページデータを 1 つのメモリセル当たり 1 - ビットで格納するシングルレベルセル領域 311、シングルレベルセル領域 311 に格納された複数のページデータを 1 つのページに一度に格納する (或いは、メモリセル当たりマルチ - ビットで格納する) マルチレベルセル領域 312、及び制御ロジック 350 を含む。シングルレベルセル領域 311 及びマルチレベルセル領域 312 の各々は複数のメモリブロックを含む。制御ロジック 350 は正常消去動作を実行する正常消去モード及び緊急消去動作を実行する緊急消去モードを有する。メモリ制御器 400 はシングルレベルセル領域 311 に格納されたページデータを読み出し、読み出されたページデータのエラーを訂正するエラー訂正回路 420 を包含することができる。

【0051】

30

本発明のメモリシステム 20 はシングルレベルセル領域 311 のメモリブロックに対して緊急消去動作を実行できる。

他の実施形態において、本発明のメモリシステム 20 はシングルレベルセル領域 311 及びマルチレベルセル領域 312 の中でいずれか 1 つに選択的に正常消去動作或いは緊急消去動作を実行することができる。

40

【0052】

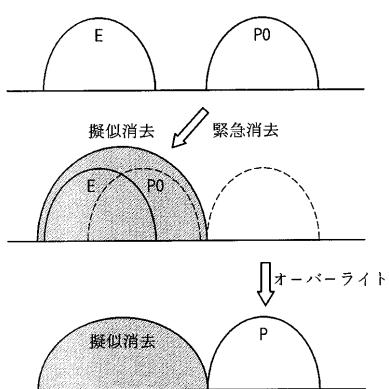

図 19 は図 18 に図示されたシングルレベルセル領域 311 のメモリブロックの閾値電圧変化過程を例示的に示す図である。図 19 を参照すれば、シングルレベルセル領域 311 のメモリブロックの閾値電圧状態変化は次の通りである。

最初に消去状態 E を利用する 1 - ビットプログラム動作が実行される。これによってメモリブロックのメモリセルは消去状態 E とプログラム状態 P0 の中でいずれか 1 つにプログラムされる。以後、メモリブロックに消去動作が必要であれば、緊急消去動作が実行される。図 19 に示したように、以前プログラム動作のプログラム状態 P0 は擬似消去状態 (pseudo E) になるように緊急消去動作を通じてメモリセルの閾値電圧が低くなる。緊急消去動作が実行された後、擬似消去状態 (pseudo E) を利用して 1 - ビ

50

ットプログラム動作が実行される。即ち、メモリブロックのメモリセルは擬似消去状態 (Psuedo E) 或いはプログラム状態 P の中でいずれか 1 つにプログラムされる。

#### 【0053】

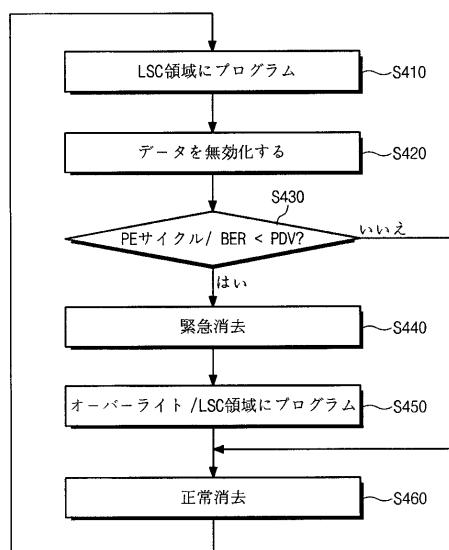

図 20 は図 18 に図示されたメモリシステム 20 のメモリブロック管理方法を例示的に示す図である。図 20 を参照すれば、メモリシステム 20 のメモリブロック管理方法は次の通りである。

優先的に、メモリブロックのシングルレベルセル領域 311 のページにプログラム動作が実行される (S410)。メモリブロックに格納されたデータが無効であると判別され得る (S420)。この時、メモリ制御器 400 は無効化されたデータを格納するメモリブロックのプログラム / 消去サイクル或いはブロック消去比率が所定の値より下であるか否かを判別する (S430)。ここで、プログラム / 消去サイクル或いはブロック消去比率はブロックの状態条件になることができる。一方、ブロックの状態条件は、消去動作、プログラム動作、或いは読み出し動作が成功的に実行された比率であり得る。

#### 【0054】

もし、プログラム / 消去サイクル或いはブロック消去比率が所定の値未満ではない時、S460 段階へ進入する。一方、プログラム / 消去サイクル或いはブロック消去比率が所定の値未満である時、無効化データを格納するメモリブロックに次のプログラム動作を実行するために緊急消去動作を実行する。ここで、緊急消去動作が実行されたメモリブロックに存在するメモリセルは擬似消去状態 (Psuedo E) に位置する (S440)。

#### 【0055】

その後、擬似消去状態 (Psuedo E) を利用してオーバーライト (overwrite) 或いはプログラム動作が実行される (S450)。ここで、オーバーライト或いはプログラム動作はメモリセル当たり 1 - ビットプログラム動作である。以後に、メモリ制御器 400 は消去状態 E を利用する正常的な 1 - ビットプログラム動作を実行するためにメモリブロックに対して正常消去動作を実行し、S410 段階へ进入する (S460)。

#### 【0056】

本発明のメモリブロック管理方法は、メモリブロックの状態を考慮して緊急消去動作を実行するか否かを決定する。

図 18 で 1 つの不揮発性メモリ装置 300 はシングルレベルセル領域 311 及びマルチレベルセル領域 312 を含む。しかし、本発明が必ずしもこれに制限される必要はない。本発明はページデータをバッファリングするためのシングルレベルセル領域 311 のみを有する別の不揮発性メモリ装置を具備することもある。

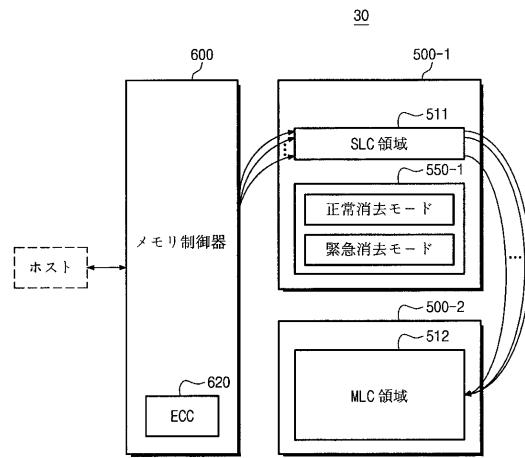

#### 【0057】

図 21 は本発明のその他の実施形態による OBP を使用するメモリシステムを例示的に示すブロック図である。図 21 を参照すれば、メモリシステム 30 は第 1 不揮発性メモリ装置 500-1、第 2 不揮発性メモリ装置 500-2、及びメモリ制御器 600 を含む。第 1 不揮発性メモリ装置 500-1 はシングルレベルセル領域 511 及び制御ロジック 550-1 を含む。第 2 不揮発性メモリ装置 500-2 はマルチレベルセル領域 512 を含む。

本発明のメモリシステム 30 は、ページデータを第 1 不揮発性メモリ装置 500-1 のシングルレベルセル領域 511 にバッファリングして置いた後に、第 2 不揮発性メモリ装置 500-2 のマルチレベルセル領域 512 にプログラムさせる。ここで、シングルレベルセル領域 511 は緊急消去モード或いは正常消去モードにしたがって消去されるメモリブロックを含む。

#### 【0058】

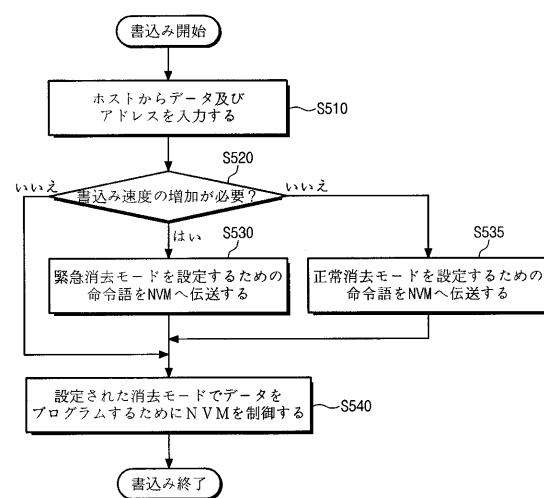

図 22 は本発明の実施形態によるメモリシステムの書き込み動作を例示的に示すフローチャートである。図 22 を参照すれば、メモリシステムの書き込み動作は次の通りである。

ホストからメモリシステムに書き込み要請が入力される。この時、データ及びアドレス (論理アドレス) が入力される (S510)。メモリシステムは書き込み速度の増加が必要で

10

20

30

40

50

あるか否かを判別する (S 5 2 0)。ここで、書き込み速度の増加に対する判別動作は、ホストの要請によって決定され得る。実施形態において、書き込み速度の増加に対する判別動作は、入力されたデータ関連情報にしたがって決定され得る。例えば、大容量データである場合、速い書き込み速度が必要であると判別される。

#### 【0059】

もし、書き込み速度を増加させる必要があれば、メモリ制御器は緊急消去モードを設定するための命令語を不揮発性メモリ装置へ伝送する (S 5 3 0)。不揮発性メモリ装置は伝送された命令語にしたがって緊急消去モードを設定し、以後消去命令に応答して緊急消去動作を実行する。

一方、書き込み速度を増加させる必要がなければ、メモリ制御器は正常消去モードを設定するための命令語を不揮発性メモリ装置へ伝送する (S 5 3 5)。不揮発性メモリ装置は伝送された命令語にしたがって正常消去モードを設定し、以後消去命令に応答して緊急消去動作を実行する。しかし、本発明のモード設定はこれに制限されない。正常消去モードの設定は別の設定過程無しでデフォルト値に決定することができる。

#### 【0060】

以後、メモリ制御器は設定された消去モードで入力されたデータを不揮発性メモリ装置にプログラムするように制御する (S 5 4 0)。

本発明によるメモリシステムの書き込み方法は書き込み速度を増加させるか否かを判別し、その結果にしたがって緊急消去動作の可否を決定する。

上述したように本発明の緊急消去動作はメモリセルを最上位状態 (図1参照、MS) 下の擬似消去状態 (Pseudo E) にセットすることである。しかし、緊急消去動作は必ずしもこれに制限されない。緊急消去動作は、別の消去動作を実行せず、以前プログラム状態をそのまま擬似消去状態 (Pseudo E) として利用することもできる。

#### 【0061】

一方、本発明の緊急消去動作は、擬似消去状態 (Pseudo E) にセットするものに制限されない。本発明の正常消去動作よりむしろ高い消去電圧或いは制限された時間内に多サイクルを印加することで具現されることもあり得る。

本発明は多様な装置に応用可能である。

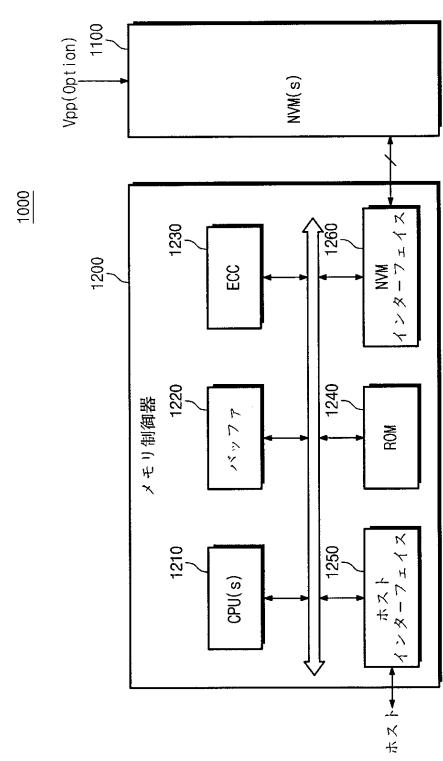

#### 【0062】

図23は本発明によるメモリシステムを例示的に示すブロック図である。図23を参照すれば、メモリシステム1000は少なくとも1つの不揮発性メモリ装置1100及びメモリ制御器1200を含む。メモリシステム1000は、図1乃至図22に上述されたように緊急消去動作を実行できる。

不揮発性メモリ装置1100は外部から高電圧Vppがオプション的に提供され得る。メモリ制御器1200は複数のチャンネルを通じて不揮発性メモリ装置1100に連結される。メモリ制御器1200は少なくとも1つの中央処理装置1210、バッファメモリ1220、エラー訂正回路1230、ROM1240、ホストインターフェイス1250、及びメモリインターフェイス1260を含む。メモリ制御器1200はデータをランダム化させるか、或いはデランダム化させるランダム化回路 (図示せず) をさらに包含できる。本発明のメモリシステム1000はPPN (Perfect Page New) に適用可能である。不揮発性メモリ装置1110は、外部の高電圧を選択的に受信することができる。

#### 【0063】

メモリ制御器1200は不揮発性メモリ装置1100のプログラム動作がフェイルされるか、或いはプログラム動作の信頼性が要求される時、データ復旧命令を発生し、発生されたデータ復旧命令を不揮発性メモリ装置1100へ伝送することができる。

メモリ制御器1200はエラー訂正コード(error correction code; ECC)にしたがってデータのエラーを訂正するエラー訂正回路1230を含む。エラー訂正回路1230は書き込み動作でプログラムされるデータのエラー訂正コード値を計算し、読み出し動作で読み出されたデータをエラー訂正コード値に基づいてエラー訂正で

10

20

30

40

50

きる。メモリ制御器 1200 はデータ復旧動作で復旧されたデータを他の物理的なページにプログラムせしめるように不揮発性メモリ装置 1100 へプログラム命令を伝送することができる。

本発明によるメモリシステム 1000 は緊急消去動作を実行することによって、速い書き込み速度が要求される大容量のデータを高速に格納できる。

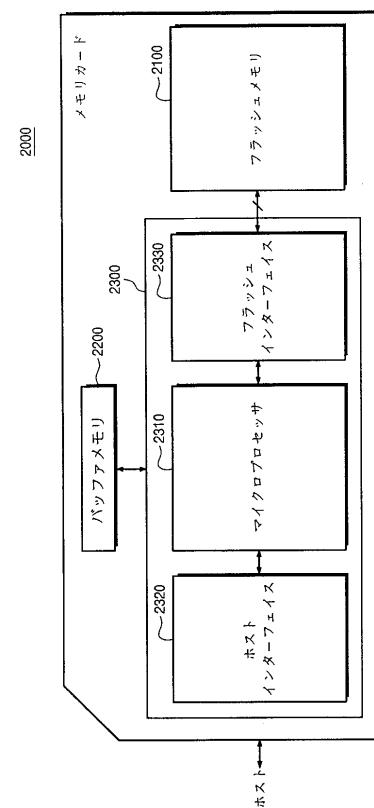

#### 【0064】

図 24 は本発明によるメモリカードを例示的に示すブロック図である。図 24 を参照すれば、メモリカード 2000 は少なくとも 1 つのフラッシュメモリ装置 2100、バッファメモリ装置 2200、及びそれらを制御するメモリ制御器 2300 を含む。メモリカード 2000 は、図 1 乃至図 22 で上述したように緊急消去動作を実行できる。

フラッシュメモリ装置 2100 は外部高電圧 Vpp をオプション的に受信することができる。バッファメモリ装置 2200 はメモリカード 2000 の動作の際に生成されるデータを臨時的に格納するための装置である。バッファメモリ装置 2200 は DRAM 或いは SRAM 等で具現され得る。メモリ制御器 2300 は複数のチャンネルを通じてフラッシュメモリ装置 2100 に連結される。メモリ制御器 2300 はホスト及びフラッシュメモリ装置 2100 の間に連結される。ホストからの要請に応答して、メモリ制御器 2300 はフラッシュメモリ装置 2100 をアクセスする。

#### 【0065】

メモリ制御器 2300 は少なくとも 1 つのマイクロプロセッサ 2310、ホストインターフェイス 2320、フラッシュインターフェイス 2330 を含む。少なくとも 1 つのマイクロプロセッサ 2310 はファームウェア (firmware) を動作するように具現される。ホストインターフェイス 2320 はホストとメモリカード 2000 との間にデータ交換を実行するためのカードプロトコル (例えば、SD/MMC) を通じてホストとインターフェイシングする。

本発明のメモリカード 2000 はマルチメディアカード (Multimedia Card: MMC)、保安デジタル (Security Digital: SD)、mini SD、USB を利用するメモリスティック (Memory Stick)、スマートメディア (Smart Media (登録商標))、トランスマルチ (TransFlash) カード等に適用可能である。

#### 【0066】

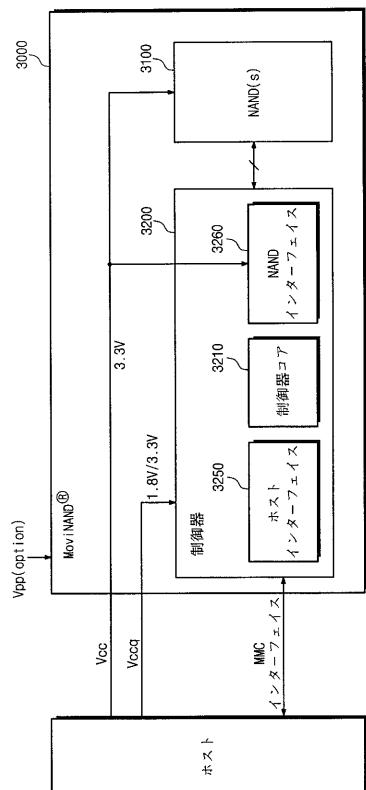

図 25 は本発明による moviNAND を例示的に示すブロック図である。図 25 を参照すれば、moviNAND 3000 は少なくとも 1 つの NAND フラッシュメモリ装置 3100 及び制御器 3200 を包含することができる。moviNAND 3000 は MMC4.4 (言い換えれば、eMMC) 規格を支援する。moviNAND 3000 は、図 1 乃至図 22 で上述したように緊急消去動作を実行できる。

#### 【0067】

NAND フラッシュメモリ装置 3100 は SDR (Single Data Rate) NAND 或いは DDR (Double Data Rate) NAND であり得る。実施形態において、NAND フラッシュメモリ装置 3100 は単品の NAND フラッシュメモリ装置を含むことができる。ここで、単品の NAND フラッシュメモリ装置は 1 つのパッケージ (例えば、FBGA、Fine-pitch Ball Grid Array) に積層され得る。メモリ制御器 3200 は複数のチャンネルを通じて NAND フラッシュメモリ装置 3100 に連結される。制御器 3200 は少なくとも 1 つの制御器コア 3210、ホストインターフェイス 3250、及び NAND インターフェイス 3260 を含む。少なくとも 1 つの制御器コア 3210 は moviNAND 3000 の全般的な動作を制御する。ホストインターフェイス 3250 は制御器 3210 とホストのインターフェイシングを実行する。NAND インターフェイス 3260 は NAND フラッシュメモリ装置 3100 と制御器 3200 のインターフェイシングを実行する。実施形態において、ホストインターフェイス 3250 は並列インターフェイス (例えば、MMC インターフェイス) であり得る。他の実施形態において、moviNAND 3000 のホストインターフェイス 3250 は

10

20

30

40

50

直列インターフェイス（例えば、UHS-II、UFSインターフェイス）であり得る。

【0068】

moviNAND3000はホストから電源電圧Vcc、Vccqを受信する。ここで、第1電源電圧（Vcc:3.3V）はNANDフラッシュメモリ装置3100及びNANDインターフェイス3230へ提供され、第2電源電圧（Vccq:1.8V/3.3V）は制御器3200へ提供される。実施形態において、moviNAND3000は外部高電圧Vppがオプション的に提供され得る。

本発明によるmoviNAND3000は大容量のデータを格納するのに有利であるこのみでなく、向上された書き込み動作特性を有する。本発明の実施形態によるmoviNAND3000は小型及び低電力が要求されるモバイル製品（例えば、ギャラクシーS（登録商標）、ギャラクシーノート（登録商標）、ギャラクシータブ（登録商標）、アイフォン（登録商標）、アイパッド（登録商標）等）に応用可能である。

【0069】

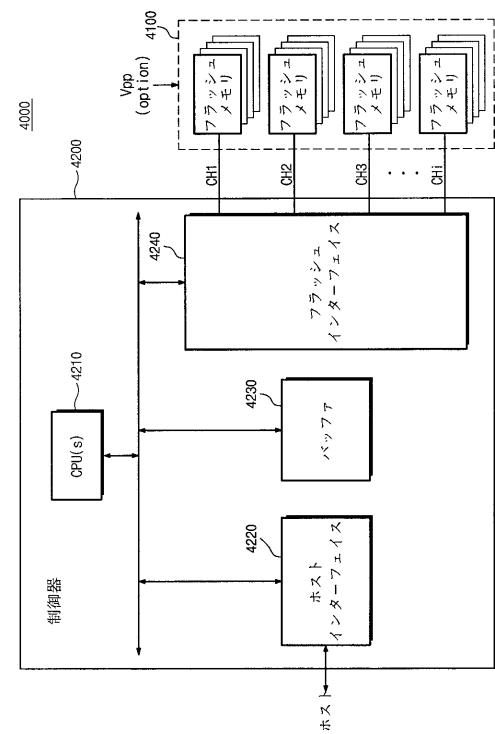

図26は本発明によるSSDを例示的に示すブロック図である。図26を参照すれば、SSD4000は複数のフラッシュメモリ装置4100及びSSD制御器4200を含む。SSD4000は、図1乃至図22に上述されたように緊急消去動作を実行できる。

フラッシュメモリ装置4100はオプション的に外部高電圧Vppを提供されるように具現され得る。SSD制御器4200は複数のチャンネルCH1～CH4を通じてフラッシュメモリ装置4100に連結される。SSD制御器4200は少なくとも1つの中央処理装置4210、バッファメモリ4220、ホストインターフェイス4250、及びフラッシュインターフェイス4260を含む。

本発明によるSSD4000はデータの信頼性を向上させるプログラム動作を実行する。一方、SSD4000に対するさらなる詳細は本出願の出願人である三星電子から出願し、先行技術文献として記載された特許文献2乃至6で説明される。

【0070】

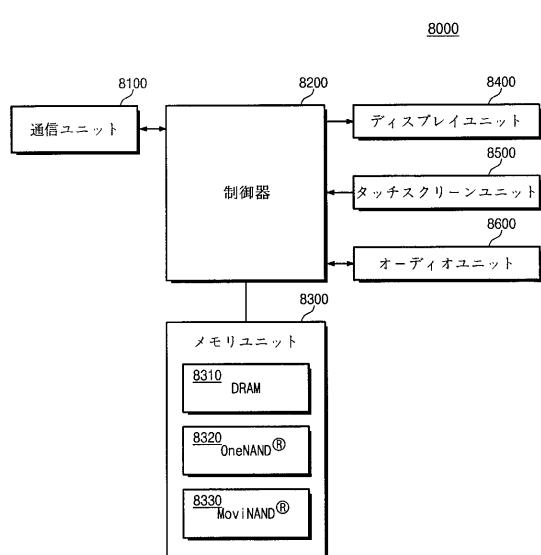

図27は本発明による通信装置を例示的に示すブロック図である。図27を参照すれば、モバイル装置8000は通信ユニット8100、制御器8200、メモリユニット8300、ディスプレイユニット8400、タッチスクリーンユニット8500、及びオーディオユニット8600を含む。メモリユニット8300は少なくとも1つのDRAM8310、少なくとも1つのOneNAND8320、及び少なくとも1つのmoviNAND8330を含む。OneNAND8320及びmoviNAND8330の中で少なくとも1つは図23に図示されたメモリシステム1000と同一な構成及び動作を有するように具現される。

【0071】

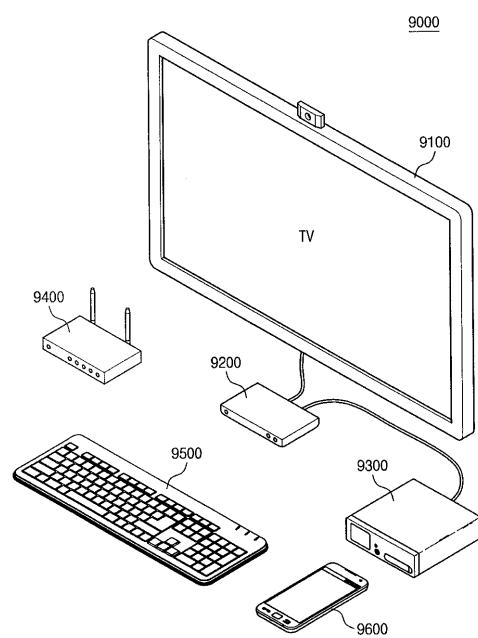

図28は本発明によるスマートTVシステムを例示的に示すブロック図である。図28を参照すれば、スマートTVシステム9000はスマートTV9100、レビュー9200、セットトップボックス9300、無線共有器9400、キーパッド9500、及びスマートフォン9600を含む。スマートTV9100と無線共有器9400との間に無線通信が実行される。スマートTV9100は開放形プラットホームであるGoogle陣営のレビュー（Review、9200）を具備することによって、インターネットに接続が可能である。スマートTV9100はセットトップボックス9300を通じてケーブル放送及び衛星放送を視聴することができる。スマートTVはキーパッド9500の制御またはスマートフォン9600の制御にしたがって運用され得る。本発明のスマートTV9100は図23に図示されたメモリシステム1000を包含することができる。

【0072】

本発明の実施形態によるメモリシステム或いは格納装置は多様な形態のパッケージを利用して実装され得る。実施形態において、本発明の実施形態によるメモリシステム或いは格納装置はPOP（Package on Package）、Ball grid arrays（BGAs）、Chip scale packages（CSPs）、Plastic Leaded Chip Carrier（PLCC）、Plastic

10

20

30

40

50

Dual In-Line Package (PDIP)、Die in Waffle Pack、Die in Wafer Form、Chip On Board (COB)、Ceramic Dual In-Line Package (CERDIP)、Plastic Metric Quad Flat Pack (MQFP)、Thin Quad Flatpack (TQFP)、Small Outline (SOIC)、Shrink Small Outline Package (SSOP)、Thin Small Outline (TSOP)、Thin Quad Flatpack (TQFP)、System In Package (SIP)、Multi Chip Package (MCP)、Wafer-level Fabricated Package (WFP)、Wafer-Level Processed Stack Package (WSP)、等のようなパッケージを利用して実装され得る。

10

【0073】

一方、本発明の詳細な説明では具体的な実施形態に関して説明したが、本発明の範囲で逸脱しない範囲内で様々に変形できる。したがって本発明の範囲は上述した実施形態に限定されてはならないし、後述する特許請求の範囲のみでなくこの発明の特許請求の範囲と均等なものによって定められる。

【符号の説明】

【0074】

ER . . . 第1消去検証レベル

PER . . . 第2消去検証レベル

QEM . . . 緊急消去マージン

Psuedo E . . . 擬似消去状態

100 . . . 不揮発性メモリ装置

110 . . . メモリセルアレイ

120 . . . アドレスデコーダ

130 . . . 電圧発生回路

140 . . . 入出力回路

150 . . . 制御ロジック

200 . . . メモリ制御器

10、20、30 . . . メモリシステム

Verase . . . 消去電圧

311 . . . シングルレベルセル領域

312 . . . マルチレベルセル領域

20

30

【図1】

【図2】

【図3】

【図4】

【図6】

【図5】

【図7】

【図 8】

【図 9】

【図 10】

【図 11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図20】

【図19】

【図21】

## 【図22】

### 【図23】

【 図 2 4 】

## 【図25】

【図26】

【図27】

【 図 2 8 】

---

フロントページの続き

(72)発明者 金 鍾 河

大韓民国京畿道城南市盆唐区二梅洞 二梅村ハンシンアパート205棟704号

(72)発明者 孔 駿 鎮

大韓民国京畿道龍仁市水枝区豊徳川2洞 三星7次アパート704棟304号

審査官 塚田 肇

(56)参考文献 特許第3798810 (JP, B2)

特開2006-018863 (JP, A)

特開2011-065736 (JP, A)

特開2003-022687 (JP, A)

特開2007-164937 (JP, A)

特開2012-027979 (JP, A)

特開2011-186555 (JP, A)

特開2006-351061 (JP, A)

米国特許出願公開第2013/0198436 (US, A1)

米国特許出願公開第2008/0198651 (US, A1)

米国特許出願公開第2012/0281471 (US, A1)

米国特許第5270979 (US, A)

(58)調査した分野(Int.Cl., DB名)

G 11 C 16 / 14

G 11 C 11 / 56