US 20150144886A1

### (19) United States

# (12) Patent Application Publication He et al.

# (10) Pub. No.: US 2015/0144886 A1

### (43) **Pub. Date:** May 28, 2015

#### (54) FINFET WITH MERGE-FREE FINS

(71) Applicant: International Business Machines Corporation, Armonk, NY (US)

(72) Inventors: Hong He, Schenectady, NY (US);

Chiahsun Tseng, Wynantskill, NY (US);

Junli Wang, Singerlands, NY (US);

Chun-chen Yeh, Clifton Park, NY (US);

Yunpeng Yin, Niskayuna, NY (US)

(21) Appl. No.: 14/605,009

(22) Filed: Jan. 26, 2015

#### Related U.S. Application Data

(60) Division of application No. 13/965,322, filed on Aug. 13, 2013, which is a continuation of application No. 13/713,842, filed on Dec. 13, 2012.

#### Publication Classification

(51) **Int. Cl.** *H01L 29/78* (2006.01)

*H01L 29/06* (52) U.S. Cl.

CPC ............ *H01L 29/785* (2013.01); *H01L 29/0673* (2013.01)

(2006.01)

#### (57) ABSTRACT

A semiconductor device comprises an insulation layer, an active semiconductor layer formed on an upper surface of the insulation layer, and a plurality of fins formed on the insulation layer. The fins are formed in the gate and spacer regions between a first source/drain region and second source/drain region, without extending into the first and second source/drain regions.

FIG. 1A

FIG. 1B

FIG. 2

FIG. 3

FIG. 4B

FIG. 7A

FIG. 8B

FIG. 10B

FIG. 12B

FIG. 13B

FIG. 14B

FIG. 15A

FIG. 15B

FIG. 17A

FIG. 17B

FIG. 18B

FIG. 19A

FIG. 19B

FIG. 20A

FIG. 20B

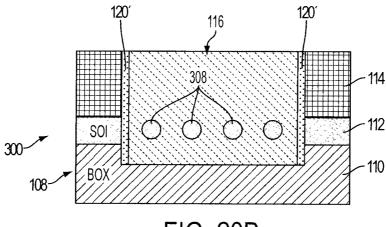

FIG. 21A

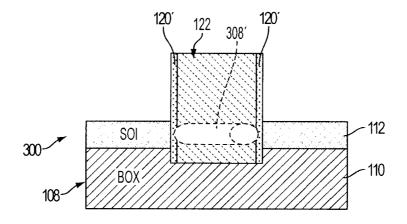

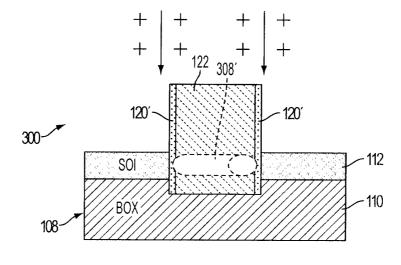

FIG. 22A

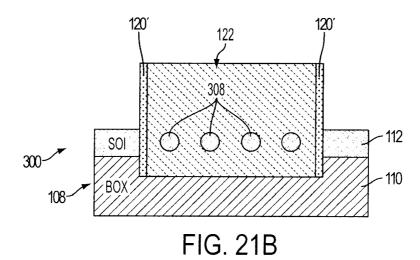

FIG. 22B

FIG. 26A

FIG. 26B

FIG. 27B

FIG. 28

FIG. 29

#### FINFET WITH MERGE-FREE FINS

#### DOMESTIC PRIORITY

[0001] This application is a division of U.S. patent application Ser. No. 13/965,322, filed Aug. 13, 2013, which is a continuation of U.S. patent application Ser. No. 13/713,842, filed Dec. 13, 2012, the disclosures of which are incorporated by reference herein in their entireties.

#### BACKGROUND

[0002] The invention relates to a semiconductor device, and more particularly, to patterning fins of a FinFET semiconductor device.

[0003] Interests in multi-gate MOSFETs have significantly increased as the industry continues to demand smaller sized MOSFET devices. One such device that is capable of maintaining industry performance standards at a reduced size is the FinFET.

[0004] A conventional FinFET includes one or more fins that are patterned on a substrate, such as a silicon-on-insulator (SOI). For example, a conventional sidewall image transfer (SIT) process can be used to form a dense array of fins, which extend into the source/drain (S/D) regions of the FinFET. Conventional FinFET fabrication requires an epitaxy (EPI) process to merge the fins formed in the S/D regions. However, this process causes undesirable gaps between the fins, and may also create source/drain shorting issues at the gate line ends if the EPI process is not properly controlled.

[0005] Moreover, conventional fabrication processes perform gate patterning for forming a gate after forming the fins. The gate patterning utilizes hardmasks, and performs additional spacer etching processes. However, the fins may be inadvertently eroded during the gate and spacer etching processes.

#### **SUMMARY**

[0006] According to an exemplary embodiment, a semiconductor device having a gate region comprises an insulation layer extending along a first direction to define a length and a second direction perpendicular to the first direction to define a width. The insulation layer has a gate insulation region disposed between first and second non-gate insulation regions that are different from the gate insulation region. An active semiconductor layer is formed on an upper surface of the insulation layer, and a plurality of fins is formed on the gate and spacer regions and between the first and second non-gate insulation regions.

[0007] In another exemplary embodiment, a semiconductor device has first and second non-gate regions. The semiconductor device comprises a semiconductor substrate including an active semiconductor layer disposed on an insulation layer, and has a gate pocket formed between the first and second non-gate regions. The gate pocket extends through the active semiconductor layer and the insulation layer to define a recessed gate insulation region. A plurality of fins are supported by walls of the recessed gate insulation region and are disposed a predetermined distance above the recessed gate insulation layer to define a void beneath each fin among the plurality of fins.

[0008] In yet another exemplary embodiment, a method of fabricating a semiconductor device comprises forming an insulation layer having a length extending along a first direction and a width extending along a second direction perpen-

dicular to the first direction. The insulation layer has a gate insulation region located between first and second non-gate insulation regions. The method further includes forming an active semiconductor layer on an upper surface of the insulation layer, and forming a plurality of fins at the gate and spacer regions and between the first and second non-gate insulation regions.

[0009] In still another exemplary embodiment, a method of forming a semiconductor device having first and second nongate regions comprises forming an active semiconductor layer disposed on an insulation layer, forming a gate pocket through the active semiconductor layer and the insulation layer to define a recessed gate insulation region between the first and second non-gate regions, forming a plurality of fins supported by walls of the gate pocket. The method further includes removing a portion of the recessed gate insulation region located beneath the plurality of fins to define a void between each fin among the plurality of fins and the recessed gate insulation region.

[0010] In still another exemplary embodiment of the present teachings, a method of fabricating a semiconductor device comprises forming a semiconductor substrate including a plurality of layers and having a gate region located between first and second non-gate regions that are different from the gate region. The method further includes forming a gate pocket at the gate region that extends through the plurality of layers, and forming a plurality of fins in the gate pocket such that each fin among the plurality of fins is isolated from the first and second non-gate regions.

[0011] In another exemplary embodiment, a method of fabricating semiconductor device comprises forming an insulation layer having a length extending along a first direction and a width extending along a second direction perpendicular to the first direction. The insulation layer has a gate insulation region disposed between first and second non-gate insulation regions. The method further includes forming an active semiconductor layer on an upper surface of the insulation layer. The method further includes forming a plurality of fins at the gate insulation region and between the first and second non-gate insulation regions.

[0012] In still another embodiment, a method of forming a semiconductor device having first and second non-gate regions comprises forming an active semiconductor layer disposed on an insulation layer. The method further includes forming a gate pocket through the active semiconductor layer and the insulation layer to define a recessed gate insulation region between the first and second non-gate regions. The method further includes forming a plurality of fins supported by walls of the gate pocket. The method further includes removing a portion of the recessed gate insulation region located beneath the plurality of fins to define a void between each fin among the plurality of fins and the recessed gate insulation region.

[0013] Additional features and utilities are realized through the techniques of the present teachings. Other exemplary embodiments and features of the teachings are described in detail herein and are considered a part of the claimed teachings. For a more detailed description of the teachings and features, drawings and descriptions of the exemplary embodiments are presented below.

## BRIEF DESCRIPTION OF THE SEVERAL VIEWS OF THE DRAWINGS

[0014] The subject matter describing exemplary embodiments of the teachings is particularly pointed out and distinctly claimed in the claims at the conclusion of the specification. The forgoing and other features, and utilities of the teachings are apparent from the following detailed description taken in conjunction with the accompanying drawings in which:

[0015] FIGS. 1-27 are a series of views illustrating a method of forming a finFET device according to exemplary embodiments of the present teachings, in which:

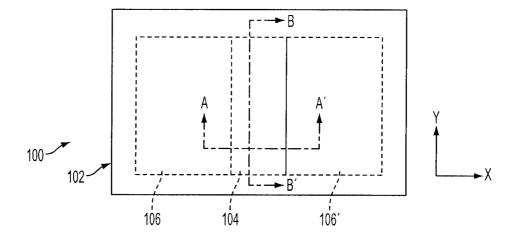

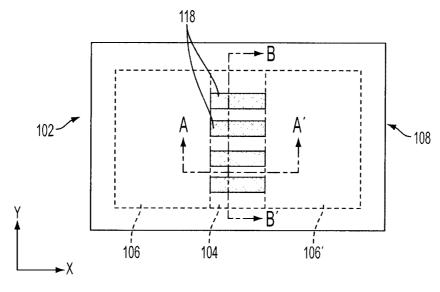

[0016] FIG. 1A is a top view illustrating a  ${\rm SiO_2}$  masking layer formed atop a starting substrate;

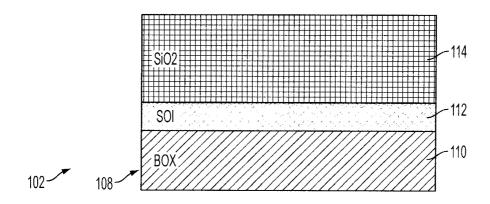

[0017] FIG. 1B is a cross sectional view of the starting substrate illustrated in FIG. 1A taken along the lines A-A' illustrating the formation of the  ${\rm SiO_2}$  masking layer atop an SOI layer;

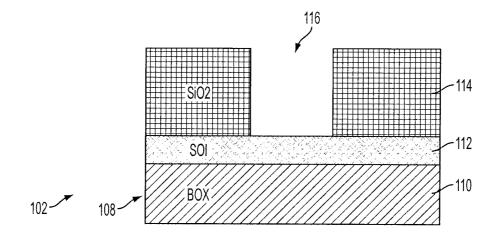

[0018] FIG. 2 is a cross sectional view illustrating patterning of the SiO<sub>2</sub> masking layer to form a gate pocket;

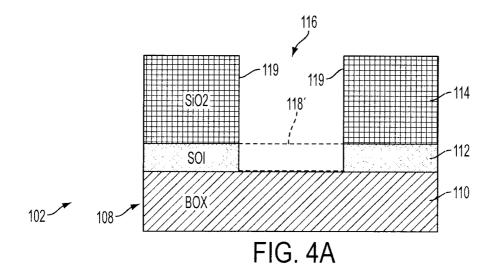

[0019] FIG. 3 is a top view of the structure of FIG. 2, following transfer of the  $SiO_2$  masking layer patterning into the SOI layer to define semiconductor fins in the gate pocket; [0020] FIG. 4A is a cross sectional view in a first orientation taken along the lines A-A' of FIG. 3;

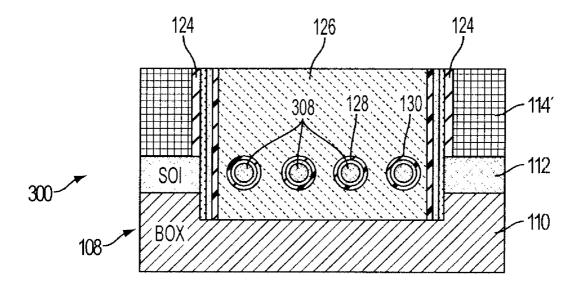

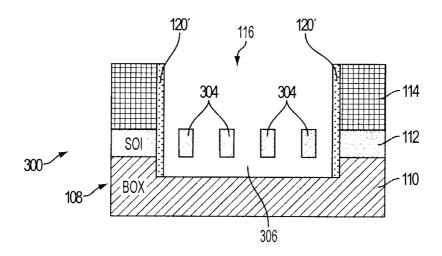

[0021] FIG. 4B is a cross sectional view in a second orientation taken along the lines B-B' of FIG. 3;

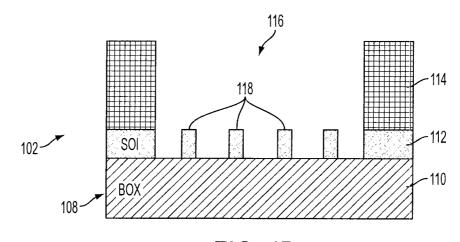

[0022] FIG. 5A is a cross sectional view in the first orientation illustrating the formation of a spacer layer over the device shown in FIG. 4A;

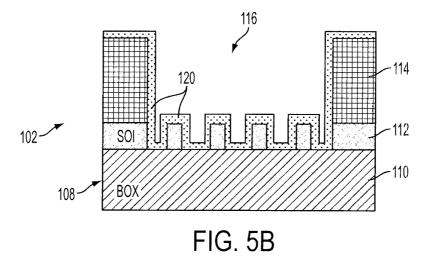

[0023] FIG. 5B is a cross sectional view in the second orientation illustrating the formation of the spacer layer over the device shown in FIG. 5A;

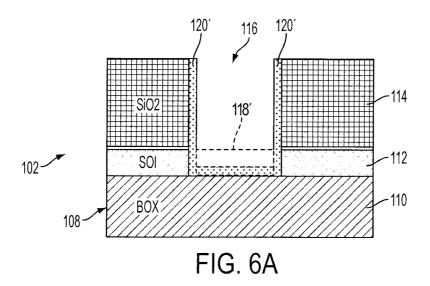

[0024] FIG. 6A is a cross sectional view in the first orientation illustrating the partial etching of the spacer layer shown in FIG. 5A;

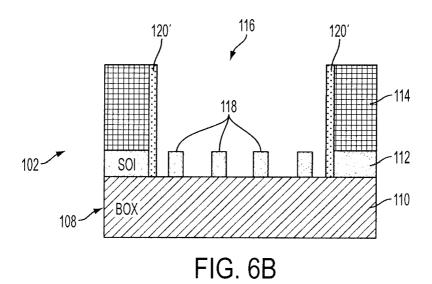

[0025] FIG. 6B is a cross sectional view in the second orientation illustrating the partial etching of the spacer layer shown in FIG. 6A;

[0026] FIG. 7A is a cross sectional view in the first orientation, following a deposition of amorphous/polysilicon gate material in the gate pocket of the device illustrated in FIG. 6A:

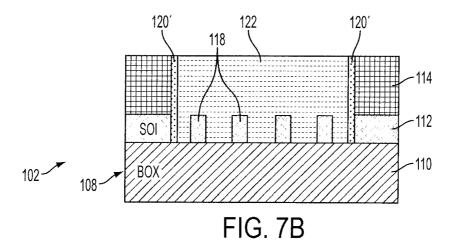

[0027] FIG. 7B is cross sectional view in the second orientation of the amorphous/polysilicon gate material deposited in the gate pocket of the device illustrated in FIG. 7A;

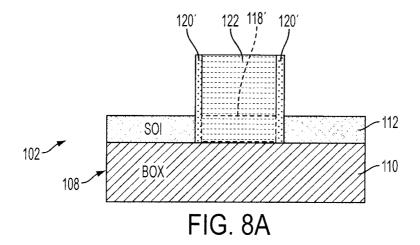

[0028] FIG. 8A is a cross sectional view in the first orientation of the device illustrated in FIG. 7A, following removal of the SiO<sub>2</sub> masking layer;

[0029] FIG. 8B is cross sectional view in the second orientation, following the removal of the SiO<sub>2</sub> masking layer illustrated in FIG. 8A;

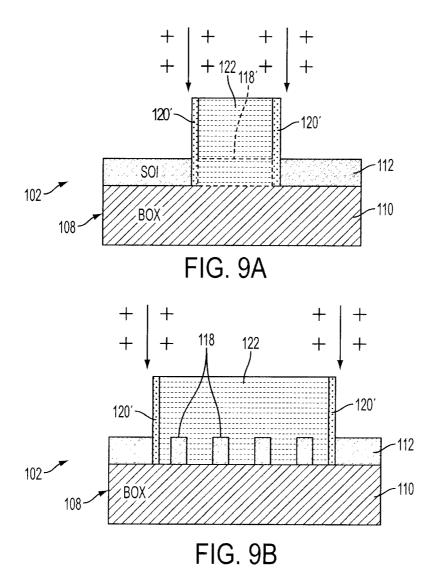

[0030] FIG. 9A is cross sectional view in the first orientation illustrating an extension ion implantation of the device shown in FIG. 8A;

[0031] FIG. 9B is a cross sectional view in the second orientation illustrating the extension implantation of the device shown in FIG. 9A;

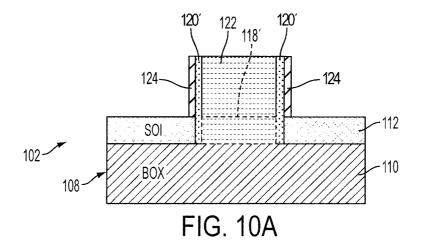

[0032] FIG. 10A is a cross sectional view in the first orientation, following deposition of a second spacer on the device shown in FIG. 9A;

[0033] FIG. 10B is a cross sectional view in the second orientation illustrating the deposition of the second spacer shown on the device of FIG. 10A;

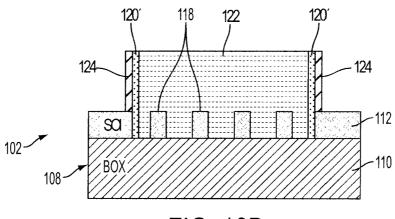

[0034] FIG. 11A is cross sectional view in the first orientation illustrating source/drain ion implantation of the device shown in FIG. 10A;

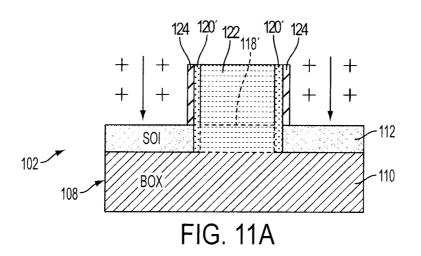

[0035] FIG. 11B is a cross sectional view in the second orientation illustrating the source/drain implantation of the device shown in FIG. 11A;

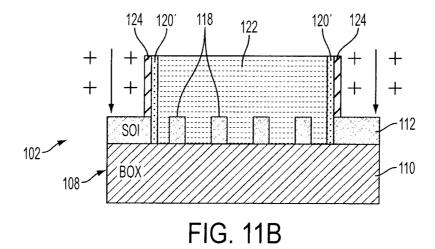

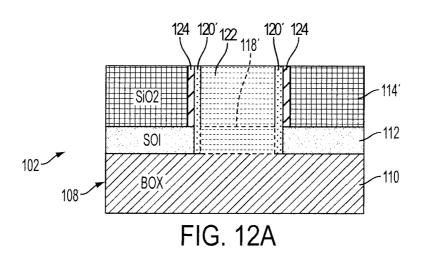

[0036] FIG. 12A is a cross sectional view in the first orientation, following a formation of a second SiO<sub>2</sub> hard mask formed on the device shown in FIG. 11A;

[0037] FIG. 12B is a cross sectional view in the second orientation of the second SiO<sub>2</sub> hard mask on the device shown in FIG. 12A;

[0038] FIG. 13A is a cross sectional view in the first orientation following removal of the amorphous/polysilicon gate material to expose the gate pocket of the device illustrated in FIG. 12A;

[0039] FIG. 13B is a cross sectional view in the second orientation following the removal of the amorphous/polysilicon gate material the device illustrated in FIG. 13A;

[0040] FIG. 14A is a cross sectional view in the first orientation, following a deposition of high-k and metal gate material in the gate pocket of the device illustrated in FIG. 13A;

[0041] FIG. 14B is cross sectional view in the second orientation of the high-k and metal gate material deposited in the gate pocket of the device illustrated in FIG. 14A;

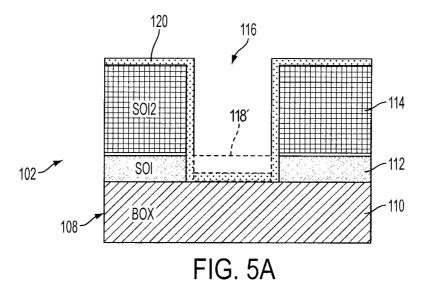

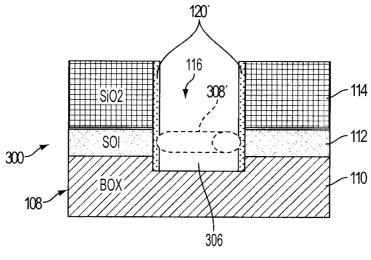

[0042] FIG. 15A is a cross sectional view in the first orientation after recessing the buried oxide layer below the semi-conductor fins of the device illustrated in FIG. 3A according to another exemplary embodiment of the present teachings;

[0043] FIG. 15B is a cross sectional view in the second orientation illustrating the buried oxide layer below the semi-conductor fins of the device illustrated in FIG. 15A;

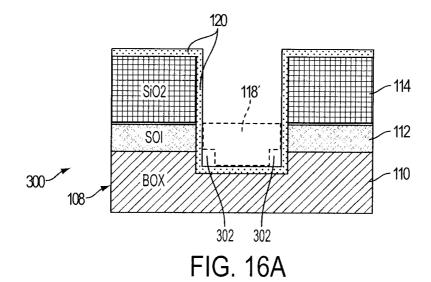

[0044] FIG. 16A is a cross sectional view in the first orientation illustrating the formation of a spacer layer over the device shown in FIG. 15A;

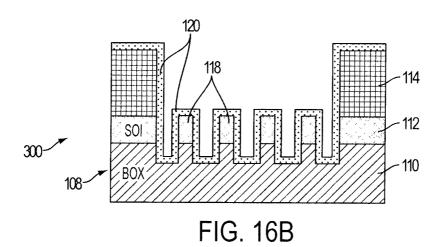

[0045] FIG. 16B is a cross sectional view in the second orientation illustrating the formation of the spacer layer over the device shown in FIG. 16A;

[0046] FIG. 17A is a cross sectional view in the first orientation illustrating the partial etching of the spacer layer shown in FIG. 16A;

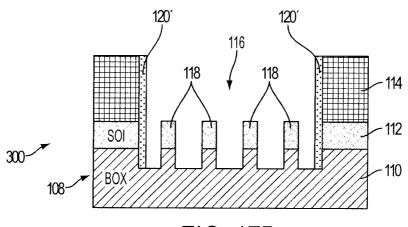

[0047] FIG. 17B is a cross sectional view in the second orientation illustrating the partial etching of the spacer layer shown in FIG. 17A;

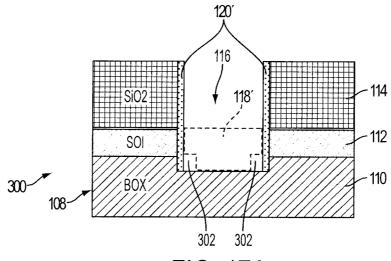

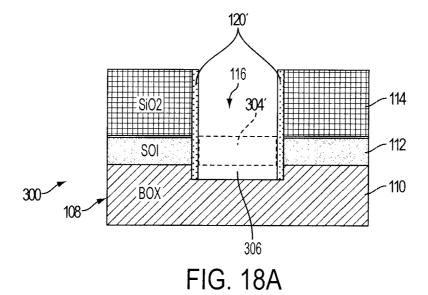

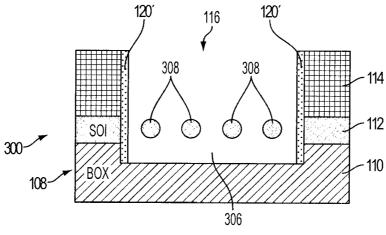

[0048] FIG. 18A is a cross sectional view in the first orientation illustrating removal of the buried oxide layer beneath the fins shown in FIG. 17A to form hanging fins;

[0049] FIG. 18B is a cross sectional view in the second orientation illustrating the removal of the buried oxide layer to form the hanging fins of the device shown in FIG. 18A;

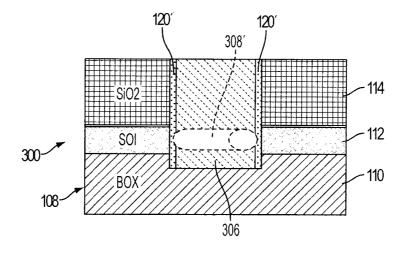

[0050] FIG. 19A is a cross sectional view in the first orientation, following an annealing process performed on the hanging fins shown in FIG. 18A to form nanowire fins;

[0051] FIG. 19B is a cross sectional view in the second orientation illustrating the nanowire fins of the device shown in FIG. 19A;

[0052] FIG. 20A is a cross sectional view in the first orientation, following a deposition of amorphous/polysilicon gate material in the gate pocket of the device illustrated in FIG. 19A;

[0053] FIG. 20B is cross sectional view in the second orientation of the amorphous/polysilicon gate material deposited in the gate pocket of the device illustrated in FIG. 20A;

[0054] FIG. 21A is a cross sectional view in the first orientation, following removal of the  $SiO_2$  masking layer shown in FIG. 20A:

[0055] FIG. 21B is cross sectional view in the second orientation, following the removal of the  $SiO_2$  masking layer illustrated in FIG. 21A;

[0056] FIG. 22A is cross sectional view in the first orientation illustrating an extension ion implantation of the device shown in FIG. 21A;

[0057] FIG. 22B is a cross sectional view in the second orientation illustrating the extension implantation of the device shown in FIG. 22A;

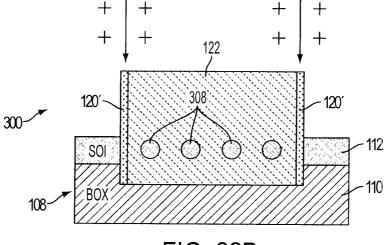

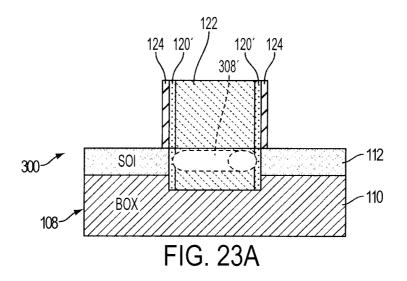

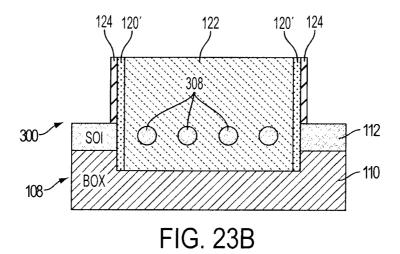

[0058] FIG. 23A is a cross sectional view in the first orientation, following deposition of a second spacer on the device shown in FIG. 22A;

[0059] FIG. 23B is a cross sectional view in the second orientation illustrating the deposition of the second spacer shown on the device of FIG. 23A;

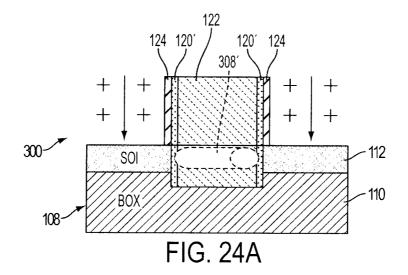

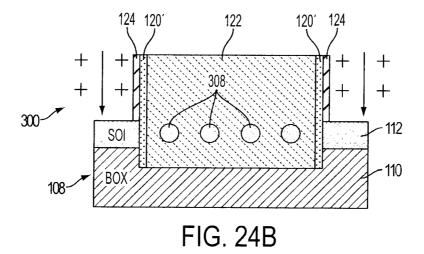

[0060] FIG. 24A is cross sectional view in the first orientation illustrating source/drain ion implantation of the device shown in FIG. 23A;

[0061] FIG. 24B is a cross sectional view in the second orientation illustrating the source/drain implantation of the device shown in FIG. 24A;

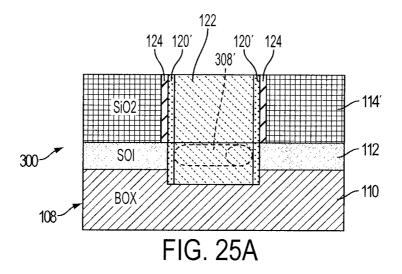

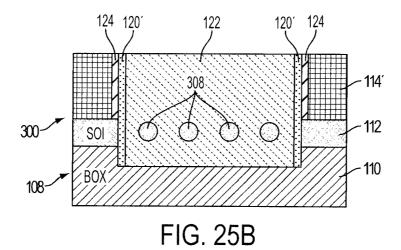

[0062] FIG. 25A is a cross sectional view in the first orientation, following a formation of a second SiO<sub>2</sub> hard mask on the device shown in FIG. 24A;

[0063] FIG. 25B is a cross sectional view in the second orientation, following the second SiO<sub>2</sub> hard mask formed on the device shown in FIG. 25B;

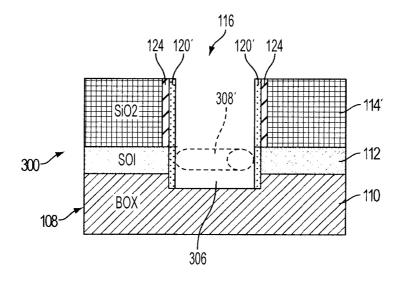

[0064] FIG. 26A is a cross sectional view in the first orientation following removal of the amorphous/polysilicon gate material to expose the gate pocket of the device illustrated in FIG. 25A;

[0065] FIG. 26B is a cross sectional view in the second orientation following the removal of the amorphous/polysilicon gate material the device illustrated in FIG. 26A;

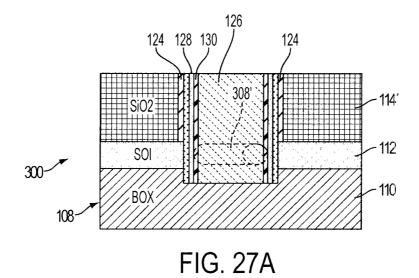

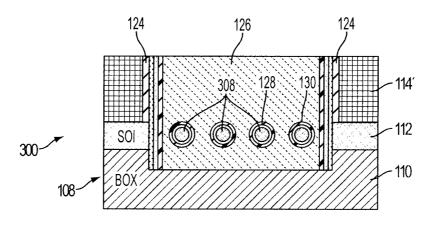

[0066] FIG. 27A is a cross sectional view in the first orientation, following a deposition of high-k and metal gate material in the gate pocket of the device illustrated in FIG. 26A; and

[0067] FIG. 27B is cross sectional view in the second orientation of the high-k and metal gate material deposited in the gate pocket of the device illustrated in FIG. 27A.

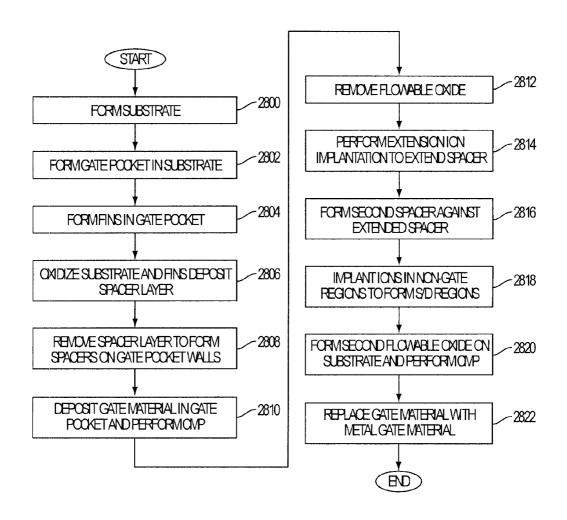

[0068] FIG. 28 is a flow diagram illustrating a method of fabricating a semiconductor structure according to an exemplary embodiment of the present teachings; and

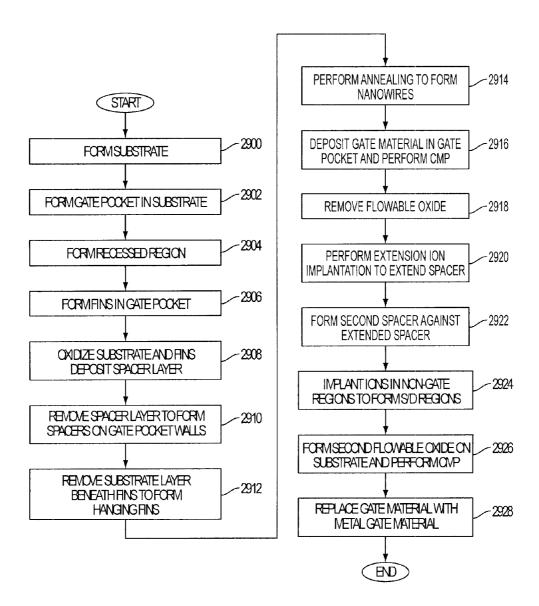

[0069] FIG. 29 is a flow diagram illustrating a method of fabricating a semiconductor structure according to another exemplary embodiment of the present teachings.

#### DETAILED DESCRIPTION

[0070] FIGS. 1A-1B illustrate a semiconductor structure 100 according to an exemplary embodiment. The semiconductor structure 100 includes a semiconductor substrate 102 generally indicated. The semiconductor substrate 102 may extend along an X-axis to define a length, and a Y-axis perpendicular to the X-axis to define a width. The semiconductor substrate 102 may include a gate region 104 disposed between first and second non-gate regions 106/106'. In at least one exemplary embodiment, the first and second non-gate regions 106/106' include first and second source/drain (S/D) regions. That is, the first non-gate region 106 may correspond to a source region and the second non-gate region 106' may

correspond to a drain region. The non-gate regions 106/106' may also include regions identified as future source/drain regions to be effected via a future doping procedure, and/or regions that have already undergone a doping procedure to effect S/D regions. Accordingly, the non-gate regions 106/106' will hereinafter be referred to as S/D regions 106/106'.

[0071] Exemplary embodiments here on out illustrate the semiconductor substrate 102 as a silicon-on-insulator (SOI) wafer. However, it can also be appreciated that other semiconductor substrates may be used. For example, the semiconductor substrate 102 may include, but is not limited to, a bulk semiconductor substrate comprising silicon, germanium, silicon germanium, silicon carbide, or a III-V compound semiconductor (e.g., GaAs), and a II-VI compound semiconductors (e.g., ZnSe). In addition, an entire semiconductor substrate 102, or a portion thereof, may be amorphous, polycrystalline, or single-crystalline. The aforementioned types of semiconductor substrates 102 may also include a hybrid oriented (HOT) semiconductor substrate, which provides surface regions of different crystallographic orientation. The semiconductor substrate 102 may be doped, undoped or contain doped regions and undoped regions therein. Further, the semiconductor substrate 102 may be strained, unstrained, contain regions of strain and no strain therein, or contain regions of tensile strain and compressive strain.

[0072] FIGS. 1-14 illustrate a flow process of forming a semiconductor structure 100, such as a FinFET device, according to an exemplary embodiment of present teachings. Referring to FIG. 1B, the semiconductor substrate 102 may be formed as a silicon-on-insulator (SOI) wafer 108. The SOI wafer 108 includes a buried insulator layer 110 formed on a bulk layer (not shown), an active SOI layer 112 such as silicon, and a masking layer 114.

[0073] The buried insulator layer 110 may be a buried oxide (BOX) layer 110 that separates and electrically isolates the bulk layer from the SOI layer 112. The buried insulator layer 110 may have a thickness ranging from about 20 nanometers (nm) to about 200 nanometers (nm). The active SOI layer 112 is disposed between the buried insulator layer 110 and the masking layer 114, and may have a thickness of about 30 nanometers (nm). The masking layer 114 is formed on an upper surface of the active SOI layer 112 to provide a hardmask or covering. The masking layer 114 may be made of a dielectric including, for example, silicon dioxide (SiO<sub>2</sub>).

[0074] Referring to FIG. 2, a cross sectional view illustrates patterning of the masking layer 114 to form a gate pocket 116 formed in the gate region 104. More specifically, the gate pocket 116 may be formed in the gate region 104 located between the first and second S/D regions 106/106', and through the masking layer 114, to expose the SOI layer 112. The gate pocket 116 may extend through the masking layer 114 and stop at the active SOI layer 112. The gate pocket may also extend through the SOI layer 112, as discussed in greater detail below. Various etching methods may be used to form the gate pocket 116 including, but not limited to, sidewall image transfer (SIT) or pitch split processing.

[0075] FIG. 3 is a top view of the semiconductor substrate 102 of FIG. 2, following transfer of the masking layer 114 patterning into the SOI layer 112 to define a plurality of semiconductor fins 118 in the gate pocket 116. Although a plurality of fins 118 is formed, a single fin may be formed on the buried insulator layer 110. The fins 118 may be made of a single crystal semiconductor shape, and may be formed to have bodies of various shapes. For example, the fins 118 may

have narrow fin bodies extending parallel to the width of the substrate in the X-axis direction, and sidewalls projecting vertically from the buried insulator layer. Further, the fins 118 may be made of single crystal semiconductor material.

[0076] The fins 118 may be formed using various conventional processes including, but not limited to, optical lithographic processes, e-beam lithographic processes, trimming processes such as, for example, resist trimming, hard mask trimming or oxidation trimming, and a combination thereof. In at least one exemplary embodiment of the present teachings, the fins 118 are formed using a sidewall image transfer (SIT) process.

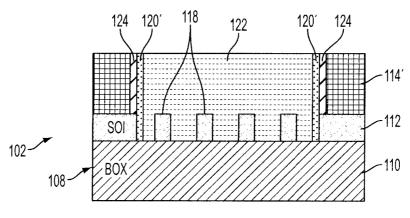

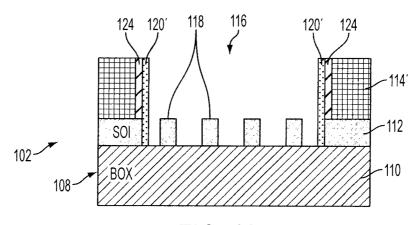

[0077] As illustrated in FIGS. 4A-4B, the plurality of fins 118 are formed in the gate pocket 116 of the SOI wafer 108, and between the first and second S/D regions 106/106'. Accordingly, walls 119 formed by the gate pocket 116 may isolate the plurality of fins 118 from the first and second S/D regions 106/106'.

[0078] More specifically, FIG. 4A is a cross-sectional view of the SOI wafer 108 illustrated in FIG. 3 taken along section A-A'. A single fin 118' among the plurality of fins 118 is illustrated in phantom. The fin 118' is formed in the gate pocket 116, and extends in a lengthwise direction along the X-axis between the first and second S/D regions 106/106' to define a length thereof. The length of the fin 118 may range from about 2 nanometers (nm) to about 50 nanometers (nm). In one embodiment, the length of fin varies from 10 nm to 40 nm

[0079] FIG. 4B is a cross-sectional view of the SOI wafer 108 taken along section B-B' of the SOI wafer 108 illustrated in FIG. 3. The plurality of fins 118 is arranged in an array that extends along the widthwise direction of the SOI wafer 108, i.e., the Y-axis. Each single fin 118' extends along the Y-axis to define a width thereof. The width of each fin 118' may range from about 3 nanometers to about 20 nanometers. Further, a distance between each single fin 118' in the Y-axis direction defines a fin pitch. At least one exemplary embodiment provides a fin pitch corresponding to the plurality of fins 118 ranging from about 8 nanometers (nm) to about 50 nanometers (nm). Accordingly, by forming the fins 118 in the gate pocket 116 and between the first and second S/D regions 106/106', fin erosion during gate and spacer patterning processes may be avoided. Moreover, at least one exemplary embodiment of the present teachings provides forming fins 118 in only the gate pocket 116 of the gate region 104, and not the S/D regions 106/106'. As a result, an epitaxy (EPI) process for merging fins located in the S/D regions may be eliminated as discussed in greater detail below.

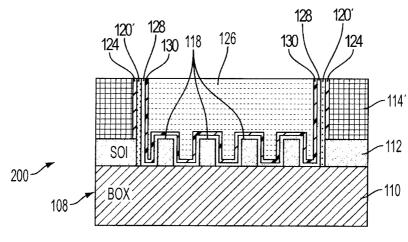

[0080] Referring now to FIGS. 5A-5B, a spacer layer 120 may be disposed on the masking layer 114. More specifically, the spacer layer 120 may be deposited on an upper surface of the masking layer 114, and into the gate pocket 116 to cover the plurality of fins 118. The spacer layer 120 may be made, for example, of SiN. Thereafter, portions of the spacer layer 120 may be etched away to expose upper surfaces of the masking layer 114, as illustrated in FIGS. 6A-6B. Further, the spacer layer 120 may be etched away from the fins 118 and the surface of the gate pocket 116 to expose the buried oxide layer 110. Various etching techniques may be used to remove the spacer layer including, but not limited to, reactive-ion etching (RIE). Accordingly, the spacer layer 120 is left to remain on the wall 119 of the gate pocket 116 to define spacers 120'.

[0081] Referring now to FIGS. 7-14, a gate stack, i.e., gate, is formed in the gate pocket 116 of the SOI wafer 108 illus-

trated in FIGS. **6A-6B**. The gate may be formed using a variety of conventional methods including, but not limited to, a replacement metal gate process, i.e., gate-last process.

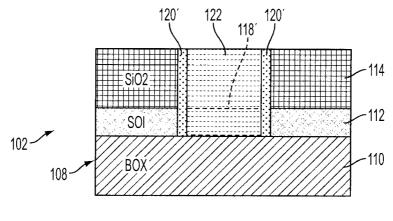

[0082] As illustrated in FIGS. 7A-7B, for example, a dummy gate 122 may be formed in the gate pocket 116. The dummy gate 122 may be formed of various material including, but not limited amorphous silicon and polysilicon. The dummy gate 122 may also be etched such that it is flush with the upper surface of the masking layer 114. Various methods for etching the dummy gate 122 may be used including, but not limited to, dry etching and chemical-mechanical polishing (CMP).

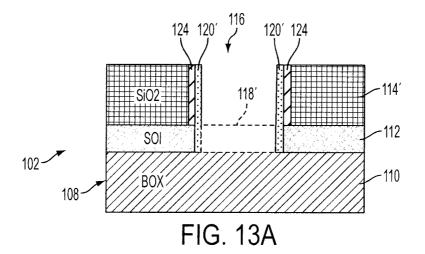

[0083] Additional procedures during the replacement metal gate process may be performed on the semiconductor device 100. For example, the initial masking layer 114 may be removed to expose the spacers 120' disposed against the walls 119 of the gate pocket 116 as illustrated in FIGS. 8A-8B. An extension of the initial spacers 120' may be achieved by implanting ions (+), as illustrated in FIGS. 9A-9B. FIGS. 10A-10B illustrated a second spacer 124 formed against the initial spacer 120' to protect gate region 104 during S/D region 106/106' diffusion. Ion implantation (+) to form the S/D regions 106/106' is illustrated in FIGS. 11A-11B, and a new flowable oxide layer 114' such as silicon oxide (SiO<sub>2</sub>) may be formed on an upper surface of the semiconductor, and may act as a new masking layer 114' as illustrated in FIGS. 12A-12B.

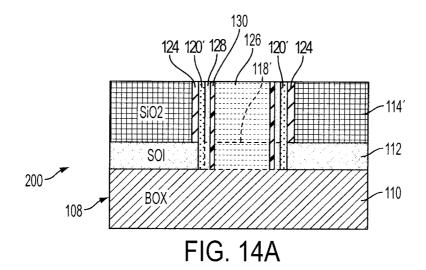

[0084] Referring now to FIGS. 13A-13B, the dummy gate 122 may be removed, i.e., pulled out, to re-expose the gate pocket 116, and a gate stack 126 may be formed in the re-exposed gate pocket 116, as illustrated in FIG. 14A-14B. The gate stack 126 may include a gate insulation layer 128 made of a high dielectric constant (high-k) material. The high-k material may include, but is not limited to, hafnium dioxide (HfO<sub>2</sub>), hafnium silicon oxynitride (HfSiON), or zirconium dioxide (ZrO<sub>2</sub>). The gate stack **126** may further include a metal electrode 130 coupled to the insulation gate layer to prevent Fermi-level pinning and increase electrical conduction at the gate stack 126. The metal electrode 130 may be formed of a metal-gate forming material including but not limited to, lanthanum (La), aluminum (Al), magnesium (Mg), ruthenium (Ru), titanium-based materials such as titanium (Ti) and titanium nitride (TiN), tantalum-based materials such as tantalum (Ta) and tantalum nitride (TaN) or tantalum carbide (Ta<sub>2</sub>C), or the like. The gate stack 126 may be planarized using various processes including, but not limited to, CMP, such that the gate stack 126 is flush with new masking layer 114'.

[0085] Accordingly, FIGS. 14A-14B illustrate a fabricated semiconductor structure 100, such as a FinFET device 200 according to at least one exemplary embodiment of the present teachings. The FinFET device 200 includes an SOI wafer 108 having a plurality of fins 118 formed in only the gate pocket 116 of the gate region 104, which is located between the S/D regions 106/106'. That is, no fins 118 are formed in the S/D regions 106/106'. Therefore, the conventional process of epitaxially merging fins formed in the S/D regions may be eliminated from the fabrication process, thereby reducing overall processing and material costs. Further, since the gate patterning is initially performed in preparation for fin formation, the fins are prevented from being eroded during a gate patterning process.

[0086] In addition to forming fins in a gate region of a semiconductor substrate without forming fins in the non-gate

regions, the present teachings allow for the formation of hanging fins and nanowire fins to produce a semiconductor FinFET device having a reduced size.

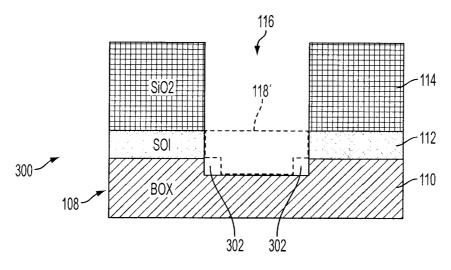

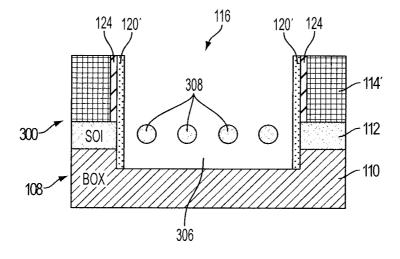

[0087] Referring to FIGS. 15-27, block diagrams corresponding to a process flow of fabricating a semiconductor structure 100, such as a FinFET device 300, are illustrated according to an exemplary embodiment of the present teachings. The process flow of fabricating the FinFET device 300 is similar to the process flow illustrated in FIGS. 1-14 discussed above. The FinFET device 300 includes an active SOI layer 112 formed between a buried insulation layer 110 and a masking layer 114.

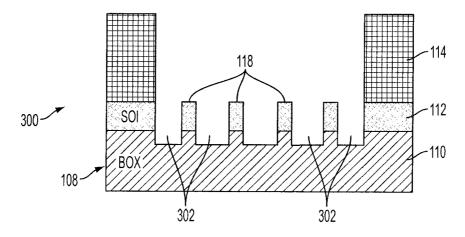

[0088] In at least one exemplary embodiment illustrated in FIG. 15A-15B, however, the buried insulation layer 110 is recessed below the active SOI layer 112 after forming the plurality of fins 118, thereby forming a recessed buried insulation region 302. After a spacer layer 120 is formed on the SOI substrate 108, and an etching procedure is performed to form spacers 120', as illustrated in FIGS. 16-17 according to the processes described above, a portion of the buried insulation layer 110 beneath the fins 118 is removed to form hanging fins 304, as illustrated in FIGS. 18A-18B. The hanging fins 304 are supported by walls 119 of the gate pocket 116, and are separated from the recessed buried insulation layer 302 by a predetermined distance. For example, the hanging fins may be separated from the recessed buried insulation layer by a distance of about 3 nanometers (nm) to about 20 nanometers (nm) such that a void area 306 is formed between a lower surface of the hanging fins 304 and the recessed buried insulation layer 302. Similar to the teachings described above, the walls 119 of the gate pocket 116 may isolate the hanging fins 304 from the non-gate regions 106/106', e.g., S/D regions, of the semiconductor structure 100.

[0089] The hanging fins 304 may undergo an annealing process that forms nanowire fins, i.e., nanowires 308, as illustrated in FIGS. 19A-19B. According to at least one exemplary embodiment of the present teachings, the nanowires 308 have a cylindrical shape, but are not limited thereto. That is, the nanowires 308 may have any shape that allows for reducing the overall size of the semiconductor device 100. Furthermore, nanowires may be sized small enough that the resulting low density allows the nanowires to be considered as onedimensional (1-D) nanostructures. Therefore, the dimensions of the nanowires 308 may be based on a diameter:length aspect ratio. According to at least one exemplary embodiment of the present teachings, the nanowires 308 have a diameter: length aspect ratio of about 1:1. Due to the small diameter of the nanowires 308, the gate region 104 may be increased to cover a larger area of the semiconductor structure 100. For example, the semiconductor device may be designed according to a wrap-gate architecture such that the gate region 104, and thus the nanowires 308, wrap completely around the semiconductor structure 100, as opposed to only two gate regions offered by the traditional dual-gate FinFET architecture.

[0090] After the nanowires 308 are formed, the semiconductor device 100 may undergo replacement metal gate procedure and S/D region formation according to the process described above to form the gate stack 126 in the gate pocket 116 as illustrated in FIGS. 20-27.

[0091] Referring to FIG. 28, a flow diagram illustrates a method of fabricating a semiconductor structure according to an exemplary embodiment of the present teachings. At operation 2800, a semiconductor substrate is formed. The semicon-

ductor substrate may include a silicon-on-insulator (SOI). A gate pocket may be formed at a gate region of the semiconductor substrate at operation 2802. The gate pocket may extend through layers of the SOI substrate to expose an active silicon layer. At operation 2804, semiconductor fins are formed in the gate pocket. The fins may be supported by walls of the gate pocket. Moreover, walls of the gate pocket may isolate the plurality of fins from non-gate regions of the semiconductor substrate. For example, the gate pocket may isolate the fins from S/D regions of the semiconductor substrate. At operation 2806, the semiconductor substrate is oxidized to prepare the surface of the substrate for forming a spacer layer thereon. Accordingly, a spacer layer is formed on the semiconductor device such that the fins are covered. The spacer layer is removed from upper surfaces of the substrate and the fins at operation 2808, thereby leaving spacers disposed against walls of the gate pocket.

[0092] At operation 2810, a gate material is deposited in the gate pocket, which covers the fins. The gate material may also undergo chemical-mechanical polishing (CMP) procedure such that deposited gate material is flush with the upper surface of the semiconductor substrate. Flowable oxide, such as a silicon oxide (SiO<sub>2</sub>) layer, which is disposed on the active silicon layer may be removed using conventional processes at operation 2812. At operation 2814, the semiconductor substrate may undergo an ion implantation to increase the volume of the spacers, and a second spacer may be formed against the extended spacer at operation 2816. At operation 2818, ions are implanted in the non-gate regions to form S/D regions. That is, a first non-gate region existing at first side of the gate region may be implanted with ions to form a source region, and a second non-gate region located on an opposite side of the gate-region may be implanted with ions to form a drain region. A second flowable oxide, such as SiO<sub>2</sub>, is formed on an upper surface of the semiconductor substrate at operation 2820. At operation 2822, the gate material deposited in the gate pocket is removed to re-expose the gate pocket and fins, and metal gate replacement process is performed such that a metal gate material different from the gate material utilized at operation 2810 is deposited in the gate-pocket to cover the fins, and the method ends.

[0093] Accordingly, fins may be formed in a gate region and between first and second S/D regions, without requiring fins to extend into the S/D regions of the semiconductor structure. Since no fins exist in the S/D regions, a merging procedure to merge the fins in the S/D regions is excluded. Further, since no etching procedure is required to etch fins merged in the S/D regions, erosion and damage of the fins existing in the source/drain region caused by a merged-fin etching process is prevented.

[0094] Referring to FIG. 29, a flow diagram illustrates another method of fabricating a semiconductor structure according to an exemplary embodiment of the present teachings. The exemplary method illustrated in FIG. 29 is similar to method illustrated in FIG. 28 discussed in detail above, but includes additional features of forming hanging fins and nanowires. More specifically, a semiconductor substrate, such as a SOI substrate, is formed and a gate pocket is formed at a gate region of the substrate at operations 2900 and 2902, respectively. At operation 2904, the gate pocket is recessed to form a recessed region in a layer of the substrate, for example the buried insulation layer. At operation 2906, semiconductor fins are formed in the gate pocket. The substrate and fins are oxidized and a spacer layer is formed thereon at operation

2908. At operation 2010, the spacer layer is partially removed to form spacers on the walls of the gate pocket. Turning now to operation 2912, a portion of the substrate located beneath the fins is removed to form hanging fins. Accordingly, a void area is defined between the recessed layer of the gate pocket and the plurality of fins such that a plurality a hanging fins are formed. The hanging fins undergo an annealing process at operation 2914, which transforms the hanging fins into nanowire fins, i.e., nanowires. A dummy gate is formed at operation 2916 by depositing an amorphous and/or polysilicon in the gate pocket at operation 2916. At operation 2918 the initial hardmask layer may be removed, and the spacers may be extended via ion implantation at operation 2920. A second spacer may be disposed against each of the initial spacers at operation 2922. At operation 2924, the source/ drain regions may be formed via ion implantation and a second hardmask may be formed on an upper surface of the substrate at operation 2926. At operation 2928, a replacement metal gate process may be performed to form a metal gate in the gate pocket, and method ends. By forming nanowires in the gate pocket, the gate region of the semiconductor structure may be increased to cover a larger area of the semiconductor structure. Therefore, the overall size of the semiconductor structure may be reduced.

[0095] The terminology used herein is for the purpose of describing exemplary embodiments only and is not intended to be limiting of the teachings. As used herein, the singular forms "a", "an" and "the" are intended to include the plural forms as well, unless the context clearly indicates otherwise. It will be further understood that the terms "comprises" and/or "comprising," when used in this specification, specify the presence of stated features, integers, steps, operations, elements, and/or components, but do not preclude the presence or addition of one more other features, integers, steps, operations, element components, and/or groups thereof.

[0096] The flow diagrams depicted herein are just one example. There may be many variations to this diagram or operations described therein without departing from the spirit of the teachings. For instance, the operations may be per-

formed in a differing order or operations may be added, deleted or modified. All of these variations are considered a part of the claimed teachings.

[0097] While exemplary embodiments to the present teachings have been described, it will be understood that those skilled in the art, both now and in the future, may make various changes the teachings which fall within the scope of the claims described below.

- 1. A semiconductor device having first and second nongate regions, comprising:

- an active semiconductor layer disposed on an insulation layer:

- a gate pocket through the active semiconductor layer and the insulation layer, the gate pocket defining a recessed gate insulation region between the first and second nongate regions; and

- a plurality of fins supported by walls of the gate pocket, wherein a portion of the recessed gate insulation region located beneath the plurality of fins defines a void between each fin among the plurality of fins and the recessed gate insulation region.

- 2. The semiconductor device of claim 1, wherein the recessed gate insulation region extends below the insulation layer at a predetermined depth.

- 3. The semiconductor device of claim 2, wherein the gate pocket has a depth that reaches the recess gate insulation region.

- **4**. The semiconductor device of claim **3**, further comprising arranging the plurality of fins sequentially in the gate pocket.

- 5. The semiconductor device of claim 4, wherein the gate insulation layer extends along a first direction to define a gate length, and each fin among the plurality of fins extends along the first direction to define a fin length not exceeding the gate length

- **6**. The semiconductor device claim **5**, further comprising a gate stack in the gate pocket to cover the plurality of fins.

- 7. The semiconductor device of claim 1, wherein the plurality of fins comprises nanowires.

\* \* \* \* \*