(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2012년07월03일

(11) 등록번호 10-1152859

(24) 등록일자 2012년05월29일

- (51) 국제특허분류(Int. C1.)

*G01J 1/20* (2006.01)

- (21) 출원번호 10-2008-7009556

- (22) 출원일자(국제) 2006년09월21일

심사청구일자 2008년04월21일

- (85) 번역문제출일자 2008년04월21일

- (65) 공개번호 10-2008-0050623

- (43) 공개일자 2008년06월09일

- (86) 국제출원번호 PCT/US2006/036794

- (87) 국제공개번호 WO 2007/035861

국제공개일자 2007년03월29일

- (30) 우선권주장

60/719,304 2005년09월21일 미국(US)

(뒷면에 계속)

- (56) 선행기술조사문현

US20020176067 A1\*

US5416616 A

US6188056 B1

US6821245 B2

- \*는 심사관에 의하여 인용된 문현

(73) 특허권자

알제이에스 테크놀로지, 인코포레이티드

미국 뉴 햄프셔 03049, 홀리스, 플래그 로드 19

(72) 발명자

다비도비치, 소린

미국, 뉴저지 07757, 오션포트, 메인 스트리트 160

(74) 대리인

특허법인이지

전체 청구항 수 : 총 12 항

심사관 : 송병준

(54) 발명의 명칭 높은 동적 범위의 감지 센서 소자 또는 배열을 위한 시스템 및 방법

**(57) 요약**

높고 낮은 세기의 이미지들을 정확히 캡쳐하기 위해 위상 도메인 적분 기술을 이용하는 높은 동적 범위 감지 센서 소자 또는 배열이 제공된다. 본 발명의 센서 소자는 선행기술에 의해 공지된 고체 상태 광셀 구조들에 나타난 동적 범위 특징들에 의해 제한되지 않으므로 따라서 높은 품질의 출력 이미지를 제공하기 위하여 전자기 복사에너지 전체 범위를 캡쳐할 수 있다.

대 표 도 - 도16

(30) 우선권주장

60/719,305 2005년09월21일 미국(US)

60/719,306 2005년09월21일 미국(US)

60/727,897 2005년10월18일 미국(US)

---

## 특허청구의 범위

### 청구항 1

픽셀 구조로부터 확장된 동적 범위의 판독 신호를 획득하는 방법에 있어서,

충돌하는 전자기 복사에너지에 대한 감광 소자 응답의 적분 값을 상기 응답에 관련된 위상 정보를 이용하여 생성하는 단계를 포함하되,

상기 감광 소자는 시간 주기 동안 상기 전자기 복사에너지에 노출되고,

상기 생성하는 단계는, 시간 주기의 마지막에서 출력 파형의 위상을 식별하는 단계 및 상기 출력 파형에 의해 이동된 주기들의 합을 누적하는 단계를 더 포함하며, 상기 적분 값은 상기 위상 및 상기 주기들의 합에 의하여 결정되는 판독 신호 획득 방법.

### 청구항 2

제1항에 있어서,

상기 위상 정보는,

상기 감광 소자의 응답을 수신하고, 상기 응답에 따라 주파수가 변하는 출력 파형을 제공하기 위해 결합된 전압 제어 발진기에 의해 제공되는 판독 신호 획득 방법.

### 청구항 3

제2항에 있어서,

상기 생성하는 단계는,

상기 출력 파형의 이동된 위상을 누적하는 단계를 포함하는 판독 신호 획득 방법.

### 청구항 4

제2항에 있어서,

상기 전자기 복사에너지의 세기에 따른 상기 전압 제어 발진기의 주파수를 조절하는 단계를 더 포함하는 판독 신호 획득 방법.

### 청구항 5

전자기 복사에너지에 응답하여 신호를 생성하는 감광 소자; 및

상기 감광 소자와 결합되고, 위상 정보를 이용하여 노출 시간 주기 동안 상기 전자기 복사에너지에 대한 상기 감광 소자의 응답을 적분하는 위상 적분기를 포함하되,

상기 위상 적분기는 상기 감광 소자로부터의 상기 신호의 값에 응답하여 출력 파형을 제공하기 위해 결합된 발진기를 더 포함하며,

상기 위상 적분기는 적분 주기 동안 상기 출력 파형의 이동된 위상을 누적하기 위한 로직을 포함하며,

상기 이동된 위상을 누적하기 위한 상기 로직은 상기 적분 주기의 시작과 끝 사이에서 상기 출력 파형의 위상 차이를 식별하기 위한 로직을 포함하는 픽셀 구조.

### 청구항 6

제5항에 있어서,

상기 누적하기 위한 로직은,

상기 발진기에 의해 제공되는 상기 출력 파형의 주기들의 합을 누적하는 누적기를 포함하는 픽셀 구조.

### 청구항 7

제5항에 있어서,

상기 발진기는,

상기 신호의 세기에 따라 상기 발진기의 주파수를 조절하기 위한 입력부를 포함하는 팩셀 구조.

### 청구항 8

제5항에 있어서,

상기 발진기는,

전압 제어 발진기인 팩셀 구조.

### 청구항 9

제5항에 있어서,

상기 발진기는,

전류 제어 발진기인 팩셀 구조.

### 청구항 10

제5항에 있어서,

상기 팩셀 구조는,

상기 광 감지 소자로부터 입력 신호들에 응답하여 큰 출력을 생성하는 팩셀 구조.

### 청구항 11

제5항에 있어서,

상기 팩셀 구조는.

상기 감광 소자로부터 신호들이 커지는 경우 포화 상태를 피하는 팩셀 구조.

### 청구항 12

이미지를 캡쳐하는 방법에 있어서,

노출 기간 동안 센서 신호를 생성하기 위해 전자기 복사에너지에 감광 소자를 노출하는 단계; 및

적분기 결과인 상기 센서 신호에 응답하여 발진기에 의해 생성되는 발진 파형을 제공하기 위해 상기 노출 기간 동안 상기 발진 파형의 이동된 위상을 누적하는 단계를 포함하되,

상기 이동된 위상을 누적하는 단계는, 시간 주기의 마지막에서 출력 파형의 위상을 식별하는 단계 및 상기 출력 파형에 의해 이동된 주기들의 합을 누적하는 단계를 더 포함하며, 상기 적분 값은 상기 위상 및 상기 주기들의 합에 의하여 결정되는 이미지 캡쳐 방법.

### 청구항 13

삭제

### 청구항 14

삭제

### 청구항 15

삭제

### 청구항 16

삭제

## 명세서

### 기술분야

[0001]

본원은 다비도비치 등에 의해 2005년 10월 18일에 출원된 가특허 출원 제60/727,897호 및 다비도비치 등에 의해 2005년 9월 21일에 출원된 가특허 출원 제60/719,306호, 제60/719,304호 및 제60/719,305호에 대한 우선권을 35 U.S.C. § 1.119(e)에 따라 주장한다. 상기 식별된 우선 출원들 모두 여기에 참조로써 통합된다. 본 발명은 일반적으로 전자 영상 분야에 관한 것으로, 더욱 상세하게는 광 세기의 측정 및 분석을 이용하여 양질의 이미지를 캡처하는 방법 및 장치에 관한 것이다.

### 배경기술

[0002]

사진술은 빛의 활동에 의해 상을 생성하는 과정이다. 빛은 인간의 눈에 보이는 주파수 대역인 전자기 복사에너지(Visible Light Energy)를 지칭하는데 일반적으로 사용되는 용어이다. 물체로부터 반사된 또는 방사된 빛 패턴들은 일정 시간의 노출을 통하여 이미지 센서에 의해 기록된다. 이미지 센서들은 사진 필름과 같이 본질적으로 화학 제품일 수 있으며, 또는 디지털 스템용 카메라 및 비디오 카메라에 사용되는 CCD 및 CMOS 이미지 센서와 같이 본질적으로 고체 상태일 수 있다.

[0003]

디지털 카메라들은 한 장면의 이미지를 생성하기 위해 빛을 집중하는 일련의 렌즈들을 포함한다. 그러나, 종래의 카메라와 같이 필름 위에 빛을 집중하는 대신에 일련의 렌즈들은 빛의 전자기 복사에너지를 전하로 변환하는 이미지 센서 위에 빛을 집중한다. 이미지 센서는 사진 요소 또는 핀셀로 불린다. 전하는 이미지 센서에 의해 인식된 전자기 복사에너지의 상대적인 세기를 나타내고, 일반적으로 광 세기 값은 핀셀과 관련되며 한다.

[0004]

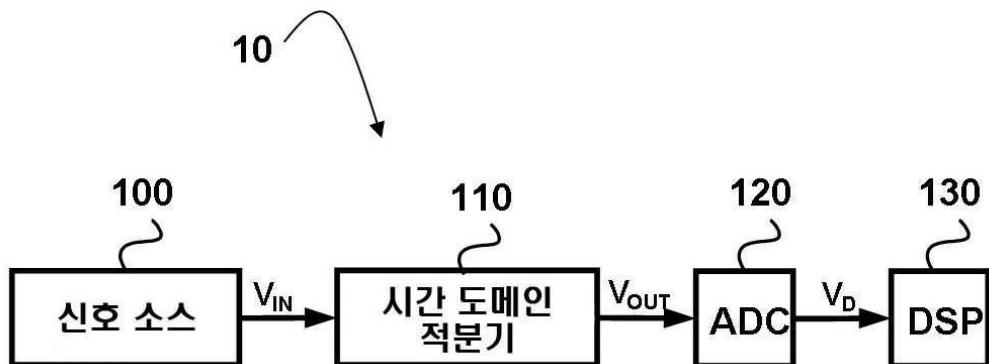

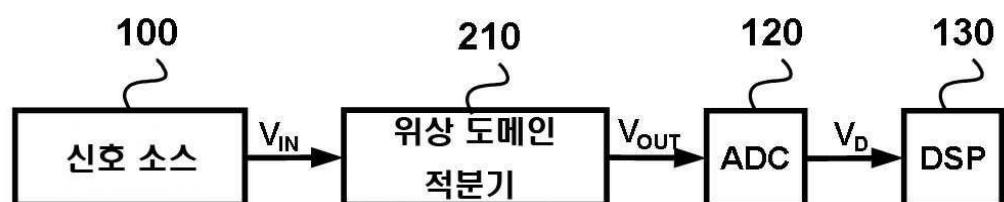

도 1은 디지털 이미지 처리 시스템(10)에 포함될 수 있는 일반적인 구성 블록을 나타낸다. 상기 시스템(10)은 신호 소스(100)와 적분기(110), 아날로그 디지털 변환기(ADC)(120) 및 DSP(130)을 포함하는 신호 처리 체인을 포함한다. 신호 소스(100)는 예를 들면 빛이 거기에 충돌하는 전자기 복사에너지에 대응하여 전기적 응답을 생성하는 광 세기 센서와 같은 센서가 될 수 있다.

[0005]

적분기(110)의 출력  $V_{out}$ 은 ADC(120)에 입력된다. ADC(120)는 아날로그를 디지털로 변환하는 기능을 수행한다. 아날로그를 디지털로 변환하는 기능은 해당 기술분야에 잘 알려져 있다. ADC(120)의 입력에 있는 아날로그 신호  $V_{out}$ 은 이산 레벨들의 집합 중 하나를 취할 수 있는 신호 VD로 변환된다.

[0006]

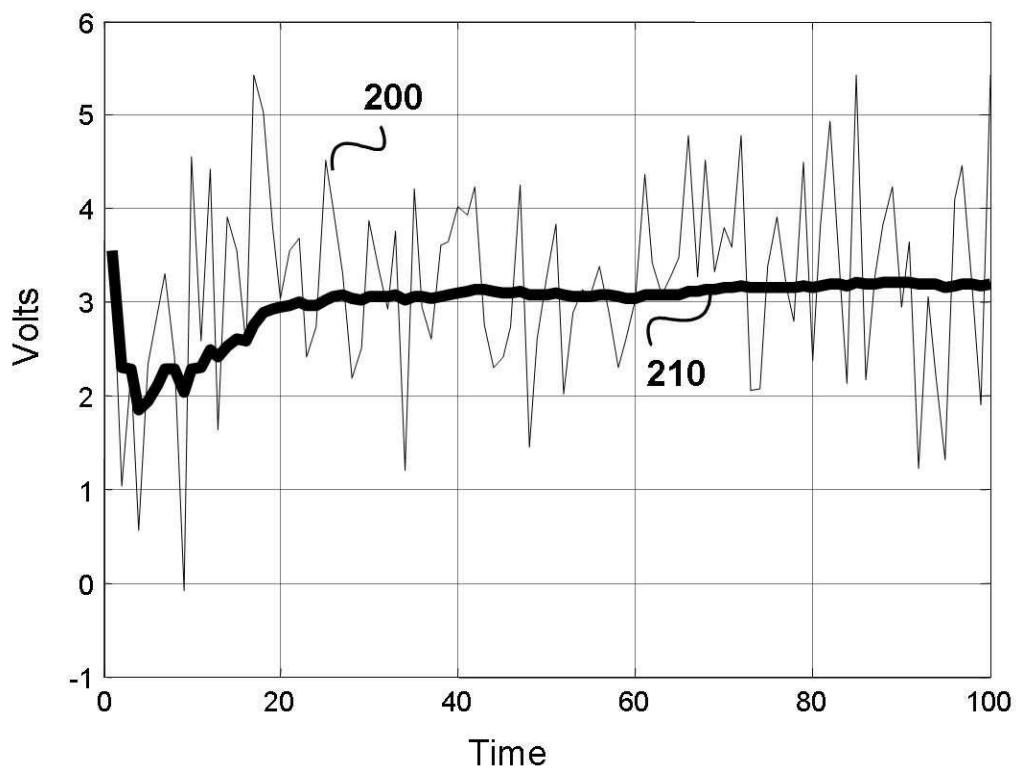

신호의 품질은 신호  $V_{in}$ 를 적분하는 적분기(110)에 의해 개선된다. 도 2는 개선된 신호의 특징을 도시한다. 과형(200)은 신호 소스(100)에 의해 생성된 상수 신호와 상수 신호를 왜곡시키는 부가 잡음의 결합이다. 과형(210)은 입력 신호 과형(200)에 응답하여 생성된 적분기 출력이다. 과형(210)에서 부가 잡음에 의해 야기된 신호 변동이 감소되었음을 쉽게 관찰할 수 있다.

[0007]

신호 소스(100)는 일반적으로 노출 시간이라 불리는 특정 시간 동안 센서가 빛에 노출되는 디지털 카메라 어플리케이션과 같은 시한적 어플리케이션에서 사용되는 광 세기 센서가 될 수 있다. 또한 적분기(110)는 노출 시간 동안 수신된 모든 광자에 의해 야기된 센서(100)의 응답을 예를 들면 전압과 같이 노출 시간의 마지막에 판독될 수 있는 하나의 값으로 적분하는 기능을 수행한다.

[0008]

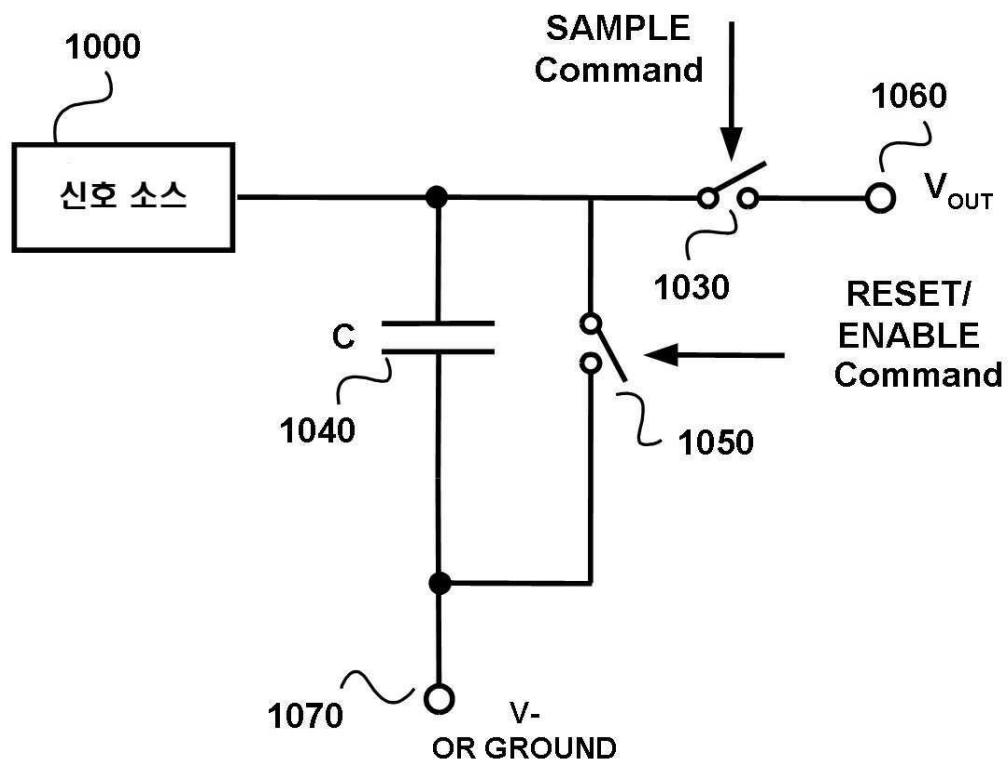

도 3은 대표적인 이미지 센서 회로를 나타낸다. 신호 소스(1000)는 일예로 포토다이오드라 불리는 광 센서이다. 커패시터(1040)는 단순한 적분기이다. 적분기의 입력은 신호 소스(1000)의 출력 값이다. 커패시터(1040)는 적분 처리를 시작하기 전에 닫힌 상태에 있는 스위치(1050)에 의해 리셋된다. 적분 처리의 시작 시, 스위치(1050)는 개방되고, 커패시터(1040) 양단의 전압은 신호 소스(1000)에서 시작된 입력 신호에 응답하여 변하기 시작한다. 적분 처리의 종료 시, 스위치(1030)는 닫히며, 적분기 출력(1060)인  $V_{out}$ 이 샘플링된다. 도 3은 예시적인 도면이다. 동일한 기능을 갖는 다른 유사한 적분기들의 구현은 본 기술분야의 당업자에게 자명하며 잘 알려져 있다.

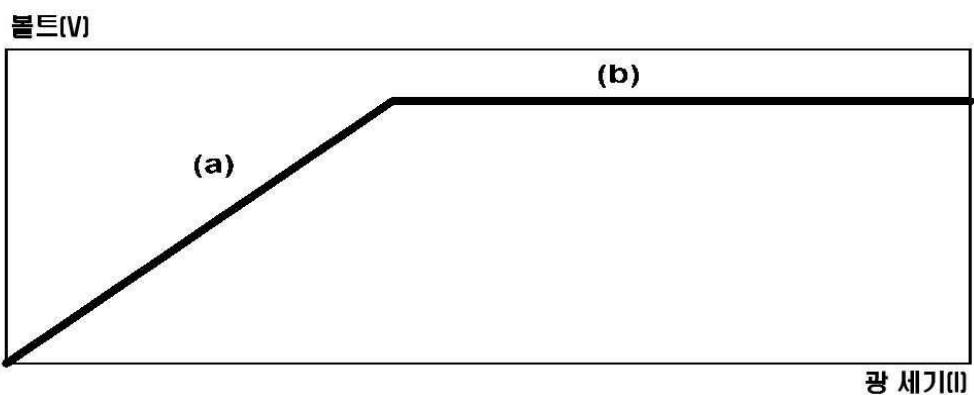

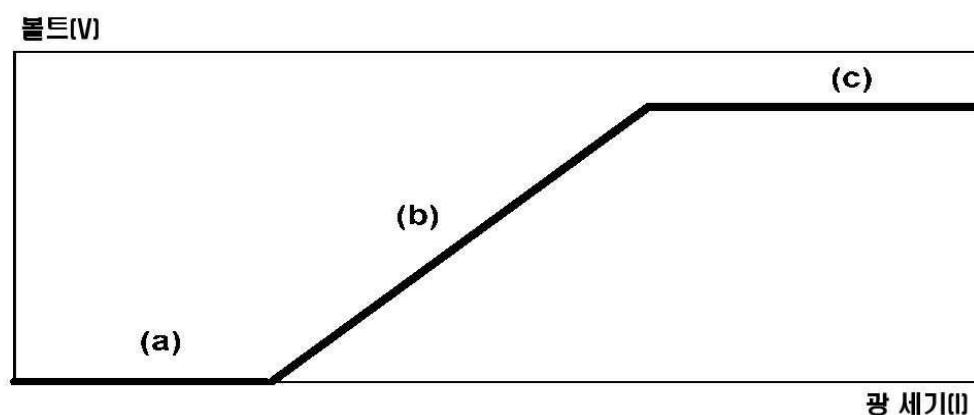

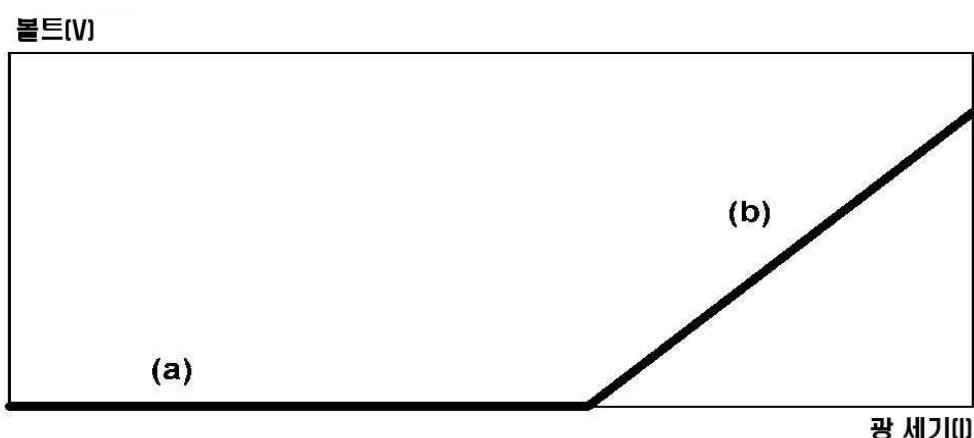

- [0009] 적분기 출력(1060)인  $V_{out}$ 은 이용 가능한 전력 공급 전압에 의해 부과된 상한을 일반적으로 초과할 수 없다. 전력 공급 전압은 엄격한 전원 소비 요구에 인해 최신 장비에서 감소하고 있다. 적분기 출력(1060)은 전력 공급 전압을 초과할 수 없고, 전력 공급 전압 수준에 도달한 후에도 계속하여 적분기 출력을 생성한다면 적분기 출력(1060)은 포화될 것이다. 포화 상태는 도 4에 나타난다. 포화 상태는 출력 전압이 이용 가능한 전력 공급 전압에 도달하고, 출력 전압이 입력 신호에서 더 많은 변화에 대해 응답할 수 없는 경우 발생한다. 신호 포화는 시스템 성능의 하락을 야기한다. 도 4A 내지 도 4C는 감광 소자 구조의 동적 범위 제한, 더 명확하게는 적분기 구조의 동적 범위 제한에 따른 광 센서(100) 및 적분기(110)를 포함하는 픽셀 구조의 출력에서 잠재적인 왜곡을 설명한다.

- [0010] 도 4A의 세그먼트 (a)는 다른 레벨의 일정한 입력 신호에 대응하는 적분기(110) 출력의 선형 증가를 나타낸다. 이미지 센서 구조는 세그먼트 (a)와 같은 선형 출력으로 증가하는 입력 광 세기들의 범위에서 잘 동작할 것이고, 이미지 센서 구조는 세그먼트 (b)와 같은 포화 상태의 출력으로 증가하는 입력 광 세기들의 범위에서 잘 동작하지 않을 것이다.

- [0011] 적분기 출력 응답은 제한된 동적 범위를 나타낸다. 도 4A에 도시된 것과 같이 이미지 센서는 쉐도우 디테일은 잘 나타낼 것이나, 하이라이트 디테일을 나타내는 데는 실패할 것이다. 도 4B 및 도 4C에 나타난 것과 같이 응답을 이동시키는 것은 가능하다. 도 4B 및 도 4C에서 이미지 센서의 동적 범위는 동일하게 남아있으나, 응답 부분은 이동되었다. 도 4B의 응답 부분은 쉐도우 및 하이라이트 디테일은 잃어버리게 되나, 중간범위의 반응은 계속 유지한다. 도 4C의 응답 부분은 좋은 하이라이트 디테일을 유지하기 위해 쉐도우 디테일 및 중간 범위의 디테일은 잃어버리게 된다.

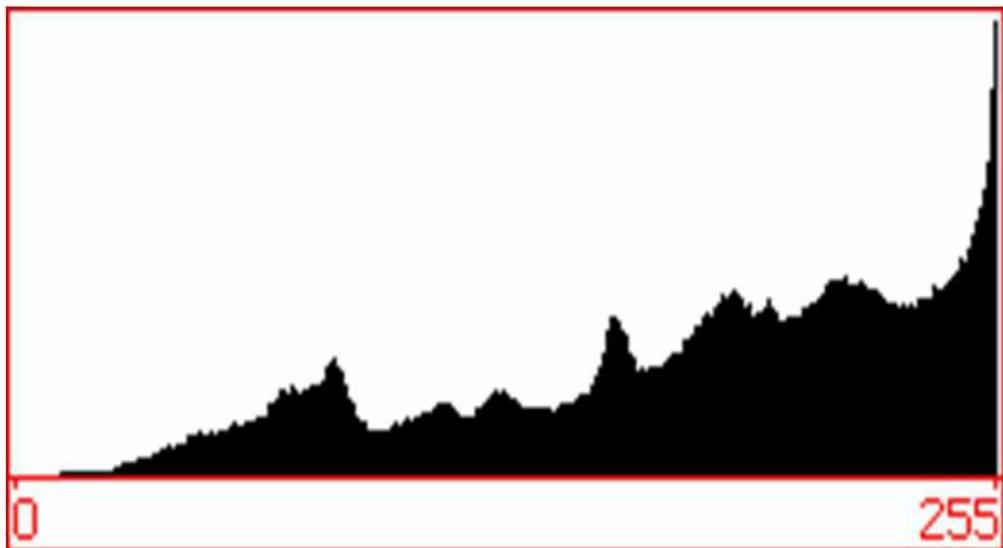

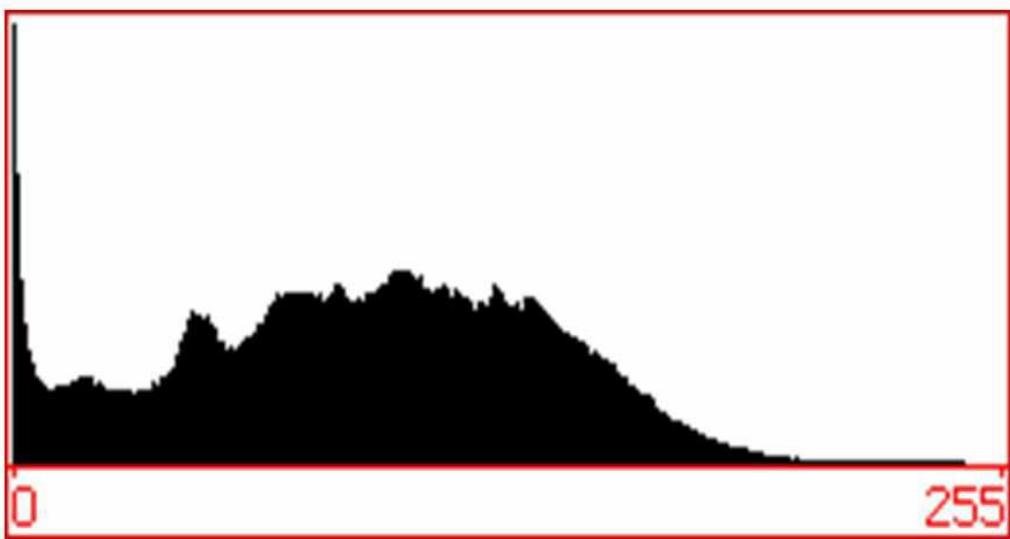

- [0012] 도 5A는 도 4A와 같은 다수의 픽셀들이 포화상태로 진입하는 과다 노출된 이미지 캡쳐의 히스토그램을 나타낸다. 도 5A에 도시된 것과 같이 최대 픽셀 구조 출력 값은 '255'이고, 사용된 유닛들은 픽셀 출력 전압과 일치하는 ADC(120) 출력이다. 광 세기는 많은 광 센서들(100)이 노출 기간 동안 노출이 진행된 적분기(110)를 포화시킨 값을 출력하도록 한다. 적분기(110) 출력의 최대(포화)값은 ADC가 8비트 ADC에서 최대 출력 코드인 출력 코드 '255'를 생성하도록 한다. 이미지 캡쳐는 이러한 픽셀들이 충분히 높은 출력 레벨을 획득하기 위한 높은 세기의 광 입력을 제시하는 것이 불가능하므로 차선의 질보다 낮아질 것이다. 255보다 낮은 출력을 등록하고, 상단 왜곡을 피하기 위해 낮은 적분기(110) 이득은 광 이미지 센서의 출력이 높은 광 세기 입력을 제시하는 원인이 되곤 하였다.

- [0013] 도 5B는 다수의 픽셀들이 최소한의 출력 값을 획득하기 위한 충분한 빛에 노출되지 않은 노출부족인 이미지 캡처의 픽셀 세기들의 히스토그램을 나타낸다. 도 5B에서 볼 수 있듯이, 최소 픽셀 구조 출력 값은 '0'이고, 사용된 단위는 픽셀 출력 전압과 일치하는 ADC(120) 출력이다. 광 세기는, 많은 광 센서들(100)이 노출 기간 동안 노출이 진행된 적분기(110)가 최소한의 ADC 출력 코드를 야기할 정도로 충분히 높은 값을 출력하게 하지 못한 값을 출력하도록 한다.

- [0014] 이미지 캡쳐는 이러한 픽셀들이 충분히 높은 출력 레벨을 획득하기 위한 높은 세기의 광 입력을 제시하는 것이 불가능하므로 차선의 질보다 낮아질 것이다. 도 5B의 히스토그램에서 나타난 왜곡은 도 4C의 개별적인 픽셀 왜곡에 대응된다. 더 높은 적분기(110) 이득은 낮은 광 세기에 영향을 받는 광 이미지 센서의 출력이 0보다 큰 출력을 등록하고, 하단 왜곡을 피하게 된다.

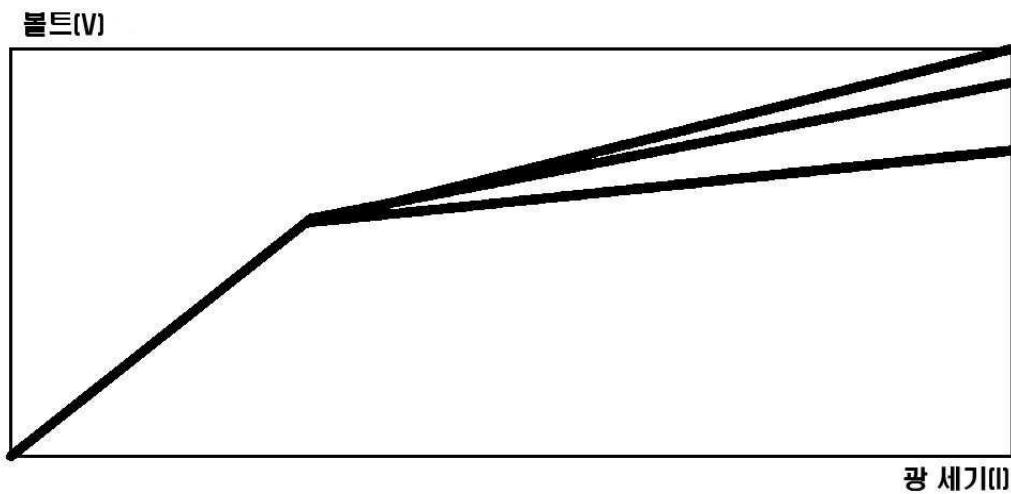

- [0015] 도 6은 더블-슬로프 기술을 사용하여 생성된 픽셀 구조의 커브 응답을 나타낸다. 도 6에서 나타난 동적 범위의 비선형 확장은 포화 효과를 피한다. 그러나, 센서에 충돌하는 전자기 에너지의 세기와 센서의 출력 사이의 비선형적인 관계는 높은 레벨의 광 세기가 존재하는 경우 해상도가 감소된 이미지가 캡쳐되는 것을 유발한다.

- [0016] 복수의 노출 조합, 조건부의 슬로프 스위칭 및 로그 응답 픽셀 구조들과 같은 다른 접근 방법은 공지되어 있다. 복수의 노출 결합, 조건부 슬로프 스위칭 및 로그 응답 픽셀 구조들은 높은 품질의 이미지를 획득하기에 적합하지 않도록 하는 품질 하락을 나타낸다.

- [0017] 적분 포화는 픽셀 구조의 동적 범위 수행에서 제한된 요소이다. 적분 포화 문제를 해결하는 방법들은 공지되어 있다. 공지된 해결책 중 하나는 적분기가 방전되고, 이벤트가 기록되는 시점에 포화 상태에 도달하는 것을 보호하기 위해 일반적인 적분 출력을 모니터링 하는 것이다. 이 수준의 해결책은 아날로그 성분과 비정형적인 아날로그 구현의 정확한 요구 때문에 접적 회로(ICs)로 효율적으로 구현하기가 어렵다. 적분기의 출력이 포화되기 시작하는, 전력 공급 전압 부근의 잡음이 심한 환경에서 동작하는 정확한 비교기의 구현은 과다한 전원을 소비하고, 바람직하지 않은 동작 특성이 있는 어려운 일이다.

[0018] 아날로그 IC 설계들은 어렵고, 구현하는데 시간이 소비된다. 완벽하게 디버그 되고, 최적의 사이즈, 전원 소비 및 수행을 갖는 표준 빌딩 블록들을 사용하는 것이 유리하다. 공지된 기술은 상기 요구를 해결하지 못한다.

### 발명의 상세한 설명

- [0019] 본 발명의 일 실시예에 따르면, 픽셀 구조로부터 높은 동적 범위 판독 신호를 획득하는 방법은 응답과 관련된 위상 정보를 사용하여 전자기 복사에너지와 충돌하는 감광 소자의 응답의 적분된 값을 생성하는 단계를 포함한다.

- [0020] 본 발명의 다른 실시예에 따르면, 픽셀 구조는 전자기 복사에너지에 대응하는 신호를 생성하는 감광 소자 및 감광 소자와 결합되고, 위상 정보를 이용하여 노출 시간 주기 동안 전자기 복사에너지에 대한 감광 소자의 응답을 적분하는 위상 적분기를 포함한다.

- [0021] 이러한 배열로, 센서에 충돌하는 전자기 에너지의 세기와 무관하게 캡쳐되는 이미지의 정확한 복제를 생성할 수 있는 고체 상태의 픽셀이 제공된다.

- [0022] 이것들과 본 발명의 다른 이점들은 아래 도면들을 통해 설명될 것이다.

### 실시예

- [0040] 본 발명의 일 실시예에 따르면, 높고 낮은 세기의 이미지들을 정확히 캡쳐하기 위해 위상 도메인 적분 기술을 이용하는 높은 동적 범위가 가능한 센서 소자 또는 배열이 제공된다. 본 발명의 센서 소자는 선행기술에 의해 공지된 고체 상태 픽셀 구조들에 나타난 동적 범위 특징들에 의해 제한되지 않으므로 따라서 높은 품질의 출력 이미지를 제공하기 위하여 전자기 복사에너지의 전체 범위를 캡쳐할 수 있다.

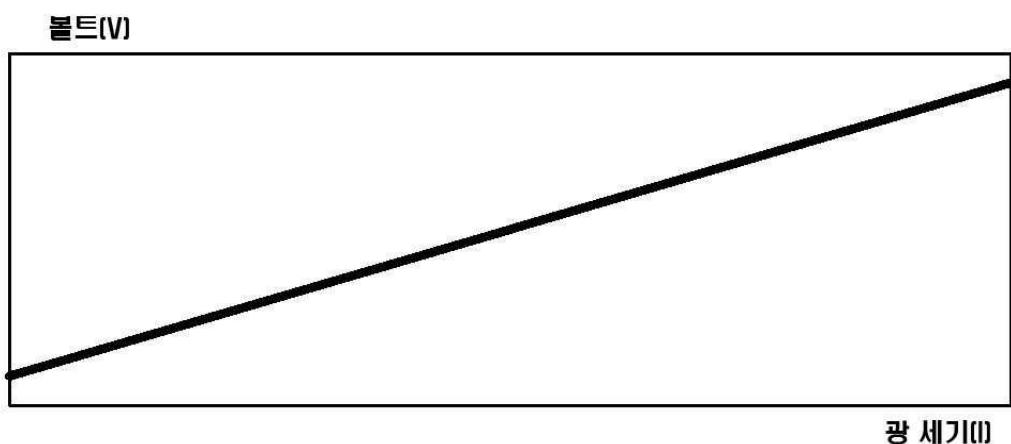

- [0041] 도 7A는 본 발명의 기술을 이용하여 제조된 센서 소자의 응답을 나타낸다. 센서 소자의 확장된 동적 범위는 전자기 복사에너지 세기의 모든 범위의 픽셀 응답을 갖는 침투하는 복사에너지에 대응되도록 하는데 충분하다. 그 결과 센서 소자는 캡쳐된 이미지의 가장 밝은 부분에서 포화 상태를 피하는 반면에 가장 어두운 부분에서 충분한 전하를 캡쳐할 수 있다. 센서와 충돌하는 전자기 에너지의 상대적인 세기와 무관하게 캡쳐된 이미지의 충실햄 복제는 순효과이다.

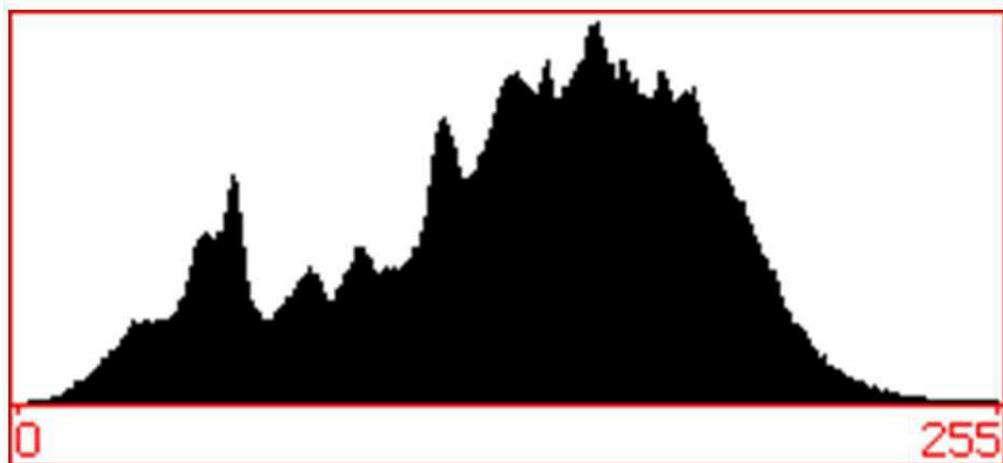

- [0042] 도 7B는 모든 픽셀 출력이 0부터 255의 8비트 ADC의 동적 범위 안에 있는 정확하게 노출된 이미지 캡쳐의 픽셀 세기의 히스토그램을 나타낸다.

- [0043] 본 발명에 의한 센서 소자는 주파수 발진 회로에 기초한 새로운 적분기 구현을 포함한다. 주파수 발진 회로들은 표준 IC 컴포넌트 블록들이며, 선행 기술인 고체 상태 장치의 불편함을 제공하지 않는다. 또한, 본 명세서에 기재된 상기 신규한 센서 소자는 이용 가능한 전원 공급 전압을 초과하고, 매우 높은 정확성과 동적 범위를 갖는 출력 신호 값을 수용할 수 있는 정확한 적분기를 사용한다.

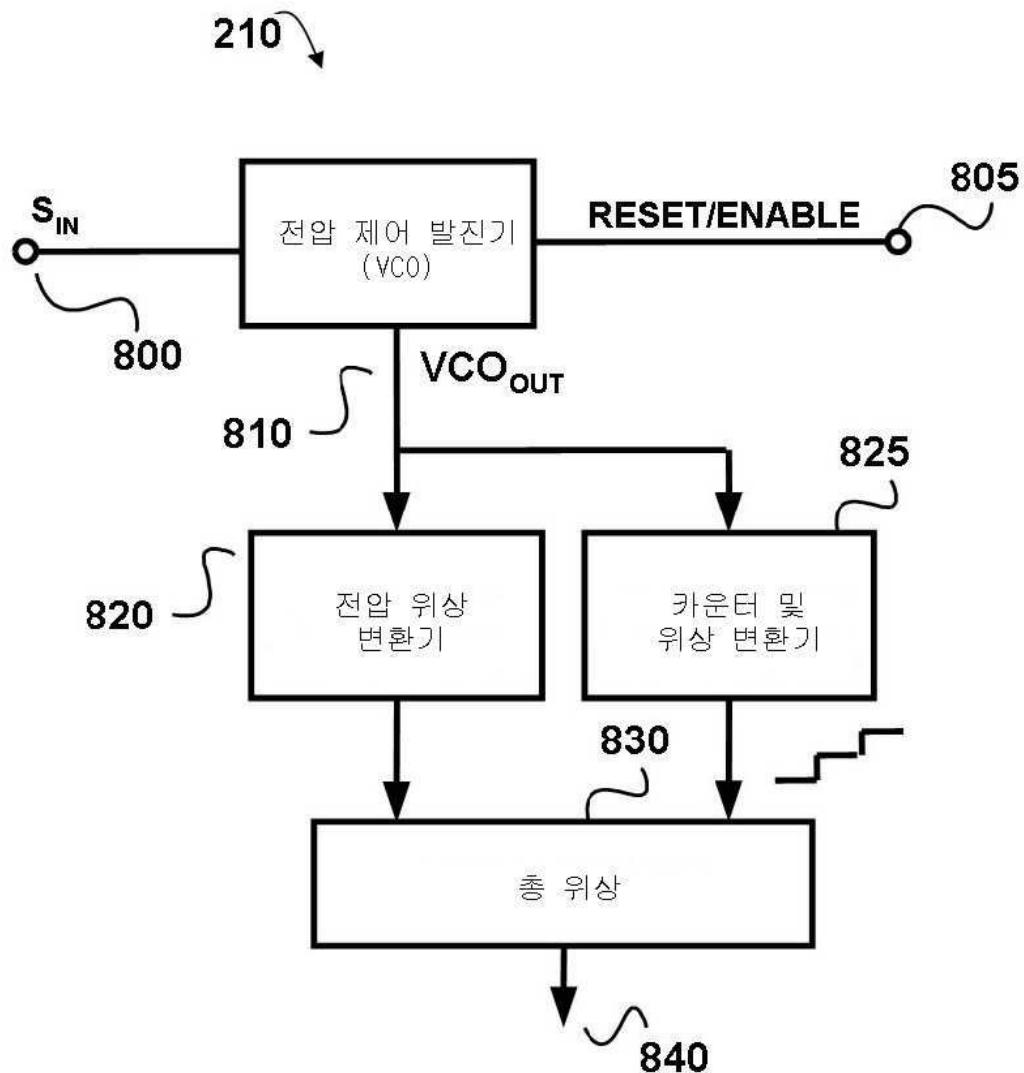

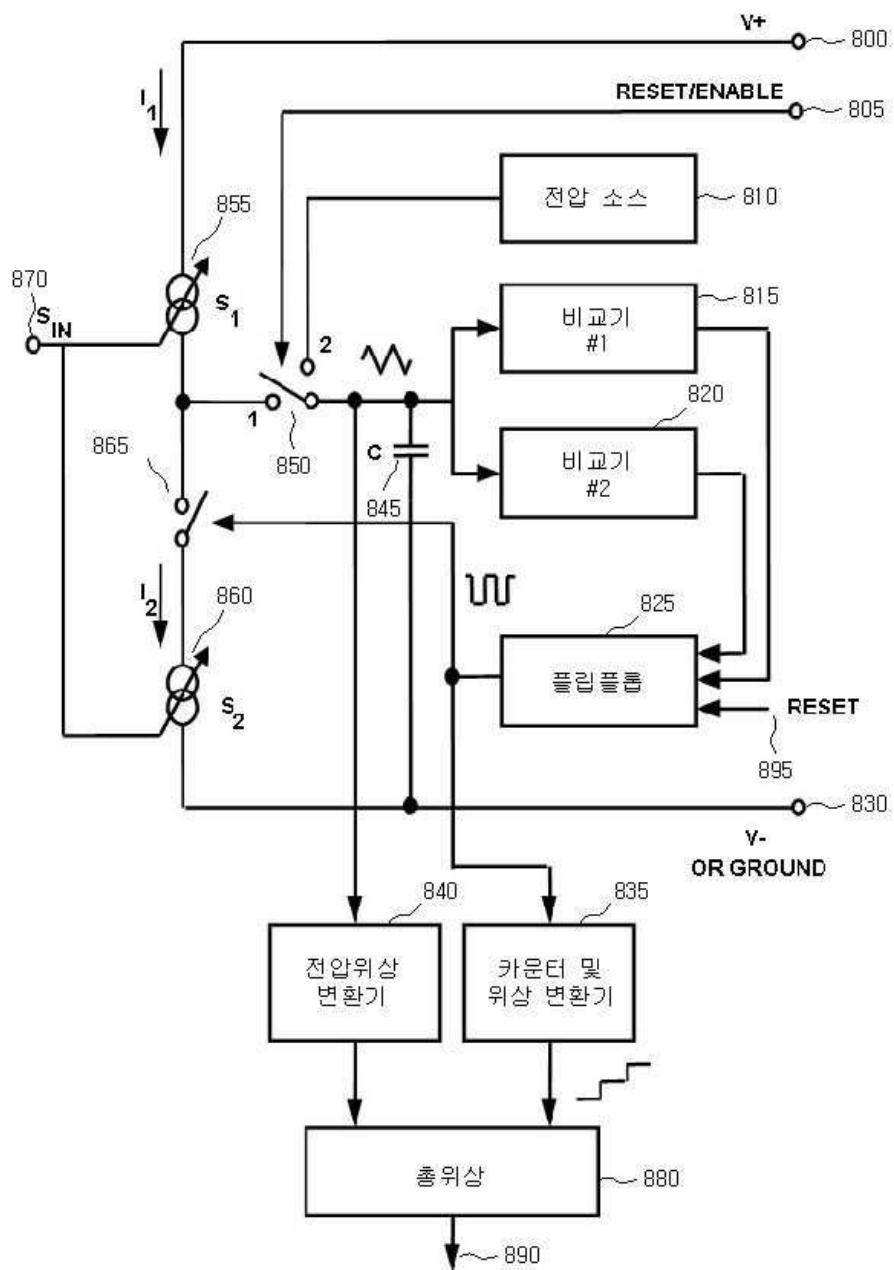

- [0044] 고품질의 이미지를 획득하는데 있어서, 하나의 이미지 센서가 해독하는 단계를 이용하여 높은 해상도 및 높은 동적 범위 이미지를 획득하는 것은 바람직하다. 도 8은 본 발명의 픽셀 구조의 일 실시예를 나타낸다. 도 8의 픽셀 구조는 도 3의 대화형 신호 획득 구조를 사용하나, 시간 도메인 적분기(110)를 새로운 위상 도메인 적분기(210)로 대체한다. 도 9는 본 발명의 보다 상세한 위상 도메인 적분기를 나타낸다.

- [0045] 본 발명에서 신호 소스(100)(도 8)의 출력은 도 9의 위상 도메인 적분기의 입력(800)으로 연결된다. 적분 구간의 마지막에 입력 신호의 적분은 위상 도메인 적분기 출력(840)에서 위상 포맷으로 읽혀진다.

- [0046] 이미지 센서 어셈블리 그리고 특히 적분기 섹션은 다음의 두 조건을 만족한다. a) 감광 소자로부터 약한 입력 신호들에 응답하여 큰 출력을 생산한다. b) 감광 소자로부터 입력 신호가 큰 경우 포화를 방지한다. 이러한 두 가지 조건은 일반적인 고체 상태의 이미지 센서 구조에서 상호 모순적이다. 그러나, 본 발명은 도 9에 도시된 것과 같이 위상 도메인 적분기를 사용함으로써 이러한 두 가지 조건이 만족될 수 있다.

- [0047] 위상 도메인 적분기의 동작은 적분기, 위상, 주파수 및 그들의 상호관계에 대한 개념을 조사함으로써 가장 잘 이해될 수 있다. 적분 함수 또는 적분은 본 기술분야에서 잘 알려진 수학 함수이다. 간단하게, 적분은 면적 또는 면적의 일반화로 해석될 수 있는 수학적 목표이다. 신호가 곡선으로 그려진 경우, 신호의 적분은 곡선

아래의 면적이다. 적분기는 입력에 있는 신호를 적분하고, 입력 신호의 적분된 버전을 출력으로 생성하는 장치이다.

[0048] 위상과 주파수는 미분 관계를 갖는다. 지속 시간  $\Delta T$  동안 발진기 출력  $V_{out}$ 에 의해 이동된 총 위상은 수학적으로  $\Delta \Theta = \int f_{inst} dt = \int (f_{nom} + f_{gain} \cdot S_{in}) dt$ 로 주어지며, 여기서 상한과 하한은 지속 시간  $\Delta T$ 이다.

[0049] 적분항들을 분리하면,  $\Delta \Theta = \int (f_{nom} + f_{gain} \cdot S_{in}) dt = \int f_{nom} dt + \int f_{gain} \cdot S_{in} dt = K + f_{gain} \int S_{in} dt$ 이며, 여기서  $K$ 항은 상수 값  $f_{nom}$ 과  $\Delta T$ (적분시간)의 함수로서 상수이고, 따라서 잘 알려져 있다.

[0050]  $f_{nom} = 0$ 인 특정 경우에,  $K=0$ 이고  $\Delta \Theta = f_{gain} \int S_{in} dt$ 이다. 제 2항은 상수 배율  $f_{gain}$ 과 입력 신호  $S_{in}$ 의 적분인  $\int S_{in} dt$  항으로 구성된다.  $f_{gain} \int S_{in} dt$  항은 시간 주기  $\Delta T$ 의 마지막에서  $\Delta \Theta$  값에서  $K$ 의 값을 감산함으로써 쉽게 얻을 수 있다.

[0051]  $f_{gain} \int S_{in} dt = \Delta \Theta - K$ 이고, 따라서  $\int S_{in} dt = (\Delta \Theta - K)/f_{gain}$ 이다.  $f_{nom} = 0$ , 즉  $K=0$ 인 특정 경우에,  $\int S_{in} dt = \Delta \Theta/f_{gain}$ 이다.

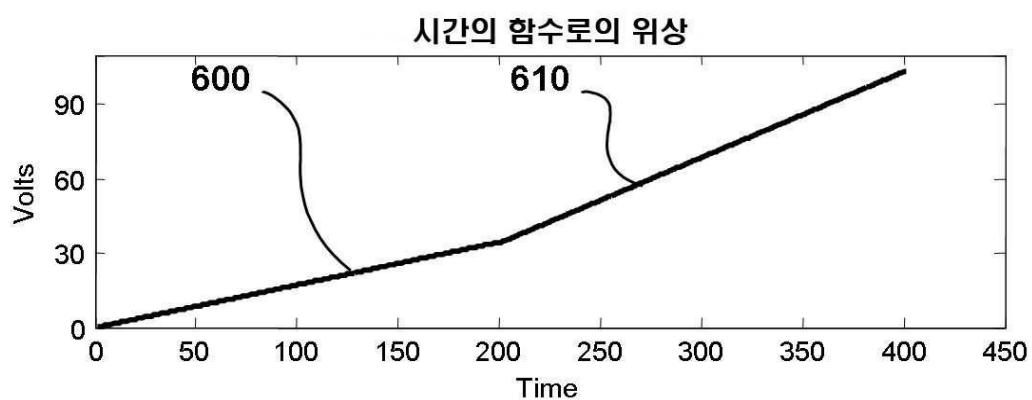

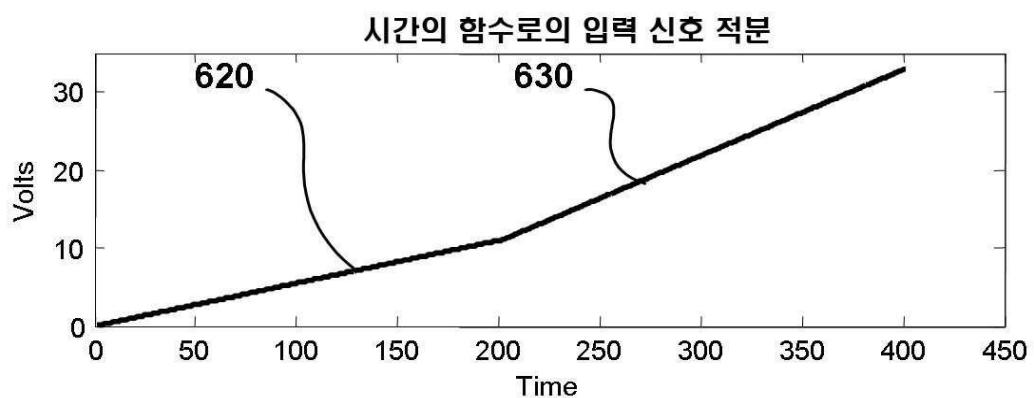

[0052] 위의 관계는 VCO 제어 입력 신호  $S_{in}$  및 시간 주기  $\Delta T$  동안의 VCO 또는 발진기 출력에 의해 이동된 위상  $\Delta \Theta$  간의 미분 관계를 입증한다. 도 10A 및 도 10B는 이러한 등가를 그래프로 도시한다. 도 10A는 시간 함수로서 VCO 출력에 의해 이동된 위상을 도시한다. 도 10B는 입력 제어 신호  $S_{in}$ 의 시간에 따른 적분을 도시한다.

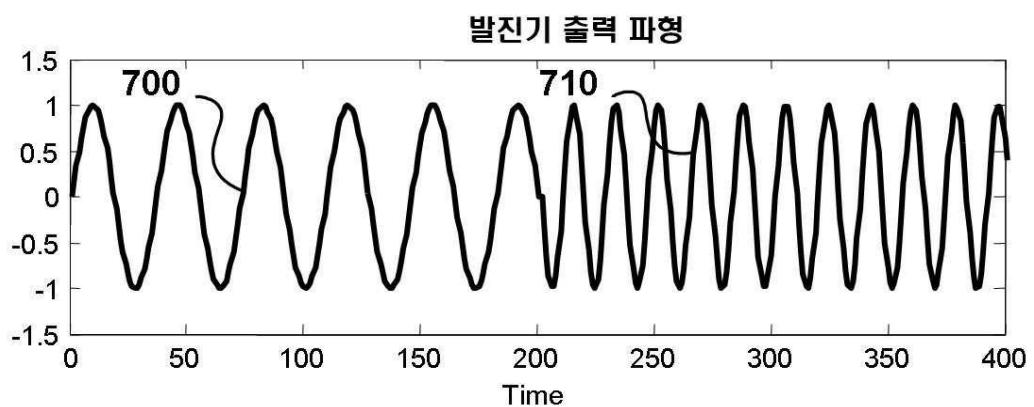

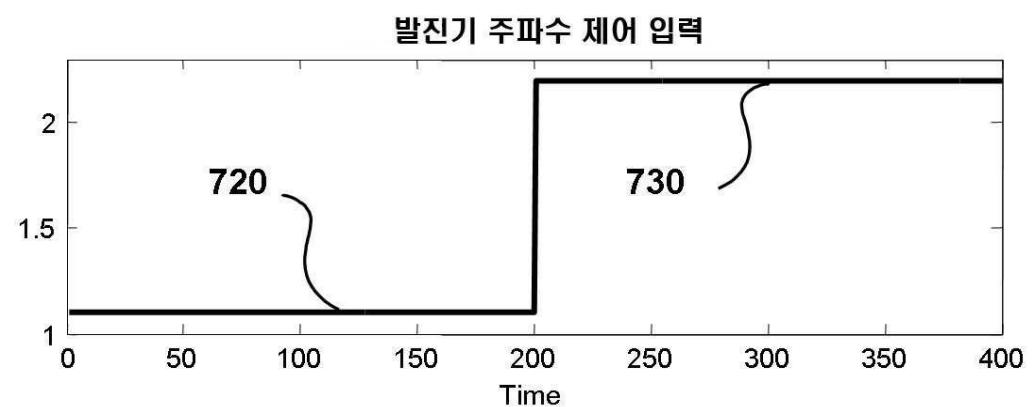

[0053] 도 11A는 도 11B에 도시된 입력 신호  $S_{in}$ 에 대응하여 생성된 전압 제어 발진기 출력 파형을 나타낸다.  $S_{in}$ 는 2 개의 상수 세그먼트들로 구성되고, 도 11B에서 720으로 표기된 제1 세그먼트들은 도 11B에서 730으로 표기된 제2 세그먼트들보다 더 낮은 값을 갖는다.

[0054] 도 10B를 다시 살펴보면, 적분기 출력 세그먼트(620)는 더 낮은 값  $S_{in}$  세그먼트(720)가 적분기에 입력된 경우  $S_{in}$ 의 시간 함수로써의 적분 출력이다. 적분기 출력 세그먼트(630)는 더 높은 값  $S_{in}$  세그먼트(730)가 적분기의 입력된 경우  $S_{in}$ 의 시간 함수로써의 적분 출력이다.

[0055] 더 낮은 값  $S_{in}$  세그먼트(720)는 VCO가 더 높은 값인  $S_{in}$  세그먼트(730)보다 더 낮은 주파수로 발진하게 한다. 도 11A의 파형 세그먼트(700)는 더 낮은 VCO 발진 주파수를 도시한다. VCO 입력에서 더 높은 값인  $S_{in}$  세그먼트(730)는 VCO가 더 낮은  $S_{in}$  세그먼트보다 더 높은 주파수로 발진하게 한다. 도 11A의 파형 세그먼트(710)는 더 높은 VCO 발진 주파수를 도시한다.

[0056] 도 10A 시간의 함수로써 VCO에 의해 이동된 위상을 나타낸다. 세그먼트(600)는 VCO 출력 세그먼트(700)에 상응한다. 세그먼트(610)는 VCO 출력 세그먼트(710)에 상응한다. 세그먼트(600)은 세그먼트(610)보다 더 낮은 위상 누적 비율을 나타낸다. 위상 누적 비율은 시간 함수로써 VCO에 의해 이동된 위상이고, 초당 라디안 단위로 표현될 수 있다. VCO가 단위 위상을 이동한 속도는 발진 주파수이고, 초당 라디안 단위로 표현될 수 있음을 동일하다.

[0057] VCO 제어 신호 입력 파형 세그먼트(720)은 VCO가 파형 세그먼트(700)를 출력하도록 한다. 시간의 함수인 VCO 출력 위상의 그래프는 곡선 세그먼트(600)를 생성한다. VCO 제어 신호 입력 파형 세그먼트(730)은 VCO가 파형 세그먼트(710)를 출력하도록 한다. 시간의 함수로서 VCO 출력 위상의 도면은 곡선 세그먼트(610)를 생성한다. 도 10a 및 도 10b에 도시된 파형들은 형태가 동일하며,  $f_{nom} = 0$ , 즉  $K=0$ 인 경우 상수  $f_{gain}$ 에 의해 관련되고, 도 10A 및 도 10B에 나타난 파형들은  $f_{nom} \neq 0$ , 즉  $K \neq 0$ 인 경우 상수  $f_{gain}$  및  $K$ 에 의해 관련된다.

[0058] 따라서, 입력 신호  $S_{in}$ 의 시간 도메인 적분은 입력 신호  $S_{in}$ 의 위상 도메인 적분과 기능적으로 동일함을 알 수 있다. 입력 신호  $S_{in}$ 의 시간 도메인 적분과 입력 신호  $S_{in}$ 의 위상 도메인 적분은 두 상수들과 관련되며,  $f_{nom} = 0$ 인 특별한 경우에 이들 중 하나의 상수는 0일 수 있다.

[0059] 신호 적분을 수행하기 위해 여기에서 개시된 방법을 사용하면 종래 적분기들보다 뛰어난 장점들을 가지며, 종래 적분기들와 관련된 어려운 성능 문제들을 해결할 수 있다. 한 가지 장점은 적분기 출력을 포화시키는 잠재성을 해결한다는 점이다. VCO 또는 발진기 출력들은 어떠한 환경 아래에서도 초과하지 않도록, 엄격히 상한

및 하한(피크 값들)에 의해 제한된다. 그러므로 출력 포화 상태는 발생할 수 없다.

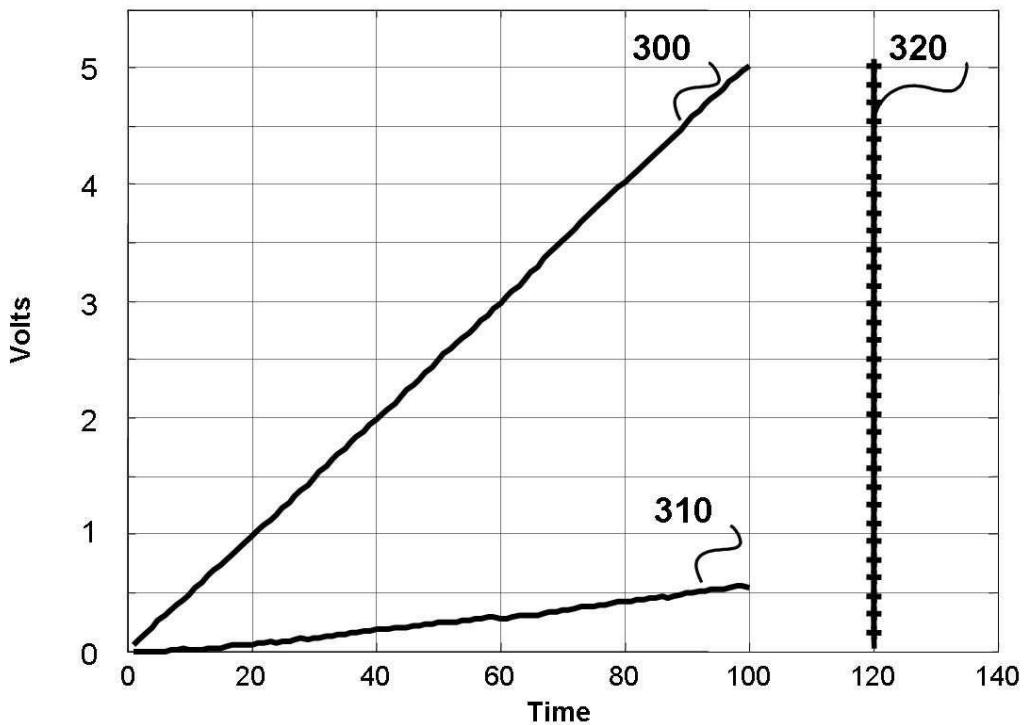

[0060] 다른 장점은 양자화 잡음 문제를 해결한다는 점이다. 도 12에 도시된 바와 같이, 낮은 레벨 신호(310)는 값과 가까운 입력 세기에 의해 생성된 출력 전압 간 거의 구별이 없는 현저하고 수용될 수 없는 양자화 잡음에 의해 왜곡될 수 있다. 적분에 기초한 위상 측정은 적분 시간  $\Delta T$  동안 발진기 출력  $\Delta \Theta$ 에 의해 이동된 위상을 측정한다. 적분 시간  $\Delta T$  동안 발진기 출력  $\Delta \Theta$ 에 의해 이동된 위상은 적분 시간  $\Delta T$  동안 입력 제어 신호의 적분에 비례하며, 이 둘은 비례한다. 최소  $\Delta \Theta$ 값은 가장 작은 적분 출력에 대해 발생한다.

[0061] 그러나,  $f_{\text{gain}}? \int S_{\text{in}} dt = \Delta \Theta - K$  이며, 여기서  $K$ 는 상수이다. 그러므로,  $\Delta \Theta - K$  항은 VCO 이득  $f_{\text{gain}}$  을 간단히 조절함으로써, 이의 최소를 포함한,  $\int S_{\text{in}} dt$  의 임의의 주어진 값에 대해 특정 값으로 독립하여 설정될 수 있다. 적분기의 이득, 및 그에 따른 측정된 적분기 출력 변수의 최소값을 설정하는 능력은 종래 적분기들과 관련된 양자화 잡음 문제를 제거한다.

[0062] 또 다른 장점은 가변 발진 회로가 다양한 종류의 시스템의 일반적이고 기본적인 빌딩 블록이라는 점이다. 그러므로 이들은 다양하게 이용할 수 있고 매우 최적화되어 있다.

[0063] 따라서, VCO에 기초한 적분기들은 양자화 잡음 및 동적 범위 또는 출력 포화가 없다는 점에서 종래 적분기들 보다 매우 뛰어나다. 다른 장점들도 있으며, 해당 기술의 통상의 지식을 가진 자에게 자명하다.

[0064] 발진기들은 본 기술분야에서 공지된 한 종류의 회로이다. 발진 회로들의 출력은 다양한 형태를 가질 수 있지만, 모두 주기적이며, 즉 출력 과형은 반복적이다. 출력 과형의 한 번 반복은 한 발진 사이클을 포함하며, 사이클의 기간은 발진 주기로 정의된다.

[0065] 발진 주파수  $f_{\text{osc}}$ 는 단위 시간당 발진 주기들의 수로 정의되고, 이는 통상 헤르츠(초당 발진 주기들)로 측정될 수 있다. 관행상 발진기의 각주파수는  $\omega = 2\pi f_{\text{osc}}$  로 정의되며, 하나의 완성된 발진 사이클은  $2\pi$  라디안의 위상각  $\Theta$  을 이동된다.

[0066] 임의의 시간  $t=0$ 에서의 시스템의 상태인 초기 상태는 발진기와 관련된다. 초기 상태의 예시는  $t=0$ 에서의 라디안으로 측정된 발진기의 초기 위상일 수 있다.

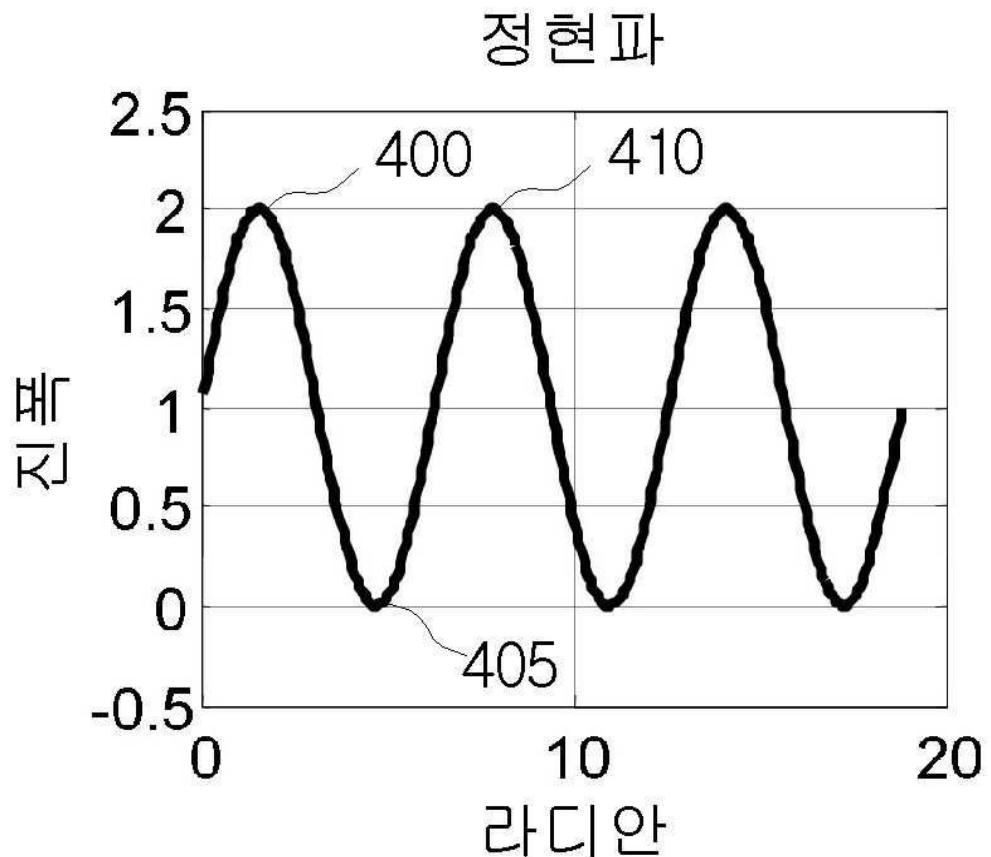

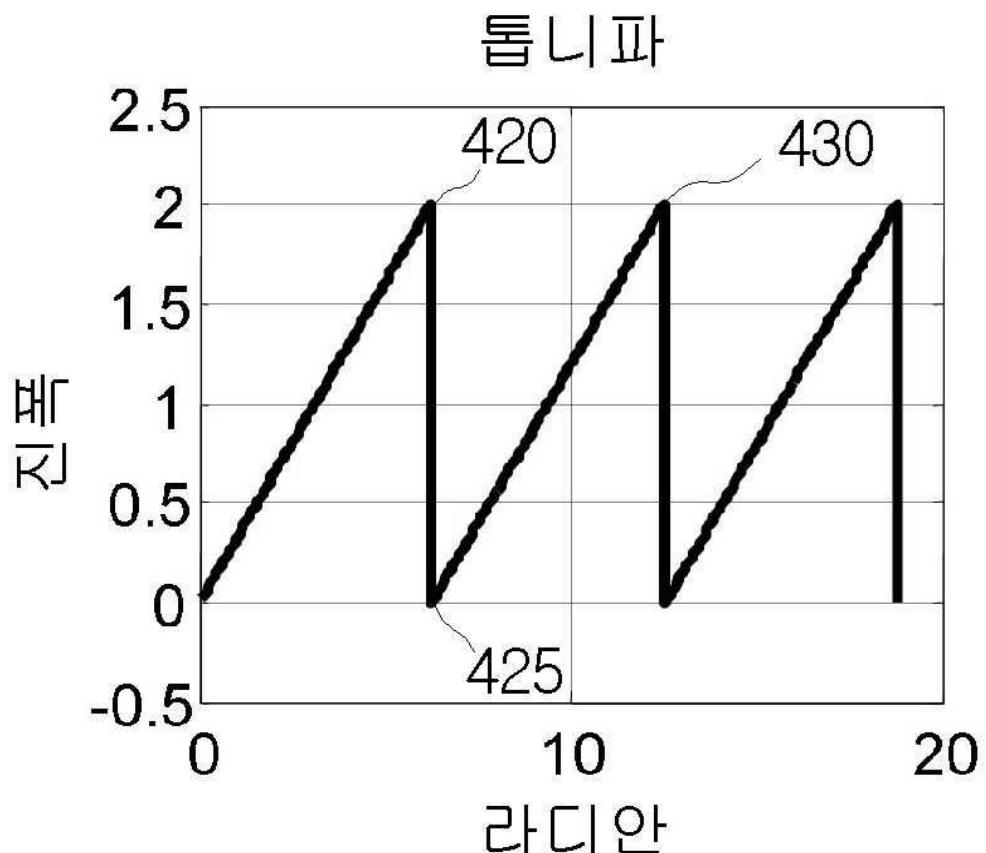

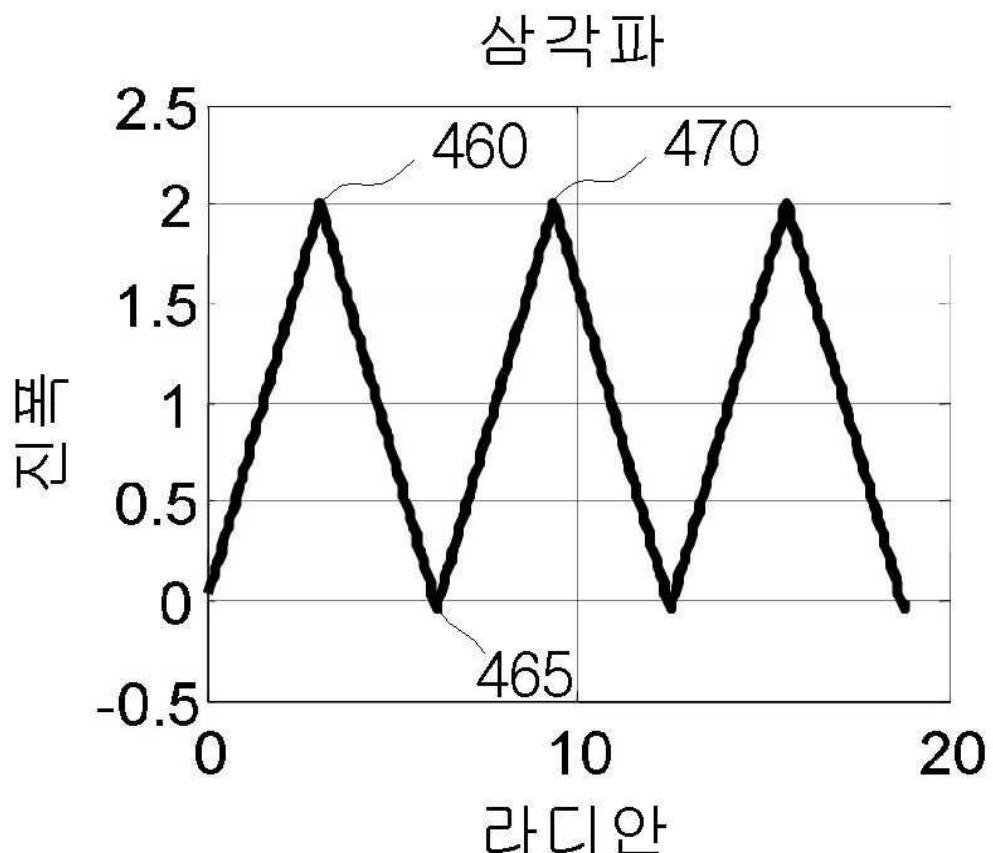

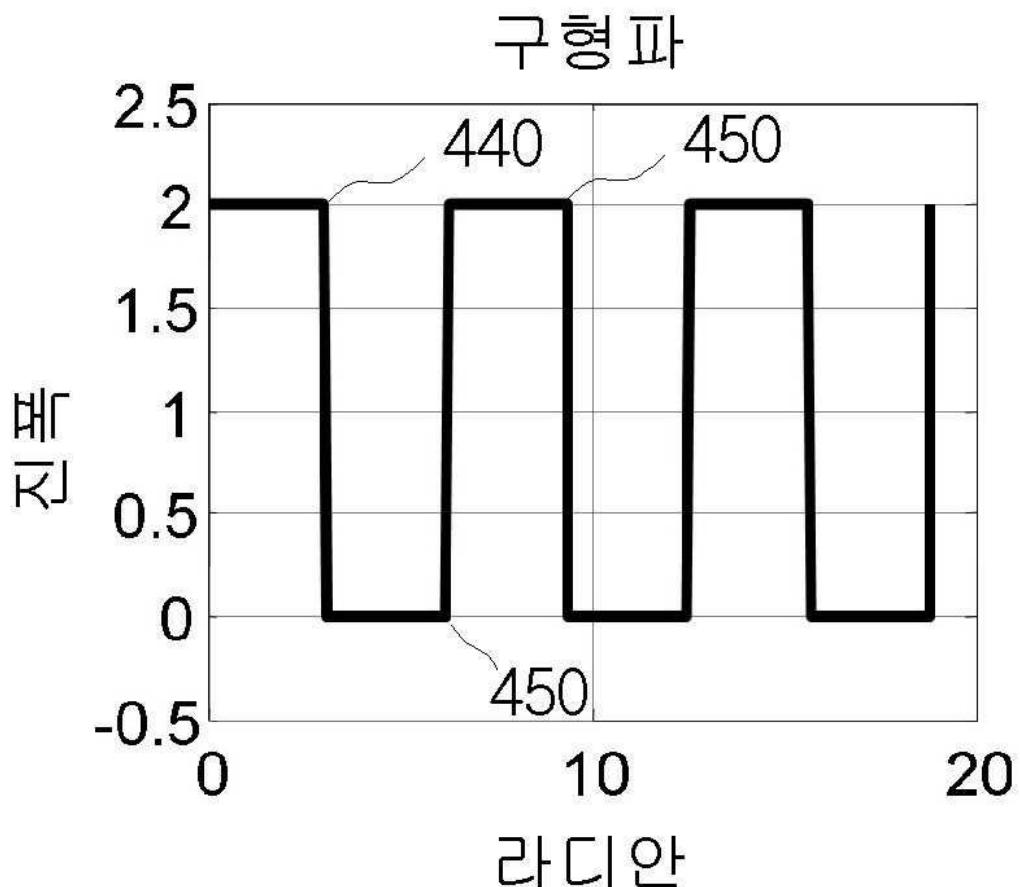

[0067] 도 13A, 도 13B, 도 13C 및 도 13D는 발진 회로의 일반적인 출력 과형을 나타낸다. 본 기술분야에 공지되어 있듯이, 도 13A, 도 13B, 도 13C 및 도 14D는 정현(sinusoidal)파, 삼각(triangular)파, 톱니(sawtooth)파 및 구형(square)파 발진기들의 출력 과형을 나타낸다. 모든 경우에 도시된 피크 전압 범위는 1V 이다.

[0068] 전자 발진 회로의 발진 주파수는 고정될 수 있고 또는 가변될 수 있다. 가변 발진 주파수를 갖는 일반적인 발진기는 전압 제어 발진기(VCO)이다. 최소한 VCO는 전압 입력을 가지며, 전압 입력에서의 신호 전압  $S_{\text{in}}$  은 발진 주파수를 제어한다. 전압은 옴의 법칙을 통해 전류와 관계하고, 신호  $S_{\text{in}}$  은 전압 특성보다는 전류를 통해 발진 주파수를 제어한다고 할 수 있다.

[0069] 또한 VCO는 발진 공칭 주파수  $f_{\text{nom}}$  을 가질 수 있다. VCO는 주파수 제어 입력  $S_{\text{in}}$  레벨이 존재하지 않거나, 또는 예컨대 0V와 같은, 발진 공칭 주파수를 변경하지 못하는 값을 갖는 경우에  $f_{\text{nom}}$  에서 발진한다. 발진 공칭 주파수는 0Hz를 포함한 임의의 특정된 값을 가질 수 있다.

[0070] VCO의 출력 주파수는 입력 신호의 진폭 변화에 응답하여 변한다. 따라서 VCO의 순간 발진 주파수는 VCO의 발진 공칭 주파수와 임의의 값  $f_{\text{delta}}$  만큼 차이가 날 것이며,  $f_{\text{inst}} = f_{\text{nom}} + f_{\text{delta}}$  로 주어질 것이다. 이때  $f_{\text{delta}} = f_{\text{gain}} ? S_{\text{in}}$ . 이다.

[0071] 본 예시에서,  $f_{\text{delta}}$ 은 초당 라디안으로 측정되며,  $f_{\text{gain}}$  은 초당 볼트당 라디안으로 측정되고,  $S_{\text{in}}$  는 볼트로 측정된다.

[0072] 상기에서 설명하였듯이, 도 11A는 VCO의 입력 및 출력 신호들을 도시한다. VCO 출력의 발진 주파수는 입력 신호 진폭의 변화에 응답하여 변한다. VCO 출력 세그먼트(700)는 입력 신호 세그먼트(720)에 대응된다. VCO 출력 세그먼트(700)의 발진 주파수는 VCO 출력 세그먼트(710)의 발진 주파수보다 더 낮다. 입력 신호 세그먼트(720)의 진폭은 입력 신호 세그먼트(730)의 진폭보다 더 낮다. 그러므로  $f_{\text{gain}}$  은 양의 값을 가지며, 발진 VCO 주파수는 입력 제어 신호 진폭과 정비례한다.

- [0073] VCO는 RESET/ENABLE 과 같은 추가적인 입력을 가질 수 있다. RESET/ENABLE 기능은, RESET 상태에서 VCO 출력 과형을 피크-피크 전압 범위 내의 임의의 값일 수 있는 미리 정해진 전압으로 리셋하는 것이다. RESET/ENABLE 기능은 ENABLE 상태에서 VCO 출력을 발진하도록 하는 것이다.

- [0074] VCO는 출력  $V_{out}$  을 갖는다. 발진의 각 주기 동안,  $V_{out}$  는  $2\pi$  라디안의 각위상을 이동한다 이것은 출력 위상이 측정 가능한  $2\pi$ 의 모듈로(modulo)이고, 정확히  $2\pi$  로 구분한 위상에서의 발진 출력 값들은 동일하다는 것을 의미한다. 도 13A 내지 도 13D 는 일반적인 VCO 출력 과형들을 도시한다. 완성된 주기 동안, 도 13의 각 과형은  $2\pi$  라디안들을 정확히 이동하며, 정확히  $2\pi$  로 구분한 위상에서의 과형 값들은 모든 과형에 대해 동일하다.

- [0075] 한 주기의 서브셋 동안 발진기 출력에 의해 이동된 위상은, 상기 한 주기의 서브셋의 시작과 끝을 표시하는 두 시점에 발진기 출력을 샘플링하고, 각 샘플과 관련된 위상을 식별하고 두 위상을 감산함으로써 결정된다.

- [0076] 두 시점에 VCO 출력의 직접 관찰을 기초로 하는 방법을 사용하는 경우, 일 발진 주기 이상의 지속 시간 동안 발진기 출력에 의해 이동된 위상은 오직  $2\pi$  라디안의 모듈로에 의해서만 결정될 수 있다. 그러므로 불명료를 해결하기 위해서 VCO 출력에 의해 이동된 주기들의 수 또는 VCO 출력에 의해 이동된 주기의 중요한 비율을 카운트하는 부가적인 기능이 사용된다.

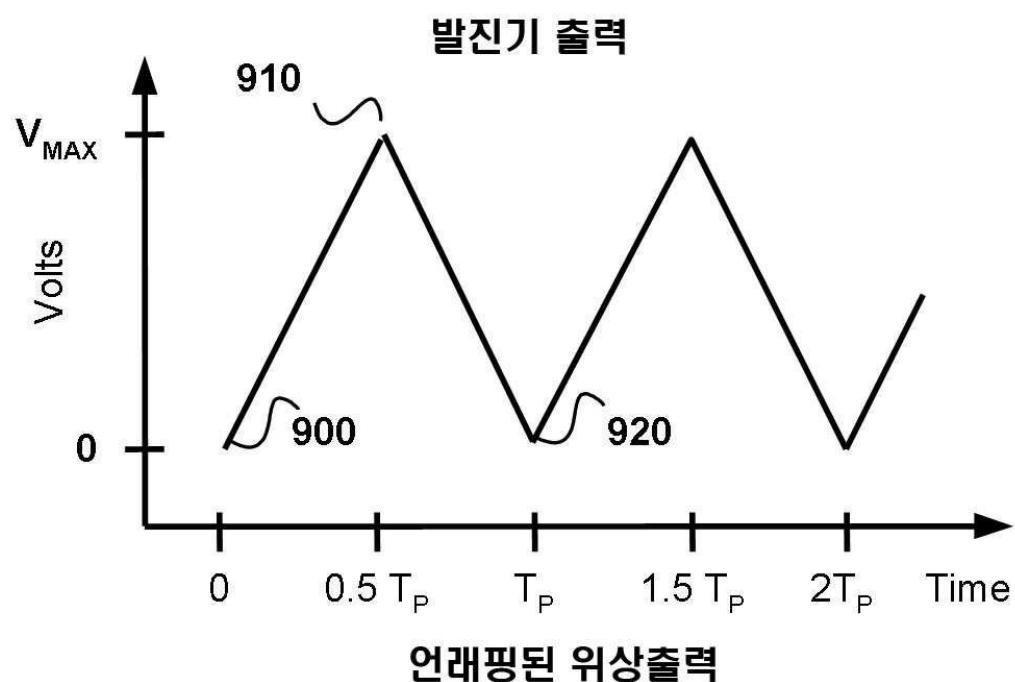

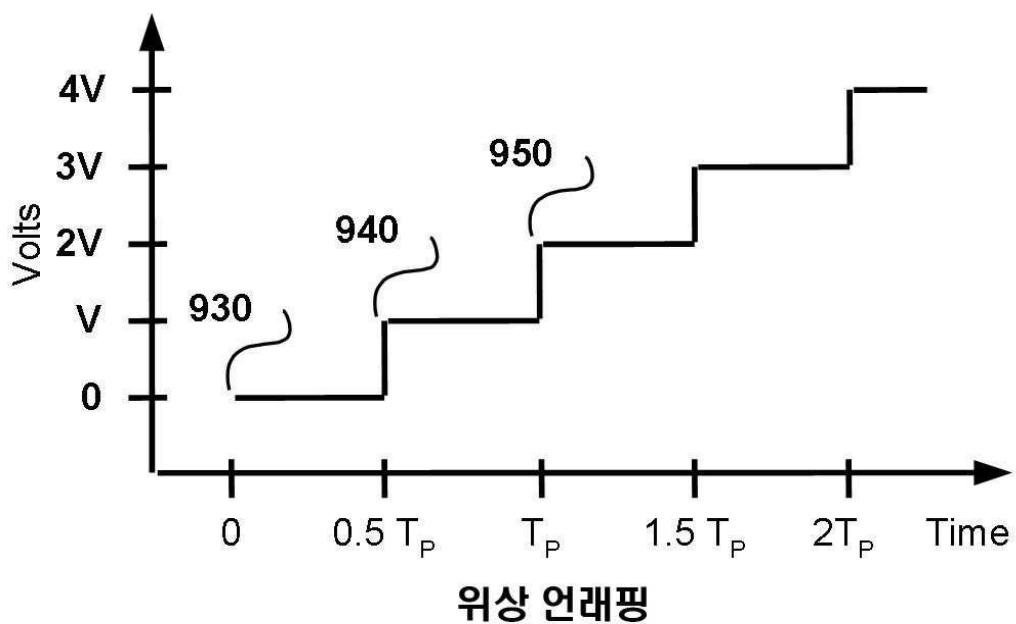

- [0077] 시구간에서 시구간에서 VCO 출력에 의해 이동된 주기들의 수 또는 VCO 출력에 의해 이동된 주기의 중요한 비율을 카운트하거나, 또는 위상을 '언래핑'하는 회로는 쉽게 구현될 수 있다. 이러한 회로와 관련된 과형은 도 14A 및 도 14B에 도시된다. 도 14A의 VCO 출력은 삼각 과형이다. 시간  $t=0$ ,  $0.5T_p$  및  $T_p$  에서, VCO 출력 과형은  $0$ ,  $\pi$  및  $2\pi$  라디안의 진행에 대응하는 900, 910 및 920으로 표기된 상태에 도달한다.

- [0078] 위상 언래핑 회로의 출력은 시간  $t=0$ ,  $0.5T_p$  및  $T_p$  에서의 상태를  $0$ ,  $V$  및  $2V$ 의 진폭의 레벨로 변화시킨다. 과도 시간들은 930, 940 및 950으로 표기되고, 이를 각각은 900, 910 및 920으로 표기된 VCO 출력 상태와 대응한다.

- [0079] VCO 출력과 VCO 출력의 한 주기 동안 도시된 위상 언래핑 회로의 출력 사이의 관계는, 임의의 수의 VCO 출력 주기들에 걸쳐 미리 정해진 양만큼 값이 증가하는 위상 언래핑 회로의 출력으로 연장될 수 있으며, 각 시간에 VCO 출력은  $0$ 과  $\pi$  ( $2\pi$ 의 모듈로) 위상 값들을 통과한다. 위상 언래핑 기능을 구현하는 방법과 VCO 출력에 의해 이동된 언래핑된 위상의 값들을 표시하는 방법은 다른 방법들이 존재함은 본 기술분야의 통상의 지식을 가진 자에게 자명하다.

- [0080] VCO 출력에 의해 이동된 총 위상은 두 항의 합에 의해 주어진다. 제1 항은 위상 언래핑 회로에 의해 기록되는 총 언래핑된 위상이다. 제2 항은 위상 언래핑 회로 출력의 최근 업데이트 이후로 VCO 출력에 의해 이동된 총 위상이다. 이 양은 VCO 출력의 직접 측정에 의해 명백히 얻을 수 있다.

- [0081] 도 15는 상업적으로 이용 가능한 IC인 ICL8038의 VCO 서브셋의 간단한 블록 다이어그램을 나타낸다. 추가적인 위상 언래핑, 이동된 총 위상 및 VCO RESET/ENABLE 기능이 추가된다.

- [0082] 전류 소스들(860 및 855)은 커패시터(845)를 충전하고 방전한다. 커패시터(845)의 충전 및 방전은 플립플롭(825)에 의해 제어되고 전류 소스(860 또는 855)를 커패시터(845)에 연결하는 스위치(865)에 의해 결정된다.

- [0083] 플립플롭(825)은 비교기들(815 및 820)에 의해 트리거되는 경우 상태를 변경한다. 비교기(815)는 커패시터(845)가 미리 설정된 고 전압에 도달하는 경우 트리거된다. 비교기(820)는 커패시터(845)가 미리 설정된 저 전압에 도달하는 경우 트리거된다.

- [0084] 비교기(815)가 트리거되는 경우, 플립플롭(825)은 스위치(865)가 닫히도록 상태를 변경한다. 전류 소스(860)의 전류  $I_2$ 는 커패시터(845)를 방전시켜 커패시터(845) 양단 전압을 감소시킨다. 커패시터(845) 양단 전압의 감소는 즉시 비교기(815)가 상태를 변경한다.

- [0085] 커패시터(845) 양단 전압이 충분히 낮은 값으로 감소하는 경우, 비교기(820)가 트리거된다. 비교기(820)가 트리거되면, 플립플롭(825)은 스위치(865)가 열리도록 상태를 변경한다. 전류 소스(855)의 전류  $I_1$ 은 커패시터(845)를 충전시켜 커패시터(845) 양단 전압을 증가시킨다. 커패시터(845) 양단 전압 증가는 즉시 비교기(820)가 상태를 변경한다.

- [0086] 커패시터(845) 양단 전압이 충분히 높은 값으로 증가하는 경우, 비교기(815)는 다시 트리거되어 플립플롭

(825)이 상태를 변경하고, 커패시터(845) 충전/방전 사이클이 반복된다.

[0087] 커패시터(845)에 수용된 전하와 커패시터(845) 양단 전압의 관계는  $Q=CV$ 이며, 여기서  $C$ 는 패럿으로 측정된 커패시터(845)의 캐apasitance이고,  $Q$ 는 쿠лон으로 측정된 커패시터(845)에 수용된 전하이며,  $V$ 는 볼트로 측정된 커패시터(845) 양단 전압이다.

[0088] 시구간  $\Delta T$  동안 흐른 일정한 전류  $I$ 로 인한 커패시터(845)에 수용된 전하의 변화는  $\Delta Q=I\Delta T$ 로 나타나며, 여기서  $\Delta Q$ 는 쿠лон으로 표시되는 커패시터(845)에 수용된 전하의 변화이며,  $I$ 는 암페어로 표시되는 전류 값이며,  $\Delta T$ 는 초로 표시되는 전류가 흐른 시구간이다. 일정한 전류는 시간의 함수로서 커패시터(845)에 수용된 전하에 있어서 선형 변화를 야기한다. 시간의 함수로서 커패시터(845)에 수용된 전하의 선형 변화는 시간의 함수로서 커패시터(845) 양단 전압의 선형 변화를 야기한다.

[0089] 전류 소스들(855 및 860)에 의해 생성된 전류들인  $I_1$  및  $I_2$ 의 일정한 값은 커패시터(845) 양단 전압이 선형적으로 증가 및 감소하여 삼각 파형을 생성한다. 전류들인  $I_1$  및  $I_2$ 의 순효과(net effect)가 같다면, 커패시터(845) 양단의 삼각 전압 파형의 상승 세그먼트와 하강 세그먼트는 도 6C에 나타난 것과 같이 대칭적이다. 전류들  $I_1$  및  $I_2$ 의 순효과가 동일하지 않다면, 커패시터(845) 양단의 삼각 전압 파형의 상승 세그먼트와 하강 세그먼트는 비대칭적이다. 전류  $I_1$ 의 순효과가 전류  $I_2$ 의 순효과보다 매우 작아지는 한도 내에서, 커패시터(845) 양단 삼각 전압 파형은 도 6b에 나타난 텁니 파형이 된다.

[0090] 커패시터(845)를 충전하고 방전하는데 필요한 시간은 전류 소스들(860 및 855)에 의해 생성된 전류  $I_1$  및  $I_2$ 의 크기에 의해 결정된다. 비교기들(815 및 820)을 트리거하는 전압 레벨로 커패시터(845)를 충전하고 방전하는데 필요한 시간들의 합이 VCO의 발진 주기를 결정한다. 그러므로 전류  $I_1$  및  $I_2$ 의 크기가 VCO의 발진 주기 및 발진 주파수를 결정한다.

[0091] 입력(870)에 인가된 제어 신호는 전류 소스들(860 및 855)을 제어하며, 따라서 VCO 발진 주파수를 제어한다. 미도시 되어 있지만, 본 기술분야의 당업자에게 잘 알려진 간단한 전압 또는 전류 스플리터는 파형 대칭성을 조절하기 위해서 870에 인가된 제어 신호와 전류 소스들(860 및 855) 사이에 추가될 수 있다.

[0092] 커패시터(845) 양단 전압의 반전은 플립플롭(825)의 상태에 의해 제어된다. 카운터(835)가 트리거되고, 플립플롭(825)이 상태를 변경할 때마다 상응하여 이의 출력 상태를 수정한다. 카운터(835) 출력 상태의 변화는 도 8B에 도시된 것과 같이 수정된 전압 레벨일 수 있다. 다른 전압 레벨 수정 방식들은 개별 상태가 분해 가능한 동안에 사용될 수 있다. 또한 카운터(835) 출력은 B 비트를 포함하는 디지털 워드로 구성된 디지털 포맷일 수 있다. 이와 같은 경우에, 출력 상태의 변화는 다른 상태들이 하나 이상의 비트에 있어서 다른 이진수일 수 있다.

[0093] 카운터(835)의 출력 상태는 플립플롭(825)이 상태를 변경하는 매 시간 변하고, 따라서 VCO 출력이 이의 최소 및 최대값들에 도달한 횟수를 카운트한다. 카운터(835)의 출력 상태가 짹수라면, VCO 출력은  $2\pi$  라디안의 정수배를 이동한 것이다. 그리고 VCO 출력에 의해 이동된  $2\pi$  라디안의 수는 카운터(835)의 출력 카운트를 2로 나눔으로써 주어진다.

[0094] 만약 카운터(835)의 출력 상태가 홀수라면, VCO 출력에 의해 이동된  $2\pi$  라디안의 수는 정수부와 분수부를 갖는다. VCO 출력에 의해 이동된  $2\pi$  라디안의 수의 정수부는 카운터(835)의 출력 상태에서 1을 빼서 얻어진 수를 2로 나눔으로써 주어진다. VCO 출력에 의해 이동된  $2\pi$  라디안의 수의 분수부는 파형의 상승 세그먼트와 하강 세그먼트 사이의 비대칭 정도에 좌우되며, 본 기술분야의 당업자는 이를 쉽게 얻을 수 있다. 예를 들면, 파형의 상승 세그먼트가 파형의 하강 세그먼트보다 2배 더 길다면, 완료하는데 발진 주기의 2/3을 필요하다.

[0095] 커패시터(845) 양단 전압은 플립플롭(825)의 상태의 마지막 변경 후의 VCO 출력에 의해 이동된 위상과 비례한다. 만약 a) 비교기들(815 및 820)의 트리거 전압들(즉, VCO 출력의 최대 및 최소 전압들)과 b) VCO 출력 파형의 상승 및 하강 세그먼트들 간의 비대칭들이 알려진다면, 그것은 본 기술분야의 당업자가 쉽게 알 수 있다. 예를 들면, 만약 a) VCO 출력 전압이 파형의 상승 세그먼트에서 최소 및 최대값 사이의 중간이고, b) 파형의 상승 세그먼트가 파형의 하강 세그먼트보다 2배 더 길다고 가정하면, 파형 측정은 발진 주기의 1/3에서 이뤄진다.

[0096] VCO 출력에 의해 이동된 총 위상은, 전압 위상 변환기(840)에 의해 그리고 카운터 및 위상 변환기(835)에 의해 기록된, VCO 출력에 의해 이동된 위상을 더함으로써 얻어진다. 이 기능은 합산기(summer; 880)에 의해 수

행되고, 출력(890)에서 이용 가능하게 만들어진다.

[0097] 스위치(850)는 커패시터(845)를 리셋하여, VCO 발진기 출력을 전압 소스(810)에 의한 초기 전압 출력으로 리셋한다. 플립플롭(825)은 신호(895)에 의해 리셋된다. 플립플롭(825)의 리셋 상태 및 VCO 출력 파형의 상승 및 하강 세그먼트들 간의 비대칭 정도와 함께 갖는 전압 소스(810)의 초기 전압은 VCO 출력 파형의 초기 위상을 결정하기에 충분하다. 이러한 유도는 본 기술분야의 당업자에게 잘 알려져 있다.

[0098] 본 기술분야에 공지되어 있고 ICL8083에 설명되어 있듯이, 본원은 정현, 구형 및 톱니 파형들이 본원에서 개시된 기본적인 삼각 파형을 이용하여 추가적인 내부 회로에 의해 생성된다는 것을 언급한다. 그러므로 상술한 항목들은 다른 VCO 출력 파형 형태에도 동등하게 적용된다.

[0099] 따라서, 본 발명은 종래의 픽셀 구조의 적분기 구성 요소를 위상 도메인에서 입력 신호의 시간 적분을 수행하는 높은 이득 및 높은 동적 범위 적분기로 대체할 수 있다.

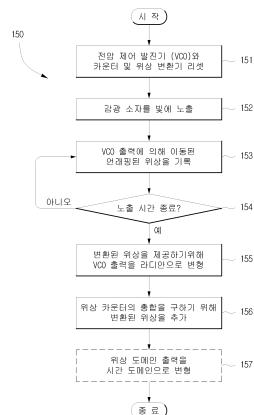

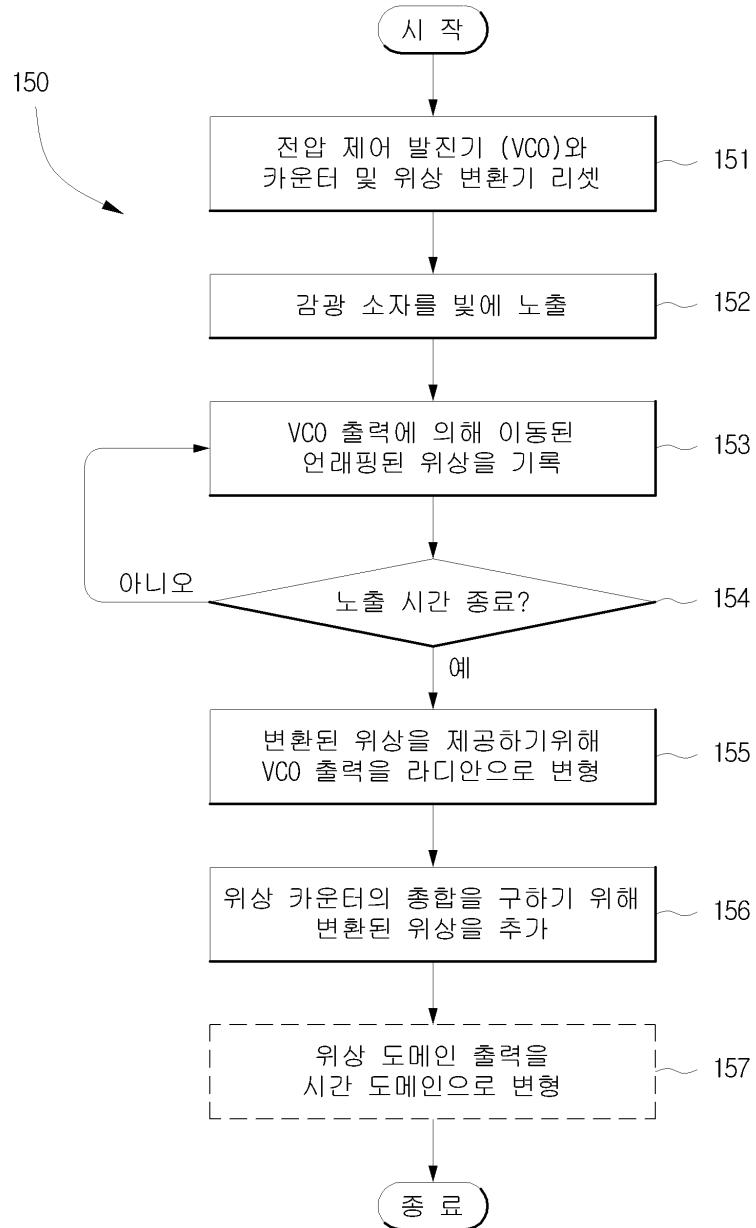

[0100] 도 16은 본 발명에 따른 위상 도메인 적분기를 사용하는 픽셀 구조에 의해 캡쳐 과정(150) 동안 수행될 수 있는 여러 단계의 예시를 나타내는 흐름도이다.

[0101] 노출 시간의 시작에서(단계 151) VCO 출력, 카운터 및 위상 변환기(835)가 리셋된다. 단계 152에서 감광 소자가 빛에 노출되고, VCO는 출력이 주파수로 변화하도록 하는 전기적 특징을 변화한다. 감광 소자는 포토다이오드, 포토게이트, 포토트랜지스터 또는 포토레지스터와 같은 어떠한 소자가 될 수 있다. 또한 본 발명은 상기에서 설명한 구조를 갖는 픽셀들 또는 적어도 픽셀들의 일 부분의 기하학적 특징을 갖는 CMOS, MOS 이미지 장치와 같은 고체 상태의 이미지 장치와 관련된다.

[0102] 단계 153에서 카운터 및 위상 변환기(835)는 VCO 출력에 의해 이동된 언랩핑된 위상을 기록한다. 단계 154에서 노출 프레임이 종료하는 것이 결정되는 경우, 단계 155에서 전압 위상 변환기(840)에 의해 VCO의 출력은 라디안으로 변경된다. 카운터 및 위상 변환기(835) 및 전압 위상 변환기(840)의 출력들은 전체 위상 추가부(880)에 의해 합해진다. 바람직하게는 단계 156에서 위상 도메인 적분 출력은 시간 도메인 적분 출력으로 변경될 수 있다. 파선으로 나타난 단계 156의 캡쳐 프로세스 단계는 필수적이지 않음을 나타낸다.

[0103] 고체 상태의 픽셀 구조(CCD, CMOS 및 MOS 기반의 픽셀 구조들을 포함함)의 판독 신호를 획득하는 방법 및 장치에 대해 상술하였다. 픽셀 구조는 적어도 출력 노드를 갖는 감광 소자, 위상 도메인에서 출력 노드 신호를 적분하는 수단 및 위상 도메인 적분 값을 읽는 수단을 포함한다. 센서에 충돌하는 전자기 에너지의 세기와 무관하게 캡쳐되는 이미지의 정확한 복제를 생성할 수 있는 이러한 배열을 갖는 고체 상태의 픽셀이 제공된다.

[0104] 본 발명의 다양한 실시예들이 기술되었으나, 그러나 특정 구성요소 및 단계가 설명되었더라도 다른 기능적 설명이나 추가적인 단계 및 구성요소가 본 기술분야의 통상의 지식을 가진 자에 의하여 추가될 수 있으며, 본 발명이 개시된 특정 실시예에 한정되는 것이 아닌 것으로 이해한다. 또한 다양한 예시적인 요소들은 하드웨어, 컴퓨터 상에서 실행되는 소프트웨어, 또는 이들의 조합으로 구현될 수 있는 것으로 이해하고, 예시된 실시예들에 대한 수정 및 이들의 변형이 여기에 개시된 발명적인 개념으로부터 벗어나지 않고 만들어질 수 있음을 이해할 것이다. 따라서 본 발명은 첨부된 청구범위의 범위 및 사상에 의해서가 아니면 제한되어 해석되지 않아야 한다.

## 도면의 간단한 설명

[0023] 도 1은 이미지 취득 체인에 포함될 수 있는 대표적인 구성을 나타낸 블록도이다.

[0024] 도 2는 적분기의 출력을 나타낸 그래프이다.

[0025] 도 3은 대표적인 픽셀 구조의 블록도이다.

[0026] 도 4A 내지 도 4C는 동적 범위 제한의 효과를 나타내는 도 3과 같은 픽셀 구조의 출력에서 왜곡을 묘사하기 위해 제공된 전환 곡선이다.

[0027] 도 5A 및 도 5B는 노출과다 및 노출부족인 이미지 캡쳐 각각의 픽셀 세기의 히스토그램이다.

[0028] 도 6은 더블-슬로프 기술을 사용하여 제작된 픽셀 구조 응답 곡선이다.

[0029] 도 7A는 본 발명의 픽셀 구조의 응답 곡선이다.

[0030] 도 7B는 본 발명의 캡쳐된 이미지에서 픽셀 세기들의 대표적인 히스토그램을 나타낸다.

- [0031] 도 8은 위상 도메인 적분기를 포함한 이미지 센서에 포함될 수 있고 일련의 과정과 관련된 대표적인 구성을 나타낸 블록도이다.

- [0032] 도 9는 본 발명의 위상 도메인 적분기의 일 실시예의 블록도이다.

- [0033] 도 10A 및 도 10B는 본 발명의 신호 적분 능력을 설명하는데 사용되는 발진기 위상(9A) 및 시간 도메인 적분기 출력 신호(9B)를 나타내는 그래프이다.

- [0034] 도 11A는 도 11B에서 도시된 발진기 입력에 응답하여 주파수가 변하는 조절 가능한 발진기 파형을 나타낸 그래프이다.

- [0035] 도 12는 낮은 세기 신호들에서 양자 에러의 양상을 나타낸 그래프이다.

- [0036] 도 13A 내지 도 13D는 여러 가지의 일반적인 VCO 출력 파형을 나타낸다.

- [0037] 도 14A 및 도 14B는 본 발명의 위상 언래핑 메커니즘을 나타내기 위해 제공된 그래프이다.

- [0038] 도 15는 위상 도메인 적분기를 포함한 본 발명의 센서 소자의 블록도이다.

- [0039] 도 16은 도 14의 위상 도메인 적분기에 의해 이미지 캡쳐 과정 동안 수행될 수 있는 여러 단계들을 나타내기 위해 제공된 흐름도이다.

## 도면

### 도면1

도면2

도면3

도면4A

도면4B

도면4C

도면5A

도면5B

도면6

도면7A

도면7B

도면8

도면9

도면10A

도면10B

도면11A

도면11B

도면12

도면13A

도면13B

도면13C

도면13D

도면14A

도면14B

도면15

## 도면16

【심사관 직권보정사항】

【직권보정 1】

【보정항목】 청구범위

【보정세부항목】 청구항 12, 7째줄

【변경전】

상기 시간 주기

【변경후】

시간 주기