**【特許請求の範囲】****【請求項 1】**

装置であって、

電圧信号を発生させるために入力信号を増幅するように構成された増幅器と、ここにおいて、前記入力信号は、超音波がイメージング対象アイテムに反射して、圧電層を介して伝播することに応答して発生する、

前記増幅器の出力からノードへのノイズの伝播を低減しつつ、前記増幅器の前記出力から前記ノードに前記電圧信号を伝えるように構成されたノイズ低減回路と、

前記ノードにおける前記電圧信号に基づいてDC画素電圧を発生させるように構成された回路と

10

を備える装置。

**【請求項 2】**

前記ノイズ低減回路は、前記増幅器と前記ノードとの間に結合されたキャパシタを備える、請求項1に記載の装置。

**【請求項 3】**

前記ノイズは、前記増幅器で発生する低周波数ノイズを備える、請求項1に記載の装置。

**【請求項 4】**

前記入力信号は、入力電流信号を備え、前記増幅器は、前記電圧信号を発生させるために前記入力電流信号のトランスインピーダンス増幅を実行するように構成されたトランスインピーダンス増幅器を備える、請求項1に記載の装置。

20

**【請求項 5】**

前記トランスインピーダンス増幅に関連付けられたゲインは、前記圧電層のセンス容量に基づく、請求項4に記載の装置。

**【請求項 6】**

前記トランスインピーダンス増幅に関連付けられたゲインは、前記圧電層のセンス容量に対する、前記増幅器の前記出力と入力との間に結合されたフィードバックキャパシタの容量の比に基づく、請求項4に記載の装置。

**【請求項 7】**

前記増幅器は、ソースフォロア増幅器を備える、請求項1に記載の装置。

30

**【請求項 8】**

前記回路は、前記電圧信号の1つ以上のピークに実質的に基づいて前記DC画素電圧を発生させるように構成されたピーク検出器を備える、請求項1に記載の装置。

**【請求項 9】**

前記回路は、前記電圧信号のサンプリングされた部分に実質的に基づいて前記DC画素電圧を発生させるように構成されたサンプル及びホールド回路を備える、請求項1に記載の装置。

**【請求項 10】**

前記DC画素電圧を選択的に出力するように構成された出力回路を更に備える、請求項1に記載の装置。

40

**【請求項 11】**

方法であって、

電圧信号を発生させるために入力信号を増幅することと、ここにおいて、前記入力信号は、超音波がイメージング対象アイテムに反射して、圧電層を介して伝播することに応答して発生する、

前記電圧信号からノイズを低減することと、

前記低減ノイズ電圧信号に基づいてDC画素電圧を発生させることと

を備える方法。

**【請求項 12】**

前記電圧信号から前記ノイズを低減することは、キャパシタを通じて前記電圧信号を伝

50

えることを備える、請求項 1 1 に記載の方法。

**【請求項 1 3】**

前記ノイズは、前記入力信号の前記増幅に関する 1 つ以上のデバイスで発生する低周波数ノイズを備える、請求項 1 1 に記載の方法。

**【請求項 1 4】**

前記入力信号は、入力電流信号を備え、前記入力信号を増幅することは、前記電圧信号を発生させるために前記入力電流信号のトランスインピーダンス増幅を実行することを備える、請求項 1 1 に記載の方法。

**【請求項 1 5】**

前記トランスインピーダンス増幅に関連付けられたゲインは、前記圧電層のセンス容量に基づく、請求項 1 4 に記載の方法。10

**【請求項 1 6】**

前記トランスインピーダンス増幅に関連付けられたゲインは、前記圧電層のセンス容量に対する、前記トランスインピーダンス増幅に関連付けられたフィードバックキャパシタの容量の比に基づく、請求項 1 4 に記載の方法。

**【請求項 1 7】**

前記入力信号を増幅することは、ソースフォロア増幅器を使用して前記入力信号を増幅することを備える、請求項 1 1 に記載の方法。

**【請求項 1 8】**

前記 DC 画素電圧を発生させることは、前記 DC 画素電圧を発生させるために前記電圧信号の 1 つ以上のピークを検出することを備える、請求項 1 1 に記載の方法。20

**【請求項 1 9】**

前記 DC 画素電圧を発生させることは、前記 DC 画素電圧を発生させるために前記電圧信号の一部をサンプリング及びホールドすることを備える、請求項 1 1 に記載の方法。

**【請求項 2 0】**

前記 DC 画素電圧を選択的に出力することを更に備える、請求項 1 1 に記載の方法。

**【請求項 2 1】**

装置であって、

電圧信号を発生させるために入力信号を増幅するための手段と、ここにおいて、前記入力信号は、超音波がイメージング対象アイテムに反射して、圧電層を介して伝播することに応答して発生する。30

前記電圧信号からノイズを低減するための手段と、

前記低減ノイズ電圧信号に基づいて DC 画素電圧を発生させるための手段と

を備える装置。

**【請求項 2 2】**

前記電圧信号から前記ノイズを前記低減するための手段は、キャパシタを通じて前記電圧信号を伝えるための手段を備える、請求項 2 1 に記載の装置。

**【請求項 2 3】**

前記ノイズは、前記増幅するための手段で発生する低周波数ノイズを備える、請求項 2 1 に記載の装置。40

**【請求項 2 4】**

前記入力信号は、入力電流信号を備え、前記入力信号を前記増幅するための手段は、前記電圧信号を発生させるために前記入力電流信号のトランスインピーダンス増幅を実行するための手段を備える、請求項 2 1 に記載の装置。

**【請求項 2 5】**

前記トランスインピーダンス増幅に関連付けられたゲインは、前記圧電層のセンス容量に基づく、請求項 2 4 に記載の装置。

**【請求項 2 6】**

前記トランスインピーダンス増幅に関連付けられたゲインは、前記圧電層のセンス容量に対する、前記増幅するための手段の出力と入力とのに結合されたフィードバックキャバ50

シタの容量の比に基づく、請求項 24 に記載の装置。

【請求項 27】

前記入力信号を前記増幅するための手段は、ソースフォロア増幅器を備える、請求項 21 に記載の装置。

【請求項 28】

前記 DC 画素電圧を前記発生させるための手段は、前記 DC 画素電圧を発生させるために前記電圧信号の 1 つ以上のピークを検出するための手段を備える、請求項 21 に記載の装置。

【請求項 29】

前記 DC 画素電圧を前記発生させるための手段は、前記 DC 画素電圧を発生させるために前記電圧信号の一部をサンプリング及びホールドするための手段を備える、請求項 21 に記載の装置。 10

【請求項 30】

前記 DC 画素電圧を選択的に出力するための手段を更に備える、請求項 21 に記載の装置。

【発明の詳細な説明】

【関連出願への相互参照】

【0001】

[0001]本願は、2015年9月17日に米国特許商標庁に出願された非仮出願第 14 / 857,575 に対する優先権及びその利益を主張し、その全内容は、参照によって本明細書に組み込まれる。 20

【技術分野】

【0002】

[0002]本開示の態様は一般に、超音波イメージング装置に関し、より具体的には、超音波イメージング装置で使用するための、低周波数ノイズ低減を有する画素受信機に関する。 30

【背景技術】

【0003】

[0003]超音波イメージング装置は、指紋のような特定のアイテムの電子又はデジタルイメージを取得するために使用され得る。超音波イメージング装置は典型的に、(例えば、ポリフッ化ビニリデン (PVDF) 層のような)送信圧電層を含む超音波送波器と、受信圧電層(例えば、PVDF 層)と、画素センサの 2 次元アレイを備える画素受信機とを備える。一般に、超音波送波器は、画素受信機の下方に位置し、画素受信機は、受信圧電層の下方に位置する。ユーザの指紋のようなイメージング対象アイテムは、受信圧電層の上方に配置される。

【0004】

[0004]動作中、超音波送波器の送信圧電層は、超音波(例えば、10 MHz の超音波)がユーザの指紋のようなイメージング対象アイテムに当たる(encounter)まで画素受信機及び受信圧電層を通って上向きにこの波を発生させるために励起される。超音波は、指紋に反射して、画素受信機に向かって下向きに伝播する。受信圧電層は、画素受信機の画素センサのそれぞれの入力において反射波を電圧へと変換する。画素センサの入力において発生した電圧は、対応する波がユーザの指紋の山に当たったか谷に当たったかの関数である。 40

【0005】

[0005]画素センサは、それぞれの高周波数電圧を処理して、DC 出力画素電圧を発生させる。この DC 出力画素電圧をデジタル化するためにアナログ / デジタル変換器が設けられる。次いで、デジタル化された信号は、指紋認識、指紋データベース格納、及び他のような様々な動作を実行するためにイメージプロセッサによって処理され得る。

【0006】

[0006]これまで、画素受信機は、薄膜トランジスタ (TFT) 技術を使用して実施され 50

てきた。しかしながら、TFT技術を使用して実施される回路は一般に、相補型金属酸化膜半導体(CMOS)技術のような他の技術を使用して実施される回路よりも、電圧変換効率が低く、ノイズが多い。

**【発明の概要】**

**【0007】**

[0007]以下に、1つ又は複数の実施形態の基本的な理解を与えるために、そのような実施形態の簡略化された概要を提示する。この概要は、予期される全ての実施形態の広範な概観ではなく、全ての実施形態の重要な又は不可欠な要素を識別するようにも、任意又は全ての実施形態の範囲を線引きするようにも意図されない。その唯一の目的は、後に提示されるより詳細な説明への前置きとして、1つ又は複数の実施形態のいくつかの概念を簡略化された形式で提示することである。

10

**【0008】**

[0008]本開示の態様は、DC画素電圧を発生させるための装置に関する。装置は、電圧信号を発生させるために入力信号を増幅するように構成された増幅器と、ここにおいて、入力信号は、超音波がイメージング対象アイテムに反射して、圧電層を介して伝播することに応答して発生する、増幅器の出力からノードへの伝播を低減しつつ、増幅器の出力からノードに電圧信号を伝えるように構成されたノイズ低減回路と、低減ノイズ電圧信号(reduced-noise voltage signal)に基づいてDC画素電圧を発生させるように構成された回路とを備える。

20

**【0009】**

[0009]本開示の別の態様は、PC画素電圧を発生させる方法に関する。方法は、電圧信号を発生させるために入力信号を増幅することと、ここにおいて、入力信号は、超音波がイメージング対象アイテムに反射して、圧電層を介して伝播することに応答して発生する、電圧信号からノイズを低減することと、低減ノイズ電圧信号に基づいてDC画素電圧を発生させることとを備える。

30

**【0010】**

[0010]本開示の別の態様は、DC画素電圧を発生させるための装置に関する。装置は、電圧信号を発生させるために入力信号を増幅するための手段と、ここにおいて、入力信号は、超音波がイメージング対象アイテムに反射して、圧電層を介して伝播することに応答して発生する、電圧信号からノイズを低減するための手段と、低減ノイズ電圧信号に基づいてDC画素電圧を発生させるための手段とを備える。

30

**【0011】**

[0011]前述の目的及び関連する目的を達成するために、1つ又は複数の実施形態は、以下に十分に説明されかつ特許請求の範囲において具体的に示される特徴を備える。以下の説明及び添付の図面は、1つ又は複数の実施形態の実例となる特定の態様を詳細に示す。しかしながら、これらの態様は、様々な実施形態の原理が用いられ得る様々な方法のほんの一部しか示さず、説明の実施形態は、そのような態様及びそれらの同等物を全て含むよう意図される。

**【図面の簡単な説明】**

**【0012】**

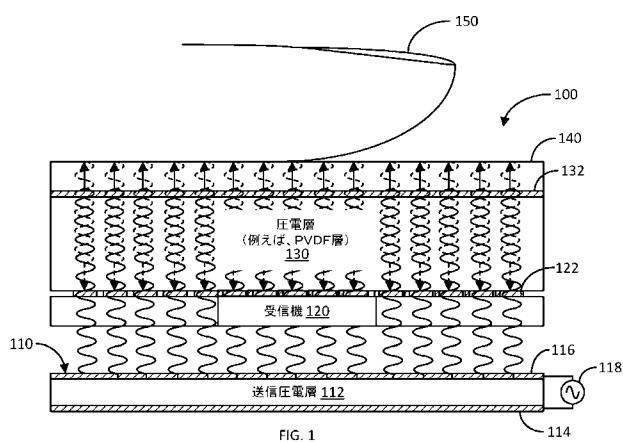

【図1】[0012]図1は、本開示の態様にかかる、例示的な超音波イメージング装置の垂直断面図を例示する。

40

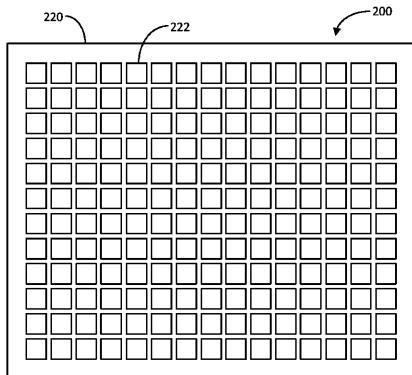

【図2】[0013]図2は、本開示の別の態様にかかる、超音波イメージング装置のための例示的なCMOS受信機の上面図を例示する。

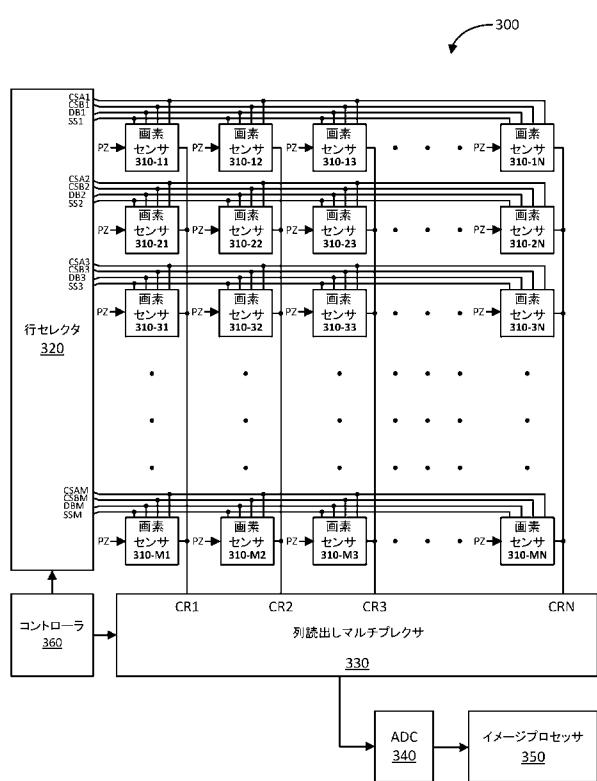

【図3】[0014]図3は、本開示の別の態様にかかる、超音波イメージング装置のための例示的なCMOS受信機の概略図を例示する。

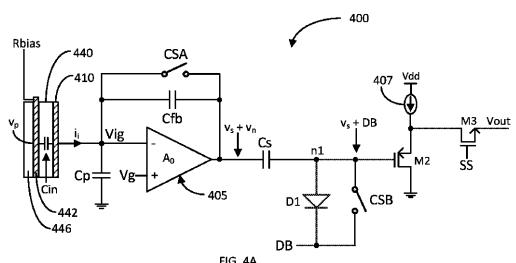

【図4A】[0015]図4Aは、本開示の別の態様にかかる、超音波イメージング装置のための例示的な画素センサの概略図を例示する。

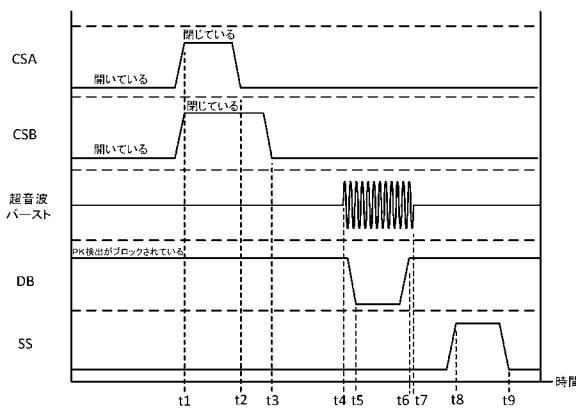

【図4B】[0016]図4Bは、本開示の別の態様にかかる、図4A、5、及び6の画素センサの例示的な動作に関連付けられたタイミング図を例示する。

50

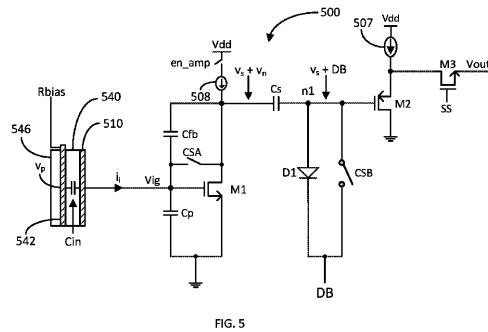

【図5】[0017]図5は、本開示の別の態様にかかる、超音波イメージング装置のための別の画素センサの例示的な概略図を例示する。

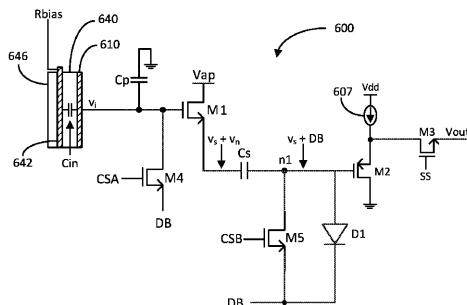

【図6】[0018]図6は、本開示の別の態様にかかる、超音波イメージング装置のための別の例示的な画素センサの概略図を例示する。

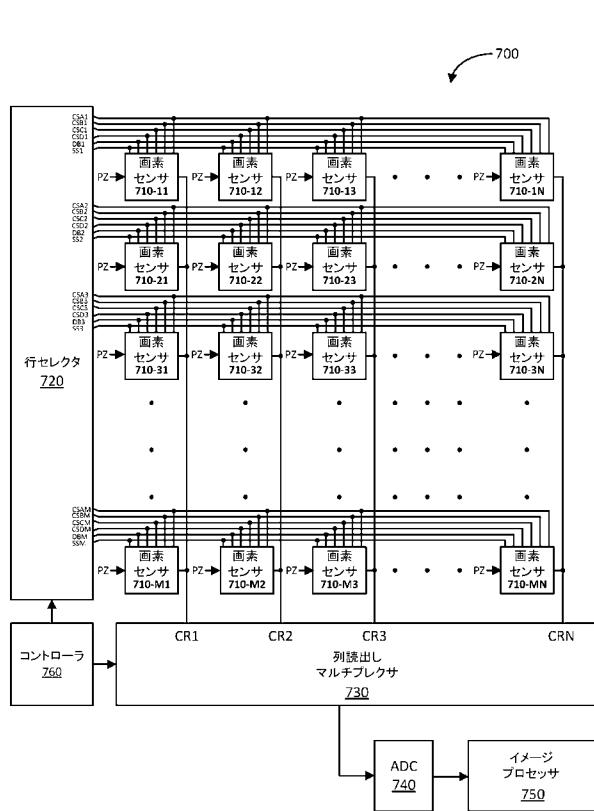

【図7】[0019]図7は、本開示の別の態様にかかる、例示的な超音波イメージング装置のための例示的なCMOS受信機の概略図を例示する。

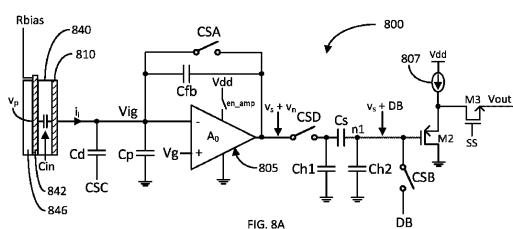

【図8A】[0020]図8Aは、本開示の別の態様にかかる、超音波イメージング装置のための別の例示的な画素センサの概略図を例示する。

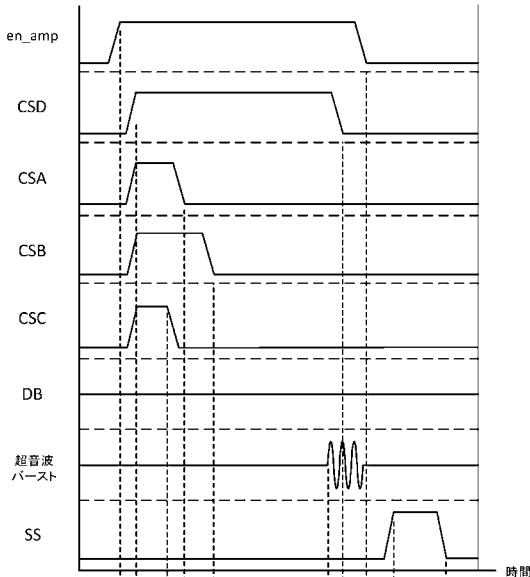

【図8B】[0021]図8Bは、本開示の別の態様にかかる、図8Aの画素センサの例示的な動作に関連付けられたタイミング図を例示する。

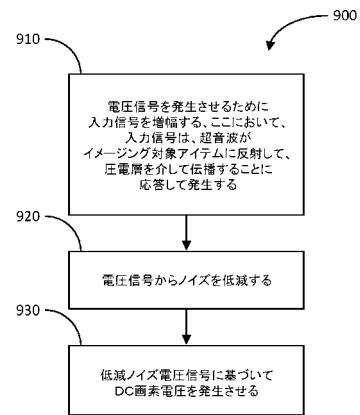

【図9】[0022]図9は、本開示の別の態様にかかる、画素センサによってDC画素電圧を発生させる例示的な方法のフロー図を例示する。

#### 【発明の詳細な説明】

##### 【0013】

[0023]添付の図面に関連して以下に示される詳細な説明は、様々な構成の説明として意図されるものであり、本明細書で説明される概念が実践され得る唯一の構成を表すよう意図されるものではない。詳細な説明は、様々な概念の完全な理解を与えるために特定の詳細を含む。しかしながら、これらの概念がこれらの特定の詳細なしに実践され得ることは当業者には明らかであろう。いくつかの事例では、そのような概念をあいまいにしないために、周知の構造及び構成要素はブロック図の形式で示される。

##### 【0014】

[0024]図1は、本開示の態様にかかる、例示的な超音波イメージング装置100の垂直断面図を例示する。超音波イメージング装置100は、超音波（例えば、10MHzの超音波）を発生させるように構成された超音波送波器110を備える。超音波送波器110は、本明細書で更に述べるように、様々な層を通って上向きに伝播するように超音波を発生させるように構成される。

##### 【0015】

[0025]より具体的には、超音波送波器110は、送信圧電層112と、送信圧電層112に結合された一対の電極114及び116と、励振源118とを備え得る。圧電層112は、ポリフッ化ビニリデン(PVDF)層又は他のタイプの圧電層を備え得る。励振源118は、層が所望の周波数（例えば、10MHz）の超音波を発することができるように、送信圧電層112のための励起電圧を発生させるように構成される。

##### 【0016】

[0026]超音波イメージング装置100は、超音波送波器110の上方に配置された画素受信機120を更に備える。グラススペーサのようなスペーサ（図示されない）が、超音波送波器110と画素受信機120との間に挟まれ得る。本明細書で更に述べるように、画素受信機120は、ユーザの指紋のようなイメージング対象アイテムに関連付けられたそれぞれの電圧を受け、処理するように構成された画素センサの2次元アレイを備える。画素受信機120は、イメージング対象アイテムに関連付けられた入力画素電圧を受けるための、2次元アレイ状に配列された複数の入力メタライゼーションパッド122を備える。

##### 【0017】

[0027]超音波イメージング装置100は、画素受信機120上に配設された及び／又はその上方に配置された受信圧電層130を更に備える。受信圧電層130は、イメージング対象アイテム（例えば、ユーザの指紋）から反射した超音波を、画素受信機120の画素センサのための入力画素電圧へと変換する。同様に、受信圧電層130は、ポリフッ化ビニリデン(PVDF)層又は他のタイプの圧電層を備え得る。電極132（例えば、メタライゼーション層）は、異なる動作のための（例えば、接地又は他の）電位を受けるために受信圧電層130の上に設けられ得る。

##### 【0018】

10

20

30

40

50

[0028]超音波イメージング装置100は、電極132の上に配設された圧盤140を更に備える。圧盤140は、圧盤より下層の超音波イメージング装置100の構成要素のための保護被膜として機能する。追加的に、圧盤140は、図1に例示されるように、ユーザの指150のようなイメージング対象アイテムが置かれ得る表面を設ける働きをする。

#### 【0019】

[0029]動作中、超音波送波器110は、画素受信機120、受信圧電層130、及び圧盤140を経由してユーザの指150に向かって上向きに伝播する超音波（例えば、10MHzの超音波）のバーストを発生させるように動作される。ユーザの指150上の入射超音波は、受信圧電層130を通って下向きに伝播する反射超音波を生成する。圧電層130は、受信機120の画素センサのそれぞれの入力122において反射波を電圧へと変換する。電圧の各々の振幅は、対応する反射超音波部分が指紋の山に当たったか谷に当たったかに依存する。画素センサは、所望のイメージングアプリケーションに従って更にデジタル化及び処理するための対応する直流(DC)画素電圧を発生させるために入力画素電圧を処理する。

10

#### 【0020】

[0030]図2は、本開示の別の態様にかかる、超音波イメージング装置のための例示的なCMOS受信機200の上面図を例示する。CMOS受信機200は、前述した超音波イメージング装置100の画素受信機120の例示的な詳細な実施であり得る。

#### 【0021】

[0031]CMOS受信機200は、画素センサのアレイを含むCMOS集積回路(ASIC)220を備える。CMOS ASIC220の上部は、2次元アレイ状に配列された複数の入力メタライゼーションパッド222を含む。図2には示されていないが、CMOS受信機200は、入力メタライゼーションパッド222のアレイの上に配設された誘電体保護層を含み得る。受信圧電層130は、例えば、接着剤を使用して、CMOS ASIC220の上面に取り付けられ得る。メタライゼーションパッド222は、CMOS受信機200の画素センサへのそれぞれの入力として機能し、そこでは、対応する反射超音波に関する入力画素電圧が出現する。

20

#### 【0022】

[0032]図3は、本開示の別の態様にかかる、超音波イメージング装置のための例示的なCMOS受信機300の概略図を例示する。CMOS受信機300は、前述した受信機120及びCMOS受信機200のうちの一方又は両方の例示的な詳細な実施であり得る。

30

#### 【0023】

[0033]具体的には、CMOS受信機300は、画素センサ $310 - 11 \sim 310 - MN$ の2次元アレイを備える。この例では、画素センサアレイのサイズは $M \times N$ である。すなわち、画素センサアレイは、M行の画素センサ及びN列の画素センサを有する。画素センサ $310 - 11 \sim 310 - 1N$ は、アレイの第1の行にあり、画素センサ $310 - 21 \sim 310 - 2N$ は、アレイの第2の行にあり、画素センサ $310 - 31 \sim 310 - 3N$ は、アレイの第3の行にあり、画素センサ $310 - M1 \sim 310 - MN$ は、アレイの第Mの行にある。同様に、画素センサ $310 - 11 \sim 310 - M1$ は、アレイの第1の列にあり、画素センサ $310 - 12 \sim 310 - M2$ は、アレイの第2の列にあり、画素センサ $310 - 13 \sim 310 - M3$ は、アレイの第3の列にあり、画素センサ $310 - 1N \sim 310 - MN$ は、アレイの第Nの列にある。示されるように、画素センサ $310 - 11 \sim 310 - MN$ の全てが、そこからそれぞれの入力画素電圧を受けるために圧電(PZ)層に結合されている。

40

#### 【0024】

[0034]CMOS受信機300は、行セレクタ320と、列読出しマルチプレクサ330と、アナログ/デジタル変換器(ADC)340と、イメージプロセッサ350と、コントローラ360とを更に備える。行セレクタ320は、対応する出力DC画素電圧を発生させる目的で、コントローラ360の制御下で、画素センサの行をアクティブ化する。これに関連して、行セレクタ320は、行 $310 - 11 / 310 - 1N \sim 310 - M1 / 3$

50

10-MNに対して、それぞれ、4つの信号CSA1/CSB1/DB1/SS1~CSA M/CSBM/DBM/SSMを発生させる。

#### 【0025】

[0035]本明細書でより詳細に述べられるように、CSA1~CSA M信号は、対応する画素センサの電荷をフィードバックキャパシタからクリアする。CSB1~CSBM信号は、対応する画素センサで発生する、増幅された電圧信号に対して共通モード電圧を設定する。DB1~DBM信号は、対応する画素センサの、増幅された電圧信号のピークに関するDC画素電圧を発生させるためのピーク検出器をイネーブルするために使用される。SS1~SSM信号は、対応する画素センサで発生するDC画素電圧を、対応する列読出しラインCR1~CRNに印加させる。

10

#### 【0026】

[0036]コントローラ360の制御下で、列読出しマルチプレクサ330は、アクティブ化された行の画素センサから出力DC画素電圧を読み出す。マルチプレクサ330は、DC画素電圧を連続方法でADC340に出力し得る。マルチプレクサ330が、それぞれ、複数のADCに並行してDC画素電圧の少なくとも一部を出力するように構成され得ることは理解されるものとする。ADC340は、DC画素電圧をデジタル化し、それらをイメージプロセッサ350に供給する。イメージプロセッサ350は、受けたデジタル化済み画素電圧に基づいて、任意の数の動作を実行し得る。例えば、イメージプロセッサ350は、前に記憶された認証済み指紋イメージに基づいて指紋認証を実行し得る。

20

#### 【0027】

[0037]図4Aは、本開示の別の態様にかかる、超音波イメージング装置のための例示的な画素センサ400の概略図を例示する。画素センサ400は、前述した画素センサ310-11~310-MNのうちの任意のものの例示的な詳細な実施であり得る。例示されるように、画素センサ400は、受信圧電層440に結合された入力メタライゼーションパッド410を備える。前述したように、電極442は、受信圧電層440の上に配設され、圧盤446は、電極442の上に配設される。指紋のようなイメージング対象アイテムは、圧盤442の上に配置され得る。電極442は、接地電位又は他の電位であり得るRbias電圧を受けるように構成され得る。

20

#### 【0028】

[0038]画素センサ400は、正の入力と、負の入力と、出力とを含むトランスインピーダンス増幅器(TIA)405を備える。TIA405は、出力と負の入力との間に結合されたフィードバックキャパシタCfbを更に備える。TIA405の正の入力は、基準DC電圧Vgを受けるように構成される。TIA405の負の入力は、画素センサ400の入力メタライゼーションパッドに結合される。画素センサ400が相補型金属酸化膜半導体(CMOS)技術を使用して実施され得るため、TIA405は、接地基板上に形成された電界効果トランジスタ(FET)で実施され得る。そのため、寄生容量Cpが、入力メタライゼーション層410と接地基板との間に存在し得る。

30

#### 【0029】

[0039]そのような構成では、TIA405は、超音波バーストが、圧盤446の上に配設されたイメージング対象アイテムに反射することに応答して圧電層440で発生する電圧v<sub>p</sub>に基づいて入力電流信号i<sub>i</sub>を増幅するように構成される。TIA405が、非常に高い開ループゲインA<sub>o</sub>(例えば、カスコード構成)を有すると仮定すると、負の入力における電圧Vigは、TIAの正の入力における基準DC電圧Vgと略同じであり得る。そのため、TIA405は、実質的に以下の関係によって求められ得る閉ループゲインA<sub>c1</sub>で入力電圧v<sub>p</sub>を増幅するように構成される:

40

#### 【数1】

$$A_{cl} = \frac{C_{in}}{C_{fb}}$$

ここで、Cfbは、フィードバックキャパシタCfbの容量であり、Cinは、圧電層440のセンス容量である。

50

## 【0030】

[0040]追加的に、画素センサ400は、TIA405の出力と負の入力との間に結合された制御可能スイッチCSAを備える。制御可能スイッチCSAは、前述したように、行セレクタ320で発生する制御信号CSA1～CSAMのうちの対応する1つによって制御されるよう構成される。対応する制御信号は、前の動作周期から残っている可能性のある全ての(any)電荷をフィードバックキャパシタCfbからクリアするために、特定の時間にスイッチCSAを開閉する。TIA405は、実質的に以下の式によって求められ得る電圧信号 $v_s$ を発生させるように構成される：

## 【数2】

$$v_s = v_p * A_{cl} = v_p * \frac{C_{in}}{C_{fb}} = \frac{i_i}{C_{fb}}$$

TIA405が、入力電流信号 $i_i$ を増幅するように構成されるため、TIA405で発生する電圧信号 $v_s$ が実質的に寄生容量 $C_p$ から独立することは留意されるべきである。すなわち、換言すると、画素センサ400の感度は、実質的に、寄生容量 $C_p$ に依存しない。

## 【0031】

[0041]追加的に、画素センサ400の感度に対する寄生容量 $C_p$ の影響を更に最小化するために、TIA405は、1つ又は複数の小型デバイス又はFETを使用して実施され得る。しかしながら、小型デバイスは、より多くの低周波数ノイズを発生させる。したがって、画素センサ400は、TIA405で発生する電圧信号 $v_s$ の一次ノイズ成形又は低減を実行するための回路を更に備える。これに関連して、画素センサ400は、キャパシタCsと、ダイオードD1と、制御可能スイッチCSBとを更に備える。キャパシタCsは、TIA405の出力と中間ノードn1との間に結合される。ダイオードD1は、中間ノードn1に結合されたアノードと、ダイオードバイアス(DB)電圧のソースに結合されたカソードと含む(例えば、行セレクタ320、これは、信号DB1～DBMのうちの対応する1つを発生させる)。制御可能スイッチCSBは、中間ノードn1とDB電圧のソースとの間に結合される。制御可能スイッチCSBは、前述したように、行セレクタ320で発生する制御信号CSB1～CSBMのうちの対応する1つによって制御されるよう構成される。

## 【0032】

[0042]画素センサ400は、p型MOSFET(「PMOS」)M2と、電流源407と、n型MOSFET(「NMOS」)M3とを含む出力回路を更に備える。PMOS M2は、NMOS M3のドレインに結合されたソースと、中間ノードn1に結合されたゲートと、接地に結合されたドレインとを含むソースフォロア増幅器(例えば、略ユニティゲインを有する)として構成される。電流源407は、電圧レールVddとPMOS M2のソースとの間に結合される。NMOS M3は、次に、信号SSを受けるように構成されたゲートと、対応する列読出しラインに結合されたソースとを含む。信号SSは、行セレクタ320で発生する信号SS1～SSMのうちの対応する1つであり得る。出力DC画素電圧 $V_{out}$ は、NMOS M3のソースにおいて生成される。

## 【0033】

[0043]図4Bは、本開示の別の態様にかかる、画素センサ400の例示的な動作に関連付けられたタイミング図を例示する。タイミング図の水平軸すなわちx軸は時間を表し、垂直軸は、CSA、CSB、超音波バースト、DB、及びSSの状態又は振幅を表す。

## 【0034】

[0044]このタイミング図によれば、時間t1において、CSA及びCSBは、スイッチCSA及びCSBを閉じるためにアサート状態(asserted states)にされる。スイッチCSAを閉じることは、例えば、画素センサ400の前の動作周期からフィードバックキャパシタCfb上に存在し得る全ての電荷をクリアする。スイッチCSBを閉じることは、中間ノードn1において発生する後続の電圧信号に対して共通モード電圧を設定するためにDB電圧を中間ノードn1に印加するように構成される。フィードバックキャパシタ

10

20

30

40

50

$C_{fb}$  から電荷をクリアするのに十分な所定の時間インターバルの後、時間  $t_2$  において、スイッチ CSA が開けられる。スイッチ CSA が開けられると、スイッチ及び低周波数ノイズ  $v_n$  が、TIA 405 の出力において生成される。キャパシタ Cs は、ノイズ  $v_n$  が、そのハイパス周波数特性により、最終的に中間ノード n1 に行くことを防ぎ、中間ノード n1 は、DB 電圧に接続される。これは、TIA 405 の出力において行われる一次ノイズ成形又は低減の一部である。一次ノイズ成形を達成するための所定の時間インターバルの後、時間  $t_3$  において、スイッチ CSB が開けられる。

#### 【0035】

[0045] 時間  $t_4$  において、受信圧電層 440、電極 442、及び圧盤 446 を通る超音波バーストを発生させるために、超音波送波器がイネーブルにされる。前述したように、超音波バーストは、入力電圧信号  $v_p$ （例えば、10 MHz の入力電圧信号）を生成するために、ユーザの指に反射して、圧電層 440 に戻る。入力電圧信号の振幅は、対応する反射超音波がユーザの指紋の山に当たったか谷に当たったかの関数、すなわち、イメージング対象アイテムの関数、である。10

#### 【0036】

[0046] 入力画素電圧  $v_p$  に応答して、入力電流信号  $i_i$  が発生し、これは、増幅された電圧信号  $v_s$  を発生させるために TIA 405 によって増幅される。したがって、電圧信号  $v_s$  の振幅は、反射した超音波に基づき、これは、次に、イメージング対象アイテム（例えば、ユーザの指紋）に基づく。電圧信号  $v_s$  が、超音波（例えば、10 MHz）と略同じ周波数で交流(alternate)となるため、キャパシタ Cs は、TIA 405 の出力において低周波数ノイズ  $v_n$  の少なくとも一部を維持しつつ、電圧信号  $v_s$  が、中間ノード n1 に通過することを可能にする。この場合もやはり、これは、TIA 405 の出力において行われる一次ノイズ成形又は低減の一部である。20

#### 【0037】

[0047] 時間  $t_5$  において、DB 電圧は、ダイオード D1 によって実行される電圧信号  $v_s$  のピーク検出をイネーブルにするために下げられる（アサート状態）。電圧信号  $v_s$  のピークがダイオード D1 に順方向バイアスをかけるため、ダイオード D1 にわたって寄生キャパシタを充電するためにこのダイオードを通して電流が発生する。故に、中間ノード n1 における DC 画素電圧は、電圧信号  $v_s$  の 1 つ又は複数のピークに基づいて出現する。故に、述べたように、電圧信号  $v_s$  がイメージング対象アイテムに基づくため、DC 画素電圧もまた、イメージング対象アイテムに基づく。DC 画素電圧を出現させるのに十分な時間インターバルの後、時間  $t_6$  において、DB 電圧は、その元のレベル（デアサート状態（de-asserted state））に戻され、時間  $t_7$  において、超音波バーストを発生させることを停止するために、超音波送波器がディセーブルにされる。30

#### 【0038】

[0048] DC 画素電圧が中間ノード n1 において出現した後、時間  $t_8$  において、SS は、NMOS M3 をオンにし、ソースフォロア PMOS M2 を経由して対応する列読出しラインにおいて出力 DC 画素電圧  $V_{out}$  を生成するために、アサート状態に上げられる。列読出しマルチプレクサ 330 が出力 DC 画素電圧  $V_{out}$  を読み出すのに十分な時間インターバルの後、画素センサ 400 の動作周期を完了するために、SS がそのデアサート状態に下げられる。40

#### 【0039】

[0049] 図 5 は、本開示の別の態様にかかる、超音波イメージング装置のための別の例示的な画素センサ 500 の概略図を例示する。画素センサは、画素センサ 400 の例示的なりより詳細な実施であり得る。画素センサ 500 中の同様の要素は、同じ識別子と、最上位の桁が「4」ではなく「5」である点を除いて同じ参照番号とを含む。

#### 【0040】

[0050] 要するに、画素センサ 500 は、増幅された電圧信号  $v_s$  を発生させるために（超音波がイメージング対象アイテムに反射することに応答して圧電層 540 で発生する電圧  $v_p$  に基づいて）入力電流信号  $i_i$  を増幅するためのトランスインピーダンス増幅器（50

TIA)と、電圧信号 $v_s$ から低周波数ノイズを低減するための一次ノイズ成形及び低減回路と、低減ノイズ電圧信号 $v_s$ の1つ又は複数のピークに基づいてDC画素電圧を発生させるためのピーク検出器と、列読出しラインに出力DC画素電圧 $V_{out}$ を選択的に供給するための出力回路とを備える。

#### 【0041】

[0051]具体的には、画素センサ500は、受信圧電層540に結合された入力メタライゼーションパッド510を備える。画素センサ400と同様に、電極542は、受信圧電層540の上に配設され、圧盤546は、電極542の上に配設される。指紋のようなイメージング対象アイテムは、圧盤542の上に配置され得る。電極542は、接地電位又は他の電位であり得るRbias電圧を受けるように構成され得る。

10

#### 【0042】

[0052]画素センサ500は、電圧信号 $v_s$ を発生させるために入力電流信号 $i_i$ のトランスインピーダンス増幅を実行するように構成されたNMOS M1を備える。入力電流信号 $i_i$ は、超音波がイメージング対象アイテムに反射して、圧電層540を介して伝播することに応答して発生する。NMOS M1は、入力メタライゼーションパッド510に結合されたゲートと、接地に結合されたソースと、電圧信号 $v_s$ を発生させるための出力として機能するドレインとを含む。NMOS M1がCMOS IC基板上に実施され得るため、入力メタライゼーション層510と接地基板との間に寄生容量 $C_p$ が存在し得る。

20

#### 【0043】

[0053]画素センサ500は、NMOS M1のドレインとゲートとの間にフィードバックキャパシタ $C_{fb}$ を更に備える。追加的に、制御可能スイッチCSAも、NMOS M1のドレインとゲートとの間に結合される。スイッチ $en\_amp$ 及び電流源508は、電圧レール $V_{dd}$ と接地との間でNMOS M1と直列に結合される。スイッチ $en\_amp$ は、NMOS M1によって実施される入力電流信号 $i_i$ のトランスインピーダンス増幅をイネーブルにするために閉じられ、このトランスインピーダンス増幅をディセーブルするために開けられる。バイアス電圧 $V_{ig}$ は、制御可能スイッチCSAが閉じられている間、NMOS M1のゲートにおいて出現する。このような構成では、NMOS M1は、実質的に以下の関係によって求められ得る閉ループゲイン $A_{cl}$ を供給する：

#### 【数3】

30

$$A_{cl} = \frac{C_{in}}{C_{fb}}$$

ここで、 $C_{fb}$ は、フィードバックキャパシタ $C_{fb}$ の容量であり、 $C_{in}$ は、圧電層540のセンス容量である。

#### 【0044】

[0054]制御可能スイッチCSAは、前述したように、行セレクタ320で発生する制御信号CSA1～CSAMのうちの対応する1つによって制御されるように構成される。対応する制御信号は、前の動作周期から残っている可能性のある全ての電荷をフィードバックキャパシタ $C_{fb}$ からクリアするために、及び、NMOS M1のゲートにおいてバイアス電圧 $V_{ig}$ を出現させるために、特定の時間にスイッチCSAを開閉する。NMOS M1は、実質的に以下の式によって求められ得る電圧信号 $v_s$ を発生せるように構成される：

40

#### 【数4】

$$v_s = v_p * A_{cl} = v_p * \frac{C_{in}}{C_{fb}} = \frac{i_i}{C_{fb}}$$

NMOS M1によって供給される開ループゲイン $A_{cl}$ がハイである場合(これは、カスコード動作のために1つ又は複数の追加のデバイスによりハイにされ得る)、電圧信号 $v_s$ は、寄生容量 $C_p$ から実質的に独立しているであろうことは留意されるべきある。すなわち、換言すると、画素センサ500の感度は、寄生容量 $C_p$ の影響を大きくは受けないであろう。

50

## 【0045】

[0055]追加的に、画素センサ500の感度に対する寄生容量C<sub>p</sub>の影響を更に最小化するため、NMOS M1(及び、付隨の1つ又は複数のカスコードデバイス)は、比較的小さくされ得る。しかしながら、前述したように、小型デバイスは、より多くの低周波数ノイズを発生させる。したがって、画素センサ500は、NMOS M1のドレインにおいて発生する電圧信号v<sub>s</sub>の一次ノイズ成形又は低減を実行するための回路を更に備える。これに関連して、画素センサ500は、キャパシタC<sub>s</sub>と、ダイオードD1と、制御可能スイッチCSBとを更に含む。キャパシタC<sub>s</sub>は、NMOS M1のドレインと中間ノードn1との間に結合される。ダイオードD1は、中間ノードn1に結合されたアノードと、ダイオードバイアス(DB)電圧のソース(例えば、行セレクタ320、これは、信号DB1～DBMのうちの対応する1つを発生させる)に結合されたカソードとを含む。制御可能スイッチCSBは、中間ノードn1とDB電圧のソースとの間に結合される。制御可能スイッチCSBは、前述したように、行セレクタ320で発生する制御信号CSB1～CSBMのうちの対応する1つによって制御されるように構成される。10

## 【0046】

[0056]画素センサ500は、p型MOSFET(「PMOS」)M2と、電流源507と、n型MOSFET(「NMOS」)M3とを含む出力回路を更に備える。PMOS M2は、NMOS M3のドレインに結合されたソースと、中間ノードn1に結合されたゲートと、接地に結合されたドレインとを含む(例えば、略ユーティゲインを有する)ソースフォロア增幅器として構成される。電流源507は、電圧レールVddとPMOS M2のソースとの間に結合される。NMOS M3は、次に、信号SSを受けるように構成されたゲートと、対応する列読出しラインに結合されたソースとを含む。信号SSは、行セレクタ320で発生する信号SS1～SSMのうちの対応する1つであり得る。画素センサ500で発生する出力DC画素電圧は、NMOS M3のソースにおいて生成される。20

## 【0047】

[0057]図4Aのタイミング図は、画素センサ500の動作に適用可能である。タイミング図には反映されていないが、en\_ampスイッチは、NMOS M1によって実施されるトランスインピーダンス増幅をイネーブルにするために、動作周期の開始時に閉じられ、終了時に開けられる。30

## 【0048】

[0058]具体的には、時間t1において、スイッチCSA及びCSBが閉じられる。スイッチCSAは、例えば、画素センサ500の前の動作周期から存在し得る全ての電荷をフィードバックキャパシタCfbからクリアするために閉じられる。スイッチCSAを閉じることはまた、NMOS M1のためのゲートバイアス電圧Vigを生成する。スイッチCSBは、中間ノードn1において共通モード電圧DBを出現させるために閉じられる。時間t2において、スイッチCSAが開けられ、これにより、スイッチ及び低周波数ノイズv<sub>n</sub>が、NMOS M1のドレインにおいて発生する。しかしながら、ノイズv<sub>n</sub>は、一次ノイズ成形又は低減が、閉じられたCSBスイッチを介してDB電圧につながっているキャパシタCsによって実行されることにより、中間ノードn1に伝播しない。時間t3において、スイッチCSBが開けられる。40

## 【0049】

[0059]時間t4において、超音波バーストを発生させるために、超音波送波器がイネーブルにされる。前述したように、超音波バーストは、入力電流信号i<sub>i</sub>を生成する。NMOS M1は、NMOS N1のドレインにおいて電圧信号v<sub>s</sub>を発生させるために入力電流信号i<sub>i</sub>にトランスインピーダンス増幅を適用する。電圧信号v<sub>s</sub>が、超音波(例えば、10MHz)と略同じ周波数で周期する(cycle)ため、キャパシタCsのハイパスフィルタ特性は、中間ノードn1に伝播することからノイズv<sub>n</sub>の少なくとも一部を維持しつつ、電圧信号v<sub>s</sub>が中間ノードn1に通過することを可能にする。時間t5において、DB電圧は、ダイオードD1によって実行される電圧信号v<sub>s</sub>のピーク検出をイネーブル50

にするために下げられる。ピーク検出は、中間ノード n 1においてDC画素電圧を生成する。

#### 【0050】

[0060]中間ノード n 1においてDC画素電圧を出現させるのに十分な時間インターバルの後、時間 t 6において、ダイオード D 1によって実行されるピーク検出をディセーブルにするためにDB電圧がその元の電圧レベルに上げられる。次いで、時間 t 8において、NMOS M 3をオンにして、ソースフォロアPMOS M 2を経由して対応する列読出しラインに出力DC画素電圧 V<sub>out</sub>を印加するために、SS信号がアサート状態に上げられる。列読出しマルチプレクサ 330が出力DC画素電圧 V<sub>out</sub>を読み出すのに十分な時間インターバルの後、NMOS M 3をオフにして、画素センサ 500の動作周期を完了するために、SS信号がそのデアサート状態に下げられる。10

#### 【0051】

[0061]図 6 は、本開示の別の様にかかる、超音波イメージング装置のための別の例示的な画素センサ 600 の概略図を例示する。画素センサ 600 は、画素センサ 500 と同様の要素を含み、これらは、同じ構成要素識別子と、最上位の桁が「5」ではなく「6」である点を除いて同じ参照番号とによって識別され得る。

#### 【0052】

[0062]要するに、画素センサ 600 は、増幅された電圧信号 v<sub>s</sub> を発生させるために(超音波がイメージング対象アイテムに反射して、圧電層を介して伝播することに応答して発生する)入力電圧信号 v<sub>i</sub> を増幅するように構成されたソースフォロア増幅器と、電圧信号 v<sub>s</sub> から低周波数ノイズへの一次ノイズ成形及び低減と、増幅された電圧信号 v<sub>s</sub> の1つ又は複数のピークに基づいてDC画素電圧を発生させるためのピーク検出器と、列読出しラインにDC画素電圧を選択的に出力するための出力回路とを備える。20

#### 【0053】

[0063]具体的には、画素センサ 600 は、受信圧電層 640 に結合された入力メタライゼーションパッド 610 を備える。前の実施形態にあるように、電極 642 は、受信圧電層 640 の上に配設され、圧盤 646 は、電極 642 の上に配設される。指紋のようなイメージング対象アイテムは、圧盤 642 の上に配置され得る。電極 642 は、接地電位又は他の電位であり得る Rbias 電圧を受けるように構成され得る。

#### 【0054】

[0064]画素センサ 600 は、略ユニティ電圧ゲインを有する入力メタライゼーションパッド 610において出現する入力電圧信号 v<sub>i</sub> を増幅するためにソースフォロア増幅器として構成されたNMOS M 1を備える。入力電圧信号 v<sub>i</sub> は、超音波がイメージング対象アイテムに反射して、圧電層 640 を介して伝播することに応答して発生する。NMOS M 1は、入力メタライゼーションパッド 610 に結合されたゲートと、バイアス電圧レール V<sub>ap</sub> に結合されたドレインと、出力電圧信号 v<sub>s</sub> を発生させるためのソースとを含む。NMOS M 1がCMOS IC基板上に実施され得るため、入力メタライゼーション層 610 と接地基板との間に寄生容量 C<sub>p</sub> が存在し得る。30

#### 【0055】

[0065]画素センサ 600 は、NMOS M 1のゲートとDB電圧のソース(例えば、行セレクタ 320)との間に結合された別のNMOS M 4を更に備える。NMOS M 4は、行セレクタ 320 で発生する制御信号 CSA1 ~ CSAM のうちの対応する1つである制御信号 CSA を受けるように構成されたゲートを含む。制御信号 CSA は、例えば、画素センサ 600 の前の動作周期から残っている全ての電荷を NMOS M 1 のゲートからクリアするために、特定の時間に NMOS M 4 をオン及びオフにする。追加的に、NMOS M 4 をオンにすることはまた、NMOS M 1 のゲートに対するバイアス電圧を出現させるために行われる。40

#### 【0056】

[0066]画素センサ 600 の感度に対する寄生容量 C<sub>p</sub> の影響を低減するために、NMOS M 1 は、比較的小さくされ得る。しかしながら、前述したように、小型デバイスは、50

より多くの低周波数ノイズを発生させる。したがって、画素センサ600は、ソースフォロア增幅器(NMOS M1)の出力において一次ノイズ成形又は低減を実行するための回路を更に備える。これに関連して、画素センサ600は、キャパシタCsと、ダイオードD1と、NMOS M5とを更に含む。キャパシタCsは、NMOS M1のソースと中間ノードn1との間に結合される。ダイオードD1は、中間ノードn1に結合されたアノードと、DB電圧のソース(例えば、行セレクタ320)に結合されたカソードとを含む。NMOS M5は、中間ノードn1とDB電圧のソースとの間に結合される。NMOS M5は、前述したように、行セレクタ320で発生する制御信号CSB1～CSBMのうちの対応する1つであり得る制御信号CSBを受けるように構成されたゲートを含む。

## 【0057】

[0067]画素センサ600は、p型MOSFET(「PMOS」)M2と、電流源607と、n型MOSFET(「NMOS」)M3とを含む出力回路を更に備える。PMOS M2は、NMOS M3のドレインに結合されたソースと、中間ノードn1に結合されたゲートと、接地に結合されたドレインとを含む(例えば、略ユニティゲインを有する)ソースフォロア增幅器として構成される。NMOS M3は、次に、信号SSを受けるように構成されたゲートと、対応する列読出しラインに結合されたソースとを含む。信号SSは、行セレクタ320で発生する信号SS1～SSMのうちの対応する1つであり得る。画素センサ600で発生する出力DC画素電圧Voutは、NMOS M3のソースにおいて生成される。

## 【0058】

[0068]図4Aのタイミング図は、画素センサ600の動作に適用可能である。例えば、時間t1において、NMOS M4及びM5がオンにされる。NMOS M4は、例えば、画素センサ600の前の動作周期からNMOS M1のゲートに存在し得る全ての電荷をゲートからクリアするために閉じられる。NMOS M4をオンにすることはまた、NMOS M1のためのゲートバイアス電圧を生成する。NMOS M5は、中間ノードn1において共通モード電圧DBを出現させるためにオンにされる。時間t2において、NMOS M4がオフにされ、これにより、スイッチ及び低周波数ノイズvnが、ソースフォロア増幅器(NMOS M1)の出力(ソース)において発生する。しかしながら、ノイズvnは、一次ノイズ成形又はハイパスフィルタ処理が、NMOS M5を介してDB電圧につながっているキャパシタCsによって実行されることにより、中間ノードn1に伝播しない。時間t3において、NMOS M5がオフにされる。

## 【0059】

[0069]時間t4において、超音波バーストを発生させるために、超音波送波器がイネーブルにされる。前述したように、超音波バーストは、入力電圧信号viを生成する。ソースフォロアとして構成されたNMOS M1は、NMOS N1のソースにおいて、増幅された電圧信号vsを発生させるために、略ユニティゲインで、入力電圧信号viを増幅する。電圧信号vsが、超音波(例えば、10MHz)と略同じ周波数で周期するため、キャパシタCsのハイパスフィルタ特性は、ノイズvnが中間ノードn1に通過することを実質的に防ぎしつつ、電圧信号vsが中間ノードn1に通過することを可能にする。時間t5において、DB電圧は、ダイオードD1によって実行される電圧信号vsのピーク検出をイネーブルにするために下げられる。ピーク検出は、DC画素電圧を生成する。

## 【0060】

[0070]DC画素電圧を出現させるのに十分な時間インターバルの後、時間t6において、ダイオードD1によって実行されるピーク検出をディセーブルするためにDB電圧がその元の電圧レベルに上げられる。次いで、時間t8において、NMOS M3をオンにして、出力DC画素電圧Voutを対応する列読出しラインに印加するために、SS信号がアサート状態に上げられる。列読出しマルチプレクサ330が出力DC画素電圧Voutを読み出すのに十分な時間インターバルの後、NMOS M3をオフにして、画素センサ600の動作周期を完了するために、SS信号がそのデアサート状態に下げられる。

## 【0061】

10

20

30

40

50

[0071]図7は、本開示の別の態様にかかる、超音波イメージング装置のための例示的なCMOS受信機700の概略図を例示する。CMOS受信機700は、前述したCMOS受信機300のものに類似し、最上位の桁が「3」ではなく「7」である同じ参照番号によって示されるように多くの同様の素子を含む。CMOS受信機700は、行セレクタ720が、画素センサを動作させるための追加の信号を発生させる点で、CMOS300とは異なる。

#### 【0062】

[0072]より具体的には、CMOS受信機700は、M行及びN列の2次元アレイ状に配列された画素センサ710-11~710-MNを備え、ここにおいて、画素センサは、受信圧電層(PZ)に結合される。CMOS受信機700は、それぞれ、画素センサ710-11/710-1N~710-M1/710-MNのための制御信号CSA1/CSB1/CSC1/CSD1/DB1/SS1~CSAM/CSBM/CSCM/CSDM/DBM/SSMを発生させるように構成された行セレクタ720を更に備える。追加的に、CMOS受信機700は、列読出しラインCR1~CRNを介して画素センサで発生する出力DC画素電圧を読み出すように構成された列読出しマルチブレクサ730を含む。

10

#### 【0063】

[0073]CMOS700は、行セレクタ720及び列読出しマルチブレクサ730の動作を制御するためのコントローラ760を更に備える。更に、CMOS受信機700は、読み出したDC画素電圧をデジタル画素信号に変換するためのアナログ/デジタル変換器(ADC)740と、1つ又は複数の所定のアプリケーションに基づいてデジタル画素信号を処理するためのイメージプロセッサ750とを備える。

20

#### 【0064】

[0074]行セレクタ720で発生する信号CSA1/CSB1/DB1/SS1~CSAM/CSBM/DBM/SSMは、CMOS受信機300の行セレクタ320を参照して述べられている。これらの信号に加えて、行セレクタ720は、制御信号CSC1/CSD1~CSCM/CSDMを発生させる。本明細書でより詳細に述べたように、CSC1~CSCM信号は、対応する画素センサのトランスインピーダンス(TIA)増幅器の出力において共通モード電圧を設定するためのものである。CSD1~CSDMは、本明細書で更に詳細に述べたように、信号のピーク検出のために、電圧信号 $V_s$ のピーク中、TIA増幅器の出力を中間ノードn1から結合解除するためのものである。

30

#### 【0065】

[0075]図8Aは、本開示の別の態様にかかる、超音波イメージング装置のための別の例示的な画素センサ800の概略図を例示する。画素センサ800は、前述した画素センサ710-11~710-MNのうちの任意のものの例示的な詳細な実施であり得る。例示したように、画素センサ800は、受信圧電層840に結合された入力メタライゼーションパッド810を備える。前述したように、電極842は、受信圧電層840の上に配設され、圧盤846は、電極842の上に配設される。指紋のようなイメージング対象アイテムは、圧盤842の上に配置され得る。電極842は、接地電位又は他の電位であり得るRbias電圧を受けるように構成され得る。

40

#### 【0066】

[0076]画素センサ800は、正の入力と、負の入力と、出力とを含むトランスインピーダンス増幅器(TIA)805を備える。TIA805は、出力と負の入力との間に結合されたフィードバックキャパシタCfbを更に備える。TIA805の正の入力は、基準DC電圧Vgを受けるように構成される。TIA805の負の入力は、入力メタライゼーションパッド810に結合される。画素センサ800がCMOS技術を使用して実施され得るため、TIA805は、接地基板上に形成され1つ又は複数のFETで実施され得る。そのため、入力メタライゼーション層810と接地基板との間に寄生容量Cpが存在し得る。

#### 【0067】

50

[0077] そのような構成では、TIA805は、超音波バーストが、圧盤846の上に配設されたイメージング対象アイテムに反射することに応答して、圧電層840で発生する電圧 $v_p$ に基づいて入力電流信号 $i_i$ を増幅するように構成される。TIA805が、非常に高い開ループゲイン $A_o$ （例えば、カスコード構成）を有すると仮定すると、負の入力における電圧 $V_{ig}$ は、TIAの正の入力における基準DC電圧 $V_g$ と略同じであり得る。そのため、TIA805は、実質的に以下の関係によって求められ得る閉ループゲイン $A_{cl}$ で入力電圧信号 $v_p$ を増幅するように構成される：

【数5】

$$A_{cl} = \frac{C_{in}}{C_{fb}}$$

10

ここで、 $C_{fb}$ は、フィードバックキャパシタ $C_{fb}$ の容量であり、 $C_{in}$ は、圧電層840のセンス容量である。

【0068】

[0078] 追加的に、画素センサ800は、TIA805の出力と負の入力との間に結合された制御可能スイッチCSAを備える。制御可能スイッチCSAは、前述したように、行セレクタ720で発生する制御信号CSA1～CSAMのうちの対応する1つによって制御されるように構成される。対応する制御信号は、前の動作周期から残っている可能性のある全ての電荷をフィードバック容量 $C_{fb}$ からクリアするために、特定の時間にスイッチCSAを開閉する。TIA805は、実質的に以下の式によって求められ得る、増幅された電圧信号 $v_s$ を発生させるように構成される：

20

【数6】

$$v_s = v_i * A_{cl} = v_i * \frac{C_{in}}{C_{fb}} = \frac{i_i}{C_{fb}}$$

TIA805が入力電流信号 $i_i$ を増幅するように構成されるため、TIA805で発生する電圧信号 $v_s$ が寄生容量 $C_p$ から実質的に独立しているであろうことは留意されるべきである。すなわち、換言すると、画素センサ800の感度は、寄生容量 $C_p$ の影響を大きく受けない。

【0069】

[0079] 画素センサ800は、TIA805の負の入力と、制御信号CSCのソース（例えば、行セレクタ720）との間に結合されたキャパシタ $C_d$ を更に備える。制御信号CSCは、行セレクタ720で発生する制御信号CSC1～CSCMのうちの対応する1つであり得る。信号CSCは、TIA805の出力において共通モード電圧（例えば、VD<sub>D/2</sub>）を設定するように構成される。追加的に、TIA805は、本明細書で更に述べるように、en\_amp信号を介してイネーブル及びディセーブルにされる。

30

【0070】

[0080] 画素センサ800の感度に対する寄生容量 $C_p$ の影響を更に最小化するために、TIA805は、1つ又は複数の小型デバイス又はFETを使用して実施され得る。しかしながら、前述したように、小型デバイスは、より多くの低周波数ノイズを発生させる。したがって、画素センサ800は、TIA805の出力において一次ノイズ成形又は低減を実行するための回路を更に備える。これに関連して、画素センサ800は、制御可能スイッチCSDと、キャパシタCsと、サンプル及びホールドキャパシタCh1及びCh2と、制御可能スイッチCSBとを更に備える。

40

【0071】

[0081] 制御可能スイッチCSDは、TIA805の出力とキャパシタCsの第1の端との間に結合される。キャパシタCsは、中間ノードn1に結合された第2の端を含む。キャパシタCh1は、キャパシタCsの第1の端と接地との間に結合される。キャパシタCh2は、中間ノードn1と接地との間に結合される。制御可能スイッチCSBは、中間ノードn1と、DB電圧のソース（例えば、行セレクタ720）との間に結合される。制御可能スイッチCSBは、前述したように、行セレクタ720で発生する制御信号DB1～DBMのうちの対応する1つによって制御されるように構成される。

50

## 【0072】

[0082] 画素センサ800は、p型MOSFET(「PMOS」)M2と、電流源807と、n型MOSFET(「NMOS」)M3とを含む出力回路を更に備える。PMOS M2は、NMOS M3のドレインに結合されたソースと、中間ノードn1に結合されたゲートと、接地に結合されたドレインとを含む(例えば、実質的に、ユニティゲインを有する)ソースフォロア增幅器として構成される。電流源807は、電圧レールVddとPMOS M2のソースとの間に結合される。NMOS M3は、次に、信号SSを受けるよう構成されたゲートと、対応する列読出しラインに結合されたソースとを含む。信号SSは、行セレクタ720で発生する信号SS1～SSMのうちの対応する1つであり得る。出力DC画素電圧Voutは、NMOS M3のソースにおいて生成される。

10

## 【0073】

[0083] 図8Bは、本開示の別の態様にかかる、画素センサ800の例示的な動作に関連付けられたタイミング図を例示する。タイミング図の水平軸すなわちx軸は時間を表し、垂直軸は、CSD、CSA、CSB、CSC、DB、超音波バースト、及びSSの状態又は振幅を表す。

## 【0074】

[0084] このタイミング図によれば、時間t1において、TIA805をイネーブルにするために、en\_amp信号がアサート状態に上げられる。時間t2において、スイッチCSD、CSA、CSBを閉じ、CSCを所定の電圧レベルに設定するために、CSD、CSA、CSB、及びCSCがアサート状態にされる。スイッチCSDを閉じることは、TIA805の出力をキャパシタCsに結合する。スイッチCSAを閉じることは、例えば、画素センサ800の前の動作周期から存在し得る全ての電荷をフィードバックキャパシタCfbからクリアする。スイッチCSBを閉じることは、中間ノードn1において発生した後続の信号に対して共通モード電圧を設定するために、DB電圧を中間ノードn1に印加するように構成される。そして、CSCを所定の電圧レベルに設定することは、TIA805の出力において共通モード電圧(例えば、Vdd/2)を設定するためである。時間t3において、CSC電圧は、その元のレベルに下げられる。

20

## 【0075】

[0085] 時間t4において、スイッチCSAが開けられる。スイッチCSAが開けられると、スイッチ及び低周波数ノイズvnが、TIA805の出力において生成され得る。キャパシタCsは、このキャパシタCsのハイパスフィルタ特性により、ノイズvnが中間ノードn1に行くことを防ぐ。これは、TIA805の出力において行われる一次ノイズ成形又は低減の一部である。一次ノイズ成形を達成するための所定の時間インターバルの後、時間t4において、スイッチCSBが開けられる。

30

## 【0076】

[0086] 時間t6において、受信圧電層840、電極842、及び圧盤846を通る超音波バーストを発生させるために、超音波送波器がイネーブルにされる。前述したように、超音波バーストは、ユーザの指に反射して、圧電層840に戻る。反射した超音波バーストに応答して、入力電流信号iiが発生する。入力電流信号iiは、超音波(例えば、10MHz)と略同じ周波数で周期し、対応する反射した超音波がユーザの指紋の山に当たったか谷に当たったかの関数として、すなわち、イメージング対象アイテムの関数として、振幅を有する。

40

## 【0077】

[0087] TIA805は、増幅された電圧信号vsを発生させるために、閉ループゲインAc1で入力電圧信号vpを増幅する。したがって、電圧信号vsの振幅はまた、反射した超音波に基づき、これは、次に、イメージング対象アイテム(例えば、ユーザの指紋)に基づく。電圧信号vsがまた、超音波(例えば、10MHz)と略同じ周波数で交流になるため、キャパシタCsは、TIA805の出力において低周波数ノイズvnを維持しつつ、電圧信号vsが中間ノードn1に通過することを可能にする。この場合もやはり、これは、TIA805の出力において行われる一次ノイズ成形又は低減の一部である。

50

## 【0078】

[0088] 時間  $t_7$ において、スイッチ C S D は、増幅された電圧信号  $v_s$  のピーク（又は、他の部分）と実質的に合致する時間に開けられる。キャパシタ C h 2 は、中間ノード n 1において電圧信号  $v_s$  のピーク値をサンプリング及びホールドする。したがって、D C 画素電圧は、中間ノード n 1において出現し、これは、電圧信号  $v_s$  のピークに実質的に基づく。故に、述べたように、電圧信号  $v_s$  の振幅又はピークがイメージング対象アイテムに基づくため、D C 画素電圧もまた、イメージング対象アイテムに基づく。時間  $t_8$ において、超音波バーストの発生を停止するために超音波送波器がディセーブルにされ、T I A 8 0 5 をディセーブルにするために e n \_ a m p 信号がデアサーント状態にされる。

## 【0079】

10

[0089] 時間  $t_9$ において、N M O S M 3 をオンにし、ソースフォロア P M O S M 2 を経由して対応する列読出しラインにD C 画素電圧 V o u t を出力するために、S S がアサートレベルに上げられる。列読出しマルチブレクサ 7 3 0 が出力D C 画素電圧 V o u t を読み出すのに十分な時間インターバルの後、時間  $t_{10}$ において、画素センサ 8 0 0 の動作周期を完了するために、S S がそのデアサーント状態に下げられる。

## 【0080】

20

[0090] 図 9 は、本開示の別の態様にかかる、D C 画素電圧を発生させる例示的な方法 9 0 0 のフロー図を例示する。方法 9 0 0 は、電圧信号を発生させるために入力信号を増幅することを備え、ここにおいて、入力信号は、超音波がイメージング対象アイテムに反射して、圧電層を介して伝播することに応答して発生する（ブロック 9 1 0）。方法 9 0 0 は、電圧信号からノイズを低減することを更に備える（ブロック 9 2 0）。そして、方法 9 0 0 は、低減ノイズ電圧信号に基づいてD C 画素電圧を発生させることを備える（ブロック 9 3 0）。

## 【0081】

30

[0091] 本開示の先の説明は、当業者による本開示の実行又は使用を可能にするために提供される。本開示に対する様々な修正は、当業者には容易に明らかとなり、本明細書で定義された包括的な原理は、本開示の精神又は範囲から逸脱せずに、他の変形に適用され得る。故に、本開示は、本明細書で説明された例に制限されるよう意図されるのではなく、本明細書で開示された原理及び新規な特徴に合致する最も広い範囲が与えられるべきである。

【図1】

【図2】

FIG. 2

【図3】

FIG. 3

【図4A】

FIG. 4A

【図 4 B】

【図 5】

【図 6】

【図 7】

【図 8 A】

【図 8B】

【図 9】

FIG. 9

## 【手続補正書】

【提出日】平成30年5月25日(2018.5.25)

## 【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

## 【補正の内容】

【特許請求の範囲】

## 【請求項1】

装置であって、

電圧信号を発生させるために入力信号を増幅するように構成された増幅器と、ここにおいて、前記入力信号は、超音波がイメージング対象アイテムに反射して、圧電層を介して伝播することに応答して発生する、

前記増幅器の出力からノードへの低周波数ノイズの伝播を低減しつつ、前記増幅器の前記出力から前記ノードに前記電圧信号を伝えるように構成されたノイズ低減回路と、ここでにおいて、前記低周波数ノイズは、前記電圧信号が周期する周波数より周波数が低い、

前記ノードにおける前記電圧信号に基づいてDC画素電圧を発生するように構成された回路と

を備える装置。

## 【請求項2】

前記ノイズ低減回路は、前記増幅器と前記ノードとの間に結合されたキャパシタを備える、請求項1に記載の装置。

## 【請求項3】

前記低周波数ノイズは、前記増幅器で発生する、請求項1に記載の装置。

## 【請求項4】

前記入力信号は、入力電流信号を備え、前記増幅器は、前記電圧信号を発生させるために前記入力電流信号のトランスインピーダンス増幅を実行するように構成されたトランスインピーダンス増幅器を備える、請求項1に記載の装置。

【請求項5】

前記トランスインピーダンス増幅に関連付けられたゲインは、前記圧電層のセンス容量に基づく、請求項4に記載の装置。

【請求項6】

前記トランスインピーダンス増幅に関連付けられたゲインは、前記増幅器の前記出力と入力との間に結合されたフィードバックキャパシタの容量に対する、前記圧電層のセンス容量の比に基づく、請求項4に記載の装置。

【請求項7】

前記増幅器は、ソースフォロア増幅器を備える、請求項1に記載の装置。

【請求項8】

前記回路は、前記電圧信号の1つ以上のピークに実質的に基づいて前記DC画素電圧を発生させるように構成されたピーク検出器を備える、請求項1に記載の装置。

【請求項9】

前記回路は、前記電圧信号のサンプリングされた部分に実質的に基づいて前記DC画素電圧を発生させるように構成されたサンプル及びホールド回路を備える、請求項1に記載の装置。

【請求項10】

前記DC画素電圧を選択的に出力するように構成された出力回路を更に備える、請求項1に記載の装置。

【請求項11】

前記増幅器は、

基準電圧を受けるように構成された第1の入力を含む演算増幅器と、

前記演算増幅器の出力と第2の入力との間に結合されたキャパシタと、

前記演算増幅器の前記出力と前記第2の入力との間に結合されたスイッチと

を備え、前記スイッチは、前記キャパシタを放電するために第1の時間インターバルの間閉じられるように構成され、前記スイッチは、第2の時間インターバルの間開けられるように構成され、前記演算増幅器が前記第2の時間インターバルにおいて前記電圧信号を発生させるように構成される、

請求項1に記載の装置。

【請求項12】

前記回路は、

共通モード電圧のソースと、

前記ノードと前記共通モード電圧の前記ソースとの間に結合されたダイオードと、

前記ノードと前記共通モード電圧の前記ソースとの間に結合されたスイッチと

を備え、前記スイッチは、前記ノードにおいて共通モード電圧を設定するため及び前記ダイオードによる前記電圧信号のピーク検出をディセーブルにするために第1の時間インターバルの間閉じられ、前記スイッチは、前記DC画素電圧を発生させるための、前記ダイオードによる前記電圧信号のピーク検出をイネーブルにするために第2の時間インターバルの間開けられる、

請求項1に記載の装置。

【請求項13】

前記増幅器は、

前記入力信号を受けるように構成されたゲートと、電圧レールに結合されたドレインと、

前記電圧信号を生成するように構成されたソースを含む電界効果トランジスタ(FET)と、

ゲートバイアス電圧のためのソースと、

前記FETの前記ゲートと前記ゲートバイアス電圧の前記ソースとの間に結合されたス

### イッチと

を備え、前記スイッチは、前記FETの前記ゲートから電荷を取り除き、前記FET上で前記ゲートバイアス電圧を生成するために第1の時間インターバルの間閉じられるように構成され、前記スイッチは、第2の時間インターバルの間開けられるように構成され、前記FETが前記第2の時間インターバルにおいて前記電圧信号を発生させるように構成される、

請求項1に記載の装置。

#### 【請求項14】

前記增幅器は、

基準電圧を受けるように構成された第1の入力を含む演算增幅器と、

前記演算增幅器の出力と第2の入力との間に結合された第1のキャパシタと、

前記演算增幅器の前記出力と前記第2の入力との間に結合されたスイッチと、ここにおいて、前記スイッチは、前記キャパシタを放電するために第1の時間インターバルの間閉じられるように構成され、前記スイッチは、第2の時間インターバルの間開けられるように構成され、前記演算增幅器が前記第2の時間インターバルにおいて前記電圧信号を発生させるように構成される、

制御信号のソースと、

前記演算增幅器の前記第2の入力と前記制御電圧の前記ソースとの間に結合された第2のキャパシタと

を備え、前記制御信号は、前記演算增幅器の前記出力において共通モード電圧を設定するために前記第1の時間インターバルの間所定の電圧レベルに設定される、

請求項1に記載の装置。

#### 【請求項15】

前記増幅器の前記出力と前記ノイズ低減回路との間に結合されたスイッチを更に備え、前記スイッチは、前記増幅器が前記電圧信号を発生させる第1の時間インターバルの間閉じられるように構成され、前記スイッチは、前記DC画素電圧を発生させるために、前記回路が前記電圧信号のピークを検出する第2の時間インターバルの間開けられるように構成される、請求項1に記載の装置。

#### 【請求項16】

方法であって、

電圧信号を発生させるために入力信号を増幅することと、ここにおいて、前記入力信号は、超音波がイメージング対象アイテムに反射して、圧電層を介して伝播することに応答して発生する、

前記電圧信号から低周波数ノイズを低減することと、ここにおいて、前記低周波数ノイズは、前記電圧信号が周期する周波数より周波数が低い、

前記低減ノイズ電圧信号に基づいてDC画素電圧を発生させることとを備える方法。

#### 【請求項17】

前記電圧信号から前記ノイズを低減することは、キャパシタを通じて前記電圧信号を伝えることを備える、請求項16に記載の方法。

#### 【請求項18】

前記低周波数ノイズは、前記入力信号の前記増幅に関する1つ以上のデバイスで発生する、請求項16に記載の方法。

#### 【請求項19】

前記入力信号は、入力電流信号を備え、前記入力信号を増幅することは、前記電圧信号を発生させるために前記入力電流信号のトランスインピーダンス増幅を実行することを備える、請求項16に記載の方法。

#### 【請求項20】

前記トランスインピーダンス増幅に関連付けられたゲインは、前記圧電層のセンス容量に基づく、請求項19に記載の方法。

**【請求項 2 1】**

前記トランスインピーダンス増幅に関連付けられたゲインは、前記トランスインピーダンス増幅に関連付けられたフィードバックキャパシタの容量に対する、前記圧電層のセンス容量の比に基づく、請求項1\_9に記載の方法。

**【請求項 2 2】**

前記入力信号を増幅することは、ソースフォロア増幅器を使用して前記入力信号を増幅することを備える、請求項1\_6に記載の方法。

**【請求項 2 3】**

前記DC画素電圧を発生させることは、前記DC画素電圧を発生させるために前記電圧信号の1つ以上のピークを検出することを備える、請求項1\_6に記載の方法。

**【請求項 2 4】**

前記DC画素電圧を発生させることは、前記DC画素電圧を発生させるために前記電圧信号の一部をサンプリング及びホールドすることを備える、請求項1\_6に記載の方法。

**【請求項 2 5】**

前記DC画素電圧を選択的に出力することを更に備える、請求項1\_6に記載の方法。

**【請求項 2 6】**

装置であって、

電圧信号を発生させるために入力信号を増幅するための手段と、ここにおいて、前記入力信号は、超音波がイメージング対象アイテムに反射して、圧電層を介して伝播することに応答して発生する、

前記電圧信号から低周波数ノイズを低減するための手段と、ここにおいて、前記低周波数ノイズは、前記電圧信号が周期する周波数より周波数が低い、

前記低減ノイズ電圧信号に基づいてDC画素電圧を発生させるための手段とを備える装置。

**【請求項 2 7】**

前記電圧信号から前記ノイズを前記低減するための手段は、キャパシタを通じて前記電圧信号を伝えるための手段を備える、請求項2\_6に記載の装置。

**【請求項 2 8】**

前記ノイズは、前記増幅するための手段で発生する低周波数ノイズを備える、請求項2\_6に記載の装置。

**【請求項 2 9】**

前記入力信号は、入力電流信号を備え、前記入力信号を前記増幅するための手段は、前記電圧信号を発生させるために前記入力電流信号のトランスインピーダンス増幅を実行するための手段を備える、請求項2\_6に記載の装置。

**【請求項 3 0】**

前記トランスインピーダンス増幅に関連付けられたゲインは、前記圧電層のセンス容量に基づく、請求項2\_9に記載の装置。

**【請求項 3 1】**

前記トランスインピーダンス増幅に関連付けられたゲインは、前記増幅するための手段の出力と入力との結合されたフィードバックキャパシタの容量に対する、前記圧電層のセンス容量の比に基づく、請求項2\_9に記載の装置。

**【請求項 3 2】**

前記入力信号を前記増幅するための手段は、ソースフォロア増幅器を備える、請求項2\_6に記載の装置。

**【請求項 3 3】**

前記DC画素電圧を前記発生させるための手段は、前記DC画素電圧を発生させるために前記電圧信号の1つ以上のピークを検出するための手段を備える、請求項2\_6に記載の装置。

**【請求項 3 4】**

前記DC画素電圧を前記発生させるための手段は、前記DC画素電圧を発生させるため

に前記電圧信号の一部をサンプリング及びホールドするための手段を備える、請求項2\_6に記載の装置。

【請求項3\_5】

前記DC画素電圧を選択的に出力するための手段を更に備える、請求項2\_6に記載の装置。

【手続補正2】

【補正対象書類名】明細書

【補正対象項目名】0\_0\_8\_1

【補正方法】変更

【補正の内容】

【0\_0\_8\_1】

[0091]本開示の先の説明は、当業者による本開示の実行又は使用を可能にするために提供される。本開示に対する様々な修正は、当業者には容易に明らかとなり、本明細書で定義された包括的な原理は、本開示の精神又は範囲から逸脱せずに、他の変形に適用され得る。故に、本開示は、本明細書で説明された例に制限されるよう意図されるのではなく、本明細書で開示された原理及び新規な特徴に合致する最も広い範囲が与えられるべきである。

以下に本願発明の当初の特許請求の範囲に記載された発明を付記する。

[C\_1]

装置であつて、

電圧信号を発生させるために入力信号を増幅するように構成された増幅器と、ここにおいて、前記入力信号は、超音波がイメージング対象アイテムに反射して、圧電層を介して伝播することに応答して発生する、

前記増幅器の出力からノードへのノイズの伝播を低減しつつ、前記増幅器の前記出力から前記ノードに前記電圧信号を伝えるように構成されたノイズ低減回路と、

前記ノードにおける前記電圧信号に基づいてDC画素電圧を発生させるように構成された回路と

を備える装置。

[C\_2]

前記ノイズ低減回路は、前記増幅器と前記ノードとの間に結合されたキャパシタを備える、C\_1に記載の装置。

[C\_3]

前記ノイズは、前記増幅器で発生する低周波数ノイズを備える、C\_1に記載の装置。

[C\_4]

前記入力信号は、入力電流信号を備え、前記増幅器は、前記電圧信号を発生させるために前記入力電流信号のトランスインピーダンス増幅を実行するように構成されたトランスインピーダンス増幅器を備える、C\_1に記載の装置。

[C\_5]

前記トランスインピーダンス増幅に関連付けられたゲインは、前記圧電層のセンス容量に基づく、C\_4に記載の装置。

[C\_6]

前記トランスインピーダンス増幅に関連付けられたゲインは、前記圧電層のセンス容量に対する、前記増幅器の前記出力と入力との間に結合されたフィードバックキャパシタの容量の比に基づく、C\_4に記載の装置。

[C\_7]

前記増幅器は、ソースフォロア増幅器を備える、C\_1に記載の装置。

[C\_8]

前記回路は、前記電圧信号の1つ以上のピークに実質的にに基づいて前記DC画素電圧を発生させるように構成されたピーク検出器を備える、C\_1に記載の装置。

[C\_9]

前記回路は、前記電圧信号のサンプリングされた部分に実質的に基づいて前記DC画素電圧を発生させるように構成されたサンプル及びホールド回路を備える、C1に記載の装置。

[ C 1 0 ]

前記DC画素電圧を選択的に出力するように構成された出力回路を更に備える、C1に記載の装置。

[ C 1 1 ]

方法であつて、

電圧信号を発生させるために入力信号を増幅することと、ここにおいて、前記入力信号は、超音波がイメージング対象アイテムに反射して、圧電層を介して伝播することに応答して発生する、

前記電圧信号からノイズを低減することと、

前記低減ノイズ電圧信号に基づいてDC画素電圧を発生させることとを備える方法。

[ C 1 2 ]

前記電圧信号から前記ノイズを低減することは、キャパシタを通じて前記電圧信号を伝えることを備える、C11に記載の方法。

[ C 1 3 ]

前記ノイズは、前記入力信号の前記増幅に関する1つ以上のデバイスで発生する低周波数ノイズを備える、C11に記載の方法。

[ C 1 4 ]

前記入力信号は、入力電流信号を備え、前記入力信号を増幅することは、前記電圧信号を発生させるために前記入力電流信号のトランスインピーダンス増幅を実行することを備える、C11に記載の方法。

[ C 1 5 ]

前記トランスインピーダンス増幅に関連付けられたゲインは、前記圧電層のセンス容量に基づく、C14に記載の方法。

[ C 1 6 ]

前記トランスインピーダンス増幅に関連付けられたゲインは、前記圧電層のセンス容量に対する、前記トランスインピーダンス増幅に関連付けられたフィードバックキャパシタの容量の比に基づく、C14に記載の方法。

[ C 1 7 ]

前記入力信号を増幅することは、ソースフォロア増幅器を使用して前記入力信号を増幅することを備える、C11に記載の方法。

[ C 1 8 ]

前記DC画素電圧を発生させることは、前記DC画素電圧を発生させるために前記電圧信号の1つ以上のピークを検出することを備える、C11に記載の方法。

[ C 1 9 ]

前記DC画素電圧を発生させることは、前記DC画素電圧を発生させるために前記電圧信号の一部をサンプリング及びホールドすることを備える、C11に記載の方法。

[ C 2 0 ]

前記DC画素電圧を選択的に出力を更に備える、C11に記載の方法。

[ C 2 1 ]

装置であつて、

電圧信号を発生させるために入力信号を増幅するための手段と、ここにおいて、前記入力信号は、超音波がイメージング対象アイテムに反射して、圧電層を介して伝播することに応答して発生する、

前記電圧信号からノイズを低減するための手段と、

前記低減ノイズ電圧信号に基づいてDC画素電圧を発生させるための手段とを備える装置。

[ C 2 2 ]

前記電圧信号から前記ノイズを前記低減するための手段は、キャパシタを通って前記電圧信号を伝えるための手段を備える、C 2 1に記載の装置。

[ C 2 3 ]

前記ノイズは、前記増幅するための手段で発生する低周波数ノイズを備える、C 2 1に記載の装置。

[ C 2 4 ]

前記入力信号は、入力電流信号を備え、前記入力信号を前記増幅するための手段は、前記電圧信号を発生させるために前記入力電流信号のトランスインピーダンス増幅を実行するための手段を備える、C 2 1に記載の装置。

[ C 2 5 ]

前記トランスインピーダンス増幅に関連付けられたゲインは、前記圧電層のセンス容量に基づく、C 2 4に記載の装置。

[ C 2 6 ]

前記トランスインピーダンス増幅に関連付けられたゲインは、前記圧電層のセンス容量に対する、前記増幅するための手段の出力と入力とのに結合されたフィードバックキャパシタの容量の比に基づく、C 2 4に記載の装置。

[ C 2 7 ]

前記入力信号を前記増幅するための手段は、ソースフォロア増幅器を備える、C 2 1に記載の装置。

[ C 2 8 ]

前記DC画素電圧を前記発生させるための手段は、前記DC画素電圧を発生させるために前記電圧信号の1つ以上のピークを検出するための手段を備える、C 2 1に記載の装置。

[ C 2 9 ]

前記DC画素電圧を前記発生させるための手段は、前記DC画素電圧を発生させるために前記電圧信号の一部をサンプリング及びホールドするための手段を備える、C 2 1に記載の装置。

[ C 3 0 ]

前記DC画素電圧を選択的に出力するための手段を更に備える、C 2 1に記載の装置。

## 【手続補正書】

【提出日】平成30年5月28日(2018.5.28)

## 【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

## 【補正の内容】

【特許請求の範囲】

## 【請求項1】

装置であって、

電圧信号を発生させるために入力信号を増幅するように構成された増幅器と、ここにおいて、前記入力信号は、超音波がイメージング対象アイテムに反射して、圧電層を介して伝播することに応答して発生する、

前記増幅器の出力からノードへの低周波数ノイズの伝播を低減しつつ、前記増幅器の前記出力から前記ノードに前記電圧信号を伝えるように構成された、ハイパスフィルタ特性を有するノイズ低減回路と、ここにおいて、前記低周波数ノイズは、前記電圧信号が周期する周波数より周波数が低い、

前記ノードにおける前記電圧信号に基づいてDC画素電圧を発生させるように構成された回路と

を備える装置。

**【請求項 2】**

前記ノイズ低減回路は、前記増幅器と前記ノードとの間に結合されたキャパシタを備える、請求項1に記載の装置。

**【請求項 3】**

前記低周波数ノイズは、前記増幅器で発生する、請求項1に記載の装置。

**【請求項 4】**

前記入力信号は、入力電流信号を備え、前記増幅器は、前記電圧信号を発生させるために前記入力電流信号のトランスインピーダンス増幅を実行するように構成されたトランスインピーダンス増幅器を備える、請求項1に記載の装置。

**【請求項 5】**

前記トランスインピーダンス増幅に関連付けられたゲインは、前記圧電層のセンス容量に基づく、請求項4に記載の装置。

**【請求項 6】**

前記トランスインピーダンス増幅に関連付けられたゲインは、前記増幅器の前記出力と入力との間に結合されたフィードバックキャパシタの容量に対する、前記圧電層のセンス容量の比に基づく、請求項4に記載の装置。

**【請求項 7】**

前記増幅器は、ソースフォロア増幅器を備える、請求項1に記載の装置。

**【請求項 8】**

前記回路は、前記電圧信号の1つ以上のピークに実質的に基づいて前記DC画素電圧を発生させるように構成されたピーク検出器を備える、請求項1に記載の装置。

**【請求項 9】**

前記回路は、前記電圧信号のサンプリングされた部分に実質的に基づいて前記DC画素電圧を発生させるように構成されたサンプル及びホールド回路を備える、請求項1に記載の装置。

**【請求項 10】**

前記DC画素電圧を選択的に出力するように構成された出力回路を更に備える、請求項1に記載の装置。

**【請求項 11】**

前記増幅器は、

基準電圧を受けるように構成された第1の入力を含む演算増幅器と、

前記演算増幅器の出力と第2の入力との間に結合されたキャパシタと、

前記演算増幅器の前記出力と前記第2の入力との間に結合されたスイッチと

を備え、前記スイッチは、前記キャパシタを放電するために第1の時間インターバルの間閉じられるように構成され、前記スイッチは、前記演算増幅器が前記電圧信号を発生させるように構成された第2の時間インターバルの間開けられるように構成される、

請求項1に記載の装置。

**【請求項 12】**

前記回路は、

共通モード電圧のソースと、

前記ノードと前記共通モード電圧の前記ソースとの間に結合されたダイオードと、

前記ノードと前記共通モード電圧の前記ソースとの間に結合されたスイッチと

を備え、前記スイッチは、前記ノードにおいて共通モード電圧を設定するため及び前記ダイオードによる前記電圧信号のピーク検出をディセーブルにするために第1の時間インターバルの間閉じられ、前記スイッチは、前記DC画素電圧を発生させるための、前記ダイオードによる前記電圧信号のピーク検出をイネーブルにするために第2の時間インターバルの間開けられる、

請求項1に記載の装置。

**【請求項 13】**

前記増幅器は、

前記入力信号を受けるように構成されたゲートと、電圧レールに結合されたドレインと、前記電圧信号を生成するように構成されたソースを含む電界効果トランジスタ(FET)と、

ゲートバイアス電圧のためのソースと、

前記FETの前記ゲートと前記ゲートバイアス電圧の前記ソースとの間に結合されたスイッチと

を備え、前記スイッチは、前記FETの前記ゲートから電荷を取り除き、前記FET上で前記ゲートバイアス電圧を生成するために第1の時間インターバルの間閉じられるよう構成され、前記スイッチは、第2の時間インターバルの間開けられるように構成され、前記FETが前記第2の時間インターバルにおいて前記電圧信号を発生させるように構成される、

請求項1に記載の装置。

#### 【請求項14】

前記增幅器は、

基準電圧を受けるように構成された第1の入力を含む演算增幅器と、

前記演算增幅器の出力と第2の入力との間に結合された第1のキャパシタと、

前記演算增幅器の前記出力と前記第2の入力との間に結合されたスイッチと、ここにおいて、前記スイッチは、前記キャパシタを放電するために第1の時間インターバルの間閉じられるよう構成され、前記スイッチは、第2の時間インターバルの間開けられるように構成され、前記演算增幅器が前記第2の時間インターバルにおいて前記電圧信号を発生させるように構成される、

制御信号のソースと、

前記演算增幅器の前記第2の入力と前記制御電圧の前記ソースとの間に結合された第2のキャパシタと

を備え、前記制御信号は、前記演算增幅器の前記出力において共通モード電圧を設定するために前記第1の時間インターバルの間所定の電圧レベルに設定される、

請求項1に記載の装置。

#### 【請求項15】

前記增幅器の前記出力と前記ノイズ低減回路との間に結合されたスイッチを更に備え、前記スイッチは、前記増幅器が前記電圧信号を発生させる第1の時間インターバルの間閉じられるよう構成され、前記スイッチは、前記DC画素電圧を発生させるために、前記回路が前記電圧信号のピークを検出する第2の時間インターバルの間開けられるよう構成される、請求項1に記載の装置。

#### 【請求項16】

方法であつて、

電圧信号を発生させるために入力信号を増幅することと、ここにおいて、前記入力信号は、超音波がイメージング対象アイテムに反射して、圧電層を介して伝播することに応答して発生する、

前記電圧信号をハイパスフィルタ処理することで前記電圧信号から低周波数ノイズを低減することと、ここにおいて、前記低周波数ノイズは、前記電圧信号が周期する周波数より周波数が低い、

前記低減ノイズ電圧信号に基づいてDC画素電圧を発生させることと

を備える方法。

#### 【請求項17】

前記電圧信号から前記ノイズを低減することは、キャパシタを通じて前記電圧信号を伝えることを備える、請求項16に記載の方法。

#### 【請求項18】

前記低周波数ノイズは、前記入力信号の前記増幅に関与する1つ以上のデバイスで発生する、請求項16に記載の方法。

#### 【請求項19】

前記入力信号は、入力電流信号を備え、前記入力信号を増幅することは、前記電圧信号を発生させるために前記入力電流信号のトランスインピーダンス増幅を実行することを備える、請求項16に記載の方法。

【請求項20】

前記トランスインピーダンス増幅に関連付けられたゲインは、前記圧電層のセンス容量に基づく、請求項19に記載の方法。

【請求項21】

前記トランスインピーダンス増幅に関連付けられたゲインは、前記トランスインピーダンス増幅に関連付けられたフィードバックキャパシタの容量に対する、前記圧電層のセンス容量の比に基づく、請求項19に記載の方法。

【請求項22】

前記入力信号を増幅することは、ソースフォロア増幅器を使用して前記入力信号を増幅することを備える、請求項16に記載の方法。

【請求項23】

前記DC画素電圧を発生させることは、前記DC画素電圧を発生させるために前記電圧信号の1つ以上のピークを検出することを備える、請求項16に記載の方法。

【請求項24】

前記DC画素電圧を発生させることは、前記DC画素電圧を発生させるために前記電圧信号の一部をサンプリング及びホールドすることを備える、請求項16に記載の方法。

【請求項25】

前記DC画素電圧を選択的に出力することを更に備える、請求項16に記載の方法。

【請求項26】

装置であって、

電圧信号を発生させるために入力信号を増幅するための手段と、ここにおいて、前記入力信号は、超音波がイメージング対象アイテムに反射して、圧電層を介して伝播することに応答して発生する、

前記電圧信号をハイパスフィルタ処理することで前記電圧信号から低周波数ノイズを低減するための手段と、ここにおいて、前記低周波数ノイズは、前記電圧信号が周期する周波数より周波数が低い、

前記低減ノイズ電圧信号に基づいてDC画素電圧を発生させるための手段とを備える装置。

【請求項27】

前記電圧信号から前記ノイズを前記低減するための手段は、キャパシタを通じて前記電圧信号を伝えるための手段を備える、請求項26に記載の装置。

【請求項28】

前記ノイズは、前記増幅するための手段で発生する低周波数ノイズを備える、請求項26に記載の装置。

【請求項29】

前記入力信号は、入力電流信号を備え、前記入力信号を前記増幅するための手段は、前記電圧信号を発生させるために前記入力電流信号のトランスインピーダンス増幅を実行するための手段を備える、請求項26に記載の装置。

【請求項30】

前記トランスインピーダンス増幅に関連付けられたゲインは、前記圧電層のセンス容量に基づく、請求項29に記載の装置。

【請求項31】

前記トランスインピーダンス増幅に関連付けられたゲインは、前記増幅するための手段の出力と入力との結合されたフィードバックキャパシタの容量に対する、前記圧電層のセンス容量の比に基づく、請求項29に記載の装置。

【請求項32】

前記入力信号を前記増幅するための手段は、ソースフォロア増幅器を備える、請求項2

6に記載の装置。

【請求項33】

前記DC画素電圧を前記発生させるための手段は、前記DC画素電圧を発生させるために前記電圧信号の1つ以上のピークを検出するための手段を備える、請求項26に記載の装置。

【請求項34】

前記DC画素電圧を前記発生させるための手段は、前記DC画素電圧を発生させるために前記電圧信号の一部をサンプリング及びホールドするための手段を備える、請求項26に記載の装置。

【請求項35】

前記DC画素電圧を選択的に出力するための手段を更に備える、請求項26に記載の装置。

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | International application No<br>PCT/US2016/050435            |           |                                                                                    |                       |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |   |  |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-----------|------------------------------------------------------------------------------------|-----------------------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---|--|------|

| <b>A. CLASSIFICATION OF SUBJECT MATTER</b><br>INV. G06K9/00<br>ADD.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                              |           |                                                                                    |                       |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |   |  |      |

| According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                              |           |                                                                                    |                       |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |   |  |      |

| <b>B. FIELDS SEARCHED</b><br>Minimum documentation searched (classification system followed by classification symbols)<br>G06K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                              |           |                                                                                    |                       |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |   |  |      |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                              |           |                                                                                    |                       |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |   |  |      |

| Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)<br><br>EPO-Internal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                              |           |                                                                                    |                       |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |   |  |      |

| <b>C. DOCUMENTS CONSIDERED TO BE RELEVANT</b> <table border="1" style="width: 100%; border-collapse: collapse;"> <thead> <tr> <th style="text-align: left; padding: 2px;">Category*</th> <th style="text-align: left; padding: 2px;">Citation of document, with indication, where appropriate, of the relevant passages</th> <th style="text-align: left; padding: 2px;">Relevant to claim No.</th> </tr> </thead> <tbody> <tr> <td style="padding: 2px;">Y</td> <td style="padding: 2px;">US 2015/123931 A1 (KITCHENS JACK C [US] ET AL) 7 May 2015 (2015-05-07) paragraphs [0040] - [0043], [0064] - [0065]; figures 1c,6<br/>-----<br/>Kumen Blake ET AL: "Amplifying High-Impedance Sensors - Photodiode Example Step 2: Stability Compensation", Microchip Technology Inc, 1 January 2004 (2004-01-01), XP055320808, Retrieved from the Internet:<br/>URL:<a href="http://ww1.microchip.com/downloads/en/AppNotes/00951a.pdf">http://ww1.microchip.com/downloads/en/AppNotes/00951a.pdf</a> [retrieved on 2016-11-18]<br/>abstract<br/>-----<br/>-/-</td> <td style="padding: 2px;">1-30</td> </tr> <tr> <td style="padding: 2px;">Y</td> <td style="padding: 2px;"></td> <td style="padding: 2px;">1-30</td> </tr> </tbody> </table> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                              | Category* | Citation of document, with indication, where appropriate, of the relevant passages | Relevant to claim No. | Y | US 2015/123931 A1 (KITCHENS JACK C [US] ET AL) 7 May 2015 (2015-05-07) paragraphs [0040] - [0043], [0064] - [0065]; figures 1c,6<br>-----<br>Kumen Blake ET AL: "Amplifying High-Impedance Sensors - Photodiode Example Step 2: Stability Compensation", Microchip Technology Inc, 1 January 2004 (2004-01-01), XP055320808, Retrieved from the Internet:<br>URL: <a href="http://ww1.microchip.com/downloads/en/AppNotes/00951a.pdf">http://ww1.microchip.com/downloads/en/AppNotes/00951a.pdf</a> [retrieved on 2016-11-18]<br>abstract<br>-----<br>-/- | 1-30 | Y |  | 1-30 |

| Category*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Relevant to claim No.                                        |           |                                                                                    |                       |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |   |  |      |

| Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | US 2015/123931 A1 (KITCHENS JACK C [US] ET AL) 7 May 2015 (2015-05-07) paragraphs [0040] - [0043], [0064] - [0065]; figures 1c,6<br>-----<br>Kumen Blake ET AL: "Amplifying High-Impedance Sensors - Photodiode Example Step 2: Stability Compensation", Microchip Technology Inc, 1 January 2004 (2004-01-01), XP055320808, Retrieved from the Internet:<br>URL: <a href="http://ww1.microchip.com/downloads/en/AppNotes/00951a.pdf">http://ww1.microchip.com/downloads/en/AppNotes/00951a.pdf</a> [retrieved on 2016-11-18]<br>abstract<br>-----<br>-/- | 1-30                                                         |           |                                                                                    |                       |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |   |  |      |

| Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1-30                                                         |           |                                                                                    |                       |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |   |  |      |

| <input checked="" type="checkbox"/> Further documents are listed in the continuation of Box C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <input checked="" type="checkbox"/> See patent family annex. |           |                                                                                    |                       |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |   |  |      |

| * Special categories of cited documents :<br>"A" document defining the general state of the art which is not considered to be of particular relevance<br>"E" earlier application or patent but published on or after the international filing date<br>"L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)<br>"O" document referring to an oral disclosure, use, exhibition or other means<br>"P" document published prior to the international filing date but later than the priority date claimed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                              |           |                                                                                    |                       |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |   |  |      |

| *T* later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention<br>*X* document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone<br>*Y* document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art<br>"&" document member of the same patent family                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                              |           |                                                                                    |                       |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |   |  |      |