(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2015-0080098

(43) 공개일자 2015년07월09일

(51) 국제특허분류(Int. Cl.)

*G11C 5/06* (2006.01)

(21) 출원번호 10-2013-0167019

(22) 출원일자 2013년12월30일

심사청구일자 없음

(71) 출원인

에스케이하이닉스 주식회사

경기도 이천시 부발읍 경충대로 2091

(72) 발명자

허은호

경기도 이천시 부발읍 아미1리 704동 1001호

(74) 대리인

김성남

전체 청구항 수 : 총 8 항

(54) 발명의 명칭 반도체 장치

### (57) 요 약

본 기술에 따른 반도체 장치는 복수 개의 인버터가 직렬 연결되는 인버터 체인을 포함하고, 상기 복수 개의 인버터들 중 적어도 하나는 복수 개의 출력노드를 포함할 수 있다.

대 표 도 - 도4

## 명세서

### 청구범위

#### 청구항 1

복수 개의 인버터가 직렬 연결되는 인버터 체인을 포함하는 반도체 장치에 있어서,

상기 복수 개의 인버터들 중 적어도 하나는 복수 개의 출력노드를 포함하는 것을 특징으로 하는 반도체 장치.

#### 청구항 2

제 1항에 있어서,

상기 복수 개의 출력노드는, 상기 복수 개의 인버터 중 어느 하나의 인버터와 상기 어느 하나의 인버터와 후속 연결되는 인버터를 연결하는 복수 개의 연결배선을 통해 형성되는 것을 특징으로 하는 반도체 장치.

#### 청구항 3

제2항에 있어서,

상기 각 인버터는 PMOS 트랜지스터와, NMOS 트랜지스터를 포함하고,

상기 복수 개의 연결배선은, 상기 어느 하나의 인버터의 각 트랜지스터의 드레인을 연결하는 드레인 배선과, 상기 후속 연결되는 인버터의 각 트랜지스터의 게이트를 연결하는 게이트 배선을 연결하는 것을 특징으로 하는 반도체 장치.

#### 청구항 4

제3항에 있어서,

상기 복수 개의 연결배선은, 상기 드레인 배선 상에서 상기 드레인 배선의 중심을 기준으로 상기 PMOS 트랜지스터에 근접한 위치에 배치되는 제1연결배선과, 상기 드레인 배선 상에서 상기 드레인 배선의 중심을 기준으로 상기 NMOS 트랜지스터에 근접한 위치에 배치되는 제2연결배선을 포함하는 것을 특징으로 하는 반도체 장치.

#### 청구항 5

제1항에 있어서,

상기 인버터 체인은 오실레이터인 것을 특징으로 하는 반도체 장치.

#### 청구항 6

복수 개의 인버터가 직렬 연결되는 인버터 체인을 포함하는 반도체 장치에 있어서,

상기 복수 개의 인버터 중 마지막 인버터를 제외한 각 인버터는 복수 개의 출력노드를 포함하고,

상기 복수 개의 인버터 중 두번째 이후의 각 인버터는 복수 개의 입력노드를 포함하는 것을 특징으로 하는 반도체 장치.

#### 청구항 7

제6항에 있어서,

인접하는 인버터 간의 출력노드와 입력노드를 각각 연결하는 복수 개의 연결배선을 더 포함하는 것을 특징으로 하는 반도체 장치.

#### 청구항 8

제7항에 있어서,

상기 연결배선은 상기 각 인버터의 라이징 신호를 전달하는 제1연결배선과, 상기 각 인버터의 폴링 신호를 전달

하는 제2연결배선을 포함하는 것을 특징으로 하는 반도체 장치.

### 발명의 설명

#### 기술 분야

[0001] 본 발명은 반도체 장치에 관한 것으로, 더욱 상세하게는 라이징 타임과 폴링 타임을 개선할 수 있는 인버터 체인을 포함하는 반도체 장치에 관한 것이다.

#### 배경기술

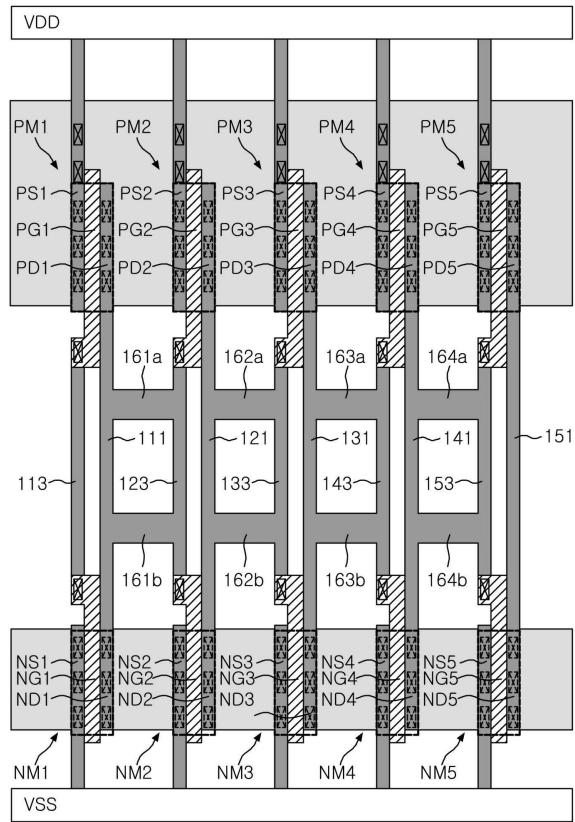

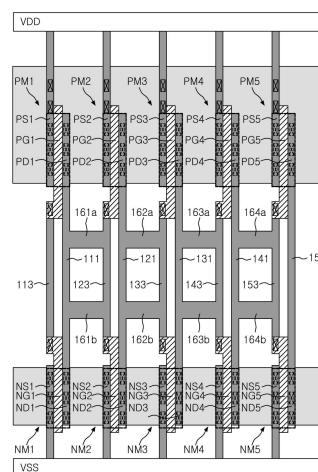

[0002] 도 1 및 도 2를 참조하면, 종래의 인버터 체인(10)은 복수 개의 인버터(11, 12, 13, 14, 15)로 구성될 수 있다.

[0003] 상기의 인버터 체인(10)의 각 인버터의 출력단은 도시된 바와 같이 다음으로 연결되는 인버터의 입력단과 연결된다. 예를 들면, 제1인버터(11)의 출력단은 제2인버터(12)의 입력단과 연결된다. 이때, 제1,2인버터(11, 12)의 연결은 제1인버터(11)의 출력단의 중간에서 제2인버터(12)의 입력단과 단 한번만 연결된다.

[0004] 부연하면, 각 인버터(11, 12, 13, 14, 15)의 출력단은 인터버를 구성하는 PMOS 트랜지스터의 드레인단자(PD)과 NMOS 트랜지스터의 드레인단자(ND)을 연결하는 배선(20)의 중간의 위치에 배치된다. 그리고 각 인버터(11, 12, 13, 14, 15)의 입력단은 PMOS 트랜지스터의 게이트단자(PG)와 NMOS 트랜지스터의 게이트단자(NG)를 연결하는 배선(30)의 중간의 위치에 배치된다.

[0005] 이로 인해 종래에는 상술한 바와 같이 어느 하나의 인버터의 출력단 중간에서 다음 인버터의 입력단과 연결되는 패스(Path)를 가짐에 따라, 각 인버터의 라이징(Rising) 또는 폴링(Falling) 동작 시 라이징 타임(Rising time) 및 폴링 타임(Falling time)에서 손해를 보게 된다.

#### 발명의 내용

##### 해결하려는 과제

[0006] 본 발명의 실시예는 복수 개의 인버터가 직렬 연결되는 인버터 체인에서 라이징 타임 및 폴링 타임을 개선할 수 있는 반도체 장치를 제공한다.

##### 과제의 해결 수단

[0007] 본 발명의 실시예에 따른 반도체 장치는 복수 개의 인버터가 직렬 연결되는 인버터 체인을 포함하고, 상기 복수 개의 인버터들 중 적어도 하나는 복수 개의 출력노드를 포함할 수 있다.

#### 발명의 효과

[0008] 본 기술에 의하면, 전류 패스 거리가 짧은 라이징 패스와 폴링 패스를 가짐에 따라 인버터 체인의 라이징 타임 및 폴링 타임의 효율을 높일 수 있다.

#### 도면의 간단한 설명

[0009] 도 1은 종래의 인버터 체인의 회로도이다.

도 2는 도 1에 도시된 인버터 체인의 레이아웃도이다.

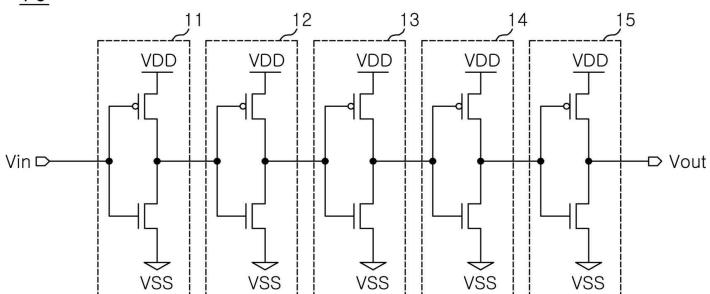

도 3은 본 발명의 실시예에 따른 인버터 체인의 회로도이다.

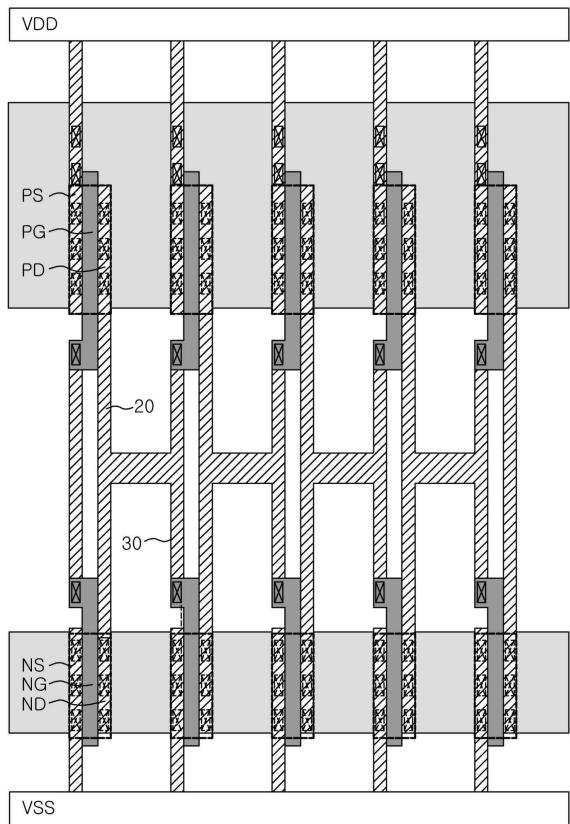

도 4는 도 3에 도시된 인버터 체인의 레이아웃도이다.

#### 발명을 실시하기 위한 구체적인 내용

[0010] 이하, 첨부한 도면을 참조하여 본 발명의 바람직한 실시예를 설명하기로 한다. 그러나, 본 발명은 여기서 설명되는 실시예들에 한정되지 않고 다른 형태로 구체화될 수도 있다. 그리고 본 발명의 요지와 무관한 공지의 구성은 생략될 수 있다. 각 도면의 구성요소들에 참조 번호를 부가함에 있어서, 동일한 구성 요소들에 대해서는 비록 다른 도면상에 표시되더라도 가능한 한 동일한 번호를 가지도록 하고 있음에 유의하여야 한다.

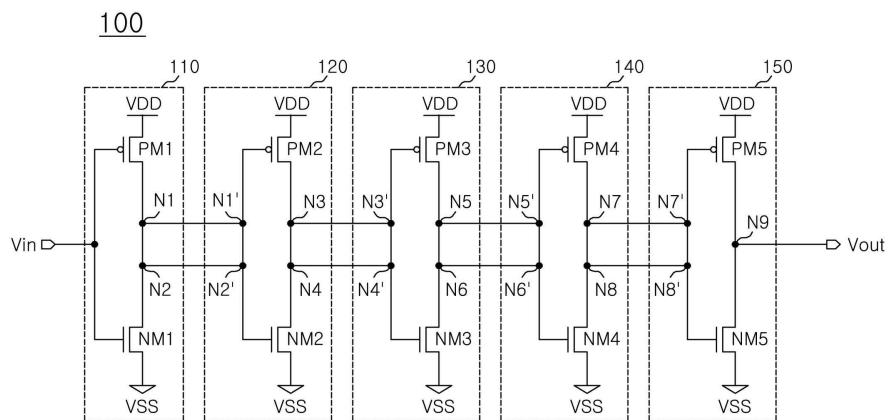

[0011] 도 3 및 도 4를 참조하면, 인버터 체인(100)은 상호 직렬 연결되는 복수 개의 인버터로 구성되는데, 본 발명의

실시예에서는 도시된 바와 같이 다섯 개의 인버터(110, 120, 130, 140, 150)로 구성될 수 있다. 예를 들면, 인버터 체인(100)은 복수 개의 인버터가 직렬 연결되는 오실레이터일 수 있다.

[0012] 구체적으로, 제1인버터(110)는 입력단(Vin)과 연결되는 게이트단자(PG1)와, 전원 전압단(VDD)에 연결되는 소스 단자(PS1) 및 제1출력노드(N1)에 연결되는 드레인단자(PD1)를 갖는 제1PMOS 트랜지스터(PM1)와, 입력단(Vin)과 연결된 게이트단자(NG1)와, 접지 전압단(VSS)에 연결되는 소스단자(NS1) 및 제2출력노드(N2)와 연결되는 드레인 단자(ND1)를 갖는 제1NMOS 트랜지스터(NM1)를 포함한다.

[0013] 제2인버터(120)는 제1입력노드(N1')와 연결되는 게이트단자(PG2)와, 전원 전압단(VDD)과 연결되는 소스단자 (PS2) 및 제3출력노드(N3)에 연결되는 드레인단자(PD2)를 갖는 제2PMOS 트랜지스터(PM2)와, 제2입력노드(N2')와 연결되는 게이트단자(NG2)와, 접지 전압단(VSS)에 연결되는 소스단자(NS2) 및 제4출력노드(N4)와 연결되는 드레인 단자(ND2)를 갖는 제2NMOS 트랜지스터(NM2)를 포함한다.

[0014] 제3인버터(130)는 제3입력노드(N3')와 연결되는 게이트단자(PG3)와, 전원 전압(VDD)단과 연결되는 소스단자 (PS3) 및 제5출력노드(N5)에 연결되는 드레인단자(PD3)를 갖는 제3PMOS 트랜지스터(PM3)와, 제4입력노드(N4')와 연결되는 게이트단자(NG3)와, 접지 전압단(VSS)에 연결되는 소스(NS3) 및 제6출력노드(N6)와 연결되는 드레인단자(ND3)를 갖는 제3NMOS 트랜지스터(NM3)를 포함한다.

[0015] 제4인버터(140)는 제5입력노드(N5')와 연결되는 게이트단자(PG4)와, 전원 전압(VDD)단에 연결되는 소스단자 (PS4) 및 제7출력노드(N7)에 연결되는 드레인단자(PD4)를 갖는 제4PMOS 트랜지스터(PM4)와, 제6입력노드(N6')와 연결되는 게이트단자(NG4)와, 접지 전압단(VSS)에 연결되는 소스(NS4) 및 제8출력노드(N8)에 연결되는 드레인단자(ND4)를 갖는 제4NMOS 트랜지스터(NM4)를 포함한다.

[0016] 제5인버터(150)는 제7입력노드(N7')와 연결되는 게이트단자(PG5)와, 전원 전압단(VDD)에 연결되는 소스단자 (PS5) 및 출력단(Vout)에 연결되는 드레인단자(PD5)을 갖는 제5PMOS 트랜지스터(PM5)와, 제8입력노드(N8')와 연결되는 게이트단자(NG5)와, 접지 전압단(VSS)에 연결되는 소스(NS5) 및 출력단(Vout)에 연결되는 드레인단자(ND5)를 갖는 제5NMOS 트랜지스터(NM5)를 포함한다.

[0017] 즉, 본 발명의 실시예에서 인버터 체인(100)을 구성하는 인버터들 중 일부(예를 들면, 제1, 2, 3, 4인버터)는 상술한 바와 같이 복수 개의 출력노드(N1, N2, N3, N4, N5, N6, N7, N8, N9)를 갖는다.

[0018] 부연 설명하면, 제1, 2, 3, 4인버터(110, 120, 130, 140)는 PMOS 트랜지스터(PM1, PM2, PM3, PM4)와, NMOS 트랜지스터(NM1, NM2, NM3, NM4)를 포함한다. 그리고 제1, 2, 3, 4인버터(110, 120, 130, 140)의 복수 개의 출력노드 (N1, N2, N3, N4, N5, N6, N7, N8)는 각 트랜지스터의 드레인단자를 연결하는 배선(이하, 드레인 배선으로 지칭, 111, 121, 131, 141, 151)과 후속 연결되는 인버터(예를 들면, 제2, 3, 4, 5인버터)의 각 트랜지스터의 게이트단자를 연결하는 배선(이하, 게이트 배선으로 지칭, 113, 123, 133, 143, 153)을 연결하는 복수 개의 연결배선을 통해 형성될 수 있다.

[0019] 이때, 상기의 복수 개의 연결배선은 각 인버터(110, 120, 130, 140, 150)의 드레인 배선(111, 121, 131, 141, 151) 상에서 PMOS 트랜지스터의 드레인단자(PD1, PD2, PD3, PD4, PD5)와 인접한 위치에 연결되는 제1연결배선 (161a, 162a, 163a, 164a)과, 각 인버터(110, 120, 130, 140, 150)의 드레인 배선(111, 121, 131, 141, 151) 상에서 NMOS 트랜지스터의 드레인단자(ND1, ND2, ND3, ND4, ND5)와 인접한 위치에 연결되는 제2연결배선(161b, 162b, 163b, 164b)을 포함할 수 있다.

[0020] 상기의 설명에서 PMOS 트랜지스터의 드레인단자(PD1, PD2, PD3, PD4, PD5)와 인접한 위치란 드레인 배선 ((111, 121, 131, 141, 151) 상에서 드레인 배선(111, 121, 131, 141, 151)의 중간 보다 PMOS 트랜지스터의 드레인단자 (PD1, PD2, PD3, PD4, PD5)에 가까운 위치를 말한다.

[0021] 그리고 NMOS 트랜지스터의 드레인단자(ND1, ND2, ND3, ND4, ND5)와 인접한 위치란 드레인 배선 (111, 121, 131, 141, 151) 상에서 드레인 배선(111, 121, 131, 141, 151)의 중간 보다 NMOS 트랜지스터의 드레인단자 (ND1, ND2, ND3, ND4, ND5)에 가까운 위치를 말한다.

[0022] 또한, 본 발명의 실시예에서 상술한 바와 같이 인버터들 중 일부(제1, 2, 3, 4인버터(110, 120, 130, 140))에는 복수 개의 출력노드(N1, N2, N3, N4, N5, N6, N7, N8)가 형성되고, 상기의 일부의 인버터 다음으로 연결되는 인버터(제 2, 3, 4, 5인버터(120, 130, 140, 150))에는 상기의 복수 개의 출력노드(N1, N2, N3, N4, N5, N6, N7, N8)와 각각 연결되는 복수 개의 입력노드(N1', N2', N3', N4', N5', N6', N7', N8')가 형성될 수 있다.

[0023] 또한, 본 발명의 실시예에서는 상술한 바와 같이 연결배선을 제1, 2연결배선을 예로 들어 설명하였으나, 더 많은

숫자의 연결배선을 포함할 수도 있다.

[0024] 한편, 본 발명의 실시예에 따른 인버터 체인 회로의 동작을 살펴보면 다음과 같다.

[0025] 제1인버터(110)의 입력단으로 로우 레벨의 전위가 입력되면, 제1인버터(110)에서는 제1PMOS 트랜지스터(PM1)가 편온되고, 제2인버터(120)에서는 제2NMOS 트랜지스터(NM2)가 편온되고, 제3인버터(130)에서는 제3PMOS 트랜지스터(PM3)가 편온되고, 제4인버터(140)에서는 제4NMOS 트랜지스터(NM4)가 편온되고, 제5인버터(150)에서는 제5PMOS 트랜지스터(PM5)가 편온되어 하이 레벨의 전위가 출력될 수 있다.

[0026] 상기의 과정에서 제1,2인버터(110,120)에서는 전원 전압(VDD)의 전류가 제1인버터(110)의 드레인 배선(111)에서 제1연결배선(161a)을 통해 제2인버터(120)의 게이트 배선(123)으로 흐르는 제1라이징 패스(Rising path)가 형성된다.

[0027] 그리고 제2,3인버터(120,130)에서는 접지 전압(VSS)의 전류가 제2인버터(120)의 드레인 배선(121)에서 제2연결배선(162b)을 통해 제3인버터(130)의 게이트 배선(133)으로 흐르는 제1폴링 패스(Falling path)가 형성된다.

[0028] 제3,4인버터(130,140)에서는 전원 전압(VDD)의 전류가 제3인버터(130)의 드레인 배선(131)에서 제1연결배선(163a)을 통해 제4인버터(140)의 게이트 배선(143)으로 흐르는 제2라이징 패스가 형성된다.

[0029] 제4,5인버터(140,150)에서는 접지 전압(VSS)의 전류가 제4인버터(140)의 드레인 배선(141)에서 제2연결배선(164b)을 통해 제5인버터(150)의 게이트 배선(153)으로 흐르는 제2폴링 패스가 형성된다.

[0030] 상기의 과정에서 각 제1연결배선(161a,162a,163a,164a)은 드레인 배선(111,121,131,141,151) 상에서 PMOS 트랜지스터의 드레인단자(PM1,PM2,PM3,PM4)와 인접한 위치에 연결됨에 따라, 라이징 패스의 거리가 짧아지게 된다. 이로 인해 본 발명의 실시예에서는 인버터 체인의 라이징 타임 역시 짧아지게 된다.

[0031] 또, 각 제2연결배선(161b,162b,163b,164b)은 드레인 배선(111,121,131,141,151) 상에서 NMOS 트랜지스터의 드레인단자(NM1,NM2,NM3,NM4)와 인접한 위치에 연결됨에 따라, 폴링 패스의 거리가 짧아지게 된다. 이로 인해 본 발명의 실시예에서는 인버터의 폴링 타임 역시 짧아지게 된다.

[0032] 따라서 본 발명의 실시예에서는 라이징 패스와 폴링 패스의 개선을 통해 인버터의 라이징 타임 및 폴링 타임의 효율을 높일 수 있게 된다.

[0033] 본 발명이 속하는 기술분야의 당업자는 본 발명이 그 기술적 사상이나 필수적 특징으로 변경하지 않고서 다른 구체적인 형태로 실시될 수 있으므로, 이상에서 기술한 실시예들은 모든 면에서 예시적인 것이며 한정적인 것이 아닌 것으로서 이해해야만 한다. 본 발명의 범위는 상기의 상세한 설명보다는 후술하는 특허청구범위에 의하여 나타내어지며, 특허청구범위의 의미 및 범위 그리고 그 등가개념으로부터 도출되는 모든 변경 또는 변형된 형태가 본 발명의 범위에 포함되는 것으로 해석되어야 한다.

## 도면

### 도면1

10

## 도면2

## 도면3

## 도면4