(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2005-524239

(P2005-524239A)

(43) 公表日 平成17年8月11日(2005.8.11)

(51) Int.Cl.<sup>7</sup>

H01L 23/52

H01L 23/28

F 1

H01L 23/52

H01L 23/28

テーマコード(参考)

4M109

D

A

審査請求 未請求 予備審査請求 未請求 (全 40 頁)

|               |                              |

|---------------|------------------------------|

| (21) 出願番号     | 特願2004-502330 (P2004-502330) |

| (86) (22) 出願日 | 平成15年4月29日 (2003.4.29)       |

| (85) 翻訳文提出日   | 平成16年12月15日 (2004.12.15)     |

| (86) 國際出願番号   | PCT/US2003/013524            |

| (87) 國際公開番号   | W02003/094203                |

| (87) 國際公開日    | 平成15年11月13日 (2003.11.13)     |

| (31) 優先権主張番号  | 60/376,482                   |

| (32) 優先日      | 平成14年4月29日 (2002.4.29)       |

| (33) 優先権主張国   | 米国(US)                       |

| (31) 優先権主張番号  | 60/400,180                   |

| (32) 優先日      | 平成14年7月31日 (2002.7.31)       |

| (33) 優先権主張国   | 米国(US)                       |

|          |                                                                                                 |

|----------|-------------------------------------------------------------------------------------------------|

| (71) 出願人 | 504403563<br>シリコン・パイプ・インコーポレーテッド<br>アメリカ合衆国カリフォルニア州9512<br>6-3448, サン・ホセ, パークムーア<br>・アベニュー 1299 |

| (74) 代理人 | 100089705<br>弁理士 松本 一夫                                                                          |

| (74) 代理人 | 100076691<br>弁理士 増井 忠式                                                                          |

| (74) 代理人 | 100075270<br>弁理士 小林 泰                                                                           |

| (74) 代理人 | 100080137<br>弁理士 千葉 昭男                                                                          |

| (74) 代理人 | 100096013<br>弁理士 富田 博行                                                                          |

最終頁に続く

(54) 【発明の名称】ダイレクト・コネクト形信号システム

## (57) 【要約】

ダイレクトコネクト信号システム(200)は、プリント回路ボード(205)と、このプリント回路ボード上に配置された第1(201A)と第2(201B)の集積回路パッケージとを備える。複数の電気信号導体(203)は、第1と第2の集積回路パッケージの間ににおいて、プリント回路ボード上に浮遊させて延在させる。

**【特許請求の範囲】****【請求項 1】**

集積回路パッケージであって、

基板と、

該基板の第1の表面に配置され、第1の複数のコンタクトを含む集積回路ダイと、

前記基板の前記第1表面に配置された複数の導電性トレースであって、前記第1表面に沿って前記第1の複数のコンタクトから前記第1表面の露出領域まで延在した、前記の複数の導電性トレースと、

を備えた集積回路パッケージ。

**【請求項 2】**

請求項1記載の集積回路パッケージであって、さらに、前記基板の前記第1表面に配置されかつ前記集積回路ダイを部分的に包囲するハウジングを備え、該ハウジングは、前記第1表面のすべてを、前記露出領域を除き覆ったこと、を特徴とする集積回路パッケージ。

**【請求項 3】**

請求項1記載の集積回路パッケージにおいて、前記複数の導電性トレースは、前記第1表面の前記露出領域上に配置しあつコネクタに接触するように構成したそれぞれの端子端部を含むこと、を特徴とする集積回路パッケージ。

**【請求項 4】**

請求項3記載の集積回路パッケージにおいて、前記端子端部は、コネクタと接触するように構成したこと、を特徴とする集積回路パッケージ。

**【請求項 5】**

請求項3記載の集積回路パッケージであって、さらに前記コネクタを含み、該コネクタは、前記導電性トレースの前記端子端部に結合され、かつケーブル内のそれぞれの信号導体と接触するように構成されたこと、を特徴とする集積回路パッケージ。

**【請求項 6】**

請求項1記載の集積回路パッケージであって、さらに、

前記基板に固着されたコネクタであって、前記導電性トレースの端子端部に接触する複数の導電性コンタクトを有する、前記のコネクタと、

前記複数の導電性トレースの前記端子端部に対し、前記複数の導電性コンタクトを介して結合された複数の導体を有するケーブルと、

を備えたこと、を特徴とする集積回路パッケージ。

**【請求項 7】**

請求項6記載の集積回路パッケージにおいて、前記導電性トレースの前記端子端部は、前記第1表面の前記露出領域上に配置したこと、を特徴とする集積回路パッケージ。

**【請求項 8】**

請求項6記載の集積回路パッケージにおいて、前記コネクタは、前記基板に取り外し可能に固着されること、を特徴とする集積回路パッケージ。

**【請求項 9】**

請求項1記載の集積回路パッケージにおいて、前記基板は、コネクタの突出要素を受けるように適合させた前記露出領域内の少なくとも1つの凹部区域を含むこと、を特徴とする集積回路パッケージ。

**【請求項 10】**

請求項9記載の集積回路パッケージにおいて、前記凹部区域は、前記基板中へ延在する孔であって、前記コネクタの前記突出要素の形状に従った形状を有する前記の孔であること、を特徴とする集積回路パッケージ。

**【請求項 11】**

請求項10記載の集積回路パッケージにおいて、前記孔は、前記基板を貫通して延在すること、を特徴とする集積回路パッケージ。

**【請求項 12】**

10

20

30

40

50

請求項 9 記載の集積回路パッケージにおいて、前記凹部区域は、前記突出要素の幅に従う幅を有するチャンネルであること、を特徴とする集積回路パッケージ。

【請求項 13】

請求項 1 記載の集積回路パッケージにおいて、前記集積回路ダイは、さらに、第 2 の複数のコンタクトを含み、前記基板は、複数の導電性構造を含み、該複数の導電性構造は、前記第 2 の複数のコンタクトと接触し、かつ前記基板の前記第 1 表面から第 2 表面まで前記基板を貫通して延在すること、を特徴とする集積回路パッケージ。

【請求項 14】

請求項 13 記載の集積回路パッケージにおいて、前記複数の導電性構造のうちの少なくとも 1 つは、前記基板中へ延在する導電性ビアを含むこと、を特徴とする集積回路パッケージ。 10

【請求項 15】

請求項 13 記載の集積回路パッケージにおいて、前記複数の導電性構造は、前記基板の前記第 2 表面に配置された複数の導電性ランドを含むこと、を特徴とする集積回路パッケージ。

【請求項 16】

請求項 15 記載の集積回路パッケージにおいて、前記導電性ランドは、プリント回路ボードに配置された対応する導電性ランドに結合されるように構成されたこと、を特徴とする集積回路パッケージ。

【請求項 17】

請求項 16 記載の集積回路パッケージにおいて、前記導電性ランドは、前記プリント回路ボード上の対応する導電性ランドにハンダ付けされるように構成されたこと、を特徴とする集積回路パッケージ。 20

【請求項 18】

請求項 1 記載の集積回路パッケージにおいて、前記複数の導電性トレースは、前記基板のエッジを超えて延在すること、を特徴とする集積回路パッケージ。

【請求項 19】

請求項 18 記載の集積回路パッケージにおいて、前記複数の導電性トレースは、絶縁材料内に少なくとも部分的にカプセル封入され、前記絶縁材料は、前記導電性トレースを、実質上互いに固定された位置に維持すること、を特徴とする集積回路パッケージ。 30

【請求項 20】

請求項 19 記載の集積回路パッケージにおいて、前記絶縁材料は、ポリマー材料であること、を特徴とする集積回路パッケージ。

【請求項 21】

請求項 1 記載の集積回路パッケージにおいて、前記複数の導電性トレースは、前記第 1 の複数のコンタクトから前記露出領域の第 1 の部分まで延在する第 1 の複数のトレース・セグメントと、前記第 1 の複数のコンタクトから前記露出領域の第 2 の部分まで延在する第 2 の複数のトレース・セグメントとを含むこと、を特徴とする集積回路パッケージ。

【請求項 22】

請求項 21 記載の集積回路パッケージにおいて、前記第 1 の複数のトレース・セグメントは、前記第 2 の複数のトレース・セグメントとは実質上反対の方向に延在すること、を特徴とする集積回路パッケージ。 40

【請求項 23】

請求項 21 記載の集積回路パッケージにおいて、前記第 1 の複数のトレース・セグメントは、前記第 2 の複数のトレース・セグメントとは実質上直交する方向に延在すること、を特徴とする集積回路パッケージ。

【請求項 24】

請求項 21 記載の集積回路パッケージにおいて、前記第 1 の複数のトレース・セグメントは、前記露出領域の前記第 1 部分上に配置されかつ第 1 のコネクタを受けるように構成された端子端部を含むこと、を特徴とする集積回路パッケージ。 50

**【請求項 2 5】**

請求項 2 4 記載の集積回路パッケージにおいて、前記第 2 の複数のトレース・セグメントは、前記露出領域の前記第 2 部分に配置されかつ第 2 のコネクタを受けるように構成された端子端部を含むこと、を特徴とする集積回路パッケージ。

**【請求項 2 6】**

請求項 2 1 記載の集積回路パッケージにおいて、前記第 1 表面の前記露出領域は、前記集積回路ダイを囲む前記第 1 表面の周辺領域を含み、前記周辺領域は、前記第 1 基板のエッジにより境界を定められること、を特徴とする集積回路パッケージ。

**【請求項 2 7】**

請求項 2 6 記載の集積回路パッケージにおいて、前記露出領域の前記第 1 部分と第 2 部分は、前記基板の対向するエッジにより境界を定められること、を特徴とする集積回路パッケージ。 10

**【請求項 2 8】**

請求項 2 6 記載の集積回路パッケージにおいて、前記露出領域の前記第 1 部分と第 2 部分は、前記基板の隣接するエッジにより境界を定められること、を特徴とする集積回路パッケージ。

**【請求項 2 9】**

集積回路パッケージであって、

第 1 の組のコンタクトと第 2 の組のコンタクトとを有する集積回路ダイと、

該集積回路ダイに隣接して配置された第 1 の表面と、該第 1 表面と対向する第 1 の表面とを有する基板と、

前記第 1 組のコンタクトに結合した第 1 の組の導電性構造であって、前記第 1 表面から前記基板を貫通して前記第 2 表面へ延在する、前記の第 1 組の導電性構造と、

前記第 2 組のコンタクトに結合した第 2 の組の導電性構造であって、前記第 1 表面と第 2 表面との間に形成された前記基板のエッジまで延在する、前記の第 2 の組の導電性構造と、

を備えた集積回路パッケージ。 20

**【請求項 3 0】**

請求項 2 9 記載の集積回路パッケージにおいて、前記第 2 組の導電性構造は、少なくとも部分的に前記基板内に配置されたこと、を特徴とする集積回路パッケージ。 30

**【請求項 3 1】**

請求項 2 9 記載の集積回路パッケージにおいて、前記第 1 組の導電性構造は、前記第 2 表面まで延在する導電性ビアを含むこと、を特徴とする集積回路パッケージ。

**【請求項 3 2】**

請求項 2 9 記載の集積回路パッケージにおいて、前記第 1 組の導電性構造は、前記集積回路パッケージを、プリント回路ボード上の導電性トレースに電気的に結合できるようするため、前記第 2 表面上に配置された複数の導電性ランドを含むこと、を特徴とする集積回路パッケージ。

**【請求項 3 3】**

請求項 2 9 記載の集積回路パッケージにおいて、前記第 2 組の導電性構造は、

前記第 1 表面と第 2 表面との間において前記基板内に配置され、かつ前記基板の前記エッジまで延在する複数の導電性トレースと、

前記複数の導電性トレースと接触するため前記第 1 表面から延在した複数の導電性ビアと、

を備えたこと、を特徴とする集積回路パッケージ。 40

**【請求項 3 4】**

請求項 3 3 記載の集積回路パッケージにおいて、前記複数の導電性トレースは、前記基板の前記エッジを超えて延在したこと、を特徴とする集積回路パッケージ。

**【請求項 3 5】**

請求項 3 4 記載の集積回路パッケージであって、さらに、前記基板の前記エッジを超える 50

た前記複数の導電性トレースに対し固着されたコネクタを含むこと、を特徴とする集積回路パッケージ。

【請求項 3 6】

請求項 3 5 記載の集積回路パッケージにおいて、前記コネクタは、別の集積回路パッケージから延在した導電性トレースに対し結合された対応するもう片方のコネクタを受けるように構成されたこと、を特徴とする集積回路パッケージ。

【請求項 3 7】

請求項 3 5 記載の集積回路パッケージにおいて、前記コネクタは、別の集積回路パッケージ上の電気的コンタクト・ポイントに接続するように構成されたこと、を特徴とする集積回路パッケージ。

10

【請求項 3 8】

請求項 3 4 記載の集積回路パッケージにおいて、前記複数の導電性トレースは、絶縁材料内に少なくとも部分的にカプセル封入され、前記絶縁材料は、前記導電性トレースを、実質上互いに固定された位置に維持すること、を特徴とする集積回路パッケージ。

【請求項 3 9】

信号システムであって、

プリント回路ボードと、

該プリント回路ボード上に配置された第 1 の集積回路パッケージと、

前記プリント回路ボード上に配置された第 2 の集積回路パッケージと、

前記プリント回路ボード上に浮遊させた複数の電気信号導体であって、前記第 1 集積回路パッケージと第 2 集積回路パッケージとの間に延在する、前記の複数の電気信号導体と

、

を備えた信号システム。

【請求項 4 0】

請求項 3 9 記載の信号システムにおいて、前記プリント回路ボードは、前記第 1 集積回路パッケージおよび第 2 集積回路パッケージに対し、これらに電力を供給するため結合された導電性構造を含むこと、を特徴とする信号システム。

20

【請求項 4 1】

請求項 3 9 記載の信号システムにおいて、前記第 1 集積回路パッケージは、基板と、該基板の第 1 の表面に配置された集積回路ダイとを含み、該集積回路ダイは、前記複数の電気信号導体に結合された第 1 の複数のコンタクトを含むこと、を特徴とする信号システム。

30

【請求項 4 2】

請求項 4 1 記載の信号システムにおいて、前記第 1 集積回路パッケージは、さらに、複数の導電性トレースを含み、該複数の導電性トレースは、前記基板の前記第 1 表面に配置され、かつ前記第 1 表面に沿って前記第 1 複数のコンタクトから前記第 1 表面の露出領域まで延在し、前記複数の電気信号導体は、前記第 1 の複数のコンタクトに対し前記導電性トレースを介して結合されたこと、を特徴とする信号システム。

【請求項 4 3】

請求項 4 2 記載の信号システムにおいて、前記複数の電気信号導体は、前記第 1 表面の前記露出領域において導電性トレースに結合されたこと、を特徴とする信号システム。

40

【請求項 4 4】

請求項 4 1 記載の信号システムにおいて、前記プリント回路ボードは、前記第 1 集積回路パッケージおよび第 2 集積回路パッケージに対し電力を供給するため導電性構造を含み、前記第 1 集積回路ダイは、さらに、前記導電性構造に対しこれからの電力を受けるため結合された第 2 の複数のコンタクトを含むこと、を特徴とする信号システム。

【請求項 4 5】

請求項 4 4 記載の信号システムにおいて、前記基板は、導電性構造を含み、該導電性構造は、前記第 2 の複数のコンタクトのうちの少なくとも 1 つに結合され、かつ前記基板を貫通して前記第 1 表面から前記基板の第 2 の表面まで延在し、前記第 2 表面は、前記プリ

50

ント回路ボードのある表面に対向したこと、を特徴とする信号システム。

【請求項 4 6】

請求項 4 5 記載の信号システムにおいて、前記基板を貫通して延在する前記導電性構造は、導電性ランドを含み、該ランドは、前記基板の前記第 2 表面に配置され、かつ前記プリント回路ボードの前記導電性構造のうちの少なくとも 1 つに結合されたこと、を特徴とする信号システム。

【請求項 4 7】

請求項 3 9 記載の信号システムにおいて、前記複数の電気信号導体は、ある材料内に力プセル封入され、前記材料は、前記電気信号導体を、実質上互いに固定した位置に維持すること、を特徴とする信号システム。

10

【請求項 4 8】

請求項 3 9 記載の信号システムであって、さらに、第 1 のコネクタを含み、該第 1 コネクタは、前記複数の電気信号導体の第 1 の端部に固着され、かつ前記第 1 集積回路パッケージに結合されたこと、を特徴とする信号システム。

【請求項 4 9】

請求項 4 8 記載の信号システムにおいて、前記コネクタは、前記第 1 集積回路パッケージに対し取り外し可能に結合されたこと、を特徴とする信号システム。

【請求項 5 0】

請求項 4 8 記載の信号システムであって、さらに、第 2 のコネクタを含み、該第 2 コンポーネントは、前記複数の電気信号導体の第 2 の端部に固着され、かつ前記第 2 集積回路パッケージに結合されたこと、を特徴とする信号システム。

20

【請求項 5 1】

請求項 4 8 記載の信号システムにおいて、前記第 1 集積回路パッケージは、

基板と、

該基板の第 1 の表面に配置され、第 1 の複数のコンタクトを含む集積回路ダイと、

前記基板の前記第 1 表面に配置され、かつ前記第 1 表面に沿って前記第 1 の複数のコンタクトから前記第 1 表面の露出領域まで延在した複数の導電性トレースであって、前記第 1 コネクタが、前記複数の導電性トレースに対し前記露出領域において結合された、前記の複数の導電性トレースと、

を含むこと、を特徴とする信号システム。

30

【請求項 5 2】

請求項 3 9 記載の信号システムにおいて、前記第 1 集積回路パッケージと第 2 集積回路パッケージとの間に延在した前記複数の電気信号導体は、第 1 の複数の電気信号導体を構成し、前記信号システムは、さらに、

前記プリント回路ボードに装着された第 3 の集積回路パッケージと、

前記プリント回路ボード上に浮遊させ、かつ前記第 1 集積回路パッケージと第 3 集積回路パッケージとの間に延在した第 2 の複数の電気信号導体と、

を含むこと、を特徴とする信号システム。

【請求項 5 3】

請求項 5 2 記載の信号システムにおいて、第 1 集積回路パッケージは、基板を含み、該基板は、前記第 1 の複数の電気信号導体に結合された第 1 の組のコンタクトと、前記第 2 の複数の電気信号導体に結合された第 2 の複数のコンタクトとを有すること、を特徴とする信号システム。

40

【請求項 5 4】

請求項 5 3 記載の信号システムにおいて、前記第 1 組のコンタクトと前記第 2 組のコンタクトは、前記基板の第 1 の領域と第 2 の領域とそれぞれ配置されたこと、を特徴とする信号システム。

【請求項 5 5】

請求項 5 4 記載の信号システムにおいて、前記第 1 組のコンタクトと第 2 組のコンタクトは、前記基板の互いに対向する表面に配置されたこと、を特徴とする信号システム。

50

**【請求項 5 6】**

請求項 5 4 記載の信号システムにおいて、前記第 1 集積回路パッケージは、さらに、前記基板の第 1 の表面に配置された集積回路ダイを含み、前記第 1 組のコンタクトは、前記基板の前記第 1 表面に対し前記集積回路ダイの第 1 のエッジに隣接して配置され、前記第 2 組のコンタクトは、前記基板の前記第 1 表面に対し前記集積回路ダイの第 2 のエッジに隣接して配置されたこと、を特徴とする信号システム。

**【請求項 5 7】**

請求項 5 6 記載の信号システムにおいて、前記第 1 エッジは、前記第 2 エッジに対向したこと、を特徴とする信号システム。

**【請求項 5 8】**

請求項 5 6 記載の信号システムにおいて、前記第 1 エッジは、前記第 2 エッジに隣接したこと、を特徴とする信号システム。

**【請求項 5 9】**

請求項 5 6 記載の信号システムであって、さらに、複数の導電性トレースを含み、該複数の導電性トレースは、前記基板上に配置され、かつ前記集積回路ダイから、前記第 1 組のコンタクトへまた前記第 2 組のコンタクトへ延在したこと、を特徴とする信号システム。

**【請求項 6 0】**

請求項 5 9 記載の信号システムにおいて、前記複数の導電性トレースは、前記基板の前記第 1 表面に亘って前記集積回路ダイから前記第 1 組のコンタクトまで延在したこと、を特徴とする信号システム。

**【請求項 6 1】**

請求項 5 9 記載の信号システムにおいて、前記複数の導電性トレースは、少なくとも部分的に、前記基板の内部層に沿ってルーティングされたこと、を特徴とする信号システム。

**【請求項 6 2】**

請求項 5 2 記載の信号システムにおいて、前記第 2 の複数の電気信号導体は、前記第 1 の複数の電気信号導体に結合されたこと、を特徴とする信号システム。

**【請求項 6 3】**

請求項 5 2 記載の信号システムであって、さらに、コネクタを含み、該コネクタは、前記第 1 の複数の電気信号導体の第 1 の端部にまた前記第 2 の複数の電気信号導体の第 1 の端部に結合され、前記コネクタは、前記第 1 集積回路パッケージに結合されたこと、を特徴とする信号システム。

**【請求項 6 4】**

請求項 6 3 記載の信号システムにおいて、前記第 1 の複数の電気信号導体は、前記コネクタ内において前記第 2 の複数の電気信号導体に結合されたこと、を特徴とする信号システム。

**【請求項 6 5】**

請求項 5 2 記載の信号システムであって、さらに、

前記第 1 の複数の電気信号導体の第 1 の端部に固着され、かつ前記第 1 集積回路パッケージに結合された第 1 のコネクタと、

前記第 2 の複数の電気信号導体の第 1 の端部に固着され、かつ前記第 1 集積回路パッケージに結合された第 2 のコネクタと、

を含むこと、を特徴とする信号システム。

**【請求項 6 6】**

信号システムであって、

プリント回路ボードと、

該プリント回路ボード上に配置された第 1 の集積回路パッケージと、

前記プリント回路ボード上に配置された第 2 の集積回路パッケージと、

前記第 1 集積回路パッケージと前記第 2 集積回路パッケージとに固着されたケーブルで

10

20

30

40

50

あって、複数の電気信号導体を含む、前記のケーブルと、

を備えた信号システム。

【請求項 6 7】

請求項 6 6 記載の信号システムにおいて、前記ケーブルは、その長さの少なくとも一部

において空中に浮遊させたこと、を特徴とする信号システム。

【請求項 6 8】

請求項 6 6 記載の信号システムにおいて、前記ケーブルの少なくとも 1 部分は、前記ブ

リント回路ボードに接触すること、を特徴とする信号システム。

【請求項 6 9】

請求項 6 6 記載の信号システムにおいて、前記ケーブルの前記少なくとも 1 部分は、前

記プリント回路ボードに固着されたこと、を特徴とする信号システム。 10

【請求項 7 0】

請求項 6 6 記載の信号システムにおいて、前記ケーブルは、前記第 1 プリント回路デバ

イスに取り外し可能に固着されたこと、を特徴とする信号システム。

【請求項 7 1】

請求項 6 6 記載の信号システムにおいて、前記ケーブルは、非導通材料を含み、該非導

通材料は、前記電気信号導体を、実質上互いに固定された位置に維持すること、を特徴と

する信号システム。

【請求項 7 2】

請求項 6 6 記載の信号システムにおいて、前記ケーブルは、リボン・スタイルのケーブ

ルであること、を特徴とする信号システム。 20

【請求項 7 3】

請求項 6 6 記載の信号システムにおいて、前記ケーブルは、フレキシブルのケーブルで

あること、を特徴とする信号システム。

【請求項 7 4】

請求項 6 6 記載の信号システムにおいて、前記第 1 集積回路パッケージは、基板と、該基

板上に配置された集積回路ダイとを含み、前記ケーブルは、前記基板に固着されたこと

、を特徴とする信号システム。

【請求項 7 5】

請求項 7 4 記載の信号システムにおいて、前記第 1 集積回路パッケージは、さらに、複

数の導電性トレースを含み、該複数の導電性トレースは、前記基板上に配置され、かつ第

1 の端部において前記ケーブルの前記複数の電気信号導体に結合されたこと、を特徴と

する信号システム。 30

【請求項 7 6】

請求項 7 5 記載の信号システムにおいて、前記集積回路ダイは、複数の電気信号領域を

含み、該複数の電気信号領域は、前記基板上に配置された前記複数の導電性トレースの第

2 の端部に結合されたこと、を特徴とする信号システム。

【請求項 7 7】

請求項 7 6 記載の信号システムにおいて、前記集積回路ダイは、前記基板の第 1 の表面

に配置され、前記複数の導電性トレースは、前記基板の前記第 1 表面に沿ってエンドツー

エンドで延在すること、を特徴とする信号システム。 40

【請求項 7 8】

請求項 6 6 記載の信号システムにおいて、前記第 1 と第 2 の集積回路パッケージは、前

記プリント回路ボードの互いに対向する側に配置されたこと、を特徴とする信号システム

。

【請求項 7 9】

請求項 6 6 記載の信号システムにおいて、前記プリント回路ボードは、前記第 1 集積回

路パッケージの電源電圧端子に結合した導電性構造を含むこと、を特徴とする信号システ

ム。

【請求項 8 0】

信号システムであって、

第1の回路ボードと、

該第1回路ボード上に配置され、かつ第1のインバータ上に配置された第1の集積回路ダイを含む第1の集積回路パッケージと、

第2の基板上に配置された第2の集積回路ダイを含む第2の集積回路パッケージと、

前記第1基板と前記第2基板とに固着された、複数の電気信号導体を含むケーブルと、

を備えた信号システム。

【請求項 8 1】

請求項 8 0 記載の信号システムであって、さらに、第2の回路ボードを含み、前記第2集積回路パッケージは、前記第2回路ボード上に配置されたこと、を特徴とする信号システム。 10

【請求項 8 2】

請求項 8 1 記載の信号システムにおいて、前記第1回路ボードは、前記第1回路ボードに対し取り外し可能に結合されたこと、を特徴とする信号システム。

【請求項 8 3】

請求項 8 1 記載の信号システムであって、さらに、前記第1および第2の回路ボードのうちの少なくとも一方に取り外し可能に結合されたバックプレーンを含むこと、を特徴とする信号システム。

【請求項 8 4】

請求項 8 0 記載の信号システムにおいて、前記ケーブルは、その長さの少なくとも一部において空中に浮遊させたこと、を特徴とする信号システム。 20

【請求項 8 5】

請求項 8 0 記載の信号システムにおいて、前記ケーブルは、前記第1集積回路パッケージに取り外し可能に固着されたこと、を特徴とする信号システム。

【請求項 8 6】

請求項 8 0 記載の信号システムにおいて、前記ケーブルは、リボン・スタイルのケーブルであること、を特徴とする信号システム。

【請求項 8 7】

請求項 8 0 記載の信号システムにおいて、前記ケーブルは、フレキシブルのケーブルであること、を特徴とする信号システム。 30

【請求項 8 8】

請求項 6 6 記載の信号システムにおいて、前記第1集積回路パッケージは、さらに、複数の導電性トレースを含み、該複数の導電性トレースは、前記第1基板上に配置され、かつ前記第1集積回路ダイと前記ケーブルの前記複数の電気信号導体との間に結合されたこと、を特徴とする信号システム。

【請求項 8 9】

請求項 8 8 記載の信号システムにおいて、前記集積回路ダイは、前記基板の第1の表面上に配置され、前記複数の導電性トレースは、前記基板の前記第1表面上に沿ってエンドツーエンド延在すること、を特徴とする信号システム。

【請求項 9 0】

回路ボード上に装着するための集積回路パッケージであって、

基板と、

該基板上に配置された第1の集積回路ダイと、

該基板上に配置された第2の集積回路ダイと、

前記第1集積回路ダイと第2集積回路ダイとの間に電気的に結合されたケーブルと、

を備えた集積回路パッケージ。

【請求項 9 1】

請求項 9 0 記載の集積回路パッケージにおいて、前記ケーブルは、前記基板に対し少なくとも1つの端部において取り外し可能に固着されたこと、を特徴とする集積回路パッケージ。 40

**【請求項 9 2】**

請求項 9 1 記載の集積回路パッケージにおいて、前記ケーブルは、複数の電気信号導体を含むこと、を特徴とする集積回路パッケージ。

**【請求項 9 3】**

第 1 のダイと第 2 のダイとを含む集積回路パッケージを製造するための方法であって、前記第 1 ダイを、前記集積回路パッケージの表面に装着し、前記第 1 ダイを前記基板に装着した後に、前記第 1 ダイをテスト装置でテストし、前記第 2 ダイを前記基板に装着し、前記第 2 ダイを前記基板に装着した後に、前記第 2 ダイを前記テスト装置でテストし、前記テスト装置により前記第 1 ダイと前記第 2 ダイを成功裏にテストできた場合、前記第 1 ダイと前記第 2 ダイとの間に第 1 のケーブルを結合すること、

10 を備えた製造方法。

**【請求項 9 4】**

請求項 9 3 記載の方法であって、さらに、前記第 1 ダイと前記第 2 ダイとの間に前記第 1 ケーブルを結合した後に、前記第 1 ダイ、第 2 ダイおよび第 1 ケーブルをハウジング内に封入すること、を含むこと、を特徴とする製造方法。

**【請求項 9 5】**

請求項 9 3 記載の方法において、前記第 1 と第 2 のダイは、前記基板の第 1 の表面に装着し、前記方法が、さらに、前記基板に複数の構造を配置することを含み、前記複数の構造は、前記基板の前記第 1 表面から前記基板の第 2 の表面への導電性経路を確立すること、

20 を特徴とする製造方法。

**【請求項 9 6】**

請求項 9 5 記載の方法であって、さらに、前記集積回路パッケージをプリント回路ボードに装着できるようにするため、前記基板の前記第 2 表面に複数のコンタクト構造を配置すること、を含むことを特徴とする製造方法。

**【請求項 9 7】**

請求項 9 3 記載の方法において、前記第 1 ダイと前記第 2 ダイとの間に前記第 1 ケーブルを結合することは、

前記基板上に配置されかつ前記第 1 ダイのコンタクトに接続された第 1 の複数のトレースに対し、前記第 1 ケーブルの第 1 の端部を結合し、

30

前記基板上に配置されかつ前記第 2 ダイのコンタクトに接続された第 2 の複数のトレースに対し、前記第 1 ケーブルの第 2 の端部を結合すること、

を含むこと、を特徴とする製造方法。

**【請求項 9 8】**

請求項 9 7 記載の方法において、前記第 1 ダイを前記テスト装置でテストすることは、前記テスト装置と前記第 1 の複数のトレースとの間に第 2 のケーブルを結合すること、を含むことを特徴とする製造方法。

**【請求項 9 9】**

請求項 9 8 記載の方法において、前記第 2 ダイを前記テスト装置でテストすることは、前記テスト装置と前記第 2 の複数のトレースとの間に前記第 2 ケーブルを結合すること、

40 を含むことを特徴とする製造方法。

**【請求項 1 0 0】**

請求項 9 9 記載の方法において、前記第 2 ダイを前記テスト装置でテストすることは、前記テスト装置と前記第 2 の複数のトレースとの間に第 3 のケーブルを結合すること、を含むことを特徴とする製造方法。

**【請求項 1 0 1】**

請求項 9 7 記載の方法において、前記第 1 ケーブルの第 1 の端部を第 1 の複数のトレースに結合することは、前記第 1 ケーブルの前記第 1 端部を、前記第 1 の複数のトレースの終端に形成されたコンタクトに結合すること、を含むことを特徴とする製造方法。

**【請求項 1 0 2】**

10

20

30

40

50

請求項 9 3 記載の方法において、前記第 2 ダイは、前記第 1 ダイをテストした後に、前記基板に装着すること、を特徴とする製造方法。

【請求項 103】

請求項 9 3 記載の方法において、前記第 2 ダイは、前記第 1 ダイを成功裏にテストできた場合に、前記基板に装着すること、を特徴とする製造方法。

【請求項 104】

請求項 9 3 記載の方法において、前記第 1 ダイを前記テスト装置でテストすることは、前記第 1 ダイが欠陥ダイか非欠陥ダイかを判定すること、を含むことを特徴とする製造方法。

【請求項 105】

請求項 104 記載の方法において、前記第 1 ダイが非欠陥ダイであると判定した場合、前記テスト装置により前記第 1 ダイを成功裏にテストできていること、を特徴とする製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本願は、2002年4月29日出願の米国仮特許出願第60/376,482号および2002年7月31日出願の米国仮特許出願第60/400,180号に基づく優先権を主張するものである。尚、米国仮特許出願第60/376,482号および米国仮特許出願第60/400,180号の内容は、本文に援用する。

【0002】

本発明は、一般的には、電子通信の分野に関し、そして詳細には、集積回路デバイス間における高速シグナリングのための相互接続構造に関するものである。

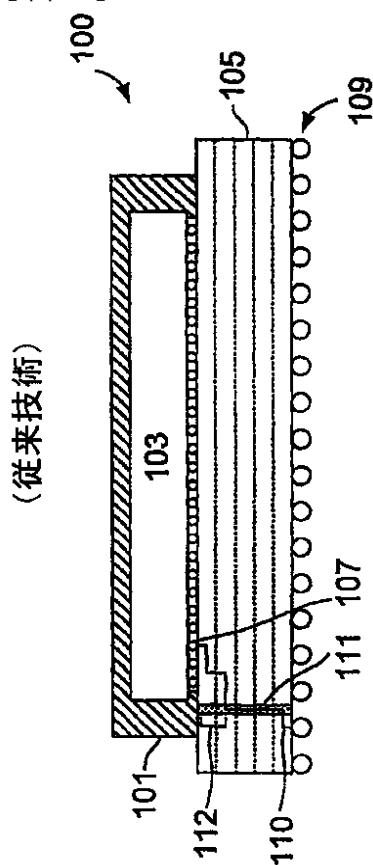

より速い信号レートに対する絶え間のない要求と歩調を合わせるため、集積回路（IC）パッケージは、ワイヤ・ボンディング形パッケージのような比較的に帯域制限される技術から、図1に示す従来技術のフリップチップ・パッケージ100へと発展してきている。このフリップチップ・パッケージ100は、集積回路ダイ103を含み、これは、多層基板105上にパッド側を下にして装着され、そして非導電性ハウジング101内に封入されている。信号ルーティング構造110は、多層基板105内に配置され、これにより比較的密な配置のダイ・パッド107からの信号を、このパッケージの下面のより散らばったボールグリッドアレイ（BGA）109に再分配している。BGA109の個々のコントクト・ボールは、次に、プリント回路ボード上の対応するランドに対しハンダ付けすることができる。

【発明の開示】

【発明が解決しようとする課題】

【0003】

フリップチップ・パッケージ100は、一般にワイヤ・ボンディング形パッケージよりも良好な性能を提供するが、信号レートがギガヘルツ・レンジへと深く進行するにつれ、システム設計者に多くの難題を提示する。例えば、信号再分配のため基板105に必要とされる層の数が、ダイ・パッド107の数の増大に応じて常に増してきており、これは、フリップチップ・パッケージ100をより複雑でコスト高のものとする。また、スルーホール・ビア110（すなわち、多層基板を完全に貫通するように延在するビア）を多くの場合使用して、これにより基板を貫通して信号をルーティングするようしている。しかし残念ながら、それらビアのうちの使用されない部分（例えば領域112）は、使い残りであるスタブを構成し、これが、寄生容量を増しました信号反射を発生するが、これらは双方とも、信号品質を劣化させる。バック・ドリル加工(back-drilling)およびその他の技術を使ってビアのスタブ部分を減少させることもできるが、このような労力は、製造コストをさらに増大させ、またある種のパッケージ基板構造物に適さなかったりあるいは不可能なものとなる。

【0004】

10

20

30

40

50

多層基板 105 内の信号再分配により提示される別の難題は、ルーティング距離の差が、同時に伝送される信号の間にタイミング・スキューを導入する傾向があることである。すなわち、ダイ 103 から同時に出力される信号は、複数の BGA コンタクト 109 に対し異なる時点に到達し、これが、それら信号の集合的データ有効インターバルを減少させてしまう。多くのシステムでは、クロックまたはストローブのような单一の制御信号を、信号受信側デバイス内において使用して、多数の同時に伝送された信号のサンプリングをトリガるようにしている。この結果、信号スキューに起因する集合的データ有効インターバルの圧縮は、受信側のセットアップまたはホールド時間の制約を侵さずにそのようなシステムにおいて実現できる最大の信号レートを、最終的に制限する。このようなスキューに関係する問題を回避するため、込み入ったルーティング法が、多層基板 105 内で時折用いられ、これにより、ダイ・コンタクト経路長を互いに等しくするが、これは、フリップチップ・パッケージ 100 の複雑さおよびコストをさらに増大させる。

#### 【0005】

図 2 は、従来技術の信号システム 120 を示しており、このシステムは、2つのフリップチップ・パッケージ 100A および 100B を含み、そしてこれらは、多層のプリント回路ボード (PCB) 121 内に配置された信号ルーティング構造を介して互いに結合されている。高速シグナリングの観点からすると、集積回路パッケージ 100 内における信号再分配から生ずるこれら問題の多くは、PCB 121 内の多層の信号ルーティングからも生じるものである。例えば、PCB の層間で信号を導くためにスルーホール・ビア 123 を時折使用するが、これは、スタブ容量および信号反射の問題を提示する。また、集積回路パッケージ 100A および 100B の間でルーティングされる各信号経路の長さは、種々の PCB の入口ポイントおよび出口ポイント、並びに種々のトレース 126 の異なった PCB 沈降深度に起因して、異なったものとなる傾向もあり、これにより、タイミング・スキューが導入される。集積回路パッケージ 100 それ自体では、ビア・スタブを減少させるために多くの技術を使え、また経路長を互いに等しくするためにルーティング戦略を使えるが、これら解決策は、システムの複雑さおよびコストを増大させる傾向があるものである。

#### 【課題を解決するための手段】

#### 【0006】

以下の説明および添付図面においては、本発明の十分な理解が得られるように特定の用語および図面シンボルを用いる。場合によっては、これら用語およびシンボルは、本発明を実施するのに必要でない特定の詳細を意味することがある。例えば、回路要素または回路ロック間の相互接続は、多数導体または単一導体の信号ラインとして図示し記述することがある。それら多数導体の信号ラインの各々は、代替的には単一導体の信号ラインとすることができる、また、単一導体の信号ラインの各々は、代替的には多数導体の信号ラインとすることもできる。また、シングルエンデッドとして図示または記述する信号および信号経路は、差動形とすることもでき、また、その逆も可能である。

#### 【0007】

本発明の実施形態においては、各集積回路パッケージ間に電気信号導体を直接接続することにより高速信号システムを実現し、これによりプリント回路ボード上のトレースまたは他の導電性構造を通らずに伝送されるようとする。1 実施形態では、1 対の集積回路パッケージは、回路ボード上に装着され、そしてこのプリント回路ボードの上方に浮遊させたケーブルを介して互いに結合される。高速信号は、一方の集積回路パッケージから他方へとそのケーブルを介してルーティングされる一方で、より低速の信号並びにシステム電源電圧は、トレースおよびプリント回路ボード内の導電性構造を介してそれら集積回路パッケージにルーティングされる。このケーブルは、本文ではダイレクトコネクト・ケーブルと呼ぶが、これは、それら集積回路パッケージの一方または双方に対し、除去可能にあるいは恒久的に固着することができる。また、1 実施形態においては、このケーブル内の導体は、それら集積回路パッケージの少なくとも一方の一体のコンポーネントであり、これは、その集積回路パッケージ内に含まれる 1 つ以上の集積回路ダイのダイ・パッドに接

10

20

30

40

50

触するように延在する。基本原理のシステムでは、ダイレクトコネクト・ケーブルで相互接続された2つの集積回路パッケージを含むが、任意の数の追加のICをそのようなシステムに含め、そしてダイレクトコネクト・ケーブルを介してそれらICのうちの他の1つまたは以上のものに結合されるようにできる。また、単一の集積回路パッケージ内に含まれる2つ以上の集積回路ダイ間において、高速のシグナリングを可能にするために、ダイレクトコネクト・ケーブルを使用することもできる。さらにまた、他の実施形態においては、異なった回路ボード上にまたは同じ回路ボード上の反対側に装着された集積回路デバイス間において、高速の信号経路を確立するために、ダイレクトコネクト・ケーブルが使用される。本発明のこれらおよび他の実施形態は、以下でさらに詳細に説明する。

#### 【発明を実施するための最良の形態】

##### 【0008】

本発明について、添付図面の図により、限定目的ではなく例示として説明する。尚、図面において、同様の要素を参照するのに同じ参照番号を使用している。

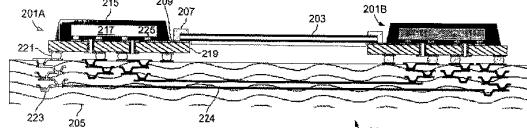

図3は、本発明の1実施形態によるダイレクトコネクト信号システム200を示している。信号システム200は、1対の集積回路パッケージ201Aおよび201B（これらは、“集積回路デバイス”とも呼ぶ）を備え、これらは、プリント回路ボード205に装着しましたダイレクトコネクト・ケーブル203を介して互いに結合されている。図示のように、ダイレクトコネクト・ケーブル203は、集積回路パッケージ201の各々に固着され、そしてプリント回路ボード205より上に持ち上げられた形式で延在している。すなわち、ケーブル203は、プリント回路ボード205より上の空中に浮遊させ、これにより、トレースまたはプリント回路ボード205内の他の導電性構造を通らずに、集積回路パッケージ201間で高速信号の伝送を可能にする。この構成により、プリント回路ボードの入口および出口の構造（例えば、導電性ピア等）から生ずる寄生容量および信号反射が回避される。さらに、ダイレクトコネクト・ケーブル203が1組の同一長さの導体で構成することができるため、プリント回路ボード205を通る信号経路の異なった長さから生ずるタイミング・スキューも、回避される。尚、ダイレクトコネクト・ケーブル203は、図3においては、集積回路パッケージ201への接続部によってのみ支持されるものとして示したが、1つ以上の機械的な支持部を、オプションとして、ケーブル203の下に配置することもできる。

##### 【0009】

図3のこの実施形態では、集積回路パッケージ201の各々は、フリップチップ・パッケージであって、これは、基板219の上面に対しパッド側を下にして装着した集積回路ダイ217を備えている。集積回路ダイ217は、オプションとして、非導電性のハウジング215（例えば、セラミックまたはポリマー材料により形成されたもの）にカプセル封入するようにもできる。基板219の上面のダイ217またはハウジング215により覆われていない部分は、露出された領域を構成し、そしてこの領域に対し、1つ以上のダイレクトコネクト・ケーブル203を取り付けることもできる。したがって、この基板219の下側にある回路ボード・コンタクト221へ基板219を通して高速信号をルーティングするのではなく、導電性トレース209は、基板219の上面に配置し、そして高速I/Oパッド225（すなわち、ダイ217上に形成された高速入出力（I/O）回路に結合される、集積回路ダイ217上のパッド）と基板219の上記露出領域との間でルーティングする。コネクタ207を使うことにより、ダイレクトコネクト・ケーブル内の電気信号導体（すなわち、電流を運ぶことができる導体）を導電性トレース209に対し、恒久的に結合するかあるいは除去可能に結合する。この構成により、基板層219内の信号再分配により生ずる寄生容量、信号反射およびタイミング・スキューは、回避される。

##### 【0010】

続いて図3を参照すると、電源電圧と低速信号（すなわち、高いデータ・スループットを当てにしない信号）は、在来のルーティング技法（例えば、図3に示す部分的入口ピア223およびPCBトレース224等）を使って、パッケージ基板219およびプリント

10

20

30

40

50

回路ボード 205 中をルーティングするようにできる。かなりの数のチップ - チップ間接続は、ダイレクトコネクト・ケーブル 203 により果たすことができるため、パッケージ基板 219 およびプリント回路ボード 200 内の信号ルーティングは、実質上密集度が低くなり、これにより基板およびプリント回路ボードの層の数を減少させるのを可能にする。また、パッケージ基板 219 およびプリント回路ボード 205 を通してスキューレトランクトの信号のみ（目的地に対し他の信号と特定の位相関係で到達することが必要でない信号）をルーティングすることにより、パッケージ基板 219 およびプリント回路ボード 205 内における信号経路長を等しくするのに使用される、蛇行ルーティング技法およびその他の技法は不要となり、これによりさらに、ルーティング密集を軽減し、パッケージ基板 219 およびプリント回路ボード 205 の接続を簡単化する。10 1 実施形態においては、すべての信号またはほぼすべての信号を、1つ以上のダイレクトコネクト・ケーブル 203 を介してルーティングし、電源電圧（例えば、電力とグランド）および無視できる数の信号（またはゼロ信号）をプリント回路ボード 205 およびパッケージ基板 219 内の導電性構造を介して分配する。このような実施形態では、プリント回路ボード 205 およびパッケージ基板 219 の一方または双方は、幾つかの基板層のみあるいは単一の層のみをもつ単純な構造へと変えることもできる。

#### 【0011】

図 3 を再考すると、注目すべきことは、ダイレクトコネクト信号システム 200 を実現するためにはプリント回路ボード 205 に何等変更を要しない点である。このため、設計者が、多数の在来ルーティングの信号経路をもつシステム（すなわち、回路ボード貫通ルーティング形システム（through-circuit-board-routed systems）を、図 3 のダイレクトコネクト信号ルーティングをもつシステムに移したいとき、このような移しは、ボード・レベルでの変更を必要とせずに、一時に1つの信号経路で実現することもできる。在来のルーティングのためのプリント回路ボード上のトレースは、単に、接続しないままに残しておき、そしてその代わりにダイレクトコネクト・ケーブルで高速信号経路を提供するようになる。このシステム内の各信号経路（あるいは1グループの信号経路）は、ダイレクトコネクト・信号配置にうまく移されるため、プリント回路ボードの製作は、それら痕跡的なトレースを省くことによって簡略化することもできる。20

#### 【0012】

ダイレクトコネクト信号システム 200 のさらに別の利点は、集積回路パッケージ 201 のいずれかと高速テスト（図示せず）との間のダイレクトコネクト・ケーブル接続を通して、高速テスト（“AC テスト”としても知られている）を実行することができる。後でさらに詳細に説明するが、ダイレクトコネクト・ケーブル接続を通しての集積回路パッケージ 201 の高速テストは、3 状態デバイス 201B に対する必要性を除去し、そしてプリント回路ボード 205 上のプローブ用トレースから通常生ずる寄生容量および信号反射が回避される。30

#### 【0013】

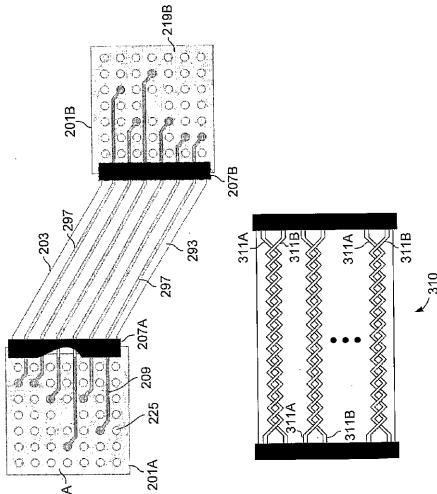

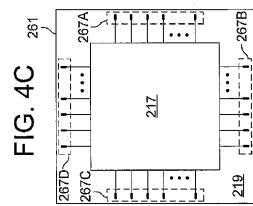

図 4A は、図 3 の集積回路パッケージ 201A の上面図であり、ハウジング 215 および集積回路ダイ 217 の一部を透明にして、パッケージ基板 219 上に配置されたダイ・パッド 225（または集積回路ダイ 217 上に形成されたバンプまたはその他のタイプのコンタクト）と導電性トレース 209 を露出させてある。40 1 実施形態においては、導電性トレース 209 の全長は、基板 219 の表面に沿って、ダイ・パッドのあるコンタクト（これらは、スプリング・タイプのコンタクト、粒子インターフェクト、または他の高密度のインターフェクト構造により確立することができる）からパッケージ基板 219 のその露出領域上のコンタクト・ゾーン 231 へと延在している。以下で説明する代替の実施形態においては、トレース 209 は、基板 219 の下側（すなわち装着側）または基板 219 の内部層上に沿って、全体または部分的に延在させることができる。

#### 【0014】

このトレース 209 は、コンタクト・ゾーン 231 において、例えばダイレクトコネクト・ケーブルからのコンタクトを受けるのに適合させた高密度ランドにおいて終了する。50

代替的には、トレース 209 は、ダイレクトコネクト・ケーブルの一体的コンポーネントを形成するため、基板 219 を超えて延在することができる。また、図 4B および図 4C に示すように、追加のコンタクト・ゾーン（すなわち、図 4B のゾーン 247 および 249、図 4C のゾーン 267A - 267D）を設けることができ、これにより、多数のダイレクトコネクト・ケーブルへの接続ができるようにしたり、あるいは集積回路ダイ 217 の反対側および隣接する側の一方または双方におけるパッケージ基板の露出領域に接触するため単一のダイレクトコネクト・ケーブルへの接続ができるようにしたりする。また、トレース 209 のうちの 1 つ以上のものに、共通のダイ・コンタクトから異なったコンタクト・ゾーンへ延在する 2 以上のトレース・セグメントを含ませることもできる。例えば、図 4B を参照すると、トレース 250 は、トレース・セグメント 251A を含み、これは、ダイ・コンタクト 245 からコンタクト・ゾーン 249 へ延在し、そして別のトレース・セグメント 251B は、ダイ・コンタクトからコンタクト・ゾーン 247 へと延在している。以下で説明するが、このような多セグメントのトレースは、任意の数の集積回路パッケージへの高速の多ドロップ形接続（例えば多数のドロップ・バス）を確立するために使用することができる。

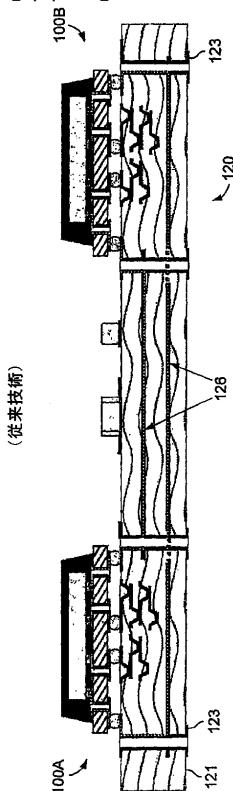

#### 【0015】

図 5A は、図 3 の集積回路パッケージ 201A および 201B 並びにダイレクトコネクト・ケーブル 203 の上面図である。各集積回路パッケージ 201 のハウジングおよび集積回路ダイは、透明にして、パッケージ基板上に配置したダイ・パッド 225 およびトレース 209 を露出させてある。図示した実施形態においては、ダイレクトコネクト・ケーブル 203 は、リボン・スタイルのケーブルであって、フレキシブルで低ロスの誘電体材料 293 内にコプレーナ配列で配置した 1 組の電気信号導体 297 を備えている。ケーブル・コネクタ 207A、207B を使用することにより、電気信号導体 297 とパッケージ基板 219A および 219B のそれぞれの上に配置したトレース 209 との間に接続を確立する。1 つのシートまたはウェブの導電性材料（図示せず）は、シールド目的（例えば、グランドまたは他の基準電圧への接続により）のため、導体 297 の上または下に配置することができ、これにより、マイクロ・ストリップライン・ケーブルを実現する。代替的には、導電性のシートまたはウェブを、導体 297 の上および下の両方に配置することができ、これによって、コプレーナのストリップライン・ケーブルを形成する。また、代替的には、電気信号導体 297 それ自体を信号とグランドに結合することもでき、これにより、隣接する信号間のクロストークを低減する。さらに、図 5B に示すように、ダイレクトコネクト・ケーブル 310 内の導体 311A、311B の対を撲り線対構成（例えば、互いに他方の上に交差させるが、絶縁材料で分離）に配置することもでき、これにより、誘導性結合を低減することができる。2 つより多い導体を互いに撲ることは、さらに別の実施形態で行うこともできる。また、コプレーナ構造ではなく、それら導体を、同軸構成または他の 3 次元構造で配置することもできる。さらに、ダイレクトコネクト・ケーブルは好ましくはフレキシブルにすることによって広範なインターフェース距離および集積回路トポロジーを許容するようにしているが、リジッドな相互接続構造を使用することもできる。図 5A および図 5B には単一平面の導体を示しているが、多数の平面の導体をケーブル 203 および 310 内に形成することもでき、このとき、各平面は、絶縁層により、オプションとしてはシールド層により隣接する平面から分離する。

#### 【0016】

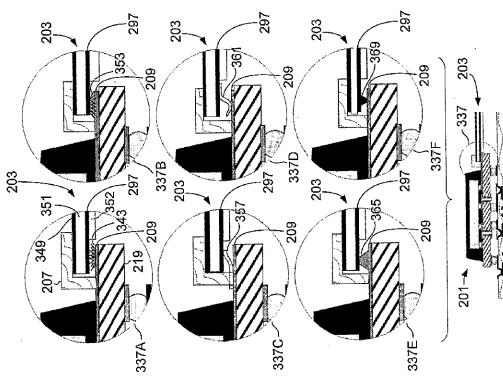

図 6 は、代表的なコンタクト・トポロジーを示しており、そしてこれは、集積回路パッケージ 201 の基板上に配置したトレースと、ダイレクトコネクト・ケーブル 203 内の導体 297 との間に電気的接続を確立するために使用することができる。詳細図 337A においては、導電性スプールまたは樹枝状コンタクト 343 を、パッケージ基板 209 上に配置した各々のトレース 209 に対しハンダ付けしたり、形成したりあるいはその他の方法で固着したりでき、そしてそれらは、ダイレクトコネクト・ケーブル 203 内の対応する導体 297 を突き刺すことにより電気的接続を確立するために使用することができる。また逆に、詳細図 337B に示すように、スプールまたは樹枝状コンタクト 353 をダ

イレクトコネクト・ケーブル導体 297 に固着することができ、そしてこれらは、対応する基板トレース 209 を突き刺すことによって電気的接続を確立するために使用することもできる。

### 【0017】

再び詳細図 337A を参照するが、コネクタ 207 を使用することにより、ダイレクトコネクト・ケーブルをパッケージ基板 219 の露出領域に結合する。また、描いた実施形態では、ダイレクトコネクト・ケーブルは、導体 297 の上と下に配置した絶縁層 351 および 352 と、絶縁層 351 の上に配置したシールド層 349 を備えている。上述のように、追加のシールド層を絶縁層 352 の下に配置することができ、これにより、ストリップラインまたはコプレーナのストリップライン・ケーブルを形成することができる。

10

### 【0018】

別の実施形態においては、詳細図 337C に示したように、基板トレース 209 に固着したフィンガ状の突出要素 357 を使用することにより、ケーブル導体 297 と電気的コンタクトをつくる。突出要素 357 は、好ましくは、弾性のスプリング状の材料から製作し、そしてこれは、ダイレクトコネクト・ケーブル 203 を基板に固着する際に導体 297 に対し偏倚させる。但し、他のタイプの材料も使用することができる。詳細図 337D に示すように、フィンガ状の突出要素 361 は、代替的には、ダイレクトコネクト・ケーブル 297 に固着することができ、そしてダイレクトコネクト・ケーブル 203 を基板に接続するときに基板トレース 209 に対し付勢することもできる。詳細図 337E は、さらに別の実施形態を示しており、これでは、基板トレース 209 に固着したあるいはそれに対し一体的に形成したポイント・コンタクト 365 を使用して、ダイレクトコネクト・ケーブル 203 内の対応する導体 297 と接触する。詳細図 337F を参照すると、ポイント・コンタクト 369 を代替的にはケーブル導体 297 の端部に固着するかあるいは一體的に形成し、そしてこれを使用して基板トレース 209 と接触する。種々の他の構造も使用でき、これにより、他の実施形態においてダイレクトコネクト・ケーブル 203 の導体 297 と基板トレース 209 との間に電気的接続を確立することができ、そしてこれは、ハンダ・ジョイント、スプリング・スタイルのコンタクト、オス対メスの接続構造、粒子インターフェクト構造等（これらに限定しない）を含む。より一般的には、本発明の要旨および範囲から逸脱することなく、任意の構造または技術を使用することができ、これによりダイレクトコネクト・ケーブル 203 の導体 297 を、基板 219 上にあるいはその中に配意した対応するコンタクトに接続することができる。

20

30

40

### 【0019】

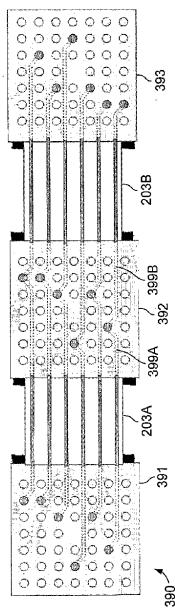

図 7 は、1 組の集積回路パッケージ 391, 392 および 393 を示しており、これらは、2 つのダイレクトコネクト・ケーブル 203A および 203B を介して結合されて、多ドロップの信号システム 390 を確立する。集積回路パッケージ 392 を参照すると、基板トレースの各々は、1 対のトレース・セグメント 399A および 399B を含んでいて、反対のコンタクト・ゾーンまで延在している。したがって、集積回路パッケージ 392 のこの多セグメントの基板トレース（これは、本文ではブリッジ集積回路パッケージ（“ブリッジ I C”）と呼ぶ）は、ダイレクトコネクト・ケーブル 203A と 203B との間のブリッジを形成し、そして一緒にになると、ダイレクトコネクト・ケーブル 203A および 203B の導体と集積回路パッケージ 392 の多セグメント・トレースとは、集積回路パッケージ 391, 392 および 393 の各々間の連続した信号経路を形成する。この信号経路は、集積回路パッケージ 392 のダイ・パッドに対し、回路ボード・ルーティング形信号経路において通常存在する長いスタブ接続なしで、接触し、多くの多ドロップ形信号システムを悩ます寄生容量および信号反射は実質的に低減される。尚、任意の数のブリッジ用 I C を信号システム 390 に含めることもできる。また、ブリッジ I C 392 は、図示した反対側のエッジ上ではなく、隣接するエッジ上のダイレクトコネクト・コンタクト・ゾーンを含むこともできる。信号システム 390 は、マスター / スレーブ・システム（この場合、スレーブ・デバイスは、マスター・デバイス（例えば、メモリ・コントローラとスレーブ・メモリ・デバイス）からのコマンドまたは要求に応答してダイレクトコネク

50

ト・信号経路へ信号を駆動する)としたり、ピア・ツー・ピアの信号システム(この場合、集積回路パッケージのうちの任意のもの(またはその部分集合)が、信号経路の制御を得て、それ自身の意志に基づいて信号経路へ信号を出力する)としたり、もしくは、多ドロップ形動作が望まれる任意の他の信号システムとしたりできる。他の実施形態においては、ブリッジIC392は、2つより多いダイレクトコネクト・コンタクト・ゾーンを含むことができ(各コンタクト・ゾーンに延在する1組のトレース・セグメントを伴う)、これにより、1つより多い多ドロップ形信号経路がブリッジIC392により確立されるのを可能にしたり、あるいはブリッジIC392がハブ・デバイスを構成するスター・トポロジーを可能にしたりするようにできる。

## 【0020】

10

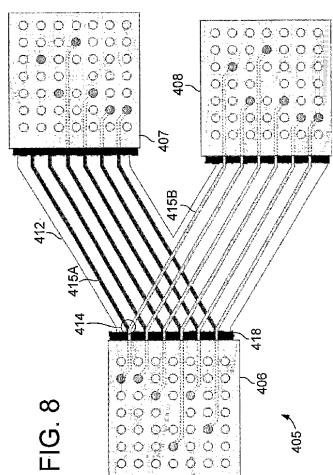

図8は、代替のダイレクトコネクト信号システム405を示しており、これは、多ドロップ形信号経路を確立するのに使用する。パッケージ基板上の多セグメント・トレースを通して多ドロップ形ルーティングを確立するのではなく、2組の導体415Aおよび415Bをダイレクトコネクト・ケーブル・アセンブリ412内に設け、そして各組の導体は、中間の集積回路パッケージ406と、エンド・ポイントの集積回路パッケージ407, 408のそれぞれとの間に結合する。組415Aの導体は、組415Bの導体にそれぞれ結合して、エンド・ポイントのパッケージ407, 408間に延在する多ドロップ信号経路を確立し、また中間パッケージ406に結合される。1実施形態においては、それら導体組は、コネクタ418内で互いに結合(例えば、ハンダ・ジョイント、圧力コントラクトまたは他の導電性結合を介して接続)することにより、各対の導体間にYジョイント414を形成する。代替の実施形態においては、導体415A, 415Bは、コネクタ418においてではなく、それらの長さに沿った点において互いに結合することもできる。また、代替の実施形態では、2つより多い組の導体をダイレクトコネクト・ケーブル・アセンブリ412内に含めることができ、そして互いに結合することによって、任意の数の追加の中間集積回路パッケージに対する接続を(例えば、各々の追加の中間集積回路パッケージにおいてYジョイント414を使用することにより)可能にすることができる。

20

## 【0021】

20

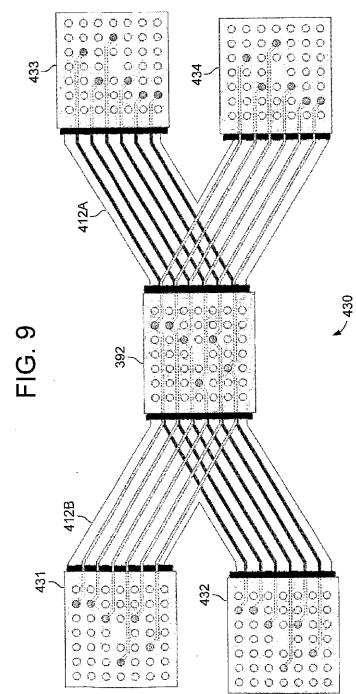

図9は、スター・タイプのインターロネクト・トポロジー430を示しており、これは、図8の1対のダイレクトコネクト・ケーブル・アセンブリ(すなわち、アセンブリ412Aおよび412Bと図7のブリッジIC392とを使用して実現する。ブリッジIC392は、スター・トポロジーのハブ・デバイスを構成し、そしてこれは、エンド・ポイントの集積回路パッケージ431, 432, 433および434の各々に結合する。このため、図7, 図8および図9の例から見られるように、事実上任意の高速のインターロネクト・トポロジーを、図6および図7で説明したダイレクトコネクト・ケーブル・アセンブリおよびブリッジICの一方または双方を使用して実現することができる。

30

## 【0022】

30

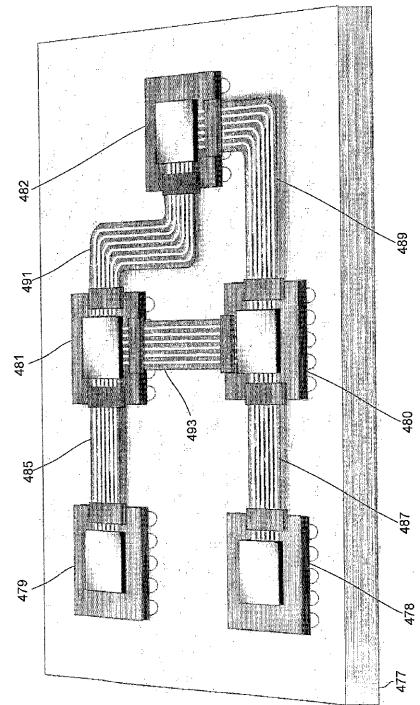

図10は、ダイレクトコネクト信号経路485, 487, 489, 491, 493の例示の配置を示しており、これらは、プリント回路ボード477上の装着した多数の集積回路パッケージ(478, 480, 481および482)の間に確立する。種々の他のコンポーネント(図示せず)も、プリント回路ボード477に装着し、そして在来の相互接続構造を使用してまたは追加のダイレクトコネクト・ケーブルを使用して、互いに相互接続したりあるいは集積回路パッケージ478-482へ相互接続したりまたはその双方を行うようにすることができる。図示したように、集積回路パッケージ478-482間に信号経路を確立するのに使用するそれらダイレクトコネクト・ケーブルは、直線のケーブル485, 487および493、Sタイプのケーブル491およびエルボーフォームケーブル489を含んでいる。任意の他の数の湾曲部または形状をもつケーブルも、使用することができる。また、コプレーナのケーブルを図示したが、他のケーブル幾何形状を使用することもできる(例えば、同軸ケーブル)。集積回路パッケージ481は、ブリッジICとして、ダイレクトコネクト・ケーブル485, 491および493のすべてまたはその1対間にスルーリード接続を確立することができる。代替的には、ダイレクトコネクト・ケーブル48

40

50

5, 491 および 493 は、各々、集積回路パッケージ 481 内の別個の組の I/O 回路に結合することもできる。集積回路パッケージ 480 および 482 は、同様にブリッジ IC とすることによって、ダイレクトコネクト・ケーブル間にスルー接続を確立することもできる。尚、集積回路パッケージ間の高速のシグナリングが必要とされる事実上任意のタイプのシステムに対し、図 10 に示したダイレクトコネクト信号経路を適用したり、あるいは適用のため修正することができる。例えば、データ処理システムにおける集積回路パッケージ間（例えば、汎用または専用のプロセッサと対応するチップセット・コンポーネントまたは特定用途向け集積回路との間、またはメモリ・コントローラとメモリ・デバイスおよびメモリ・モジュールの一方または双方との間）、ネットワーク・スイッチング・システム間の集積回路パッケージ間（例えば、1つ意序のライン・カード、スイッチ・ファブリック・カード等上の集積回路パッケージ間）、高速データ多重化システム等の集積回路パッケージ間において、ダイレクトコネクト・ケーブルを使用して接続を確立することができる。

10

### 【0023】

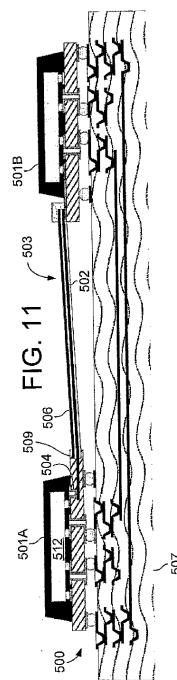

図 11 は、本発明の代替の実施形態によるダイレクトコネクト信号システム 500 を示している。信号システム 500 は、1 対の集積回路パッケージ 501A および 501B を備えており、これらは、プリント回路ボード 507 に装着され、そしてダイレクトコネクト・ケーブル 503 を介して互いに結合されている。図 3 のダイレクトコネクト・ケーブル 203 とは対照的に、ダイレクトコネクト・ケーブル 503 は、両端にコネクタを含んでおらず、むしろ集積回路パッケージ 501A の一体的なコンポーネントである。図示の実施形態では、ダイレクトコネクト・ケーブル 503 は、パッケージ基板 509 のエッジ（例えば、パッケージ基板 509 の上側表面と下側表面との間に形成された凹部）内に受け、そしてダイレクトコネクト・ケーブル 503 の電気信号導体 502 は、基板 509 内を（例えば、基板の内部の層の表面に沿って）延在することにより、集積回路ダイ 512 に結合された 1 組のビア 504 またはその他の導電性構造に接触する。代替的には、ダイレクトコネクト・ケーブル 503 の導体 502 は、パッケージ基板 509 の上面に沿って延在することができ、これにより、ダイ 512 に直接接觸することもできる（ビア 504 を不要にする）。さらに別の実施形態では、ダイレクトコネクト・ケーブル 503 の導体 502 は、パッケージ基板 509 の底面に沿って延在し、そしてパッケージ基板 509 内に配置したビアまたはその他の導電性構造を通してダイ 512 と接觸するようである。

20

図 3 のダイレクトコネクト・ケーブル 203 の場合と同じように、ダイレクトコネクト・ケーブル 503 は、フレキシブルあるいはリジッドのものとしたりでき、またマイクロ・ストリップライン（すなわち、導電性シールド 506 を有する）、コプレーナのストリップライン、あるいは非コプレーナのケーブル（例えば、同軸またはその他の非コプレーナの構成）とすることもできる。

30

### 【0024】

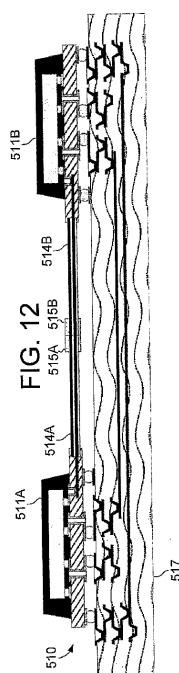

図 12 は、信号システム実施形態 510 を示しており、これは、集積回路パッケージ 511A, 511B を備えていて、これらは、プリント回路ボード 517 に装着され、そして各々、一体的なダイレクトコネクト・ケーブル 514A, 514B を有し、これらは、それぞれ中間スパン・コネクタ 515A, 515B において終端している。1 実施形態においては、中間スパン・コネクタ 515A, 515B は、互いに異なっており、そして中間スパン・コネクタ 515A は、中間スパン・コネクタ 515B の突出コンタクトを受けるように構成されている（すなわち、オス / メス・コネクタ対）。代替の実施形態においては、中間スパン・コネクタ 515A, 515B は、互いに同一のものであり、そしてこれらは、ラッチ構造を含むことによって、ケーブル 514A, 514B 内のそれぞれの組の導体を、互いに整列したコンタクト状態で維持する。中間スパン・コネクタ 515A, 515B は、恒久的にあるいは取り外し可能に互いに結合するようにすることができる。図 11 の実施形態と同じように、ダイレクトコネクト・ケーブル 514A, 514B の一方または両方における導体は、全体的にあるいは部分的に、対応するパッケージ基板内において延在するようにしたり（図示）、あるいはそのいずれかの表面上で延在するよう 40

50

したりできる。また、ダイレクトコネクト・ケーブル 514A, 514B は、フレキシブルあるいはリジッドのものとしたりでき、またマイクロ・ストリップライン（すなわち、導電性シールド 506 を有する）、コプレーナのストリップライン、あるいは非コプレーナのケーブルとすることもできる。

#### 【0025】

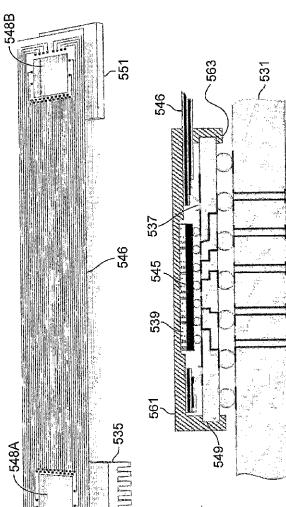

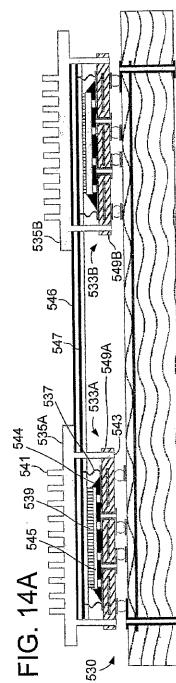

図 13 は、本発明の別の実施形態によるダイレクトコネクト信号システム 512 を示している。信号システム 512 は、集積回路パッケージ 522A, 522B を含んでおり、これらは、互いにダイレクトコネクト・ケーブル 523 を介して結合されており、そしてこのケーブルは、その長さの全体あるいは一部に沿ってプリント回路ボード 527 上に載置されている。ダイレクトコネクト・ケーブル 523 は、好ましくは、コプレーナの構造のものであって、複数の並列の導体を有しているが、しかしこれは、代替的には、同軸または他の非コプレーナのケーブルとすることもできる。また、このダイレクトコネクト・ケーブルの導体 525 は、パッケージ基板 526 の下側にあるランド 524A または他の導電性の構造に直接接触したり、あるいは、図 13 に示したように、在来のインタークネクト構造、例えばコンタクト・ボール 528（例えば、BGA のコンタクト・ボール）、コンタクト・スプリング等によって集積回路パッケージに結合するようにしたりできる。この構成により、ダイレクトコネクト・ケーブル 523 を従来通りに製作された集積回路パッケージ（図 13 に示したフリップチップ・パッケージ 522A, 522B、またはダイレクトコネクト・ケーブル 523 内の導体と接触するためのリードまたは他のコンタクトを有する集積回路パッケージ）と共に使用することができる。集積回路パッケージ内の信号再分配に関連する上述の問題は、図 13 の実施形態では依然として存在することがあるが、PCB ルーティングに関連する寄生容量、信号反射および信号スキューは、相当低減され、これによって、より高い信号レートを可能にし、プリント回路ボード 527 におけるルーティング密集を軽減することができる。ダイレクトコネクト・ケーブル 523 の導体 525 は、好ましくは、低ロスの誘電体材料の層 529 によってプリント回路ボードから電気的に分離され、これにより、プリント回路ボード 527 の上面にプリントされたあるいは他の方法で形成された導電性トレースを、ケーブルの下側でルーティングできるようになる。図 3、図 9 および図 10 を参照して上述したダイレクトコネクト・ケーブルの場合と同じように、ダイレクトコネクト・ケーブル 523 は、好ましくは、フレキシブルのものとし、これによりこのケーブルが、プリント回路ボード 527 に装着された他のコンポーネント（例えば、集積回路パッケージ 522A, 522B の間に配置された他の集積回路デバイスまたは回路コンポーネント）の上へそしてその上（及び／またはその周り）をルーティングできるようになる。代替的には、ダイレクトコネクト・ケーブル 523 は、リジッドのものとすることもできる。また、ダイレクトコネクト・ケーブル 523 は、システム・アセンブリの間にプリント回路ボード 527 に固着したり（例えば、接着剤または締結部材を使用）、あるいはプリント回路ボード 527 上に固着せずに載置されるようにしたりできる。

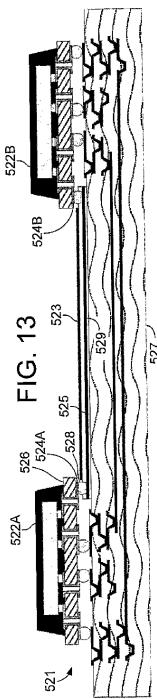

#### 【0026】

図 14A～図 14C は、本発明の別の実施形態によるダイレクトコネクト信号システム 530 を示している。先ず、図 14A を参照すると、ダイレクトコネクト・ケーブル 546 は、回路ボード 531 に装着された集積回路パッケージ 533A, 533B の間に延在し、そしてこれは、リッド・コンポーネント 535A, 535B のそれぞれの 1 つにより各パッケージ 533 に固着されている。1 実施形態においては、スプリング・タイプのコンタクト 537 は、ダイレクトコネクト・ケーブル 546 から延在して、パッケージ基板 549A, 549B の表面に配置されたトレースと接触する（例えば、図 4A～図 4C で説明したのと同じ）。他のケーブル・パッケージ相互接続の構造および技術は、代替の実施形態において使用することもでき、その代替の実施形態では、限定する訳ではないが、図 6 で上述したコンタクトの構造および技術を含んでいる。図 14A の実施形態においては、リッド・コンポーネント 549 は、熱伝導材料から形成され、そしてこれは、パッケージ・ハウジング 544 の上面と接触した状態で配置されたヒート・シンク構造 541（

10

20

30

40

50

例えば、フィン)を含んでいる。熱伝導性材料539(または接着剤)を使用することもでき、これによって、集積回路パッケージ533からリッド・コンポーネント535への熱伝導を向上させることができる。

#### 【0027】

1実施形態においては、図14Bに示したように、ダイレクトコネクト・ケーブル546の個々の導体547は、集積回路ダイ・ハウジング544にしたがってサイズを決めたケーブル546内の開口548A, 548Bの周囲にルーティングし、これによって、パッケージ・ハウジング544とリッド・コンポーネント535との間のより直接的な接続を可能にする。代替的には、その開口を省略し、そして導体547を、パッケージ・ハウジングの上面の上に直接ルーティングするようにすることもできる。ヒート・シンク構造541は、リッド・コンポーネント535と区別したものとしたり、あるいは代替の実施形態においては、それらを一緒に省略することができる(例えば、図14Bの551で示す)、そしてリッド・コンポーネント535を、熱伝導性材料以外の材料から形成することもできる。

#### 【0028】

図14Aの実施形態においては、リッド・コンポーネント535は、突出部材543を含み、これは、パッケージ基板549内の対応する孔またはスロット内へ延在することにより、リッド・コンポーネント535を基板549に固定する。図14Cを参照すると、リッド・コンポーネント561は、代替的には、パッケージ基板549に部材563によって固着することもでき、そして部材563は、パッケージ基板549の外側エッジに周りにスナップして、リッド・コンポーネント561を基板549の上側表面および下側表面に対し固着する。このような実施形態においては、ハウジングを省略し、そして熱伝導材料を、集積回路ダイ545とリッド・コンポーネント561との間に直接配置するようになることもできる。詳しくは、リッド561(または535)とダイレクトコネクト・ケーブル546を集積回路パッケージ533に固着するための任意の機構または材料を、本発明の要旨および範囲から逸脱せずに使用することもできる。

#### 【0029】

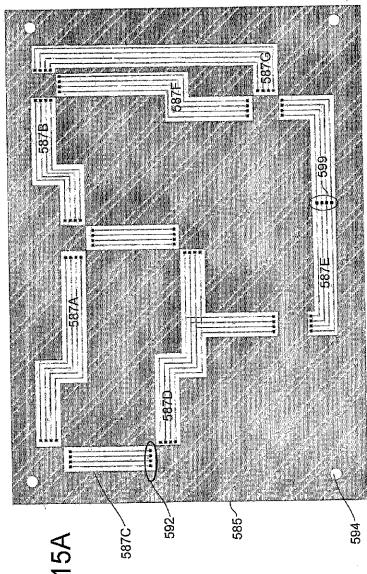

図15Aおよび図15Bは、本発明の別の実施形態によるダイレクトコネクト信号システム580を示している。ディスクリートのダイレクトコネクト・ケーブルではなく、ダイレクトコネクト信号経路587A-587Gをスーパー構造585内に配置し、このスーパー構造585は、プリント回路ボード581に対し、集積回路パッケージ583A~583Nの上面の上で装着されている(尚、図15Bのプロファイル図では、ダイレクトコネクト信号経路587Aおよび587Bのみを示している)。図15Bの実施形態においては、ポスト591は、プリント回路ボード581に固着され、またスーパー構造585の孔594内に受けられて、これにより、スーパー構造585とプリント回路ボード581を整列させる。その他の整列技術も、代替の実施形態においては使用することができる。

#### 【0030】

ダイレクトコネクト信号経路587は、スーパー構造585上にプリントしたまたはその他の方法で配置した導電性トレースにより形成したり、あるいは、図3~図14で説明したダイレクトコネクト・ケーブルの1つまたはそれ以上をスーパー構造585の表面上に固着することにより形成することもできる。いずれの場合でも、コンタクト構造589を設けることによって、ダイレクトコネクト信号経路の端子592と、集積回路パッケージ583の基板上に配置されたコンタクトとの間にコンタクトを確立する。図15Bにおいては、コンタクト構造589を、突出フィンガ・タイプのコンタクトとして示したが、他のタイプのコンタクト構造も使用することができ、それには、限定する訳ではないが、図6で説明したコンタクト構造が含まれる。図15Aを参照すると、これら分かるように、ダイレクトコネクト信号経路587A~587Gは、多ドロップ信号構造487Dおよび587Eだけでなく、集積回路パッケージ間のポイント・ツー・ポイントのリンク587A, 587B, 587C, 587Fおよび587Gを形成することができる。多ドロップ

構造 587E を特に参照すると、分かるように、コンタクト領域 599 は、信号経路 587E の長さに沿った 1 点において配置され（すなわち、両端とは異なる）、これにより、コンタクト領域 599 内の各コンタクトからコンタクト構造 589 とパッケージ基板トレースとの組み合わされた長さまで延在するスタブを制限する。尚、このような中間スパン・コンタクトは、本文に記述した他のダイレクトコネクト・ケーブルと共に使用することができ、これにより、図 7 で説明したプリッジ IC382 あるいは図 8 で説明したケーブル・アセンブリ 412 を必要とせずに、多ドロップ信号経路を確立することができる。また、ダイレクトコネクト・信号経路 587A ~ 587G のコンタクトと集積回路パッケージ 583 上の対応するコンタクトとの間に細かな配列を容易にするため、アパートチャを、スーパー構造 585 においてコンタクト・ポイント 592 の上に設けることもできる。

10

### 【0031】

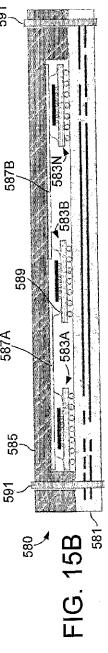

図 16A および図 16B は、ダイレクトコネクト信号システム 610, 625 をそれぞれ示しており、これらは、図 3 および図 9 ~ 図 12 に示したフリップチップ・パッケージではなくあるいはそれらフリップチップ・パッケージと組み合わせて、リード付きの集積回路パッケージを含んでいる。図 16A を参照すると、ダイレクトコネクト・ケーブル 617 は、リード付き集積回路パッケージ 613 および 645 の上を延在し、そしてソケット 614 および 616 により集積回路パッケージに固着されている。すなわち、ソケット 614 は、集積回路パッケージ 613 の周りに配置し、そしてこれは、導電性部材 618A を含んでいて、この部材は、それぞれのケーブル接続ポイント 612A から集積回路パッケージ 613 の対応するリード 621 まで延在している。同様に、ソケット 616 は、集積回路パッケージ 615 の周りに配置し、そしてこれは、導電性部材 618B を含んでいて、この部材は、それぞれのケーブル接続ポイント 612B から集積回路パッケージ 615 の対応するリード 622 まで延在している。ケーブル内の導体 619A ~ 619N は、導電性部材 618 をもつ各対のコンタクト 620 間に延在する。上述のダイレクトコネクト・ケーブルの場合と同じように、ダイレクトコネクト・ケーブル 617 は、好ましくは、フレキシブルのものとして、集積回路パッケージ 613 および 615 が互いに異なった異なった位置および向きで配置されるときに、これらパッケージの相互接続を可能にする。代替的には、ダイレクトコネクト・ケーブル 617 は、リジッドのものとすることもできる。また、このダイレクトコネクト・ケーブルは、マイクロ・ストリップライン、コプレーナのストリップライン、あるいは非コプレーナのケーブルとすることもできる。最後に、集積回路パッケージ 613 および 615 は、ガルティング・リード付きまたは J リード付きのパッケージとして図示したが、他のタイプのリードをもつパッケージを代替の実施形態において使用することもできる。

20

### 【0032】

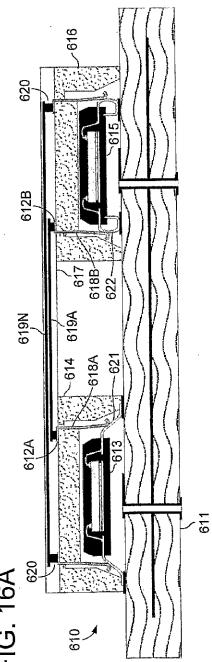

図 16B において、ダイレクトコネクト・ケーブル 635 を使用することにより、フリップチップ集積回路パッケージ 626 とリード付きパッケージ 627 とを相互接続する。フリップチップ・パッケージ 626 は、概して図 3 を参照して説明したように実現し、そして導電性トレース 629 は、パッケージ基板 628 の表面に沿ってルーティングして、基板 628 の露出した領域にあるゾーンに接触させる。導電性構造 630 は、トレース 629 と接触する状態で配置し、そしてこれは、このパッケージ・ハウジングの表面に沿ってこのハウジングの上面まで延在する。コンタクト 631（例えば、ハンダ・ボールまたはその他の構造）を設けることにより、構造 630 とダイレクトコネクト・ケーブル 635 の導体 632A ~ 632N との間の電気的接続を行う。リード付きパッケージ 627 では、導電性構造 642 は、同様にパッケージ・リード 641 からパッケージ・ハウジングの上面へ延在し、そしてその上面で、コンタクト 643 を使用してダイレクトコネクト・ケーブル 635 の導体 632A ~ 632N との電気的接続を行う。代替の実施形態においては、フリップチップ・パッケージ 626 は、図 3 ~ 図 14 で上述した接続技術および構造の任意のものを使用して、ダイレクトコネクト・ケーブル 635 に結合することもできる。同様に、リード付きパッケージ 627 は、図 16A で説明したソケット構成を使用してダイレクトコネクト・ケーブル 635 に結合することもできる。さらに、図 15A およ

30

40

50

び図15Bで説明したダイレクトコネクト・スーパー構造585は、図16Aおよび図16Bに示したディスクリートのダイレクトコネクト・ケーブル617および635の代わりに使用することもできる。

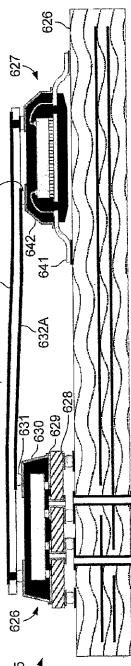

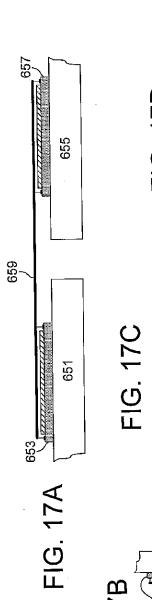

### 【0033】

図17A～図17Fは、追加のダイレクトコネクト信号システムの実施形態を示している。先ず図17Aを参照すると、集積回路パッケージ653および657は、別個のプリント回路ボード651および655にそれぞれ装着しており、そしてダイレクトコネクト・ケーブル659を介して互いに結合している。プリント回路ボード651および655は、互いに任意に位置決めし、そして任意の許容可能なシグナリング距離で分離するようになることができる。プリント回路ボード651および655は、追加の集積回路パッケージを有することができ、そしてこれらは、1つ以上の他のダイレクトコネクト・ケーブルを通して互いに結合するか、あるいは図7で説明した多ドロップ構成で結合することができる。また、ダイレクトコネクト・ケーブル659は、図8で説明した多数の組の導体を含むことができ、これにより、それら2つのプリント回路ボード651および655上の多数の集積回路パッケージの相互接続を可能にする。

10

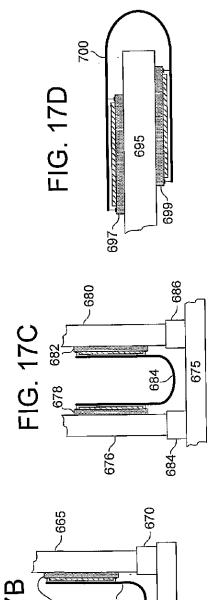

### 【0034】

図17Bは、ダイレクトコネクト信号システムを示しており、これにおいては、マザーボードまたはバックプレーン661上に装着された集積回路パッケージ663は、ドーターボード665上に装着した集積回路パッケージ667に対しダイレクトコネクト・ケーブル669を介して結合する（すなわち、プリント回路ボードは、マザーボードに対しコネクタ670または類似の構造を介して取り外し可能に結合される）。図17Cは、別のダイレクトコネクト信号システムを示しており、これにおいては、集積回路パッケージ678および682は、それぞれのドーターボード676および680に装着され、またダイレクトコネクト・ケーブル684を介して互いに結合されている。ドーターボード676および680は、バックプレーンまたはマザーボード675のそれぞれのコネクタ684および686内へ取り外し可能に挿入される。図17Bおよび図17Cの信号システムの例示的な応用例には、これに限定する訳ではないが、ネットワーク・スイッチング装置（例えば、スイッチまたはルータ）内のバックプレーンに挿入されるライン・カードまたは他のカード、コンピューティング・デバイスまたはコンシューマ電子デバイス等のマザーボードまたはバックプレーンに挿入されるメモリ・モジュールが含まれる。

20

### 【0035】

図17Dは、さらに別のダイレクトコネクト信号システムを示しており、これにおいて、集積回路パッケージ697および699は、プリント回路ボード695または他の基板の対向する側に装着し、そしてこれらは、ダイレクトコネクト・ケーブル700を介して互いに結合する。図17Aの信号システムの場合と同じように、図17B～図14Dで示した実施形態の各々は、ダイレクトコネクト・ケーブルで互いに結合した追加の集積回路パッケージを含むことができ、また、ダイレクトコネクト・ケーブル669, 684および700は、図7で説明した多数の組のコネクタを含むことができ、これによって多数の集積回路パッケージの相互接続を可能にすることができる。

30

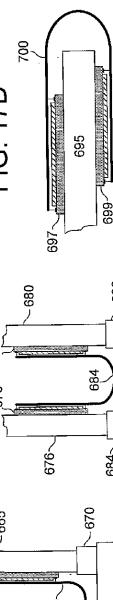

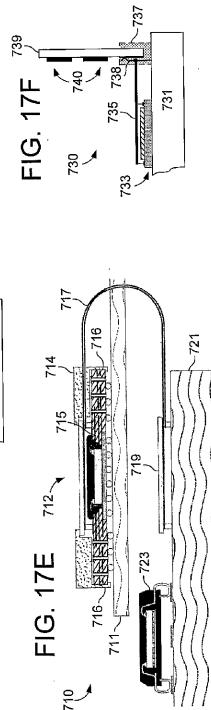

### 【0036】

図17Eは、本発明の別の実施形態による信号システム710を示している。信号システム710は、第1の集積回路パッケージ712を含み、これは、プリント回路ボード711に装着され、そしてボンド・ワイヤ715または他のコンタクト構造を介してダイレクトコネクト・ケーブル・アセンブリ717の導体に結合されている。その他のボンド・ワイヤを使用することもでき、これにより、集積回路パッケージ712の下面上のハンダ・ボールまたは他のコンタクトに対し、集積回路ダイを結合することができる。ダイレクトコネクト・ケーブル・アセンブリ717は、締結部材716をもつリッド・コンポーネント714を含み、これにより、このアセンブリ717を集積回路パッケージ712に固着する。また、このダイレクトコネクト・ケーブル・アセンブリは、コネクタ719を含み、これにより、ケーブル・アセンブリ717の遠い方の端部を別のプリント回路ボード

40

50

721に固着し、またケーブル・アセンブリ717の導体をプリント回路ボード721上に配置したトレースに結合する。このプリント回路ボード・トレースは、別の集積回路パッケージ723のリード（または他のコンタクト）に結合し、これにより、集積回路パッケージ712と723との間の高速信号経路を完成させる。このように、システム710の高速信号経路全体は、ハイブリッド経路であって、集積回路パッケージ712へのダイレクトコネクト・ケーブル接続と、集積回路パッケージ723への在来の接続とを有している。ケーブル・ボード・コネクタ719は、プリント回路ボード721に対し恒久的にあるいは取り外し可能に結合することができる。

#### 【0037】

引き続き図17Eを参照すると、理解されるべきであるが、集積回路パッケージ712は、代替的には、図3～図13で説明したタイプの集積回路パッケージのうちの任意のものとすることができる、また図3～図13で説明したケーブル接続のうちの任意のものを有するようである。同様に、集積回路パッケージ723は、Jリード付き表面実装集積回路パッケージとして示したが、任意の他のタイプの集積回路パッケージを代替の実施形態において使用することもできる。また、ダイレクトコネクト・ケーブル・アセンブリ717は、たった1つの集積回路パッケージ712に結合したものとして示したが、このケーブルは、図6および図7で上述したように1つまたはそれより多い追加のパッケージに結合することもできる。さらに、集積回路パッケージ712および723は、図17Eに示した別個の回路ボード711および721ではなく、同じ回路ボード上に装着することもできる。

10

20

30

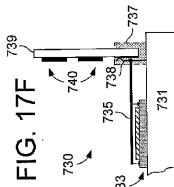

#### 【0038】

図17Fは、本発明の別の実施形態による信号システム730を示している。信号システム730は、第1の集積回路パッケージ733を含み、これは、プリント回路ボード731に装着され、またダイレクトコネクト・ケーブル735に結合されている。しかし、もう1つの集積回路パッケージに結合する代わりに、ダイレクトコネクト・ケーブル735の導体は、集積回路ボード・コネクタ737内の端子738に結合されている。1実施形態においては、集積回路ボード・コネクタ737は、ソケット・スタイルのコネクタであり、これは、他のコンポーネント740が上に配置されたプリント回路ボード739（例えば、ライン・カード、メモリ・モジュール等）のエッジ・コネクタを受けるように構成されている。代替の実施形態においては、他のタイプのコネクタを、コネクタ737の代わりに使用することもでき（例えば、ドーター・ボード上のメス・コネクタに挿入するように構成したピン拡張部）、そしてダイレクトコネクト・ケーブル735は、コネクタ737に対し恒久的にまたは取り外し可能に結合することもできる。また、コネクタ737は、代替的には、プリント回路ボード731の集積回路パッケージ733とは反対の側に装着したり、あるいは全く別のプリント回路ボード上に装着することもできる。集積回路パッケージ733は、代替的には、図3～図16で説明したタイプの集積回路パッケージのうちの任意のものとしたり、またそれら図で説明したダイレクトコネクト・ケーブル接続のうちの任意のものを有するようにすることができる。

40

#### 【0039】

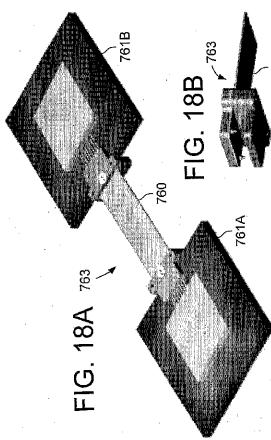

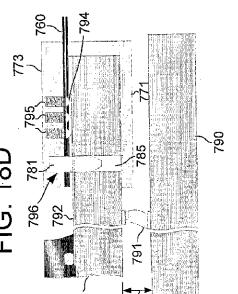

図18A～図18Dは、例示的なコネクタ・システム763を示しており、これは、集積回路パッケージ761Aと761Bとの間ににおいて、または集積回路パッケージ761とプリント回路ボード（メモリ・モジュールのようなモジュールを含む）との間ににおいて、ダイレクトコネクト・ケーブル接続を確立するのに使用することができる。先ず、図18Aおよび図18Bにおいては、接続は、“クラム・シェル（clam shell）”状のコネクタ・システム763により行い、これは、伝送ケーブル760を、プレーナのインラインまたはアレイのコンタクトにより、相互接続コンポーネントのエッジに整列させしっかりホールドする（例えば、集積回路パッケージ761の基板またはプリント回路ボードまたはモジュール）。

50

#### 【0040】

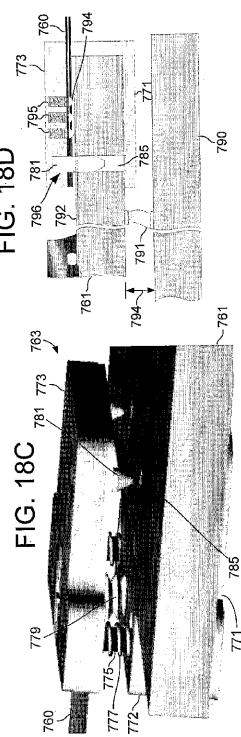

図18Cにより詳細に示した実施形態においては、クラム・シェル接続システム763

50

は、以下のものを含んでいる。すなわち、平らなクラムシェル・コネクタ773の上部リップ（電気的接続を基板の上面においてのみ作るべき用途のため）と、インターロネクト・コンポーネント761の基板の厚さのスペーサ772を含むクラムシェル・コネクタ771の底部リップと、インターロネクト・コンポーネント761上に配置された導体（図18Dに792で示す）との間で電気信号を運び、またケーブル760の導体またはインターロネクト・コンポーネント761の導体のいずれかにある盛り上がり表面または突出構造（すなわち、端子として作用）を通して接続を行うフレックスの回路／伝送ケーブル760と、インターロネクト・コンポーネント761のコンタクト端子に対するダイレクトコネクト・ケーブルの位置合わせを確実に行い、また機械的なアンカーを提供して衝撃または振動により意図しないプルオフを防止する位置合わせピン781と、コネクタ771と773の上部リップと底部リップが、これらがz方向に動くときに互いに位置合わせ状態を保持できるようにするガイド・ピン775（代替の実施形態ではより多いまたはより少ないガイド・ピンを設けることもできる）と、コネクタの各半部を挿入に対してあるいは取り外しが必要なときは取り外しに対して互いに離れる方向に偏倚させるスプリング777と、クラムシェル771, 773の上部リップと底部リップを、インターロネクト・コンポーネント761の対応する表面に対し物理的にクランプする締結機構779（例えば、ネジ、または他の閉止力伝達デバイス）とである。ここで、インターロネクト・コンポーネント（例えば、集積回路パッケージ基板、プリント回路ボードまたはモジュール等）は、位置合わせピン781を受けるような形状にした、孔またはスロットのような凹部区域を含んでいる。図18Bおよび図18Cにおいては2つの位置合わせピン781を示しているが、代替の実施形態においては、それより多いまたは少ない位置合わせピン781を設けることもできる。尚、スペーサ772がインターロネクト・コンポーネント761のエッジに当接してインターロネクト・コンポーネント761に向かって延びる方向における位置合わせを制御するように、クラムシェル・コネクタ・システム763を設計する場合、単一の位置合わせ孔を使うこともでき、これによって、インターロネクト・コンポーネント761のエッジに沿った横方向における位置合わせを確立することができる。また、ピンではなく、長手方向の突起（例えば、フィンまたはブレード）あるいは他の突起幾何形状を使用することができ、これにより、コネクタ・システム763とインターロネクト・コンポーネント761の間の位置合わせを確立することができ、そしてインターロネクト・コンポーネント761内の凹部区域785（例えば、孔、チャンネル、溝等）は、その突起幾何形状にしたがった形状とする。位置合わせピン781は、コネクタ・システム763のリップ771および773の一方または両方に配置することもできる。また、これら位置合わせピンは、代替的には、インターロネクト・コンポーネント761上に配置することができ、そして凹部区域785をリップ771および773の一方または両方に配置することもできる。

#### 【0041】

続けて図18Cを参照すると、コネクタ・システム763の喉部（すなわち、リップ771および773のインターロネクト・コンポーネント761より上への延長）の深さは、重要ではないが、より薄いスペーサ772が使用される場合、より浅い喉部は剛性を向上させることができる。また、コネクタ771の底部リップは、上部リップ773と同じ深さのものとする必要はなく、したがって1実施形態では、より深い深さのものとする。上述したように、底部リップ771はまた、より大きな機械的堅牢性のために位置合わせピン781を含むこともできる。また、図18Dに示したように、コネクタの底部リップ771の厚さを、パッケージ基板とプリント回路ボード790との間の予期される隙間794よりも小さな値に減少させる（その隙間は、少なくとも部分的に、パッケージ・ボード間コンタクト791の性質により決まる）。コネクタの上部リップおよび底部リップ771および773は、任意の材料から形成することができ、そして導電性材料で作る場合、これらは、ケーブル760およびインターロネクト・コンポーネント761の一方または双方内のグランド基準（例えば、シールド層）に結合することもできる。1実施形態では、位置合わせピン781を使用することによって、インターロネクト・コンポーネント

761上またはインターフェクト・コンポーネント761内に配置されたグランド基準導体(またはグランド・プレーン)および電源電圧導体の一方または双方に係合するよう し、これにより、グランドおよび電源の一方または双方の接続を確立する。

【0042】

図18Dを参照すると、ケーブル760上に配置された電気コントラクト・ポイント794(例えば、パッド)とインターフェクト・コンポーネント761上の対応する導体792との間の位置合わせは、位置合わせピン781により確立する。1実施形態においては、インターフェクト・コンポーネント761内の位置合わせ孔785は、基板導体792の端部に対して指定した位置で穿孔する。この位置合わせピンのためのスルーホール796も、ケーブル760において、ケーブル・コントラクト794に対し指定した位置で穿孔する。コネクタ上部リップ773の位置合わせピン781が、ケーブル760のスルーホール796中に挿入されると、このコネクタがインターフェクト・コンポーネント761に閉じられるときに、ケーブル・コントラクト794は、導体792の端部に接触するように位置合わせされる。図18Cに示したように、位置合わせピン781の先端は、ピン781のセルフ・アライメントを可能にするため、先細とすることもできる。

【0043】

ダイレクトコネクト・ケーブル導体とインターフェクト・コンポーネント761状のトレース792との間に電気的コントラクトを確立するのに使用する構造は、これに限定する訳ではないが、金ドット、ナノピアス・コントラクト、ポゴピン、エラストマ・パッド、マイクロ・スプリング、メッキ・バンプ、粒子インターフェクト、異方性導電性フィルム等を含むことができる。異なったバンプ・コントラクト間の高さの共面性、特に高いピン・カウントに対するものは、任意の多くの技術を使用して実現することができ、それら技術には、これに限定する訳ではないが、ダイレクトコネクト・ケーブルとコネクタの上部リップとの間のエラストマをサンドイッチすること、および図18Dに示したようなダイレクトコネクト・ケーブル導体上の任意のバンプ・コントラクト794の背後のスプリング装荷コントラクト795の一方または双方が含まれる。

【0044】

図17Eおよび図17Fで上述したように、ダイレクトコネクト・ケーブルは、一端を集積回路パッケージにそして他端をプリント回路ボードまたは回路ボード(またはモジュール)コネクタに結合することができる。したがって、ダイレクトコネクト・ケーブルは、図18A～図18Dで説明したコネクタ・システム763を、一端にのみ含むことができる。このコネクタの他端は、プリント回路ボード(またはモジュール)への接続のため表面実装タイプまたはメザニン・タイプのコネクタを含むようにしたり、あるいは、例えば図17Fに示したようなボードまたはモジュールのコネクタのコントラクトへの接続に対し適合させるようにしたりできる。

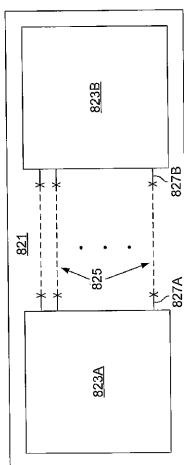

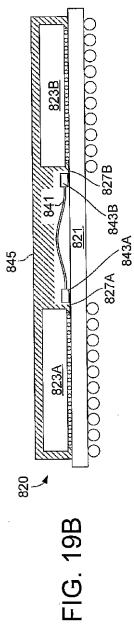

【0045】

図19Aおよび図19Bは、本発明の別の実施形態によるダイレクトコネクト信号システムを示している。図19Aは、集積回路パッケージ820の上面図であって、このパッケージは、共用のパッケージ基板上に配置された多数の集積回路ダイ823Aおよび823Bを有している(図19Aには、2つのダイを示しているが、他の実施形態では、任意の数のダイを設けることができる)。このような集積回路パッケージ(これは本文では多チップ・モジュール(MCM)と呼ぶ)においては、それらダイ823間の相互接続は、通常、共用基板821のトレースがプリントされた1つ以上の層により行われる。このアプローチに対する1つの欠点は、一旦基板821に実装すると、個々のダイ823の高速のテストが、1つ以上の他のダイ823への接続により困難となることである。他のダイ823が、ある場合には、高インピーダンスのノード(例えば、3状態にされたすべてのI/O回路)内に置かれことがあるが、このような他のダイ823への基板トレースは、高速シグナリング・テスト中はスタブとして作用する傾向があり、これは、信号品質を劣化させ、ランタイム周波数でのテストを困難にするかもしくは不可能とする。また、個々のダイは、ウエハ・プロービング技術を使ってテストすることもできるが、それらプロ

ープの比較的高いインダクタンスは、通常、ランタイム周波数でのテストを妨げる。その結果、多チップ・モジュールは、完全に組み立てられて、そしてその集積された形態でテストされることが多い。このアプローチでの問題は、多チップ・モジュール内のダイのうちの任意のものが欠陥であった場合、多チップ・モジュール全体が通常廃棄されることである。

#### 【0046】

本発明の1実施形態においては、多チップ・モジュールに関連するテスト容易性問題の多くは、ダイレクトコネクト・ケーブルを使用してダイ間に高速リンク（例えば、信号経路）を確立することにより、克服される（あるいは少なくとも軽減される）。したがって、図19Aにおける不連続部825（“x-----x”）により示すように、ダイ間の基板トレース接続は、不完全なまとまりされ、そして代わりとしてそれらトレースは、ダイレクトコネクト・ケーブル内の電気信号導体と接触するように構成したコンタクト・ゾーン（827A, 827B）において終端される。図19Bは、図19Aの配置の側面図であり、ダイレクトコネクト・ケーブル841の配置を示している。ダイレクトコネクト・ケーブル841は、1対のコネクタ843A, 843Bを含み、これらは、集積回路ダイ823A, 823Bのコンタクトから延在した各組のトレースにより確立されたコンタクト・ゾーン827A, 827Bに対し、恒久的にもしくは取り外し可能に固着される。この配置により、各ダイ823がパッケージ基板821に装着されると、高速回路テスタ（図示せず）は、ダイレクトコネクト・テスト・ケーブル（例えば、パッケージ・ダイ823を互いに相互接続するのに使用するケーブル841に対応したケーブル）を使って対応するコンタクト・ゾーン827に結合し、そしてランタイム周波数でテストすることができる。もしこのダイがテストに合格すると、別のダイをパッケージに装着し、そしてこの別のダイを、合格したダイの対またはグループ間にダイレクトコネクト・ケーブル841を結合した状態で、同様にテストする。もし1つのダイが、テストに合格しなかったとする、これを基板から取り外し、そして別のダイと交換する。あるいは、その部分的に組み立てたモジュールを廃棄することもできる。いずれにしても、個々のダイは、多チップ・モジュール全体の組立を完成させる必要なしで、ランタイム周波数でテストすることができる。尚、図19Aおよび図19Bに示した多チップ・モジュール820はプレーナ・スタイルのモジュール（すなわち、すべてのダイが、同一の平面、例えば、共通基板821の表面に装着されたもの）であるが、ダイレクトコネクト・ケーブルは、スタック形多チップ・モジュールの異なる平面に装着されたダイの間の高速信号経路を形成するにも使用することができる。

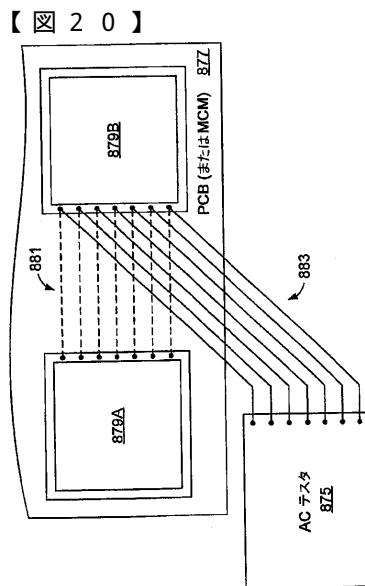

#### 【0047】

図20は、テスト配置を示しており、これは、ダイレクトコネクト・ケーブルを介して相互接続されるべき回路ボード実装した集積回路パッケージ879A, 879Bをテストするのに使うことができる。これと類似の配置を、ダイレクトコネクト・ケーブルを介して相互接続すべき多チップ・モジュールの基板上に装着されたダイをテストするのに使うことができる。点線881は、これから取り付けるべきダイレクトコネクト接続ケーブルの導体の経路を示し、883は、高速テスト装置（例えば、プログラムしたパターンのテスト信号を発生する装置）へのダイレクトコネクト・ケーブル取り付けを示している。集積回路パッケージ879A, 879B間の相互接続はまだ確立していないため、パッケージ879Aは、879Bをテストするために高インピーダンス状態に駆動される必要はない。また、プリント回路ボード877上のテスト・ポイントに接触するためにプローブを使用するボード・レベルのテストとは異なり、プリント回路ボード・トレースのスタブ部分からの寄生容量および信号反射は、回避され、これにより高速テスト装置がランタイム周波数でシグナリング・テストを実行できるようにする。パッケージ879Bをテストした後、集積回路パッケージ879Bへのダイレクトコネクト・ケーブル接続を取り外し、そして集積回路パッケージ879Aへのダイレクトコネクト・ケーブル接続を確立する。このように、ボード・レベルの集積回路パッケージ・テストを、ランタイム周波数で、一時に1つの集積回路パッケージにて実行することができる。ダイレクトコネクト・ケーブ

10

20

30

40

50

ルは、パッケージ・レベルのテストに合格したと判定した集積回路パッケージの各対（または集積回路パッケージのグループ）間に固着することができる。

【0048】

以上、本発明について特定の例示の実施形態を参照して説明したが、特許請求の範囲に記載した本発明の要旨および範囲から逸脱せずに、種々の修正、変更を行えることが明かである。したがって、本明細書および図面は、限定する意味でなく、例示として見なされるべきである。

【図面の簡単な説明】

【0049】

【図1】図1は、従来技術のフリップチップ集積回路パッケージを示す。 10

【図2】図2は、従来技術の信号システムを示す。

【図3】図3は、本発明の1実施形態によるダイレクト・コネクト形信号システムを示す。

【図4A】図4Aは、本発明の実施形態による集積回路パッケージの上面図を示す。

【図4B】図4Bは、本発明の実施形態による集積回路パッケージの上面図を示す。

【図4C】図4Cは、本発明の実施形態による集積回路パッケージの上面図を示す。

【図5A】図5Aは、本発明の実施形態によるダイレクトコネクト・ケーブルを示す。

【図5B】図5Bは、本発明の実施形態によるダイレクトコネクト・ケーブルを示す。

【図6】図6は、集積回路パッケージの基板上に配置されたトレースと、ダイレクトコネクト・ケーブル内の導体との間の電気的接続を確立するのに使用できるコンタクト技法を示す。 20

【図7】図7は、多ドロップ形信号システムを確立するため多数のダイレクトコネクト・ケーブルを介して互いに結合する、1組の集積回路パッケージを示す。

【図8】図8は、多ドロップ形信号システムを確立するのに使用する、ダイレクトコネクト・ケーブル・アセンブリを示す。

【図9】図9は、図8のダイレクトコネクト・ケーブル・アセンブリを使用して実現する、スター・タイプの相互接続トポロジーを示す。

【図10】図10は、プリント回路ボード上に装着された多数の集積回路パッケージ間で確立されるダイレクトコネクト信号経路の例示の配置を示す。

【図11】図11は、本発明の代替の実施形態によるダイレクトコネクト信号システムを示す。 30

【図12】図12は、信号システムの実施形態を示し、これは、複数の集積回路パッケージを含み、その各々が中間スパン・コネクタと一体のダイレクトコネクト・ケーブルを有する。

【図13】図13は、本発明の代替の実施形態によるダイレクトコネクト信号システムを示す。

【図14A】図14Aは、本発明の別の実施形態によるダイレクトコネクト信号システムを示す。

【図14B】図14Bは、本発明の別の実施形態によるダイレクトコネクト信号システムを示す。 40

【図14C】図14Cは、本発明の別の実施形態によるダイレクトコネクト信号システムを示す。

【図15A】図15Aは、本発明の別の実施形態によるダイレクトコネクト信号システムを示す。

【図15B】図15Bは、本発明の別の実施形態によるダイレクトコネクト信号システムを示す。

【図16A】図16Aは、リード形集積回路パッケージを含むダイレクトコネクト信号システムを示す。

【図16B】図16Bは、リード形集積回路パッケージを含むダイレクトコネクト信号システムを示す。 50

【図17A】図17Aは、追加のダイレクトコネクト信号システムの実施形態を示す。

【図17B】図17Bは、追加のダイレクトコネクト信号システムの実施形態を示す。

【図17C】図17Cは、追加のダイレクトコネクト信号システムの実施形態を示す。

【図17D】図17Dは、追加のダイレクトコネクト信号システムの実施形態を示す。

【図17E】図17Eは、追加のダイレクトコネクト信号システムの実施形態を示す。

【図17F】図17Fは、追加のダイレクトコネクト信号システムの実施形態を示す。

【図18A】図18Aは、例示的なコネクタ・システムを示し、これは、各集積回路パッケージ間に、または集積回路パッケージとプリント回路ボードとの間に、ダイレクトコネクト・ケーブル接続を確立するのに使用することができる。

【図18B】図18Bは、例示的なコネクタ・システムを示し、これは、各集積回路パッケージ間に、または集積回路パッケージとプリント回路ボードとの間に、ダイレクトコネクト・ケーブル接続を確立するのに使用することができる。 10

【図18C】図18Cは、例示的なコネクタ・システムを示し、これは、各集積回路パッケージ間に、または集積回路パッケージとプリント回路ボードとの間に、ダイレクトコネクト・ケーブル接続を確立するのに使用することができる。

【図18D】図18Dは、例示的なコネクタ・システムを示し、これは、各集積回路パッケージ間に、または集積回路パッケージとプリント回路ボードとの間に、ダイレクトコネクト・ケーブル接続を確立するのに使用することができる。 20

【図19A】図19Aは、本発明の1実施形態による多チップ・モジュール内のダイレクトコネクト・シグナリングを示す。

【図19B】図19Bは、本発明の1実施形態による多チップ・モジュール内のダイレクトコネクト・シグナリングを示す。 20

【図20】図20は、テスト配置を示し、これは、ダイレクトコネクト・ケーブルを介して相互接続されるべき回路ボード装着された集積回路パッケージまたは多チップ・モジュール内の集積回路ダイをテストするのに使用できる。

【図1】

【図2】

【図3】

FIG. 5A

FIG. 5B

The diagram shows a 25x16 grid of squares. Several regions are outlined and labeled:

- Region A:** A 5x5 square centered at (13, 8).

- Region B:** A 3x3 square centered at (13, 10).

- Region C:** A 3x3 square centered at (13, 12).

- Region D:** A 3x3 square centered at (13, 14).

- Region E:** A 3x3 square centered at (13, 16).

- Region F:** A 3x3 square centered at (15, 8).

- Region G:** A 3x3 square centered at (15, 10).

- Region H:** A 3x3 square centered at (15, 12).

- Region I:** A 3x3 square centered at (15, 14).

- Region J:** A 3x3 square centered at (15, 16).

- Region K:** A 3x3 square centered at (17, 8).

- Region L:** A 3x3 square centered at (17, 10).

- Region M:** A 3x3 square centered at (17, 12).

- Region N:** A 3x3 square centered at (17, 14).

- Region O:** A 3x3 square centered at (17, 16).

- Region P:** A 3x3 square centered at (19, 8).

- Region Q:** A 3x3 square centered at (19, 10).

- Region R:** A 3x3 square centered at (19, 12).

- Region S:** A 3x3 square centered at (19, 14).

- Region T:** A 3x3 square centered at (19, 16).

【 図 6 】

FIG. 6

【図7】

FIG. 7

【図8】

FIG. 8

【図9】

FIG. 9

【図10】

FIG. 10

【図 1 1】

【図 1 2】

【図 1 3】

FIG. 15A

FIG. 15B

FIG. 16A

FIG. 16B

FIG. 17A

FIG. 17B

FIG. 17C

FIG. 17D

FIG. 17E

FIG. 17F

FIG. 18A

FIG. 18B

FIG. 18C

FIG. 18D

FIG. 19A

FIG. 19B

【 図 2 0 】

## 【手続補正書】

【提出日】平成17年1月5日(2005.1.5)

## 【手続補正1】

#### 【補正対象書類名】特許請求の範囲

### 【補正対象項目名】全文

## 【補正方法】変更

## 【補正の内容】

## 【特許請求の範囲】

### 【請求項1】

集積回路パッケージであって、

基板と、

該基板の第1の表面に配置され、第1の複数のコンタクトを含む集積回路ダイと、前記基板の前記第1表面に配置された複数の導電性トレースであって、前記第1表面に沿って前記第1の複数のコンタクトから前記第1表面の露出領域まで延在した、前記の複数の導電性トレースと、を備えた集積回路パッケージ。

【請求項2】

請求項 1 記載の集積回路パッケージにおいて、前記集積回路ダイは、さらに、第 2 の複数のコンタクトを含み、前記基板は、複数の導電性構造を含み、該複数の導電性構造は、前記第 2 の複数のコンタクトと接触し、かつ前記基板の前記第 1 表面から第 2 表面まで前記基板を貫通して延在すること、を特徴とする集積回路パッケージ。

### 【請求項 3】

請求項 1 記載の集積回路パッケージにおいて、前記複数の導電性トレースは、前記基板のエッジを超えて延在すること、を特徴とする集積回路パッケージ。

【請求項4】

集積回路パッケージであって、

第1の組のコンタクトと第2の組のコンタクトとを有する集積回路ダイと、

該集積回路ダイに隣接して配置された第1の表面と、該第1表面と対向する第1の表面とを有する基板と、

前記第1組のコンタクトに結合した第1の組の導電性構造であって、前記第1表面から前記基板を貫通して前記第2表面へ延在する、前記の第1組の導電性構造と、

前記第2組のコンタクトに結合した第2の組の導電性構造であって、前記第1表面と第2表面との間に形成された前記基板のエッジまで延在する、前記の第2の組の導電性構造と、

を備えた集積回路パッケージ。

【請求項5】

請求項4記載の集積回路パッケージにおいて、前記第2組の導電性構造は、

前記第1表面と第2表面との間ににおいて前記基板内に配置され、かつ前記基板の前記エッジまで延在する複数の導電性トレースと、

前記複数の導電性トレースと接触するため前記第1表面から延在した複数の導電性ビアと、

を備えたこと、を特徴とする集積回路パッケージ。

【請求項6】

請求項5記載の集積回路パッケージにおいて、前記複数の導電性トレースは、前記基板の前記エッジを超えて延在したこと、を特徴とする集積回路パッケージ。

【請求項7】

請求項6記載の集積回路パッケージにおいて、前記複数の導電性トレースは、絶縁材料内に少なくとも部分的にカプセル封入され、前記絶縁材料は、前記導電性トレースを、実質上互いに固定された位置に維持すること、を特徴とする集積回路パッケージ。

【請求項8】

信号システムであって、

プリント回路ボードと、

該プリント回路ボード上に配置された第1の集積回路パッケージと、

前記プリント回路ボード上に配置された第2の集積回路パッケージと、

前記プリント回路ボード上に浮遊させた複数の電気信号導体であって、前記第1集積回路パッケージと第2集積回路パッケージとの間に延在する、前記の複数の電気信号導体と、

を備えた信号システム。

【請求項9】

請求項8記載の信号システムにおいて、前記プリント回路ボードは、前記第1集積回路パッケージおよび第2集積回路パッケージに対し、これらに電力を供給するため結合された導電性構造を含むこと、を特徴とする信号システム。

【請求項10】

請求項8記載の信号システムにおいて、前記第1集積回路パッケージと第2集積回路パッケージとの間に延在した前記複数の電気信号導体は、第1の複数の電気信号導体を構成し、前記信号システムは、さらに、

前記プリント回路ボードに装着された第3の集積回路パッケージと、

前記プリント回路ボード上に浮遊させ、かつ前記第1集積回路パッケージと第3集積回路パッケージとの間に延在した第2の複数の電気信号導体と、

を含むこと、を特徴とする信号システム。

【請求項11】

信号システムであって、

プリント回路ボードと、

該プリント回路ボード上に配置された第1の集積回路パッケージと、

前記プリント回路ボード上に配置された第2の集積回路パッケージと、

前記第1集積回路パッケージと前記第2集積回路パッケージとに固着されたケーブルであって、複数の電気信号導体を含む、前記のケーブルと、

を備えた信号システム。

【請求項12】

請求項11記載の信号システムにおいて、前記第1集積回路パッケージは、基板と、該基板上に配置された集積回路ダイとを含み、前記ケーブルは、前記基板に固着されたこと、

を特徴とする信号システム。

【請求項13】

請求項12記載の信号システムにおいて、前記第1集積回路パッケージは、さらに、複数の導電性トレースを含み、該複数の導電性トレースは、前記基板上に配置され、かつ第1の端部において前記ケーブルの前記複数の電気信号導体に結合されたこと、

を特徴とする信号システム。

【請求項14】

請求項13記載の信号システムにおいて、前記集積回路ダイは、複数の電気信号領域を含み、該複数の電気信号領域は、前記基板上に配置された前記複数の導電性トレースの第2の端部に結合されたこと、

を特徴とする信号システム。

【請求項15】

請求項11記載の信号システムにおいて、前記第1と第2の集積回路パッケージは、前記プリント回路ボードの互いに対向する側に配置されたこと、

を特徴とする信号システム。

【請求項16】

信号システムであって、

第1の回路ボードと、

該第1回路ボード上に配置され、かつ第1のインバータ上に配置された第1の集積回路ダイを含む第1の集積回路パッケージと、

第2の基板上に配置された第2の集積回路ダイを含む第2の集積回路パッケージと、

前記第1基板と前記第2基板とに固着された、複数の電気信号導体を含むケーブルと、

を備えた信号システム。

【請求項17】

請求項16記載の信号システムにおいて、前記第1回路ボードは、前記第1回路ボード

に対し取り外し可能に結合されたこと、

を特徴とする信号システム。

【請求項18】

請求項16記載の信号システムにおいて、前記第1集積回路パッケージは、さらに、複数の導電性トレースを含み、該複数の導電性トレースは、前記第1基板上に配置され、かつ前記第1集積回路ダイと前記ケーブルの前記複数の電気信号導体との間に結合されたこと、

を特徴とする信号システム。

【請求項19】

回路ボード上に装着するための集積回路パッケージであって、

基板と、

該基板上に配置された第1の集積回路ダイと、

該基板上に配置された第2の集積回路ダイと、

前記第1集積回路ダイと第2集積回路ダイとの間に電気的に結合されたケーブルと、

を備えた集積回路パッケージ。

【請求項20】

第1のダイと第2のダイとを含む集積回路パッケージを製造するための方法であって、

前記第1ダイを、前記集積回路パッケージの表面に装着し、

前記第1ダイを前記基板に装着した後に、前記第1ダイをテスト装置でテストし、

前記第2ダイを前記基板に装着し、

前記第2ダイを前記基板に装着した後に、前記第2ダイを前記テスト装置でテストし、

前記テスト装置により前記第1ダイと前記第2ダイを成功裏にテストできた場合、前記

第1ダイと前記第2ダイとの間に第1のケーブルを結合すること、

を備えた製造方法。

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                             | International application No.<br>PCT/US03/13524 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------|

| <b>A. CLASSIFICATION OF SUBJECT MATTER</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                             |                                                 |

| IPC(7) :H04B 15/00, H05B 3/00<br>US CL : 257/686,686,723,777,691,698,668,784,786<br>According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                             |                                                 |

| <b>B. FIELDS SEARCHED</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                             |                                                 |

| Minimum documentation searched (classification system followed by classification symbols)<br>U.S. : 257/686,686,723,777,691,698,668,784,786                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                             |                                                 |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched<br>none                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                             |                                                 |

| Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)<br>EAST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                             |                                                 |

| <b>C. DOCUMENTS CONSIDERED TO BE RELEVANT</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                             |                                                 |

| Category*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Citation of document, with indication, where appropriate, of the relevant passages          | Relevant to claim No.                           |

| Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | US 5,715,274 A (Rostoker et al) 03 February 1998, see figures 2-8.                          | 1-105                                           |

| Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | US 6,304,450 B1 (Dibene, II et al) 16 October 2001, figures 1A-6.                           | 1-105                                           |

| <input type="checkbox"/> Further documents are listed in the continuation of Box C. <input type="checkbox"/> See patent family annex.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                             |                                                 |

| * Special categories of cited documents:<br>"A" document defining the general state of the art which is not considered to be of particular relevance<br>"E" earlier document published on or after the international filing date<br>"L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)<br>"O" document referring to an oral disclosure, use, exhibition or other means<br>"P" document published prior to the international filing date but later than the priority date claimed                                                                                    |                                                                                             |                                                 |

| "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention<br>"X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone<br>"Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art<br>"&" document member of the same patent family |                                                                                             |                                                 |

| Date of the actual completion of the international search<br><br>29 SEPTEMBER 2003                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Date of mailing of the international search report<br><br>03 NOV 2003                       |                                                 |

| Name and mailing address of the ISA/US<br>Commissioner of Patents and Trademarks<br>Box PCT<br>Washington, D.C. 20231<br>Facsimile No. (703) 305-3230                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Authorized officer<br>ALEXANDER WILLIAMS <i>Dawn Frantz</i><br>Telephone No. (703) 308-4863 |                                                 |

**INTERNATIONAL SEARCH REPORT**

|                                                 |

|-------------------------------------------------|

| International application No.<br>PCT/US03/13524 |

|-------------------------------------------------|

**Box I Observations where certain claims were found unsearchable (Continuation of item 1 of first sheet)**

This international report has not been established in respect of certain claims under Article 17(2)(a) for the following reasons:

1.  Claims Nos.:

because they relate to subject matter not required to be searched by this Authority, namely:

2.  Claims Nos.:

because they relate to parts of the international application that do not comply with the prescribed requirements to such an extent that no meaningful international search can be carried out, specifically:

3.  Claims Nos.:

because they are dependent claims and are not drafted in accordance with the second and third sentences of Rule 6.4(a).

**Box II Observations where unity of invention is lacking (Continuation of item 2 of first sheet)**

This International Searching Authority found multiple inventions in this international application, as follows:

Please See Extra Sheet.

1.  As all required additional search fees were timely paid by the applicant, this international search report covers all searchable claims.

2.  As all searchable claims could be searched without effort justifying an additional fee, this Authority did not invite payment of any additional fee.

3.  As only some of the required additional search fees were timely paid by the applicant, this international search report covers only those claims for which fees were paid, specifically claims Nos.:

4.  No required additional search fees were timely paid by the applicant. Consequently, this international search report is restricted to the invention first mentioned in the claims; it is covered by claims Nos.:

**Remark on Protest**

|                                     |

|-------------------------------------|

| <input type="checkbox"/>            |

| <input checked="" type="checkbox"/> |

The additional search fees were accompanied by the applicant's protest.

No protest accompanied the payment of additional search fees.

**INTERNATIONAL SEARCH REPORT**

|                                                 |

|-------------------------------------------------|

| International application No.<br>PCT/US03/13524 |

|-------------------------------------------------|

**BOX II. OBSERVATIONS WHERE UNITY OF INVENTION WAS LACKING**

This ISA found multiple inventions as follows:

This application contains the following inventions or groups of inventions which are not so linked as to form a single inventive concept under PCT Rule 13.1. In order for all inventions to be searched, the appropriate additional search fees must be paid.

Group I, claims 1-38 and 90-92, drawn to an integrated circuit package.

Group II, claims 93-105, drawn to a method of manufacturing an integrated circuit package.

Group III, claims 39-90, drawn to a singaling system.

The inventions listed as Groups I, II and III do not relate to a single inventive concept under PCT Rule 13.1 because, under PCT Rule 13.2, they lack the same or corresponding special technical features for the following reasons: Group I has features of a substrate having an integrated circuit die; Group II has features of a first and second die mounted on a substrate with a cable coupled between the first and second dies; and Group III has features of a printed circuit board with first and second integrated circuit packages disposed on the printed circuit board.

---

フロントページの続き

(81)指定国 AP(GH,GM,KE,LS,MW,MZ,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HU,IE,IT,LU,MC,NL,PT,RO,SE,SI,SK,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AT,AU,AZ,BA,BB,BG,BR,BY,BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,DZ,EC,EE,ES,FI,GB,GD,GE,GH,GM,HR,HU,ID,IL,IN,IS,JP,KE,KG,KP,KR,KZ,LC,LK,LR,LS,LT,LU,LV,MA,MD,MG,MK,MN,MW,MX,MZ,NO,NZ,OM,PH,PL,PT,RO,RU,SD,SE,SG,SK,SL,TJ,TM,TN,TR,TT,TZ,UA,UG,UZ,VN,YU,ZA,ZM,ZW

(74)代理人 100120112

弁理士 中西 基晴

(72)発明者 フジエルスタッド, ジョセフ・シー

アメリカ合衆国ワシントン州 98038, メープル・ヴァレー, ツーハンドレッドアンドサーティ

ファースト・プレイス・サウスイースト 28128

(72)発明者 セガラム, パラ・ケイ

アメリカ合衆国カリフォルニア州 95008, キャンベル, ロイヤルトン・ドライブ 788

(72)発明者 ハバ, ベルガセム

アメリカ合衆国カリフォルニア州 95014, クバチーノ, サイプレス・コート 10541

F ターム(参考) 4M109 AA01 BA04 DA10