(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5028968号

(P5028968)

(45) 発行日 平成24年9月19日(2012.9.19)

(24) 登録日 平成24年7月6日(2012.7.6)

(51) Int.Cl.

F 1

|             |           |

|-------------|-----------|

| H01L 23/12  | (2006.01) |

| H01L 25/065 | (2006.01) |

| H01L 25/07  | (2006.01) |

| H01L 25/18  | (2006.01) |

|            |      |

|------------|------|

| H01L 23/12 | 501B |

| H01L 25/08 | Z    |

請求項の数 6 (全 16 頁)

(21) 出願番号

特願2006-311850 (P2006-311850)

(22) 出願日

平成18年11月17日 (2006.11.17)

(65) 公開番号

特開2008-130678 (P2008-130678A)

(43) 公開日

平成20年6月5日 (2008.6.5)

審査請求日

平成21年5月22日 (2009.5.22)

(73) 特許権者 000005120

日立電線株式会社

東京都千代田区外神田四丁目14番1号

(74) 代理人 100071526

弁理士 平田 忠雄

(74) 代理人 100099597

弁理士 角田 賢二

(74) 代理人 100119208

弁理士 岩永 勇二

(74) 代理人 100124235

弁理士 中村 恵子

(74) 代理人 100124246

弁理士 遠藤 和光

(74) 代理人 100128211

弁理士 野見山 孝

最終頁に続く

(54) 【発明の名称】半導体装置、積層型半導体装置およびインターポーラ基板

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体素子、該半導体素子に電気的接続された配線パターンと該配線パターンが形成された絶縁基板とを有するインターポーラ基板、前記半導体素子と前記インターポーラ基板との間を接着する接続層、および前記インターポーラ基板上に配置される半田ボール等の外部端子を備えた半導体装置であって、

前記絶縁基板は、前記半導体素子の外側に配置される前記外部端子の搭載部が折り曲げられて、該絶縁基板の折り曲げられていない部分と折り曲げられた部分とが空隙を形成するように対向しており、前記外部端子は、前記半導体素子よりも外側に位置していることを特徴とする半導体装置。

## 【請求項 2】

前記空隙には、ソルダーレジスト、応力緩和エラストマ、又はエラストマ代替接続層が詰められていることを特徴とする請求項 1 に記載の半導体装置。

## 【請求項 3】

前記接続層は、応力緩和エラストマ接続層又はエラストマ代替接続層を有することを特徴とする請求項 1 または 2 に記載の半導体装置。

## 【請求項 4】

前記半導体装置は、BGA型、CSP型又はSIP型、若しくはそれらの複合体(MCP:マルチチップパッケージ)の半導体装置であることを特徴とする請求項 1 乃至請求項 3 のいずれか 1 項に記載の半導体装置。

**【請求項 5】**

請求項 1 乃至請求項 4 のいずれか 1 項に記載の半導体装置を前記外部端子により複数積層してなることを特徴とする積層型半導体装置。

**【請求項 6】**

半導体素子に電気的接続される配線パターンと該配線パターンが形成された絶縁基板とを有するインターポーザ基板であって、

前記絶縁基板は、搭載される半導体素子の外側に配置される半田ボール等の外部端子の搭載部が折り曲げられて、該絶縁基板の折り曲げられていない部分と折り曲げられた部分とが空隙を形成するように対向しており、前記外部端子は、半導体素子よりも外側に位置するように設けられていることを特徴とするインターポーザ基板。

10

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、半導体装置、積層型半導体装置およびインターポーザ基板に関し、特に、半導体素子とインターポーザ基板の間や、インターポーザ基板とプリント配線板（マザーボード）の間に応力が作用する BGA 型、 CSP 型、 SIP 型、それらの複合体等の半導体装置、積層型半導体装置および該半導体装置に用いるインターポーザ基板に関する。

**【背景技術】****【0002】**

従来、半導体装置のインターポーザ基板と半導体素子の間に生じる応力を緩和するため、半導体素子とインターポーザ基板との間に応力緩和エラストマを配置した構造の BGA 型等の半導体装置がある。

20

**【0003】**

この半導体装置の特徴は、応力緩和エラストマの存在にある。この応力緩和エラストマとしては、半田リフロー温度での弾性率が 1 MPa 以上の高分子材料からなる接着テープ（特許文献 1 参照）や、連続気泡構造体もしくは三次元網目構造体からなる多孔質樹脂テープ（特許文献 2 参照）が知られている。

**【0004】**

しかしながら、このような応力緩和エラストマは、材料価格が高く、特に特許文献 2 に示される連続気泡構造体もしくは三次元網目構造体からなる多孔質樹脂テープの種類において顕著である。

30

**【0005】**

そこで、応力緩和エラストマの代替として開発し、本願出願人により先に特許出願がなされた（未公開先願）ものとして、以下の発明がある。

**【0006】**

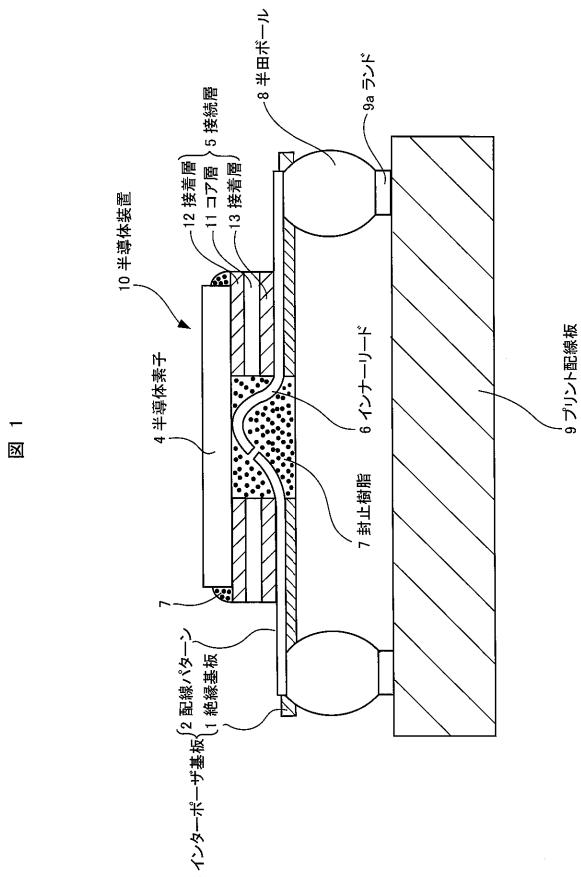

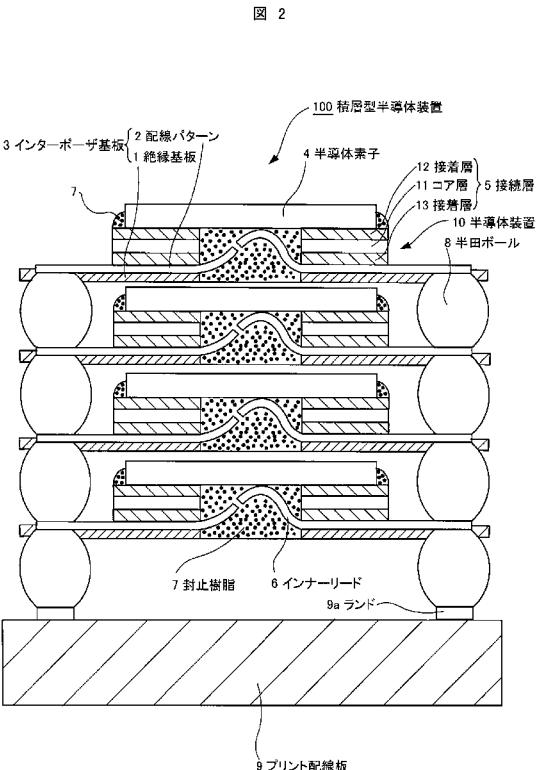

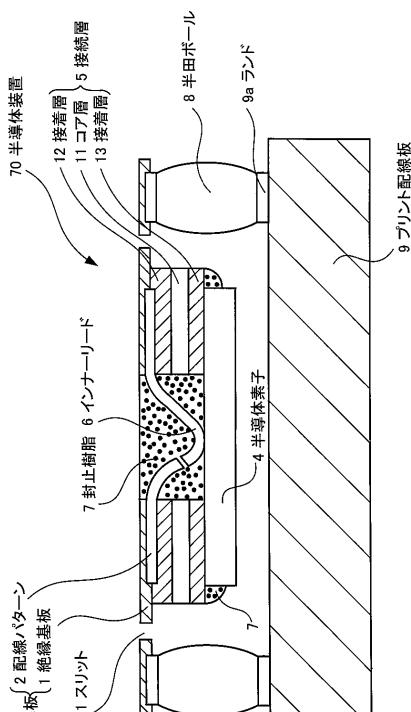

図 1 は、所定の接続層を有する半導体装置の構造を示す説明図であり、図 2 は、その積層型半導体装置の構造を示す説明図である。

**【0007】**

BGA 型の半導体装置 10 は、ポリイミド等の絶縁基板（絶縁テープ）1 の上に銅の配線パターン 2 を形成してなるインターポーザ基板 3 と、Si チップからなる半導体素子 4 との間に接続層 5 を配置し、これらを接着一体化して構成されている。

40

**【0008】**

半導体装置 10 は、所定のボンディングツール（図示せず）を用いて、配線パターン 2 のインナーリード 6 を半導体素子 4 の電極パッドにリードボンディングされている。リードボンディングの接合部および接続層 5 の上面と半導体素子 4 の側面との間に形成される直角状のコーナー部分は、全体がモールドレジンやポッティングレジン等の封止樹脂 7 で封止されている。インターポーザ基板 3 に形成されたビアホールに半田ボール 8 が搭載され、この半田ボール 8 と配線パターン 2 の所定部分とが電気的に接続されている。

**【0009】**

応力緩和エラストマの代替としての接続層 5（以下、「エラストマ代替接続層」と言う）

50

ことがある。)は、半導体素子4とインターポーザ基板3との間に応力が作用することにより、破壊、ずれ(すべり)又は剥がれを生じる材質で構成された層を有する、若しくは、破壊、ずれ(すべり)又は剥がれを生じる構造を有する(「応力」とは、半導体素子と実装基板との熱膨張率差により発生する熱応力や、BGAパッケージにおける半田ボール9へ加わる外部衝撃による応力などを言う。また、破壊としては、脆性破壊や延性破壊があり、例えば、ひび割れ、破断等がある)。

#### 【0010】

破壊、ずれ(すべり)又は剥がれは、半導体素子4と接続層5との接着界面の一部、インターポーザ基板3と接続層5との接着界面の一部、又は接続層5内における層間界面の一部で、あるいは、半導体素子4とインターポーザ基板3が分離しない範囲で該接続層内部の一部で生じる。なお、半導体素子4とインターポーザ基板3が分離しないように封止樹脂7で保持されている場合には、破壊、ずれ(すべり)又は剥がれが生じる部位は上記の一部に限られず、例えば接着界面全体に生じてもよい。10

#### 【0011】

具体的には、例えば図1に示すように、半導体素子4とインターポーザ基板3の間に介在する接続層5は、支持体として用いられるコア層11と、コア層11を半導体素子4およびインターポーザ基板3に接着するための接着層12、13とを含んで構成されている。

#### 【0012】

コア層11は、例えば、光を当てたときに硬化する光硬化性物質(感光材)をフィルム化したドライフィルム材、内部に液状層を有する機械的構造を持つフィルム材等により構成されている。コア層11に接着剤をしみ込ませる等により接着力を持たせることでコア層11のみで接続層5を構成することもできる。なお、接続層5としてAgペースト材を用いる場合には、Agペースト材自体が接着層として機能するためAgペースト材単層で用いることができる。すなわち、接続層5は、テープ(フィルム)又はペーストで構成された層を有し、当該層を単層、2層、3層、又は4層以上の構造として用いることができる。20

#### 【0013】

接着層12、13は、応力が作用することでコア層11との接着界面、半導体素子4との接着界面、又はインターポーザ基板3との接着界面に破壊、ずれ(すべり)又は剥がれを生じる材質で構成してもよいし、それらのいずれかの接着界面が破壊、ずれ(すべり)又は剥がれを生じる構造を有するものとしてもよい。30

【特許文献1】特開平9-321084号公報

【特許文献2】特開平10-340968号公報

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0014】

上記発明によりインターポーザ基板と半導体素子の間に生じる応力の緩和が可能であるが、それに加えて、半導体パッケージとそれを組み込むプリント配線板(マザーボード)との熱膨張率係数差により生じる応力(ストレス)の緩和、或いは積層型半導体装置における半導体装置間に生じる応力の緩和が構造設計の重要なポイントとなっており、より優れた応力緩和能を持つ半導体装置、積層型半導体装置および該半導体装置に用いるインターポーザ基板が求められている。40

#### 【0015】

従って、本発明の目的は、インターポーザ基板とプリント配線板(マザーボード)の間に生じる応力の緩和、或いは積層型半導体装置における半導体装置間に生じる応力の緩和に優れた半導体装置、積層型半導体装置および該半導体装置に用いるインターポーザ基板を提供することにある。

#### 【課題を解決するための手段】

#### 【0016】

10

20

30

40

50

本発明は、上記目的を達成するため、半導体素子、該半導体素子に電気的接続された配線パターンと該配線パターンが形成された絶縁基板とを有するインターポーラ基板、前記半導体素子と前記インターポーラ基板との間を接着する接続層、および前記インターポーラ基板上に配置される半田ボール等の外部端子を備えた半導体装置であって、前記絶縁基板は、前記半導体素子の外側に配置される前記外部端子の搭載部が折り曲げられて、該絶縁基板の折り曲げられていない部分と折り曲げられた部分とが空隙を形成するように対向しており、前記外部端子は、前記半導体素子よりも外側に位置していることを特徴とする半導体装置を提供する。

#### 【0017】

また、本発明は、上記目的を達成するため、上記の本発明に係る半導体装置を前記外部端子により複数積層してなることを特徴とする積層型半導体装置を提供する。 10

#### 【0018】

また、本発明は、上記目的を達成するため、半導体素子に電気的接続される配線パターンと該配線パターンが形成された絶縁基板とを有するインターポーラ基板であって、前記絶縁基板は、搭載される半導体素子の外側に配置される半田ボール等の外部端子の搭載部が折り曲げられて、該絶縁基板の折り曲げられていない部分と折り曲げられた部分とが空隙を形成するように対向しており、前記外部端子は、半導体素子よりも外側に位置するように設けられていることを特徴とするインターポーラ基板を提供する。

#### 【発明の効果】

#### 【0019】

本発明によれば、インターポーラ基板とプリント配線板（マザーボード）の間に生じる応力の緩和、或いは積層型半導体装置における半導体装置間に生じる応力の緩和に優れた半導体装置、積層型半導体装置および該半導体装置に用いるインターポーラ基板を得ることができる。 20

#### 【発明を実施するための最良の形態】

#### 【0020】

##### 〔本発明の第1の実施の形態〕

##### （半導体装置の構成）

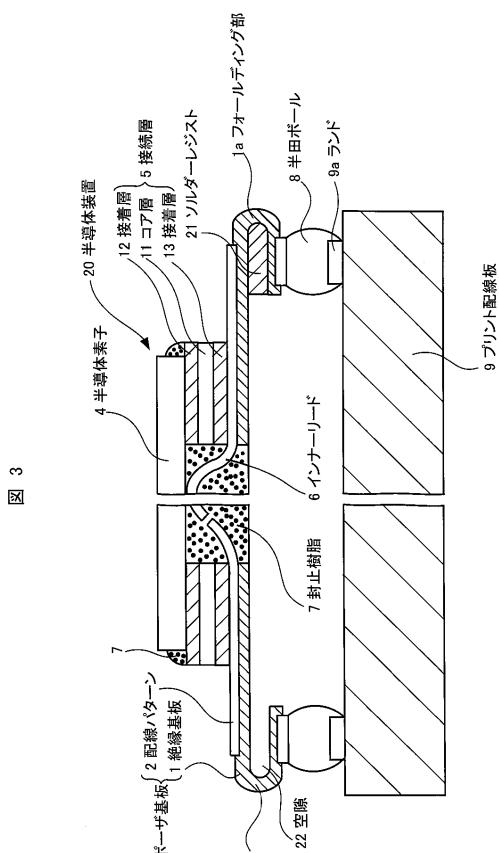

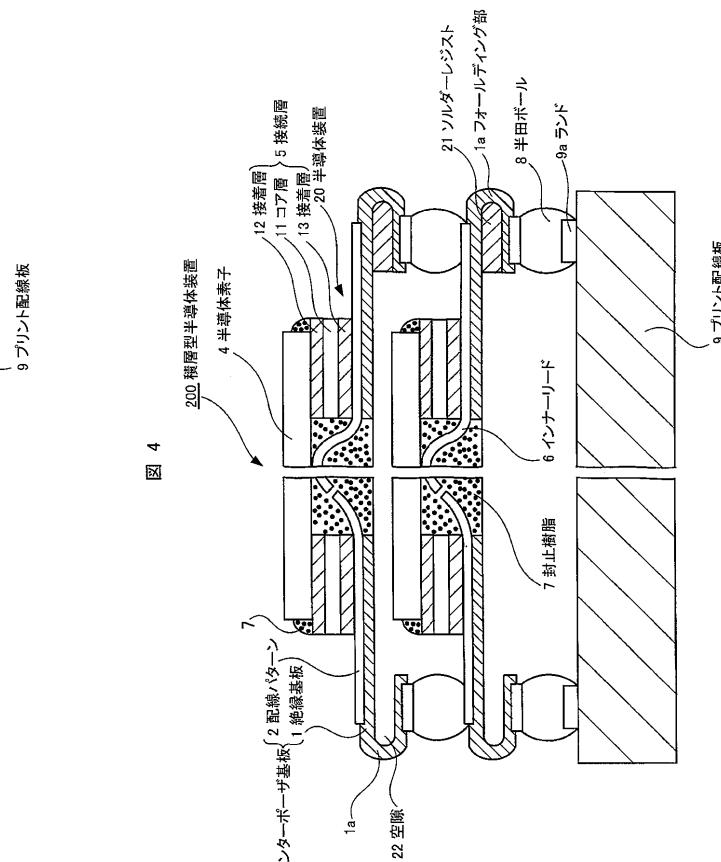

図3は、本発明の第1の実施の形態に係る半導体装置の構造を示す説明図であり、図4は、その積層型半導体装置の構造を示す説明図である。以下に説明する事項以外は、図1, 2に示した半導体装置・積層型半導体装置と同様である。なお、接続層5は、エラストマ代替接続層に限らず、従来の応力緩和エラストマを用いた構成としてもよい。また、緩和層を設けずに接着層のみとしてもよい。 30

#### 【0021】

BGA型の半導体装置20は、インターポーラ基板3を構成する絶縁基板1の半田ボール8（半導体素子4の外側の半田ボール8）搭載部がプリント配線板9側（半導体素子4の非接着面側）に約180°折り曲げられてフォールディング部1aが形成されている。

#### 【0022】

絶縁基板1の折り曲げられていない部分と折り曲げられた部分は、空隙22を有するように対向している。これにより、応力が緩和できるとともに、スペース効率向上の効果、半田ボール8の縮小化の効果がある。 40

#### 【0023】

空隙22には、図3の右半分に示したように、ソルダーレジストを詰めてもよい。ソルダーレジストに替えて、応力緩和エラストマやエラストマ代替接続層などを詰め物として用いてもよい。これにより、フォールディング部の固定化、寸法精度、平衡度の点で有利な効果が得られる。

#### 【0024】

本実施の形態においては、図3に示されるような、外部端子である半田ボール8が半導体素子4の外側にある場合（Fan-Outタイプ）のほか、半田ボール8が半導体素子4の下と外側の両方にある場合（Fan-In / Outタイプ）にも適用できる。 50

**【 0 0 2 5 】**

なお、図3および図4において、図示は省略しているが、配線パターン2は、半田ボール8と電気的に接続されている（以下に説明する第2の実施の形態、第1～4の参考形態の説明図である図5～14においても同様）。

**【 0 0 2 6 】****(本実施の形態の効果)**

(1) 絶縁基板1の半田ボール搭載部にフォールディング部1aを設けたため、半導体装置20とプリント配線板9（マザーボード）の間に生じる応力と、積層型半導体装置20における半導体装置20間に生じる応力を緩和することができる。

(2) 半導体装置20の積層時に、上下の半導体装置20の間隔をフレキシブルに調整できる。また、半田ボール等の多ピン化が可能である。10

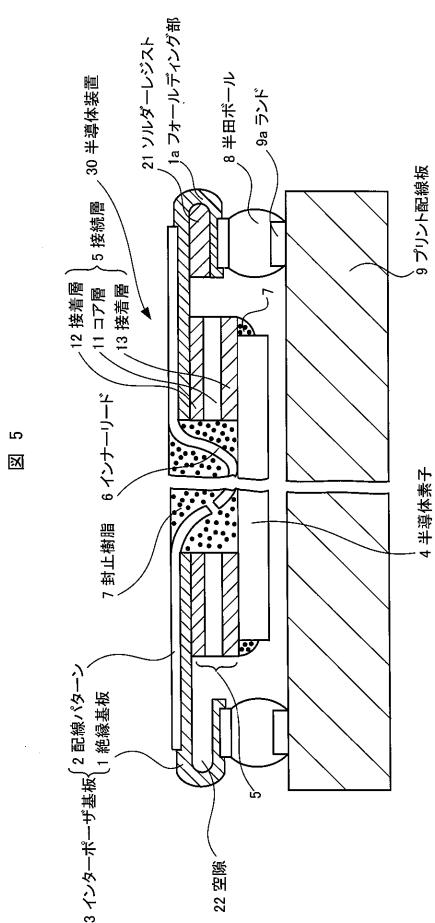

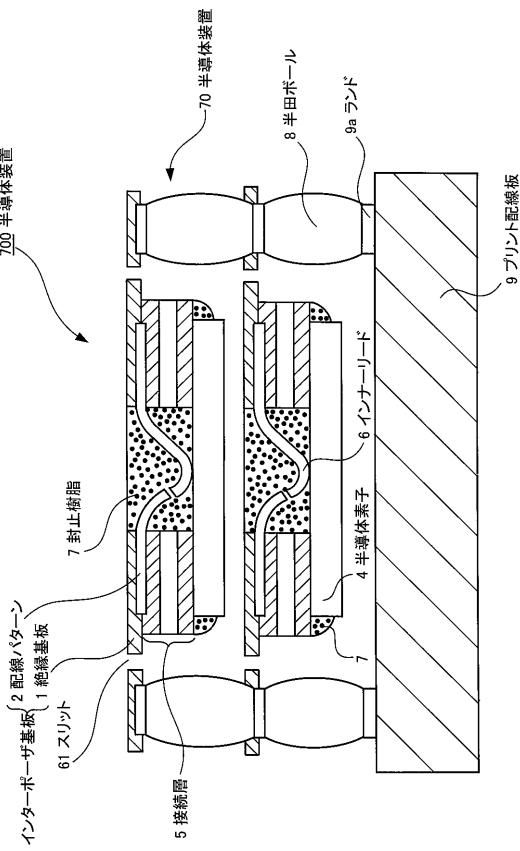

**【 0 0 2 7 】****(本発明の第2の実施の形態)****(半導体装置の構成)**

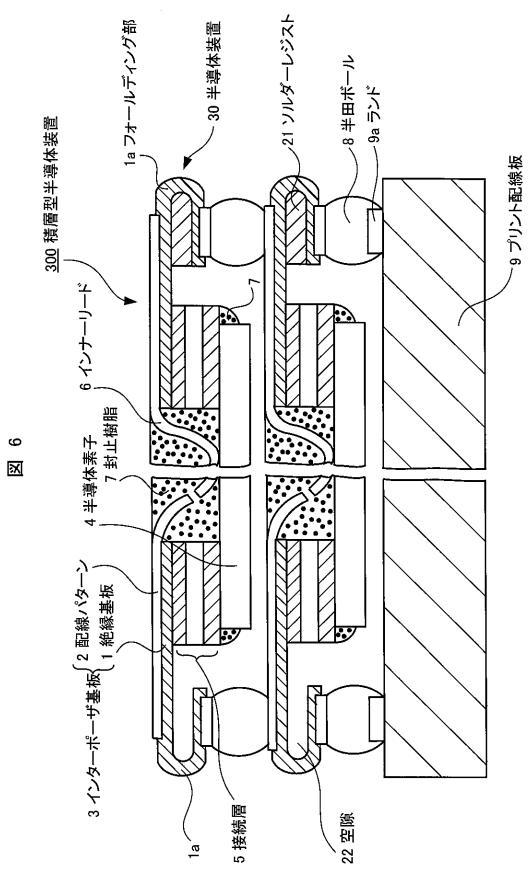

図5は、本発明の第2の実施の形態に係る半導体装置の構造を示す説明図であり、図6は、その積層型半導体装置の構造を示す説明図である。以下に説明する事項以外は、第1の実施の形態に係る半導体装置・積層型半導体装置と同様である。

**【 0 0 2 8 】**

すなわち、第1の実施の形態に係る半導体装置20の半導体素子4がプリント配線板9と対向する面とは反対の面に接着されているのに対し、本実施の形態に係る半導体装置30の半導体素子4は、プリント配線板9と対向する面に接着されている点で相違する。20

**【 0 0 2 9 】**

フォールディング部1aは、インターポーザ基板3を構成する絶縁基板1の半田ボール8（半導体素子4の外側の半田ボール8）搭載部がプリント配線板9側（半導体素子4の接着面側）に約180°折り曲げられて形成されている。

**【 0 0 3 0 】**

本実施の形態においては、図5に示されるような、外部端子である半田ボール8が半導体素子4の外側にある場合（Fan-Outタイプ）に適用できる。

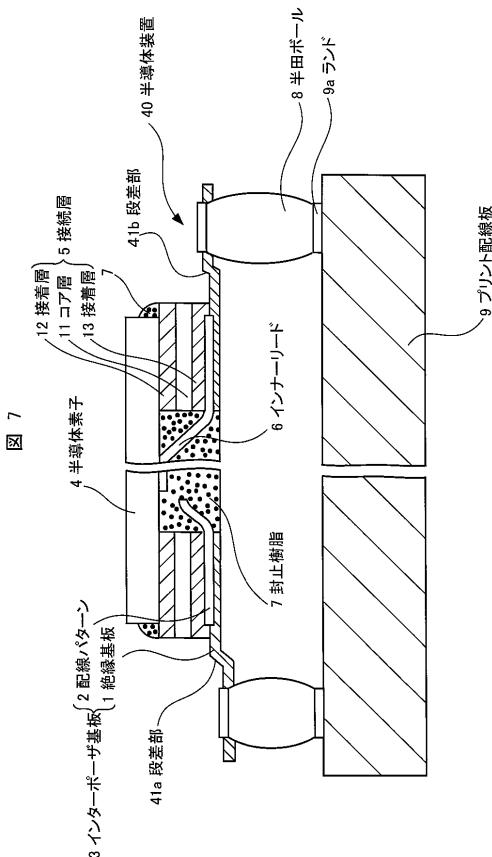

**【 0 0 3 1 】****(本発明の第1の参考形態)**30**(半導体装置の構成)**

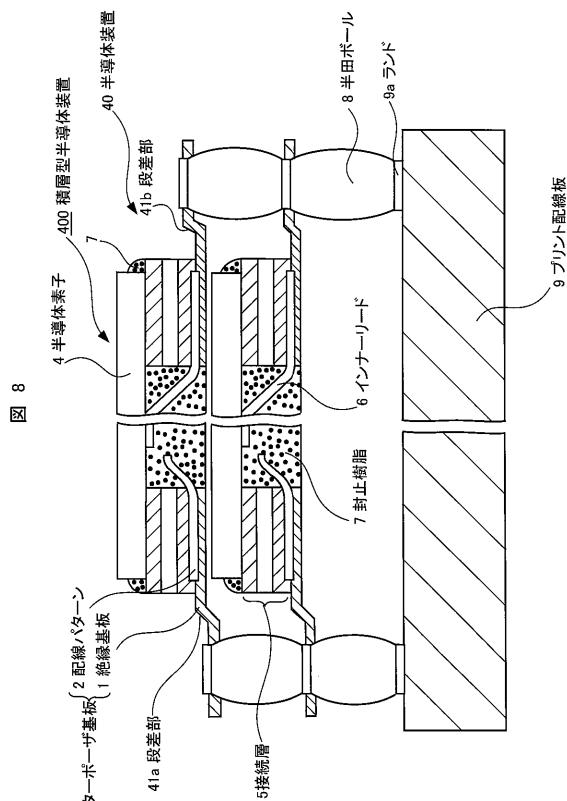

図7は、本発明の第1の参考形態に係る半導体装置の構造を示す説明図であり、図8は、その積層型半導体装置の構造を示す説明図である。以下に説明する事項以外は、図1、2に示した半導体装置・積層型半導体装置と同様である。なお、接続層5は、エラストマ代替接続層に限らず、従来の応力緩和エラストマを用いた構成としてもよい。また、緩和層を設げずに接着層のみとしてもよい。

**【 0 0 3 2 】**

BGA型の半導体装置40は、インターポーザ基板3を構成する絶縁基板1の半田ボール8（半導体素子4の外側の半田ボール8）搭載部が半導体素子4の接着部（搭載部）の下方向（図7の左半分の構成）又は上方向（図7の右半分の構成）へ段形状となるような段差部41a、41bが形成されている。40

**【 0 0 3 3 】**

半田ボール搭載部と半導体素子4搭載部とが同一平面とならなければよく、その段差は、インターポーザ基板の厚さ以上、当該パッケージ高さ以下であることが望ましい。

**【 0 0 3 4 】**

本参考形態においては、図7に示されるような、外部端子である半田ボール8が半導体素子4の外側にある場合（Fan-Outタイプ）のほか、半田ボール8が半導体素子4の下と外側の両方にある場合（Fan-In/Outタイプ）にも適用できる。

**【 0 0 3 5 】****(本参考形態の効果)**50

(1) 半田ボール8搭載部と半導体素子4搭載部とが段形状となるような段差部41a, 41bを設けたため、半導体装置40とプリント配線板9(マザーボード)の間に生じる応力と、積層型半導体装置400における半導体装置40間に生じる応力を緩和することができる。

**【0036】**

**[本発明の第2の参考形態]**

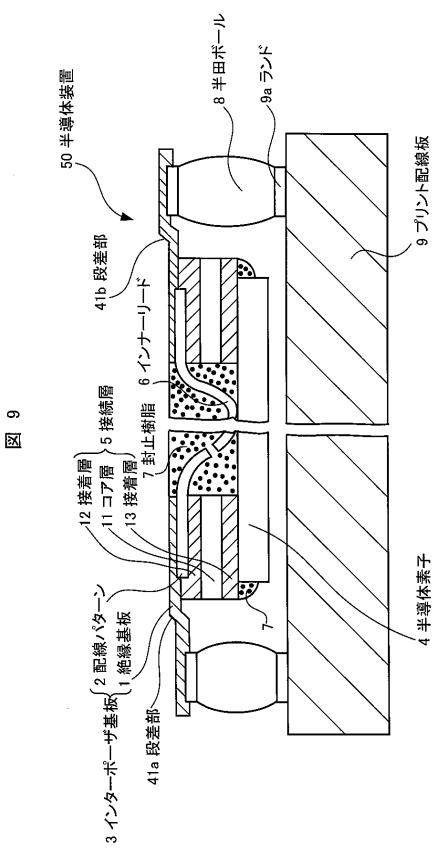

**(半導体装置の構成)**

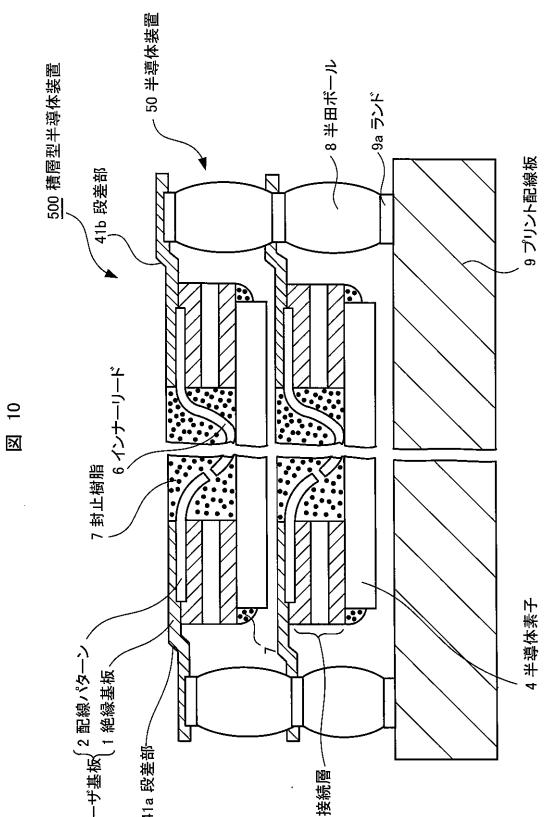

図9は、本発明の第2の参考形態に係る半導体装置の構造を示す説明図であり、図10は、その積層型半導体装置の構造を示す説明図である。以下に説明する事項以外は、第1の参考形態に係る半導体装置・積層型半導体装置と同様である。

10

**【0037】**

すなわち、第1の参考形態に係る半導体装置40の半導体素子4がプリント配線板9と対向する面とは反対の面に接着されているのに対し、本参考形態に係る半導体装置50の半導体素子4は、プリント配線板9と対向する面に接着されている点で相違する。

**【0038】**

本参考形態においては、図9に示されるような、外部端子である半田ボール8が半導体素子4の外側にある場合(Fan-Outタイプ)に適用できる。

**【0039】**

**[本発明の第3の参考形態]**

**(半導体装置の構成)**

20

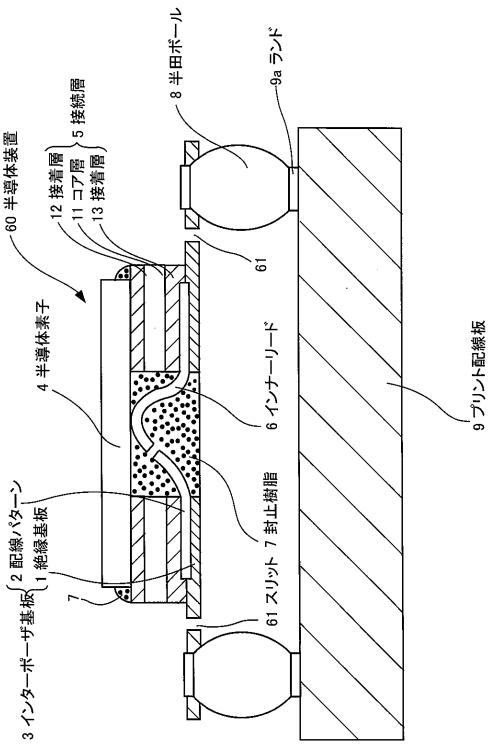

図11は、本発明の第3の参考形態に係る半導体装置の構造を示す説明図であり、図12は、その積層型半導体装置の構造を示す説明図である。以下に説明する事項以外は、図1, 2に示した半導体装置・積層型半導体装置と同様である。なお、接続層5は、エラストマ代替接続層に限らず、従来の応力緩和エラストマを用いた構成としてもよい。また、緩和層を設げずに接着層のみとしてもよい。

**【0040】**

BGA型の半導体装置60は、半導体素子4の接着部(搭載部)よりも外側、例えば、半導体素子4搭載部と半田ボール8(半導体素子4の外側の半田ボール8)搭載部の間に、スリット61がパンチングやレーザ等により絶縁基板1に形成されている。スリット61上に、配線パターン2が部分的に配置されている設計とする。

30

**【0041】**

スリット61には、緩衝材、他のプラスチック等が充填されていてもよい。

**【0042】**

スリット61は、幅 $1\text{ }\mu\text{m} \sim 1\text{ mm}$ 程度、長さ $100\text{ }\mu\text{m} \sim$ パッケージ全長程度であることが望ましい。形状の詳細については後述する。

**【0043】**

本参考形態においては、図11に示されるような、外部端子である半田ボール8が半導体素子4の外側にある場合(Fan-Outタイプ)のほか、半田ボール8が半導体素子4の下と外側の両方にある場合(Fan-In/Outタイプ)にも適用できる。

**【0044】**

40

**(本参考形態の効果)**

(1) 半導体素子4搭載部よりも外側に(ここでは半田ボール8搭載部と半導体素子4搭載部との間に)、スリット61を形成したため、半導体装置60とプリント配線板9(マザーボード)の間に生じる応力と、積層型半導体装置600における半導体装置60間に生じる応力を緩和することができる。

**【0045】**

**[本発明の第4の参考形態]**

**(半導体装置の構成)**

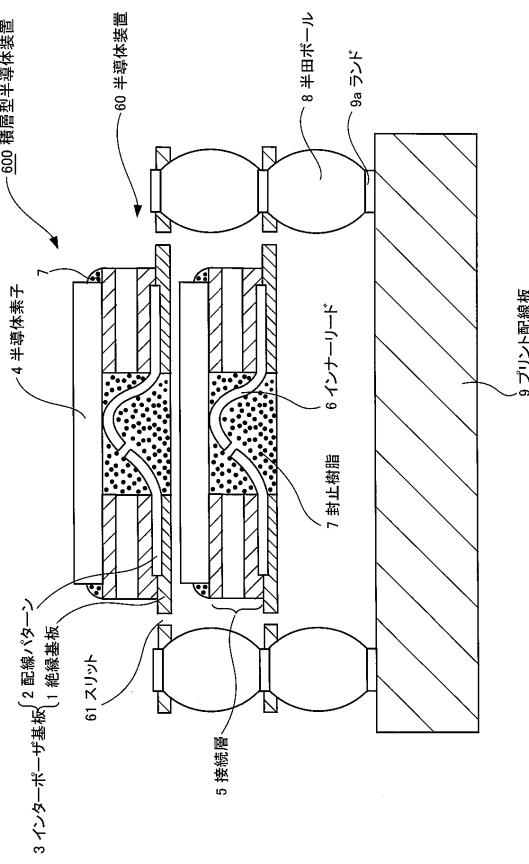

図13は、本発明の第4の参考形態に係る半導体装置の構造を示す説明図であり、図14は、その積層型半導体装置の構造を示す説明図である。以下に説明する事項以外は、第

50

3の参考形態に係る半導体装置・積層型半導体装置と同様である。

【0046】

すなわち、第3の参考形態に係る半導体装置60の半導体素子4がプリント配線板9と対向する面とは反対の面に接着されているのに対し、本参考形態に係る半導体装置70の半導体素子4は、プリント配線板9と対向する面に接着されている点で相違する。

【0047】

本参考形態においては、図13に示されるような、外部端子である半田ボール8が半導体素子4の外側にある場合(Fan-Outタイプ)に適用できる。

【0048】

(スリットの形状)

10

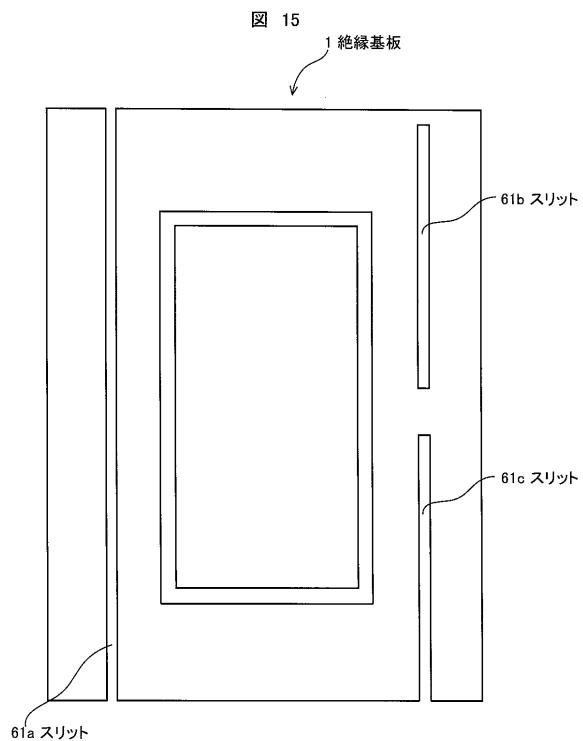

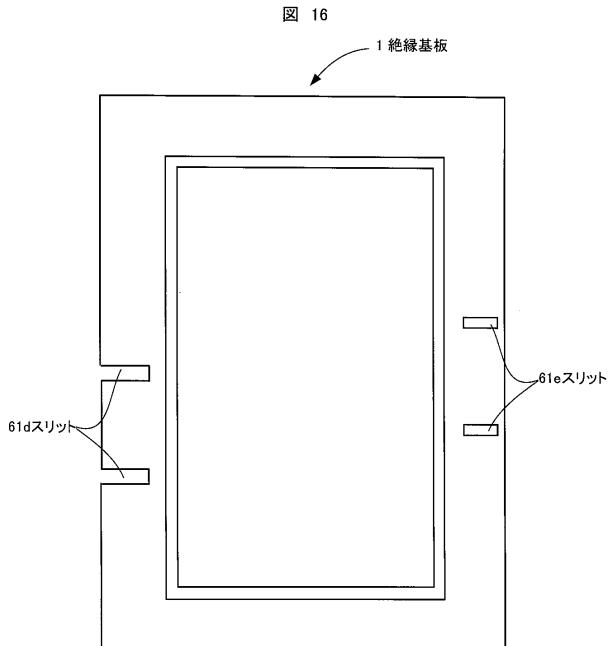

上記第3、第4の参考形態に係る半導体装置・積層型半導体装置において、スリット61は、以下に説明するように種々の形状を取り得る。

【0049】

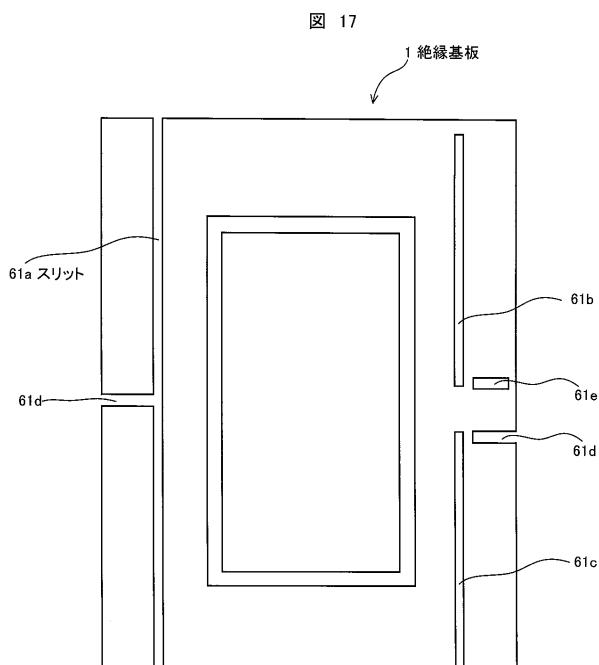

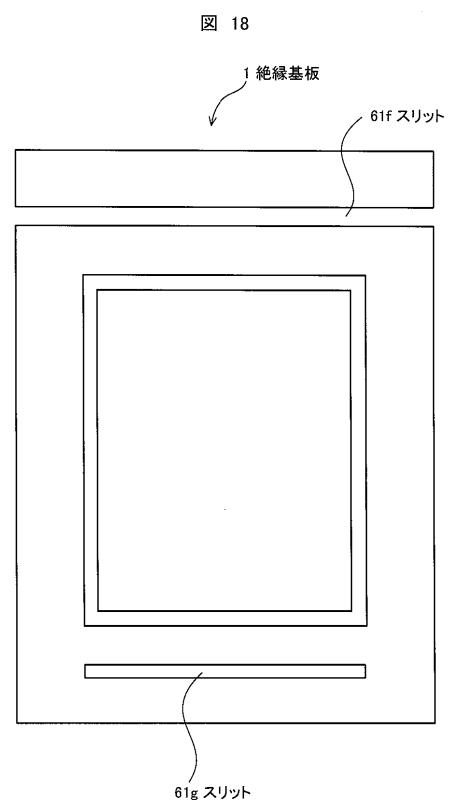

図15～図18は、本発明の第3、第4の参考形態に係る半導体装置・積層型半導体装置における絶縁基板1に形成されたスリット61の形状の例示である。

【0050】

図15におけるスリット61aは、図の中央に位置する半導体素子4搭載部の長辺と平行に、半導体素子4搭載側と半田ボール8のランド／コンタクト側を完全に分離する。一方、スリット61b、61cは、半導体素子4搭載部の長辺と平行に、半導体素子4搭載側と半田ボール8のランド／コンタクト側を不完全に分離する(スリット61bは長方形のウインドウ形状であり、スリット61cは一端が分離した櫛形状である)。

20

【0051】

すなわち、スリット61a～61cは、図の中央に位置する半導体素子4搭載部の長辺と平行に形成され、半導体素子4搭載部と半導体素子4の外側に配置される半田ボール8の搭載部を完全に又は部分的に分離するものである。

【0052】

図16におけるスリット61dは、図の中央に位置する半導体素子4搭載部の長辺(又は短辺も可)に直角に、半導体素子4搭載部の外側で、半田ボール8のランド／コンタクト領域を櫛形状に分離する。また、スリット61eは、長方形のウインドウ形状をしており、半導体素子4搭載部の長辺(又は短辺も可)に直角に、半導体素子4搭載部の外側で、半田ボール8のランド／コンタクト領域を分離する。

30

【0053】

すなわち、スリット61d、61eは、図の中央に位置する半導体素子4搭載部の長辺又は短辺と垂直に形成され、半導体素子4搭載部と半導体素子4の外側に配置される半田ボール8の搭載部を完全に又は部分的に分離するものである。

【0054】

図17は、図15及び図16に示すスリット61a～61eのすべてを有する複合形態を示す。

【0055】

図18におけるスリット61fは、図の中央に位置する半導体素子4搭載部の短辺と平行に、半導体素子4搭載側と半田ボール8のランド／コンタクト側を完全に分離する。一方、スリット61gは、半導体素子4搭載部の短辺と平行に、半導体素子4搭載側と半田ボール8のランド／コンタクト側を不完全に分離する(スリット61gは長方形のウインドウ形状である)。

40

【0056】

すなわち、スリット61f、61gは、図の中央に位置する半導体素子4搭載部の短辺と平行に形成され、半導体素子4搭載部と半導体素子4の外側に配置される半田ボール8の搭載部を完全に又は部分的に分離するものである。

【0057】

[エラストマ代替接続層5の形態]

50

前述の説明と一部重複するが、エラストマ代替接続層5の取りうる形態は、以下の通りである。

(1) 接続層5は、半導体素子4とインターポーザ基板3との間に応力が作用することにより、半導体素子4と接続層5との接着界面の一部、インターポーザ基板3と接続層5との接着界面の一部、又は接続層5内における層間界面の一部が、破壊、ずれ(すべり)又は剥がれを生じる材質で構成された層を有する、若しくは、破壊、ずれ(すべり)又は剥がれを生じる構造を有する。

#### 【0058】

(2) 接続層5は、半導体素子4とインターポーザ基板3との間に応力が作用することにより、半導体素子4とインターポーザ基板3が分離しない範囲で該接続層5内部の一部が、破壊又はずれ(すべり)を生じる材質で構成された層を有する、若しくは、破壊又はずれ(すべり)を生じる構造を有する。 10

#### 【0059】

(3) 半導体素子4とインターポーザ基板3は、分離しないように樹脂で一部或いは全体が保持されており、かつ、接続層5は、半導体素子4とインターポーザ基板3との間に応力が作用することにより、半導体素子4と接続層5との接着界面、インターポーザ基板3と接続層5との接着界面、又は接続層5内における層間界面が、破壊、ずれ(すべり)又は剥がれを生じる材質で構成された層を有する、若しくは、破壊、ずれ(すべり)又は剥がれを生じる構造を有する。

#### 【0060】

(4) 半導体素子4とインターポーザ基板3は、分離しないように樹脂で一部或いは全体が保持されており、かつ、接続層5は、半導体素子4とインターポーザ基板3との間に応力が作用することにより、該接続層5内部が、破壊又はずれ(すべり)を生じる材質で構成された層を有する、若しくは、破壊又はずれ(すべり)を生じる構造を有する。 20

#### 【0061】

(5) 接続層5は、テープ(フィルム)又はペーストで構成された層を有する。

#### 【0062】

(6) 接続層5は、コア層11と、コア層11を半導体素子4およびインターポーザ基板3に接着するための接着層12, 13とを含んで構成されている。

#### 【0063】

(7) 接続層5は、単層又は2層の接着層から構成されている。 30

#### 【0064】

(8) 接続層5は、2層以上の接着力を持たせたコア層から構成されている。

#### 【0065】

(9) 接続層5は、光硬化性物質(感光材)をフィルム化したドライフィルム材、内部に液状層を有する機械的構造を持つフィルム材、又はAgペースト材で構成された層を有する。

#### 【0066】

以下に、さらに具体的にエラストマ代替接続層5の取りうる形態を説明する。

#### 【0067】

##### (单層接続層)

接続層5は、単層のフィルム基材とその基材にしみ込ませる接着剤とから構成されている。この接着剤の半導体素子4又はインターポーザ基板3に対する接着力を $1 \sim 500 \text{ g f}$  ( $0.01 \sim 5 \text{ N}$ ) /  $\text{mm}^2$ の比較的弱い状態にすることで、接着相手との間に、ずれ(すべり)又は剥がれ等を生じさせ、応力を吸収する。

#### 【0068】

##### (单層接続層)

接続層5は、樹脂材とフィラー等の充填材とからなるペーストで構成されている。樹脂材と充填材の界面での剥れ等、或いは、樹脂材内部(バルク)での亀裂、割れ等が、 $0.01 \sim 5 \text{ N} / \text{mm}^2$ 以上の応力で部分的、或いは、全面的に生じるもの用いることにより 50

、応力を吸収する。

**【0069】**

(2層接続層)

接続層5は、上記した接着剤をしみ込ませた単層のフィルム基材を2枚重ね合わせて2層構造としたものである。この接着剤の半導体素子4又はインターポーラ基板3に対する接着力を $0.01 \sim 5 \text{ N/mm}^2$ の間の比較的弱い状態にすることで、接着相手との間に、或いは、2層のフィルム基材間に、ずれ(すべり)又は剥がれ等を生じさせ、応力を吸収する。

**【0070】**

(2層接続層)

10

接続層5は、上記した接着剤をしみ込ませた単層のフィルム基材と該フィルム基材と接着力の異なるフィルム基材とを2枚重ね合わせて2層構造としたものである。この接着剤の半導体素子4又はインターポーラ基板3に対する接着力を $0.01 \sim 5 \text{ N/mm}^2$ の間の比較的弱い状態にすることで、接着相手との間に、或いは、2層のフィルム基材間に、ずれ(すべり)又は剥がれ等を生じさせ、応力を吸収する。

**【0071】**

(3層接続層)

接続層5は、上記した接着剤をしみ込ませた単層のフィルム基材を3枚、或いは、該フィルム基材2枚と該フィルム基材とは接着力の異なるフィルム基材1枚を重ね合わせて(重ね順は順不同)3層構造としたものである。この接着剤の半導体素子4又はインターポーラ基板3に対する接着力を $0.01 \sim 5 \text{ N/mm}^2$ の間の比較的弱い状態にすることで、接着相手との間に、或いは、同種又は異種のフィルム基材間に、ずれ(すべり)又は剥がれ等を生じさせ、応力を吸収する。

20

**【0072】**

(2層接続層 <接続層の方向性の例> )

接続層5は、上記した接着剤をしみ込ませた単層のフィルム基材(コア層11A, 11B)を2枚、或いは、該フィルム基材1枚と該フィルム基材とは接着力の異なるフィルム基材1枚を重ね合わせて2層構造としたものであって(半導体素子4又はインターポーラ基板3に対する接着力を $0.01 \sim 5 \text{ N/mm}^2$ の間の比較的弱い状態とする)、各層は剥れ又はヘキ開強度に方向性(例えば、X方向に強く、Y方向に弱い)を有する。例えば、同種の2枚のフィルム基材を90度ずらして重ねることで、各層の剥れ、ヘキ開等を意図的に生じさせ、半導体素子4に加わる360度あらゆるXY面からの応力を吸収する。尚、上下2層の接着層の方向ずらしは、45~135度の範囲とする。

30

**【0073】**

(3層以上接続層 <コア層で吸収する例> )

接続層5は、上記した接着剤をしみ込ませた単層のフィルム基材(コア層11A, 11B)を3枚以上、或いは、該フィルム基材2枚と該フィルム基材とは接着力の異なるフィルム基材1枚以上を重ね合わせて3層以上の構造としたものであって(半導体素子4又はインターポーラ基板3に対する接着力を $0.01 \sim 5 \text{ N/mm}^2$ の間の比較的弱い状態とする)、各層は剥れ又はヘキ開強度に方向性(例えば、X方向に強く、Y方向に弱い)を有する。例えば、同種の2枚のフィルム基材(コア層11A)を90度ずらして重ね、これらを挟むようにしてコア層11Aとは異なる同種の2枚のフィルム基材(コア層11B)を90度ずらして重ねることで、半導体素子4に加わる360度あらゆるXY面からの応力を、各層の剥れ、ヘキ開等を生じさせて吸収する。尚、同種の上下2層の接着層の方向ずらしは、45~135度の範囲とする。

40

**【0074】**

上記具体例においては、コア層に接着剤をしみ込ませる形態を挙げたが、これらの具体例において、接着力を有する接着層を片側又は両側に別途設ける形態としてもよい。

**【0075】**

(接着強度の調整)

50

接続層5の接着力を調整する方法を以下に例示する。

(1) ペースト基材の量を減らし、フィラー等の直接接着性に関係しない部分の割合を多くすることで、接続層内部における、および接着相手との接着面積減少で、接着強度を低く抑えることができる。

(2) 接着剤をまだら(不均一)にしみ込ませることにより、接着強度のバラつき(0~100%)を実現できる。

(3) 接着剤を部分的にしみ込ませ、接続層内部における、および接着相手との接着面積減少で、接着強度を低く抑えることができる。

(4) 2層以上のコア層を持つ場合に、しみ込ませる接着剤を各層毎に変更し、接着層間の接着強度を、接着層と接着相手との接着強度より低く調整することで、接着層間で先にずれ(すべり)又は剥がれ等を生じるようにできる。10

#### 【0076】

(エラストマ代替接続層5の効果)

エラストマ代替接続層5を用いた実施の形態によれば、以下の効果を奏する。

(1) 半導体素子とインターポーラ基板との間に応力が作用したときに、破壊、ずれ(すべり)又は剥がれを生じる材質で構成されている、又は、破壊、ずれ(すべり)又は剥がれを生じる構造を有する接続層を使用することにより、当該応力を緩和できる半導体装置が得られる。ここで、緩和とは、吸収、分散等をいう。

#### 【0077】

(2) 従来の応力緩和エラストマの使用を要しないため、半導体装置およびインターポーラ基板を構成する上で材料価格の低減が可能となり、また、従来の応力緩和エラストマと比較してその取り扱いも容易となる。20

#### 【0078】

(本発明のその他の実施の形態)

本発明は、上記各実施の形態に限定されず、本発明の技術思想を逸脱あるいは変更しない範囲内で種々の変形が可能である。

例えば、上記実施の形態においては、BGA型半導体装置を例に説明したが、同様の問題を生じる半導体装置、例えば、CSP型やSIP型の半導体装置にも適用することができる。また、MCP(マルチチップパッケージ)にも適用することができる。

#### 【図面の簡単な説明】

#### 【0079】

【図1】エラストマ代替接続層を有する半導体装置の構造を示す説明図である。

【図2】エラストマ代替接続層を有する積層型半導体装置の構造を示す説明図である。

【図3】本発明の第1の実施の形態に係る半導体装置の構造を示す説明図である。

【図4】本発明の第1の実施の形態に係る積層型半導体装置の構造を示す説明図である。

【図5】本発明の第2の実施の形態に係る半導体装置の構造を示す説明図である。

【図6】本発明の第2の実施の形態に係る積層型半導体装置の構造を示す説明図である。

【図7】本発明の第1の参考形態に係る半導体装置の構造を示す説明図である。

【図8】本発明の第1の参考形態に係る積層型半導体装置の構造を示す説明図である。

【図9】本発明の第2の参考形態に係る半導体装置の構造を示す説明図である。40

【図10】本発明の第2の参考形態に係る積層型半導体装置の構造を示す説明図である。

【図11】本発明の第3の参考形態に係る半導体装置の構造を示す説明図である。

【図12】本発明の第3の参考形態に係る積層型半導体装置の構造を示す説明図である。

【図13】本発明の第4の参考形態に係る半導体装置の構造を示す説明図である。

【図14】本発明の第4の参考形態に係る積層型半導体装置の構造を示す説明図である。

【図15】本発明の第3, 第4の参考形態に係る半導体装置・積層型半導体装置における絶縁基板に形成されたスリットの形状の例示である。

【図16】本発明の第3, 第4の参考形態に係る半導体装置・積層型半導体装置における絶縁基板に形成されたスリットの形状の例示である。

【図17】本発明の第3, 第4の参考形態に係る半導体装置・積層型半導体装置における絶縁基板に形成されたスリットの形状の例示である。50

絶縁基板に形成されたスリットの形状の例示である。

【図18】本発明の第3, 第4の参考形態に係る半導体装置・積層型半導体装置における絶縁基板に形成されたスリットの形状の例示である。

【符号の説明】

【0080】

1 : 絶縁基板

1 a : フォールディング部

2 : 配線パターン

3 : インターポーラ基板

4 : 半導体素子

10

5 : 接続層

6 : インナーリード

7 : 封止樹脂

8 : 半田ボール

9 : プリント配線板

9 a : ランド

10, 20, 30, 40, 50, 60, 70 : 半導体装置

11 : コア層

12, 13 : 接着層

20

21 : ソルダーレジスト

22 : 空隙

41a, 41b : 段差部

61, 61a ~ 61g : スリット

100, 200, 300, 400, 500, 600, 700 : 積層型半導体装置

【図1】

【図2】

【図3】

【図5】

【図4】

【図6】

【図7】

【図9】

9

【 四 8 】

【 図 1 0 】

10

【図 1 1】

図 11

【図 1 2】

図 12

【図 1 3】

図 13

【図 1 4】

図 14

【図15】

【図16】

【図17】

【図18】

---

フロントページの続き

(72)発明者 細野 真行

東京都千代田区外神田四丁目14番1号 日立電線株式会社内

(72)発明者 柴田 明司

東京都千代田区外神田四丁目14番1号 日立電線株式会社内

(72)発明者 稲葉 公男

東京都千代田区外神田四丁目14番1号 日立電線株式会社内

審査官 坂本 薫昭

(56)参考文献 特開2003-309138(JP,A)

特開2002-289741(JP,A)

特開平08-31868(JP,A)

特開平07-201912(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 23/12

H01L 21/60