(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7293968号**

**(P7293968)**

(45)発行日 令和5年6月20日(2023.6.20)

(24)登録日 令和5年6月12日(2023.6.12)

(51)国際特許分類

H 02 M      7/12 (2006.01)

H 02 M      3/155(2006.01)

F I

H 02 M      7/12

H 02 M      3/155

Q

H

請求項の数 6 (全21頁)

(21)出願番号 特願2019-147052(P2019-147052)

(22)出願日 令和1年8月9日(2019.8.9)

(65)公開番号 特開2021-27788(P2021-27788A)

(43)公開日 令和3年2月22日(2021.2.22)

審査請求日 令和4年6月7日(2022.6.7)

(73)特許権者 000002945

オムロン株式会社

京都府京都市下京区塙小路通堀川東入南

不動堂町801番地

(74)代理人 100101454

弁理士 山田 卓二

(74)代理人 100091524

弁理士 和田 充夫

(74)代理人 100172236

弁理士 岩木 宣憲

(72)発明者 石橋 寛基

京都府京都市下京区塙小路通堀川東入南

不動堂町801番地 オムロン株式会社内

大西 浩之

京都府京都市下京区塙小路通堀川東入南

最終頁に続く

(54)【発明の名称】 電力変換装置の制御回路及び電力変換装置

**(57)【特許請求の範囲】****【請求項1】**

インダクタを含み、電流臨界モードで動作する力率改善回路を含む電力変換装置の制御回路であって、

前記インダクタの電流、もしくは前記インダクタの電流に対応し又は前記インダクタの電流を含む電流を検出し、前記検出した電流に対応する電圧を所定の利得で増幅した後、検出電圧として出力する第1の検出回路と、

前記検出電圧を所定の基準電圧と比較して比較結果信号を出力する比較回路と、

前記電力変換装置の入力電圧を検出する第2の検出回路と、

前記電力変換装置の出力電圧を検出する第3の検出回路とを備え、

前記制御回路は、前記検出した入力電圧、前記検出した出力電圧、予め設定された遅延時間、前記インダクタのインダクタンス値、前記第1の検出回路により検出した電流を電圧に変換するときの変換係数、電源電圧、及び前記利得に基づいて、前記インダクタの電流のゼロ値を検出するときの遅延を実質的にゼロにするための基準電圧を計算して前記比較回路に出力し、

前記比較回路は、

前記検出電圧を所定の第1の基準電圧と比較し、前記検出電圧が正から負に変化するゼロクロス検出点で第1の比較結果信号を出力する第1の比較器と、

前記検出電圧を前記第1の基準電圧よりも低い所定の第2の基準電圧と比較し、前記検出電圧が負から正に変化するゼロクロス検出点で第2の比較結果信号を出力する第2の比

較器と、

前記第1の比較結果信号の立ち上がりを検出して第1のパルス信号を出力する第1のパルス生成回路と、

前記第2の比較結果信号の立ち上がりを検出して第2のパルス信号を出力する第2のパルス生成回路と、

セット端子、リセット端子及び出力端子を有するセットリセット型フリップフロップであって、前記第1のパルス信号をセット端子に入力し、前記第2のパルス信号をリセット端子に入力し、出力端子から前記比較回路の比較結果信号を出力するセットリセット型フリップフロップとを備えることを特徴とする電力変換装置の制御回路。

#### 【請求項2】

前記第1のパルス生成回路は、前記第1の比較結果信号を微分する第1の微分回路と、前記第1の微分回路に接続されかつ負電圧を出力しない第1の保護ダイオードとを備え、

前記第2のパルス生成回路は、前記第2の比較結果信号を微分する第2の微分回路と、前記第2の微分回路に接続されかつ負電圧を出力しない第2の保護ダイオードとを備え、

前記第1のパルス生成回路は、前記第1の保護ダイオードから出力される電圧を、電源電圧の半分の電圧と比較して比較結果信号を前記第1のパルス信号として出力する第3の比較器を備え、

前記第2のパルス生成回路は、前記第2の保護ダイオードから出力される電圧を、前記電源電圧の半分の電圧と比較して比較結果信号を前記第2のパルス信号として出力する第4の比較器を備えることを特徴とする請求項1記載の電力変換装置の制御回路。

#### 【請求項3】

前記制御回路は、前記電力変換装置のソフトスッティングに必要な負電流を考慮して前記基準電圧を計算する、

請求項1又は2記載の電力変換装置の制御回路。

#### 【請求項4】

前記制御回路は、前記第1の検出回路により変換された電圧をDA変換するDA変換器を内蔵する、

請求項1～3のうちのいずれか1つに記載の電力変換装置の制御回路。

#### 【請求項5】

請求項1～4のうちのいずれか1つに記載の電力変換装置の制御回路を備える、

電力変換装置。

#### 【請求項6】

前記電力変換装置はスイッチング電源装置又はDC/DC変換装置である、

請求項5記載の電力変換装置。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、例えば力率改善回路などの電力変換装置の制御回路と、当該電力変換装置とに関する。

#### 【背景技術】

#### 【0002】

例えば電流臨界モードで動作する力率改善回路（以下、PFC回路という。）においては、インダクタ電流が0になってからスイッチング素子をオンする必要がある。従って、インダクタ電流のゼロ点を正確に検出する必要がある（例えば、非特許文献1参照）。

#### 【先行技術文献】

#### 【特許文献】

#### 【0003】

【文献】Qingyun Huang et al., "Predictive ZVS Control with Improved ZVS Time Margin and Limited Variable Frequency Range for A 99%

10

20

30

40

50

**E f f i c i e n t , 1 3 0 W / i n 3 M H z G a N T o t e m - P o l e P F C R e c t i f i e r , " I E E E T r a n s a c t i o n s o n P o w e r E l e c t r o n i c s , V o l . 3 4 , N o . 7 , 2 0 1 8**

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0 0 0 4】**

従来、当該インダクタ電流の検出回路では、シャント抵抗とオペアンプ、コンパレータを用いて電流検出を行っていた（例えば、非特許文献1参照）。そのため、I Cの遅延や、ノイズ除去用のフィルタでの遅延が発生して、正確にゼロ検出を行うことができないという課題があった。

10

**【0 0 0 5】**

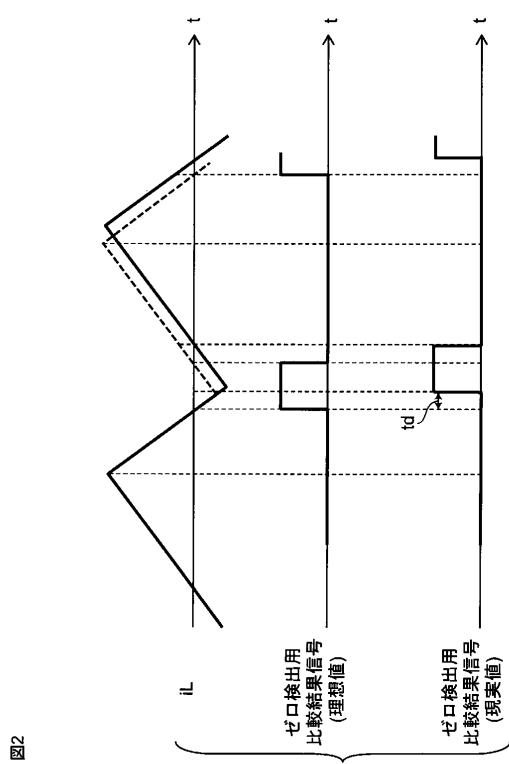

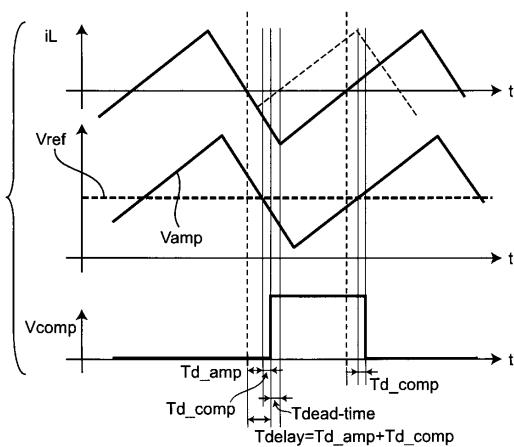

図2は従来例における電流検出回路におけるインダクタ電流*i<sub>L</sub>*のゼロ検出の遅延を説明するためのタイミングチャートである。図2において、ゼロ検出用比較結果信号の理想値と現実値を図示している。図2のt<sub>d</sub>は、オペアンプ及びノイズフィルタによる遅延のためのゼロ検出の遅延時間を示す。すなわち、コンパレータI Cの遅延やノイズフィルタの時定数により、理想値の電流ゼロ検出点から遅れてコンパレータが立ち上がるため、図2に示すように負電流が増加する。

**【0 0 0 6】**

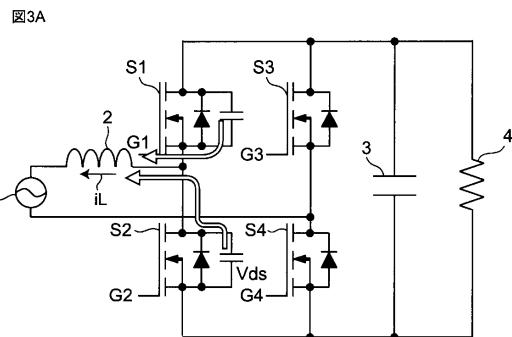

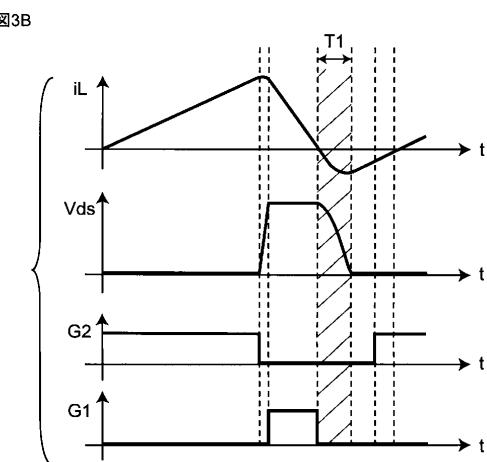

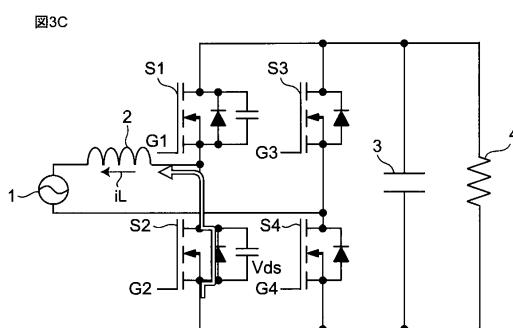

図3Aは前記インダクタ電流のゼロ検出の遅延によるスイッチング電源装置の損失が増加するメカニズムを説明するためのスイッチング電源装置の回路図であり、図3Bは図3Aのスイッチング電源装置の動作を示すタイミングチャートである。図3Aにおいて、スイッチング電源装置は、交流電源1と、インダクタ2と、スイッチング素子S1～S4と、平滑用キャパシタ3と、負荷抵抗4とを備える。図3Bにおいて、インダクタ電流*i<sub>L</sub>*と、スイッチング素子S2のドレイン・ソース間電圧V<sub>ds</sub>と、スイッチング素子S2に対する駆動信号G2と、スイッチング素子S1に対する駆動信号G1とを示す。ここで、T1は、インダクタ電流*i<sub>L</sub>*の負電流によりソフトスイッチングさせる期間を示す。

20

**【0 0 0 7】**

前記ソフトスイッチングによる遅延により、図3C及び図3Dに示すように、インダクタ電流*i<sub>L</sub>*の負電流はスイッチング素子S2のボディダイオードを流れる。この余分な負電流が流れることで、スイッチング電源装置の損失が増大する。

30

**【0 0 0 8】**

特に、小型大容量電源の開発過程においては、高周波でかつ大電流の検出を行う必要があり、それに対する解決手段が課題となっていた。

**【0 0 0 9】**

本発明の目的は以上の問題点を解決し、電流臨界モードで動作するPFC回路において、従来技術に比較して正確にインダクタ電流のゼロ点を正確に検出することができる電力変換装置の制御回路及び、当該電力変換装置を提供することにある。

**【課題を解決するための手段】**

**【0 0 1 0】**

本発明の一態様に係る電力変換装置の制御回路は、

インダクタを含み、電流臨界モードで動作する力率改善回路を含む電力変換装置の制御回路であって、

40

前記インダクタの電流、もしくは前記インダクタの電流に対応し又は前記インダクタの電流を含む電流を検出し、前記検出した電流に対応する電圧を所定の利得で增幅した後、検出電圧として出力する第1の検出回路と、

前記検出電圧を所定の基準電圧と比較して比較結果信号を出力する比較回路と、

前記電力変換装置の入力電圧を検出する第2の検出回路と、

前記電力変換装置の出力電圧を検出する第3の検出回路とを備え、

前記制御回路は、前記検出した入力電圧、前記検出した出力電圧、予め設定された遅延時間、前記インダクタのインダクタンス値、前記第1の検出回路により検出した電流を電

50

圧に変換するときの変換係数、電源電圧、及び前記利得に基づいて、前記インダクタの電流のゼロ値を検出するときの遅延を実質的にゼロにするための基準電圧を計算して前記比較回路に出力し、

前記比較回路は、

前記検出電圧を所定の第1の基準電圧と比較し、前記検出電圧が正から負に変化するゼロクロス検出点で第1の比較結果信号を出力する第1の比較器と、

前記検出電圧を前記第1の基準電圧よりも低い所定の第2の基準電圧と比較し、前記検出電圧が負から正に変化するゼロクロス検出点で第2の比較結果信号を出力する第2の比較器と、

前記第1の比較結果信号の立ち上がりを検出して第1のパルス信号を出力する第1のパルス生成回路と、

前記第2の比較結果信号の立ち上がりを検出して第2のパルス信号を出力する第2のパルス生成回路と、

セット端子、リセット端子及び出力端子を有するセットリセット型フリップフロップであって、前記第1のパルス信号をセット端子に入力し、前記第2のパルス信号をリセット端子に入力し、出力端子から前記比較回路の比較結果信号を出力するセットリセット型フリップフロップとを備えることを特徴とする。

#### 【発明の効果】

#### 【0011】

従って、本発明によれば、電流臨界モードで動作するPFC回路において、インダクタ電流の検出遅延を防止して、従来技術に比較して正確にインダクタ電流のゼロ点を正確に検出することができる。これにより、電力変換装置の損失が低減され、電源装置の高密度化につながる。

#### 【図面の簡単な説明】

#### 【0012】

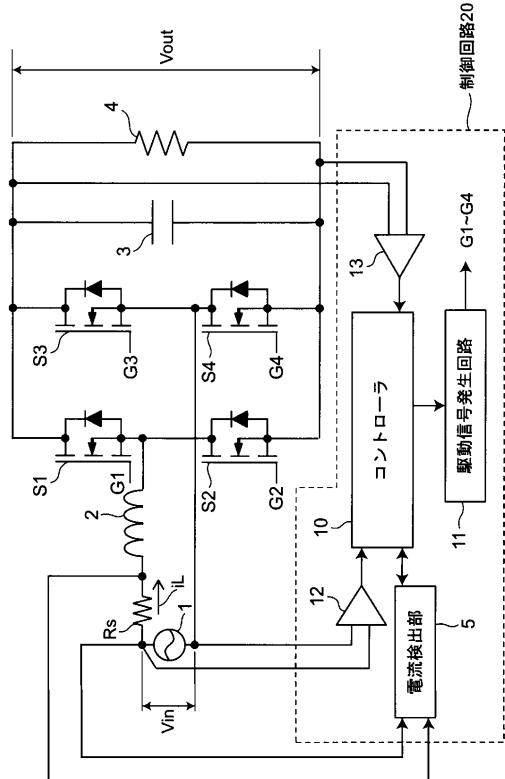

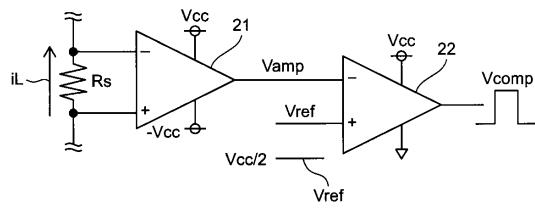

【図1A】実施形態1に係る制御回路20を備えたスイッチング電源装置の構成例を示す回路図である。

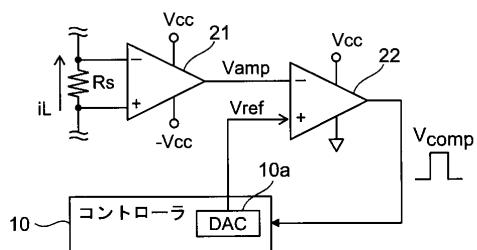

【図1B】図1Aの電流検出部5の構成例を示す回路図である。

【図2】従来例における電流検出回路におけるインダクタ電流のゼロ検出の遅延を説明するためのタイミングチャートである。

【図3A】前記インダクタ電流のゼロ検出の遅延によるスイッチング電源装置の損失が増加するメカニズムを説明するためのスイッチング電源装置の回路図である。

【図3B】図3Aのスイッチング電源装置の動作を示すタイミングチャートである。

【図3C】前記インダクタ電流のゼロ検出の遅延によるスイッチング電源装置の損失が増加するメカニズムを説明するためのスイッチング電源装置の回路図である。

【図3D】図3Cのスイッチング電源装置の動作を示すタイミングチャートである。

【図4A】従来例に係る電流検出部の構成例を示す回路図である。

【図4B】図4Aの電流検出部の動作を示すタイミングチャートである。

【図4C】実施形態に係る電流検出部5の構成例を示す回路図である。

【図4D】図4Cの電流検出部5の動作を示すタイミングチャートである。

【図5】実施形態1に係る電流検出部5の動作を示すグラフである。

【図6】実施形態1に係るPFC回路を用いた電力変換装置の構成例を示すブロック図である。

【図7】実施形態1に係る電流検出部5に用いる基準電圧Vrefの導出方法を説明するための波形図である。

【図8A】実施形態1に係る電流検出部5によるPFC回路のソフトスイッチングを説明するための波形図である。

【図8B】実施形態1に係る電流検出部5によるPFC回路のソフトスイッチングを説明するための波形図である。

【図9】変形例に係る電流検出部5に用いる基準電圧Vrefの導出方法を説明するため

10

20

30

40

50

の波形図である。

【図10A】変形例1に係るスイッチング電源装置の構成例を示すブロック図である。

【図10B】変形例2に係るスイッチング電源装置の構成例を示すブロック図である。

【図11A】変形例3に係るスイッチング電源装置の構成例を示すブロック図である。

【図11B】変形例4に係るスイッチング電源装置の構成例を示すブロック図である。

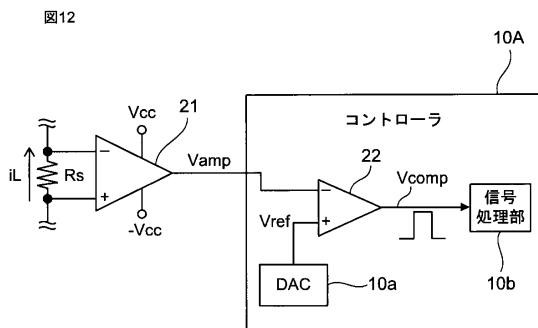

【図12】図1Bの電流検出部5の変形例を示す回路図である。

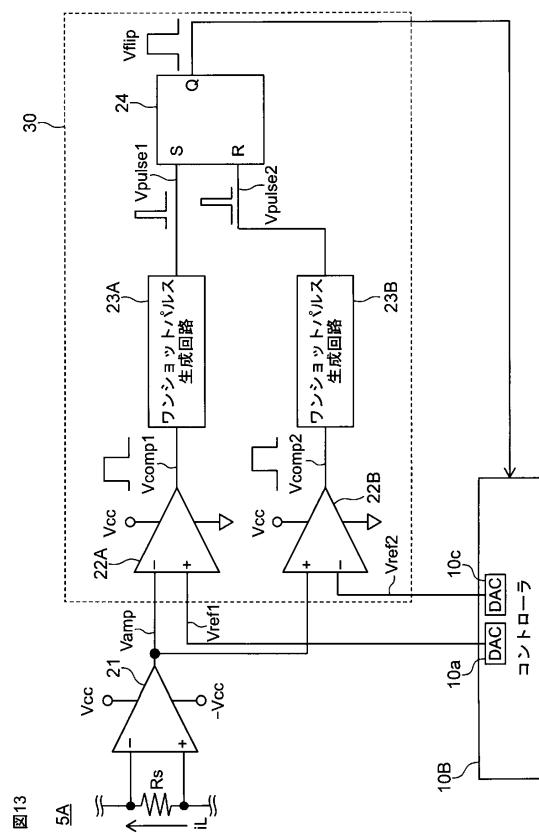

【図13】実施形態2に係る電流検出部5Aの構成例を示す回路図である。

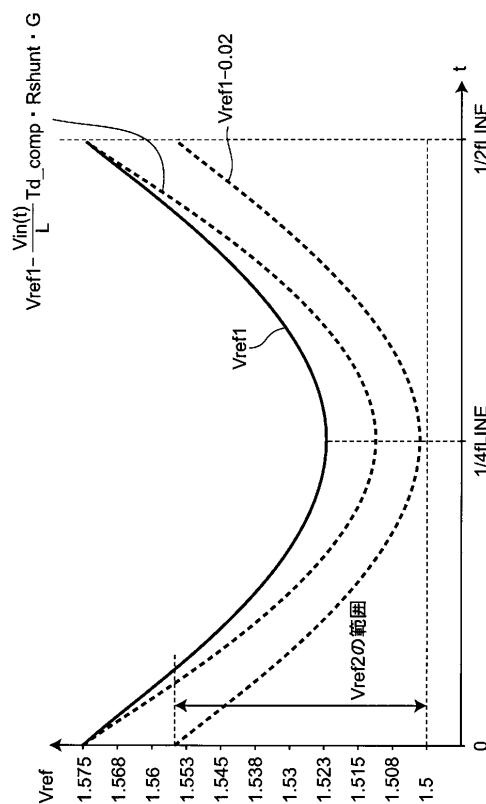

【図14】図13の電流検出部5Aに用いる基準電圧 $V_{ref1}$ ,  $V_{ref2}$ の導出方法を説明するための波形図である。

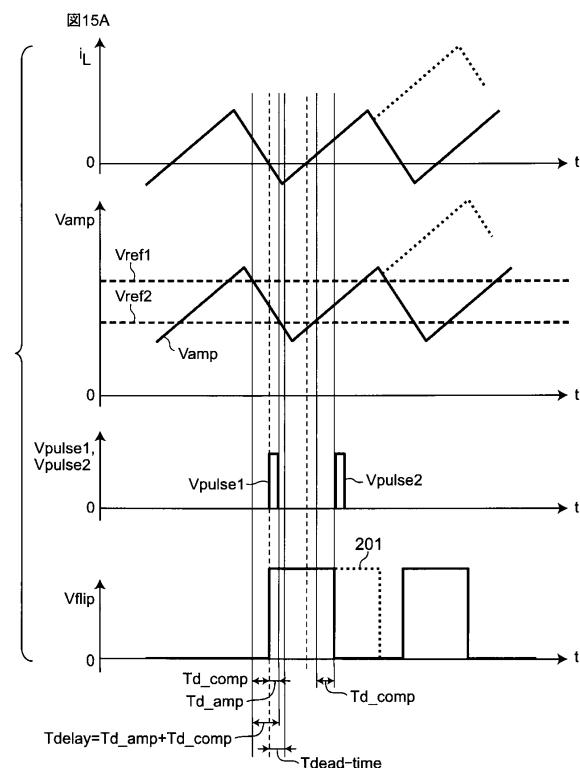

【図15A】図13の電流検出部5Aの動作を示すタイミングチャートである。 10

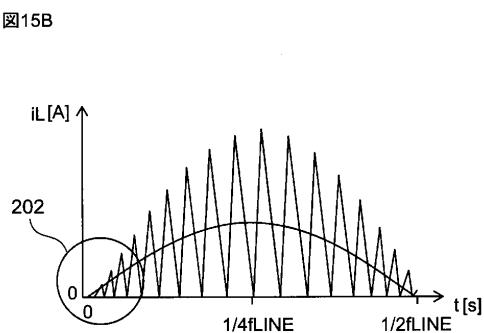

【図15B】実施形態1に係る電流検出部5の課題を説明するための図であって、インダクタ電流 $i_L$ を示す波形図である。

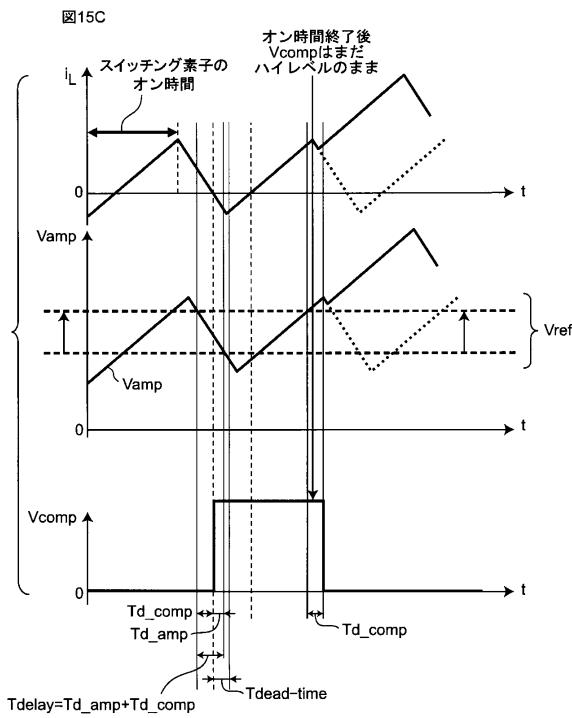

【図15C】実施形態1に係る電流検出部5の課題を説明するための図であって、図15Bの波形図の部分202に対応する各信号等のタイミングチャートである。

【図16】図13の電流検出部5Aの変形例を示す回路図である。

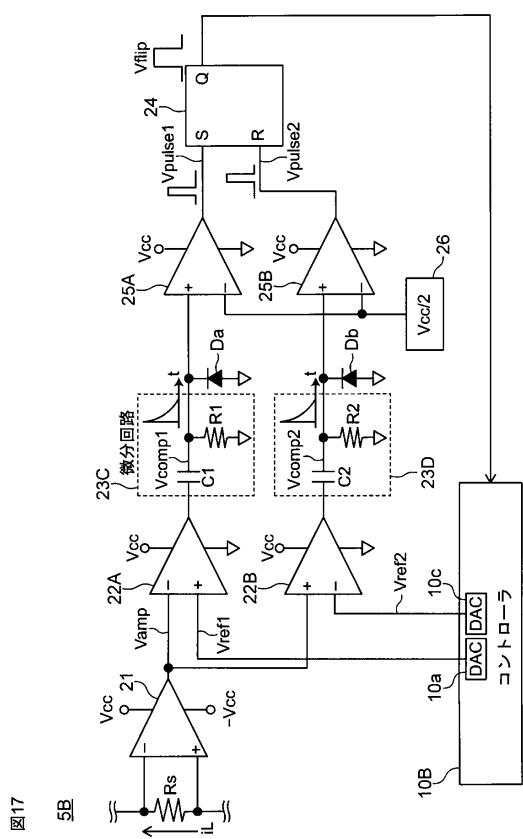

【図17】実施形態3に係る電流検出部5Bの構成例を示す回路図である。

【発明を実施するための形態】

【0013】

以下、本発明に係る実施形態について図面を参照して説明する。なお、同一又は同様の構成要素については同一の符号を付している。 20

【0014】

(実施形態1)

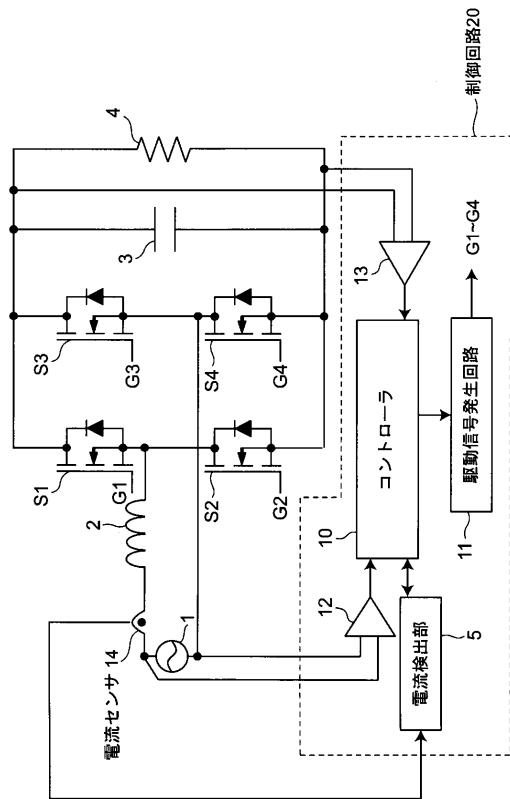

図1Aは実施形態1に係る制御回路20を備えたスイッチング電源装置の構成例を示す回路図である。

【0015】

図1Aにおいて、本実施形態に係るスイッチング電源装置は、交流電源1と、リクトルであるインダクタ2と、ブリッジ接続されたスイッチング素子S1～S4と、平滑用キャパシタ3と、負荷抵抗4と、シャント抵抗Rsと、制御回路20とを備える。ここで、制御回路20は、コントローラ10と、電流検出部5と、駆動信号発生回路11と、入力電圧検出回路12と、出力電圧検出回路13とを備える。 30

【0016】

交流電源1により発生された入力電圧 $V_{in}$ は、シャント抵抗Rs及びインダクタ2を介して、スイッチング素子S1～S4のブリッジ接続回路に入力される。各スイッチング素子S1～S4は駆動信号発生回路11からの駆動信号G1～G4によりオン／オフ制御されることで、入力電圧 $V_{in}$ がスイッチングされた後、平滑用キャパシタ3を介して、平滑された直流電圧が出力電圧 $V_{out}$ として負荷抵抗4に出力される。

【0017】

シャント抵抗Rsはインダクタ電流 $i_L$ を電圧値に変換して電流検出部5に出力する。入力電圧検出回路12は入力電圧 $V_{in}$ を検出してコントローラ10に出力し、出力電圧検出回路13は出力電圧 $V_{out}$ を検出してコントローラ10に出力する。コントローラ10は、入力される各信号に基づいて、例えば電流臨界モードで駆動信号G1～G4を発生するように駆動信号発生回路11を制御する。なお、コントローラ10は、詳細後述する方法で予め決められる基準電圧 $V_{ref}$ を発生するDA変換器10aを備える。 40

【0018】

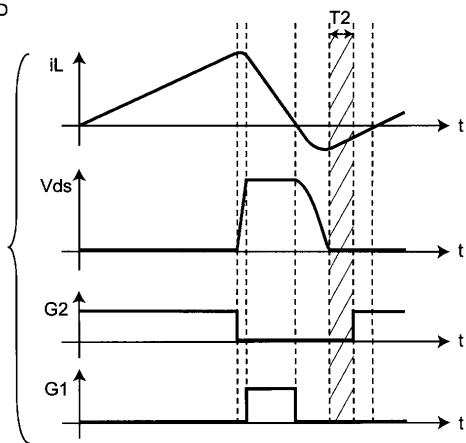

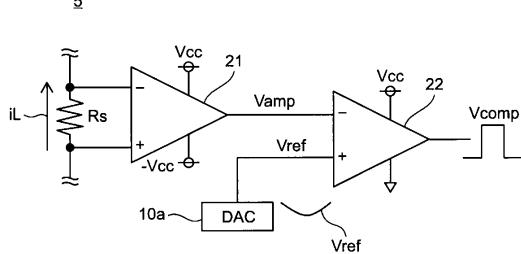

図1Bは図1Aの電流検出部5の構成例を示す回路図である。図1Bにおいて、電流検出部5は、オペアンプ21と、コンパレータ22とを備えて構成される。なお、 $V_{cc}$ は電源電圧である。

【0019】

オペアンプ21は、シャント抵抗Rsにより検出されたインダクタ電流 $i_L$ に対応する電圧を増幅し、増幅電圧 $V_{amp}$ をコンパレータ22に出力する。コンパレータ22は、 50

入力される増幅電圧  $V_{amp}$  を、コントローラ 10 内の DA 変換器 10a からの基準電圧  $V_{ref}$  と比較して、比較結果電圧  $V_{comp}$  を発生してコントローラ 10 に出力する。これに応答して、コントローラ 10 は、比較結果電圧  $V_{comp}$  に基づいて、インダクタ電流  $i_L$  のゼロ電流を検出し、これに基づいて、例えば電流臨界モードでのスイッチング動作をさせて駆動信号 G1 ~ G4 を発生するように駆動信号発生回路 11 を制御する。なお、基準電圧  $V_{ref}$  の極性は、PFC 回路への入力電圧  $V_{in}$  (図 1A) に応じて、すなわち、インダクタ電流  $i_L$  の向きに応じて反転される。

#### 【0020】

以上のように構成された制御回路 20 を備えたスイッチング電源装置によれば、コンパレータ 22 の基準電圧  $V_{ref}$  を遅延時間に応じて変化させることで、検出遅延を防止することができる。これにより、臨界モード PFC 回路におけるインダクタ電流  $i_L$  のゼロ点検出遅延による効率悪化を防止することができる。以下、本実施形態の作用効果について詳述する。

10

#### 【0021】

図 4A は従来例に係る電流検出部の構成例を示す回路図であり、図 4B は図 4A の電流検出部の動作を示すタイミングチャートである。図 4A に示すように、コンパレータ 22 の基準電圧  $V_{ref}$  が例えば  $V_{cc}/2$  等の一定電圧では、図 4B に示すように、遅延時間  $T_{delay}$  が発生する。

#### 【0022】

図 4C は実施形態 1 に係る電流検出部 5 の構成例を示す回路図であり、図 4D は図 4C の電流検出部 5 の動作を示すタイミングチャートである。図 4C に示すように、コントローラ 10 の DA 変換器 10a から、基準電圧  $V_{ref}$  を遅延時間に応じて上昇させる。すなわち、入力電圧が交流である PFC 回路において、入力電圧  $V_{in}$  に依存して基準電圧  $V_{ref}$  を変化させることで、図 4D に示すように、図 4B との比較により、遅延時間  $T_{delay}$  を減少させることができる。なお、図 4D において、

20

(1)  $T_{d\_amp}$  はオペアンプ 21 の増幅動作による遅延時間であり、

(2)  $T_{d\_comp}$  はコンパレータ 22 の比較動作による遅延時間であり、

(3)  $T_{dead-time}$  はスイッチング素子 S1, S2 のデッドタイムである。

#### 【0023】

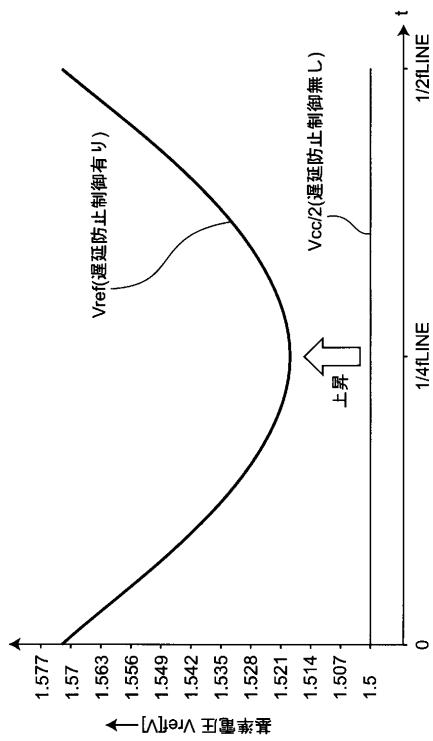

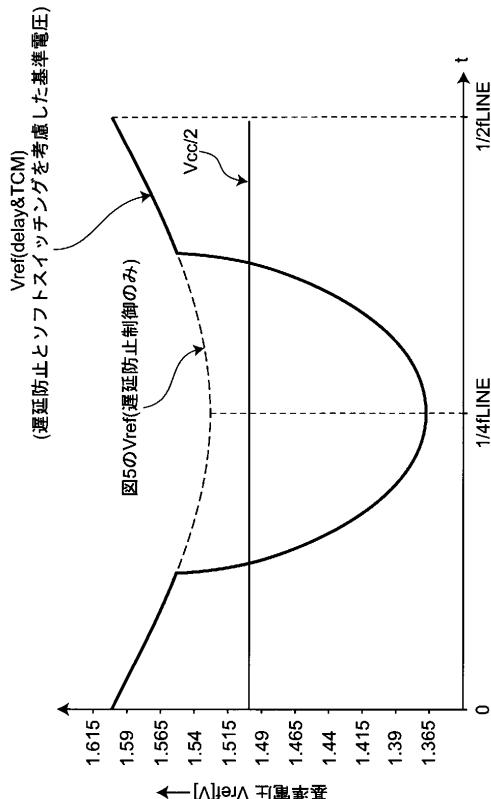

図 5 は実施形態 1 に係る電流検出部 5 の動作を示すグラフである。図 5 において、例えば、 $V_{cc} = 3V$ ,  $T_{delay} = 50\text{ ns}$ ,  $V_{in}(\text{rms}) = 200V$ ,  $f_{LINE} = 50\text{ Hz}$  のときの基準電圧  $V_{ref}$  (入力電圧  $V_{in}$  の半周期) の一例を図示している。図 1B 及び図 5C の電流検出部 5 及びコントローラ 10 を用いることで、遅延時間  $T_{delay}$  から導出された基準電圧  $V_{ref}$  を、電流検出部 5 のコンパレータ 22 に帰還して入力することで、遅延時間  $T_{delay}$  を減少させることができる。

30

#### 【0024】

以下、基準電圧  $V_{ref}$  の導出方法の一例について以下に説明する。

#### 【0025】

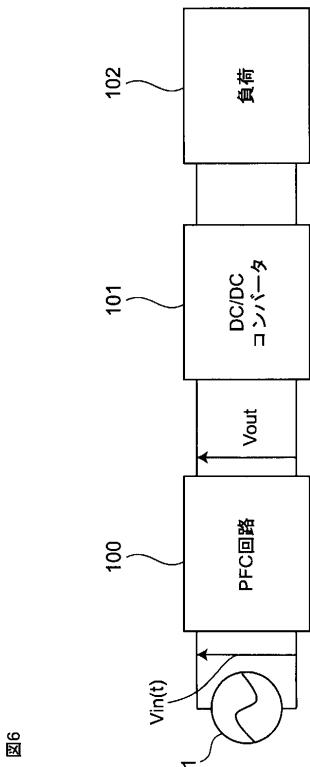

図 6 は実施形態 1 に係る PFC 回路を用いた電力変換装置の構成例を示すブロック図である。図 6 において、電力変換装置は、交流電源 1 と、PFC 回路 100 と、DC/DC コンバータ 101 と、負荷 102 とを備えて構成される。制御対象は PFC 回路であるため、入力交流電圧及び出力直流電圧であり、それぞれ  $V_{in}(t)$ 、 $V_{out}$  とする。入力電圧  $V_{in}(t)$  は次式で表される。

40

#### 【0026】

#### 【数 1】

$$V_{in}(t) = \sqrt{2} V_{in}(\text{rms}) \times \sin(2\pi f_{LINE} t)$$

#### 【0027】

ここで、入力電圧  $V_{in}(\text{rms})$  及びライン周波数  $f_{LINE}$  は国や地域によって異

50

なり、それらの一例は以下の通りである。

$V_{in} (\text{rms}) = 100 \text{ V}, 200 \text{ V}, 230 \text{ V}$

$f_{LINE} = 50 \text{ Hz}$ 、又は  $60 \text{ Hz}$

#### 【0028】

図1B及び図4Cの電流検出部5を用いたとき、シャント抵抗Rsの抵抗値をRsとし、オペアンプ21の利得をGとし、オペアンプ21及びコンパレータ22に印加する電圧をVccとする。

#### 【0029】

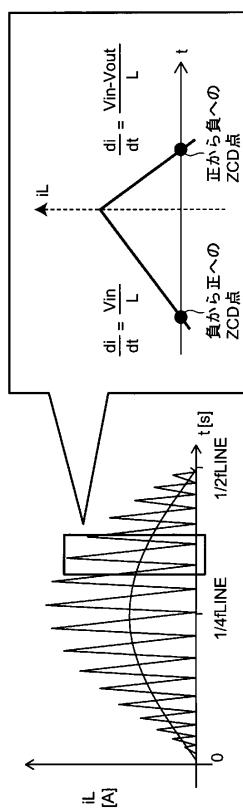

図7は実施形態1に係る電流検出部5に用いる基準電圧Vrefの導出方法を説明するための波形図である。

10

#### 【0030】

入力電圧Vinの半周期におけるインダクタ電流iLは、図7のグラフのようになり、1スイッチング周期分を抜き出した拡大図を右側に図示する。ここで、インダクタ電流iLの傾きはvin(t)、Vout、インダクタンス値Lにより求められる。電流ゼロの検出遅延時間Tdelayに基づいて、遅延時間中に変化する電流変動量idelayは次式で表される。

#### 【0031】

#### 【数2】

$$\Delta i_{delay} = \frac{V_{out} - v_{in}(t)}{L} T_{delay}$$

20

#### 【0032】

この電流変動量idelayだけ、早く電流ゼロを検出すればよい。当該電流変動量idelayに対してシャント抵抗の抵抗値Rs及びオペアンプ21の利得Gを乗算することで電圧に変換できるので、遅延時間を考慮した基準電圧Vrefは次式で表される。

#### 【0033】

#### 【数3】

$$V_{ref} = \frac{V_{out} - v_{in}(t)}{L} T_{delay} \cdot R_{shunt} \cdot G + \frac{V_{cc}}{2}$$

30

#### 【0034】

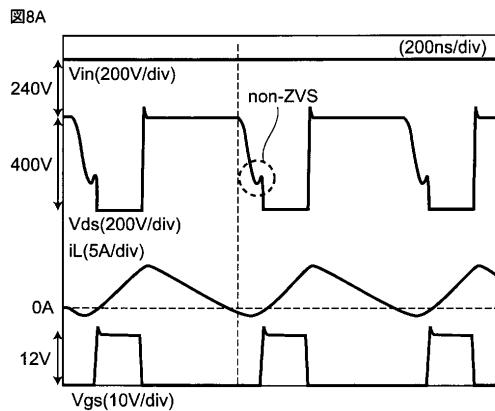

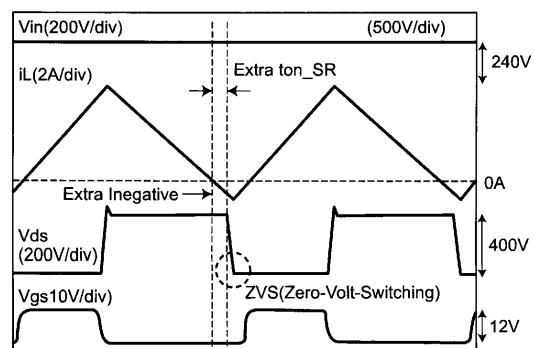

図8A及び図8Bは実施形態1に係る電流検出部5によるPFC回路のソフトスイッチングを説明するための波形図である。ここで、図8AはVin > Vout/2のときの波形図であり、図8Bは追加オン時間制御のときの波形図である。

#### 【0035】

本実施形態1では、公知のTCM(Triangular Current Mode)制御方法を用いて、コンパレータ22の基準電圧Vrefを変化させるのみでTCM制御を行うことを特徴としている。図8A及び図8Bにおいて、各符号は以下の通りである。

Vin : 入力電圧

Vds : メインスイッチ素子のドレイン・ソース間電圧

40

iL : インダクタ電流

Vgs : メインスイッチ素子のゲート・ソース間電圧

#### 【0036】

以上の実施形態1では、コントローラ10は、検出した入力電圧Vin及び出力電圧Vout、予め設定された遅延時間、インダクタ2のインダクタンス値、シャント抵抗Rsの抵抗値(後述する変形例では、電流検出時のインダクタ電流iLを電圧に変換するときの変換係数であり、一般的には、当該変換係数である。)、電源電圧Vcc、オペアンプ21の利得に基づいて、インダクタ電流iLのゼロ値を検出するときの遅延を実質的にゼロにするための基準電圧Vrefを計算してコンパレータ22に出力する。これにより、電流臨界モードで動作するPFC回路を備えた電力変換装置において、インダクタ電流の

50

検出遅延を防止して、従来技術に比較して正確にインダクタ電流のゼロ点を正確に検出することができる。

#### 【0037】

図8 A の  $V_{in} > V_{out}/2$  の条件下では、スイッチング素子の電荷を引き抜くための負電流が足りずソフトスイッチングできない。従って、TCM制御方法を用いて、同期整流スイッチ素子を、電流ゼロ検出点から所定の追加時間 [ns]だけオンし続けることによって電荷を引き抜くための負電流を流す。

#### 【0038】

図8 A 及び図8 B で図示したソフトスイッチング手法は + [ns] オンし続けて追加オン時間を与えることでソフトスイッチングに必要な負電流を流す。しかしながら、図9を参照して以下に示すように、基準電圧  $V_{ref}$  を変化させることでソフトスイッチングに必要な負電流を流すように調整することもできる。

10

#### 【0039】

図9は変形例に係る電流検出部5に用いる基準電圧  $V_{ref}$  の導出方法を説明するための波形図である。図9に示すように、図5の遅延防止制御のみの基準電圧  $V_{ref}$  に対して、所定の時間期間のみ例えば橢円形状で低下させる。ここで、ソフトスイッチングに必要な負電流は入力電圧  $V_{in}$ 、出力電圧  $V_{out}$  及びインダクタ2のインダクタンスより求めることができ、遅延時間を考慮した基準電圧  $V_{ref}$  に追加することで実現できる。

#### 【0040】

図10 A は変形例1に係るスイッチング電源装置の構成例を示すブロック図である。図1 A の実施形態1では、シャント抵抗  $R_s$  に流れるインダクタ電流  $i_L$  を検出しているが、本発明はこれに限らず、図10 A のように、例えばCT (Current Transformer)、ホール素子、GMR (Giant Magneto Resistive effect) 素子等の電流センサ14を用いてインダクタ電流  $i_L$  を検出してもよい。

20

#### 【0041】

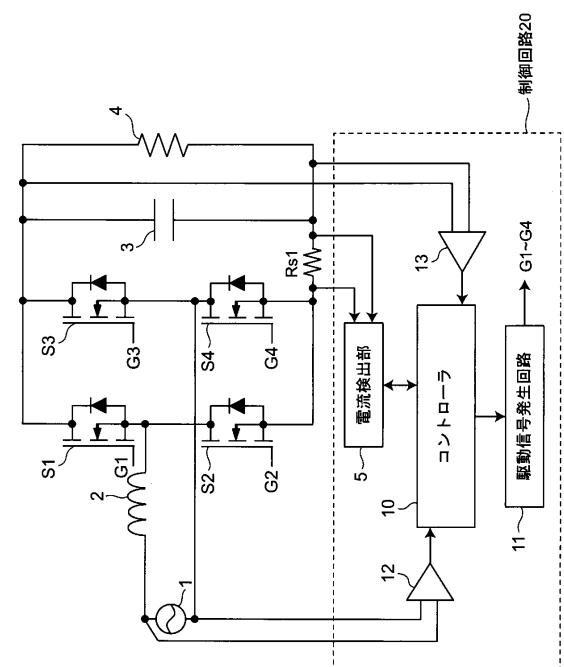

図10 B は変形例2に係るスイッチング電源装置の構成例を示すブロック図である。図10 Bにおいて、スイッチング素子 S2, S4 の接地側と負荷抵抗 4との間にシャント抵抗  $R_{s1}$  を挿入して、インダクタ電流  $i_L$  がゼロ点を検出してもよい。

#### 【0042】

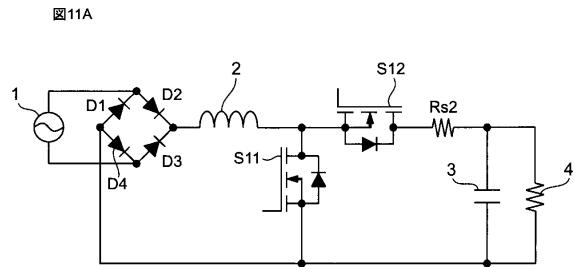

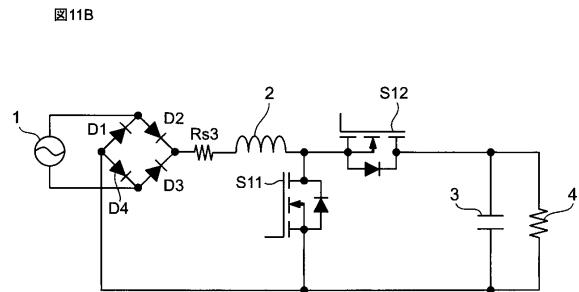

図11 A は変形例3に係るスイッチング電源装置の構成例を示すブロック図である。図11 A は同期整流方式昇圧型PFC回路の一例を示している。図11 Aにおいて、スイッチング電源装置は、交流電源1と、ブリッジ接続の4個のダイオード D1 ~ D4 と、リクトルであるインダクタ2と、スイッチング素子 S11, S12 と、シャント抵抗  $R_{s2}$  と、平滑用キャパシタ3と、負荷抵抗4とを備えて構成される。図11 Aにおいては、同期整流方式昇圧型PFC回路において、本実施形態を適用した場合は、スイッチング素子 S12 と平滑用キャパシタ3との間に、インダクタ電流  $i_L$  のゼロ点を検出するシャント抵抗  $R_{s2}$  を挿入することが好ましい。

30

#### 【0043】

図11 B は変形例4に係るスイッチング電源装置の構成例を示すブロック図である。図11 B の変形例4では、図11 A の変形例3に代えて、ダイオード D1, D4 とインダクタ2との間に、インダクタ電流  $i_L$  のゼロ点を検出するシャント抵抗  $R_{s3}$  を挿入してもよい。

40

#### 【0044】

以上の変形例2~4においては、インダクタ電流  $i_L$  に対応する電流又はインダクタ電流  $i_L$  を含む電流を検出するように構成している。

#### 【0045】

図12は図1 B の電流検出部5の変形例を示す回路図である。図12において、コントローラ10に代えて、DA変換器10a、コンパレータ22及び信号処理部10bを有するコントローラ10Aを備えたことを特徴とする。ここで、信号処理部10bはコンパレータ22からの比較結果信号  $V_{comp}$  に基づいて、上述の基準電圧  $V_{ref}$  を変更する

50

信号処理を行う。

#### 【0046】

DSP（デジタル・シグナル・プロセッサ）などのコントローラには、AD変換器、DA変換器だけでなく、コンパレータの機能も内蔵しているものがある。内蔵のコンパレータ22を使用することで外付けのコンパレータICが不要になるという利点がある。

#### 【0047】

以上説明したように、実施形態1及び変形例によれば、電流臨界モードで動作するPFC回路を備えた電力変換装置において、インダクタ電流の検出遅延を防止して、従来技術に比較して正確にインダクタ電流のゼロ点を正確に検出することができる。これにより、電力変換装置の損失が低減され、電源装置の高密度化につながる。特に、磁性体を使用しないので高周波駆動した際も損失が増加せず、追加部品が必要ない。また、基準電圧Vrefを変化させる手法を応用すれば、電圧共振を使用したソフトスイッチング機能を簡単に実装できる。

10

#### 【0048】

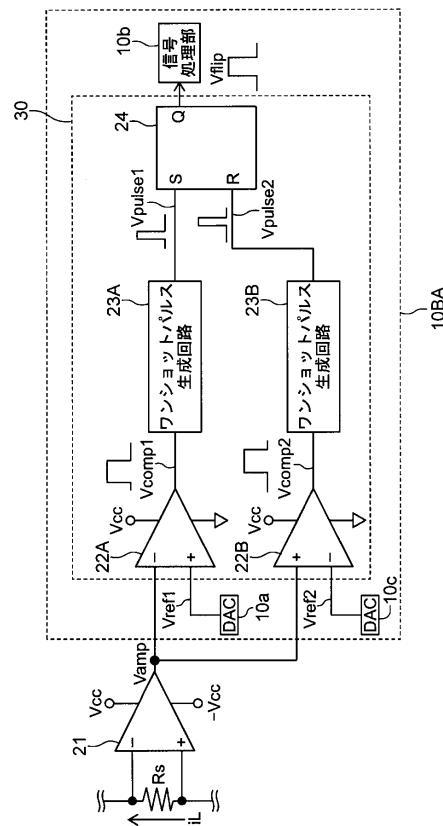

##### （実施形態2）

図13は実施形態2に係る電流検出部5Aの構成例を示す回路図である。図13において、実施形態2に係る電流検出部5Aは、図1Bの電流検出部5に比較して以下の相違点を有する。

（1）コンパレータ22に代えて、コンパレータ22A，22B、ワンショットパルス生成回路23A，23B、及びセットリセット型フリップフロップ24を備えた比較回路30を備えた。

20

（2）DAC10aを有するコントローラ10に代えて、DAC10a，10bを有するコントローラ10Bを備えた。

以下、上記の相違点について詳述する。

#### 【0049】

図13において、オペアンプ21は、シャント抵抗Rsにより検出されたインダクタ電流iLに対応する電圧を増幅し、増幅電圧Vampをコンパレータ22A，22Bに出力する。コントローラ10Bは、後述する所定の基準電圧Vref1を発生するDA変換器10aと、後述する所定の基準電圧Vref2を発生するDA変換器10cとを備える。

30

#### 【0050】

コンパレータ22Aは、入力される増幅電圧Vampを、コントローラ10B内のDA変換器10aからの基準電圧Vref1と比較して、比較結果電圧Vcomp1を発生してワンショットパルス生成回路23Aに出力する。また、コンパレータ22Bは、入力される増幅電圧Vamp2を、コントローラ10B内のDA変換器10cからの基準電圧Vref2と比較して、比較結果電圧Vcomp2を発生してワンショットパルス生成回路23Bに出力する。ここで、基準電圧Vref1，Vref2の電圧設定は図14を参照して後述する。

#### 【0051】

ワンショットパルス生成回路23A，23Bは例えばマルチプレクサバイブレータで構成され、各ワンショットパルス生成回路23A，23Bはそれぞれ、入力されるパルス信号の比較結果電圧Vcomp1，Vcomp2の立ち上がりに応答して1個のパルスを発生してセットリセット型フリップフロップ24のセット端子及びリセット端子に出力する。これに応答して、セットリセット型フリップフロップ24はゼロクロス検出パルス電圧Vf1ipをコントローラ10Bに出力する。さらに、コントローラ10Bは、ゼロクロス検出パルス電圧Vf1ipに基づいて、インダクタ電流iLのゼロ電流を検出し、これに基づいて、例えば電流臨界モードでのスイッチング動作をさせて駆動信号G1～G4を発生するように駆動信号発生回路11（図1A）を制御する。

40

#### 【0052】

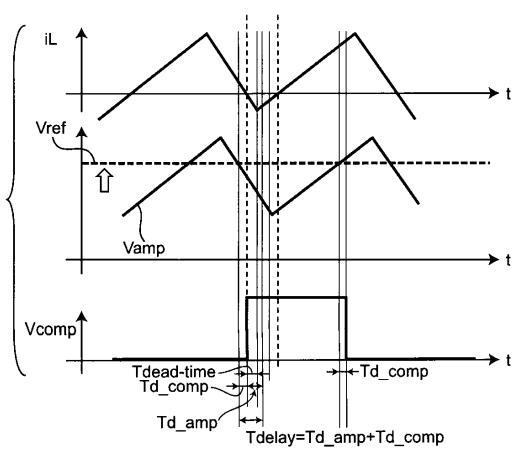

図14は図13の電流検出部5Aに用いる基準電圧Vref1，Vref2の導出方法を説明するための波形図であり、図15Aは図13の電流検出部5Aの動作を示すタイミ

50

ングチャートである。

#### 【0053】

図14に示すように、基準電圧 $V_{ref1}$ は実施形態1における基準電圧 $V_{ref}$ と同一の値に設定され、 $V_{cc}/2 < V_{ref1}$ に設定される。ここで、基準電圧 $V_{ref1}$ は、インダクタ電流 $i_L$ の正から負に変化するゼロクロス検出点（ZCD点）のタイミング（図7）を検出して、ゼロクロス検出点（ZCD点）の立ち上がりの遅延を補償する。一方、基準電圧 $V_{ref2}$ は $V_{ref2} < V_{ref1}$ のように設定され、インダクタ電流 $i_L$ の負から正に変化するゼロクロス検出点（ZCD点）のタイミング（図7）を検出して、ゼロクロス検出パルス電圧 $V_{f1ip}$ のパルス幅を短くすることに貢献する。

#### 【0054】

すなわち、図13のコンパレータ22Aは、PFC回路への入力電圧 $V_{in}$ （図1A）が正極性のとき、 $V_{ref1} > V_{cc}/2$ であり、コンパレータ22Aは、インダクタ電流 $i_L$ の正から負に変化するタイミングを検出し、それを示す比較結果電圧 $V_{comp1}$ を出力する。これにより、ゼロクロス検出パルス電圧 $V_{f1ip}$ の立ち上がり遅延を解消する。また、コンパレータ22Bは、PFC回路への入力電圧 $V_{in}$ （図1A）が正極性のとき、 $V_{ref2} < V_{ref1}$ であり、インダクタ電流 $i_L$ の負から正に変化するタイミングを検出し、それを示す比較結果電圧 $V_{comp2}$ を出力する。これにより、ゼロクロス検出パルス電圧 $V_{f1ip}$ の立ち下がり遅延を解消する。なお、ここで、PFC回路への入力電圧 $V_{in}$ （図1A）が正極性のときについて説明しているが、負極性のときは上述の基準電圧 $V_{ref}$ の反転と同様に、基準電圧 $V_{ref1}, V_{ref2}$ も反転され、コンパレータ22A, 22Bは、これら極性の反転を除いて同様に動作する。

#### 【0055】

基準電圧 $V_{ref1}$ の場合、図7の「ゼロクロス検出点」を正確に検出する必要があるため正確な計算で導出した（実施形態1）が、基準電圧 $V_{ref2}$ の役割はゼロクロス検出パルス電圧 $V_{f1ip}$ のパルス幅を短くする（図15Aの201）ことなので、正確に図7の「負から正に変化するゼロクロス検出点（ZCD点）に合わせる必要はない。

#### 【0056】

図15B及び図15Cは実施形態1に係る電流検出部5の課題を説明するための図であって、図15Bはインダクタ電流 $i_L$ を示す波形図であり、図15Cは図15Bの波形図の部分202に対応する各信号等のタイミングチャートである。実施形態1に係る図5から明らかのように、ゼロクロス点付近の基準電圧 $V_{ref}$ は相対的に大きくなる。また、高周波駆動の場合は、インダクタンス値 $L$ が比較的小さいため、インダクタ電流 $i_L$ の傾きが急になり、スイッチング素子のオン時間（ $d_i/dt$ が正の時間）が短くなる。その結果、図15B（インダクタ電流 $i_L$ の部分202）及び図15Cに示すように、比較結果電圧 $V_{comp}$ の立下がりが遅延して、比較結果電圧 $V_{comp}$ において連続的にオン状態が発生するという実施形態1の課題があった。

#### 【0057】

上述のように、正確に図7の「負から正に変化するゼロクロス検出点（ZCD点）に合わせる必要はないが、ただし、図15B及び図15Cに示すようコンパレータ22A, 22Bの遅延時間 $T_{d\_comp}$ 分だけは早める必要があるので、次式を満たすように設定すれば、図15Aに示すように2回のオン状態を防止できる。

#### 【0058】

##### 【数4】

$$V_{ref2} < V_{ref1} - \frac{v_{in}(t)}{L} T_{d\_comp} \cdot R_{shunt} \cdot G$$

#### 【0059】

上式と $V_{ref2} < V_{ref1}$ の関係を満たせば、基準電圧 $V_{ref2}$ は例えば、

(1)  $V_{ref2} = V_{cc}/2$ 、もしくは

10

20

30

40

50

(2)  $V_{ref2} = V_{ref1} - (\text{定数})$

など、どの様な値に設定してもよい。また、電流臨界モード（CRM）で動作するPFC回路の場合、インダクタ電流*i<sub>L</sub>*は、入力されるAC電圧が正極性のとき、ほとんど負側に流れないので、基準電圧*V<sub>ref2</sub>*は以下の範囲に設定するのが妥当である

【0060】

【数5】

$$\frac{V_{CC}}{2} < V_{ref2} < V_{ref1} - \frac{v_{in}(t)}{L} T_{d\_comp} \cdot R_{shunt} \cdot G$$

10

【0061】

以上説明したように、本実施形態において、基準電圧*V<sub>ref2</sub>*は、図14に示すよう上式を満たすように設定すればよい。

【0062】

図16は図13の電流検出部5Aの変形例を示す回路図である。図16において、コントローラ10Bに代えて、DA変換器10a, 10b、比較回路30、及び信号処理部10bを有するコントローラ10BAを備えたことを特徴とする。ここで、信号処理部10bはセットリセット型フリップフロップ24からのゼロクロス検出パルス電圧*V<sub>f1ip</sub>*に基づいて、上述の基準電圧*V<sub>ref1</sub>*, *V<sub>ref2</sub>*を変更する信号処理を行う。

【0063】

なお、実施形態1に係る変形例1～4に係るスイッチング電源装置において、実施形態2に係る図13の電流検出部5Aを適用してもよい。

【0064】

以上説明したように、実施形態2及び変形例によれば、電流臨界モードで動作するPFC回路を備えた電力変換装置において、インダクタ電流の検出遅延を防止して、従来技術に比較して正確にインダクタ電流のゼロ点を正確に検出することができる。これにより、電力変換装置の損失が低減され、電源装置の高密度化につながる。特に、磁性体を使用しないので高周波駆動した際も損失が増加せず、追加部品が必要ない。また、基準電圧*V<sub>ref</sub>*を変化させる手法を応用すれば、電圧共振を使用したソフトスイッチング機能を簡単に実装できる。

30

【0065】

（実施形態3）

図17は実施形態3に係る電流検出部5Bの構成例を示す回路図である。図17において、実施形態3に係る電流検出部5Bは、実施形態2に係る電流検出部5Aに比較して以下の相違点がある。

(1) ワンショットパルス生成回路23Aに代えて、微分回路23C、保護ダイオードD<sub>a</sub>及びコンパレータ25Aの回路を備えた。

(2) ワンショットパルス生成回路23Bに代えて、微分回路23D、保護ダイオードD<sub>b</sub>及びコンパレータ25Bの回路を備えた。

以下、前記相違点について説明する。

40

【0066】

図17において、微分回路23CはキャパシタC1及び抵抗R1を備えて構成される。微分回路23Cの出力端子に、負電流を接地に流して負電圧を出力しない保護ダイオードD<sub>a</sub>を備える。微分回路23Cから出力される微分電圧は保護ダイオードD<sub>a</sub>を介して、基準電圧発生器26からの基準電圧*V<sub>cc/2</sub>*が印加されたコンパレータ25Aに入力される。コンパレータ25Aは、入力される微分電圧を基準電圧*V<sub>cc/2</sub>*と比較して、比較結果電圧*V<sub>pulse1</sub>*をセットリセット型フリップフロップ24に出力する。

【0067】

微分回路23DはキャパシタC2及び抵抗R2を備えて構成される。微分回路23Dの出力端子に、負電流を接地に流して負電圧を出力しない保護ダイオードD<sub>b</sub>を備える。微

50

分回路 2 3 D から出力される微分電圧は保護ダイオード D b を介して、基準電圧発生器 2 6 からの基準電圧 V c c / 2 が印加されたコンパレータ 2 5 B に入力される。コンパレータ 2 5 B は、入力される微分電圧を基準電圧 V c c / 2 と比較して、比較結果電圧 V p u l s e 2 をセットリセット型フリップフロップ 2 4 に出力する。

#### 【 0 0 6 8 】

以上のように構成された電流検出部 5 B は、上記の構成の違いを除いて、図 1 3 の電流検出部 5 A と同様に動作する。

#### 【 0 0 6 9 】

なお、実施形態 1 に係る変形例 1 ~ 4 に係るスイッチング電源装置において、実施形態 2 に係る図 1 7 の電流検出部 5 B を適用してもよい。また、電流検出部 5 B を図 1 6 のコントローラ 1 0 B A のごとく構成してもよい。10

#### 【 0 0 7 0 】

以上のように構成された実施形態 3 及び変形例においても、実施形態 1 及び 2 と同様の作用効果を有する。

#### 【 0 0 7 1 】

##### ( 適用例 )

以上の実施形態又は変形例においては、スイッチング電源装置について説明しているが、本発明はこれに限らず、スイッチング電源装置を含む種々の電力変換装置に適用することができる。

#### 【 産業上の利用可能性 】

#### 【 0 0 7 2 】

以上詳述したように、本発明によれば、電流臨界モードで動作する P F C 回路において、インダクタ電流の検出遅延を防止して、従来技術に比較して正確にインダクタ電流のゼロ点を正確に検出することができる。これにより、電力変換装置の損失が低減され、電源装置の高密度化につながる。20

#### 【 符号の説明 】

#### 【 0 0 7 3 】

1 交流電源

2 インダクタ

3 平滑用キャパシタ

4 負荷抵抗

5 , 5 A , 5 B 電流検出部

1 0 , 1 0 A , 1 0 B , 1 0 B A コントローラ

1 0 a , 1 0 c D A 変換器 ( D A C )

1 0 b 信号処理部

1 1 駆動信号発生回路

1 2 入力電圧検出回路

1 3 出力電圧検出回路

1 4 電流センサ

2 0 制御回路

2 1 オペアンプ

2 2 , 2 2 A , 2 2 B コンパレータ

2 3 A , 2 3 B ワンショットパルス生成回路

2 3 C , 2 3 D 微分回路

2 4 セットリセット型フリップフロップ

2 5 S , 2 5 B コンパレータ

2 6 基準電圧発生器

3 0 比較回路

1 0 0 P F C 回路

1 0 1 D C / D C コンバータ

10

20

30

40

50

102 負荷

C1, C2 キャパシタ

D1 ~ D4 ダイオード

Da, Db 保護ダイオード

R1, R2 抵抗

Rs, Rs1, Rs2, Rs3 シャント抵抗

S1 ~ S4, S11, S12 スイッチング素子

【図面】

【図1A】

図1A

【図1B】

図1B

電流検出部 5

10

20

30

40

50

【図 2】

【図 3 A】

10

【図 3 B】

【図 3 C】

30

40

50

【図 3 D】

図3D

【図 4 A】

図4A

10

【図 4 B】

図4B

【図 4 C】

図4C

20

30

40

50

【図 4 D】

図4D

【図 5】

10

20

図5

【図 6】

【図 7】

30

40

図7

50

【図 8 A】

【図 8 B】

【図 9】

【図 10 A】

10

20

30

40

50

【図 10B】

図10B

【図 11A】

10

20

【図 11B】

図11B

【図 12】

30

40

50

【図 1 3】

【図 1 4】

【図 1 5 A】

【図 1 5 B】

【図 15C】

【図16】

【図17】

10

20

30

40

50

---

フロントページの続き

不動堂町 801 番地 オムロン株式会社内

(72)発明者 長岡 真吾

京都府京都市下京区塩小路通堀川東入南不動堂町 801 番地 オムロン株式会社内

審査官 柳下 勝幸

(56)参考文献 特開 2015 - 35851 (JP, A)

特開 2014 - 18012 (JP, A)

特開 2011 - 244583 (JP, A)

(58)調査した分野 (Int.Cl., DB名)

H02M 7/12

H02M 3/155