【公報種別】特許法第17条の2の規定による補正の掲載

【部門区分】第6部門第4区分

【発行日】平成24年9月27日(2012.9.27)

【公開番号】特開2012-123881(P2012-123881A)

【公開日】平成24年6月28日(2012.6.28)

【年通号数】公開・登録公報2012-025

【出願番号】特願2010-275370(P2010-275370)

【国際特許分類】

G 11 C 11/401 (2006.01)

H 01 L 27/04 (2006.01)

H 01 L 21/822 (2006.01)

G 11 C 11/4074 (2006.01)

G 11 C 11/4093 (2006.01)

【F I】

G 11 C 11/34 3 7 1 K

H 01 L 27/04 D

H 01 L 27/04 H

G 11 C 11/34 3 5 4 F

G 11 C 11/34 3 5 4 Q

【手続補正書】

【提出日】平成24年8月13日(2012.8.13)

【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

【補正の内容】

【特許請求の範囲】

【請求項1】

第1の外部電圧が供給される複数の第1の電源パッドと、

複数のデータ出力パッドと、

前記複数の第1の電源パッドに共通接続された第1の電源線と、

前記第1の電源線に共通に接続されるとともに、それぞれが前記複数のデータ出力パッドのうちの対応する1つに接続された複数の出力バッファと、

それぞれが前記第1の電源線と前記複数の出力バッファのうちの対応する1つとの間に挿入された複数のローパスフィルタ回路と、を備えることを特徴とする半導体装置。

【請求項2】

第2の外部電圧が供給される複数の第2の電源パッドと、

前記複数の第2の電源パッドに共通に接続された第2の電源線と、を更に備え、

前記複数のローパスフィルタ回路のそれぞれは、前記第1の電源線と前記複数の出力バッファのうちの前記対応する1つとの間に直列接続された第1の抵抗素子と、前記第1の抵抗素子の一端に一方の電極が接続され他方の電極が前記第2の電源線に接続された第1の容量素子とを含むことを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記複数のローパスフィルタ回路のそれぞれは、前記第2の電源線と前記複数の出力バッファのうちの対応する1つとの間に直列に接続された第2の抵抗素子と、前記第2の抵抗素子の一端に一方の電極が接続され他方の電極が前記第1の電源線に接続された第2の容量素子とをさらに含むことを特徴とする請求項2に記載の半導体装置。

【請求項4】

前記複数のローパスフィルタ回路のそれぞれの前記第1の抵抗素子が、第1のトランジスタを含むことを特徴とする請求項2に記載の半導体装置。

**【請求項5】**

前記複数のローパスフィルタ回路のそれぞれの前記第1のトランジスタの制御電極に、制御信号を供給する制御回路であって、前記第1及び第2の外部電圧の供給開始後の第1の期間前記複数のローパスフィルタ回路のそれぞれの前記第1のトランジスタを非導通状態とする前記制御回路をさらに備えることを特徴とする請求項4に記載の半導体装置。

**【請求項6】**

前記第1の外部電圧に基づいて第1の内部電圧を生成する第1の内部電圧生成回路をさらに備え、前記制御回路は、前記電源投入後の前記第1の期間に続く第2の期間に、前記複数のローパスフィルタ回路のそれぞれの前記第1のトランジスタの前記制御電極に前記第1の内部電圧を供給して前記複数のローパスフィルタ回路のそれぞれの前記第1のトランジスタを導通状態とすることを特徴とする請求項5に記載の半導体装置。

**【請求項7】**

前記第1の外部電圧に基づいて第2の内部電圧を生成する第2の内部電圧生成回路と、前記複数の出力バッファに入力信号を供給する内部回路とをさらに備え、前記内部回路は前記第2の内部電圧によって動作することを特徴とする請求項5に記載の半導体装置。

**【請求項8】**

前記複数の第1の電源パッドと前記第2の内部電圧生成回路との間に挿入された第2のトランジスタをさらに備え、

前記制御回路は、前記制御信号を前記第2のトランジスタの制御電極に供給することを特徴とする請求項7に記載の半導体装置。

**【請求項9】**

前記第1の内部電圧は前記第1の外部電圧よりも高く、前記第2の内部電圧は前記第1の外部電圧よりも低いことを特徴とする請求項7に記載の半導体装置。

**【請求項10】**

一対のデータストローブパッドと、

前記第1の電源線に共通に接続され、前記複数の出力バッファのそれぞれが前記複数のデータ出力パッドのうちの対応する1つを駆動するタイミングと実質的に同じタイミングで前記一対のデータストローブパッドを駆動する一対のストローブバッファとをさらに備えることを特徴とする請求項1に記載の半導体装置。

**【請求項11】**

第1の外部電圧が供給される複数の第1の電源パッドと、

複数のデータ出力パッドと、

前記複数の第1の電源パッドに共通接続された第1の電源線と、

それぞれが前記第1の電源線から供給される前記第1の外部電圧で動作し、活性化されると前記複数のデータ出力パッドのうちの対応する1つを第1及び第2の論理レベルのうちの一方で駆動する複数の出力バッファと、

それぞれが前記複数の出力バッファのうちの対応する1つに対応して設けられ、前記複数の出力バッファのうちの対応する1つが動作したときに発生しうるノイズが、前記複数の出力バッファのうちの対応する1つから前記第1の電源線に伝播する前に前記ノイズを取り除く、複数のローパスフィルタ回路と、を備えることを特徴とする半導体装置。

**【請求項12】**

第2の外部電圧が供給される複数の第2の電源パッドと、

前記複数の第2の電源パッドに共通に接続された第2の電源線と、を更に備え、

前記複数のローパスフィルタ回路のそれぞれは、前記第1の電源線と前記複数の出力バッファのうちの前記対応する1つとの間に直列接続された第1の抵抗素子と、前記第1の抵抗素子の一端に一方の電極が接続され他方の電極が前記第2の電源線に接続された第1の容量素子とを含むことを特徴とする請求項11に記載の半導体装置。

**【請求項 1 3】**

前記複数のローパスフィルタ回路のそれぞれは、前記第2の電源線と前記複数の出力バッファのうちの対応する1つとの間に直列に接続された第2の抵抗素子と、前記第2の抵抗素子の一端に一方の電極が接続され他方の電極が前記第1の電源線に接続された第2の容量素子とをさらに含むことを特徴とする請求項12に記載の半導体装置。

**【請求項 1 4】**

前記複数のローパスフィルタ回路のそれぞれの前記第1の抵抗素子が、第1のトランジスタを含むことを特徴とする請求項12に記載の半導体装置。

**【請求項 1 5】**

前記複数のローパスフィルタ回路のそれぞれの前記第1のトランジスタの制御電極に、制御信号を供給する制御回路であって、前記第1及び第2の外部電圧の供給開始後の第1の期間前記複数のローパスフィルタ回路のそれぞれの前記第1のトランジスタを非導通状態とする前記制御回路をさらに備えることを特徴とする請求項14に記載の半導体装置。

**【請求項 1 6】**

前記第1の外部電圧に基づいて第1の内部電圧を生成する第1の内部電圧生成回路をさらに備え、前記制御回路は、前記電源投入後の前記第1の期間に続く第2の期間に、前記複数のローパスフィルタ回路のそれぞれの前記第1のトランジスタの前記制御電極に前記第1の内部電圧を供給して前記複数のローパスフィルタ回路のそれぞれの前記第1のトランジスタを導通状態とすることを特徴とする請求項15に記載の半導体装置。

**【請求項 1 7】**

前記第1の外部電圧に基づいて第2の内部電圧を生成する第2の内部電圧生成回路と、前記複数の出力バッファに入力信号を供給する内部回路とをさらに備え、前記内部回路は前記第2の内部電圧によって動作することを特徴とする請求項15に記載の半導体装置。

**【請求項 1 8】**

前記複数の第1の電源パッドと前記第2の内部電圧生成回路との間に挿入された第2のトランジスタをさらに備え、

前記制御回路は、前記制御信号を前記第2のトランジスタの制御電極に供給することを特徴とする請求項17に記載の半導体装置。

**【請求項 1 9】**

前記第1の内部電圧は前記第1の外部電圧よりも高く、前記第2の内部電圧は前記第1の外部電圧よりも低いことを特徴とする請求項17に記載の半導体装置。

**【請求項 2 0】**

前記複数のデータ出力パッドが複数のデータストローブパッドを含み、前記複数の出力バッファが、それぞれが前記複数のデータストローブパッドのうちの対応する1つを前記第1及び第2の論理レベルのうちの一方に駆動する複数のストローブバッファを含むことを特徴とする請求項11に記載の半導体装置。

**【手続補正2】**

【補正対象書類名】明細書

【補正対象項目名】0 0 0 9

【補正方法】変更

【補正の内容】

【0 0 0 9】

【図1】本発明の好ましい実施形態による半導体装置10の構成を示すブロック図である。

【図2】半導体装置10のレイアウトを説明するための全体図である。

【図3】データ入出力回路70におけるデータ出力回路700のプロック図である。

【図4】本発明の好ましい実施形態による複数のデータ出力回路700と、これらに電源を供給する電源幹線及び電源パッドやデータ出力パッド等を示す模式図である。

【図5】本発明の好ましい第1の実施形態による半導体装置におけるローパスフィルタ回路1000の詳細を説明するための模式図である。

【図6】半導体装置10における電源投入後（パワーオンリセット信号PONが入力されてから）の電源電圧VDDと内部電圧VPERIの時間経過にともなう電位変化を示す図である。

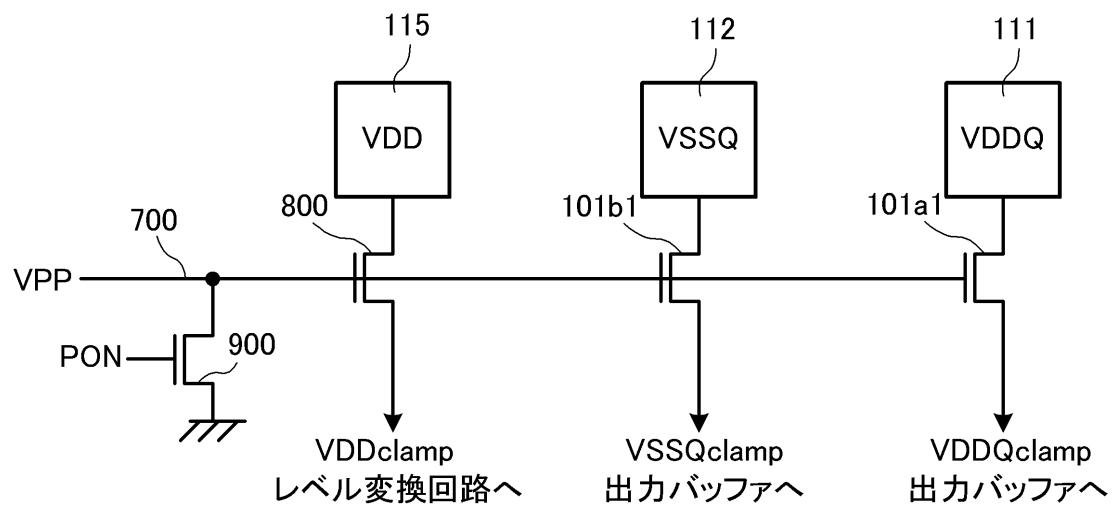

【図7】図6に示す問題の対応を説明するための模式図である。

【図8】図7に示す問題の対応を行った半導体装置10における電源投入後（パワーオンリセット信号PONが入力されてから）の電源電圧VDDと内部電圧VPERIの時間経過にともなう電位変化を示す図である。

【図9】第2の実施形態による半導体装置におけるローパスフィルタ回路1000の詳細を説明するための模式図である。

【手続補正3】

【補正対象書類名】明細書

【補正対象項目名】0023

【補正方法】変更

【補正の内容】

【0023】

以上が本実施形態による半導体装置10の全体構成である。図1に示した各要素のうち、パッド群100は2つのパッド列に配置され、アレイ系回路200はメモリセルアレイ領域に配置され、その他の周辺回路300は周辺回路領域に配置される。ここで、パッド群100とは、上述の通り、クロック端子11a, 11b、コマンド端子12a～12e、アドレス端子13、データ入出力端子14、電源端子15a, 15b、データ入出力用の電源端子16a, 16b及びデータストローブ端子17a, 17bを含む外部端子群である。一方、アレイ系回路200とは、メモリセルアレイ60、ロウデコーダ61、カラムデコーダ62、センス回路63及びデータアンプ64からなる回路群である。また、周辺回路300とは、アレイ系回路200を除く他の全ての回路である。

【手続補正4】

【補正対象書類名】明細書

【補正対象項目名】0044

【補正方法】変更

【補正の内容】

【0044】

図6に示すように、パワーオンリセット信号PONの電位の上昇とともに電源電圧VDDの電位も上昇するが内部電源発生回路によって生成される内部電圧VPERIの電位は初期段階において不定である。このため、例えば、図3に示すデータ出力回路700において、電源電圧VDDと接地電圧VSSとの間で動作するレベル変換回路711, 712内のPチャネル型MOSトランジスタとNチャネル型MOSトランジスタがともにオンし、貫通電流が流れてしまうこととなる。これにより、電源電圧VDDの電位も期待値まで上がらないという問題が生じ、したがって、内部電圧VPERIの電位も予定の電位まで上がらないことになってしまう。

【手続補正5】

【補正対象書類名】明細書

【補正対象項目名】0045

【補正方法】変更

【補正の内容】

【0045】

このような問題に対応する構成を図7に示す。図7に示すように、電源電圧VDDが供給される電源パッド115に接続される電源配線にNチャネル型MOSトランジスタ800を挿入し、このゲート電極に内部電圧VPPを入力させるとともに、電源投入後の一定期間、トランジスタ800をオフさせるスイッチ回路900を設ける。スイッチ回路900としては、ゲート電極にパワーオンリセット信号PONを受け、ドレイン電極が内部電圧VPPの供給ライン700に接続され、ソース電極が接地電圧に接続されたNチャネル

型MOSトランジスタにより構成することができる。

【手続補正6】

【補正対象書類名】明細書

【補正対象項目名】0047

【補正方法】変更

【補正の内容】

【0047】

ここで、パワーオンリセット信号PONが入力されている間、電源電圧VDDのレベル変換回路711, 712への供給をストップさせていることにより、図3に示すデータ出力回路700において、電源電圧VDDQと接地電圧VSSQとの間で動作する出力バッファ72に入力される電位も不定となり、出力バッファ72に貫通電流が流れるおそれがある。しかしながら、第1の実施形態によれば、図5に示すように、電源電圧VDDQが供給される電源パッド111と出力バッファ72との間にはゲート電極に内部電圧VPPが入力されるトランジスタ101a1が設けられ、接地電圧VSSQが供給される電源パッド112と出力バッファ72との間にはゲート電極に内部電圧VPPが入力されるトランジスタ101b1が設けられていることから、図7に示すような構成となる。すなわち、パワーオンリセット信号PONの電位が入力されている間はスイッチ回路(トランジスタ)900がオンすることにより内部電圧VPPの供給ライン700の電位が接地電位となり、これにより、トランジスタ800と同様、トランジスタ101a1及び101b1もオフする。したがって、トランジスタ101a1のソース電極には電源電圧VDDQが供給されず、その電位VDDQc1ampは上がらない。また、トランジスタ101b1の電極パッド112と反対側の電極に接地電圧VSSQは供給されない。その後、パワーオンリセット信号PONの入力が終了し、スイッチ回路(トランジスタ)900がオフすることから内部電圧VPPの電位が上がっていき、トランジスタ101a1がオンすることにより、トランジスタ101a1のソース電極の電位VDDQc1ampもVDDc1ampと同様、問題なく期待値まで上昇する。また、トランジスタ101b1の電極パッド112と反対側の電極に接地電圧VSSQが電位VSSQc1ampとして供給される。

【手続補正7】

【補正対象書類名】図面

【補正対象項目名】図7

【補正方法】変更

【補正の内容】

【図7】