(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6126718号

(P6126718)

(45) 発行日 平成29年5月10日(2017.5.10)

(24) 登録日 平成29年4月14日(2017.4.14)

(51) Int.Cl.

F 1

G02F 1/1368 (2006.01)

G02F 1/1368

G02F 1/1343 (2006.01)

G02F 1/1343

請求項の数 6 (全 97 頁)

(21) 出願番号 特願2016-56828 (P2016-56828)

(22) 出願日 平成28年3月22日 (2016.3.22)

(62) 分割の表示 特願2015-201653 (P2015-201653)

原出願日 平成18年10月31日 (2006.10.31)

(65) 公開番号 特開2016-106282 (P2016-106282A)

(43) 公開日 平成28年6月16日 (2016.6.16)

審査請求日 平成28年4月15日 (2016.4.15)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 木村 肇

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 廣田 かおり

最終頁に続く

(54) 【発明の名称】 液晶表示装置

(57) 【特許請求の範囲】

【請求項 1】

基板上のコモン電極と、

前記コモン電極と電気的に接続された配線と、

前記配線の上面に接する領域を有する第1の導電膜と、

前記コモン電極上、前記配線上、及び前記第1の導電膜上の第1の絶縁膜と、

前記第1の絶縁膜の上面に接する領域を有する画素電極と、

前記コモン電極の上面に接する領域と、前記第1の導電膜の上面に接する領域と、前記第1の絶縁膜の上面に接する領域と、を有する第2の導電膜と、

前記画素電極上及び前記第2の導電膜上の配向膜と、

前記配向膜上の液晶と、

前記画素電極と電気的に接続されたトランジスタと、

前記トランジスタと電気的に接続されたゲート配線と、

前記トランジスタと電気的に接続されたソース配線と、を有し、

前記第1の絶縁膜は、前記トランジスタ上に設けられており、

前記画素電極は、複数の開口を有し、

前記コモン電極、前記画素電極、及び前記第2の導電膜の各々は、透光性を有する導電膜であり、

前記配線は、前記第1の導電膜及び前記第2の導電膜を介して、前記コモン電極と電気的に接続され、

10

20

前記液晶の配向は、前記コモン電極と前記画素電極との間の電界によって制御されることを特徴とする液晶表示装置。

【請求項 2】

基板上のコモン電極と、

前記コモン電極と電気的に接続された配線と、

前記配線の上面に接する領域を有する第1の導電膜と、

前記コモン電極上、前記配線上、及び前記第1の導電膜上の第1の絶縁膜と、

前記第1の絶縁膜の上面に接する領域を有する画素電極と、

前記コモン電極の上面に接する領域と、前記第1の導電膜の上面に接する領域と、前記第1の絶縁膜の上面に接する領域と、を有する第2の導電膜と、

前記画素電極上及び前記第2の導電膜上の配向膜と、

前記配向膜上の液晶と、

前記画素電極と電気的に接続されたトランジスタと、

前記トランジスタと電気的に接続されたゲート配線と、

前記トランジスタと電気的に接続されたソース配線と、を有し、

前記コモン電極は、前記ゲート配線と重なる領域と、前記配線と重なる領域と、前記トランジスタの半導体層と重なる領域と、前記ソース配線と重なる領域と、前記画素電極と重なる領域と、を有し、

前記第1の絶縁膜は、前記トランジスタ上に設けられており、

前記画素電極は、複数の開口を有し、

前記コモン電極、前記画素電極、及び前記第2の導電膜の各々は、透光性を有する導電膜であり、

前記配線は、前記第1の導電膜及び前記第2の導電膜を介して、前記コモン電極と電気的に接続され、

前記液晶の配向は、前記コモン電極と前記画素電極との間の電界によって制御されることを特徴とする液晶表示装置。

【請求項 3】

請求項2において、

前記半導体層は、多結晶シリコンを有することを特徴とする液晶表示装置。

【請求項 4】

基板上のコモン電極と、

前記コモン電極と電気的に接続された配線と、

前記配線の上面に接する領域を有する第1の導電膜と、

前記コモン電極上、前記配線上、及び前記第1の導電膜上の第1の絶縁膜と、

前記第1の絶縁膜の上面に接する領域を有する画素電極と、

前記コモン電極の上面に接する領域と、前記第1の導電膜の上面に接する領域と、前記第1の絶縁膜の上面に接する領域と、を有する第2の導電膜と、

前記画素電極上及び前記第2の導電膜上の配向膜と、

前記配向膜上の液晶と、

前記画素電極と電気的に接続されたトランジスタと、

前記トランジスタと電気的に接続されたゲート配線と、

前記トランジスタと電気的に接続されたソース配線と、を有し、

前記第1の絶縁膜は、前記トランジスタ上に設けられており、

前記トランジスタの半導体層は、酸化物半導体を有し、

前記画素電極は、複数の開口を有し、

前記コモン電極、前記画素電極、及び前記第2の導電膜の各々は、透光性を有する導電膜であり、

前記配線は、前記第1の導電膜及び前記第2の導電膜を介して、前記コモン電極と電気的に接続され、

前記液晶の配向は、前記コモン電極と前記画素電極との間の電界によって制御されるこ

10

20

30

40

50

とを特徴とする液晶表示装置。

**【請求項 5】**

請求項 4において、

前記半導体層は、In、Ga、及びZnを含む酸化物半導体を有することを特徴とする液晶表示装置。

**【請求項 6】**

請求項 1乃至 5のいずれか一において、

前記ソース配線は、上面から見たとき、曲がった部分を有し、

前記画素電極は、前記ソース配線の前記曲がった部分に沿うような形状を有し、

前記複数の開口は、前記ソース配線の前記曲がった部分に沿うような形状を有すること 10

を特徴とする液晶表示装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、半導体装置及び液晶表示装置に関する。特に、基板に平行な成分を有する電界を生じさせて、液晶分子を制御する半導体装置及び液晶表示装置に関する。

**【背景技術】**

**【0002】**

液晶表示装置の技術開発方針の一つに、視野角を広くすることがある。広い視野角を実現する技術として、基板に平行（すなわち水平な方向）な電界を生じさせて、基板と平行な面内で液晶分子を動かして、階調を制御する方式が用いられている。 20

**【0003】**

このような方式として、IPS (In-Plane switching) とFFS (Fringe-field switching) とがある。

**【0004】**

IPS方式の液晶表示装置では、一対の基板の片側の基板に、櫛状の電極（櫛歯型電極や櫛型電極ともいう）を二つ配置する。そして、これらの電極（櫛状の電極の一方が画素電極で他方が共通電極）間の電位差により発生する横方向の電界により、基板と平行な面内で液晶分子を動かしている。

**【0005】**

FFSは、液晶の下方に開口を有する第2の電極（例えば各画素別に電圧が制御される画素電極）を配置し、さらにその開口の下方に第1の電極（例えば全画素に共通の電圧が供給される共通電極）を配置するものがある。画素電極と共通電極との間に電界が加わり、液晶が制御される。液晶には水平方向の電界が加わるため、その電界を用いて液晶分子を制御できる。つまり、基板と平行に配向している液晶分子（いわゆるホモジニアス配向）を、基板と平行な方向で制御できるため、視野角が広くなる。 30

**【0006】**

従来の液晶分子を制御する半導体装置及び液晶表示装置においては、画素電極又は共通電極を透光性を有する導電膜、例えばインジウム錫酸化物（Indium Tin Oxide (ITO)）で形成していた（例えば特許文献1参照）。 40

**【先行技術文献】**

**【特許文献】**

**【0007】**

**【特許文献1】特許第3742836号**

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0008】**

上記したように、画素電極又は共通電極を透光性を有する導電膜、例えばITOで形成していた。透過型の液晶分子を制御する半導体装置及び透過型液晶表示装置を作製するには、画素電極及び共通電極を透光性を有する導電膜で形成しなくてはならない。従来は、 50

透光性を有する導電膜を成膜後、エッティング等によって成形して画素電極及び共通電極を形成してきた。このため、製造工程数やマスク数が多くなり、製造コストが高くなっていた。

#### 【0009】

そこで、本発明は、広い視野角を有しており、製造工程数やマスク数が少なく、製造コストが低い半導体装置及び液晶表示装置並びに電子機器を提供することを課題とする。

#### 【課題を解決するための手段】

#### 【0010】

本発明では、画素電極または共通電極の一方を、透光性を有する導電膜（以下「透光性導電膜」と呼ぶ）を成膜して成形を行わずにそのまま電極として用いる。これにより透光性導電膜をエッティング等で成形する必要がなく、製造工程数やフォトマスク数を少なくすることができ、製造コストを抑えることができる。

10

#### 【0011】

なお、液晶素子は画素電極と、画素部の複数の画素に渡って接続された共通電極との間の電位差により生ずる横方向の電界により、光量を制御する液晶分子の分子配列を基板に対して概ね水平方向に回転させることができればよい。

#### 【0012】

本発明は、基板の一方の表面の全面に形成された第1の電極と、前記第1電極の上に形成された第1の絶縁膜と、前記第1の絶縁膜上に形成された薄膜トランジスタと、前記薄膜トランジスタ上に形成された第2の絶縁膜と、前記第2の絶縁膜上に形成され、複数の開口を有する第2の電極と、前記前記第1の電極と前記第2の電極との間に液晶とを有し、前記第1の電極と前記第2の電極との間の電界によって、前記液晶を制御することを特徴とする液晶表示装置に関するものである。

20

#### 【0013】

本発明において、前記薄膜トランジスタは、トップゲート型薄膜トランジスタである。

#### 【0014】

本発明において、前記薄膜トランジスタは、ボトムゲート型薄膜トランジスタである。

#### 【0015】

本発明において、前記第1の電極及び第2の電極は、透光性を有する導電膜である。

#### 【0016】

本発明において、前記第1の電極または第2の電極の一方は、透光性を有する導電膜であり、前記第1の電極または第2の電極の一方は、反射性を有する導電膜である。

30

#### 【0017】

また本発明は、本発明を用いて作製した液晶表示装置を具備する電子機器にも関するものである。

#### 【0018】

なお、本書類（明細書、特許請求の範囲又は図面など）に示すスイッチは、様々な形態のものを用いることができる。例としては、電気的スイッチや機械的なスイッチなどがある。つまり、電流の流れを制御できるものであればよく、特定のものに限定されない。例えば、スイッチとして、トランジスタ（例えば、バイポーラトランジスタ、MOSトランジスタなど）、ダイオード（例えば、PNダイオード、PINダイオード、ショットキーダイオード、MIM（Metal Insulator Metal）ダイオード、MIS（Metal Insulator Semiconductor）ダイオード、ダイオード接続のトランジスタなど）、サイリスタなどを用いることが出来る。または、これらを組み合わせた論理回路をスイッチとして用いることが出来る。

40

#### 【0019】

スイッチとしてトランジスタを用いる場合、そのトランジスタは、単なるスイッチとして動作するため、トランジスタの極性（導電型）は特に限定されない。ただし、オフ電流を抑えたい場合、オフ電流が少ない方の極性のトランジスタを用いることが望ましい。オフ電流が少ないトランジスタとしては、LCD領域を有するトランジスタやマルチゲート

50

構造を有するトランジスタ等がある。または、スイッチとして動作させるトランジスタのソース端子の電位が、低電位側電源（V<sub>SS</sub>、GND、0Vなど）に近い状態で動作する場合はNチャネル型トランジスタを用いることが望ましい。反対に、ソース端子の電位が、高電位側電源（V<sub>DD</sub>など）に近い状態で動作する場合はPチャネル型トランジスタを用いることが望ましい。なぜなら、Nチャネル型トランジスタではソース端子が低電位側電源に近い状態で動作するとき、Pチャネル型トランジスタではソース端子が高電位側電源に近い状態で動作するとき、ゲートソース間電圧の絶対値を大きくできるため、スイッチとして、動作しやすいからである。また、ソースフォロワ動作をしてしまうことが少ないといため、出力電圧の大きさが小さくなってしまうことが少ないからである。

## 【0020】

10

なお、Nチャネル型トランジスタとPチャネル型トランジスタの両方を用いて、CMOS型のスイッチをスイッチとして用いてもよい。CMOS型のスイッチにすると、Pチャネル型トランジスタまたはNチャネル型トランジスタのどちらか一方のトランジスタが導通すれば電流が流れるため、スイッチとして機能しやすくなる。例えば、スイッチへの入力信号の電圧が高い場合でも、低い場合でも、適切に電圧を出力させることが出来る。さらに、スイッチをオン・オフさせるための信号の電圧振幅値を小さくすることが出来るので、消費電力を小さくすることも出来る。

## 【0021】

なお、スイッチとしてトランジスタを用いる場合、スイッチは、入力端子（ソース端子またはドレイン端子の一方）と、出力端子（ソース端子またはドレイン端子の他方）と、導通を制御する端子（ゲート端子）とを有している。一方、スイッチとしてダイオードを用いる場合、スイッチは、導通を制御する端子を有していない場合がある。そのため、トランジスタよりもダイオードをスイッチとして用いた方が、端子を制御するための配線を少なくすることが出来る。

20

## 【0022】

なお、本書類（明細書、特許請求の範囲又は図面など）において、AとBとが接続されている、と明示的に記載する場合は、AとBとが電気的に接続されている場合と、AとBとが機能的に接続されている場合と、AとBとが直接接続されている場合とを含むものとする。ここで、A、Bは、対象物（例えば、装置、素子、回路、配線、電極、端子、導電膜、層、など）であるとする。したがって、本書類（明細書、特許請求の範囲又は図面など）が開示する構成において、所定の接続関係、例えば、図または文章に示された接続関係に限定されず、図または文章に示された接続関係以外のものも含むものとする。

30

## 【0023】

例えば、AとBとが電気的に接続されている場合として、AとBとの電気的な接続を可能とする素子（例えば、スイッチ、トランジスタ、容量素子、インダクタ、抵抗素子、ダイオードなど）が、AとBとの間に1個以上配置されていてもよい。あるいは、AとBとが機能的に接続されている場合として、AとBとの機能的な接続を可能とする回路（例えば、論理回路（インバータ、NAND回路、NOR回路など）、信号変換回路（DA変換回路、AD変換回路、ガンマ補正回路など）、電位レベル変換回路（電源回路（昇圧回路、降圧回路など）、信号の電位レベルを変えるレベルシフタ回路など）、電圧源、電流源、切り替え回路、增幅回路（信号振幅または電流量などを大きく出来る回路、オペアンプ、差動增幅回路、ソースフォロワ回路、バッファ回路など）、信号生成回路、記憶回路、制御回路など）が、AとBとの間に1個以上配置されていてもよい。あるいは、AとBとが直接接続されている場合として、AとBとの間に他の素子や他の回路を挟まずに、AとBとが直接接続されていてもよい。

40

## 【0024】

なお、AとBとが直接接続されている、と明示的に記載する場合は、AとBとが直接接続されている場合（つまり、AとBとの間に他の素子や他の回路を間に介さずに接続されている場合）と、AとBとが電気的に接続されている場合（つまり、AとBとの間に別の素子や別の回路を挟んで接続されている場合）とを含むものとする。

50

## 【0025】

なお、AとBとが電気的に接続されている、と明示的に記載する場合は、AとBとが電気的に接続されている場合（つまり、AとBとの間に別の素子や別の回路を挟んで接続されている場合）と、AとBとが機能的に接続されている場合（つまり、AとBとの間に別の回路を挟んで機能的に接続されている場合）と、AとBとが直接接続されている場合（つまり、AとBとの間に別の素子や別の回路を挟まずに接続されている場合）とを含むものとする。つまり、電気的に接続されている、と明示的に記載する場合は、単に、接続されている、とのみ明示的に記載されている場合と同じであるとする。

## 【0026】

なお、表示素子、表示素子を有する装置である表示装置、発光素子、発光素子を有する装置である発光装置は、様々な形態を用いたり、様々な素子を有することが出来る。例えば、表示素子、表示装置、発光素子または発光装置としては、EL素子（有機EL素子、無機EL素子又は有機物及び無機物を含むEL素子）、電子放出素子、液晶素子、電子インク、電気泳動素子、グレーティングライトバルブ（GLV）、プラズマディスプレイ（PDP）、デジタルマイクロミラーデバイス（DMD）、圧電セラミックディスプレイ、カーボンナノチューブ、など、電気磁気的作用により、コントラスト、輝度、反射率、透過率などが変化する表示媒体を用いることができる。なお、EL素子を用いた表示装置としてはELディスプレイ、電子放出素子を用いた表示装置としてはフィールドエミッショングディスプレイ（FED）やSED方式平面型ディスプレイ（SED：Surface-conduction Electron-emitter Display）など、液晶素子を用いた表示装置としては液晶ディスプレイ（透過型液晶ディスプレイ、半透過型液晶ディスプレイ、反射型液晶ディスプレイ、直視型液晶ディスプレイ、投射型液晶ディスプレイ）、電子インクや電気泳動素子を用いた表示装置としては電子ペーパーがある。

## 【0027】

なお、本書類（明細書、特許請求の範囲又は図面など）に記載されたトランジスタとして、様々な形態のトランジスタを用いることが出来る。よって、用いるトランジスタの種類に限定はない。例えば、非晶質シリコン、多結晶シリコン、微結晶（マイクロクリスタル、セミアモルファスとも言う）シリコンなどに代表される非単結晶半導体膜を有する薄膜トランジスタ（TFT）などを用いることが出来る。TFTを用いる場合、様々なメリットがある。例えば、単結晶シリコンの場合よりも低い温度で製造できるため、製造コストの削減、又は製造装置の大型化を図ることができる。製造装置を大きくできるため、大型基板上に製造できる。そのため、同時に多くの個数の表示装置を製造できるため、低コストで製造できる。さらに、製造温度が低いため、耐熱性の弱い基板を用いることができる。そのため、透明基板上にトランジスタを製造できる。そして、透明な基板上のトランジスタを用いて表示素子での光の透過を制御することが出来る。あるいは、トランジスタの膜厚が薄いため、トランジスタを構成する膜の一部は、光を透過させることができる。そのため、開口率が向上させることができる。

## 【0028】

なお、多結晶シリコンを製造するときに、触媒（ニッケルなど）を用いることにより、結晶性をさらに向上させ、電気特性のよいトランジスタを製造することが可能となる。その結果、ゲートドライバ回路（走査線駆動回路）やソースドライバ回路（信号線駆動回路）、信号処理回路（信号生成回路、ガンマ補正回路、DA変換回路など）を基板上に一体形成することが出来る。

## 【0029】

なお、微結晶シリコンを製造するときに、触媒（ニッケルなど）を用いることにより、結晶性をさらに向上させ、電気特性のよいトランジスタを製造することが可能となる。このとき、レーザーを用いず、熱処理を加えるだけで、結晶性を向上させることができる。その結果、ゲートドライバ回路（走査線駆動回路）やソースドライバ回路の一部（アナログスイッチなど）を基板上に一体形成することが出来る。さらに、結晶化のためにレーザーを用いない場合は、シリコンの結晶性のムラを抑えることができる。そのため、綺麗な

10

20

30

40

50

画像を表示することが出来る。

【0030】

ただし、触媒（ニッケルなど）を用いずに、多結晶シリコンや微結晶シリコンを製造することは可能である。

【0031】

または、半導体基板やS O I 基板などを用いてトランジスタを形成することが出来る。その場合、M O S 型トランジスタ、接合型トランジスタ、バイポーラトランジスタなどを本明細書に記載されたトランジスタとして用いることが出来る。これらにより、特性やサイズや形状などのバラツキが少なく、電流供給能力が高く、サイズの小さいトランジスタを製造することができる。これらのトランジスタを用いると、回路の低消費電力化、又は回路の高集積化を図ることができる。 10

【0032】

または、Z n O 、a - I n G a Z n O 、S i G e 、G a A s 、I Z O 、I T O 、S n O などの化合物半導体または酸化物半導体を有するトランジスタや、さらに、これらの化合物半導体または酸化物半導体を薄膜化した薄膜トランジスタなどを用いることが出来る。これらにより、製造温度を低くでき、例えば、室温でトランジスタを製造することが可能となる。その結果、耐熱性の低い基板、例えばプラスチック基板やフィルム基板に直接トランジスタを形成することが出来る。なお、これらの化合物半導体または酸化物半導体を、トランジスタのチャネル部分に用いるだけでなく、それ以外の用途で用いることも出来る。例えば、これらの化合物半導体または酸化物半導体を抵抗素子、画素電極、透明電極として用いることができる。さらに、それらをトランジスタと同時に成膜又は形成できるため、コストを低減できる。 20

【0033】

または、インクジェットや印刷法を用いて形成したトランジスタなどを用いることが出来る。これらにより、室温で製造、低真空中で製造、又は大型基板上に製造することができる。また、マスク（レチクル）を用いなくても製造することが可能となるため、トランジスタのレイアウトを容易に変更することが出来る。さらに、レジストを用いる必要がないので、材料費が安くなり、工程数を削減できる。さらに、必要な部分にのみ膜を付けるため、全面に成膜した後でエッティングする、という製法よりも、材料が無駄にならず、低コストにできる。 30

【0034】

または、有機半導体やカーボンナノチューブを有するトランジスタ等を用いることができる。これらにより、曲げることが可能な基板上にトランジスタを形成することができる。そのため、衝撃に強くできる。

【0035】

その他、様々なトランジスタを用いることができる。

【0036】

なお、トランジスタが形成されている基板の種類は、様々なものを用いることができ、特定のものに限定されることはない。トランジスタが形成される基板としては、例えば、単結晶基板、S O I 基板、ガラス基板、石英基板、プラスチック基板、紙基板、セロファン基板、石材基板、木材基板、布基板（天然纖維（絹、綿、麻）、合成纖維（ナイロン、ポリウレタン、ポリエステル）若しくは再生纖維（アセテート、キュプラ、レーヨン、再生ポリエステル）などを含む）、皮革基板、ゴム基板、ステンレス・スチール基板、ステンレス・スチール・ホイルを有する基板などを用いることが出来る。または、ある基板でトランジスタを形成し、その後、別の基板にトランジスタを転置し、別の基板上にトランジスタを配置してもよい。トランジスタが転置される基板としては、単結晶基板、S O I 基板、ガラス基板、石英基板、プラスチック基板、紙基板、セロファン基板、石材基板、木材基板、布基板（天然纖維（絹、綿、麻）、合成纖維（ナイロン、ポリウレタン、ポリエステル）若しくは再生纖維（アセテート、キュプラ、レーヨン、再生ポリエステル）などを含む）、皮革基板、ゴム基板、ステンレス・スチール基板、ステンレス・スチール・ホイル 40

を有する基板などを用いることができる。あるいは、人などの動物の皮膚（皮表、真皮）又は皮下組織を基板として用いてもよい。これらの基板を用いることにより、特性のよいトランジスタの形成、消費電力の小さいトランジスタの形成、壊れにくい装置の製造、耐熱性の付与、又は軽量化を図ることができる。

【0037】

なお、トランジスタの構成は、様々な形態をとることができる。特定の構成に限定されない。例えば、ゲート電極が2個以上のマルチゲート構造を用いてもよい。マルチゲート構造にすると、チャネル領域が直列に接続されるため、複数のトランジスタが直列に接続された構成となる。マルチゲート構造により、オフ電流の低減、トランジスタの耐圧向上による信頼性の向上を図ることができる。あるいは、マルチゲート構造により、飽和領域で動作する時に、ドレイン・ソース間電圧が変化しても、ドレイン・ソース間電流があまり変化せず、電圧・電流特性の傾きがフラットな特性にすることができる。電圧・電流特性の傾きがフラットである特性を利用すると、理想的な電流源回路や、非常に高い抵抗値をもつ能動負荷を実現することが出来る。その結果、特性のよい差動回路やカレントミラーハイブ回路を実現することが出来る。また、チャネルの上下にゲート電極が配置されている構造でもよい。チャネルの上下にゲート電極が配置されている構造にすることにより、チャネル領域が増えるため、電流値の増加、又は空乏層ができやすくなることによるS値の低減を図ることができる。チャネルの上下にゲート電極が配置されると、複数のトランジスタが並列に接続されたような構成となる。

【0038】

あるいは、チャネル領域の上にゲート電極が配置されている構造でもよいし、チャネル領域の下にゲート電極が配置されている構造でもよい。あるいは、正スタガ構造または逆スタガ構造でもよいし、チャネル領域が複数の領域に分かれてもよいし、チャネル領域が並列に接続されていてもよいし、チャネル領域が直列に接続されていてもよい。また、チャネル領域（もしくはその一部）にソース電極やドレイン電極が重なっていてもよい。チャネル領域（もしくはその一部）にソース電極やドレイン電極が重なる構造にすることにより、チャネル領域の一部に電荷がたまって、動作が不安定になることを防ぐことができる。また、LDD領域を設けても良い。LDD領域を設けることにより、オフ電流の低減、又はトランジスタの耐圧向上による信頼性の向上を図ることができる。あるいは、LDD領域を設けることにより、飽和領域で動作する時に、ドレイン・ソース間電圧が変化しても、ドレイン・ソース間電流があまり変化せず、電圧・電流特性の傾きがフラットな特性にすることができる。

【0039】

なお、本書類（明細書、特許請求の範囲又は図面など）におけるトランジスタは、様々なタイプを用いることができ、様々な基板上に形成させることができる。したがって、所定の機能を実現させるために必要な回路の全てが、同一の基板に形成されていてもよい。例えば、所定の機能を実現させるために必要な回路の全てが、ガラス基板、プラスチック基板、単結晶基板、またはSOI基板上に形成されていてもよく、さまざまな基板上に形成されていてもよい。所定の機能を実現させるために必要な回路の全てが同じ基板上に形成されていることにより、部品点数の削減によるコストの低減、又は回路部品との接続点数の低減による信頼性の向上を図ることができる。あるいは、所定の機能を実現させるために必要な回路の一部が、ある基板に形成されており、所定の機能を実現させるために必要な回路の別の一部が、別の基板に形成されていてもよい。つまり、所定の機能を実現させるために必要な回路の全てが同じ基板上に形成されていなくてもよい。例えば、所定の機能を実現させるために必要な回路の一部は、ガラス基板上にトランジスタを用いて形成され、所定の機能を実現させるために必要な回路の別の一部は、単結晶基板上に形成され、単結晶基板上のトランジスタで構成されたICチップをCOG（Chip On Glass）でガラス基板に接続して、ガラス基板上にそのICチップを配置してもよい。あるいは、そのICチップをTAB（Tape Automated Bonding）やプリント基板を用いてガラス基板と接続してもよい。このように、回路の一部が同じ基板

10

20

30

40

50

に形成されていることにより、部品点数の削減によるコストの低減、又は回路部品との接続点数の低減による信頼性の向上を図ることができる。また、駆動電圧が高い部分や駆動周波数が高い部分の回路は、消費電力が大きくなってしまうので、そのような部分の回路は同じ基板に形成せず、そのかわりに、例えば、単結晶基板上にその部分の回路を形成して、その回路で構成されたICチップを用いるようにすれば、消費電力の増加を防ぐことができる。

#### 【0040】

なお、本書類（明細書、特許請求の範囲又は図面など）においては、一画素とは画像の最小単位を示すものとする。よって、R（赤）G（緑）B（青）の色要素からなるフルカラー表示装置の場合には、一画素とはRの色要素のドットとGの色要素のドットとBの色要素のドットとから構成されるものとする。なお、色要素は、三色に限定されず、三色以上を用いても良いし、RGB以外の色を用いても良い。例えば、白色を加えて、RGBW（Wは白）としてもよい。また、RGBに、例えば、イエロー、シアン、マゼンタ、エメラルドグリーン、朱色などを一色以上追加してもよい。または、例えば、RGBの中の少なくとも一色に類似した色を、RGBに追加してもよい。例えば、R、G、B1、B2としてもよい。B1とB2とは、どちらも青色であるが、少し周波数が異なっている。同様に、R1、R2、G、Bとしてもよい。このような色要素を用いることにより、より実物に近い表示を行うことができる。あるいは、このような色要素を用いることにより、消費電力を低減することが出来る。なお、一画素に、同じ色の色要素のドットが複数個あってもよい。そのとき、その複数の色要素は、各々、表示に寄与する領域の大きさが異なっていても良い。また、複数個ある、同じ色の色要素のドットを各々制御することによって、階調を表現してもよい。これを、面積階調方式と呼ぶ。あるいは、複数個ある、同じ色の色要素のドットを用いて、各々のドットに供給する信号を僅かに異ならせるようにして、視野角を広げるようにしてよい。つまり、複数個ある、同じ色の色要素が各々有する画素電極の電位が、各々異なっていてもよい。その結果、液晶分子に加わる電圧が各画素電極によって各々異なる。よって、視野角を広くすることが出来る。

#### 【0041】

なお、本書類（明細書、特許請求の範囲又は図面など）においては、一画素とは、明るさを制御できる要素一つ分を示すものとする。よって、一例としては、一画素とは、一つの色要素を示すものとし、その色要素一つで明るさを表現する。従って、そのときは、R（赤）G（緑）B（青）の色要素からなるカラー表示装置の場合には、画像の最小単位は、Rの画素とGの画素とBの画素との三画素から構成されるものとする。なお、色要素は、三色に限定されず、三色以上を用いても良いし、RGB以外の色を用いても良い。例えば、白色を加えて、RGBW（Wは白）としてもよい。また、RGBに、例えば、イエロー、シアン、マゼンタ、エメラルドグリーン、朱色などを一色以上追加してもよい。また、例えば、RGBの中の少なくとも一色に類似した色を、RGBに追加してもよい。例えば、R、G、B1、B2としてもよい。B1とB2とは、どちらも青色であるが、少し周波数が異なっている。同様に、R1、R2、G、Bとしてもよい。このような色要素を用いることにより、より実物に近い表示を行うことができる。あるいは、このような色要素を用いることにより、消費電力を低減することが出来る。また、別の例としては、1つの色要素について、複数の領域を用いて明るさを制御する場合は、その領域一つ分を一画素としてもよい。よって、一例として、面積階調を行う場合または副画素（サブ画素）を有している場合、一つの色要素につき、明るさを制御する領域が複数あり、その全体で階調を表現するわけであるが、明るさを制御する領域の一つ分を一画素としてもよい。よって、その場合は、一つの色要素は、複数の画素で構成されることとなる。あるいは、明るさを制御する領域が1つの色要素の中に複数あっても、それらをまとめて、1つの色要素を1画素としてもよい。よって、その場合は、一つの色要素は、一つの画素で構成されることとなる。また、1つの色要素について、複数の領域を用いて明るさを制御する場合、画素によって、表示に寄与する領域の大きさが異なっている場合がある。また、一つの色要素につき複数ある、明るさを制御する領域において、各々に供給する信号を僅かに異なら

10

20

30

40

50

せるようにして、視野角を広げるようにもよい。つまり、1つの色要素について、複数個ある領域が各々有する画素電極の電位が、各々異なっていてもよい。その結果、液晶分子に加わる電圧が各画素電極によって各々異なる。よって、視野角を広くすることが出来る。

#### 【0042】

なお、一画素（三色分）と明示的に記載する場合は、RとGとBの三画素分を一画素と考える場合であるとする。一画素（一色分）と明示的に記載する場合は、一つの色要素につき、複数の領域がある場合、それらをまとめて一画素と考える場合であるとする。

#### 【0043】

なお、本書類（明細書、特許請求の範囲又は図面など）において、画素は、マトリクス状に配置（配列）されている場合がある。ここで、画素がマトリクスに配置（配列）されているとは、縦方向もしくは横方向において、画素が直線上に並んで配置されている場合や、ギザギザな線上に配置されている場合を含む。よって、例えば三色の色要素（例えばR G B）でフルカラー表示を行う場合に、ストライプ配置されている場合や、三つの色要素のドットがデルタ配置されている場合も含む。さらに、ベイヤー配置されている場合も含む。なお、色要素は、三色に限定されず、それ以上でもよく、例えば、R G B W（Wは白）や、R G Bに、イエロー、シアン、マゼンタなどを一色以上追加したものなどがある。また、色要素のドット毎にその表示領域の大きさが異なっていてもよい。これにより、低消費電力化、又は表示素子の長寿命化を図ることができる。

#### 【0044】

なお、本書類（明細書、特許請求の範囲又は図面など）において、画素に能動素子を有するアクティブマトリクス方式、または、画素に能動素子を有しないパッシブマトリクス方式を用いることが出来る。

#### 【0045】

アクティブマトリクス方式では、能動素子（アクティブ素子、非線形素子）として、トランジスタだけでなく、さまざまな能動素子（アクティブ素子、非線形素子）を用いることが出来る。例えば、MIM（Metal Insulator Metal）やTFD（Thin Film Diode）などを用いることも可能である。これらの素子は、製造工程が少ないため、製造コストの低減、又は歩留まりの向上を図ることができる。さらに、素子のサイズが小さいため、開口率を向上させることができ、低消費電力化や高輝度化をはかることが出来る。

#### 【0046】

なお、アクティブマトリクス方式以外のものとして、能動素子（アクティブ素子、非線形素子）を用いないパッシブマトリクス型を用いることも可能である。能動素子（アクティブ素子、非線形素子）を用いないため、製造工程が少なく、製造コストの低減、又は歩留まりの向上を図ることができる。また、能動素子（アクティブ素子、非線形素子）を用いないため、開口率を向上させることができ、低消費電力化や高輝度化をはかることが出来る。

#### 【0047】

なお、トランジスタとは、ゲートと、ドレインと、ソースとを含む少なくとも三つの端子を有する素子であり、ドレイン領域とソース領域の間にチャネル領域を有しており、ドレイン領域とチャネル領域とソース領域とを介して電流を流すことが出来る。ここで、ソースとドレインとは、トランジスタの構造や動作条件等によって変わるために、いざれがソースまたはドレインであるかを限定することが困難である。そこで、本書類（明細書、特許請求の範囲又は図面など）においては、ソース及びドレインとして機能する領域を、ソースもしくはドレインと呼ばない場合がある。その場合、一例としては、それぞれを第1端子、第2端子と表記する場合がある。あるいは、それぞれを第1の電極、第2の電極と表記する場合がある。あるいは、ソース領域、ドレイン領域と表記する場合がある。

#### 【0048】

なお、トランジスタは、ベースとエミッタとコレクタとを含む少なくとも三つの端子を

10

20

30

40

50

有する素子であってもよい。この場合も同様に、エミッタとコレクタとを、第1端子、第2端子と表記する場合がある。

【0049】

なお、ゲートとは、ゲート電極とゲート配線（ゲート線、ゲート信号線、走査線、走査信号線等とも言う）とを含んだ全体、もしくは、それらの一部のことを言う。ゲート電極とは、チャネル領域を形成する半導体と、ゲート絶縁膜を介してオーバーラップしている部分の導電膜のことを言う。なお、ゲート電極の一部は、LDD（Lightly Doped Drain）領域またはソース・ドレイン領域と、ゲート絶縁膜を介してオーバーラップしている場合もある。ゲート配線とは、各トランジスタのゲート電極の間を接続するための配線、各画素の有するゲート電極の間を接続するための配線、又はゲート電極と別の配線とを接続するための配線のことを言う。

10

【0050】

ただし、ゲート電極としても機能し、ゲート配線としても機能するような部分（領域、導電膜、配線など）も存在する。そのような部分（領域、導電膜、配線など）は、ゲート電極と呼んでも良いし、ゲート配線と呼んでも良い。つまり、ゲート電極とゲート配線とが、明確に区別できないような領域も存在する。例えば、延伸して配置されているゲート配線の一部とチャネル領域がオーバーラップしている場合、その部分（領域、導電膜、配線など）はゲート配線として機能しているが、ゲート電極としても機能していることになる。よって、そのような部分（領域、導電膜、配線など）は、ゲート電極と呼んでも良いし、ゲート配線と呼んでも良い。

20

【0051】

なお、ゲート電極と同じ材料で形成され、ゲート電極と同じ島（アイランド）を形成してつながっている部分（領域、導電膜、配線など）も、ゲート電極と呼んでも良い。同様に、ゲート配線と同じ材料で形成され、ゲート配線と同じ島（アイランド）を形成してつながっている部分（領域、導電膜、配線など）も、ゲート配線と呼んでも良い。このような部分（領域、導電膜、配線など）は、厳密な意味では、チャネル領域とオーバーラップしていない場合、又は別のゲート電極と接続させる機能を有していない場合がある。しかし、製造マージンなどの関係で、ゲート電極またはゲート配線と同じ材料で形成され、ゲート電極またはゲート配線と同じ島（アイランド）を形成してつながっている部分（領域、導電膜、配線など）がある。よって、そのような部分（領域、導電膜、配線など）もゲート電極またはゲート配線と呼んでも良い。

30

【0052】

なお、例えば、マルチゲートのトランジスタにおいて、1つのゲート電極と、別のゲート電極とは、ゲート電極と同じ材料で形成された導電膜で接続される場合が多い。そのような部分（領域、導電膜、配線など）は、ゲート電極とゲート電極とを接続させるための部分（領域、導電膜、配線など）であるため、ゲート配線と呼んでも良いが、マルチゲートのトランジスタを1つのトランジスタと見なすことも出来るため、ゲート電極と呼んでも良い。つまり、ゲート電極またはゲート配線と同じ材料で形成され、ゲート電極またはゲート配線と同じ島（アイランド）を形成してつながっている部分（領域、導電膜、配線など）は、ゲート電極やゲート配線と呼んでも良い。さらに、例えば、ゲート電極とゲート配線とを接続させている部分の導電膜であって、ゲート電極またはゲート配線とは異なる材料で形成された導電膜も、ゲート電極と呼んでも良いし、ゲート配線と呼んでも良い。

40

【0053】

なお、ゲート端子とは、ゲート電極の部分（領域、導電膜、配線など）または、ゲート電極と電気的に接続されている部分（領域、導電膜、配線など）について、その一部分のことを言う。

【0054】

なお、ゲート配線、ゲート線、ゲート信号線、走査線、走査信号線などと呼ぶ場合、配線にトランジスタのゲートが接続されていない場合もある。この場合、ゲート配線、ゲー

50

ト線、ゲート信号線、走査線、走査信号線は、トランジスタのゲートと同じ層で形成された配線、トランジスタのゲートと同じ材料で形成された配線またはトランジスタのゲートと同時に成膜された配線を意味している場合がある。例としては、保持容量用配線、電源線、基準電位供給配線などがある。

【0055】

なお、ソースとは、ソース領域とソース電極とソース配線（ソース線、ソース信号線、データ線、データ信号線等とも言う）とを含んだ全体、もしくは、それらの一部のことを言う。ソース領域とは、P型不純物（ボロンやガリウムなど）やN型不純物（リンやヒ素など）が多く含まれる半導体領域のことを言う。従って、少しだけP型不純物やN型不純物が含まれる領域、いわゆる、LDD（Lightly Doped Drain）領域は、ソース領域には含まれない。ソース電極とは、ソース領域とは別の材料で形成され、ソース領域と電気的に接続されている部分の導電層のことを言う。ただし、ソース電極は、ソース領域も含んでソース電極と呼ぶこともある。ソース配線とは、各トランジスタのソース電極の間を接続するための配線、各画素の有するソース電極の間を接続するための配線、又はソース電極と別の配線とを接続するための配線のことを言う。

【0056】

しかしながら、ソース電極としても機能し、ソース配線としても機能するような部分（領域、導電膜、配線など）も存在する。そのような部分（領域、導電膜、配線など）は、ソース電極と呼んでも良いし、ソース配線と呼んでも良い。つまり、ソース電極とソース配線とが、明確に区別できないような領域も存在する。例えば、延伸して配置されているソース配線の一部とソース領域とがオーバーラップしている場合、その部分（領域、導電膜、配線など）はソース配線として機能しているが、ソース電極としても機能することになる。よって、そのような部分（領域、導電膜、配線など）は、ソース電極と呼んでも良いし、ソース配線と呼んでも良い。

【0057】

なお、ソース電極と同じ材料で形成され、ソース電極と同じ島（アイランド）を形成してつながっている部分（領域、導電膜、配線など）や、ソース電極とソース電極とを接続する部分（領域、導電膜、配線など）も、ソース電極と呼んでも良い。さらに、ソース領域とオーバーラップしている部分も、ソース電極と呼んでも良い。同様に、ソース配線と同じ材料で形成され、ソース配線と同じ島（アイランド）を形成してつながっている領域も、ソース配線と呼んでも良い。このような部分（領域、導電膜、配線など）は、厳密な意味では、別のソース電極と接続させる機能を有していない場合がある。しかし、製造マージンなどの関係で、ソース電極またはソース配線と同じ材料で形成され、ソース電極またはソース配線とつながっている部分（領域、導電膜、配線など）がある。よって、そのような部分（領域、導電膜、配線など）もソース電極またはソース配線と呼んでも良い。

【0058】

なお、例えば、ソース電極とソース配線とを接続させている部分の導電膜であって、ソース電極またはソース配線とは異なる材料で形成された導電膜も、ソース電極と呼んでも良いし、ソース配線と呼んでも良い。

【0059】

なお、ソース端子とは、ソース領域の領域や、ソース電極や、ソース電極と電気的に接続されている部分（領域、導電膜、配線など）について、その一部分のことを言う。

【0060】

なお、ソース配線、ソース線、ソース信号線、データ線、データ信号線などと呼ぶ場合、配線にトランジスタのソース（ドレイン）が接続されていない場合もある。この場合、ソース配線、ソース線、ソース信号線、データ線、データ信号線は、トランジスタのソース（ドレイン）と同じ層で形成された配線、トランジスタのソース（ドレイン）と同じ材料で形成された配線またはトランジスタのソース（ドレイン）と同時に成膜された配線を意味している場合がある。例としては、保持容量用配線、電源線、基準電位供給配線などがある。

10

20

30

40

50

## 【0061】

なお、ドレインについては、ソースと同様である。

## 【0062】

なお、半導体装置とは半導体素子（トランジスタ、ダイオード、サイリスタなど）を含む回路を有する装置のことをいう。さらに、半導体特性を利用することで機能しうる装置全般を半導体装置と呼んでもよい。

## 【0063】

なお、表示素子とは、光学変調素子、液晶素子、発光素子、EL素子（有機EL素子、無機EL素子又は有機物及び無機物を含むEL素子）、電子放出素子、電気泳動素子、放電素子、光反射素子、光回折素子、デジタルマイクロミラーデバイス（DMD）、などを言う。ただし、これに限定されない。

10

## 【0064】

なお、表示装置とは、表示素子を有する装置のことを言う。なお、表示装置とは、表示素子を含む複数の画素またはそれらの画素を駆動させる周辺駆動回路が同一基板上に形成された表示パネル本体のことでもよい。なお、表示装置は、ワイヤボンディングやバンプなどによって基板上に配置された周辺駆動回路、いわゆる、チップオングラス（COG）で接続されたICチップ、または、TABなどで接続されたICチップを含んでいても良い。なお、表示装置は、ICチップ、抵抗素子、容量素子、インダクタ、トランジスタなどが取り付けられたフレキシブルプリントサーキット（FPC）を含んでもよい。なお、表示装置は、フレキシブルプリントサーキット（FPC）などを介して接続され、ICチップ、抵抗素子、容量素子、インダクタ、トランジスタなどが取り付けられたプリント配線基盤（PWB）を含んでいても良い。なお、表示装置は、偏光板または位相差板などの光学シートを含んでいても良い。なお、表示装置は、照明装置、筐体、音声入出力装置、光センサなどを含んでいても良い。ここで、バックライトユニットのような照明装置は、導光板、プリズムシート、拡散シート、反射シート、光源（LED、冷陰極管など）、冷却装置（水冷式、空冷式）などを含んでいても良い。

20

## 【0065】

なお、照明装置は、バックライトユニット、導光板、プリズムシート、拡散シート、反射シート、光源（LED、冷陰極管、熱陰極管など）、冷却装置などを有している装置のことをいう。

30

## 【0066】

なお、発光装置とは、発光素子などを有している装置のことをいう。

## 【0067】

なお、反射装置とは、光反射素子、光回折素子、光反射電極などを有している装置のことをいう。

## 【0068】

なお、液晶表示装置とは、液晶素子を有している表示装置をいう。液晶表示装置には、直視型、投写型、透過型、反射型、半透過型などがある。

## 【0069】

なお、駆動装置とは、半導体素子、電気回路、電子回路を有する装置のことを言う。例えば、ソース信号線から画素内への信号の入力を制御するトランジスタ（選択用トランジスタ、スイッチング用トランジスタなどと呼ぶことがある）、画素電極に電圧または電流を供給するトランジスタ、発光素子に電圧または電流を供給するトランジスタなどは、駆動装置の一例である。さらに、ゲート信号線に信号を供給する回路（ゲートドライバ、ゲート線駆動回路などと呼ぶことがある）、ソース信号線に信号を供給する回路（ソースドライバ、ソース線駆動回路などと呼ぶことがある）などは、駆動装置の一例である。

40

## 【0070】

なお、表示装置、半導体装置、照明装置、冷却装置、発光装置、反射装置、駆動装置などは、互いに重複して有している場合がある。例えば、表示装置が、半導体装置および発光装置を有している場合がある。あるいは、半導体装置が、表示装置および駆動装置を有

50

している場合がある。

【0071】

なお、本書類（明細書、特許請求の範囲又は図面など）において、Aの上にBが形成されている、あるいは、A上にBが形成されている、と明示的に記載する場合は、Aの上にBが直接接して形成されていることに限定されない。直接接してはいない場合、つまり、AとBと間に別の対象物が介在する場合も含むものとする。ここで、A、Bは、対象物（例えば、装置、素子、回路、配線、電極、端子、導電膜、層、など）であるとする。

【0072】

従って例えば、層Aの上に（もしくは層A上に）、層Bが形成されている、と明示的に記載されている場合は、層Aの上に直接接して層Bが形成されている場合と、層Aの上に直接接して別の層（例えば層Cや層Dなど）が形成されていて、その上に直接接して層Bが形成されている場合とを含むものとする。なお、別の層（例えば層Cや層Dなど）は、単層でもよいし、複層でもよい。

10

【0073】

さらに、Aの上方にBが形成されている、と明示的に記載されている場合についても同様であり、Aの上にBが直接接していることに限定されず、AとBとの間に別の対象物が介在する場合も含むものとする。従って例えば、層Aの上方に、層Bが形成されている、という場合は、層Aの上に直接接して層Bが形成されている場合と、層Aの上に直接接して別の層（例えば層Cや層Dなど）が形成されていて、その上に直接接して層Bが形成されている場合とを含むものとする。なお、別の層（例えば層Cや層Dなど）は、単層でもよいし、複層でもよい。

20

【0074】

なお、Aの上にBが直接接して形成されている、と明示的に記載する場合は、Aの上に直接接してBが形成されている場合を含み、AとBと間に別の対象物が介在する場合は含まないものとする。

【0075】

なお、Aの下にBが、あるいは、Aの下方にBが、という場合についても、同様である。

【発明の効果】

【0076】

30

本発明により、広い視野角を有しており、かつ従来と比べて製造コストが低い液晶表示装置を提供することができる。

【0077】

本発明では、導電膜を基板全面に形成するので、基板からの不純物が活性層に混入されるのを防ぐことができる。これにより信頼性の高い半導体装置を得ることが可能となる。

【0078】

また本発明においては、トップゲート型薄膜トランジスタを有する半導体装置を作製した場合、バックゲートの電位が安定するので、信頼性の高い半導体装置を得ることができる。

【図面の簡単な説明】

40

【0079】

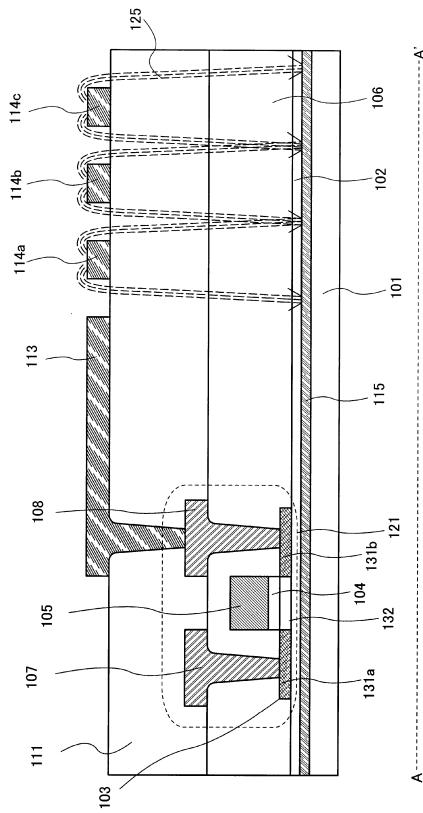

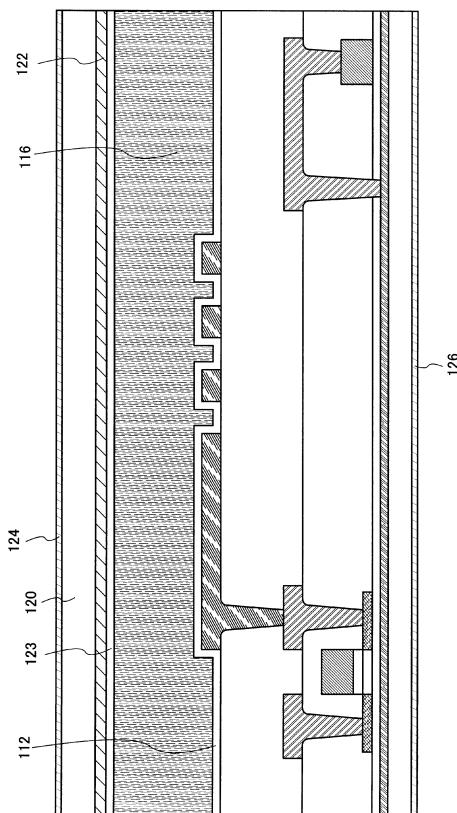

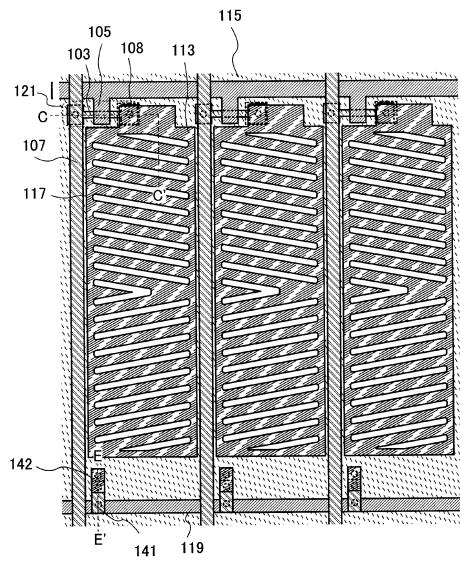

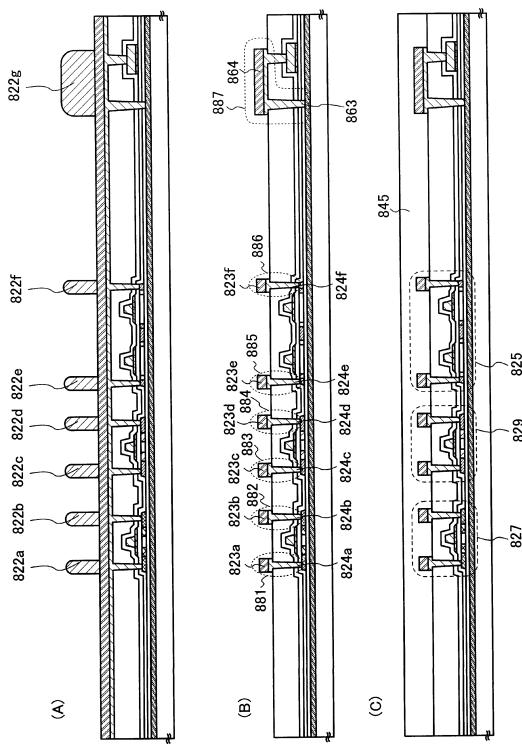

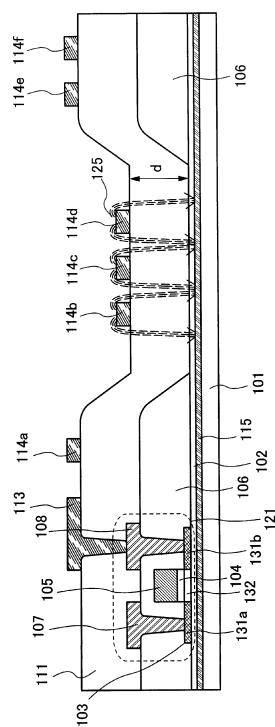

【図1】トップゲート型薄膜トランジスタを用いた画素部の構成例を示す断面図。

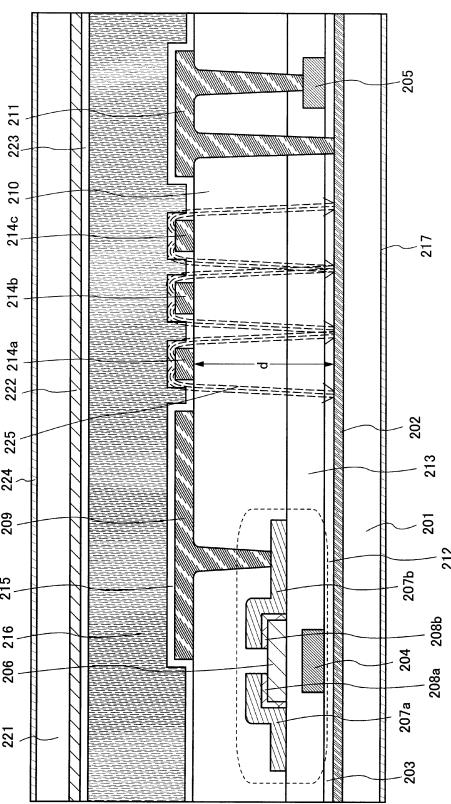

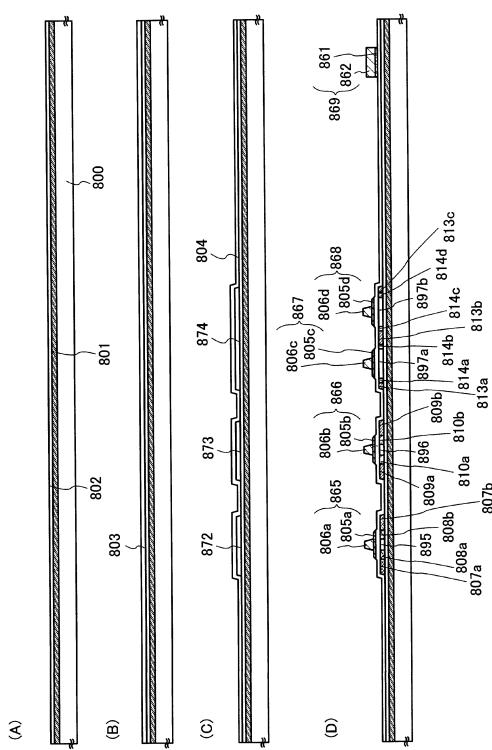

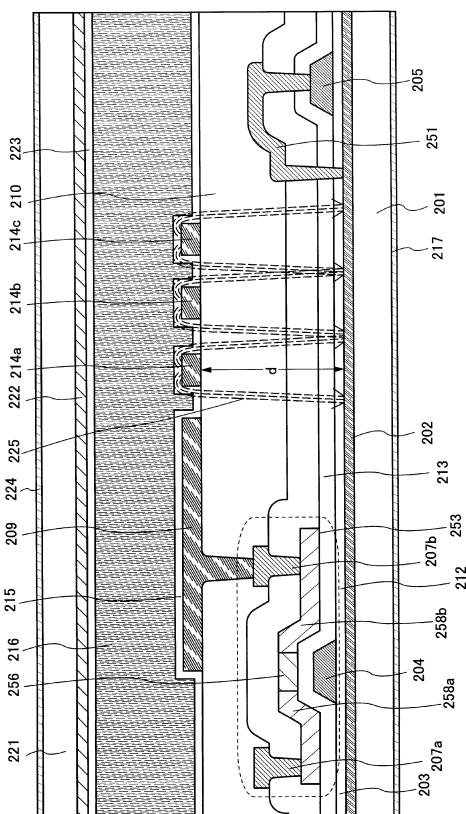

【図2】ボトムゲート型薄膜トランジスタを用いた画素部の構成例を示す断面図。

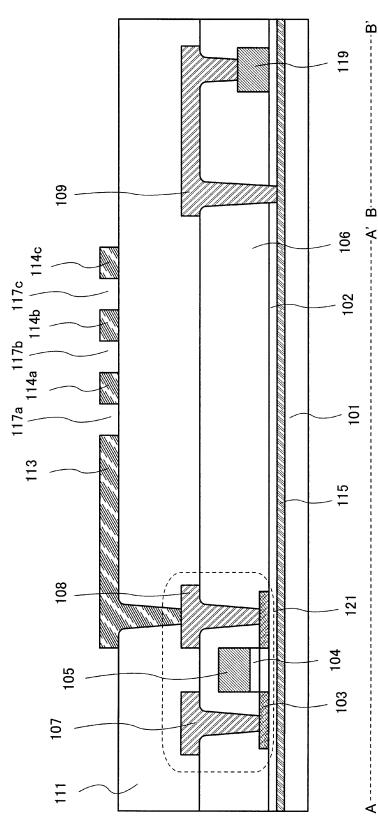

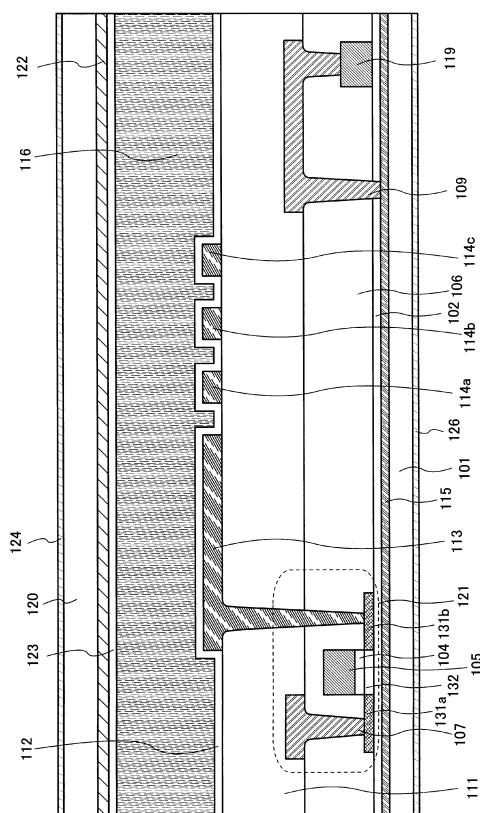

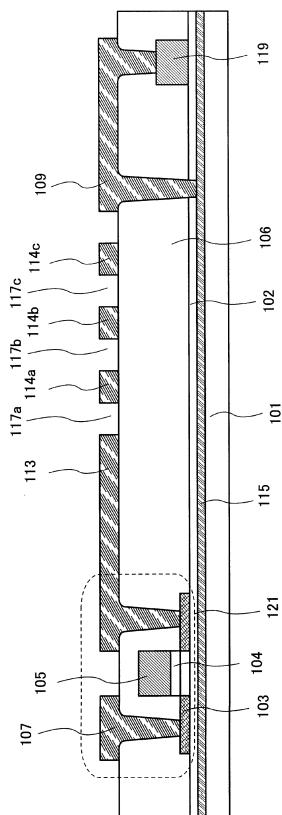

【図3】トップゲート型薄膜トランジスタを用いた画素部の構成例を示す断面図。

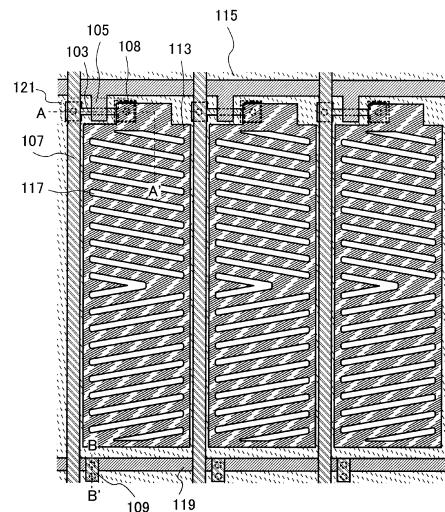

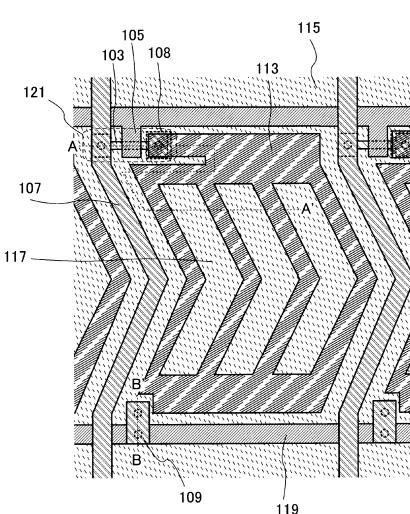

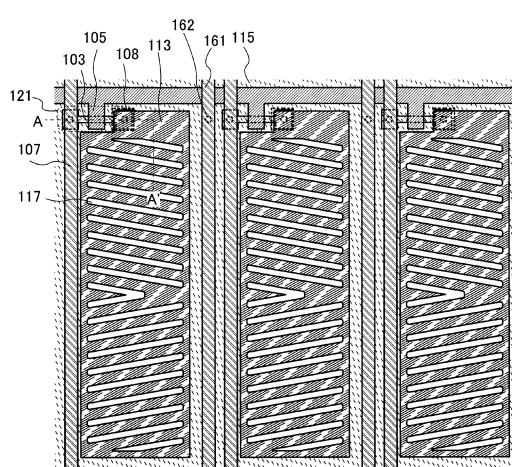

【図4】図1乃至図3で示す画素部の平面図。

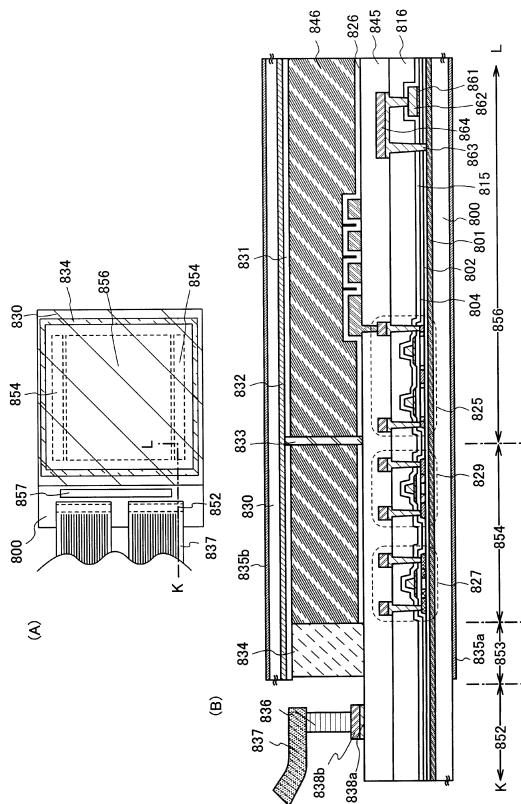

【図5】本発明の液晶表示装置の断面図。

【図6】本発明の液晶表示装置の断面図。

【図7】本発明の液晶表示装置の上面図。

【図8】本発明の液晶表示装置の上面図。

【図9】本発明の液晶表示装置の上面図。

50

- 【図10】本発明の液晶表示装置の断面図。

- 【図11】本発明の液晶表示装置の上面図。

- 【図12】本発明の液晶表示装置の断面図。

- 【図13】本発明の液晶表示装置の上面図。

- 【図14】本発明の液晶表示装置の上面図及び断面図。

- 【図15】本発明の液晶表示装置の作製工程を示す断面図。

- 【図16】本発明の液晶表示装置の作製工程を示す断面図。

- 【図17】本発明の液晶表示装置の作製工程を示す断面図。

- 【図18】本発明の液晶表示装置の作製工程を示す断面図。

- 【図19】本発明の液晶表示装置の回路図。 10

- 【図20】本発明の液晶表示装置の回路図。

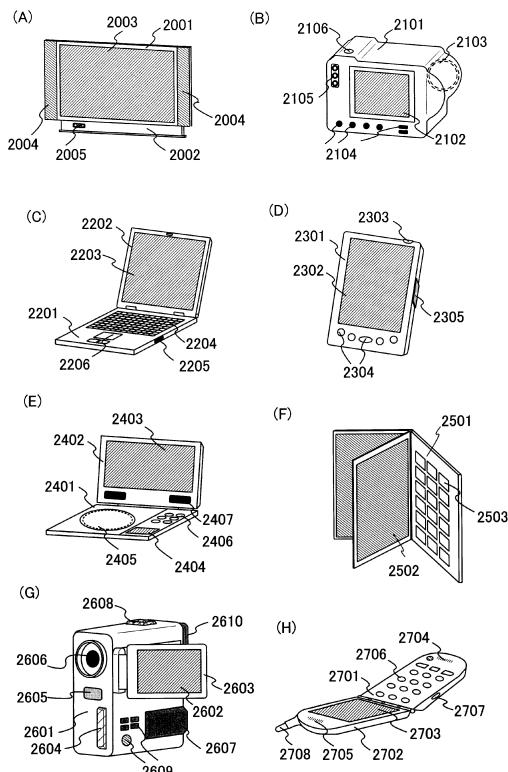

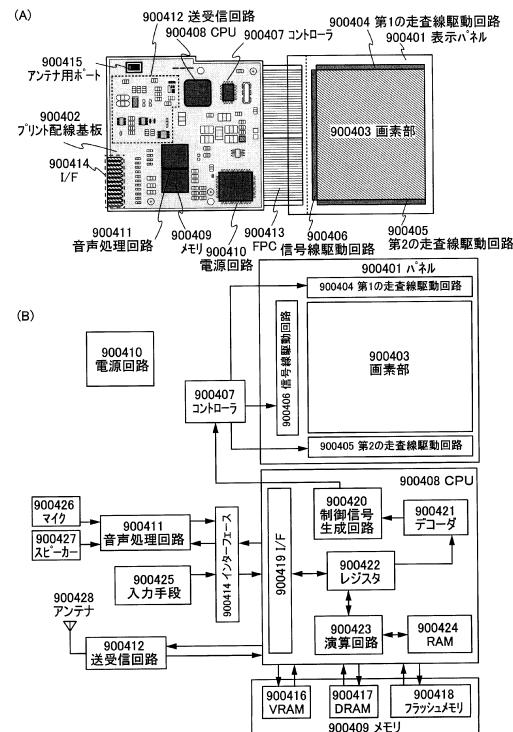

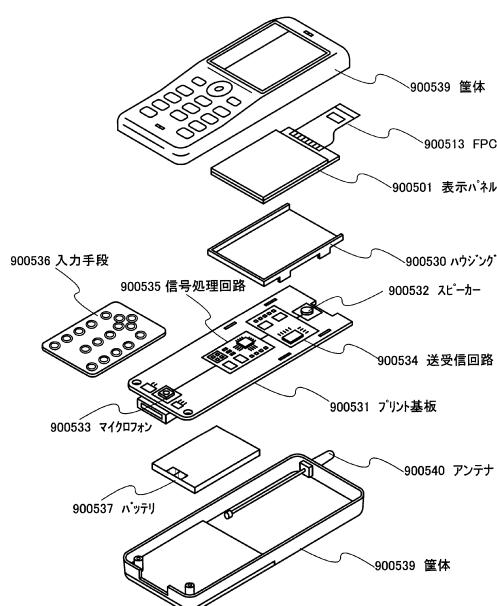

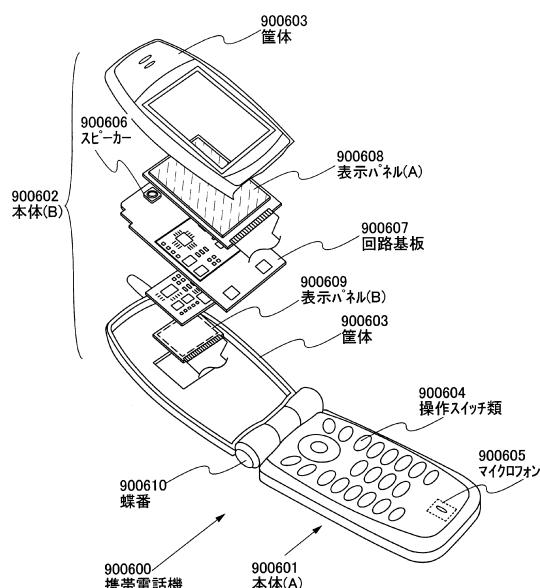

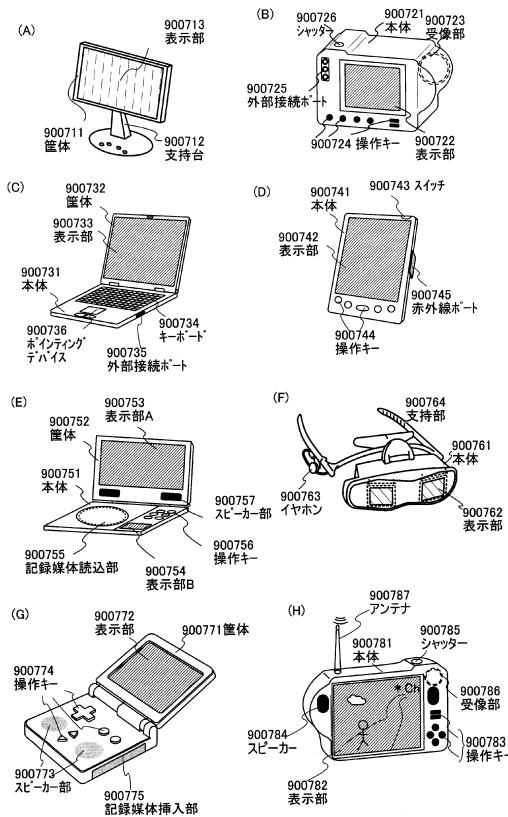

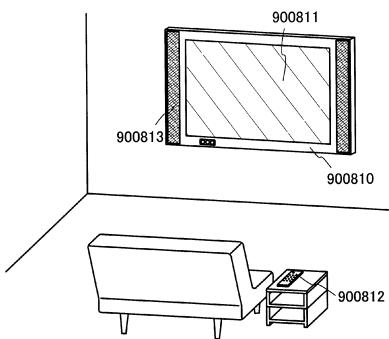

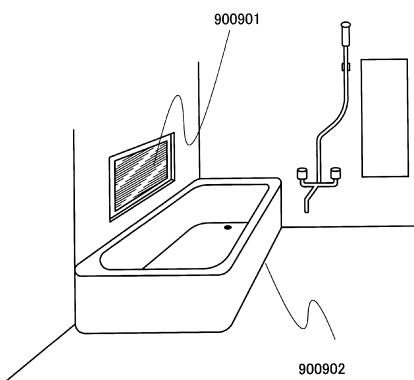

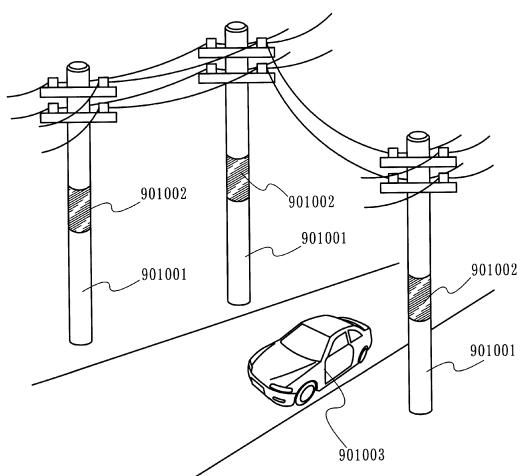

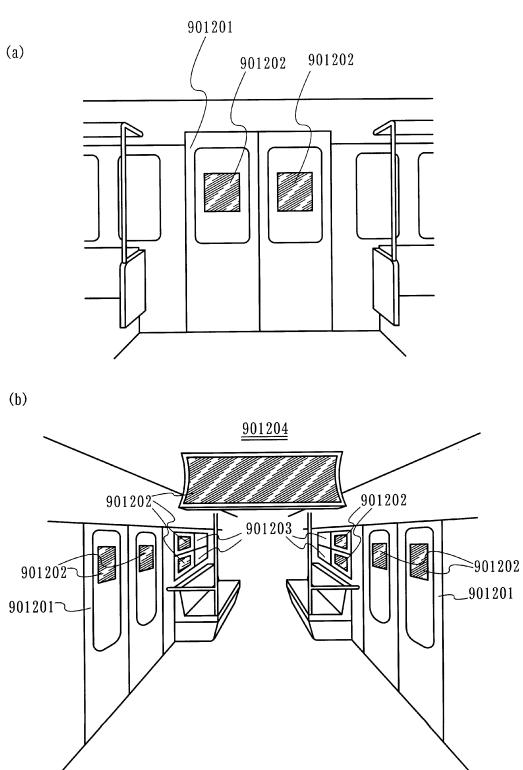

- 【図21】本発明の液晶表示装置を用いて作製した電子機器の例を示す図。

- 【図22】本発明の液晶表示装置の断面図。

- 【図23】本発明の液晶表示装置の上面図。

- 【図24】本発明の液晶表示装置の断面図。

- 【図25】本発明の液晶表示装置の断面図。

- 【図26】本発明の液晶表示装置の断面図。

- 【図27】本発明の液晶表示装置の上面図。

- 【図28】本発明の液晶表示装置を示す図。 20

- 【図29】本発明の液晶表示装置を示す図。

- 【図30】本発明の液晶表示装置を示す図。

- 【図31】本発明の液晶表示装置を示す図。

- 【図32】本発明の液晶表示装置を示す図。

- 【図33】本発明の液晶表示装置を示す図。

- 【図34】本発明の液晶表示装置を示す図。

- 【図35】本発明の液晶表示装置を示す図。

- 【図36】本発明の液晶表示装置を示す図。

- 【図37】本発明の液晶表示装置を示す図。

- 【図38】本発明の液晶表示装置を示す図。

- 【図39】本発明の液晶表示装置を示す図。 30

- 【図40】本発明の液晶表示装置を示す図。

- 【図41】本発明の液晶表示装置を示す図。

- 【図42】本発明の液晶表示装置を示す図。

- 【図43】本発明の液晶表示装置を示す図。

- 【図44】本発明の液晶表示装置を示す図。

- 【図45】本発明の液晶表示装置を示す図。

- 【図46】本発明の液晶表示装置を示す図。

- 【図47】本発明の液晶表示装置を示す図。

- 【図48】本発明の液晶表示装置を示す図。

- 【図49】本発明の液晶表示装置を示す図。 40

- 【図50】本発明の液晶表示装置を示す図。

- 【図51】本発明の液晶表示装置を示す図。

- 【図52】本発明の液晶表示装置を示す図。

- 【図53】本発明の液晶表示装置を示す図。

- 【図54】本発明の液晶表示装置を示す図。

- 【図55】本発明の液晶表示装置を示す図。

- 【図56】本発明の液晶表示装置を示す図。

- 【図57】本発明の液晶表示装置を示す図。

- 【図58】本発明の液晶表示装置を示す図。

- 【図59】本発明の液晶表示装置を示す図。 50

【図60】本発明の液晶表示装置を示す図。

【図61】本発明の液晶表示装置を示す図。

【発明を実施するための形態】

【0080】

以下、本発明の実施の態様について、図面を参照して説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本実施の形態の記載内容に限定して解釈されるものではない。なお、以下に示す図面において、同一部分又は同様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略する。

10

【0081】

【実施の形態1】

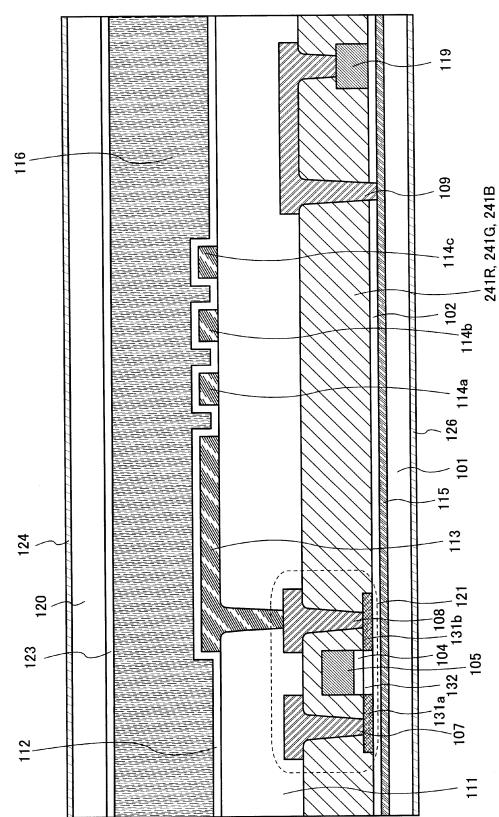

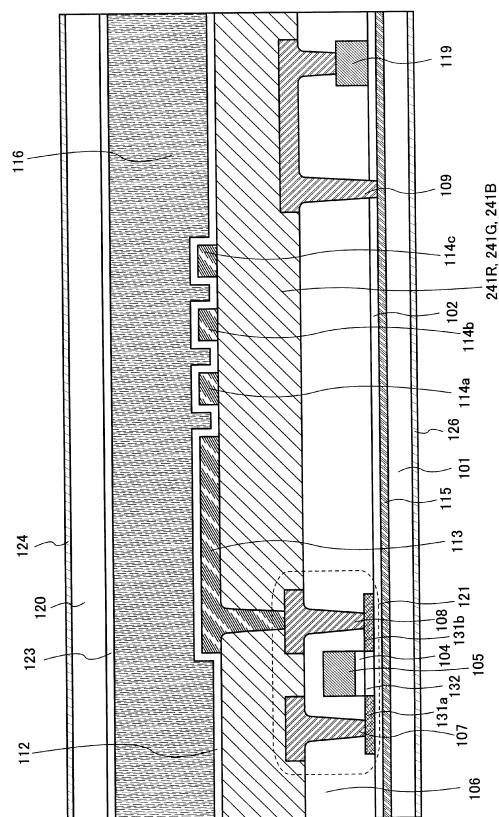

本実施の形態を、図1、図3、図4、図5を用いて説明する。

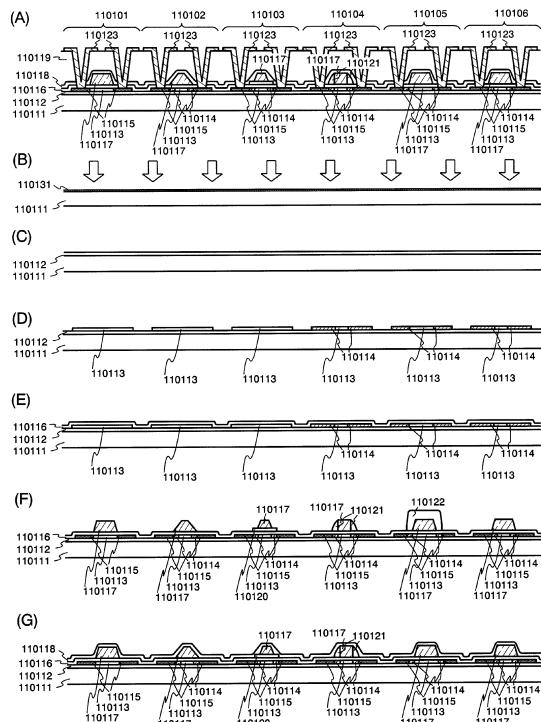

【0082】

図1は、画素部のスイッチング素子として、トップゲート型薄膜トランジスタ（Thin Film Transistor (TFT)）を用いた例である。基板101の一方の表面の全面に、FFS（Fringe-field switching）駆動における第1の電極となる導電膜115が形成されている。

【0083】

導電膜115として、透光性を有する導電膜（以下「透光性導電膜」という）を用いる。このような透光性導電膜として、インジウム錫酸化物（Indium Tin Oxide (ITO)）膜、インジウム亜鉛酸化物（Indium Zinc Oxide (IZO)）膜、酸化珪素を添加したインジウム錫酸化物（ITSOともいう）膜、酸化亜鉛（ZnO）膜、酸化スズカドミウム（CTO）膜、酸化スズ（SnO）膜などを用いればよい。

20

【0084】

導電膜115上には下地膜102、下地膜102上には、薄膜トランジスタ（Thin Film Transistor (TFT)）121が形成されている。TFT121は、ソース領域またはドレイン領域の一方である領域131a、ソース領域またはドレイン領域の他方である領域131b、チャネル形成領域132を含む活性層103、ゲート絶縁膜104、ゲート電極105を有している。なお図1ではゲート絶縁膜104は、チャネル形成領域132上部のみに形成されているが、チャネル形成領域132上部以外にも形成されていてもよい。

30

【0085】

TFT121及び下地膜102上に、層間絶縁膜106が形成されている。層間絶縁膜106上には、層間絶縁膜106中のコンタクトホールを介して、ソース領域またはドレイン領域の一方に電気的に接続される電極107、ソース領域またはドレイン領域の他方に電気的に接続される電極108が形成されている。

【0086】

層間絶縁膜106、電極107～109上に、層間絶縁膜111が形成されており、さらに層間絶縁膜111上に、層間絶縁膜111中に形成されたコンタクトホールを介して、電極108に電気的に接続される画素電極113及び114a～114cが形成されている。なお画素電極113は電極108ではなく、電極107に電気的に接続されていてもよい。また層間絶縁膜106及び111は、いずれか一方のみを形成してもよい。

40

【0087】

図1に示すように、画素電極114（114a～114c）と、画素電極113との間に電界125が発生する。後述するが、この電界125により液晶分子が駆動される。

【0088】

また図3に示すように、導電膜115は、層間絶縁膜106及び下地膜102中のコンタクトホールを介して、接続電極109と電気的に接続されており、接続電極109は配

50

線 119 と電気的に接続されている。なお配線 119 はゲート電極 105 と同じ材料、同じ工程により作製されており、接続電極 109 は、電極 107 及び電極 108 と同じ材料、同じ工程により作製されている。このように作製工程を追加せずに形成することができるため、フォトマスク数を低減させることができる。なお図 3 と図 1 に示す構成では同じものは同じ符号で示している。

【0089】

なお配線 119 は、ゲート配線 105 に平行に配置してもよい。配線 119 は、ゲート配線 105 に平行に配置すると、開口率の低下が小さくなる。

【0090】

また配線 119 を画素ごとに導電膜 115 に接続させると、導電膜 115 の抵抗を小さくさせることができる。さらにこの場合は、波形なまりを低減させることができる。 10

【0091】

また接続電極 109 を配線 119 に接続させずに、接続電極 109 を引き延ばして画素にわたって配置しても構わない。そのときは接続電極 109 をソース線 107 と平行に配置させることができ。 20

【0092】

図 4 に図 1 及び図 3 の上面図を示す。図 4 の A - A' 及び B - B' の断面図が図 3 であり、図 1 は図 4 の A - A' の断面図である。画素電極 113 及び 114a、114b、114c、等には、溝（「開口」、「スリット」、「隙間」、「間隙」、「スペース」ともいう）117 が形成されている。 20

【0093】

図 4 に示すように、複数のソース配線 107 が互いに平行（図中上下方向に延伸）かつ互いに離間した状態で配置されている。複数のゲート配線 105 は、ソース配線 107 に略直交する方向（図中左右方向）に延伸し、かつ互いに離間するように配置されている。配線 119 は、複数のゲート配線 105 それぞれに隣接する位置に配置されており、ゲート配線 105 に平行な方向、つまり、ソース配線 107 に直交する方向（図中左右方向）に延伸している。このように配置することにより、開口率を向上させることができる。ソース配線 107 と、配線 119 及びゲート配線 105 とによって、略長方形の空間が囲まれているが、この空間に液晶表示装置の画素電極 113 が配置されている。画素電極 113 を駆動する薄膜トランジスタ 121 は、図中左上の角に配置されている。画素電極及び薄膜トランジスタは、マトリクス状に複数配置されている。 30

【0094】

なお本実施の形態では、配線 119 と導電膜 115 はコンタクトホールを介して画素ごとに接続されているが、これに限定されない。

【0095】

なお、ゲート配線 105、配線 119、及びソース配線 107 は、アルミニウム（Al）、タンタル（Ta）、チタン（Ti）、モリブデン（Mo）、タングステン（W）、ネオジウム（Nd）、クロム（Cr）、ニッケル（Ni）、白金（Pt）、金（Au）、銀（Ag）、銅（Cu）、マグネシウム（Mg）、スカンジウム（Sc）、コバルト（Co）、亜鉛（Zn）、ニオブ（Nb）、シリコン（Si）、リン（P）、ボロン（B）、ヒ素（As）、ガリウム（Ga）、インジウム（In）、錫（Sn）、酸素（O）で構成された群から選ばれた一つもしくは複数の元素、または、前記群から選ばれた一つもしくは複数の元素を成分とする化合物、合金材料（例えば、インジウム錫酸化物（Indium Tin Oxide (ITO)）、インジウム亜鉛酸化物（Indium Zinc Oxide (IZO)）、酸化珪素を含むインジウム錫酸化物（ITO）、酸化亜鉛（ZnO）、酸化錫（SnO）、酸化錫カドミウム（CTO）、アルミニオジウム（Al-Nd）、マグネシウム銀（Mg-Ag）、モリブデンニオブ（Mo-Nb）など）で形成されることが望ましい。または、配線、電極、導電層、導電膜、端子などは、これらの化合物を組み合わせた物質などを有して形成されることが望ましい。もしくは、前記群から選ばれた一つもしくは複数の元素とシリコンの化合物（シリサイド）（例えば、アルミニ 40

リコン、モリブデンシリコン、ニッケルシリサイドなど)、前記群から選ばれた一つもしくは複数の元素と窒素の化合物(例えば、窒化チタン、窒化タンタル、窒化モリブデン等)を有して形成されることが望ましい。

【0096】

なお、シリコン(Si)には、n型不純物(リンなど)またはp型不純物(ボロンなど)を含んでいてもよい。シリコンが不純物を含むことにより、導電率が向上したり、通常の導体と同様な振る舞いをすることが可能となる。従って、配線、電極などとして利用しやすくなる。

【0097】

なお、シリコンは、単結晶、多結晶(ポリシリコン)、微結晶(マイクロクリスタルシリコン)など、様々な結晶性を有するシリコンを用いることが出来る。あるいは、シリコンは非晶質(アモルファスシリコン)などの結晶性を有さないシリコンを用いることが出来る。単結晶シリコンまたは多結晶シリコンを用いることにより、配線、電極、導電層、導電膜、端子などの抵抗を小さくすることが出来る。非晶質シリコンまたは微結晶シリコンを用いることにより、簡単な工程で配線などを形成することが出来る。

【0098】

なお、アルミニウムまたは銀は、導電率が高いため、信号遅延を低減することができる。さらに、エッチングしやすいので、パターニングしやすく、微細加工を行うことが出来る。

【0099】

なお、銅は、導電率が高いため、信号遅延を低減することができる。銅を用いる場合は、密着性を向上させるため、積層構造にすることが望ましい。

【0100】

なお、モリブデンまたはチタンは、酸化物半導体(ITO、IZOなど)またはシリコンと接触しても、不良を起こさない、エッチングしやすい、耐熱性が高いなどの利点を有するため、望ましい。

【0101】

なお、タンゲステンは、耐熱性が高いなどの利点を有するため、望ましい。

【0102】

なお、ネオジウムは、耐熱性が高いなどの利点を有するため、望ましい。特に、ネオジウムとアルミニウムとの合金にすると、耐熱性が向上し、アルミニウムがヒロックをおこしにくくなる。

【0103】

なお、シリコンは、トランジスタが有する半導体層と同時に形成できる、耐熱性が高いなどの利点を有するため、望ましい。

【0104】

なお、ITO、IZO、ITSO、酸化亜鉛(ZnO)、シリコン(Si)、酸化錫(SnO)、酸化錫カドミウム(CTO)は、透光性を有しているため、光を透過させる部分に用いることができる。たとえば、画素電極や共通電極として用いることができる。

【0105】

なお、IZOは、エッチングしやすく、加工しやすいため、望ましい。IZOは、エッチングしたときに、残渣が残ってしまう、ということも起こりにくい。したがって、画素電極としてIZOを用いると、液晶素子や発光素子に不具合(ショート、配向乱れなど)をもたらすことを低減出来る。

【0106】

なお、配線、電極、導電層、導電膜、端子などは、単層構造でもよいし、多層構造になつていてもよい。単層構造にすることにより、配線、電極、導電層、導電膜、端子などの製造工程を簡略化することができ、工程日数を少なくでき、コストを低減することができる。あるいは、多層構造にすることにより、それぞれの材料のメリットを生かしつつ、デメリットを低減させ、性能の良い配線、電極などを形成することができる。たとえば、低

10

20

30

40

50

抵抗材料（アルミニウムなど）を多層構造の中に含むことにより、配線の低抵抗化を図ることができる。また、低耐熱性の材料を、高耐熱性の材料で挟む積層構造にすることにより、低耐熱性の材料の持つメリットを生かしつつ、配線、電極などの耐熱性を高くすることが出来る。例えば、アルミニウムを含む層を、モリブデン、チタン、ネオジウムなどを含む層で挟む積層構造にすると望ましい。

#### 【0107】

また、配線、電極など同士が直接接する場合、お互いに悪影響を及ぼすことがある。例えば、一方の配線、電極などが他方の配線、電極など材料の中に入ってしまって、性質を変えてしまい、本来の目的を果たせなくなる。別の例として、高抵抗な部分を形成又は製造するときに、問題が生じて、正常に製造できなくなったりすることがある。そのような場合、積層構造により反応しやすい材料を、反応しにくい材料で挟んだり、覆ったりするといい。例えば、ITOとアルミニウムとを接続させる場合は、ITOとアルミニウムとの間に、チタン、モリブデン、ネオジウム合金を挟むことが望ましい。また、シリコンとアルミニウムとを接続させる場合は、ITOとアルミニウムとの間に、チタン、モリブデン、ネオジウム合金を挟むことが望ましい。

10

#### 【0108】

なお、配線とは、導電体が配置されているものを言う。線状に伸びていても良いし、伸びずに短く配置されていてもよい。したがって、電極は、配線に含まれている。

#### 【0109】

なお、ゲート配線105の方が、ソース配線107よりも耐熱性が高い材料を用いることが望ましい。なぜなら、ゲート配線105の方が、製造工程の過程で、高い温度状態に配置されることが多いからである。

20

#### 【0110】

なお、ソース配線107の方が、ゲート配線105よりも、抵抗の低い材料を用いることが望ましい。なぜなら、ゲート配線105には、H信号とL信号の2種の信号を与えるだけであるが、ソース配線107には、アナログの信号を与え、それが表示に寄与するからである。よって、ソース配線107には、正確な大きさの信号を供給できるようにするため、抵抗の低い材料を用いることが望ましい。

#### 【0111】

なお、配線119を設けなくてもよいが、配線119を設けることにより、各画素における共通電極の電位を安定化させることができる。なお、図4では、配線119は、ゲート線と平行には配置されているが、これに限定されない。ソース配線107と平行に配置されていてもよい。その時は、ソース配線107と同じ材質で形成されることが望ましい。

30

#### 【0112】

ただし、配線119は、ゲート線と平行には配置したほうが、開口率を大きくすることができ、効率的にレイアウトできるため、好適である。

#### 【0113】

基板101は、ガラス基板、石英基板、アルミナなど絶縁物で形成される基板、後工程の処理温度に耐え得る耐熱性を有するプラスチック基板、単結晶基板（単結晶シリコン基板）、SOI基板、または金属板である。また、多結晶珪素であってもよい。

40

#### 【0114】

なお、透過型の表示装置として動作させる場合は、基板101は、光透過性を有することが望ましい。

#### 【0115】

導電膜115は、光透過性を有する導電膜（例えば、酸化インジウム酸化スズ合金（Indium Tin Oxide (ITO) 膜、インジウム亜鉛酸化物（Indium Zinc Oxide (IZO)ともいう）、酸化亜鉛（ZnO）、酸化スズ（SnO）、若しくは不純物が導入された多結晶珪素膜又は非晶質珪素膜）から形成されている。

#### 【0116】

50

導電膜 115 上には、下地膜 102 として絶縁膜が形成されている。絶縁膜 102 は、基板 101 から不純物が拡散することを防止する膜であり、下地膜として機能する。絶縁膜 102 は、例えば、酸化珪素 (SiO<sub>x</sub>)、窒化珪素 (SiN<sub>x</sub>)、窒素を含む酸化珪素 (SiO<sub>x</sub>N<sub>y</sub> : x > y)、酸素を含む窒化珪素 (SiN<sub>x</sub>O<sub>y</sub> : x > y) など、酸素又は窒素を有する絶縁物質から形成される。また、これらの膜を複数積層した積層膜であってもよい。なお、基板 101 と導電膜 115 の間に絶縁膜 102 と同じ機能を有する絶縁膜があってもよい。

#### 【0117】

例えば下地膜 102 は、窒化珪素膜と酸化珪素膜の積層膜を用いてもよい。また酸化珪素膜の単層膜でもよい。酸化珪素膜を下地膜 102 として用いた場合は、ゲート絶縁膜 104 よりも厚くすると、ゲート配線 105 との容量カップリングを低減できるので有用である。そのため下地膜 102 は、ゲート絶縁膜 104 より厚く、望ましくはゲート絶縁膜 104 の 3 倍以上の厚さがあるとよい。

#### 【0118】

絶縁膜 102 上には半導体膜 103 が形成されている。半導体膜 103 には、薄膜トランジスタ 121 のソース領域またはドレイン領域の一方となる領域 131a、及びソース領域またはドレイン領域の他方となる領域 131b が形成されている。領域 131a、131b は、例えば n 型の不純物領域であるが、p 型の不純物領域であってもよい。n 型を付与する不純物としては、例えばリン (P) 及びヒ素 (As) があり、p 型を付与する不純物としては、例えばボロン (B) 及びガリウム (Ga) がある。また領域 131a と 131b との間にチャネル形成領域 132 が形成される。

#### 【0119】

さらに領域 131a とチャネル形成領域 132 との間、領域 131b とチャネル形成領域 132 との間に、低濃度不純物領域を形成してもよい。

#### 【0120】

図 4 に示すように、導電膜 115 は画素のほぼ全面に形成されている。ソース配線 107 と、配線 119 及びゲート配線 105 とによって囲まれている長方形状の領域には、それぞれ薄膜トランジスタ 121 が配置されている。すなわち第 1 の配線としてゲート線 103、第 2 の配線としてソース線 107、第 3 の配線として配線 119 が形成されている。薄膜トランジスタ 121 を配置することにより、画素内における表示に有効な領域を、より効率的に形成することができる。つまり、開口率の向上につながる。なお、半導体膜 103 は、例えば多結晶珪素膜であるが、他の半導体膜（例えば非晶質珪素膜、単結晶珪素膜、有機半導体膜、又はカーボンナノチューブ）、微結晶珪素膜（マイクロクリスタルシリコン膜、あるいはセミアモルファスシリコン膜ともいう）であってもよい。

#### 【0121】

ここで、セミアモルファスシリコン膜に代表されるセミアモルファス半導体膜とは、非晶質半導体と結晶構造を有する半導体（単結晶、多結晶を含む）膜の中間的な構造の半導体を含む膜である。このセミアモルファス半導体膜は、自由エネルギー的に安定な第 3 の状態を有する半導体膜であって、短距離秩序を持ち格子歪みを有する結晶質なものであり、その粒径を 0.5 ~ 20 nm として非単結晶半導体膜中に分散させて存在せしめることができる。セミアモルファス半導体膜は、そのラマンスペクトルが 520 cm<sup>-1</sup> よりも低波数側にシフトしており、また X 線回折では Si 結晶格子に由来するとされる (111)、(220) の回折ピークが観測される。また、未結合手（ダンギングボンド）を終端化させるために水素またはハロゲンを少なくとも 1 原子% またはそれ以上含ませている。本明細書では便宜上、このような半導体膜をセミアモルファス半導体 (SAS) 膜と呼ぶ。さらに、ヘリウム、アルゴン、クリプトン、ネオンなどの希ガス元素を含ませて格子歪みをさらに助長させることで安定性が増し良好なセミアモルファス半導体膜が得られる。

#### 【0122】

また SAS 膜は珪素（シリコン）を含む気体をグロー放電分解することにより得ること

10

20

30

40

50

ができる。代表的な珪素（シリコン）を含む気体としては、 $\text{SiH}_4$  であり、その他にも  $\text{Si}_2\text{H}_6$ 、 $\text{SiH}_2\text{Cl}_2$ 、 $\text{SiHCl}_3$ 、 $\text{SiCl}_4$ 、 $\text{SiF}_4$ などを用いることができる。また水素や、水素にヘリウム、アルゴン、クリプトン、ネオンから選ばれた一種または複数種の希ガス元素を加えたガスで、この珪素（シリコン）を含む気体を希釈して用いることで、S A S 膜の形成を容易なものとすることができます。希釈率は 2 倍～1000 倍の範囲で珪素（シリコン）を含む気体を希釈することが好ましい。またさらに、珪素（シリコン）を含む気体中に、 $\text{CH}_4$ 、 $\text{C}_2\text{H}_6$ などの炭化物気体、 $\text{GeH}_4$ 、 $\text{GeF}_4$ などのゲルマニウム化気体、 $\text{F}_2$ などを混入させて、エネルギー・バンド幅を 1.5～2.4 eV、若しくは 0.9～1.1 eV に調節しても良い。

## 【0123】

10

さらにゲート線 105 の下には半導体層を配置してもよい。これにより導電膜 115 とゲート線 105 との容量カップリングを低減することができる。そのためゲート線 105 の充電及び放電が素早くでき、波形なまりを抑制することができる。

## 【0124】

半導体膜 103 上を含む全面上には、薄膜トランジスタ 121 のゲート絶縁膜 104 が形成されている。

## 【0125】

ただし、ゲート絶縁膜 104 は、チャネル領域近傍にのみ配置され、それ以外の部分では、配置されていない場合もある。また、場所によって厚さや積層構造や厚さが異なる場合がある。例えば、チャネル近傍のみ厚かったり、層の数が多かったりして、それ以外の場所では、膜厚が薄かったり、層の数が少ないと場合もある。このようにすることにより、ソース領域やドレイン領域への不純物の添加が制御しやすくなる。また、チャネル近傍のゲート絶縁膜 104 の厚さや層の数を変えることにより、半導体膜への不純物の添加量が場所によって変わるようにして、LDD 領域を形成することができる。LDD 領域を形成することにより、漏れ電流を低減したり、ホットキャリアの発生を抑えて信頼性を向上させたりすることができる。

20

## 【0126】

画素電極 113 が形成される領域では、ゲート絶縁膜 104 は形成されなくても構わない。画素電極 113 と導電膜 113 との間の距離を小さくでき、電界制御がしやすくなる。

30

## 【0127】

ゲート絶縁膜 104 は、例えば、酸化珪素（ $\text{SiO}_x$ ）、窒化珪素（ $\text{SiN}_x$ ）、窒素を含む酸化珪素（ $\text{SiO}_x\text{N}_y$  :  $x > y$ ）、酸素を含む窒化珪素（ $\text{SiN}_x\text{O}_y$  :  $x > y$ ）など、酸素又は窒素を有する絶縁物質から形成される。また、これらの膜を複数積層した積層膜であってもよい。ゲート絶縁膜 104 上には半導体膜 103 の上方に位置するゲート電極 105 が形成されている。

## 【0128】

図 4 及び図 3 に示すように、ゲート電極（ゲート配線）105 は配線 119 と同一配線層である

40

## 【0129】

ゲート絶縁膜 104 上及びゲート電極 105 上には、第 1 層間絶縁膜 106 が形成されている。第 1 層間絶縁膜 106 には、無機材料又は有機材料を用いることができる。有機材料としては、ポリイミド、アクリル、ポリアミド、ポリイミドアミド、レジスト、シリコサン、又はポリシラザンなどを用いることができる。無機材料としては、酸化珪素（ $\text{SiO}_x$ ）、窒化珪素（ $\text{SiN}_x$ ）、窒素を含む酸化珪素（ $\text{SiO}_x\text{N}_y$  :  $x > y$ ）、酸素を含む窒化珪素（ $\text{SiN}_x\text{O}_y$  :  $x > y$ ）など、酸素又は窒素を有する絶縁物質から形成される。また、これらの膜を複数積層した積層膜であってもよい。また、有機材料と無機材料を組み合わせて積層膜にしてもよい。

## 【0130】

絶縁膜 102、ゲート絶縁膜 104、及び第 1 層間絶縁膜 106 には、領域 131a 上

50

に位置するコンタクトホール、領域 131b 上に位置するコンタクトホール、導電膜 115 上に位置するコンタクトホール、及び配線 119 上に位置するコンタクトホールが形成されている。第 1 層間絶縁膜 106 上には、ソース配線 107、電極 108、及び接続用電極 109 が形成されている。

【0131】

なお、絶縁膜として無機材料を用いることにより、水分や不純物の侵入を止めることができる。特に、窒素を含む層を用いると、水分や不純物をブロックする機能が高い。

【0132】

なお、絶縁膜として有機材料を用いることにより、表面を平坦にすることが出来る。そのため、その上の層に対して、よい効果をもたらすことが出来る。例えば、有機材料の上に形成する層も平坦にすることが出来るため、液晶の配向の乱れを防いだりすることが出来る。

10

【0133】

ソース配線 107 は領域 131a の上方に位置しており、コンタクトホールを介して領域 131a に電気的に接続している。したがって、電極 108 は、コンタクトホールを介して領域 131b に電気的に接続している。

【0134】

ただし、画素電極 113 と、不純物領域 131b とを、接続用導電膜を介さずに、直接接続してもよい。この場合、画素電極 113 と、領域 131b とを接続するためのコンタクトホールは、深く開ける必要が出てくるが、接続用導電膜が必要ないため、その領域を開口領域として画像表示に利用できる。そのため、開口率が向上し、低消費電力化をはかることができる。

20

【0135】

接続電極 109 は、配線 119 の上方に位置しており、配線 119 及び導電膜 115 それぞれに電気的に接続している。このように、導電膜 115 は、接続用電極 109 を介して配線 119 に電気的に接続している。なお、接続用電極 109 は複数設けられていてよい。このようにすると、導電膜 115 の電位が安定化する。また、接続用電極 109 を介して導電膜 115 と配線 119 を接続することにより、コンタクトホールを形成する回数を減らすことが出来るので、プロセス工程を簡略化することが出来る。

【0136】

30

なお、接続用電極 109 は、ソース配線 107 と同時に、同じ材料を用いて形成したが、これに限定されない。画素電極 113 と同時に、同じ材料を用いて形成してもよい。

【0137】

ソース配線 107、電極 108、接続用電極 109、及び第 1 層間絶縁膜 106 上には、第 2 層間絶縁膜 111 が形成されている。なお、第 2 層間絶縁膜 111 を形成しない構成としても良い(図 28 参照)。第 2 層間絶縁膜 111 には、無機材料又は有機材料を用いることができる。有機材料としては、ポリイミド、アクリル、ポリアミド、ポリイミドアミド、レジスト、又はシロキサン、ポリシラザンなどを用いることができる。無機材料としては、酸化珪素(SiO<sub>x</sub>)、窒化珪素(SiN<sub>x</sub>)、窒素を含む酸化珪素(SiO<sub>x</sub>N<sub>y</sub> : x > y)、酸素を含む窒化珪素(SiN<sub>x</sub>O<sub>y</sub> : x > y)など、酸素又は窒素を有する絶縁物質から形成される。また、これらの膜を複数積層した積層膜であってもよい。また、有機材料と無機材料を組み合わせて積層膜にしてもよい。

40

【0138】

なお第 2 層間絶縁膜 111 を形成しない場合の断面図を、図 28 に示す。図 28 中で、図 3 と同じものは同じ符号で示している。電極 108 が形成されないので、画素電極 113 が島状半導体膜 103 に直接接続されている。ソース配線 107、画素電極 113 及び画素電極 114、並びに接続用電極 109 は、同じ材料、同じ工程で形成される。図 28 に示す構成では、画素電極 113 と導電膜 105 との間隔が小さくでき、電界制御がしやすくなる。

【0139】

50

第2層間絶縁膜111上には、FSS駆動の第2の電極である画素電極113、114a、114b、114c、等が形成されている。なお断面図である図1及び図3では便宜上画素電極113と画素電極114(114a、114b、114c、等)を分けているが、上面図である図4を見れば分かるように、画素電極は、同一材料、同一工程で形成された導電膜に、溝(「開口」、「スリット」、「隙間」、「間隙」、「スペース」ともいう)117(117a、117b、117c、等)が形成されているものである。よって以下の記載においては、画素電極113、114(114a、114b、114c、等)を、まとめて画素電極113として説明することもある。

#### 【0140】

画素電極113は、画素ごとに個別の電圧が供給される画素電極として機能し、ITO(酸化インジウム酸化スズ合金)、ZnO(酸化亜鉛)、酸化インジウムに2~20wt%のZnOを交合したターゲットを用いて形成されたIZO(インジウム亜鉛酸化物)、酸化スズ(SnO)などによって形成されている。画素電極113は、一部が電極108の上方に位置しており、電極108に電気的に接続している。このように、画素電極113は、電極108を介して薄膜トランジスタ121の領域131bに電気的に接続している。

#### 【0141】

なお、接続用電極109がない場合は、画素電極113は、薄膜トランジスタ121の領域131bに直接接続している。

#### 【0142】

図3及び図4に示すように、画素電極113は略長方形であり、複数の溝117a、117b、117c、等を有している。溝117a、117b、117c、等の例としては、スリット状で互いに平行であるものを多く含む。

#### 【0143】

図4に示す例では、溝117a、117b、117c、…の向きは、ソース配線107に対して斜めであるが、画素の図中上半分に位置する溝と、下半分に位置する溝の向きは互いに異なる。溝117a、117b、117c、…が形成されることにより、導電膜115と画素電極113の間で基板に平行な成分を有する電界が、画素電極114のそれから導電膜115に向かって生じる。このため、画素電極113及び114の電位を制御することにより、後述する液晶の配向方向を制御することができる。

#### 【0144】

また、図4に示されるように、溝117(117a、117b、117c、… )は、向きが異なるものを配置されている。これによって、液晶分子の動く方向が異なる領域を複数設けることが出来る。つまり、マルチドメイン構造にすることが出来る。マルチドメイン構造にすることにより、ある特定の方向から見たとき、画像の表示が正しくなくなってしまうことを防ぐことができ、その結果、視野角を向上させることができる。

#### 【0145】

なお、溝の形状は本実施形態の形状に限定されない。溝の形状には、例えば櫛歯形状の電極における櫛歯部分の相互間のスペース等、導電体が形成されていないスペースを含まるものとする。

#### 【0146】

なお画素電極113の厚さと導電膜115の厚さを比較した場合、導電膜115の方が膜厚が厚い方が好ましい。さらに、より好ましくは導電膜115の方が画素電極113よりも1.5倍以上、その膜厚が厚い方が好ましい。こうすることにより、抵抗を低減させることができる。

#### 【0147】

第2層間絶縁膜111上及び画素電極113上には、第1配向膜112及び液晶116が積層されている。液晶116としては、強誘電性液晶(FLC)、双安定性液晶、ネマティック液晶、スマートティック液晶、高分子分散型液晶、ホモジニアス配向になるような液晶、ホメオトロピック配向になるような液晶などを用いることができる。また液晶以外

10

20

30

40

50

を用いてもよく、例えば電気映像像素子等を用いても構わない。液晶 116 上には、第 2 配向膜 123 及びカラーフィルタ 122 を介して対向基板 120 が配置されている。なお、基板 101 及び対向基板 120 それぞれには、偏光板 126、124 が設けられている。

【0148】

なお、偏光板のほかに、位相差板や  $1/4$  板などが配置されている場合も多い。

【0149】

なお、上記した構成において、導電膜 115、画素電極 113 のうち溝が形成されていない部分、及びこれらの相互間に位置する各絶縁膜によって、容量が形成される。この容量が形成されることにより保持容量が大きくなる。

【0150】

次に、本発明の半導体装置、液晶表示装置の製造方法の一例について説明する。まず、基板 101 上に透光性を有する導電膜 115（例えばインジウム錫酸化物（ITO）、インジウム亜鉛酸化物（IZO）、酸化亜鉛（ZnO）、酸化スズ（SnO）、又は珪素（Si））を基板全面に形成する。

【0151】

また図 25 に示すように、開口部で絶縁膜 106 を除去しても構わない。さらにあるいは、ゲート絶縁膜 104、下地膜 102 を除去しても構わない。すなわち、開口部で絶縁膜 106 を除去した半導体装置、開口部で絶縁膜 106 及びゲート絶縁膜 104 を除去した半導体装置、開口部で絶縁膜 106、ゲート絶縁膜 104、下地膜 102 を除去した半導体装置を作製することが可能である。これにより画素電極 114 と導電膜 115 との間隔  $d$  を小さくすることができ、その結果、電界制御をしやすくなる。

【0152】

次いで、基板 101 及び導電膜 115 上それぞれに、絶縁膜 102 を形成する。絶縁膜 102 は、後述するゲート絶縁膜 104 より厚く形成されることが望ましい。次いで、絶縁膜 102 上に半導体膜（例えば多結晶珪素膜）を形成し、この半導体膜を、レジストを用いたエッチングにより選択的に除去する。これにより、絶縁膜 102 上には島状の半導体膜 103 が形成される。

【0153】

半導体膜は多結晶珪素膜だけでなく、非晶質珪素膜やその他の非単結晶珪素膜を用いてもよい。また珪素に限定されず、ZnO、a-InGaZnO、SiGe、GaAs などの化合物半導体を用いてもよい。

【0154】

あるいは基板 101 として半導体基板や SOI（Silicon On Insulator）基板を用いて、島状の半導体膜 103 を形成してもよい。

【0155】

次いで、半導体膜 103 上及び絶縁膜 102 上に、ゲート絶縁膜 104 を形成する。ゲート絶縁膜 104 は例えば窒素を含む酸化珪素膜又は酸化珪素膜であり、プラズマ CVD 法により形成される。なお、ゲート絶縁膜 104 を窒化珪素膜、若しくは窒化珪素及び酸化珪素を有する多層膜により形成してもよい。次いで、ゲート絶縁膜 104 上に導電膜を形成し、この導電膜に、エッチングを行うことにより、選択的に除去する。これにより、半導体膜 103 上に位置するゲート絶縁膜 104 上には、ゲート電極 105 が形成される。また、本工程により、ゲート配線 105 及び配線 119 が形成される。

【0156】

なお、上記したように配線 119 を設けることにより、各画素において導電膜 115 の電位を安定化させることができる。また、配線 119 を形成しなくてもよい。また、配線 119 を他の層（例えばソース配線 107 と同一の層、又は導電膜 115 と同一の層、又は画素電極 113 と同一の層）に設けてもよく、複数の層に分けて形成してもよい。また、本図において配線 119 は、ソース配線 107 に直交する方向に延伸しているが、ソース配線 107 と同一方向に延伸する構成であってもよい。

【0157】

10

20

30

40

50

なお、ゲート電極 105、配線 119 を構成する導電膜は、アルミニウム (A1)、タンタル (Ta)、チタン (Ti)、モリブデン (Mo)、タンゲステン (W)、ネオジウム (Nd)、クロム (Cr)、ニッケル (Ni)、白金 (Pt)、金 (Au)、銀 (Ag)、銅 (Cu)、マグネシウム (Mg)、スカンジウム (Sc)、コバルト (Co)、亜鉛 (Zn)、ニオブ (Nb)、シリコン (Si)、リン (P)、ボロン (B)、ヒ素 (As)、ガリウム (Ga)、インジウム (In)、錫 (Sn)、酸素 (O) で構成された群から選ばれた一つもしくは複数の元素、または、前記群から選ばれた一つもしくは複数の元素を成分とする化合物、合金材料 (例えば、インジウム錫酸化物 (ITO)、インジウム亜鉛酸化物 (IZO)、酸化珪素を含むインジウム錫酸化物 (ITSO)、酸化亜鉛 (ZnO)、酸化錫 (SnO)、酸化錫カドミウム (CTO)、アルミニネオジウム (A1-Nd)、マグネシウム銀 (Mg-Ag)、モリブデンニオブ (Mo-Nb) など) で形成されることが望ましい。または、ゲート電極 105、配線 119 を構成する導電膜は、これらの化合物を組み合わせた物質などを有して形成されることが望ましい。もしくは、前記群から選ばれた一つもしくは複数の元素とシリコンの化合物 (シリサイド) (例えば、アルミシリコン、モリブデンシリコン、ニッケルシリサイドなど)、前記群から選ばれた一つもしくは複数の元素と窒素の化合物 (例えば、窒化チタン、窒化タンタル、窒化モリブデン等) を有して形成されることが望ましい。

## 【0158】

なお、シリコン (Si) には、n型不純物 (リンなど) またはp型不純物 (ボロンなど) を含んでいてもよい。シリコンが不純物を含むことにより、導電率が向上したり、通常の導体と同様な振る舞いをすることが可能となる。従って、配線、電極などとして利用しやすくなる。

## 【0159】

なお、シリコンは、単結晶、多結晶 (ポリシリコン)、微結晶 (マイクロクリスタルシリコン) など、様々な結晶性を有するシリコンを用いることが出来る。あるいは、シリコンは非晶質 (アモルファスシリコン) などの結晶性を有さないシリコンを用いることが出来る。単結晶シリコンまたは多結晶シリコンを用いることにより、配線、電極、導電層、導電膜、端子などの抵抗を小さくすることが出来る。非晶質シリコンまたは微結晶シリコンを用いることにより、簡単な工程で配線などを形成することが出来る。

## 【0160】

なお、アルミニウムまたは銀は、導電率が高いため、信号遅延を低減することができる。さらに、エッティングしやすいので、パターニングしやすく、微細加工を行うことが出来る。

## 【0161】

なお、銅は、導電率が高いため、信号遅延を低減することができる。銅を用いる場合は、密着性を向上させるため、積層構造にすることが望ましい。

## 【0162】

なお、モリブデンまたはチタンは、酸化物半導体 (ITO、IZOなど) またはシリコンと接触しても、不良を起こさない、エッティングしやすい、耐熱性が高いなどの利点を有するため、望ましい。

## 【0163】

なお、タンゲステンは、耐熱性が高いなどの利点を有するため、望ましい。

## 【0164】

なお、ネオジウムは、耐熱性が高いなどの利点を有するため、望ましい。特に、ネオジウムとアルミニウムとの合金にすると、耐熱性が向上し、アルミニウムがヒロックをおこしにくくなる。

## 【0165】

なお、シリコンは、トランジスタが有する半導体層と同時に形成できる、耐熱性が高いなどの利点を有するため、望ましい。

## 【0166】

10

20

30

40

50

なお、ITO、IZO、ITSO、酸化亜鉛(ZnO)、シリコン(Si)、酸化錫(SnO)、酸化錫カドミウム(CTO)は、透光性を有しているため、光を透過させる部分に用いることができる。たとえば、画素電極や共通電極として用いることができる。

#### 【0167】

なお、IZOは、エッティングしやすく、加工しやすいため、望ましい。IZOは、エッティングしたときに、残渣が残ってしまう、ということも起こりにくい。したがって、画素電極としてIZOを用いると、液晶素子や発光素子に不具合(ショート、配向乱れなど)をもたらすことを低減出来る。

#### 【0168】

なお、ゲート電極105、配線119を構成する導電膜は、単層構造でもよいし、多層構造になっていてもよい。単層構造にすることにより、ゲート電極105、配線119を構成する導電膜の製造工程を簡略化することができ、工程日数を少なくでき、コストを低減することが出来る。あるいは、多層構造にすることにより、それぞれの材料のメリットを生かしつつ、デメリットを低減させ、性能の良い配線、電極などを形成することが出来る。たとえば、低抵抗材料(アルミニウムなど)を多層構造の中に含むことにより、配線の低抵抗化を図ることが出来る。また、低耐熱性の材料を、高耐熱性の材料で挟む積層構造にすることにより、低耐熱性の材料の持つメリットを生かしつつ、配線、電極などの耐熱性を高くすることが出来る。例えば、アルミニウムを含む層を、モリブデン、チタン、ネオジウムなどを含む層で挟む積層構造にすると望ましい。

10

#### 【0169】

また、配線、電極など同士が直接接する場合、お互いに悪影響を及ぼすことがある。例えば、一方の配線、電極などが他方の配線、電極など材料の中に入ってしまって、性質を変えてしまい、本来の目的を果たせなくなる。別の例として、高抵抗な部分を形成又は製造するときに、問題が生じて、正常に製造できなくなったりすることがある。そのような場合、積層構造により反応しやすい材料を、反応しにくい材料で挟んだり、覆ったりするといい。例えば、ITOとアルミニウムとを接続させる場合は、ITOとアルミニウムとの間に、チタン、モリブデン、ネオジウム合金を挟むことが望ましい。また、シリコンとアルミニウムとを接続させる場合は、ITOとアルミニウムとの間に、チタン、モリブデン、ネオジウム合金を挟むことが望ましい。

20

#### 【0170】

なお、配線とは、導電体が配置されているものを言う。線状に伸びていても良いし、伸びずに短く配置されていてもよい。したがって、電極は、配線に含まれている。

30

#### 【0171】

次いで、ゲート電極105をマスクとして、半導体膜103に不純物を注入する。これにより、半導体膜103には、ソース領域またはドレイン領域の一方である領域131a、ソース領域またはドレイン領域の他方である131b、及びチャネル形成領域132が形成される。なお、n型、p型の不純物元素を個別に注入してもよいし、特定の領域にはn型の不純物元素及びp型の不純物元素を共に注入してもよい。ただし後者の場合には、n型の不純物元素又はp型の不純物元素のどちらか一方の注入量が多くなるようにする。なお、本工程において、レジストをマスクとして用いてもよい。

40

#### 【0172】

なお、このとき、ゲート絶縁膜104の厚さや積層構造を変えることにより、LDD領域を形成してもよい。LDD領域を形成したい部分は、ゲート絶縁膜104を厚くしたり、層の数を増やしたりすればよい。その結果、不純物の注入量が減るため、LDD領域を容易に形成することが出来る。

#### 【0173】

なお、半導体膜103に不純物を注入する場合、ゲート電極105を形成する前、例えば、ゲート絶縁膜104を成膜する前や、成膜した後に行っても良い。その場合は、レジストをマスクとして用いて、形成する。これにより、ゲートと同じレイヤの電極と、不純物が注入された半導体膜との間で、容量を形成することが出来る。ゲートと同じレイヤの

50

電極と、不純物が注入された半導体膜との間には、ゲート絶縁膜が配置されているので、膜厚がうすく、大きな容量を形成することが出来る。

【0174】

次いで、第1層間絶縁膜106を形成し、さらのコンタクトホールを形成する。次いで、第1層間絶縁膜106上に導電膜（例えば金属膜）を形成し、この導電膜を、マスクを用いたエッチングにより選択的に除去する。これにより、ソース配線107、電極108、及び接続電極109が形成される。

【0175】

次いで、第2層間絶縁膜111を形成し、さらにコンタクトホールを形成する。次いで、第2層間絶縁膜111上に透光性を有する導電膜（インジウム錫酸化物（ITO）、インジウム亜鉛酸化物（IZO）、酸化亜鉛（ZnO）、酸化スズ（SnO）、又は珪素（Si））を形成し、この導電膜を、レジストを用いたエッチングにより選択的に除去する。これにより、画素電極113が形成される。

【0176】

電極108の一部が充填されているコンタクトホールと、画素電極113の一部が充填されているコンタクトホールとは位置が同じである場合、1つの場所に収めることができると、効率的にレイアウトすることが出来る。そのため、画素の開口率を向上させることができる。

【0177】

一方、電極108の一部が充填されているコンタクトホールと、画素電極113の一部が充填されているコンタクトホールとは位置が互いに異なっていてもよい。このようにすることにより、電極108及び画素電極113のうち、コンタクトホール上に位置する部分が窪んでも、この窪みが重なることはない。このため、画素電極113に深く窪む部分が形成されず、上記したレジストのつきまわり不良が発生することを抑制できる。その後、レジストを除去する。

【0178】

次いで、第1配向膜112を形成し、カラーフィルタ122、第2配向膜123が形成された対向基板120との間に液晶116を封止する。その後、液晶116と接しない側の対向基板120や基板101に、偏光板126、124、位相差板（図示せず）、1/4板等の光学フィルム（図示せず）、拡散板やプリズムシート等の光学フィルム等を設ける。さらに、バックライトやフロントライトを設ける。バックライトとしては、直下型やサイドライト型を用いることが出来る。光源としては、冷陰極管やLED（発光ダイオード）を用いることができる。LEDとしては、白色LEDや、色ごとのLED（例えば、白、赤、青、緑、シアン、マゼンダ、イエローなど）の組み合わせて用いればよい。LEDを用いると、光の波長が鋭いため、色純度を上げることが出来る。サイドライト型の場合は、導光板を配置し、均一な面光源を実現する。このようにして、液晶表示装置が形成される。

【0179】

なお、液晶表示装置とは、基板と対向基板と、それに挟まれた液晶のみの部分を呼んでも良い。さらに、液晶表示装置とは、偏光板や位相差板などの光学フィルムを配置したものまで含む場合もあり、その他にも、拡散板やプリズムシートや光源（冷陰極管やLEDなど）や導光板などを含めてよい。

【0180】

また、本実施形態では、チャネル領域の上方にゲート電極を配置した、いわゆるトップゲート型の薄膜トランジスタについて説明をしたが、本発明は特にこれに限定されるものではない。チャネル領域の下方にゲート電極が配置された、いわゆるボトムゲート型の薄膜トランジスタにしてもよいし、チャネル領域の上下にゲート電極が配置された構造を有するトランジスタを形成してもよい。

【0181】

また本実施の形態では、ゲート電極が1つ形成される、いわゆるシングルゲートのTF

10

20

30

40

50

Tについて説明したが、ゲート電極が2つ以上形成される、いわゆるマルチゲート型TFTを形成してもよい。

【0182】

また、液晶表示装置は透過型であってもよいし、反射型の液晶表示装置であってもよい。反射型の液晶表示装置は、例えば導電膜115を光透過性の膜（例えば、インジウム錫酸化物（ITO）膜、インジウム亜鉛酸化物（IZO）、酸化亜鉛（ZnO）、若しくは不純物が導入された多結晶珪素膜又は非晶質珪素膜）により形成し、画素電極113を反射性のある導電膜、例えば金属膜により形成することにより実現できる。また、画素電極113を光透過性の膜により形成し、かつ導電膜115の一部を反射性のある導電膜、例えば金属膜により形成して残りを光透過性の膜により形成しても、半透過型の液晶表示装置を実現できる。 10

【0183】

また反射型の液晶表示装置においては、導電膜115を反射性のある導電膜、例えば金属膜にすることで、導電膜115に反射板の機能を持たせることができる。画素電極113と導電膜115を、両方とも反射性の導電膜を用いることも可能であるし、いずれか一方を反射性の導電膜にすることも可能である。また基板101と導電膜115の間に絶縁膜（例えば酸化珪素膜）を設け、この絶縁膜中に反射膜としての金属膜を形成することもできる。さらに、基板101の外側の面に、反射膜としての反射シート（例えばアルミニウム膜）を設けることもできる。なお、ここで述べた内容は、後述する各実施形態においても同様に適用できる。 20

【0184】

本実施の形態により、広い視野角を有しており、かつ従来と比べて製造コストが低い液晶表示装置を提供することができる。

【0185】

また本実施の形態では、導電膜を基板全面に形成するので、基板からの不純物が活性層に混入されるのを防ぐことができる。これにより信頼性の高い半導体装置を得ることが可能となる。

【0186】

また本実施の形態では、トップゲート型薄膜トランジスタを有する半導体装置を作製するため、バックゲートの電位が安定し、信頼性の高い半導体装置を得ることができる。 30

【0187】

[実施の形態2]

本実施の形態では、画素部のスイッチング素子として、ボトムゲート型TFTを作製した例を、図2を用いて説明する。

【0188】

基板201上に、導電膜202、下地膜203、ゲート電極204、ゲート絶縁膜213、活性層となる島状半導体膜206、ソース領域またはドレイン領域の一方である領域208a、ソース領域またはドレイン領域の他方である領域208b、ソース電極またはドレイン電極の一方である電極207a、ソース電極またはドレイン電極の他方である電極207a、画素電極209及び214（214a、214b、214c、等）が形成されている。ゲート電極204、ゲート絶縁膜213、島状半導体膜206、領域208a、領域208bにより、TFT212が構成されている。 40

【0189】

電極214と導電膜202との間で横方向電界225が発生する。これにより液晶分子が駆動される。

【0190】

また下地膜203上には、ゲート電極204と同じ材料、同じ工程で形成された電極205が配置されている。絶縁膜210上に形成され、電極209と同じ材料、同じ工程で形成された電極211が配置されている。電極211は、下地膜203、ゲート絶縁膜213、絶縁膜210に形成されたコンタクトホールを介して、導電膜202と電極205 50

に電気的に接続している。

【0191】

基板201は、基板101と同様の材料を用いればよい。

【0192】

導電膜202は、実施の形態1で述べた導電膜115と同様の導電膜を用いればよい。

【0193】

下地膜203は、下地膜102と同様の材料を用いて形成すればよい。

【0194】

ゲート電極204及び電極205は、ゲート電極105と同様の材料及び同様の工程を用いて形成すればよい。ゲート絶縁膜213は、ゲート絶縁膜104あるいは絶縁膜106と同様の材料で、基板201全面に形成する。

10

【0195】

なお本実施の形態では、ゲート電極が1つ形成される、いわゆるシングルゲートのTFTについて説明するが、ゲート電極が2つ以上形成される、いわゆるマルチゲート型TFTを形成してもよい。

【0196】

活性層である島状半導体膜206は、島状半導体膜103と同様の材料で形成すればよい。好ましくは、アモルファス半導体膜、マイクロクリスタル半導体膜（セミアモルファス半導体膜）が好ましい。その場合は、真性半導体膜（島状半導体膜206）を形成後、一導電性を付与する不純物を含む半導体膜を形成する。一導電型を付与する不純物は、例えばn型を付与する不純物であれば、リン（P）、ヒ素（As）等を用いればよく、p型を付与する不純物としては、ホウ素（B）を用いればよい。本実施の形態のボトムゲート型TFTはチャネルエッチ型を採用するので、島状半導体膜、ソース電極、ドレイン電極を形成後、チャネル形成領域の一部にエッチングが必要となる。

20

【0197】

次いでゲート絶縁膜213及び島状半導体膜206上に、導電膜を形成し、その後一導電性を付与する不純物を含む半導体膜の一部をエッチングして、領域208a及び208bを形成する。エッチングにより領域207a及び領域207bを形成する

【0198】

島状半導体膜206、領域208a、領域208b、電極207a、電極207b上には、絶縁膜210が形成される、絶縁膜210は、絶縁膜106あるいは絶縁膜111と同様の材料、同様の工程を用いて形成すればよい。ただし絶縁膜210として、有機材料を用いないと、画素電極214と導電膜202との間隔dを小さくすることができ、電界制御がしやすくなる。

30

【0199】

絶縁膜210上に、画素電極209及び214（214a、214b、214c、…）、電極211を形成する。画素電極209及び214は、画素電極113及び114と同様に、導電膜に溝が形成されたものである。

【0200】

電極211は、ゲート絶縁膜213及び絶縁膜210に形成されたコンタクトホールを介して、電極205に電気的に接続されている。かつ、下地膜203、ゲート絶縁膜213及び絶縁膜210に形成されたコンタクトホールを介して、導電膜202に電気的に接続されている。

40

【0201】

電極208、画素電極209及び214、電極211上には配向膜215が形成される。配向膜215は、配向膜112と同様の材料を用いて形成すればよい。

【0202】

対向基板221上には、カラーフィルタ222、配向膜223が形成されている。対向基板221、カラーフィルタ222、配向膜223は、それぞれ対向基板120、カラーフィルタ122、配向膜123と同様の材料を用いればよい。

50

## 【0203】

対向基板221上の配向膜223、及び基板201上の配向膜215を向かい合わせ、その空隙に液晶216を注入する。

## 【0204】

その後、液晶216と接しない側の対向基板221や基板201に、偏光板224、217、位相差板(図示せず)、 $\lambda/4$ 板等の光学フィルム(図示せず)、拡散板やプリズムシート等の光学フィルム等を設ける。さらに、バックライトやフロントライトを設ける。バックライトとしては、直下型やサイドライト型を用いることが出来る。光源としては、冷陰極管やLED(発光ダイオード)を用いることができる。LEDとしては、白色LEDや、色ごとのLED(例えば、白、赤、青、緑、シアン、マゼンダ、イエローなど)の組み合わせて用いればよい。LEDを用いると、光の波長が鋭いため、色純度を上げることが出来る。サイドライト型の場合は、導光板を配置し、均一な面光源を実現する。このようにして、液晶表示装置が形成される。

## 【0205】

また図26に、TFT212の活性層を、結晶性半導体膜で形成した例を示す。なお図26では、図2と同じものは同じ符号で示している。図26では、TFT212は結晶性島状半導体膜253を活性層として有しており、結晶性島状半導体膜253は、チャネル形成領域256、ソース領域またはドレイン領域の一方である領域258a、ソース領域またはドレイン領域の他方である領域258bを有している。

## 【0206】

また図26の電極211の代わりに、ソース電極またはドレイン電極の一方である電極207a及びソース電極またはドレイン電極の他方である電極207bと同じ材料、同じ工程で形成された電極251を用いる。

## 【0207】

なお本実施の形態は、実施の形態1のTFT121を、ボトムゲート型TFT212に変えただけであるので、その他の構成における作製材料や作製工程は、実施の形態1で述べたものを参照すればよい。

## 【0208】

本実施の形態により、広い視野角を有しており、かつ従来と比べて製造コストが低い液晶表示装置を提供することができる。

## 【0209】

本発明では、導電膜を基板全面に形成するので、基板からの不純物が活性層に混入されるのを防ぐことができる。これにより信頼性の高い液晶表示装置を得ることが可能となる。

## 【0210】

## [実施の形態3]

本実施の形態は、実施の形態1の電極108を形成せず、画素電極113を直接領域131bに接続されるように形成した例を、図6に示す。図6中の符号は実施の形態1のものを援用している。その他の構成における作製材料や作製工程は、実施の形態1で述べたものを参照すればよい。本実施の形態は、電極108を形成しないので、開口率が高くなるという利点がある。

## 【0211】

また必要であれば、実施の形態2で述べたボトムゲート型TFTを援用してもよい。

## 【0212】

本実施の形態により、広い視野角を有しており、かつ従来と比べて製造コストが低い液晶表示装置を提供することができる。

## 【0213】

本発明では、導電膜を基板全面に形成するので、基板からの不純物が活性層に混入されるのを防ぐことができる。これにより信頼性の高い液晶表示装置を得ることが可能となる。

10

20

30

40

50

**【0214】**

また本発明においては、トップゲート型薄膜トランジスタを有する液晶表示装置を作製した場合、バックゲートの電位が安定するので、信頼性の高い液晶表示装置を得ることができる。

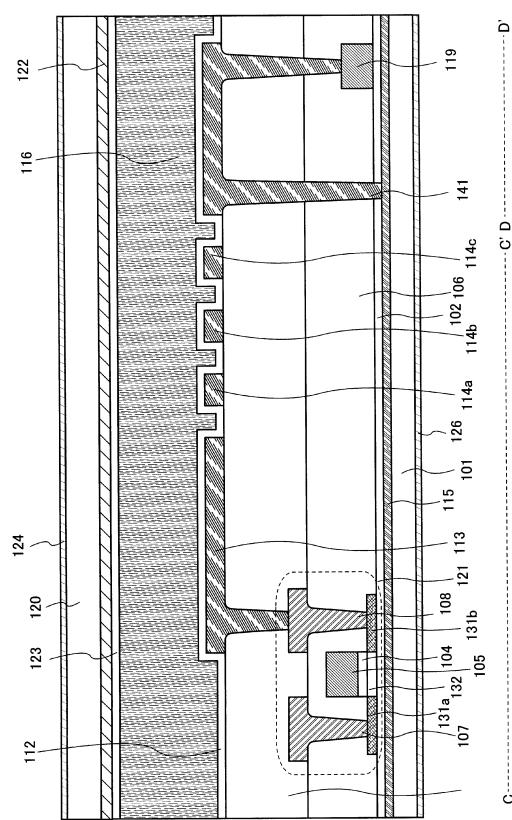

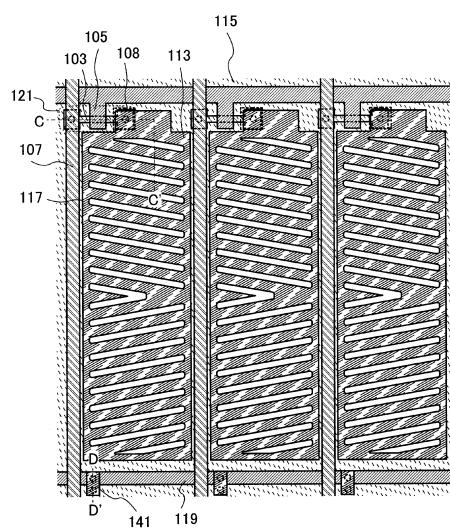

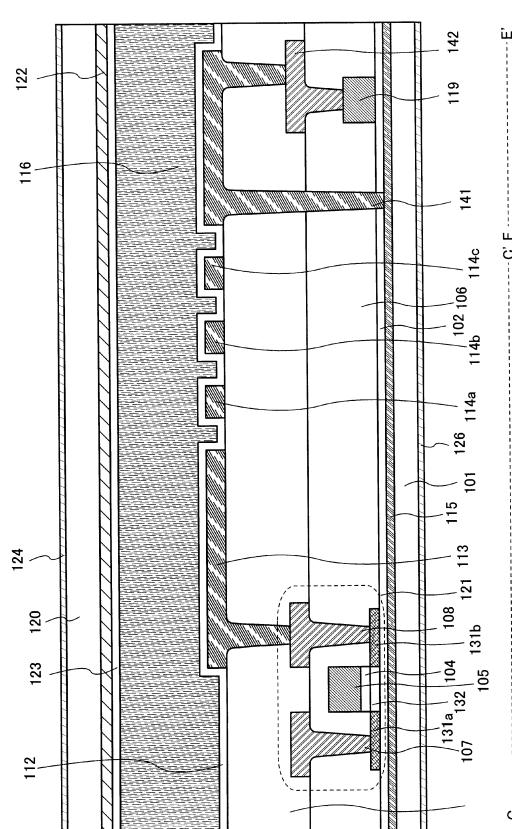

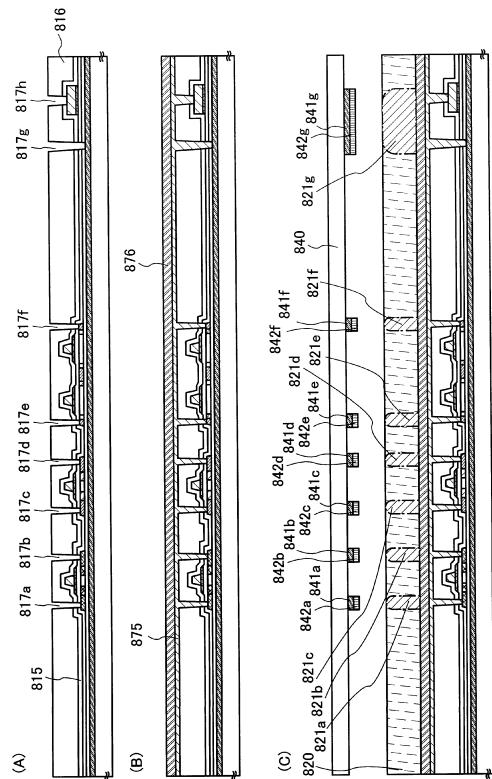

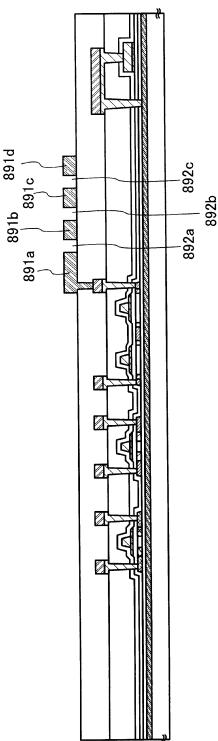

**【0215】****[実施の形態4]**

本実施の形態を、図10、図11、図12、図13を用いて説明する。図10、図11、図12、図13中の符号は実施の形態1のものを援用している。その他の構成における作製材料や作製工程は、実施の形態1で述べたものを参照すればよい。

**【0216】**

また必要であれば、実施の形態2で述べたボトムゲート型TFTを援用してもよい。

10

**【0217】**

さらに必要であれば、実施の形態3で述べた、画素電極を直接活性層に接続させる構成を用いてもよい。

**【0218】**

図10では、図6の接続電極109に代えて、画素電極113と同様の材料及び同様の工程で形成された電極141を用いる。配線119及び導電膜115は、電極141を介して電気的に接続されている。

**【0219】**

また図10の上面図を図11に示す。図11においても図4及び図10と同じものは同じ符号で示されている。図11中C-C'及びD-D'の断面図が図10である。

20

**【0220】**

また、図12では、図6の接続電極109に代えて、画素電極113と同様の材料及び同様の工程で形成された電極141、かつ、電極107及び電極108と同様の材料及び同様の工程で形成された電極142を用いる。配線119及び導電膜115は、電極141かつ電極142を介して電気的に接続されている。

**【0221】**

また図12の上面図を図13に示す。図13においても図4及び図12と同じものは同じ符号で示されている。図13中C-C'及びE-E'の断面図が図12である。

**【0222】**

30

本実施の形態により、広い視野角を有しており、かつ従来と比べて製造コストが低い液晶表示装置を提供することができる。

**【0223】**

本発明では、導電膜を基板全面に形成するので、基板からの不純物が活性層に混入されるのを防ぐことができる。これにより信頼性の高い液晶表示装置を得ることが可能となる。

**【0224】**

また本発明においては、トップゲート型薄膜トランジスタを有する液晶表示装置を作製した場合、バックゲートの電位が安定するので、信頼性の高い液晶表示装置を得ることができる。

40

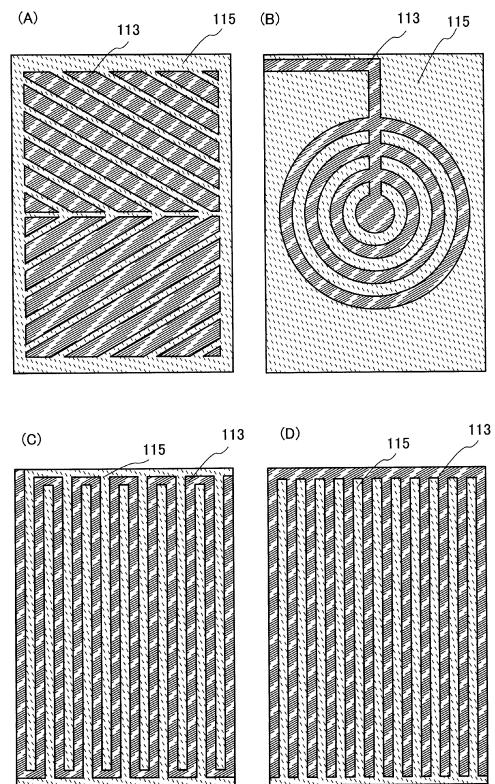

**【0225】****[実施の形態5]**

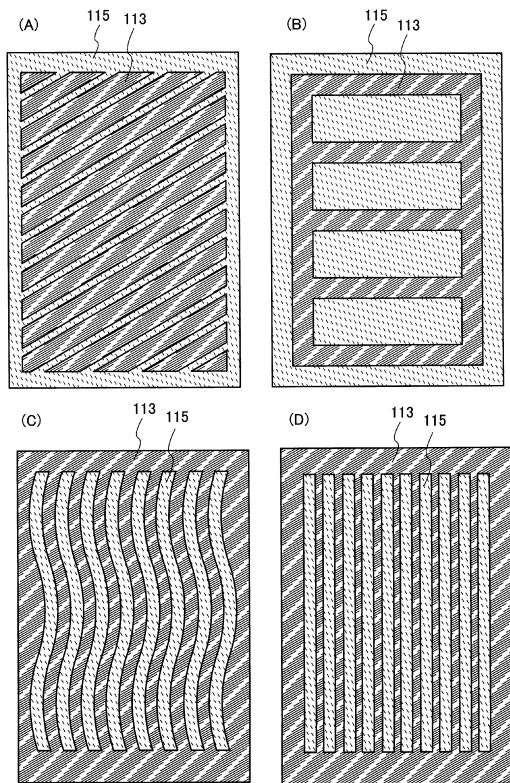

本実施の形態では、画素電極を様々な形状に形成した例を、図7、図8(A)～図8(D)、図9(A)～図9(D)に示す。図7、図8(A)～図8(D)、図9(A)～図9(D)中の符号は実施の形態1のものを援用している。その他の構成における作製材料や作製工程は、実施の形態1で述べたものを参照すればよい。

**【0226】**

また必要であれば、実施の形態2で述べたボトムゲート型TFTを援用してもよい。

**【0227】**

さらに必要であれば、実施の形態3で述べた、画素電極を直接活性層に接続させる構成

50

を用いてもよい。

【0228】

またさらに実施の形態4で述べた導電膜115と配線119の接続構造を用いてもよい。

。

【0229】

図7は画素電極113を櫛状に形成したものであり、図7における、A-A'及びB-B'の断面図は図3と同じである。また図8(A)~図8(B)では、図面の見やすさを考慮して、画素電極113と導電膜115のみを示している。

【0230】

図8(A)において画素電極113には、スリット状の開口がそれぞれ複数形成されている。スリット状の開口はソース配線に対して斜めである。かつ、画素電極113の上半分に形成されているスリット状の開口と、画素電極113の下半分に形成されているスリット状の開口は、画素電極113の中心線に対して互いの角度が異なる。画素電極113の上半分に形成されているスリット状の開口と、画素電極113の下半分に形成されているスリット状の開口は、中心線に対して線対称であってもよい。

10

【0231】

図8(B)において、画素電極113は、それが円周に沿う形状を有していて半径が異なる複数の電極を同心に配置し、これらを接続した形状である。そして、各電極の相互間のスペースが、開口の役割を果たしている。

【0232】

20

図8(C)において、画素電極113は、櫛歯状の2つの電極を、逆向きかつ櫛歯部分が互い違いになるように配置したものである。そして櫛歯部分の相互間に位置するスペースが開口の役割を果たしている。

【0233】

図8(D)において、画素電極113は櫛歯状の形状を有しており、櫛歯部分の相互間に位置するスペースが開口の役割を果たしている。

【0234】

図9(A)において、画素電極113は斜めの方向にストライプ状であり、ストライプ状部分の相互間に位置するスペースが開口の役割を果たしている。

30

【0235】

図9(B)において、画素電極113には矩形状の開口部が複数形成されている。

【0236】

図9(C)において、画素電極113中に、細長い長方形の互いに向かい合う二辺が波状である開口部が形成されている。

【0237】

図9(D)において、画素電極113中に、細長い長方形の開口部が形成されている。

。

【0238】

本発明により、広い視野角を有しており、かつ従来と比べて製造コストが低い液晶表示装置を提供することができる。

40

【0239】

本発明では、導電膜を基板全面に形成するので、基板からの不純物が活性層に混入されるのを防ぐことができる。これにより信頼性の高い液晶表示装置を得ることが可能となる。

。

【0240】

また本発明においては、トップゲート型薄膜トランジスタを有する液晶表示装置を作製した場合、バックゲートの電位が安定するので、信頼性の高い液晶表示装置を得ることができる。

【0241】

[実施の形態6]

50

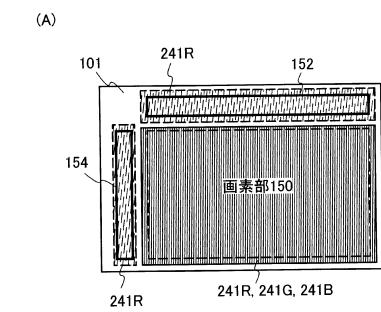

本実施の形態では、実施の形態1と異なる場所にカラーフィルタを設けた例について、図22、図23(A)～図23(B)、図24を用いて説明する。

【0242】

図22は、本実施の形態に係るFFS方式の液晶表示装置の画素部の構成を説明する為の断面図である。本実施の形態に係る液晶表示装置の画素部は、対向基板120側にカラーフィルタを配置せず、層間絶縁膜106の代わりにカラーフィルタ241(赤色のカラーフィルタ241R、青色のカラーフィルタ241B、及び緑色のカラーフィルタ241G)を配置した点を除いて、実施の形態1に示した液晶表示装置と同様の構成である。

【0243】

従って、実施の形態1以外の他の実施の形態で説明した内容は、本実施形態においても適用できる。以下、実施の形態1と同様の構成については同一の符号を付し、説明を省略する。

【0244】

なお、カラーフィルタ241とゲート電極105との間に、無機材料の絶縁膜を配置してもよい。無機材料としては、酸化珪素、窒化珪素、窒素を含む酸化珪素、酸素を含む窒化珪素など、酸素又は窒素を有する絶縁物質から形成される。不純物の侵入をブロックするためには、窒素を多く含む材料にすることが望ましい。また、カラーフィルタ241上に、平坦化膜を形成してもよい。

【0245】

なお、カラーフィルタ241の色は、赤、青、緑以外の色でも良いし、3色よりも多く、例えば、4色や6色でもよい。例えば、イエローやシアンやマゼンダや白が追加されてよい。また、カラーフィルタだけでなく、ブラックマトリックスも配置してもよい。さらに、ブラックマトリックスは、樹脂材料で形成しても、金属膜で形成しても構わない。さらにブラックマトリックスは、カーボンブラックを用いて形成しても構わない。

【0246】

このように、基板101上にカラーフィルタ241を配置することにより、対向基板120との位置合わせを正確にやる必要がないため、容易に製造することが可能となり、コストが低減し、製造歩留まりが向上する。

【0247】

本実施の形態に係る液晶表示装置の製造方法は、層間絶縁膜106を形成する工程の代わりにカラーフィルタ241(241R、241G、241B)を形成する工程が入る点を除いて、実施の形態1に係る液晶表示装置の製造方法と同様である。

【0248】

カラーフィルタ241R、241G、241Bは、カラーフィルタ層を形成する工程、カラーフィルタ層上にレジストを形成する工程、及びレジストをマスクとしてカラーフィルタ層を選択的にドライエッチングする工程を3回繰り返すことにより形成される。

【0249】

または、レジストを用いずに、感光性の材料や顔料などを用いて形成される。なお、カラーフィルタ層相互間にスペースが生じるが、このスペースには層間絶縁膜111が埋め込まれる。あるいは、さらに無機材料や有機材料が、積層される。あるいは、ブラックマトリックスなどが積層される。また、カラーフィルタ241R、241G、241Bやブラックマトリックスは液滴吐出法(例えばインクジェット法)を用いても形成することができる。

【0250】

このため、液晶表示装置の製造工程数を減らすことができる。また、基板101側にカラーフィルタを設けているため、対向基板120にカラーフィルタを設ける場合と比較して、対向基板120との間に位置ずれが生じても開口率が低下することを抑制できる。すなわち対向基板120の位置ずれに対するマージンが大きくなる。

【0251】

図23(A)は、図22に示した液晶表示装置の平面図である。図23(A)に示すよ

10

20

30

40

50

うに、本実施の形態の液晶表示装置は、画素部 150 の周囲に、周辺駆動回路であるソース線駆動回路 152 及びゲート線駆動回路 154 が設けられている。

【0252】

ソース線駆動回路 152 及びゲート線駆動回路 154 それぞれ上には、赤色のカラーフィルタ 241R が設けられていてもよい。カラーフィルタ 241R が設けられることにより、ソース線駆動回路 152 及びゲート線駆動回路 154 が有する薄膜トランジスタの活性層の光劣化が防止され、かつ平坦化が図られている。

【0253】

図 23 (B) は、図 23 (A) の画素部 150 の一部 (3 × 3 行列) を拡大した図である。画素部 150 には、赤色のカラーフィルタ 241R、青色のカラーフィルタ 241B 10 及び緑色のカラーフィルタ 241G がストライプ状に交互に配置されている。また、各画素が有する薄膜トランジスタ上には赤色のカラーフィルタ 241R が配置されている。

【0254】

また、ソース配線 (図示せず) 及びゲート配線 (図示せず) は、各カラーフィルタの相互間のスペースと重なるように配置されているため、光漏れが生じることが抑制される。

【0255】

このようにカラーフィルタ 241R はブラックマトリックスの役割を果たすため、従来必要であったブラックマトリックスの形成工程を省略することも可能である。

【0256】

以上、本実施の形態によれば、他の実施の形態と同様の効果を得ることができる。また、層間絶縁膜 106 の代わりにカラーフィルタ 241R、241G、241B を設けたため、液晶表示装置の製造工程数を減らすことができる。また、対向基板 120 にカラーフィルタを設ける場合と比較して、対向基板 120 との間に位置ずれが生じても、開口率の低下が抑制できる。すなわち対向基板 120 の位置ずれに対するマージンが大きくなる。

【0257】

また、カラーフィルタだけでなく、ブラックマトリックスも配置してもよい。

【0258】

なお、他の実施の形態で示した FFS 方式の液晶表示装置において、本実施の形態と同様に、層間絶縁膜 106 や、あるいは第 2 層間絶縁膜 111 の代わりに (図 24 参照)、カラーフィルタ 241 (241R、241G、241B) を設けてもよい。この場合においても、本実施の形態と同様の効果を得ることができる。

【0259】

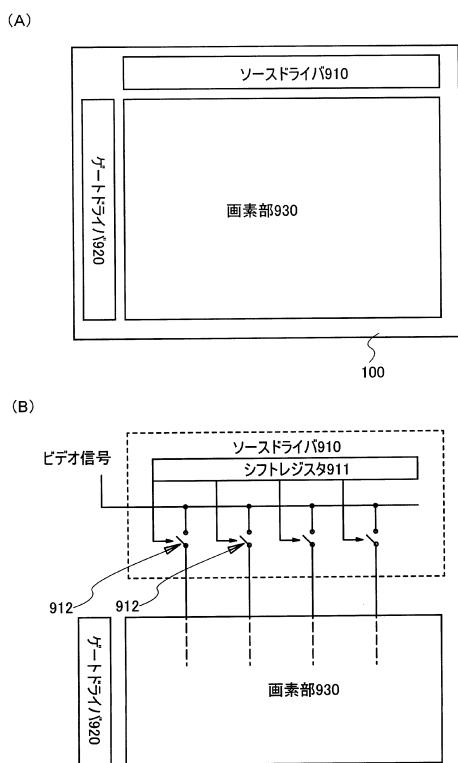

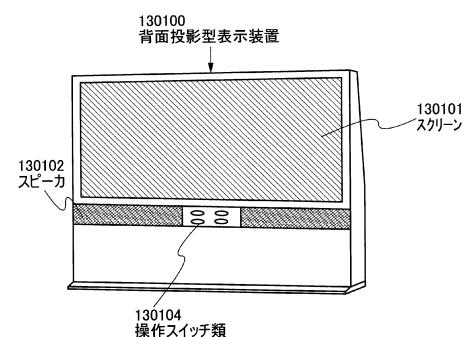

[実施の形態 7]

本実施形態においては、表示装置の表示パネル構成、および周辺構成について説明する。特に、液晶表示装置の表示パネル (液晶パネルとも記す) 構成、および周辺構成について説明する。

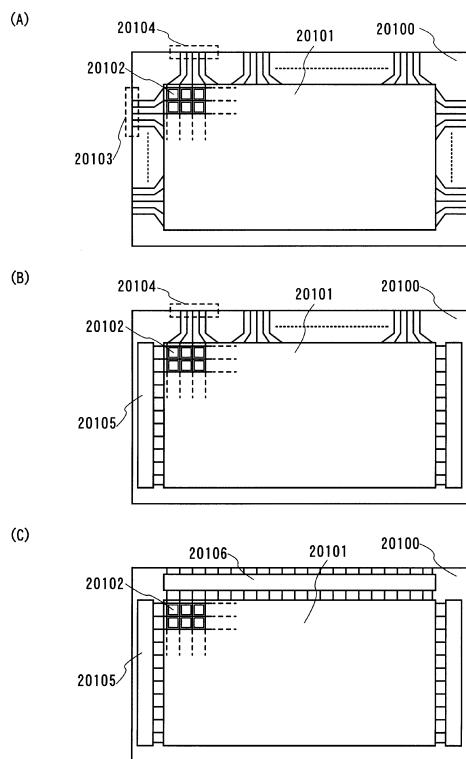

【0260】

まず、液晶パネルの簡単な構成について、図 29 (A) を参照して説明する。また、図 29 (A) は、液晶パネルの上面図である。

【0261】

図 29 (A) に示す液晶パネルは、基板 20100 上に、画素部 20101、走査線側入力端子 20103 及び信号線側入力端子 20104 が形成されている。走査線側入力端子 20103 から走査線が行方向に延在して基板 20100 上に形成され、信号線側入力端子 20104 から信号線が列方向に延在して基板 20100 上に形成されている。また、画素部 20101 には、画素 20102 が走査線と、信号線とが交差するところで、マトリックス上に配置されている。また、画素 20102 には、スイッチング素子と画素電極層とが配置されている。

【0262】

図 29 (A) の液晶パネルに示すように、走査線側入力端子 20103 は、基板 20100 の行方向の両側に形成されている。信号線側入力端子 20103 は、基板 20100 の

10

20

30

40

50

列方向のうち一方に形成されている。また、一方の走査線側入力端子 20103 から延在する走査線と、他方の走査線側入力端子 20103 から延在する走査線とは、交互に形成されている。

【0263】

また、画素部 20101 の画素 20102 それでは、スイッチング素子の第 1 端子が信号線に接続され、第 2 端子が画素電極層に接続されることによって、個々の画素 20102 を外部から入力する信号によって独立して制御することができる。なお、スイッチング素子のオン・オフは走査線に供給されている信号によって制御されている。

【0264】

なお、走査線側入力端子 20103 を基板 20100 の行方向のうち両方に配置することで、画素 20102 を高密度に配置することができる。また、信号線側入力端子 20103 を基板 20100 の列方向のうち一方に配置することで、液晶パネルの狭額縁化、又は画素 20101 の領域の拡大を図ることができる。 10

【0265】

なお、基板 20100 には、すでに述べたように、単結晶基板、SOI 基板、ガラス基板、石英基板、プラスチック基板、紙基板、セロファン基板、石材基板、ステンレス・スチール基板、ステンレス・スチール・ホイルを有する基板などを用いることができる。

【0266】

なお、スイッチング素子には、すでに述べたように、トランジスタ、ダイオード（例えば、PNダイオード、PINダイオード、ショットキーダイオード、ダイオード接続のトランジスタなど）、サイリスタ、それらを組み合わせた論理回路などを用いることができる。 20

【0267】

なお、スイッチング素子として、TFT を用いた場合、TFT のゲートが走査線に接続され、第 1 端子が信号線に接続され、第 2 端子が画素電極層に接続されることにより、個々の画素 20102 を外部から入力する信号によって独立して制御することができる。

【0268】

なお、走査線側入力端子 20103 を基板 20100 の行方向のうち一方に配置してもよい。走査線側入力端子 20103 を基板 20100 の行方向のうち一方に配置することで、液晶パネルの狭額縁化、画素 20101 の領域の拡大を図ることができる。 30

【0269】

なお、一方の走査線側入力端子 20103 から延在する走査線と、他方の走査線側入力端子 20103 から延在する走査線とは、共通にしてもよい。

【0270】

なお、信号線側入力端子 20103 を基板 20100 の列方向のうち両方に配置してもよい。信号線側入力端子 20103 を基板 20100 の列方向のうち両方に配置することで、画素 20102 を高密度に配置できる。

【0271】

なお、画素 20102 には、さらに容量素子を形成してもよい。画素 20102 に容量素子を設ける場合、基板 20100 上に、容量線を形成してもよい。基板 20100 上に容量線を形成する場合、容量素子の第 1 電極が容量線に接続され、第 2 端子が画素電極層に接続されるようにする。また、基板 20100 上に容量線を形成しない場合、容量素子の第 1 電極がこの容量素子が配置されている画素 20102 とは別の走査線に接続され、第 2 端子が画素電極層に接続されているようにする。 40

【0272】

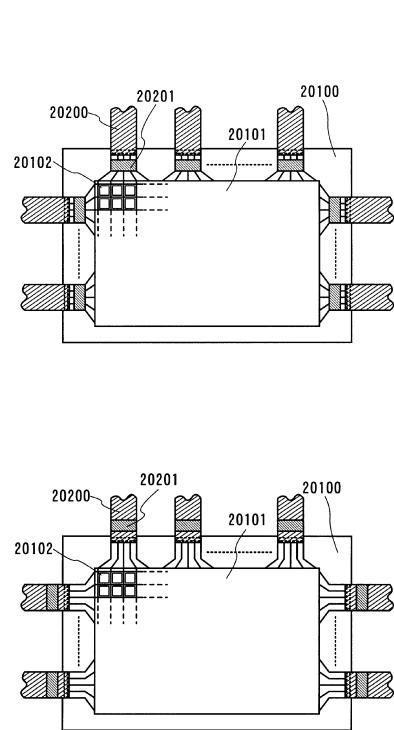

ここで、図 29 (A) に示した液晶パネルは、走査線及び信号線に供給する信号を外付けの駆動回路によって制御する構成を示しているが、図 30 (A) に示すように、COG (Chip on Glass) 方式によりドライバIC 20201 を基板 20100 上に実装してもよい。また、別の構成として、図 30 (B) に示すように、TAB (Tap e Automated Bonding) 方式によりドライバIC 20201 を FPC 50

(Flexible Printed Circuit) 20200 上に実装してもよい。また、図 30において、ドライバ I C 20201 は、FPC 20200 と接続されている。

【0273】

なお、ドライバ I C 20201 は単結晶半導体基板上に形成されたものでもよいし、ガラス基板上に TFT で回路を形成したものでもよい。

【0274】

なお、図 29 (A) に示した液晶パネルは、図 29 (B) に示すように、走査線駆動回路 20105 を基板 20100 上に形成してもよい。また、図 29 (C) に示すように、走査線駆動回路 20105 及び信号線駆動回路 20106 を基板 20100 上に形成してもよい。

10

【0275】

なお、走査線駆動回路 20105 及び走査線駆動回路 20106 は、多数の N チャネル型及び多数の P チャネル型のトランジスタから構成されている。ただし、多数の N チャネル型のトランジスタのみで構成されていてもよいし、多数の P チャネル型のトランジスタのみで構成されていてもよい。

【0276】

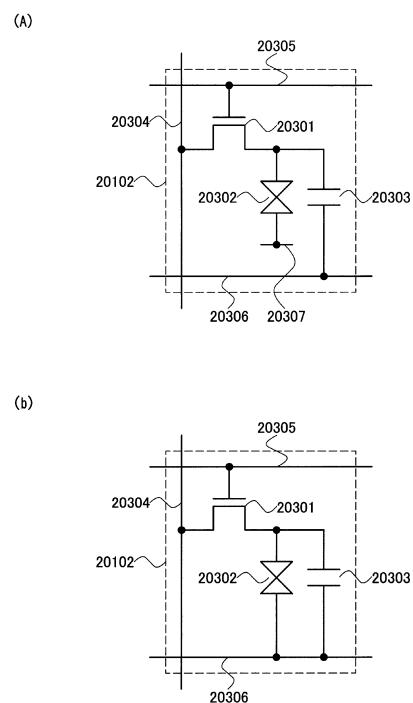

続いて、画素 20102 の詳細について、図 31 及び図 32 の回路図を参照して説明する。

【0277】

20

図 31 (A) の画素 20102 は、トランジスタ 20301、液晶素子 20302 及び容量素子 20303 を有している。トランジスタ 20301 のゲートが配線 20305 に接続され、第 1 端子が配線 20304 に接続されている。液晶素子 20302 の第 1 電極が対向電極 20307 に接続され、第 2 電極がトランジスタ 20301 の第 2 端子に接続されている。容量素子 20303 の第 1 電極が配線 20306 に接続され、第 2 電極がトランジスタ 20301 の第 2 端子に接続されている。

【0278】

なお、配線 20304 は信号線であり、配線 20305 は走査線であり、配線 20306 は容量線である。また、トランジスタ 20301 は、スイッチングトランジスタであり、P チャネル型トランジスタでも N チャネル型トランジスタでもよい。また、液晶素子 20307 は、動作モードとして TN (Twisted Nematic) モード、IPS (In-Plane-Switching) モード、FFS (Fringe Field Switching) モード、MVA (Multi-domain Vertical Alignment) モード、PVA (Patterned Vertical Alignment)、ASM (Axially Symmetric aligned Micro-cell) モード、OCB (Optical Compensated Birefringence) モード、FLC (Ferroelectric Liquid Crystal) モード、AFLC (AntiFerroelectric Liquid Crystal) などを用いることができる。

30

【0279】

40

配線 20304 及び配線 20305 には、それぞれビデオ信号、走査信号が入力されている。ビデオ信号はアナログの電圧信号であり、走査信号は H レベル又は L レベルのデジタルの電圧信号である。ただし、ビデオ信号は電流信号でもよいし、デジタル信号でもよい。また、走査信号の H レベル及び L レベルは、トランジスタ 20301 のオン・オフを制御できる電位であればよい。

【0280】

容量線 20306 には、一定の電源電圧が供給されている。ただし、パルス状の信号が供給されていてもよい。

【0281】

図 31 (A) の画素 20102 の動作について説明する。まず、配線 20305 が H レ

50

ベルになると、トランジスタ 20301 がオンし、ビデオ信号が配線 20304 からオンしたトランジスタ 20301 を介して液晶素子 20302 の第 2 電極及び容量素子 20303 の第 2 電極に供給される。そして、容量素子 20303 は配線 203076 の電位とビデオ信号の電位との電位差を保持する。

【0282】

次に、配線 20305 が L レベルになると、トランジスタ 20301 がオフし、配線 20304 と、液晶素子 20302 の第 2 電極及び容量素子 20303 の第 2 電極とは、電気的に遮断される。しかし、容量素子 20303 が配線 203076 の電位とビデオ信号の電位との電位差を保持しているため、容量素子 20302 の第 2 電極の電位はビデオ信号と同様な電位を維持することができる。

10

【0283】

こうして、図 31 (A) の画素 20102 は、液晶素子 20302 の第 2 電極の電位をビデオ信号と同電位に維持でき、液晶素子 20302 をビデオ信号に応じた透過率に維持できる。

【0284】

なお、図示はしないが、液晶素子 20302 がビデオ信号を保持できるだけの容量成分を有していれば、容量素子 20303 は必ずしも必要ではない。

【0285】

なお、図 31 (B) のように、液晶素子 20302 の第 1 電極は、配線 20306 と接続されていてもよい。例えば、液晶素子 20302 の液晶モードが FFS モードのときなどに、液晶素子 20302 は図 31 (B) の構成を用いる。

20

【0286】

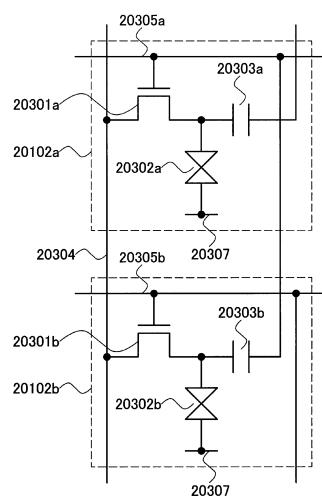

なお、図 32 のように、容量素子 20303 の第 1 電極は前行の配線 20305a に接続されていてもよい。なお、配線 20305a を n 行目 (n は正の整数) の走査線としたとき、配線 20305b は n + 1 行目の走査線である。同様に、トランジスタ 20301a、画素 20102a、容量素子 20303a を n 行目の素子としたとき、トランジスタ 20301b、画素 20102b、容量素子 20303b は n + 1 行目の素子である。このように、容量素子 20303b の第 1 電極が前列の配線 20305a に接続されることで、配線を少なくすることができる。よって、図 32 の画素 20102a および 20102b は、開口率を大きくすることができる。

30

【0287】

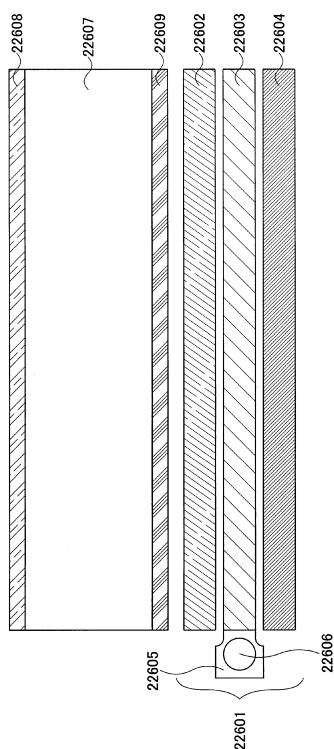

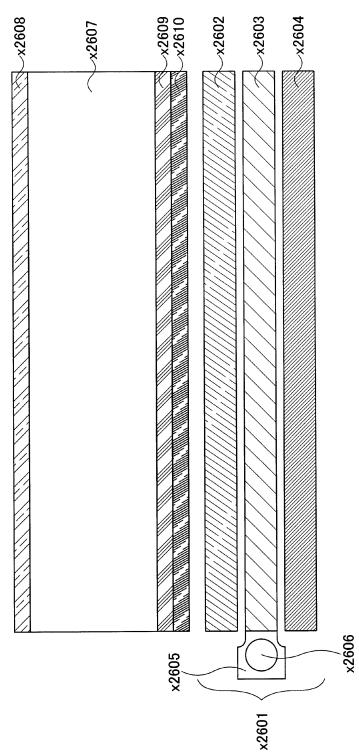

次に、図 33 に示した液晶表示装置には、バックライトユニット 22601、液晶パネル 22607、第 1 の偏光子を含む層 22608、第 2 の偏光子を含む層 22609 が設けられている。

【0288】

なお、液晶パネル 22607 は、本実施形態で説明したものと同様なものとすることができます。また、本実施形態の液晶パネルは、各画素にスイッチング素子が設けられたアクティブ型の構造について説明してきたが、図 33 の液晶パネルはパッシブ型の構造でもよい。

【0289】

40

バックライトユニット 22601 の構造について説明する。バックライトユニット 22601 は、拡散板 22602、導光板 22603、反射板 22604、ランプリフレクタ 22605、光源 22606 を有するように構成されている。光源 22606 としては冷陰極管、熱陰極管、発光ダイオード、無機 EL 又は有機 EL などが用いられ、光源 22606 は必要に応じて発光する機能を有する。ランプリフレクタ 22605 は、光源 22606 からの蛍光を効率よく導光板 22603 に導く機能を有する。導光板 22603 は、蛍光を全反射させて、全面に光を導く機能を有する。拡散板 22602 は、明度のムラを低減する機能を有する。反射板 22604 は、導光板 22603 から下方向 (液晶パネル 22607 と反対方向) に漏れた光を反射して再利用する機能を有する。

【0290】

50

なお、拡散板 22602 と第 2 の偏光子を含む層 22609との間に、プリズムシートを配置することで、本実施形態の液晶表示装置は液晶パネルの画面の明るさを向上させることができる。

【0291】

バックライトユニット 22601 には、光源 22606 の輝度を調整するための制御回路が接続されている。制御回路からの信号供給によって、光源 22606 の輝度を調整することができる。

【0292】

液晶パネル 22607 とバックライトユニット 22601との間には第 2 の偏光子を含む層 22609 が設けれ、バックライトユニット 22601 とは反対方向の液晶パネル 22607 にも第 1 の偏光子を含む層 22608 が設けられている。

10

【0293】

なお、第 1 の偏光子を含む層 22608 と第 2 の偏光子を含む層 22609 とは、液晶パネル 22607 の液晶素子が TN モードで駆動する場合、クロスニコルになるように配置される。また、第 1 の偏光子を含む層 22608 と第 2 の偏光子を含む層 22609 とは、液晶パネル 22607 の液晶素子が VA モードで駆動する場合、クロスニコルになるように配置される。また、第 1 の偏光子を含む層 22608 と第 2 の偏光子を含む層 22609 とは、液晶パネル 22607 の液晶素子が IPS モード及び FFS モードで駆動する場合、クロスニコルになるように配置されていてもよいし、パラレルニコルになるように配置されていてもよい。

20

【0294】

第 1 の偏光子を含む層 22608 及び第 2 の偏光子を含む層 22609 の両方又は一方と、液晶パネル 22607 との間に位相差板を有していてもよい。

【0295】

なお、図 36 に示すように、第 2 の偏光子を含む層 22609 とバックライトユニット 22601との間に、スリット(格子) 22610 を配置することで、本実施形態の液晶表示装置は 3 次元表示を行うことができる。

【0296】

バックライトユニット側に配置された開口部を有するスリット 22610 は、光源より入射された光をストライプ状にして透過し、表示装置へ入射させる。このスリット 22610 によって、視認側にいる視認者の両目に視差を作ることができ、視認者は右目では右目用の画素だけを、左目では左目用の画素だけを同時に見ることになる。よって、視認者は、3 次元表示を見ることができる。つまり、スリット 22610 によって特定の視野角を与えられた光が右目用画像及び左目用画像のそれぞれに対応する画素を通過することで、右目用画像と左目用画像とが異なる視野角に分離され、3 次元表示が行われる。

30

【0297】

図 36 の液晶表示装置を用いて、テレビジョン装置、携帯電話などの電子機器を作製すれば、3 次元表示を行うことができる高機能でかつ高画質の電子機器を提供することができる。

【0298】

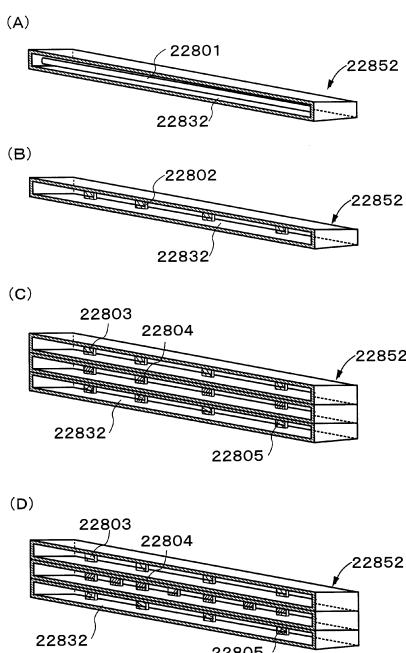

続いて、バックライトの詳細な構成について、図 35 を参照して説明する。バックライトは光源を有するバックライトユニットとして液晶表示装置に設けられ、バックライトユニットは効率よく光を散乱させるため、光源は反射板により囲まれている。

40

【0299】

図 35 (A) に示すように、バックライトユニット 22852 は、光源として冷陰極管 22801 を用いることができる。また、冷陰極管 22801 からの光を効率よく反射させるため、ランプリフレクタ 22832 を設けることができる。冷陰極管 22801 は、大型表示装置に用いることが多い。これは冷陰極管からの輝度の強度のためである。そのため、冷陰極管を有するバックライトユニットは、パーソナルコンピュータのディスプレイに用いることができる。

50

## 【0300】

図35(B)に示すように、バックライトユニット22852は、光源として発光ダイオード(LED)22802を用いることができる。例えば、白色に発する発光ダイオード(W)22802を所定の間隔に配置する。また、発光ダイオード(W)22802からの光を効率よく反射させるため、ランプリフレクタ22832を設けることができる。

## 【0301】

また図35(C)に示すように、バックライトユニット22852は、光源として各色RGBの発光ダイオード(LED)22803、22804、22805を用いることができる。各色RGBの発光ダイオード(LED)22803、22804、22805を用いることにより、白色を発する発光ダイオード(W)22802のみと比較して、色再現性を高くすることができる。また、発光ダイオードからの光を効率よく反射させるため、ランプリフレクタ22832を設けることができる。

10

## 【0302】

またさらに図35(D)に示すように、光源として各色RGBの発光ダイオード(LED)22803、22804、22805を用いる場合、それらの数や配置を同じとする必要はない。例えば、発光強度の低い色(例えば緑)を複数配置してもよい。

## 【0303】

さらに白色を発する発光ダイオード22802と、各色RGBの発光ダイオード(LED)22803、22804、22805とを組み合わせて用いてもよい。

20

なお、RGBの発光ダイオードを有する場合、フィールドシーケンシャルモードを適用すると、時間に応じてRGBの発光ダイオードを順次点灯させることによりカラー表示を行うことができる。

## 【0304】

発光ダイオードを用いると、輝度が高いため、大型表示装置に適する。また、RGB各色の色純度が良いため冷陰極管と比べて色再現性に優れており、配置面積を小さくすることができるため、小型表示装置に適応すると、狭額縁化を図ることができる。

30

## 【0305】

また、光源を必ずしも図35に示すバックライトユニットとして配置する必要はない。例えば、大型表示装置に発光ダイオードを有するバックライトを搭載する場合、発光ダイオードは該基板の背面に配置することができる。このとき発光ダイオードは、所定の間隔を維持し、各色の発光ダイオードを順に配置させることができる。発光ダイオードの配置により、色再現性を高めることができる。

## 【0306】

また、光源を必ずしも図35に示すバックライトユニットとして配置する必要はない。例えば、大型表示装置に発光ダイオードを有するバックライトを搭載する場合、発光ダイオードは該基板の背面に配置することができる。このとき発光ダイオードは、所定の間隔を維持し、各色の発光ダイオードを順に配置させることができる。発光ダイオードの配置により、色再現性を高めることができる。

40

## 【0307】

続いて、偏光子を含む層(偏光板又は偏光フィルムともいう)の一例について、図37を参照して説明する。

## 【0308】

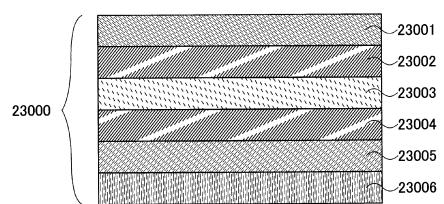

図37の偏光子を含む層23000は、保護フィルム23001、基板フィルム23002、PVA偏光フィルム23003、基板フィルム23004、粘着剤層23005及び離型フィルム23006を有するように構成されている。

40

## 【0309】

PVA偏光フィルム23003は、ある振動方向だけの光(直線偏光)を作り出す機能を有する。具体的には、PVA偏光フィルム23003は、電子の密度が縦と横で大きく異なる分子(偏光子)を含んでいる。PVA偏光フィルム23003は、この電子の密度が縦と横で大きく異なる分子の方向を揃えることで、直線偏光を作り出すことができる。

## 【0310】

一例として、PVA偏光フィルム23003は、ポリビニールアルコール(Polyvinyl Alcohol)の高分子フィルムに、ヨウ素化合物をドープし、PVAフィルムをある方向に引っ張ることで、一定方向にヨウ素分子の並んだフィルムを得ることができる。そして、ヨウ素分子の長軸と平行な光は、ヨウ素分子に吸収される。また、高

50

耐久用途及び高耐熱用途として、ヨウ素の代わりに2色性の染料が用いてもよい。なお、染料は、車載用LCDやプロジェクタ用LCDなどの耐久性、耐熱性が求められる液晶表示装置に用いられることが望ましい。

【0311】

PVA偏光フィルム23003は、両側を基材となるフィルム（基板フィルム23002及び基板フィルム3604）で挟むことで、信頼性を増すことができる。また、PVA偏光フィルム23003は、高透明性、高耐久性のトリアセチルロース（TAC）フィルムによって挟まれていてもよい。なお、基板フィルム及びTACフィルムは、PVA偏光フィルム23003が有する偏光子の保護層として機能する。

【0312】

一方の基板フィルム（基板フィルム23004）には、液晶パネルのガラス基板に貼るための粘着剤層23005が貼られている。なお、粘着剤層23005は、粘着剤を片側の基板フィルム（基板フィルム23004）に塗布することで形成される。また、粘着剤層23005には、離形フィルム23005（セパレートフィルム）が備えられている。

【0313】

他方の基板フィルム（基板フィルム23002）には、保護フィルムが備えられている。

【0314】

なお、偏光フィルム23000表面に、ハードコート散乱層（アンチグレア層）が備えられていてもよい。ハードコート散乱層は、AG処理によって表面に微細な凹凸が形成されており、外光を散乱させる防眩機能を有するため、液晶パネルへの外光の映り込みや表面反射を防ぐことができる。

【0315】

また、偏光フィルム23000表面に、複数の屈折率の異なる光学薄膜層を多層化（アンチリフレクション処理、若しくはAR処理ともいう）してもよい。多層化された複数の屈折率のことなる光学薄膜層は、光の干渉効果によって表面の反射率を低減することができる。

【0316】

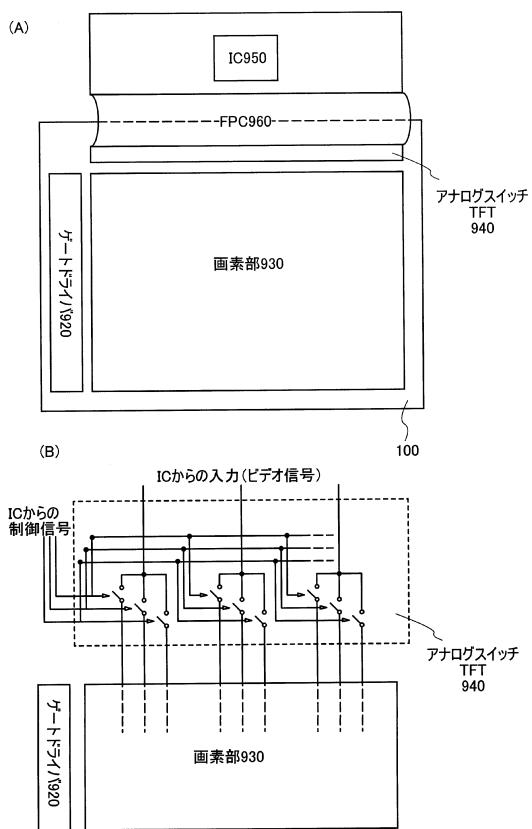

続いて、液晶表示装置が有する各回路の動作について、図34を参照して説明する。

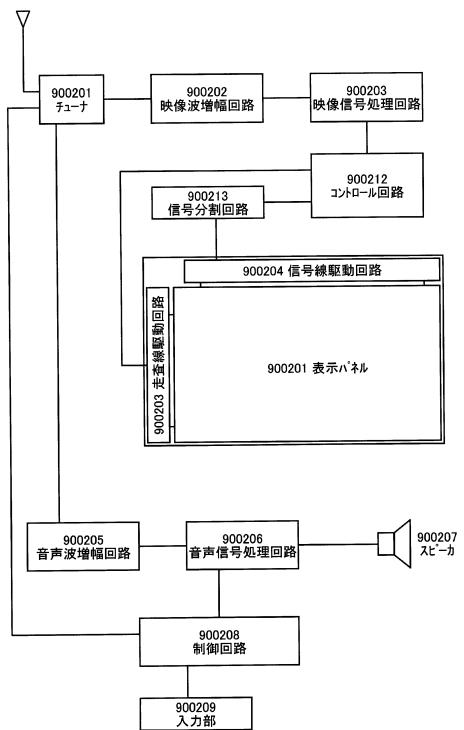

【0317】

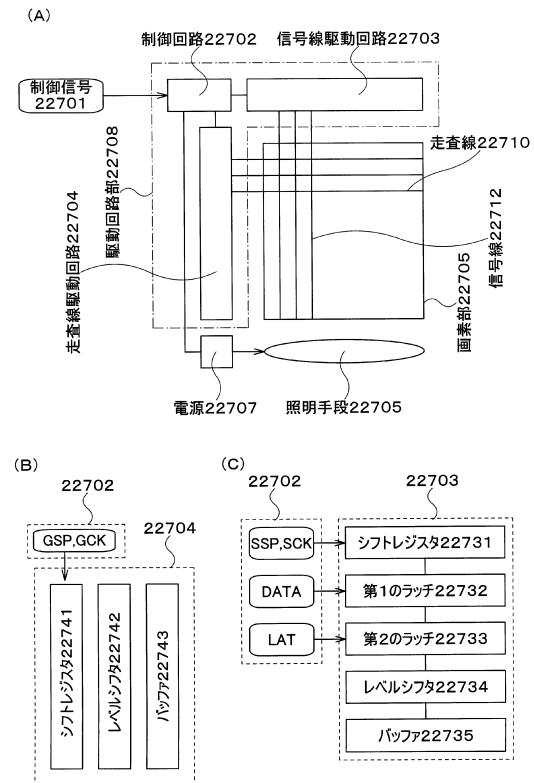

図34には、表示装置の画素部22705及び駆動回路部22708のシステムプロック図を示す。

【0318】

画素部22705は、複数の画素を有し、各画素となる信号線22712と、走査線22710との交差領域には、スイッチング素子が設けられている。スイッチング素子により液晶分子の傾きを制御するための電圧の印加を制御することができる。このように各交差領域にスイッチング素子が設けられた構造をアクティブ型と呼ぶ。本実施の形態の表示装置の画素部は、このようなアクティブ型に限定されず、パッシブ型の構成を有してもよい。パッシブ型は、各画素にスイッチング素子がないため、工程が簡便である。

【0319】

駆動回路部22708は、制御回路22702、信号線駆動回路22703、走査線駆動回路22704を有する。映像信号22701が入力される制御回路22702は、画素部22705の表示内容に応じて、階調制御を行う機能を有する。そのため、制御回路22702は、生成された信号を信号線駆動回路22703及び走査線駆動回路22704に入力する。そして、走査線駆動回路22704に基づき、走査線22710を介してスイッチング素子が選択されると、選択された交差領域の画素電極に電圧が印加される。この電圧の値は、信号線駆動回路22703から信号線を介して入力される信号に基づき決定される。

【0320】

さらに、制御回路22702では、照明手段22706へ供給する電力を制御する信号

10

20

30

40

50

が生成され、該信号は、照明手段 22706 の電源 22707 に入力される。照明手段には、上記実施の形態で示したバックライトユニットを用いることができる。なお照明手段はバックライト以外にフロントライトもある。フロントライトとは、画素部の前面側に取りつけ、全体を照らす発光体および導光体で構成された板状のライトユニットである。このような照明手段により、低消費電力で、均等に画素部を照らすことができる。

【0321】

図34(B)に示すように走査線駆動回路 22704 は、シフトレジスタ 22741、レベルシフタ 22742、バッファ 22743 として機能する回路を有する。シフトレジスタ 22741 にはゲートスタートパルス (GSP)、ゲートクロック信号 (GCK) 等の信号が入力される。なお、本実施の形態の表示装置の走査線駆動回路は、図34(B) 10 に示す構成に限定されない。

【0322】

また図34(C)に示すように信号線駆動回路 22703 は、シフトレジスタ 22731、第1のラッチ 22732、第2のラッチ 22733、レベルシフタ 22734、バッファ 22735 として機能する回路を有する。バッファ 22735 として機能する回路とは、弱い信号を増幅させる機能を有する回路であり、オペアンプ等を有する。レベルシフタ 22734 には、スタートパルス (SSP) 等の信号が、第1のラッチ 22732 にはビデオ信号等のデータ (DATA) が入力される。第2のラッチ 22733 にはラッチ (LAT) 信号を一時保持することができ、一斉に画素部 22705 へ入力させる。これを線順次駆動と呼ぶ。そのため、線順次駆動ではなく、点順次駆動を行う画素であれば、第2のラッチは不要とすることができます。このように、本実施の形態の表示装置の信号線駆動回路は図34(C)に示す構成に限定されない。 20

【0323】

このような信号線駆動回路 22703、走査線駆動回路 22704、画素部 22705 は、同一基板状に設けられた半導体素子によって形成することができる。半導体素子は、ガラス基板に設けられた薄膜トランジスタを用いて形成することができる。この場合、半導体素子には結晶性半導体膜を適用するとよい。結晶性半導体膜は、電気特性、特に移動度が高いため、駆動回路部が有する回路を構成することができる。また、信号線駆動回路 22703 や走査線駆動回路 22704 は、IC (Integrated Circuit) チップを用いて、基板上に実装することもできる。この場合、画素部の半導体素子には非晶質半導体膜を適用することができる。 30

【0324】

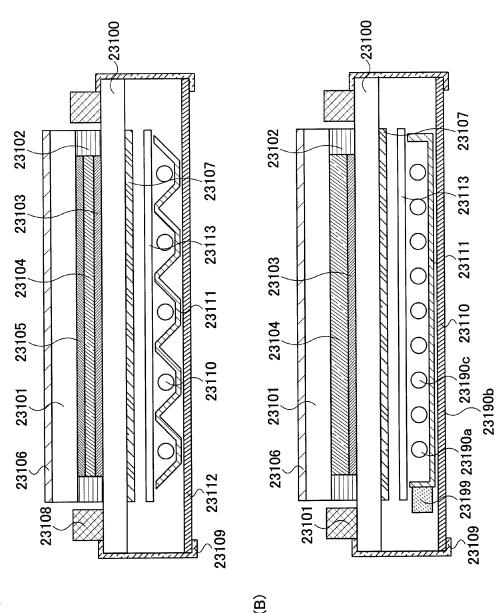

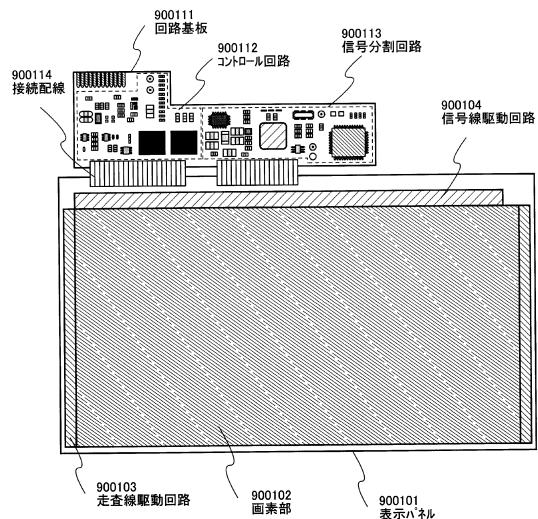

ここで、本実施形態の液晶表示モジュールを図38(A)及び図38(B)を用いて説明する。

【0325】

図38(A)は液晶表示モジュールの一例であり、TFT基板 23100 と対向基板 23101 がシール材 23102 により固着され、その間に TFT 等を含む画素部 23103 と液晶層 23104 が設けられ表示領域を形成している。着色層 23105 はカラー表示を行う場合に必要であり、RGB 方式の場合は、赤、緑、青の各色に対応した着色層が各画素に対応して設けられている。TFT 基板 23100 と対向基板 23101 の外側には第1の偏光子を含む層 23106、第2の偏光子を含む層 23107、拡散板 23113 が配設されている。光源は冷陰極管 23110 と反射板 23111 により構成され、回路基板 23112 は、フレキシブル配線基板 23109 により TFT 基板 23100 と接続され、コントロール回路や電源回路などの外部回路が組みこまれている。 40

【0326】

TFT 基板 23100 と光源であるバックライトの間には第2の偏光子を含む層 23107 が積層して設けられ、対向基板 23101 にも第1の偏光子を含む層 23106 が積層して設けられている。一方、第2の偏光子を含む層 23107 の吸収軸と、視認側に設けられた第1の偏光子を含む層 23106 の吸収軸とは、クロスニコルになるように配置される。 50

## 【0327】

積層された第2の偏光子を含む層23107や積層された第1の偏光子を含む層23106は、TFT基板23100、対向基板23101に接着されている。また積層された偏光子を含む層と、基板との間に位相差板を有した状態で積層してもよい。また、必要に応じて、視認側である第1の偏光子を含む層23106には反射防止処理を施してもよい。

## 【0328】

液晶表示モジュールには、TN(Twisted Nematic)モード、IPS( In-Plane-Switching)モード、FFS(Fringe Field Switching)モード、MVA(Multi-domain Vertical Alignment)モード、PVA(Patterned Vertical Alignment)、ASM(Axially Symmetric aligned Micro-cell)モード、OCB(Optical Compensated Birefringence)モード、FLC(Ferroelectric Liquid Crystal)モード、AFLC(AntiFerroelectric Liquid Crystal)、PDLC(Polymer Dispersed Liquid Crystal)モードなどを用いることができる。

## 【0329】

図38(B)は図38(A)の液晶表示モジュールにOCBモードを適用した一例であり、FS-LCD(Field sequential-LCD)となっている。FS-LCDは、1フレーム期間に赤色発光と緑色発光と青色発光をそれぞれ行うものであり、時間分割を用いて画像を合成しカラー表示を行うことが可能である。また、各発光を発光ダイオードまたは冷陰極管等で行うので、カラーフィルターが不要である。よって、3原色のカラーフィルターを並べ、各色の表示領域を限定する必要がなく、どの領域でも3色全ての表示を行うことができる。一方、1フレーム期間に3色の発光を行うため、液晶の高速な応答が求められる。本実施の形態の表示装置に、FS方式を用いたFLCモード及びOCBモードを適用し、高性能で高画質な表示装置、また液晶テレビジョン装置を完成させることができる。

## 【0330】

OCBモードの液晶層は、いわゆるセル構造を有している。セル構造とは、液晶分子のプレチルト角がアクティブマトリクス基板と対向基板との基板間の中心面に対して面对称の関係で配向された構造である。セル構造の配向状態は、基板間に電圧が印加されていない時はスプレイ配向となり、電圧を印加するとベンド配向に移行する。このベンド配向が白表示となる。さらに電圧を印加するとベンド配向の液晶分子が両基板と垂直に配向し、光が透過しない状態となる。なお、OCBモードにすると、従来のTNモードより約10倍速い高速応答性を実現できる。

## 【0331】

また、FS方式に対応するモードとして、高速動作が可能な強誘電性液晶(FLC:Ferroelectric Liquid Crystal)を用いたHV(Half V)-FLC、SS(Surface Stabilized)-FLCなども用いることができる。

## 【0332】

また、液晶表示モジュールのセルギャップを狭くすることで、液晶表示モジュールの光学応答速度を高速化することができる。また、液晶材料の粘度を下げる事でも高速化できる。高速化は、TNモードの液晶表示モジュールの画素領域の画素ピッチが30μm以下の場合に、より効果的である。また、液晶層にかける印加電圧を本来の電圧よりも一瞬だけ高く(または低く)するオーバードライブを用いることで、高速化を行なってもよい。

## 【0333】

図38(B)の液晶表示モジュールは透過型の液晶表示モジュールを示しており、光源として赤色光源23190a、緑色光源23190b、青色光源23190cが設けられ

10

20

30

40

50

ている。光源は赤色光源 23190a、緑色光源 23190b、青色光源 23190c のそれぞれオンオフを制御するために、制御部 23199 が設置されている。制御部 23199 によって、各色の発光は制御され、液晶に光は入射し、時間分割を用いて画像を合成し、カラー表示が行われる。

#### 【0334】

なお、本実施の形態において、様々な図を用いて述べてきたが、各々の図で述べた内容（一部でもよい）は、別の図で述べた内容（一部でもよい）に対して、適用、組み合わせ、又は置き換えなどを自由に行うことが出来る。さらに、これまでに述べた図において、各々の部分に関して、別の部分を組み合わせることにより、さらに多くの図を構成させることが出来る。

10

#### 【0335】

同様に、本実施の形態の各々の図で述べた内容（一部でもよい）は、別の実施の形態の図で述べた内容（一部でもよい）に対して、適用、組み合わせ、又は置き換えなどを自由に行うことが出来る。さらに、本実施の形態の図において、各々の部分に関して、別の実施の形態の部分を組み合わせることにより、さらに多くの図を構成させることが出来る。

#### 【0336】

なお、本実施の形態は、他の実施の形態で述べた内容（一部でもよい）を、具現化した場合の一例、少し変形した場合の一例、一部を変更した場合の一例、改良した場合の一例、詳細に述べた場合の一例、応用した場合の一例、関連がある部分についての一例などを示している。したがって、他の実施の形態で述べた内容は、本実施の形態への適用、組み合わせ、又は置き換えを自由に行うことができる。

20

#### 【0337】

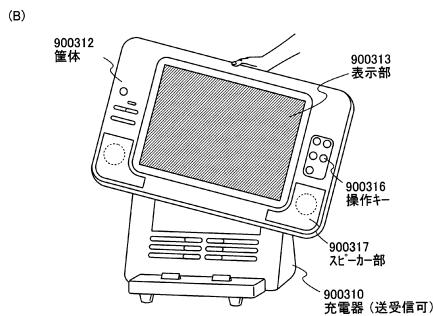

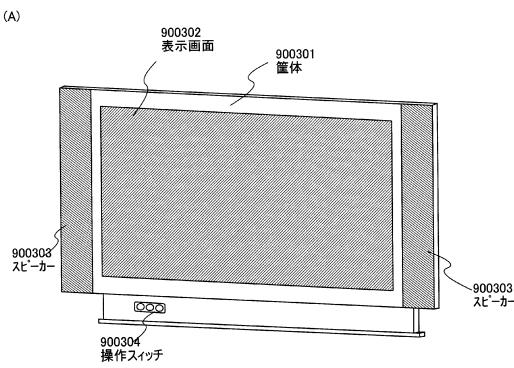

#### [実施の形態 8]

本実施形態においては、表示装置の駆動方法について説明する。特に、液晶表示装置の駆動方法について説明する。

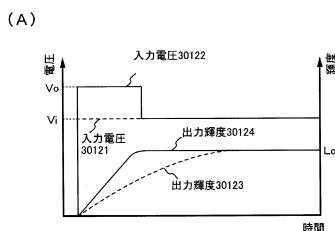

#### 【0338】

まず、オーバードライブ駆動について、図 39 を参照して説明する。図 39 の (A) は、表示素子の、入力電圧に対する出力輝度の時間変化を表したものである。破線で表した入力電圧 30121 に対する表示素子の出力輝度の時間変化は、同じく破線で表した出力輝度 30123 のようになる。すなわち、目的の出力輝度  $L_o$  を得るための電圧は  $V_i$  であるが、入力電圧として  $V_i$  をそのまま入力した場合は、目的の出力輝度  $L_o$  に達するまでに、素子の応答速度に対応した時間を要してしまう。

30

#### 【0339】

オーバードライブ駆動は、この応答速度を速めるための技術である。具体的には、まず、 $V_i$  よりも大きい電圧である  $V_o$  を素子に一定時間与えることで出力輝度の応答速度を高めて、目的の出力輝度  $L_o$  に近づけた後に、入力電圧を  $V_i$  に戻す、という方法である。このときの入力電圧は入力電圧 30122、出力輝度は出力輝度 30124 に表したようになる。出力輝度 30124 のグラフは、目的の輝度  $L_o$  に至るまでの時間が、出力輝度 30123 のグラフよりも短くなっている。

#### 【0340】

40

なお、図 39 の (A) においては、入力電圧に対し出力輝度が正の変化をする場合について述べたが、入力電圧に対し出力輝度が負の変化をする場合も、本実施の形態は含んでいる。

#### 【0341】

このような駆動を実現するための回路について、図 39 の (B) および図 39 の (C) を参照して説明する。まず、図 39 の (B) を参照して、入力映像信号 30131 がアナログ値（離散値でもよい）をとる信号であり、出力映像信号 30132 もアナログ値をとる信号である場合について説明する。図 39 の (B) に示すオーバードライブ回路は、符号化回路 30101、フレームメモリ 30102、補正回路 30103、D/A 変換回路 30104、を備える。

50

## 【0342】

入力映像信号30131は、まず、符号化回路30101に入力され、符号化される。つまり、アナログ信号から、適切なビット数のデジタル信号に変換される。その後、変換されたデジタル信号は、フレームメモリ30102と、補正回路30103と、にそれぞれ入力される。補正回路30103には、フレームメモリ30102に保持されていた前フレームの映像信号も、同時に入力される。そして、補正回路30103において、当該フレームの映像信号と、前フレームの映像信号から、あらかじめ用意された数値テーブルにしたがって、補正された映像信号を出力する。このとき、補正回路30103に出力切替信号30133を入力し、補正された映像信号と、当該フレームの映像信号を切替えて出力できるようにしてもよい。次に、補正された映像信号または当該フレームの映像信号は、DA変換回路30104に入力される。そして、補正された映像信号または当該フレームの映像信号にしたがった値のアナログ信号である出力映像信号30132が出力される。このようにして、オーバードライブ駆動が実現できる。10

## 【0343】

次に、図39の(C)を参照して、入力映像信号30131がデジタル値をとる信号であり、出力映像信号30132もデジタル値をとる信号である場合について説明する。図39の(C)に示すオーバードライブ回路は、フレームメモリ30112、補正回路30113、を備える。

## 【0344】

入力映像信号30131は、デジタル信号であり、まず、フレームメモリ30112と、補正回路30113にそれぞれ入力される。補正回路30113には、フレームメモリ30112に保持されていた前フレームの映像信号も、同時に入力される。そして、補正回路30113において、当該フレームの映像信号と、前フレームの映像信号から、あらかじめ用意された数値テーブルにしたがって、補正された映像信号を出力する。このとき、補正回路30113に出力切替信号30133を入力し、補正された映像信号と、当該フレームの映像信号を切替えて出力できるようにしてもよい。このようにして、オーバードライブ駆動が実現できる。20

## 【0345】

なお、本実施の形態におけるオーバードライブ回路は、入力映像信号30131がアナログ信号であり、出力映像信号30132がデジタル信号である場合も含む。このときは、図39の(B)に示した回路から、DA変換回路30104を省略すればよい。また、本実施の形態におけるオーバードライブ回路は、入力映像信号30131がデジタル信号であり、出力映像信号30132がアナログ信号である場合も含む。このときは、図39の(B)に示した回路から、符号化回路30101を省略すればよい。30

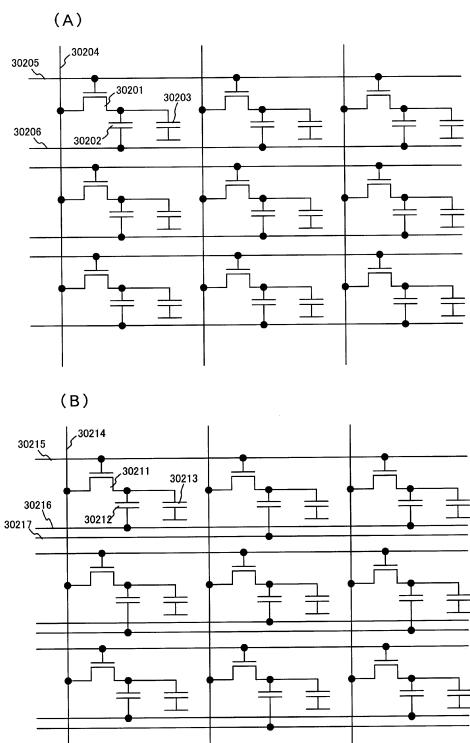

## 【0346】

次に、コモン線の電位を操作する駆動について、図40を参照して説明する。図40の(A)は、液晶素子のような容量的な性質を持つ表示素子を用いた表示装置において、走査線1本に対し、コモン線が1本配置されているときの、複数の画素回路を表した図である。図40の(A)に示す画素回路は、トランジスタ30201、補助容量30202、表示素子30203、映像信号線30204、走査線30205、コモン線30206、を備えている。40

## 【0347】

トランジスタ30201のゲート電極は、走査線30205に電気的に接続され、トランジスタ30201のソースまたはドレイン電極の一方は、映像信号線30204に電気的に接続され、トランジスタ30201のソースまたはドレイン電極の他方は、補助容量30202の一方の電極、および表示素子30203の一方の電極に電気的に接続されている。

また、補助容量30202の他方の電極は、コモン線30206に電気的に接続されている。

## 【0348】

まず、走査線 30205 によって選択された画素は、トランジスタ 30201 がオンとなるため、それぞれ、映像信号線 30204 を介して、表示素子 30203 および補助容量 30202 に映像信号に対応した電圧がかかる。このとき、その映像信号が、コモン線 30206 に接続された全ての画素に対して最低階調を表示させるものだった場合、または、コモン線 30206 に接続された全ての画素に対して最高階調を表示させるものだった場合は、画素にそれぞれ映像信号線 30204 を介して映像信号を書き込む必要はない。映像信号線 30204 を介して映像信号を書き込む代わりに、コモン線 30206 の電位を動かすことで、表示素子 30203 にかかる電圧を変えることができる。

#### 【0349】

次に、図 40 の (B) は、液晶素子のような容量的な性質を持つ表示素子を用いた表示装置において、走査線 1 本に対し、コモン線が 2 本配置されているときの、複数の画素回路を表した図である。図 40 の (B) に示す画素回路は、トランジスタ 30211、補助容量 30212、表示素子 30213、映像信号線 30214、走査線 30215、第 1 のコモン線 30216、第 2 のコモン線 30217、を備えている。

10

#### 【0350】

トランジスタ 30211 のゲート電極は、走査線 30215 に電気的に接続され、トランジスタ 30211 のソースまたはドレイン電極の一方は、映像信号線 30214 に電気的に接続され、トランジスタ 30211 のソースまたはドレイン電極の他方は、補助容量 30212 の一方の電極、および表示素子 30213 の一方の電極に電気的に接続されている。

20

また、補助容量 30212 の他方の電極は、第 1 のコモン線 30216 に電気的に接続されている。

また、当該画素と隣接する画素においては、補助容量 30212 の他方の電極は、第 2 のコモン線 30217 に電気的に接続されている。

#### 【0351】

図 40 の (B) に示す画素回路は、コモン線 1 本に対し電気的に接続されている画素が少ないため、映像信号線 30214 を介して映像信号を書き込む代わりに、第 1 のコモン線 30216 または第 2 のコモン線 30217 の電位を動かすことで、表示素子 30213 にかかる電圧を変えることができる頻度が、顕著に大きくなる。また、ソース反転駆動またはドット反転駆動が可能になる。ソース反転駆動またはドット反転駆動により、素子の信頼性を向上させつつ、フリッカを抑えることができる。

30

#### 【0352】

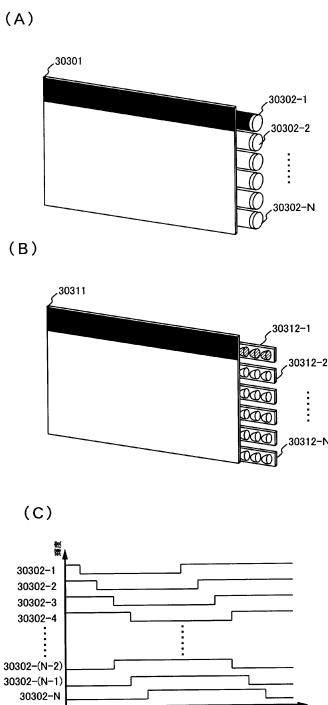

次に、走査型バックライトについて、図 41 を参照して説明する。図 41 の (A) は、冷陰極管を並置した走査型バックライトを示す図である。図 41 の (A) に示す走査型バックライトは、拡散板 30301 と、N 個の冷陰極管 30302 1 から 30302 N と、を備える。N 個の冷陰極管 30302 1 から 30302 N を、拡散板 30301 の後ろに並置することで、N 個の冷陰極管 30302 1 から 30302 N は、その輝度を変化させて走査することができる。

#### 【0353】

走査するときの各冷陰極管の輝度の変化を、図 41 の (C) を用いて説明する。まず、冷陰極管 30302 1 の輝度を、一定時間変化させる。そして、その後に、冷陰極管 30302 1 の隣に配置された冷陰極管 30302 2 の輝度を、同じ時間だけ変化させる。このように、冷陰極管 30302 1 から 30302 N まで、輝度を順に変化させる。なお、図 41 の (C) においては、一定時間変化させる輝度は、元の輝度より小さいものとしたが、元の輝度より大きくてよい。また、冷陰極管 30302 1 から 30302 N まで走査するとしたが、逆方向に冷陰極管 30302 N から 30302 1 まで走査してもよい。

40

#### 【0354】

図 41 のように駆動することで、バックライトの平均輝度を小さくすることができる。したがって、液晶表示装置の消費電力の大部分を占める、バックライトの消費電力を低減

50

することができる。

【0355】

なお、走査型バックライトの光源として、LEDを用いてもよい。その場合の走査型バックライトは、図41の(B)のようになる。図41の(B)に示す走査型バックライトは、拡散板30311と、LEDを並置した光源30312 1から30312 Nと、を備える。走査型バックライトの光源として、LEDを用いた場合、バックライトを薄く、軽くできる利点がある。また、色再現範囲を広げることができるという利点がある。さらに、LEDを並置した光源30312 1から30312 Nのそれぞれに並置したLEDも、同様に走査することができるので、点走査型のバックライトとすることもできる。点走査型とすれば、動画像の画質をさらに向上させることができる。

10

【0356】

なお、バックライトの光源としてLEDを用いた場合も、図41の(C)に示すように輝度を変化させて駆動することができる。

【0357】

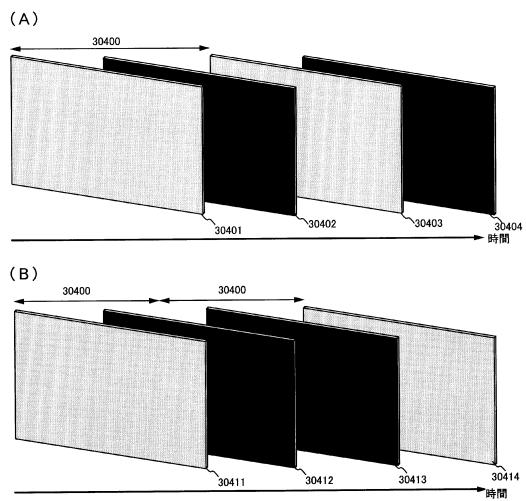

次に、高周波駆動について、図42を参照して説明する。図42の(A)は、1フレーム期間30400に1つの画像および1つの中間画像を表示するときの図である。30401は当該フレームの画像、30402は当該フレームの中間画像、30403は次フレームの画像、30404は次フレームの中間画像である。

20

【0358】

なお、当該フレームの中間画像30402は、当該フレームおよび次フレームの映像信号を元に作成された画像であってもよい。また、当該フレームの中間画像30402は、当該フレームの画像30401から作成された画像であってもよい。また、当該フレームの中間画像30402は、黒画像であってもよい。こうすることで、ホールド型表示装置の動画像の画質を向上できる。また、1フレーム期間30400に1つの画像および1つの中間画像を表示する場合は、映像信号のフレームレートと整合性が取り易く、画像処理回路が複雑にならないという利点がある。

【0359】

図42の(B)は、1フレーム期間30400が2つ連続する期間(2フレーム期間)に1つの画像および2つの中間画像を表示するときの図である。30411は当該フレームの画像、30412は当該フレームの中間画像、30413は次フレームの中間画像、30414は次々フレームの画像である。

30

【0360】

なお、当該フレームの中間画像30412および次フレームの中間画像30413は、当該フレーム、次フレーム、次々フレームの映像信号を元に作成された画像であってもよい。また、当該フレームの中間画像30412および次フレームの中間画像30413は、黒画像であってもよい。2フレーム期間に1つの画像および2つの中間画像を表示する場合は、周辺駆動回路の動作周波数をそれほど高速化することなく、効果的に動画像の画質を向上できるという利点がある。

【0361】

なお、本実施の形態において、様々な図を用いて述べてきたが、各々の図で述べた内容(一部でもよい)は、別の図で述べた内容(一部でもよい)に対して、適用、組み合わせ、又は置き換えなどを自由に行うことが出来る。さらに、これまでに述べた図において、各々の部分に関して、別の部分を組み合わせることにより、さらに多くの図を構成させることが出来る。

40

【0362】

同様に、本実施の形態の各々の図で述べた内容(一部でもよい)は、別の実施の形態の図で述べた内容(一部でもよい)に対して、適用、組み合わせ、又は置き換えなどを自由に行うことが出来る。さらに、本実施の形態の図において、各々の部分に関して、別の実施の形態の部分を組み合わせることにより、さらに多くの図を構成させることが出来る。

【0363】

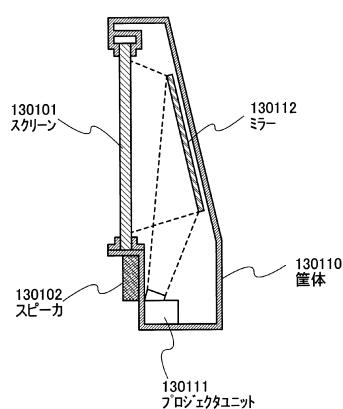

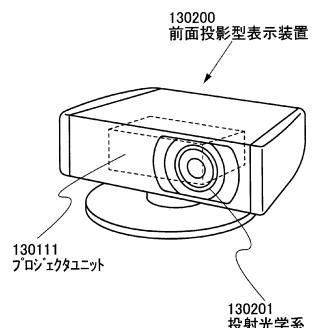

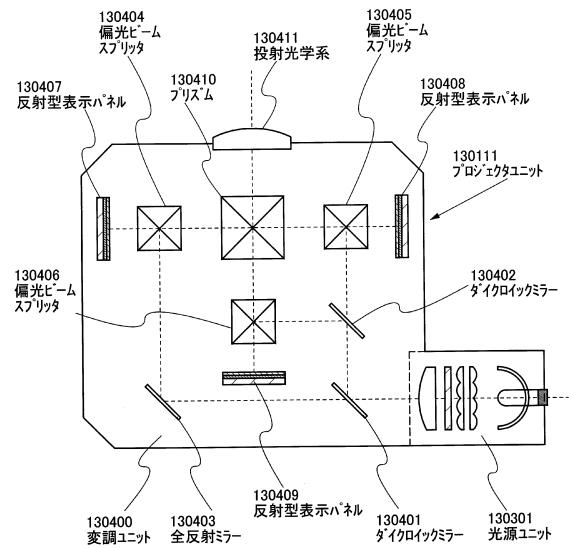

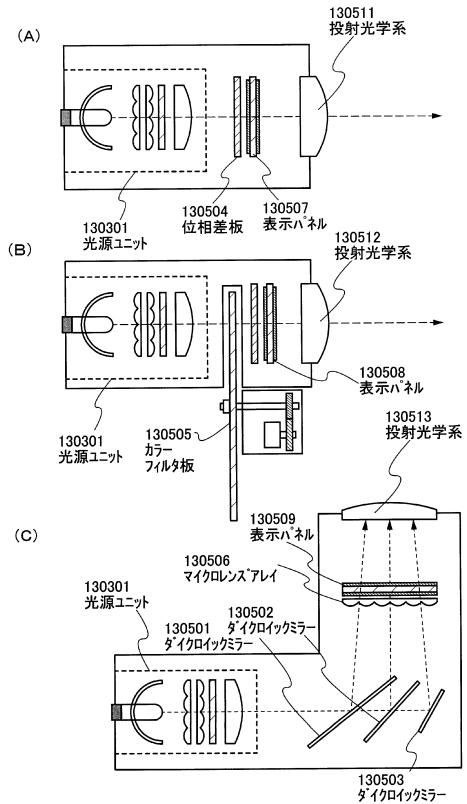

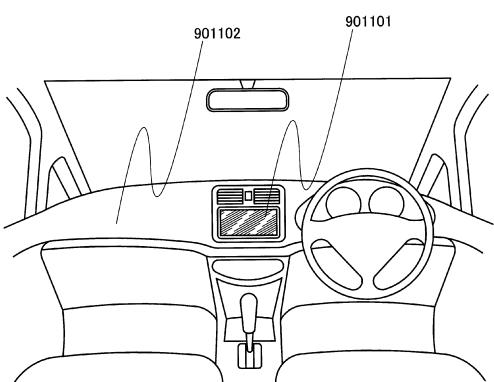

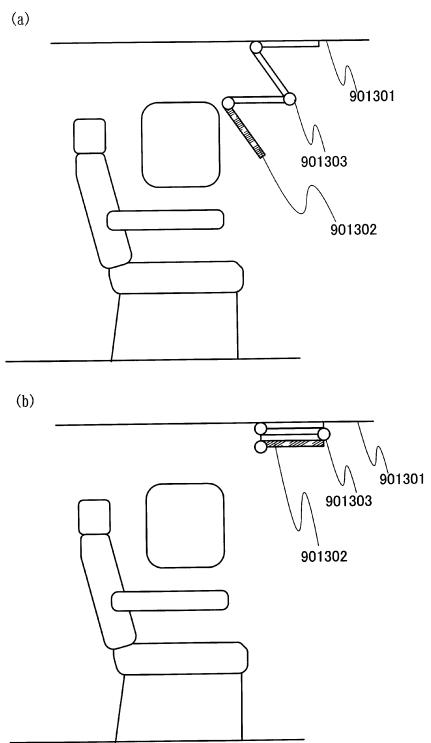

50