| [54]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | WAVEFO                                    | RM PRODUCING DEVICE                                                                                                                 |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| [75]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Inventors:                                | Norio Tomisawa, Hamamatsu;<br>Yasuji Uchiyama, Hamakita;<br>Takatoshi Okumura; Toshio<br>Takeda, both of Hamamatsu, all of<br>Japan |  |  |  |  |  |

| [73]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Assignee:                                 | Nippon Gakki Seizo Kabushiki<br>Kaisha, Shizuoka, Japan                                                                             |  |  |  |  |  |

| [22]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Filed:                                    | Oct. 23, 1973                                                                                                                       |  |  |  |  |  |

| [21]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Appl. No.:                                | 408,430                                                                                                                             |  |  |  |  |  |

| [30]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Oct. 25, 19<br>Oct. 25, 19<br>Oct. 25, 19 | 72       Japan       47-106945         72       Japan       47-106946         72       Japan       47-106947                        |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Int. Cl                                   | G11c 11/40                                                                                                                          |  |  |  |  |  |

| Yasuji Uchiyama, Hamakita; Takatoshi Okumura; Toshio Takeda, both of Hamamatsu, all of Japan  [73] Assignee: Nippon Gakki Seizo Kabushiki Kaisha, Shizuoka, Japan  [22] Filed: Oct. 23, 1973  [21] Appl. No.: 408,430  [30] Foreign Application Priority Data Oct. 25, 1972 Japan 47-106945 Oct. 25, 1972 Japan 47-106946 Oct. 25, 1972 Japan 47-106947 Oct. 25, 1972 Japan 47-106947 Oct. 25, 1972 Japan 47-106948  [52] U.S. Cl. 340/173 R; 338/22 SD  [51] Int. Cl. G11c 11/40  [58] Field of Search 340/173 R, 173 SP, 173 DR; |                                           |                                                                                                                                     |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | UNIT                                      | TED STATES PATENTS                                                                                                                  |  |  |  |  |  |

| 3,721,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 964 3/19                                  | 73 Barrett 340/173 R                                                                                                                |  |  |  |  |  |

| 3,735,367 5/1973 | Bennett | 340/173 | R |

|------------------|---------|---------|---|

|------------------|---------|---------|---|

Primary Examiner—Terrell W. Fears Attorney, Agent, or Firm—Holman & Stern

# [57] ABSTRACT

A single resistor bar having a plurality of connection points is formed by a diffused layer on a semiconduuctor substrate. A predetermined voltage is applied across the resistance layer so that the respective connection points exhibit different potentials. A decoder designates, via a reading switch circuit and successively at a predetermined time rate and order, which of the potentials to read out. Thus sequentially readout voltages constitute a waveform of a particular tone color or an envelope of a particular shape. The decoder and the reading switch circuit may be formed by MOS transistors, and the circuits thus formed may be combined together with the resistance layer in an integrated structure on the semiconductor substrate.

## 8 Claims, 29 Drawing Figures

F | G.2

-3

FIG.6(A)

FIG.6(B)

| TRANSISTOR BIT NO |         |                |                | <u> </u>                                                                                                                          |                | ſ              | TDANICICTOR | - :                   | D                                      | IT N           | <u> </u>       | - :            |                |                |

|-------------------|---------|----------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|-------------|-----------------------|----------------------------------------|----------------|----------------|----------------|----------------|----------------|

| TRANSISTOR GROUB  | -       | 2              | 311 18         | 4                                                                                                                                 | 5              | 6              |             | TRANSISTOR  <br>GROUB | <del></del>                            | 2              | 3              | .4             | 5              | 6              |

| GROOD             |         |                |                |                                                                                                                                   | <u> </u>       | -              | ł           | 00012                 |                                        |                | 7.             |                |                |                |

| ТО                | JI      | J2             | J3             | J4                                                                                                                                | J5             | J6             |             | T2I                   | J۱                                     | J2             | J3             | J4             | J5             | J6             |

| TI                | Ji      | J2             | J3             | <del>-</del> | J5             | J6             |             | T22                   | Ji.                                    | J2             | JЗ             | J4             | J <sub>5</sub> | J6             |

| T2                | Ji      | J2             | J3             | J4                                                                                                                                | J5             | J6             |             | T23                   | J١                                     | J2             | J3             | J <sub>4</sub> | J5             | J6             |

| T3                | JI      | J2             | J3             | J4                                                                                                                                | J5             | J6             |             | T24                   | Jı                                     | J2             | J3             | J4             | J5             | J6             |

| T4                | JI      | J2             | J3             | J4                                                                                                                                | J5             | J6             |             | T25                   | JI                                     | J2             | J3             | J <sub>4</sub> | J <sub>5</sub> | J6             |

| T5                | Ji      | J2             | _<br>J3        | J4                                                                                                                                | J5             | J6             |             | T26                   | JI                                     | J2             | J3             | <u></u>        | J5             | J6             |

| T6                | JI      | J <sub>2</sub> | <br>J3         | J4                                                                                                                                | J5             | J6             |             | T27                   | J١                                     | J2             | J3             | J4             | J5             | J <sub>6</sub> |

| T <sub>7</sub>    | JI      | J <sub>2</sub> | J <sub>3</sub> | J4                                                                                                                                | J5             | J6             |             | T28                   | JI                                     | J2             | J3             | J4             | J5             | J <sub>6</sub> |

| T8                | Ji      | J2             | J3             | J4                                                                                                                                | J5             | J6             |             | T29                   | Jī                                     | J2             | J3             | J4             | J5             | J <sub>6</sub> |

| Т9                | JI      | J2             | _<br>J3        | J4                                                                                                                                | J5             | J6             |             | T30                   | Ji                                     | J <sub>2</sub> | J <sub>3</sub> | J4             | J5             | J <sub>6</sub> |

| TIO               | JI      | J2             | Jз             | J4                                                                                                                                | J <sub>5</sub> | J6             |             | Т31                   | J١                                     | J2             | J3             | J4             | J <sub>5</sub> | J <sub>6</sub> |

| TU                | JI      | J2             | J3             | J4                                                                                                                                | _<br>J5        | J6             |             | T32                   | Ji                                     | J2             | J3             | J4             | J5             | J6             |

| TI2               | JI      | J <sub>2</sub> | J3             | J4                                                                                                                                | _<br>J5        | J6             |             | T33                   | JI                                     | J2             | J3             | J4             | J5             | J6             |

| T13               | Ji      | _<br>J2        | J3             | J4                                                                                                                                | J <sub>5</sub> | J6             |             | T34                   | Ji                                     | J2             | J3             | J4             | J5             | J6             |

| TI4               | JI      | J2             | <br>J3         | J4                                                                                                                                | J5             | J6             |             | T35                   | Ji                                     | J <sub>2</sub> | _<br>J3        | _<br>J4        | J5             | J <sub>6</sub> |

| T15               |         | J2             | <br>J3         | J4                                                                                                                                |                | J6             |             | T36                   | Jı                                     | J2             | J3             | J4             | J5             | J <sub>6</sub> |

| TI6               | JI      | J2             | J̃3            | J4                                                                                                                                | J5             | J6             |             | T37                   | Ji                                     | J <sub>2</sub> | J3             | J4             | J5             | J <sub>6</sub> |

| TI7               | JI      | J2             | J3             | J4                                                                                                                                | J5             | J6             |             | T38                   | Jı                                     | J2             | J <sub>3</sub> | J4             | J <sub>5</sub> | J <sub>6</sub> |

| TI8               | _<br>J1 | _<br>J2        | _<br>J3        | J4                                                                                                                                | _<br>J5        | J6             |             | T <b>3</b> 9          | Jı                                     | J2             | _<br>J3        | J4             | J5             | J <sub>6</sub> |

| Tı9               | 100     | J2             |                |                                                                                                                                   |                |                |             | T40                   | Ji                                     | J2             | J3             | J <sub>4</sub> | J5             | J <sub>6</sub> |

| T20               | -<br> J | J2             | J3             | _<br>J4                                                                                                                           | _<br>J5        | J <sub>6</sub> |             | T41                   | Ji                                     | J2             | J <sub>3</sub> | <b>J</b> 4     | J5             | <u>J</u> 6     |

|                   |         |                |                |                                                                                                                                   |                |                |             |                       |                                        |                |                |                |                |                |

| _ L               |         |                |                |                                                                                                                                   |                |                | ⅃           |                       | ــــــــــــــــــــــــــــــــــــــ | <del></del>    |                |                |                |                |

FIG.6(C)

FIG.7(A)

| TRANSISTOR | · · |                | 3IT            | NO |                |                | TIME      | ١          |

|------------|-----|----------------|----------------|----|----------------|----------------|-----------|------------|

| GROUP      | 1   | 2              | 3              | 4  | 5              | 6              | INSTANT   | ДΙ         |

| T42        | Jı  | J <sub>2</sub> | <br>J3         | J4 | J5             | J <sub>6</sub> | to        | 0          |

| T43        | JI  | J2             | J3             | J4 | J5             | J <sub>6</sub> | †ı        | ess () See |

| T44        | JI  | J <sub>2</sub> | J3             | J4 | J5             | J <sub>6</sub> | t2        | 0          |

| T45        | JI  | J <sub>2</sub> | J3             | J4 | J5             | J <sub>6</sub> | fз        | 1          |

| T46        | Jı  | J2             | J3             | J4 | J5             | J <sub>6</sub> | †4        | 0          |

| T47        | Jı  | J <sub>2</sub> | J3             | J4 | J5             | J <sub>6</sub> | †5        | 1          |

| T48        | Jı  | J2             | J3             | J4 | J5             | J6             | †6        | 0          |

| T49        | Jī  | J <sub>2</sub> | J3             | J4 | J5             | J <sub>6</sub> | <b>†7</b> | 1          |

| T50        | JI  | J2             | J3             | J4 | J5             | J6             | is        | 0          |

| T51        | JI  | Jz             | J3             | J4 | J5             | J <sub>6</sub> | 19        | 1          |

| T52        | Ji  | J2             | J3             | J4 | J <sub>5</sub> | J <sub>6</sub> | tio       | 0          |

| T53        | Jī  | J2             | J3             | J4 | J5             | J6             | *11       | 1          |

| T54        | Ji  | J2             | J3             | J4 | J5             | J <sub>e</sub> | 112       | 0          |

| T55        | J۱  | JZ             | J3             | JA | J5             | J6             | †13       | 1          |

| T56        | J١  | J2             | J3             | J4 | J5             | Je             | †14       | 0          |

| T57        | Ji  | J2             | J3             | J4 | J5             | J6             | 115       | 1          |

| T58        | Ji  | J <sub>2</sub> | J3             | J4 | J <sub>5</sub> | Je             | tis       | 0          |

| T59        | Jı  | J2             | J <sub>3</sub> | J4 | J5             | J <sub>6</sub> | 117       | ı          |

| T60        | Ji  | J2             | J3             | J4 | J5             | J <sub>6</sub> | tis       | 0          |

| T61        | J١  | J2             | J <sub>3</sub> | Ja | J <sub>5</sub> | J <sub>6</sub> | 119       | 1          |

| T62        | Ji  | J2             | <u>J</u> 3     | JA | J5             | J <sub>6</sub> | †20       | 0          |

| T63        | JI  | J2             | JЗ             | J4 | J5             | J6             | <b>L</b>  |            |

| TIME<br>INSTANT | ДΙ       | Α2     | ДЗ   | Д4 | A5 | A6 |

|-----------------|----------|--------|------|----|----|----|

| to              | 0        | 0      | 0    | 0  | 0  | 0  |

|                 | ecotypas | 0      | 0    | 0  | 0  | 0  |

| 12              | 0        |        | 0    | 0  | 0  | 0  |

| ťЗ              | 1        | Ì      | 0    | 0  | 0  | 0  |

| 14              | 0        | 0      |      | 0  | 0  | 0  |

| 15              |          | 0      | 1    | 0  | 0  | 0  |

| †6              | 0        | l      |      | 0  | 0  | 0  |

| 17              | ١        | E. 309 | i    | 0  | 0  | 0  |

| †8              | 0        | 0      | 0    |    | 0  | 0  |

| 19              | 1        | 0      | 0    | 1  | 0  | 0  |

| tio             | 0        | ı      | 0    | ļ  | 0  | 0  |

| *11             | 1        |        | 0    | 1  | 0  | 0  |

| †12             | 0        | 0      | 1    | 1  | 0  | 0  |

| 113             | -        | 0      | . [. |    | 0  | 0  |

| †I4             | 0        | -      | l    |    | 0  | 0  |

| †15             | 1        | 1      |      |    | 0  | 0  |

| †16             | 0        | 0      | 0    | 0  | I  | 0  |

| 117             | 1        | 0      | 0    | 0  | ı  | 0  |

| tis             | 0        | 1      | 0    | 0  |    | 0  |

| 119             | 1        | 1      | 0    | 0  | 1  | 0  |

| †20             | 0        | 0      | i    | 0  | 1  | 0  |

FIG.7(B)

FIG.7(C)

| TIN | IME<br>ISTANT | ДΙ | A2  | Аз  | Α4  | <b>A</b> 5 | Α6 | TIME<br>INSTANT | Αι | A2                  | Аз | Α4  | <b>A</b> 5 | A6   |   |

|-----|---------------|----|-----|-----|-----|------------|----|-----------------|----|---------------------|----|-----|------------|------|---|

|     | 121           |    | 0   |     | 0   | 1          | 0  | 142             | 0  | ı                   | 0  | 1   | 0          | ı    | 1 |

|     | 122           | 0  | 1   | 1   | 0   | - 1        | 0  | †43             | 1  | ı                   | 0  | 1   | 0          | 1    |   |

|     | 123           | 1  | 1   | į.  | 0   | 1          | 0  | <b>†44</b>      | 0  | 0                   | 1. |     | 0          | I.   |   |

|     | †24           | 0  | 0   | 0   | 1   | 1          | 0  | †45             | 1  | 0                   | ı  | 1   | 0          | 1    |   |

| -   | 125           |    | 0   | 0   | 1   | 1          | 0  | <b>†46</b>      | 0  | . 1                 | 1  | ı   | 0          | 1    | İ |

|     | <b>†26</b>    | 0  |     | 0   | 1   | 1          | 0  | 147             | 1  | 1                   | 1  | 1   | 0          | -1   |   |

|     | 127           |    | 1.  | 0   | 1   | 1          | 0  | †48             | 0  | 0                   | 0  | 0   | l          | 1    |   |

|     | 128           | 0  | 0   | 1   | . 1 | 1          | 0  | †49             | 1  | 0                   | 0  | 0   |            | 1    |   |

|     | †29           |    | 0   | ı   | 1   | 1.         | 0  | 150             | 0  | l                   | 0  | 0   | l,         | . 1  |   |

|     | 130           | 0  | 1   | - 1 | 1   | 1          | 0  | t51             | 1. | 1                   | 0  | 0   | 1          | 1    |   |

|     | †31           | 1  | . ! | 1   | 1   |            | 0  | <b>†52</b>      | 0  | 0                   | 1  | 0   | l          | 1    |   |

|     | <b>†32</b>    | 0  | 0   | 0   | 0   | 0          | 1. | †53             | 1  | 0                   | 1  | 0   |            | <br> |   |

|     | 133           |    | 0   | 0   | 0   |            |    | †54             | 0  | . 1                 | 1. | 0   | 1          | ı    |   |

|     | †34           | 0  | 1.  | 0   | 0   | 0          |    | †55             |    | 1                   |    | 0   | 1          | 1    |   |

| .   | †35           |    | . ! | 0   | 0   | 0          |    | †56             | 0  | . 1 (3).<br>. 1 (4) | 0  | 1   |            |      |   |

|     | †36           | 0  | 0   | - 1 | 0   | 0          | 1  | †57             |    | 0                   | 0  |     | - !        | . !  |   |

|     | †37           |    | 0   |     | 0   | 0          |    | †58             | 0  | l                   | 0  | - 1 | 1          |      |   |

|     | †38           | 0  | 1   | 1   | 0   |            |    | t59             |    |                     | 0  | 1   |            | 1    |   |

|     | 139           |    | 1   | 1   | C   |            |    | teo             | 0  |                     | 1  |     |            |      |   |

|     | †40           | 0  | 0   |     |     | 0          | 1. | †61             |    | 0                   | 1  | - 1 |            | 1    |   |

|     | †41           |    | 0   | 0   | , I | 0          | !  | 162             | 0  |                     |    |     | . 1        |      |   |

|     |               |    |     |     |     |            |    | 163             |    |                     |    |     | - 1        |      |   |

FIG.12

SHEET

FIG.II

ş-M<sub>IO</sub>

Q63

(9 (10 (11

V8 V9 V10 V11 V48V49 V50V51V52V53V54V55V56V57 V58 V68V69V70V71

Q<sub>16</sub>

# WAVEFORM PRODUCING DEVICE

### BACKGROUND OF THE INVENTION

This invention relates to a device for producing a waveform having a particular tone-color or an envelope of a particular shape for electronic musical instruments.

A device for producing a waveform constituted by analog sampled values at successive time points in which resistance elements having resistances decisive 10 of the amplitude values to be produced are provided and electrical circuits for these elements are sequentially formed by means of mechanical contacts, is known in the art.

However, such a conventional device needs as many 15 resistance elements as the number of amplitude values (i.e. sampling time points) for forming an analog waveform to be produced, that is, it needs a number of resistance elements, and the size of the device is therefore inevitably large. Furthermore, the more ideal analog 20 waveform we try to produce, the more amplitude values it requires, that is, much more resistance elements are necessary for the production of the ideal analog waveform. However, the actual size of the device is naturally limited to a certain extent, and accordingly the 25 number of resistance elements employed therein is also limited to a certain number. Consequently, analog waveforms produced from the conventional device are of a non-continuous (stepwise) waveform.

In general, resistance elements vary widely in their <sup>30</sup> resistance, and precision resistance elements less in resistance fluctuation are high in price.

The resistances of resistance elements available in the market are standardized. Therefore, when resistance elements having resistances other than standard resistances are required for the production of a desired analog value, it is necessary to special order them, which will result in the increase of the price of the waveform producing device.

Furthermore, since the conventional device reads information by means of mechanical contacts, it suffers from various difficulties such as a relatively short service life and a slow reading speed.

On the other hand, for the purpose of producing an analog waveform in response to digital information, a digital-to-analog converter is employed. However, in the digital-analog converter proposed heretofore, the number of bits is limited to a certain value, and therefore analog waveforms produced are not always satisfactory in waveform continuity.

Furthermore, a waveform producing device employing integrated circuits has been proposed. In this conventional waveform producing device, a plurality of diffused resistance layers each having a certain width are formed on a semiconductor substrate, resistance values corresponding to amplitude values at respective sampling time points of an analog waveform to be produced are set on the diffused resistance layers, respectively, and by sequentially scanning these resistance layers from one outermost layer to the other outermost layer terminal voltages of the resistance layers are sequentially read out, whereby a desired analog waveform having variation of amplitudes corresponding to variation of the terminal voltages thus read is produced.

In this conventional waveform producing device, since a number of parallel diffused resistance layers are

formed on the semiconductor substrate as described above, it follows that a relatively large space is necessary for the device and a relatively large amount of electric power is consumed therein. These difficulties become significant as the number of the diffused resistance layers is increased for the purpose of improving the continuity of the analog waveform to be produced.

#### SUMMARY OF THE INVENTION

Accordingly, a primary object of this invention is to provide a waveform producing device having a low manufacturing cost which is free from the above-described difficulties accompanying conventional waveform producing devices and is capable of producing analog waveforms having satisfactory waveform continuity.

Another object of the invention is to provide a waveform producing device which is suitable for the production of a tone-color waveform or an envelope waveform having a rising and decaying characteristic necessary for electronic musical instruments.

A further object of the invention is to provide a waveform producing device which can readily produce a wave-form having variation of amplitudes similar to variation of logarithmical functions.

A still further object of the invention is to provide a reliable waveform producing device which can be made to be small in size with the aid of a technique on MOS integrated circuits.

The foregoing objects and other objects of this invetion have been achieved by the provision of a waveform producing device which comprises, per unit, one diffused layer resistor formed on a semi-conductor substrate and having a plurality of connection points, means for applying a predetermined voltage across the resistance layer to respectively provide different potentials at the connection points, and a reading circuit for reading the potentials at the connection points in a predetermined order, thereby to produce a desired waveform having variation of amplitude corresponding to variation of the potentials thus selected.

It is preferable that the reading circuit comprises a switching circuit having a plurality of MOS transistors connected to the connection points and an addressing circuit with MOS transistors for driving the switching circuit so that the MOS transistors in the switching circuit are turned on in a predetermined order, the reading circuit being combined together with the resistance layer in an integrated structure on the semicondutor.

Furthermore, T-type attenuation circuits may be connected by connecting additional resistors to the resistance layer.

The manner in which the above described objects are achieved by this invention will become more apparent from the following detailed description and the appended claims when read in conjunction with the accompanying drawings, in which like parts are designated by like reference numerals or characters.

#### BRIEF DESCRIPTION OF THE DRAWINGS

In the accompanying drawings:

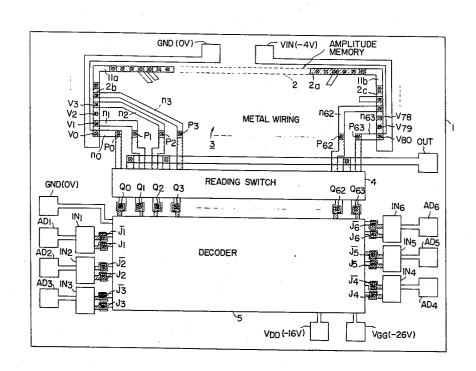

FIG. 1 is a plan view illustrating a first example of a waveform producing device according to this invention:

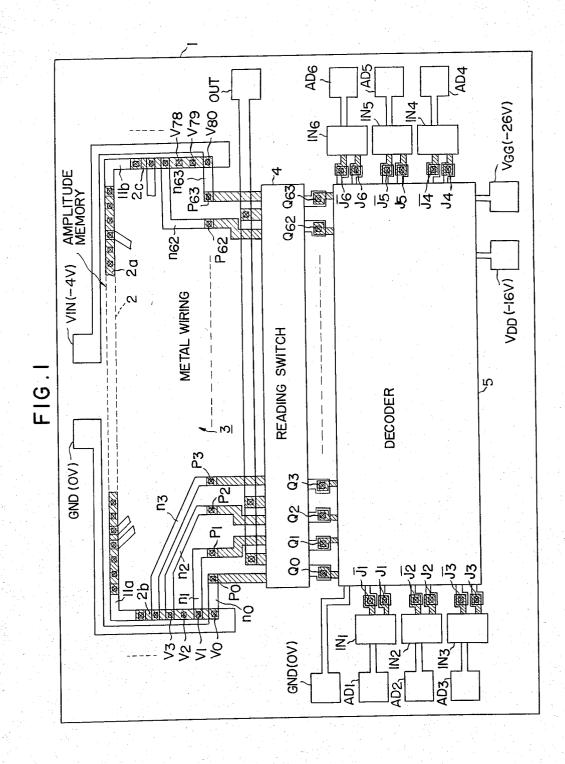

FIG. 2 is an equivalent circuit diagram of the waveform producing device shown in FIG. 1;

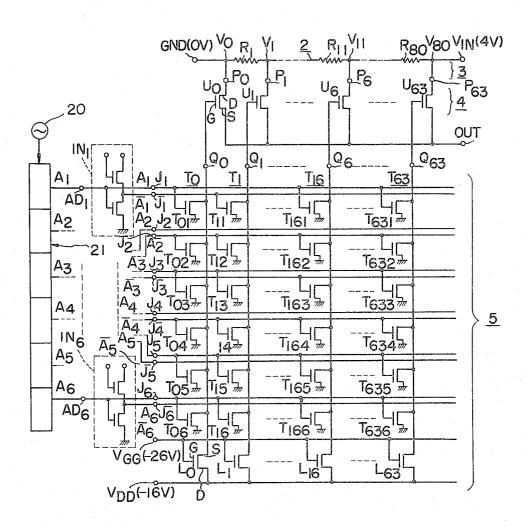

FIG. 3 is an enlarged detail of a waveform output section in the waveform producing device shown in FIG.

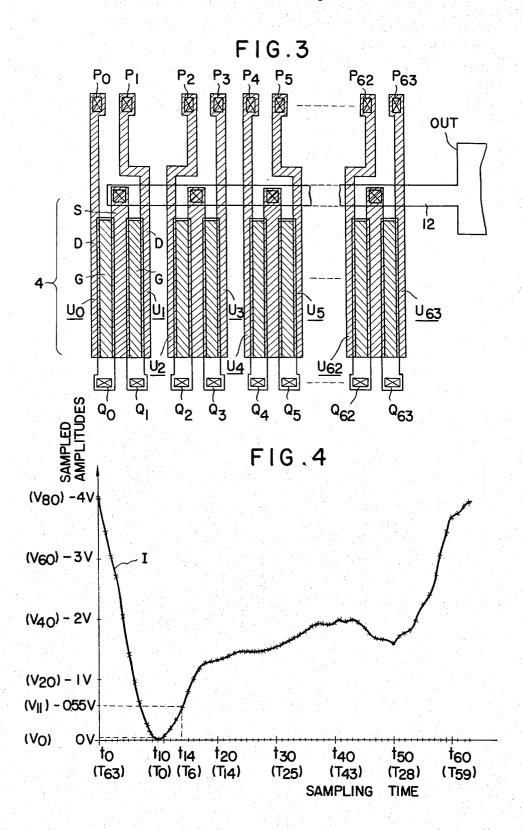

FIG. 4 is a graphical representation indicating a waveform generated;

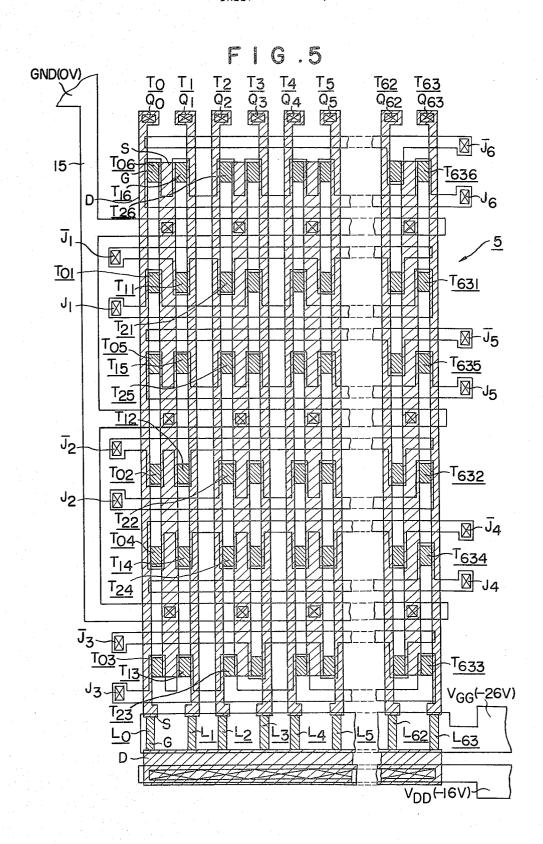

FIG. 5 is an enlarged view showing a decoder section in the device shown in FIG. 1;

FIGS. 6a, 6b and 6c provide tables indicating the relationships between transistor groups and address input connection points in the decoder section shown in FIG. 10

FIGS. 7a, 7b and 7c provide code tables for address inputs;

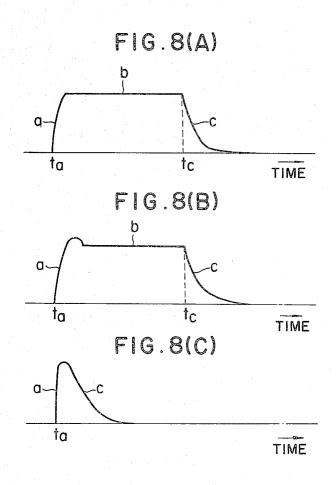

FIGS. 8(A), 8(B) and 8(C) are graphical representation indicating envelope waveforms employed in elec- 15 tronic musical instruments;

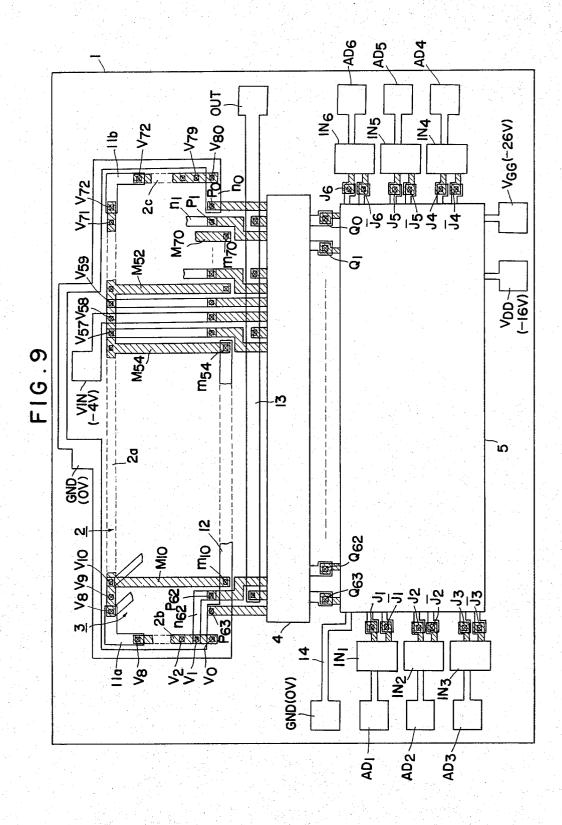

FIG. 9 is a plan view illustrating a second example of the waveform producing device according to the invention;

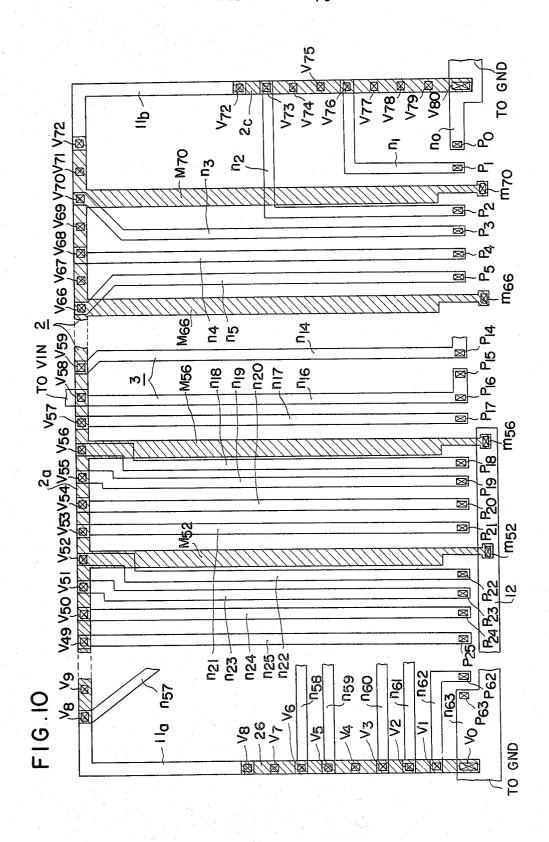

FIG. 10 is an enlarged view showing an amplitude 20 generating section and a metal wiring section in the waveform producing device shown in FIG. 9;

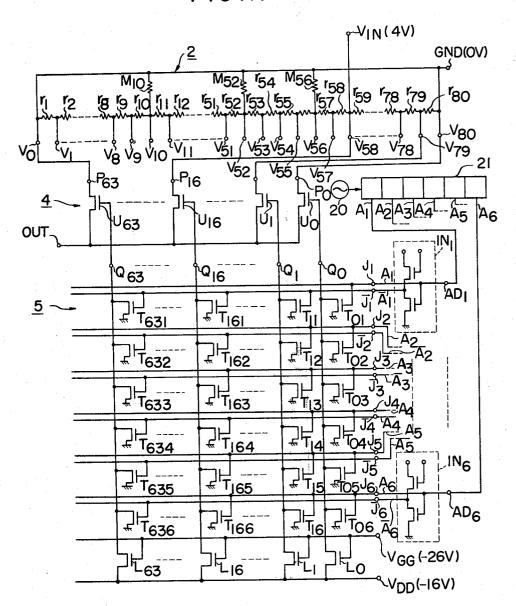

FIG. 11 is an equivalent circuit diagram of the waveform producing device shown in FIG. 9;

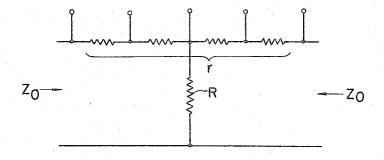

FIG. 12 is an equivalent circuit diagram of a resis- 25 tance attenuator unit in the amplitude generating section shown in FIGS. 9 and 11;

FIG. 13 is a graphical representation indicating the envelope waveform of a sustain tone;

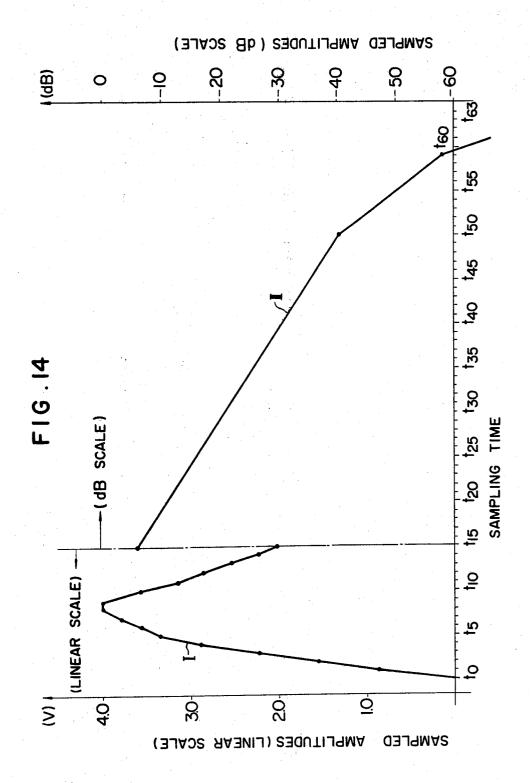

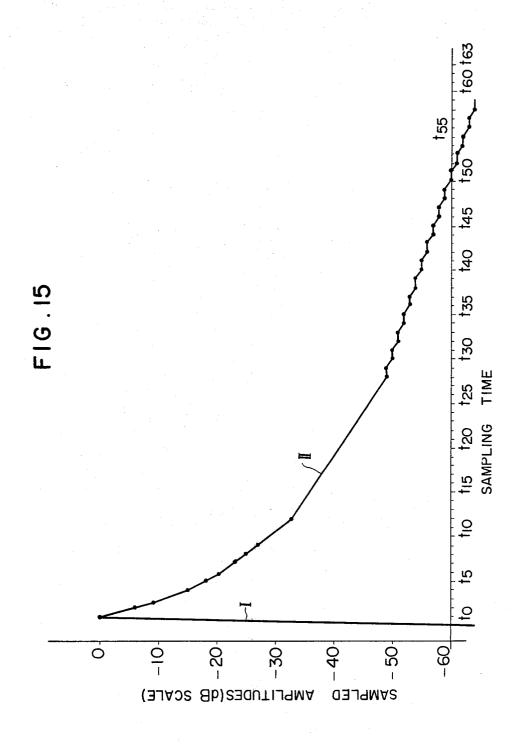

FIGS. 14 and 15 are also graphical representations respectively indicating the envelope waveforms of an attack-sustain tone and a percussive tone;

FIG. 16 is a plan view illustrating a third example of the waveform producing device according to this in-

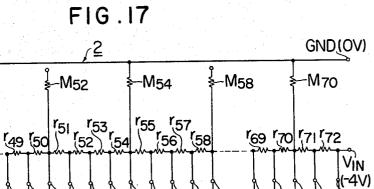

FIG. 17 is an equivalent circuit diagram of the waveform producing device shown in FIG. 16;

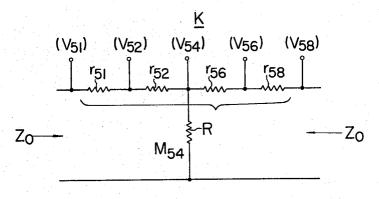

FIG. 18 is also an equivalent circuit of a resistance attenuator unit in an amplitude generating section of 17;

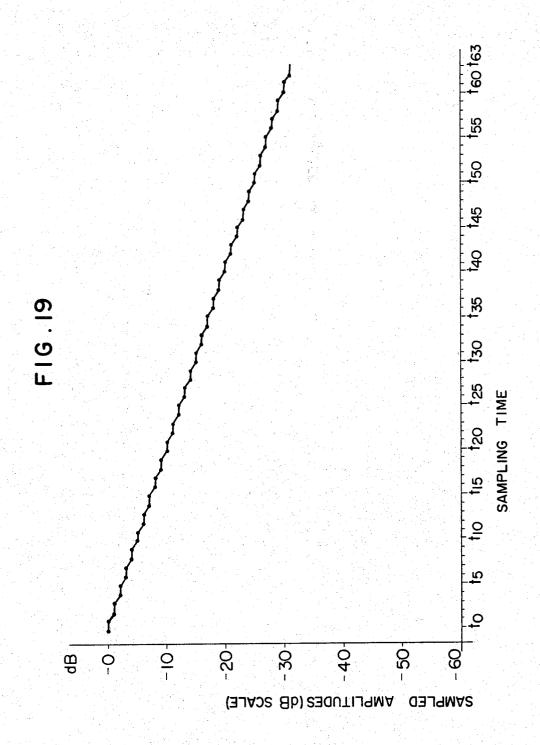

FIG. 19 is a graphical representation indicating an output waveform from the device shown in FIG. 16;

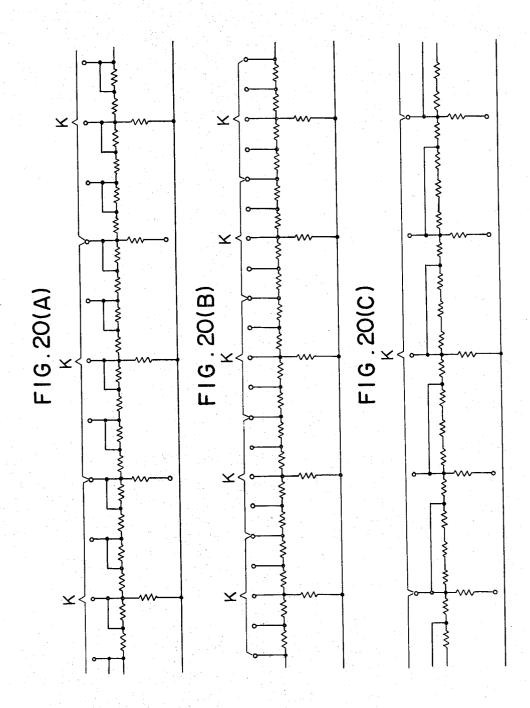

FIGS. 20(A), 20(B) and 20(C) are circuit diagrams of various attenuation circuits, and

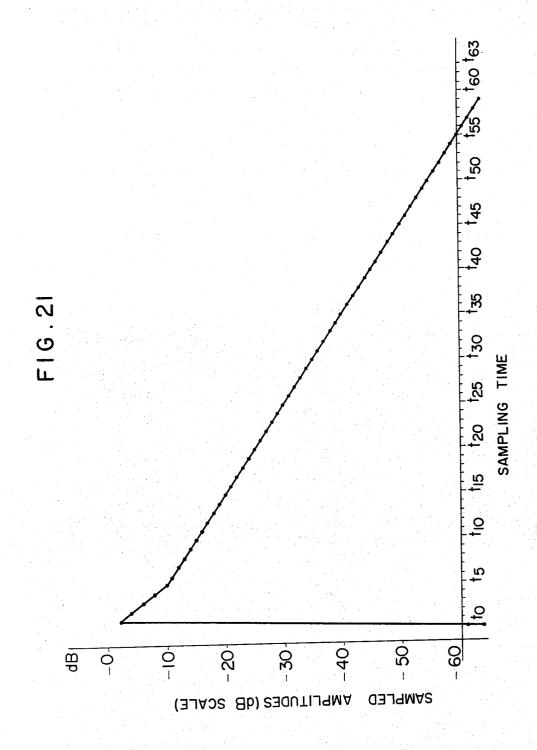

FIG. 21 is a graphical representation indicating the envelope waveform of a percussive tone.

### DETAILED DESCRIPTION OF THE INVENTION

With reference to FIG. 1 there is shown a first example of a waveform producing device for electronic musical instruments according to this invention, which comprises an N-type semiconductor substrate 1 and amplitude memory section 2 formed in the upper half portion of the substrate 1. The amplitude memory section 2 comprises a P-type diffused resistance layer 2a extended horizontally, and P-type diffused resistance layers 2b and 2c which are respectively extended vertically on the left and right sides of the layer 2a, in combination forming a single resistor zone. Below the amplitude memory section 2, or in the middle portion of the substrate 1, there is provided a waveform reading switch section 4 extended horizontally in parallel with the section 2. Between the amplitude memory section 2 and the waveform reading switch section 4, there is a metal wiring section 3 to electrically connect these two sections 2 and 4. Furthermore, below the wave-

form reading switch section 4, or in the lower half portion of the substrate 1, there is a decoder section 5 for driving the waveform reading switch section 4.

In FIG. 1, a pattern

represents a P-type diffused layer, a gate electrode of a P-channel MOS transistor  $\square$  a layer formed by vaccum-evaporation of a metal such as aluminum, and \( \simega \) a connection point for connecting the metal vacuum-evaporated layer to the Ptype diffused layer. In addition, an insulation film (not shown) is formed on the surface of the semiconductor substrate 1.

The diffused resistance layers 2a, 2b and 2c of the amplitude memory section 2 are in the form of a belt or stripe having the same width, for the left end of the layer 2a and the upper end of the layer 2b is connected by a metal connecting layer 11a while the right end of the layer 2a and the upper end of the layer 2c is connected by another metal connecting layer 11b. Thus, the layers 2a, 2b and 2c form one resistor assembly comprising resistors R<sub>1</sub> through R<sub>80</sub>, when expressed circuit diagram representation as is shown in FIG. 2. This resistor assembly has the same resistance per unit length. In the resistance layers 2a, 2b and 2c thus organized, there are provided, for instance, 81 connection points V<sub>0</sub>, V<sub>1</sub>, V<sub>2</sub> through V<sub>80</sub> at equal intervals. The connection points V<sub>0</sub> and V<sub>80</sub> provided on both ends of the resistor assembly 2 are respectively connected to terminals GND (OV) and Vin (-4V) of a power source. Thus, voltages proportional to the ratios of resistances from the connection point  $V_0$  to the other connection points V<sub>1</sub> through V<sub>80</sub> to the whole resistance from the point  $V_{\theta}$  to the point  $V_{8\theta}$  are provided at the connection points, the differences between these voltages being the same, namely, (4V/80 = 0.05V). The voltages thus provided at the connection points V<sub>0</sub> through V<sub>80</sub> are utilized as amplitude voltages of a waveform to be generated, as will be described later.

The reading switch section 4, as shown in FIG. 3, the waveform producing device shown in FIGS. 16 and 40 comprises, for instance, 64 MOS type output switching transistors U<sub>0</sub> and U<sub>1</sub> through U<sub>63</sub>, horizontally disposed in the order described. In this reading switch section 4, adjacent two transistors have a common P-type diffused layer serving as a source S and extended vertically. The adjacent transistors are disposed back-toback through two P-type diffused layers, or drains D, provided on the both sides of the source and two metal vacuum-evaporated layers, or gates G, formed between the source S and the drains D thereby to economize space.

> One-ends of the drains D of the transistors  $U_0$  and  $U_1$ through U<sub>63</sub> are extended upward. On the one-ends thus extended of the drains D there are provided connection points P<sub>0</sub> and P<sub>1</sub> through P<sub>63</sub>. One-ends of the sources S are also extended upward and are connected to a waveform output terminal OUT. Furthermore, one-ends of the gate G of the transistors U<sub>0</sub> and U<sub>1</sub> through  $U_{63}$  are extended downward and connected to driving input connection points  $Q_0$  and  $Q_1$  through  $Q_{63}$ .

Referring back to FIG. 1, the metal wiring section 3 will be described. The metal wiring section 3 comprises metal wiring connection layers  $n_0$  and  $n_1$  through  $n_{63}$ which are adapted to connect the connection points  $P_0$ and P<sub>1</sub> through P<sub>63</sub> to connection points selected, in accordance with a waveform to be produced, out of the connection points V<sub>0</sub> and V<sub>1</sub> through V<sub>80</sub> in the amplitude generating section 2. In this connection, it should

be noted that these layers  $n_0$  through  $n_{63}$  are not crossed with each other.

Consider, for instance, one period of a tone waveform of a trumpet voice as an example of the waveforms to be produced. In this case, a curve I such as 5 shown in FIG. 4 is memorized by time-sequentially plotting the amplitude voltages of the waveform to be generated. More specifically, if voltages 0.00V and -0.05V through - 4.00V respectively provided at the connection points  $V_0$  and  $V_1$  through  $V_{80}$  are read on 10 the vertical axis expressing amplitude voltages while sampling time instants  $t_0$  and  $t_1$  through  $t_{63}$  are read on the horizontal axis expressing read time instants, then for instance the voltage 0.00V at the connection point  $V_0$ , the voltage -0.05V at the connection point  $V_1$ , the 15 voltage -0.55V at the connection point V<sub>11</sub> and the voltage -4.00V at the connection point V<sub>80</sub> are read at the time instants  $t_{10}$ ,  $t_{11}$ ,  $t_{14}$  and  $t_{0}$ , respectively, whereby an analog waveform signal similar to the tone waveform of the trumpet voice can be obtained.

According to this invention, since potentials at the connection points Vo and V1 through V80 on the diffused resistance layers are selected in a particular order so that variation of these potentials represent variation of the amplitudes of a waveform to be generated, it is 25 not necessary to have the connection layers  $n_0$  and  $n_1$ through crossed with each other.

The decoder section 5 operates to address output transistors corresponding to amplitude voltages to be read at the read time instants  $t_0$ ,  $t_1$  through  $t_{63}$  in FIG. 30 4. In the first example, the decoder section 5 is of a 6binary-input and 64-individual-output type (binary to individual converter) which comprises 64 transistor groups each group comprising six MOS transistors which represents a six-bit address as is shown in FIG. 5. The transistors in each transistor group are provided with a common P-type diffused layer, or common source S, disposed vertically and a common P-type layer, or a common drain, disposed in parallel to the source S, and are arranged vertically. The upper ends of the drains D are connected to the driving input connection points  $Q_0$  and  $Q_1$  through  $Q_{63}$  of the reading switch section 4 described above, while the source S are connected through a metal connecting layer to a terminal GND (OV) of a power source. In this case also, adjacent transistors in adjacent transistor groups are disposed back-to-back in the same manner as in the case of the reading switch sectional 4. Thus, the transistor groups  $T_0 (T_{01} - T_{06})$  and  $T_1 (T_{11} - T_{16})$  through  $T_{63}$  $(T_{631} - T_{636})$  are arranged in the order described from the left to the right.

The diffused layers forming the drains D of the transistors in the transistor groups are extended downward, and the lower ends of these layers and a P-type diffused layer extended horizontally form load resistance transistors L<sub>0</sub> through L<sub>63</sub>. The drains D and the gates G of the load resistance transistors are connected to terminals  $V_{DD}$  (-16V) and  $V_{GG}$ (-26V) of the power source and a negative voltage (approximately - 16V) is supplied to the drains D of the transistor groups.

Six-bit address inputs A1 through A6 to the decoder section 5, as is apparent from FIG. 2, are applied to address input terminals AD1 through AD6 from an address signal generator constituted by a clock pulse generator 20 and a binary counter 21. These binary coded address inputs A<sub>1</sub> through A<sub>6</sub> are applied, together with address inversion inputs  $\overline{A_1}$  through  $\overline{A_6}$  which are ob-

tained by inverting the address inputs A1 through A6 in address inverters IN1 through IN6, to address input connection points  $J_1$  and  $\overline{J_1}$  through  $J_6$  and  $J_6$  provided on metal connection layers which are connected to the gates G of transistors provided for the first bit through the sixth bit in the decoder section 5.

In the case where a tone waveform shown in FIG. 4 is produced the gates G of the transistors for the first bit through the sixth bit in the transistor groups T<sub>0</sub> through T<sub>63</sub> of the decoder section 5 are connected to address input connection points predetermined out of the address input connecting points  $J_1$  or  $\overline{J_1}$  through  $J_6$ or  $\overline{J_6}$  as is indicated in FIGS. 6(a), 6(b) and 6(c) as a result of which the transistor groups T<sub>0</sub> through T<sub>63</sub> in the decoder section 5 and accordingly their driving output terminals Q<sub>0</sub> through Q<sub>63</sub> are disposed in the order described from the left to the right so as to be connected to the gate terminals Q<sub>0</sub> through Q<sub>63</sub> of the transistors in FIG. 3.

When address inputs A<sub>1</sub> through A<sub>6</sub> having codes as shown in FIGS. 7(a), 7(b) and 7(c) are applied to the address input terminals AD1 through AD6 in the decoder section 5 sequentially at the time instants  $t_0$ through  $t_{63}$ , an input of logic "0" is applied to the gates of transistors T<sub>631</sub> through T<sub>636</sub> in the transistor group T<sub>63</sub>, as a result of which a negative voltage (-16V) obtained by the transistor L<sub>63</sub>is applied to the connection point  $Q_{63}$  at the time instant  $t_0$  thereby allowing the output transistor U<sub>63</sub> to turn on, or to become conductive. Through this transistor  $U_{63}$ , a voltage (-4.00V) at the connection point  $V_{80}$  in the amplitude memory section 2 is introduced to the output terminal OUT.

Thereafter, an input of logic 0 is applied to the gates of the transistors T<sub>581</sub> through T<sub>586</sub> in the transistor group T<sub>58</sub> in the decoder section 5 at the time instant  $t_1$  and a negative voltage is applied to the connecting point  $Q_{58}$ , as a result of which a voltage (-3.4V) at the connection point V<sub>69</sub> in the amplitude memory section 2 is introduced to the output terminal OUT.

Similarly as in the cases described, the output transistors corresponding to the sampled amplitudes to be read are sequentially addressed by the address inputs applied to the decoder section 5 and the voltages at the connection points, in the amplitude memory section 2 which are connected to the transistors are sequentially introduced to the output terminal OUT. For instance, at the time instance t<sub>14</sub> the output transistor U<sub>6</sub> is addressed whereby a voltage (-0.55V) at the connecting point V<sub>11</sub> is introduced to the output terminal OUT, and at the time instant  $t_{63}$  the output transistor  $U_{62}$  is addressed whereby a voltage (-3.95V) at the connecting point  $V_{79}$  is introduced to the output terminal OUT.

As is apparent from the above description, according to this invention, only by determining the sequence for addressing a plurality of switching transistors connected to the connection points on the diffused resistance layers, desired analog waveforms can be produced. Furthermore, since the diffused resistance layer formed into one unit with the connection points provided at equal voltage intervals is employed as the amplitude memory section, it follows that the space occupied by the amplitude memory section in the semiconductor substrate can be reduced. Accordingly, the size of the semiconductor substrate in this invention can be made much smaller than that of the conventional waveform producing device in which a plurality of diffused resistance layers are employed.

Furthermore, it should be noted that in this invention the production of waveforms can be carried out by the provision of only one diffused layer resistor in the waveform memory section 2, and therefore power consumption in the waveform producing device of the invention is also much less than that in the conventional one.

In addition, in this invention since the output voltages from the amplitude memory section 2 are produced on the basis of the resistance ratios with respect to the 10 whole resistance value of the diffused resistance layers formed into one unit, even if a process of diffusion were varied in a mass production of the waveform producing devices according to this invention, the variation would not appear as fluctuation in the output voltages of the 15 amplitude memory section 2. Accordingly, the waveform producing device according to the invention can carry out reproduction of waveforms with high accuracy. On the other hand, in the conventional waveform generating device described above, a waveform is 20 stored as resistance values of the diffused resistance layers, the fluctuation in the process of diffusion will result in fluctuation in the regeneration of the waveforms. In contrast, such a result is not caused in the device of this invention.

Furthermore, according to this invention, production of other different waveforms can be achieved by changing the binary coded input signals and controlling, or turning on, the switching transistors with a different addressing sequence, and no other change is necessary. However, for the same purpose a wiring pattern of the connection layers  $n_0$  through  $n_{63}$  which adapted to connect the connection points  $V_0$  through  $V_{80}$  to the connection points  $P_0$  through  $P_{63}$  may be changed.

Furthermore, in the device according to this invention, since the connection layers of the metal wiring section 3 are not crossed with each other, the manufacturing of the device is much simpler.

Incidentally, in the case where a section for generating envelope waveforms for electronic musical instruments is practised in the form of a semiconductor integrated circuit, there are some difficulties as follows. That is, in general, there are three types of envelope waveforms: the first one, as is shown in FIG. 8(A), is a waveform consisting of a waveform portion a which abruptly rises at the time instant  $t_a$  (hereinafter referred to as "an attack waveform portion of a"), a waveform portion b (hereinafter referred to as "a sustain waveform portion b") which maintains a substantially certain amplitude, a waveform portion c (hereinafter referred to as "a decay waveform portion c") which starts logarithmically decaying at the time instant  $t_c$ , a tone having the first envelope waveform being a so-called sustain tone; the second envelope waveform is one in which the trailing edge of its attack waveform portion a falls once as is shown in FIG. 8(b), a tone having the second envelope waveform being a so-called attack-sustain tone; and the third envelope waveform is one which abruptly rises and immediately after this rise falls, that is, it has no sustain waveform portion b, as is shown in FIG. 8(c), a tone having the third envelope waveform being a so-called percussive tone.

In this connection, there has been a demand for an envelope waveform producing device which can produce such a waveform logarithmically decaying as the decay waveform portion c and such a waveform

abruptly rising as the attack waveform portion a. Furthermore, there has been a demand for an envelope waveform producing device which is small in size, low in power consumption and simple in manufacture.

In order to satisfy these demands, there is shown a second example of the wavefrom generating device, according to this invention, with reference to FIG. 9 which comprises an N-type semiconductor substrate 1, an envelope generating section 2, a metal wiring section 3, a reading switch section 4 and a decoder section 5, these sections being disposed one after another from the upper portion of the substrate 1 to the lower portion.

As is shown in FIG. 10, the amplitude generating section 2 comprises a belt-shaped section of a P-type diffused resistance layer 2a extended horizontally, and Ptype diffused resistance layers 2b and 2c extended vertically on the both sides of the layer 2a. The P-type diffused resistance layers 2b and 2c are connected through metal connection layers 11a and 11b to the left end and right end of the P-type diffused resistance layer 2a, respectively, to form a series of diffused resistance layers. That is, one resistor comprising resistors  $r_1$ through  $r_{80}$  and having an equal resistance per unit length is formed as is shown in FIG. 11 illustrating an equivalent circuit of the second device. On the resistance layers 2a, 2b and 2c thus formed into one unit, there are provided 81 connection points V<sub>0</sub> and V<sub>1</sub>  $_{30}$  through  $V_{80}$  at equal intervals.

Furthermore, there are provided P-type diffused resistance layers extended downward like legs of the resistance layer 2a (hereinafter referred to as "resistance layer legs" when applicable) from some of the connection points which are located at predetermined intervals on the resistance layer 2a, and the lower ends of these resistance layer legs are provided with connection points, respectively. More specifically, in FIG. 10, 16 resistance layer legs  $M_{10}$ ,  $M_{14}$  - - -  $M_{66}$  and  $M_{70}$  are extended from the connection points  $V_{10}$ ,  $V_{14}$  - - -  $V_{66}$  and  $V_{70}$  which are located at every fourth connection point of the connection points  $V_{9}$  through  $V_{70}$  on the resistance layer 2a.

A predetermined connection point ( $V_{58}$  in the second device shown in FIG. 10) on the resistance layer 2a is connected a terminal Vin (-4V) of a power source, while the connection points  $V_0$  and  $V_{80}$  located at the end portions of the resistance layers 2b and 2c are connected to a ground terminal GND (OV) of the power source. Connection points  $m_{56}$  - - -  $m_{10}$  are provided respectively on the lower ends of the resistance layer legs  $M_{56}$  - - -  $M_{10}$  which are disposed on the left side of the connection position  $V_{58}$ . The connection points  $m_{56}$  - -  $m_{10}$  thus provided are connected to a common connection layer 12 extended horizontally. This connection layer 12 is connected to the connection point  $V_0$  on the resistance layer 2b.

Thus, at the connection points on the resistance layers 2a and 2c on the right side of the connection point  $V_{58}$  voltages corresponding to the resistance ratios of the resistances from the points  $V_{80}$  to these connection points to the whole resistance from the point  $V_{58}$  to the point  $V_{80}$  can be obtained. The differences between the voltages thus obtained are the same, namely, (4V/24 = 0.166V), that is the voltages thus obtained are in a linear relationship. Therefore, they can be employed for the production of an attack waveform.

For each of the resistance layer legs  $M_{56}$  - - -  $M_{10}$  of the resistance layer 2a on the left side of the connection point  $V_{58}$ , a T-type resistance attenuator unit is formed. These attenuator units forms a ladder-type network as is shown in FIG. 11.

In this unit, it is assumed that, as is shown in FIG. 12, resistance of the resistance layer leg is indicated by R, the whole resistance between two connection points which are the second connection points from the connection point of the resistance layer leg R is indicated by r, a damping coefficient n is 4dB (n = 4dB), and the following equation (1) is attained:

$$\frac{R}{r} = \frac{k}{(k-1)^2} = 4.6327$$

where  $k = 10^{20}$   $\frac{n}{} = 10^{0.2} = 1.5849$

Then, at the connection points, voltages differing by 20 substantially 1 dB in attenuation from one another can be obtained.

An image impedance  $Z_0$  of this unit can be obtained by the following equation (2):

$$Z_o = \frac{2k}{k^2 - 1} r = 2.096 r \tag{2}$$

In this second device, the resistance layer 2b forms the terminal resistance of the attenuator. In the above equations, preferable values of the factors are as follows: n=4dB; r = 780 $\Omega$ ; R = 3610 $\Omega$ ;  $Z_o$  = 1634 $\Omega$ ; and k = 1.5849.

The voltages thus obtained at the connection points  $V_{58}$  through  $V_8$  on the resistance layer 2a are in a logarithmical relationship and can be utilized for the production of a decay waveform. In addition, in this second device, voltages which differ by a certain voltage from one another are obtained at the connection points on the resistance layer 2b forming the terminal resistance and may therefore be utilized for the production of the ending portion of a decay envelope waveform.

Similarly as in FIG. 3, the waveform output section 4 is constituted by, for instance, 64 MOS output switching transistors and operates in the same manner.

The metal wiring sections 3 comprises metal wiring connection layers  $n_0$  and  $n_1$  through  $n_{63}$  for connecting the connection points,  $P_0$  and  $P_1$  through  $P_{63}$  to connection points, predetermined according to an output waveform, out of the connection points  $V_{80}$  through  $V_0$ , respectively in the order described. In this connection, it should be noted that these metal wiring connection layers are arranged in such a manner that they are not crossed with each other, and some of them are formed over the resistance layer legs  $M_{56}$  - - -  $M_{10}$  through insulating films. This arrangement of the connection layers contribute to economization in size of the semiconductor substrate.

Incidentally, in FIG. 13, the attack envelope portion a of the sustain tone in FIG. 8(A) is indicated by a curve I with a vertical axis of a linear scale, while the decay envelope is indicated by a curved II with a vertical axis of a dB scale. Furthermore, the connection points  $P_0$ ,  $P_1$  through  $P_{14}$ ,  $P_{16}$  and  $P_{17}$  through  $P_{63}$  are assigned to the sampling time instants  $t_0$  and  $t_1$  through  $t_{63}$  on the horizontal axis of FIG. 13, respectively, while

the voltages at the connection points  $V_{80}$ ,  $V_{76}$  through  $V_{59}$ ,  $V_{58}$ , and  $V_{57}$  through  $V_0$  are taken as amplitude voltages on the vertical axes in FIG. 13.

The decoder section 5 operates to respectively address the output transistors corresponding to the sampled voltages to be read at the time instants  $t_0$  and  $t_1$  through  $t_{63}$ . The decoder section 5 in the second device of this invention is of a 6-binary-input and 64-individual-output type which comprises 64 transistor groups each consisting of six MOS transistors representing a 6-bit address as was described with reference to FIG. 5, and the decoder section operates in the same manner as was described before.

In the decoder section 5 thus organized, when the ad-15 dress inputs A<sub>1</sub> through A<sub>6</sub> having the codes as indicated in FIGS. 7(a), 7(b) and 7(c) are sequentially applied to the address input terminals AD<sub>1</sub> through AD<sub>6</sub> at the time instants  $t_0$  through  $t_{63}$ , an input of logic 0 is applied to the gates of the transistors  $T_{01}$  through  $T_{06}$  in the decoder section 5 at the time instant  $t_0$ , as a result of which a negative voltage (-16V) obtained by the transistor L<sub>0</sub> is applied to the connection point Q<sub>0</sub> to turn on, or to make conductive the transistor U<sub>0</sub>. Through the transistor U<sub>0</sub> thus made conductive a voltage (OV) at the connection point V<sub>80</sub> in the amplitude memory section 2 is introduced to the output terminal OUT. Similarly as in the case described above, voltages at the connection points connected to the connection layers  $n_1$  through  $n_{63}$  in the amplitude memory section 2 are sequentially introduced to the output termin<sup>2</sup> OUT.

Thus, the attack waveform portion I (in FIG. 13) corresponding to the variation of potentials at the connection points  $V_{80}$  through  $V_{58}$  is obtained during the period of from the time instant  $t_0$  to the time instant  $t_{15}$ . Furthermore, the decay waveform portion II' logarithmically decaying in correspondence to the variation of potentials at the connection points  $V_{56}$  through  $V_8$  and the decay waveform portion II'' are obtained during the period of from the time instant  $t_{15}$  to the time instant  $t_{25}$ .

Accordingly, if after the attack waveform has been read, the sustain waveform is obtained with the aid of a constant voltage source separately provided and succeedingly the decay waveform portion is obtained, then such an envelope waveform as indicated in FIG. 8(A) can be obtained.

As is apparent from the above descriptions, according to this invention, the metal wiring section 3 is formed, on the basis of the amplitude voltages forming an envelope waveform to be produced, between the reading switch section 4 and the amplitude memory section 2, and a desired waveform output can be obtained by controlling the operation of the output switching transistors, or turning on the output switching transistors, in a predetermined sequence by combining the belt-shaped section of the diffused resistance layer and the diffused resistance legs extended from the belt-shaped section leads to the production of a logarithmically decaying curve effective as a decay envelope.

The above descriptions are for the production of the sustain tone shown in FIG. 8(A).

The attack-sustain tone as shown in FIG. 8(B) can be obtained by producing an attack envelope curve I and a decay envelope curve II as shown in FIG. 14 instead of those shown in FIG. 13, while the percussive tone as

shown in FIG. 8(C) can be obtained by producing only a decay envelope curve II as shown in FIG. 15. The envelope form shown in FIG. 15 has no attack portion, and it can therefore obtained by connecting the common connection layer 12 of the amplitude memory 5 layer 2 to all of the diffused resistance legs and by connecting the terminal Vin of the power source to the connection point  $V_{72}$ . Thus, various envelope shapes can be obtained by changing the wiring pattern in the wiring section 3 or by changing the addressing se- 10 quence of the output transistors  $U_0$  through  $U_{63}$ .

With reference to FIG. 16, there is shown a third example of the waveform producing device according to this invention, which comprises an N-type semiconductor substrate 1, an amplitude memory section 2, a metal wiring section 3, a reading switch section 4 and a decoder section 5, to produce a logarithmically decaying

envelope.

The amplitude memory section 2 comprises a belt-shaped section of a P-type diffused resistance layer 2a 20 extended horizontally, and a P-type diffused resistance layer 2b extended vertically at the left side of the diffused resistance layer 2a. The left end of the diffused resistance layer 2a is connected through a metal connection layer 11a to the upper end of the diffused resistance layer 2b. There is, these layers 2a and 2b are formed into one unit, or one resistor consisting of resistors  $r_1$  through  $r_{72}$  and having an equal resistance per unit length. Furthermore, for instance 73 connection points  $V_0$ ,  $V_1$  and  $V_2$  through  $V_{72}$  are provided at equal intervals on the resistance layers 2a and 2b formed into one unit.

P-type diffused resistance layers like legs of the resistance layer 2a (hereinafter to as "resistance layer legs" when applicable) are extend downward from some of the connection points which are located at predetermined intervals on the resistance layer 2a. More specifically, in FIG. 16, 16 resistance layer legs  $M_{10}$ ,  $M_{14}$  - - - -  $M_{66}$ , and  $M_{70}$  are extended downward from the connection points  $V_{10}$ ,  $V_{14}$  - - -  $V_{66}$  and  $V_{70}$  which are located at every fourth connection point of the connection points  $V_{10}$  through  $V_{70}$ .

The lower ends with connection points  $m_{70}$  - - -  $m_{10}$  of the resistance layer legs  $M_{70}$  - - -  $M_{10}$  are extended to a common connection layer 12 which is extended horizontally below the amplitude memory section 2, but, out of the connection points  $m_{70}$  - - -  $m_{10}$ , connection points determined according to a waveform to be generated are connected to the common connection layer 12. More specifically, in FIG. 16, every other connection point of the connection points  $m_{70}$  - - -  $m_{10}$ , namely, the connection points  $m_{70}$ ,  $m_{62}$ ,  $m_{54}$  - - -  $m_{14}$  are connected to the common connection layer 12.

Furthermore, adjacent connection points  $V_{72}$  and  $V_{71}$ ,  $V_{70}$  and  $V_{69}$ ,  $V_{68}$  and  $V_{67}$ , - - -  $V_{10}$  and  $V_{9}$  on the resistance layer 2a are short-circuited by connection layers  $Y_{72}$ ,  $Y_{70}$ ,  $Y_{68}$  - - -  $Y_{10}$ , respectively.

The connection points  $V_{72}$  and  $V_0$  on the ends of the resistance layers 2a and 2b are connected to terminals Vin (-4V) and GND (OV) of a power source, respectively, and the common connection layer 12 is connected to the terminal GND. Thus, the resistance layer 2a, the resistance layer legs  $M_{70}$ ,  $M_{62}$ ,  $M_{54}$  - - -  $M_{14}$  and the common connecton layer 12 form a ladder type network, whereby a T-type resistance attenuation unit K is formed for each of the resistance layers  $M_{70}$ ,  $M_{62}$ ,  $M_{54}$  - - -  $M_{14}$ . In this unit K, if it is assumed that, as is

shown in FIG 18, resistance of a resistance layer leg (for instance  $M_{54}$ ) is represented by R, the whole resistance between two connection points ( $V_{50}$  and  $V_{58}$ ) which are the second connection points from the connection point (V<sub>54</sub>) of the resistance layer leg is represented by r, and a damping coefficient n is 4dB, then the relation between resistances R and r can be represented by equation (1) previously described, and at the connection points ( $V_{58}$ ,  $V_{56}$ ,  $V_{54}$ ,  $V_{52}$  and  $V_{50}$ ) located at every other connection point voltages differing by substantially 1 dB in attenuation from one another can be obtained. An image impedance Zo of this unit K can be obtained from equation (2) previously described. In this example, the resistance layer 2b is the terminal resistance of the attenuator. In the above equations (1) and (2), preferable values of the factors are as follows: n = 4dB;  $r = 780 \Omega R = 3610 \Omega$ ;  $Z_0 = 1634 \Omega$ ; and k =1.5849.

Thus, the voltages obtained at the connection point  $V_{72}$ ,  $V_{70}$ ,  $V_{68}$  - - -  $V_{10}$  located at every other connection point are in a logarithmic relation.

The reading switch section 4 is constituted by, for instance, 64 MOS output transistors and operates similarly as in FIG. 3.

The metal wiring section 3 comprises metal wiring connection layers for connecting the connecton points Po and P1 through P63 of the transistors in the reading switch section 4 to connection points, predetermined according to a waveform to be generated, out of the connection points V<sub>72</sub> through V<sub>8</sub> on the resistance layer 2a, respectively in the order described. In this third example of this invention, as is shown in FIG. 16, adjacent two connection points Po and P1, P2 and P3, P4 and  $P_5$  - - -  $P_{62}$  and  $P_{63}$  are short-circuited by connection layers  $Z_0$ ,  $Z_2$ ,  $Z_4$  - - -  $Z_{62}$ , respectively. Furthermore, the connection points P<sub>0</sub> and P<sub>1</sub>, P<sub>2</sub> and P<sub>3</sub>, --- P<sub>62</sub> and P<sub>63</sub> are connected through connection layers  $n_0$ ,  $n_2$  - - -  $n_{62}$ to the connection points  $V_{72}$  and  $V_{71}$ ,  $V_{70}$  and  $V_{69}$ , ---  $V_{10}$  and  $V_9$ , respectively. Thus, connection layers  $n_0$ through  $n_{62}$  are laid over the resistance layer legs  $M_{70}$ through M<sub>10</sub>, but are not crossed with each other.

The decoder section 5 is to respectively address the output transistors corresponding to the voltages to read at the time instants  $t_0$  and  $t_1$  through  $t_{63}$ . The decoder section 5 in the third example of this invention is also of a 6-binary-input and 64-individual-output type which comprises 64 transistor groups each consisting of six MOS transistors provided for a six-bit address as was described previously with reference to FIG. 5 and the decoder section 5 thus organized operates in the same manner as described previously.

In the decoder section 5 thus organized, when the address inputs  $A_1$  through  $A_6$  are sequentially applied to the address input terminals  $AD_1$  through  $AD_6$  at the time instants  $t_0$  through  $t_{63}$ , an input of logic 0 is applied to the gates of the transistors  $T_{01}$  through  $T_{06}$  in the transistor group  $T_0$  of the decoder section 5 at the time instant  $t_0$ , as a result of which a negative voltage (-16V) obtained by the transistor  $L_0$  is applied to the connection point  $Q_0$  to turn on, or to make conductive, the transistor  $U_0$ . Through the transistor  $U_0$  thus made to be conductive, a voltage (-4.00V) at the connection points  $V_{72}$  and  $V_{71}$  in the amplitude memory section 2 is introduced to the output terminal OUT. Similarly as in the operation described above, voltages at the connection points connects to the connection layers  $n_2$

through  $n_{62}$  in the amplitude memory section 2 are sequentially introduced to the output terminal OUT.

Thus, an output voltage of a decay waveform decaying at a substantially certain inclination from 0 dB to -30dB on a logarithmical scale is produced as indicated in FIG. 19.

Incidentally, it is assumed that in FIG. 16 the shorting connection layers  $Y_{72}$ ,  $Y_{70}$  - - -  $Y_{10}$  and  $Z_0$ ,  $Z_2$  - - - -  $Z_{62}$ are omitted, the connection points P<sub>0</sub>, and P<sub>1</sub> through  $P_{63}$  are connected to the connection points  $V_{72}$ , and  $V_{71}$  10 through V<sub>8</sub> through metal wiring connection layers, respectively, and all of the connection points  $m_{70}$ ,  $m_{66}$  - $--m_{10}$  on the resistance layer legs are connected to the common connection layer 12. As a result, the resistance attenuator unit K shown in FIG. 18 is formed for 15 each of the resistance layers M<sub>70</sub>, M<sub>66</sub> - - - M<sub>10</sub> as is shown in FIG. 20(B). As is apparent from the comparison of the circuit shown in FIG. 20(B) with that shown in FIG. 20(A) which is an equivalent circuit of the attenuation network in the third device of this invention 20 shown in FIG. 16, an attenuation quantity by the circuit in FIG. 20(B) is twice as much as that by the circuit in FIG. 20(A), during the period of the time instant  $t_0$  to the time instant  $t_{63}$ . Accordingly, a decay envelope from 0 dB to -60dB at an inclination twice as much as that of a curve shown in FIG. 19.

On the other hand, if in FIG. 16 the connection points V<sub>72</sub> through V<sub>8</sub> are divided into connection point groups each consisting of adjacent four connection points and in each of the connection point groups its first connection point is connected to its fourth connection point, and furthermore connection points located at every fourth connection point out of the connection points  $m_{70}$  - - -  $m_{10}$  on the resistance layer legs  $M_{70}$  - -- M<sub>10</sub> are connected to the common connection layer 12, then the resistance attenuation unit K shown in FIG. 18 is formed for every four resistance layer legs as is shown in FIG. 20(C). Accordingly, for the period of from the time instant  $t_0$  to the time instant  $t_{63}$  an attenuation quantity by the circuit shown in FIG. 20(C) is half that by the circuit shown in FIG. 20(A) which is the equivalent circuit of the attenuator units for the device shown in FIG. 16. Accordingly, a decay envelope shape obtained at the output terminal OUT decays from 0 dB 45 to -15dB at an inclination which is half that of the curve shown in FIG. 19.

As is apparent from the descriptions on the third device of this invention described above, a logarithmically decaying waveform can be produced as desired by selectively shorting the connection points on the diffused resistance layer 2a in the amplitude generating section 2 and by selectively connecting the resistance layer legs to the common connection layer 12.

While there has been described in connection with the example where an envelope decaying at a substantially, certain inclination is produced as is shown in FIG. 9, such an example can be effectively practised in a touch-responsive decay envelope producing device in electronic musical instruments.

In this example, if the amplitude memory section is rearranged so that an attenuation quantity per unit reading time interval is changed at a predetermined reading time instant, a device for producing a logarithmically decaying waveform which consists of decay curves having different inclinations can be provided. Such a device can be applied to a device for producing

14

an envelope shape of a percussive tone in electronic musical instruments. Furthermore, this invention can be effectively applied to a device for producing a logarithmical waveform.

It can be easily understood that the waveform producing devices described as the second and the third example of this invention can also provide advantages such as those provided by the device described as the first example.

In the above descriptions, the output transistors  $U_0$  through  $U_{63}$  in the decoder section 5 are addressed in the order described, but the order of addressing the output transistors may be changed as required. Furthermore, the pattern of the metal wiring section is not limitative to the example described above, that is, it may be changed in such a manner that some of the connection layers are crossed with each other.

Moreover, the above description, the MOS integrated circuit comprising MOS transistors has been disclosed, but these MOS transistors may be replaced by bipolar type transistors. In addition, a P-type semiconductor substrate can be employed as the semiconductor substrate 1.

the time instant  $t_{63}$ . Accordingly, a decay envelope shape obtained at the output terminal OUT decays from 0 dB to -60dB at an inclination twice as much as that of a curve shown in FIG. 19.

On the other hand, if in FIG. 16 the connection points  $V_{72}$  through  $V_{8}$  are divided into connection points groups each consisting of adjacent four connection points and in each of the connection point groups its

Furthermore, in the above descriptions, the amplitude memory section 2 has a pattern like a character "U" by connecting three diffused resistance layers 2a, 2b and 2c into one unit; however, this pattern and the number of the diffused resistance layers may be changed suitably as required. For instance, the amplitude generating section 2 may be formed by one belt-shaped resistance layer 2a only without the resistance layer 2b and 2c.

We claim:

- 1. A waveform producing device which comprises,

- a. a resistor zone of a diffused layer formed on a semiconductor substrate and having a plurality of connection points,

- b. means for applying a predetermined voltage across the resistor zone so that different potentials appear at the respective connection points, and

- c. a reading circuit for reading the different potentials at the connection points in a predetermined order, so that a waveform having variation of amplitudes corresponding to variation of the potentials at the connection points thus read is produced.

- 2. A waveform producing device as claimed in claim 1 in which said reading circuit comprises

- a. a read-out switching circuit having a plurality of switching transistors with input terminals connected to said connection points and with a common output terminal, and

- b. an addressing circuit for turning on the switching transistors in a predetermined order according to binary-coded signals to drive the switching circuit so as to produce said waveform at the common output terminal.

- 3. A waveform producing device as claimed in claim

2 in which said switching transistors are MOS transistors, said addressing circuit includes a decoder formed

by a plurality of MOS transistors, said switching circuit and the decoder together with said diffused resistance layer being combined in an integrated structure on said semiconductor substrate.

4. A waveform producing device as claimed in claim 5 1 in which said voltage is applied through at least one resistor to the connection points on said diffused resistance layer.

5. A waveform producing device as claimed in claim 4 in which said resistor is a diffused resistance layer 10 formed on said semiconductor substrate.

6. A waveform producing device as claimed in claim

4 in which a connection point connected with said resistor is shorted by another connection point.

7. A waveform producing device as claimed in claim 4 in which connection points to which said resistor is not connected are connected to each other.

8. A waveform producing device as claimed in claim 1 in which said voltage is applied to said diffused resistance layer through a resistor for every predetermined number of connection points and a multiple T-type attenuation circuit is formed.

15

20

25

30

35

40

45

50

55