#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

## (19) World Intellectual Property **Organization**

International Bureau

(10) International Publication Number WO 2017/189367 A1

# (51) International Patent Classification:

H05K 1/18 (2006.01) H01L 21/48 (2006.01) H01L 23/52 (2006.01) H05K 3/30 (2006.01) H01P 5/04 (2006.01) H05K 3/40 (2006.01)

(21) International Application Number:

PCT/US2017/028964

(22) International Filing Date:

21 April 2017 (21.04.2017)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

29 April 2016 (29.04.2016) 62/329,301 US

- (71) Applicant: UNIQARTA, INC. [US/US]; 42 Trowbridge Street, Unit 1, Cambridge, Massachusetts 02138 (US).

- (72) Inventor: MARINOV, Val; 95 S Woodcrest Dr N, Fargo, North Dakota 58102 (US).

- (74) Agent: DEVRIES, Gretchen A. et al.; Fish & Richardson, P.C., P.O. Box 1022, Minneapolis, Minnesota 55440-1022 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DJ, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, JP, KE, KG, KH, KN, KP, KR, KW, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME, MG,

MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

#### **Declarations under Rule 4.17:**

as to the applicant's entitlement to claim the priority of the earlier application (Rule 4.17(iii))

#### **Published:**

- with international search report (Art. 21(3))

- before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments (Rule 48.2(h))

### (54) Title: CONNECTING ELECTRONIC COMPONENTS TO SUBSTRATES

(57) Abstract: An apparatus includes a first substrate including one or more electrical connection features; and an assembly including: a second substrate; conductive features formed on the second substrate, one or more of which are electrically connected to corresponding electrical connection features of the first substrate; and an electronic component between the second substrate and the first substrate and electrically connected to one or more of the conductive features.

## CONNECTING ELECTRONIC COMPONENTS TO SUBSTRATES

# Claim of Priority

[001] This application claims priority to U.S. Patent Application Serial No. 62/329,301, filed on April 29, 2016, the entire contents of which are incorporated here by reference.

# **Background**

[002] Discrete components including integrated circuits are packaged for use in various applications. Packaging a discrete component includes electrically connecting the discrete component to a substrate, such as a printed circuit board.

10 <u>Summary</u>

5

15

20

25

[003] In an aspect, an apparatus includes a first substrate including one or more electrical connection features; and an assembly including a second substrate; conductive features in contact with the second substrate, one or more of which are electrically connected to corresponding electrical connection features of the first substrate; and an electronic component between the second substrate and the first substrate and electrically connected to one or more of the conductive features. A separation between the first substrate and the second substrate is 500 µm or less.

[004] Embodiments can include one or more of the following features.

[005] The assembly includes multiple electronic components between the second substrate and the first substrate. The electronic component includes a discrete component. The electronic component includes one or more of a sensor, a MEMS device, an LED, a power source, a chemical sensing element, and a biological sensing element. The electronic component is formed on the second substrate. The electronic component is embedded into a body of the second substrate. The apparatus includes a second electronic component embedded within a body of the second substrate. The electronic component is positioned at a first surface of the second substrate, and in which the assembly includes a second electronic component positioned at a second surface of the second substrate, the second surface opposite the first surface. The first substrate includes a circuit board.

[006] The second substrate includes an interposer. The electronic component includes an integrated circuit.

**[007]** The one or more conductive features are formed on a surface of the second substrate. A surface of the first substrate faces the surface of the second substrate on which the conductive features are formed and the electronic component is at least partially within a gap between the two surfaces. The surface of the second substrate on which the one or more conductive features are formed faces the first substrate. The gap between the two surfaces is filled with an encapsulant.

5

10

15

25

30

[008] At least portions of the one or more conductive features are embedded within a body of the interposer.

**[009]** The electronic component includes one or more bond pads, at least one of the bond pads electrically connected to a corresponding one of the conductive features of the second substrate. Each bond pad includes a corresponding bump, and in which the at least one of the bond pads is electrically connected to the corresponding one of the conductive features through the bump. The one or more bond pads are formed on a surface of the electronic component. A surface of the electronic component on which the one or more bond pads are formed faces the second substrate. A pitch of the bond pads of the electronic component is different than a pitch of the electrical connection features of the first substrate.

[010] The electronic component is electrically connected to one or more of the conductive features by an interconnection system. The interconnection system includes a conductive adhesive.

**[011]** Each conductive feature includes a first conductive structure oriented in parallel to a surface of the second substrate and a second conductive structure oriented perpendicular to a surface of the second substrate. The assembly includes an encapsulant layer between the second substrate and the first substrate, and in which the second conductive structures are formed through a thickness of the encapsulant layer. The second conductive structures protrude beyond a bottom surface of the encapsulant layer. The first conductive structures are formed of a different material than the second conductive structures. The first conductive structures include a redistribution structure.

[012] One or more of the conductive features of the second substrate each includes a contact pad connected to a corresponding conductive line. The contact pads are positioned around the edges of the electronic component. The contact pads are arranged

in an array. The contact pads are positioned on one side of the electronic component. One or more of the contact pads is each connected to a corresponding electrode, and in which one or more of the electrodes is each electrically connected to a corresponding one of the electrical connection features of the first substrate. The electrodes include one or more of solder balls, pillars, studs, bumps, pads, and conductive particles. The electronic component has a thickness no greater than the combination of a thickness of the electrodes and a thickness of the electrical connection features of the first substrate.

5

15

20

25

- [013] The apparatus includes an underfill material disposed between the first substrate and the second substrate. The underfill material includes a non-conductive polymer.

- 10 **[014]** The electronic component is encapsulated in an encapsulant. At least a portion of the conductive features is encapsulated in the encapsulant.

- [015] The separation between the first substrate and the second substrate is 200 μm or less, 100 μm or less, or 50 μm or less. The first substrate is 100 μm or less, 50 μm or less, 25 μm or less, or 10 μm or less from a surface of the electronic component facing the first substrate. The first substrate is in physical contact with the surface of the electronic component facing the first substrate.

- [016] The first substrate includes a flexible substrate. The first substrate includes a printed flexible circuit board. The second substrate includes a material that is flexible. The second substrate is stretchable. The one or more conductive features include meandering conductive features. The second substrate includes an elastomeric material. The electronic component includes a material that is flexible. The electronic component has a thickness of less than about 50 μm. The electrical connection features of the first substrate include printed conductors. The apparatus includes an adhesive disposed between the flexible substrate and the assembly. The adhesive includes a conductive adhesive. The adhesive forms a seal around the electronic component. The adhesive includes an anisotropic conductive adhesive. The anisotropic conductive adhesive provides an electrical connection between the conductive features formed on the second substrate and the corresponding electrical connection features of the first substrate.

- [017] The assembly includes second conductive features formed through a thickness of the second substrate, each second conductive feature electrically connected to one of the conductive features. The apparatus includes a second electronic component electrically connected to one or more of the second conductive features, the assembly arranged such that the second substrate is disposed between the electronic component and the second

electronic component. The apparatus includes a second assembly disposed on the second substrate, the second assembly including a third substrate; third conductive features in contact with the third substrate, one or more of which are electrically connected to corresponding second conductive features of the second substrate; and a second electronic component between the third substrate and the second substrate and electrically connected to one or more of the third conductive features.

5

10

15

20

25

**[018]** The apparatus includes a third substrate disposed on the assembly such that the assembly is between the first substrate and the third substrate, the third substrate including one or more second electrical connection features electrically connected to one or more of the electrical connection features of the first substrate. The apparatus includes an adhesive layer between the first substrate and the third substrate, wherein the assembly is at least partially encapsulated in the adhesive layer. The apparatus includes a second electronic component disposed on the third substrate and electrically connected to one or more of the second electrical connection features. The second electrical connection features are formed through a thickness of the third substrate and in which one or more of the electrical connection features of the first substrate are formed through a thickness of the first substrate. A first surface of the first substrate faces the third substrate, and including a second electronic component disposed on a second surface of the first substrate, the second electronic component electrically connected to one or more of the second electrical connection features.

[019] In an aspect, an assembly includes an electronic component having a first surface at which a pattern of electrical connection features are exposed, a substrate having a substrate surface at which a pattern of electrical connection features are exposed, and an interposer including conductors that connect at least some of the electrical connection features of the electronic component with at least some of the electrical connection features of the substrate, with the electronic component in a space between the interposer and the substrate and the first surface of the electronic component not facing the substrate surface. A second surface of the electronic component is  $100 \, \mu m$  or less from the surface of the substrate.

30 **[020]** Embodiments can include one or more of the following features.

**[021]** The electronic component includes an integrated circuit. The conductors are exposed on a surface of the interposer, and in which the surface of the interposer faces the substrate surface. The conductors are electrically connected with the electrical connection features of the electronic component through an interconnection system. Each

conductor includes a first conductive feature in physical and electrical contact with the interconnection system and a second conductive feature connecting the first conductive feature to an electrical connection feature of the substrate.

[022] One or more of the conductors of the interposer is each connected to a corresponding electrode that electrically connects the conductor to a corresponding electrical connection feature of the substrate. The electrodes include one or more of solder balls, pillars, studs, bumps, pads, and conductive particles. The electronic component has a thickness that is no greater than the combination of a thickness of the electrodes and a thickness of the electrical connection features of the substrate.

5

15

20

- 10 **[023]** The substrate includes a material that is flexible. The substrate includes an elastomeric material. The substrate is stretchable. The conductors of the interposer include meandering conductors.

- [024] The second surface of the electronic component is 50  $\mu$ m or less, 25  $\mu$ m or less, or 10  $\mu$ m or less from the surface of the substrate. The second surface of the electronic component is in physical contact with the surface of the substrate. A separation between the substrate and the interposer is 500  $\mu$ m or less, 200  $\mu$ m or less, 100  $\mu$ m or less, or 50  $\mu$ m or less.

- **[025]** In an aspect, a method includes electrically connecting an electronic component to one or more conductive features formed on a second substrate; disposing the second substrate on a surface of a first substrate, including positioning the electronic component between the first substrate and the second substrate, in which a separation between the second substrate and the surface of the first substrate is  $500 \, \mu m$  or less; and electrically connecting one or more of the conductive features of the second substrate each to a corresponding electrical connection feature of the first substrate.

- 25 **[026]** Embodiments can include one or more of the following features.

- **[027]** Electrically connecting the electronic component includes electrically connecting one or more bond pads of the electronic component each to a corresponding one of the conductive features. Positioning the electronic component between the first substrate and the second substrate includes positioning the electronic component such that a surface including the bond pads faces away from the second substrate.

- [028] Electrically connecting the one or more conductive features each to a corresponding electrical connection feature includes applying a stimulus to an adhesive

disposed between the first substrate and the second substrate. Applying the stimulus includes applying heat or light. The adhesive includes a conductive adhesive.

[029] The method includes bonding the first substrate to the second substrate. The method includes curing an adhesive disposed between the first substrate and the second substrate.

- [030] The first substrate includes a printed circuit board. The first substrate includes a printed flexible circuit board. The second substrate includes an interposer. The electronic component has a thickness that is no greater than the combination of a thickness of the electrodes and a thickness of the electrical contacts of the first substrate.

- [031] In an aspect, a method includes disposing one or more electronic components on a first surface of an interposer substrate, in which one or more sets of conductive features are formed on the first surface of the interposer substrate and extend away from the interposer substrate, in which each conductive feature extends to a height of 500 μm or less from the first surface of the interposer substrate, and in which the height of the conductive features is greater than or equal to a height of the electronic components; electrically connecting each electronic component to a corresponding set of conductive features; and separating the interposer substrate into multiple packages, each package including a portion of the interposer substrate, one or more of the electronic components, and the corresponding set of conductive features.

- 20 **[032]** Embodiments can include one or more of the following features.

- [033] Each conductive feature extends to a height of 200  $\mu$ m or less, 100  $\mu$ m or less, or 50  $\mu$ m or less from the first surface of the interposer substrate. The conductive features are not formed through a thickness of the interposer substrate.

- [034] Separating the interposer substrate into multiple packages includes dicing the interposer substrate. The method includes attaching the interposer substrate to a support substrate. Dicing the interposer substrate into multiple packages includes dicing the support substrate such that each package includes a portion of the support substrate. The method includes attaching the interposer substrate to the support substrate with a temporary bonding material.

- [035] The method includes connecting one of the packages to a device substrate such that at least one of the electronic components of the package is disposed between the interposer substrate and the device substrate. Connecting the package to the device

substrate includes electrically connecting the conductive features of the package to respective electrical connection features of the device substrate. Connecting the package to the device substrate includes orienting the package such that the electronic component is between the interposer substrate and the device substrate.

- 5 **[036]** The method includes forming molded layer on the surface of the interposer substrate, the molded layer including an encapsulant at least partially covering the electronic components and sets of conductive features. The method includes thinning the molded layer to expose ends of the conductive features. The electronic components include ultra-thin electronic components.

- [037] In an aspect, a method includes forming one or more interconnection structures on an interposer substrate, including connecting a first end of each of one or more interconnection structures to corresponding conductive features on a surface of an interposer substrate, in which an electronic component disposed on the surface of the interposer substrate is electrically connected to one or more of the conductive features,

and in which a second surface of the electronic component and a second end of each of the interconnection structures are less than 500 μm from the surface of the interposer substrate; disposing the interposer substrate on a device substrate, including positioning the electronic component between the interposer substrate and the device substrate; and electrically connecting the second end of each of one or more of the interconnection structures to a corresponding electrical connection feature of the device substrate.

- [038] In an aspect, an apparatus includes a substrate; conductive features formed on a surface of the substrate, each conductive feature having a first end and a second end on the first side of the substrate, in which at least a portion each conductive feature extends away from the substrate, in which each conductive feature extends to a height of 500  $\mu m$  or less from the surface of the substrate; an electronic component disposed on the surface of the substrate, one or more connection elements on a first surface of the electronic component each electrically connected to the first end of a corresponding one of the conductive features, in which a second surface of the electronic component is 500  $\mu m$  or less from the surface of the substrate, and in which the height of the conductive features is greater than or equal to the separation between the second surface of the electronic component and the surface of the substrate; and a second end of one or more of the conductive features arranged to each be in electrical contact with a corresponding electrical contact of a circuit board.

[039] Embodiments can include one or more of the following features.

25

**[040]** The second surface of the electronic component is 200 μm or less, 100 μm or less, or 50 μm or less from the surface of the substrate. A separation between the surface of the substrate and the circuit board is 500 μm or less, 200 μm or less, 100 μm or less, or 50 μm or less. The second surface of the electronic component is 100 μm or less, 50 μm or less, 25 μm or less, or 10 μm or less from the circuit board. The second surface of the electronic component is in physical contact with the circuit board.

**[041]** The conductive features are not formed through a thickness of the substrate. The apparatus includes multiple electronic components disposed on the surface of the first side of the substrate. The first ends of the conductive features are electrically connected to the corresponding connection elements of the electronic component through an interconnection system. When the conductive features are in electrical contact with the electrical contacts of the circuit board, the circuit board and the electronic component are both disposed on a same side of the substrate.

10

15

20

25

- [042] The second end of one or more of the conductive features is each in physical contact with a corresponding electrode disposed on the surface of the substrate. The electrodes include one or more of solder balls, pillars, studs, bumps, pads, and conductive particles. The second end of each conductive feature includes a contact pad formed on the surface of the substrate. The second ends of one or more of the conductive features are arranged in an array. The second ends of one or more of the conductive features are positioned around the edges of the electronic component. A pitch of the connection elements of the electronic component is different than a pitch of the electrical contacts of the circuit board.

- **[043]** The apparatus includes a support substrate attached to the substrate such that the substrate is disposed between the electronic component and the support substrate. The support substrate is releasably attached to the substrate. The support substrate is attached to the substrate with a temporary bonding material. The temporary bonding material has an adhesion that changes responsive to application of a stimulus. The substrate includes a material that is flexible. The substrate is stretchable. The electronic component includes a material that is flexible. The apparatus includes an adhesive disposed on the surface of the substrate.

- [044] In an aspect, an assembly includes an interposer substrate, multiple sets of conductive features being formed on a surface of the interposer substrate, in which at least a portion of each conductive feature extends away from the interposer substrate, and in which each conductive feature extends to a height of 500 µm or less from the surface

of the interposer substrate; and multiple electronic components disposed on the surface of the interposer substrate, each electronic component corresponding to one of the multiple sets of conductive features formed on the surface of the interposer substrate, in which, for each electronic component, one or more connection elements on a first surface of the electronic component are each electrically connected to an end of a corresponding one of the conductive features of the corresponding set, in which a second surface of the electronic component is 500 µm or less from the surface of the interposer substrate, and in which the height of the conductive features is greater than or equal to the separation between the second surface of the electronic component and the surface of the interposer substrate.

[045] Embodiments can include one or more of the following features.

5

10

15

20

25

30

**[046]** The assembly includes a support substrate, wherein the interposer substrate is disposed between the support substrate and the multiple electronic components.

**[047]** In an aspect, an apparatus includes a first substrate including one or more electrical connection features; and an assembly including a second substrate; conductive features formed on the second substrate, one or more of which are electrically connected to corresponding electrical connection features of the first substrate; and an electronic component positioned at a surface of the second substrate and electrically connected to one or more of the conductive features, the surface of the second substrate facing the first substrate, in which a separation between the surface of the second substrate and the first substrate is  $500 \ \mu m$  or less.

**[048]** In an aspect, an apparatus includes a first substrate, a first electrical connection feature formed on a surface of the first substrate; and a molded layer including an electronic component and a conductive element encapsulated within a molding material, a second electrical connection feature formed on a surface of the electronic component, the second electrical connection feature of the electronic component being electrically connected to the first electrical connection feature of the first substrate through the conductive element; the surface of the electronic component facing away from the surface of the first substrate.

[049] Embodiments can include one or more of the following features.

[050] The apparatus includes a second substrate attached to the molded layer such that the molded layer is positioned between the first substrate and the second substrate. At least a portion of the conductive element is in physical contact with the surface of the

second substrate. The conductive element includes a first conductive feature and a second conductive feature, the first conductive feature formed along a surface of the second substrate, and the second conductive feature formed through a thickness of the molded layer. The second substrate is releasably attached to the molded layer. The second substrate is attached to the molded layer with a temporary bonding material. The temporary bonding material has an adhesion that changes responsive to application of a stimulus. The second substrate is removable from the molded layer by one or more of wet etching, dry etching, and mechanical removal. The method includes a third substrate attached to the second substrate such that the molded layer and second substrate are positioned between the first substrate and the third substrate. The third substrate is releasably attached to the second substrate. The third substrate is attached to the second substrate with a temporary bonding material. The apparatus includes a second conductive element formed through a thickness of the second substrate and electrically connected to the portion of the conductive element. The apparatus includes a second electronic component electrically connected to the second conductive element, in which the second substrate is disposed between the molded layer and the second electronic component. The apparatus includes a second molded layer disposed such that the molded layer is between the second molded layer and the first substrate, the second molded layer including a second electronic component and a third conductive element encapsulated within a molding material, a third electrical connection feature of the second electronic component formed on a surface of the second electronic component, the third electronic feature of the electronic component being electrically connected to the second conductive element of the second substrate through the third conductive element. The surface of the second electronic component faces away from the first molded layer.

5

10

15

20

25

30

[051] The apparatus includes a second substrate disposed such that the molded layer is between the first substrate and the second substrate, the second substrate including one or more third electrical connection features electrically connected to one or more of the first electrical connection features of the first substrate. The apparatus includes a second electronic component disposed on the second substrate and electrically connected to one or more of the third electrical connection features. The third electrical connection features are formed through a thickness of the second substrate and in which one or more of the first electrical connection features of the first substrate are formed through a thickness of the first substrate are formed through a thickness of the first substrate. The surface of the first substrate faces the second substrate, and including a second electronic component disposed on a second surface of the first

substrate, the second electronic component electrically connected to one or more of the third electrical connection features.

[052] The second electrical connection feature of the electronic component is connected to the conductive element through an interconnection system.

5

10

15

20

25

- [053] The conductive element includes a first conductive element and a second conductive element. The first conductive element is oriented parallel to the molded layer and the second conductive element is oriented perpendicular to the molded layer. A first end of the first conductive feature is in physical contact with an interconnection system that is in contact with the second electrical connection feature of the electronic component, and a second end of the first conductive feature is in physical contact with a first end of the second conductive feature. A second end of the second conductive feature includes an interconnection structure. The interconnection structure includes one or more of solder cap, solder ball, pillar, stud, bump, pad, conductive particle. The interconnection structure includes a conductive adhesive. The interconnection structure is in physical contact with the first electrical connection feature of the first substrate. The second end of the second conductive feature is flush with a bottom surface of the molded layer. The second conductive feature is formed through a thickness of the molded layer. The first conductive feature is exposed on a top surface of the molded layer, the top surface facing away from the first substrate. A top surface of the first conductive feature is coplanar with the top surface of the molded layer. The apparatus includes a second electronic component disposed on the top surface of the molded layer, in which an electrical connection feature of the second electronic component is electrically connected to the exposed first conductive feature.

- [054] The electronic component includes an ultra-thin electronic component. The apparatus includes an underfill in a gap between the molded layer and the first substrate. The apparatus includes an assembly including a second electronic component, the assembly disposed on the molded layer such that the molded layer is positioned between the assembly and the first substrate. The molded layer includes multiple conductive elements, and in which the second electronic component is electrically connected to the first substrate through a conductive element. The molded layer includes multiple electronic components encapsulated within the molding material. The multiple electronic components are disposed between the conductive element and the first substrate.

- [055] In an aspect, an apparatus includes a first substrate; a molded layer disposed on the first substrate such that a first surface of the molded layer is in contact with the first

substrate, the molded layer including an electronic component encapsulated within a molding material, the electronic component having electrical connection features, the electronic connection features facing the first substrate; and conductive elements, each conductive element electrically connected to a corresponding electrical connection feature of the electrical component; in which first ends of the conductive elements are exposed at a second surface of the molded layer and arranged in an arrangement corresponding to an arrangement of electrical contacts of a circuit board.

[056] Embodiments can include one or more of the following features.

10

15

20

25

30

**[057]** The electronic component includes an ultra-thin electronic component. The apparatus includes a second substrate attached to the first substrate such that the first substrate is positioned between the molded layer and the second substrate. The second substrate is releasably attached to the first substrate. The second substrate is attached to the first substrate with a temporary bonding material. The first substrate is releasably attached to the molded layer. The first substrate is removable from the molded layer by one or more of wet etching, dry etching, and mechanical removal. The first substrate is attached to the molded layer with a temporary bonding material.

**[058]** The apparatus includes an interconnection structure in physical and electrical contact with each of the first ends of the conductive elements. The interconnection structure includes one or more of solder cap, solder ball, pillar, stud, bump, pad, and conductive particle. The interconnection structure includes a conductive adhesive.

**[059]** Second ends of the conductive elements are in physical and electrical contact with an anisotropic conductive adhesive that is in electrical contact with the electrical connection features of the electronic component. Each conductive element includes a first portion formed on a surface of the first substrate and a second portion formed through a thickness of the molded layer. The apparatus includes an interconnection structure disposed at the first end of each conductive element. The apparatus includes a second conductive element formed through a thickness of the first substrate and electrically connected to at least one of the conductive elements of the molded layer. The apparatus includes a second electronic component electrically connected to the second conductive element, in which the first substrate is disposed between the molded layer and the second electronic component.

[060] In an aspect, an apparatus includes a molded layer including: an electronic component encapsulated within a molding material, the electronic component having

electrical connection features, the electronic connection features facing a first surface of the molded layer; and conductive elements, each conductive element electrically connected to a corresponding electrical connection feature of the electrical component; in which first ends of the conductive elements are exposed at a second surface of the molded layer and arranged in an arrangement corresponding to an arrangement of electrical contacts of a circuit board.

[061] Embodiments can include one or more of the following features.

5

10

15

20

25

30

[062] A portion of each conductive element is exposed at the first surface of the molded layer. The apparatus includes a second electronic component disposed on the first surface of the molded layer. The second electronic component is electrically connected to one or more of the exposed portions of the conductive elements. The second electronic component includes one or more of a passive component, a battery, and a sensor. The apparatus includes an interconnection structure in physical and electrical contact with each of the first ends of the conductive elements. The interconnection structure includes one or more of solder cap, solder ball, pillar, stud, bump, pad, and conductive particle. The interconnection structure includes a conductive adhesive. Second ends of the conductive elements are in physical and electrical contact with an anisotropic conductive adhesive that is in electrical contact with the electrical connection features of the electronic component. The apparatus includes a second molded layer disposed facing the first surface of the molded layer, the second molded layer including: a second electronic component encapsulated within a molding material, the second electronic component having second electrical connection features, the second electrical connection features facing a first surface of the second molded layer; and second conductive elements, a second end of each second conductive element electrically connected to a corresponding second electrical connection feature of the electrical component, in which first ends of the second conductive elements are exposed at a second surface of the second molded layer and arranged in an arrangement corresponding to an arrangement of the exposed portions of the conductive elements.

**[063]** In an aspect, an apparatus includes a molded layer including multiple electronic components encapsulated within a molding material, each electronic component having electrical connection features facing a first surface of the molded layer; and multiple sets of conductive elements, each set corresponding to one of the electronic components, each conductive element of a set electrically connected to a corresponding electrical

connection feature of the corresponding electronic component; in which first ends of the conductive elements are exposed at a second surface of the molded layer.

[064] Embodiments can include one or more of the following features.

5

10

15

20

25

30

**[065]** The apparatus includes a substrate, in which the molded layer is disposed on the substrate such that the first surface of the molded layer is in contact with the substrate. The apparatus includes a support substrate, in which the substrate is disposed on the support substrate such that the substrate is between the support substrate and the molded layer.

**[066]** The apparatus includes multiple interconnection structures, each interconnection structure in physical and electrical contact with the first ends of a corresponding set of conductive elements. Each interconnection structure includes one or more of solder cap, solder ball, pillar, stud, bump, pad, conductive particle.

**[067]** The apparatus includes a second electronic component disposed on the first surface of the molded layer. The second electronic component is in electrical contact with at least one of the conductive elements of one of the sets of conductive elements. The apparatus includes multiple second electronic components disposed on the first surface of the molded layer, each second electronic component in electrical contact with at least one of the conductive elements of a corresponding set of conductive elements. The second electronic component includes one or more of a passive component, a battery, and a sensor.

[068] In an aspect, a method includes attaching an interposer substrate to a support substrate, in which multiple sets of conductive features are formed on a surface of the interposer substrate; electrically connecting each of multiple electronic components to a corresponding set of conductive features; forming a molded layer on the surface of the interposer substrate, the molded layer including an encapsulant covering the electronic components and sets of conductive features; thinning the molded layer to expose ends of the conductive features, in which thinning the molded layer includes thinning the electronic components; and separating the thinned molded layer into multiple packages, each package including at least one of the electronic components, and the corresponding set of conductive features.

[069] Embodiments can include one or more of the following features.

**[070]** Thinning the electronic components includes forming ultra-thin electronic components. The method includes forming an interconnection structure at the exposed end of each of one or more of the conductive features. The interconnection structure includes one or more of a solder cap, a solder ball, a pillar, a stud, a bump, a pad, and a conductive particle. The method includes attaching the interposer substrate to the support substrate with a temporary bonding material.

5

10

15

20

25

30

[071] The method includes connecting one of the packages to a device substrate. Connecting the package to the device substrate includes electrically connecting the conductive features of the package to respective electrical connection features of the device substrate. The method includes removing the support substrate from the interposer substrate of the connected package.

**[072]** Separating the thinned molded layer into multiple packages includes dicing the interposer substrate and the support substrate such that each package includes a portion of the interposer substrate and a portion of the support substrate. The method includes connecting one of the packages to a device substrate and removing the portion of the support substrate from the portion of the interposer substrate of the connected package. Connecting the package to the device substrate includes orienting the package such that the electronic component is between the portion of the interposer substrate and the device substrate. The method includes assembling a second molded layer onto the portion of the interposer substrate, the second molded layer including a second electronic component encapsulated within a molding material. Assembling the second molded layer includes electrically connecting the second electronic component to a conductive feature formed through a thickness of the portion of the interposer substrate.

[073] The method includes removing the support substrate from the interposer substrate after thinning the molded layer. Separating the thinned molded layer into multiple packages includes dicing the interposer substrate such that each package includes a portion of the interposer substrate. The method includes connecting one of the packages to a device substrate such that the electronic component is between the portion of the interposer substrate and the device substrate. The method includes assembling a second molded layer onto the portion of the interposer substrate, the second molded layer including a second electronic component encapsulated within a molding material. The method includes assembling the second molded layer includes electrically connecting the second electronic component to a conductive feature formed through a thickness of the interposer substrate.

5

10

15

20

25

30

35

[074] The method includes removing the support substrate from the interposer substrate after forming the molded layer. The method includes removing the interposer substrate from the molded layer. The method includes removing the interposer substrate by one or more of wet etching, dry etching, and mechanical removal. The method includes attaching the molded layer to a second support substrate. Thinning the molded layer includes thinning the molded layer attached to the second support substrate. Separating the thinned molded layer into multiple packages includes dicing the second support substrate such that each package includes a portion of the second support substrate. The method includes connecting one of the packages to a device substrate such that the electronic component is between the portion of the second support substrate and the device substrate. The method includes removing the portion of the second support substrate from the connected package. When the portion of the second support substrate is removed, one or more electrical connection features of the electronic component are exposed on a surface of the electronic component facing away from the device substrate. The method includes assembling one or more second electronic components onto a surface of the electronic component facing away from the device substrate. The method includes assembling a second molded layer onto the molded layer, the second molded layer including a second electronic component encapsulated within a molding material. Assembling the second molded layer includes electrically connecting the second electronic component to one or more of the conductive features in the molded layer. The method includes removing the second support substrate from the thinned molded layer. When second support substrate is removed, the ends of the conductive features are exposed on a first surface of the molded layer and one or more electrical connection features of the electronic component are exposed on a second surface of the molded layer. The method includes assembling one or more second electronic components onto the second surface of the molded layer. The method includes assembling a second molded layer onto the molded layer, the second molded layer including a second electronic component encapsulated within a molding material. The method includes assembling the second molded layer includes electrically connecting the second electronic component to one or more of the conductive features in the molded layer. Assembling the second electronic component includes electrically connecting the second electronic component to at least one of the electrical connection features exposed on the second surface of the molded layer. The method includes connecting one of the packages to a device substrate such that the first surface of the molded layer of the package faces the device substrate.

**[075]** We use the term discrete component broadly to include, for example, any unit that is to become part of a product or electronic device, for example, electronic, electromechanical, or optoelectronic components, modules, or systems, for example, any semiconductor material having a circuit formed on a portion of the semiconducting material.

[076] Other aspects, features, implementations and advantages will become apparent from the following description and from the claims.

# **Brief Description of Drawings**

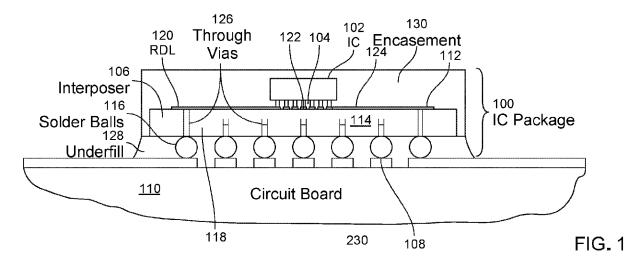

- [077] Fig. 1 is a diagram of an integrated circuit package.

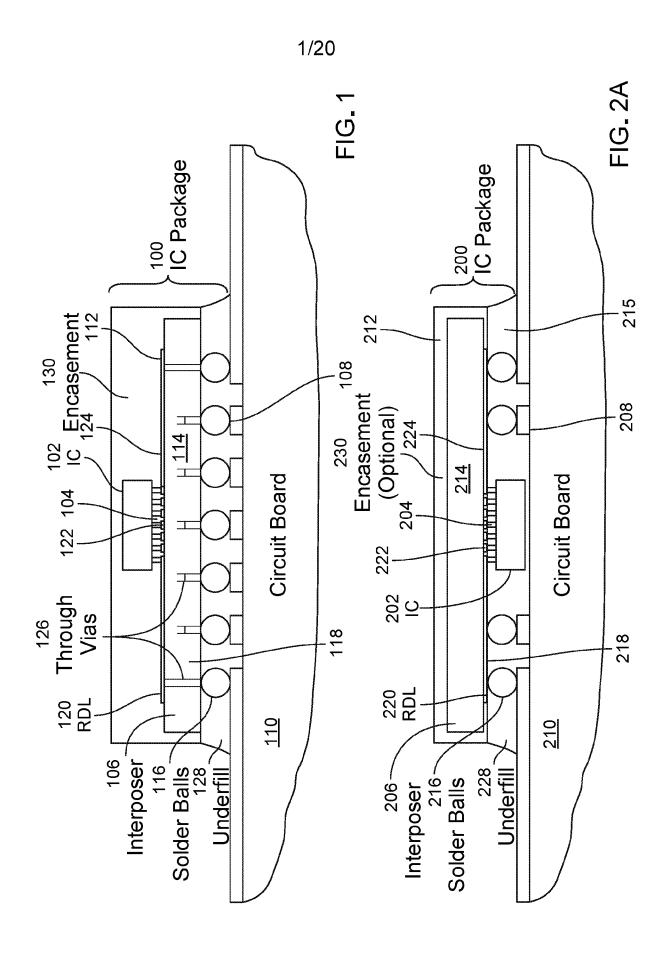

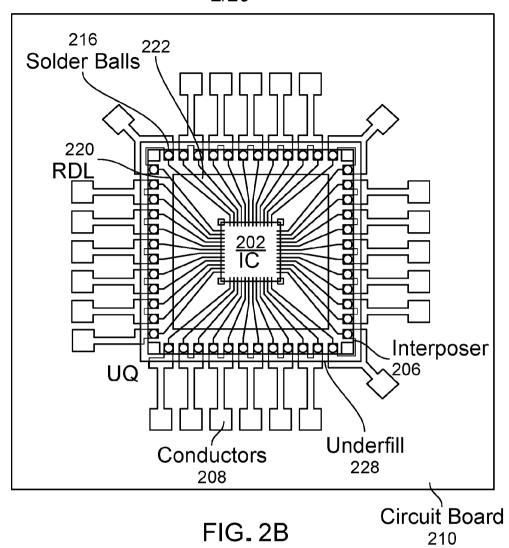

- 10 **[078]** Figs. 2A and 2B are side view and top view diagrams, respectively, of an integrated circuit package.

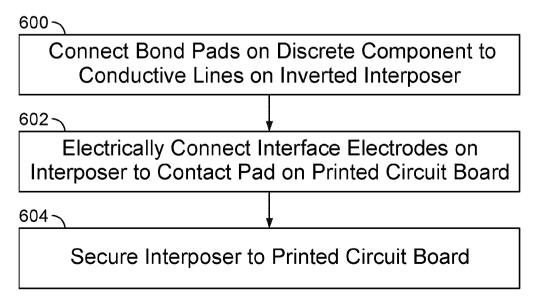

- [079] Fig. 3 is a flow chart.

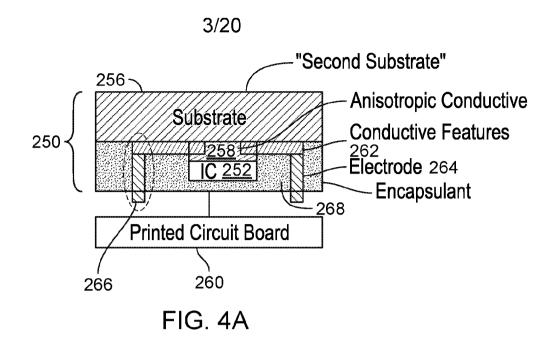

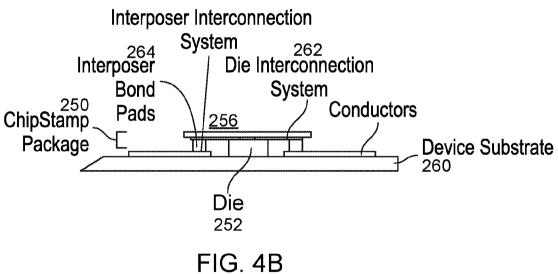

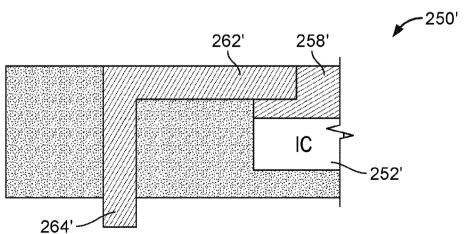

- [080] Figs. 4A-4C are diagrams of integrated circuit packages.

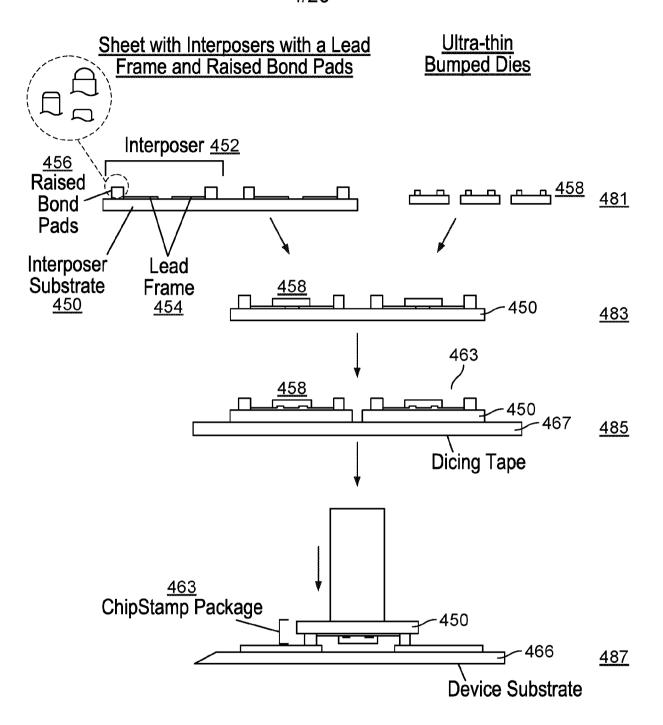

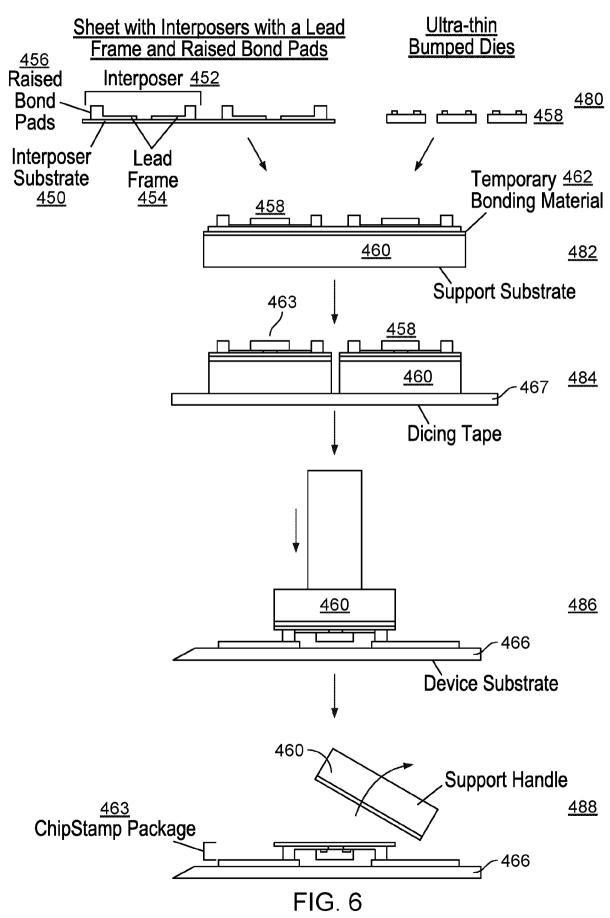

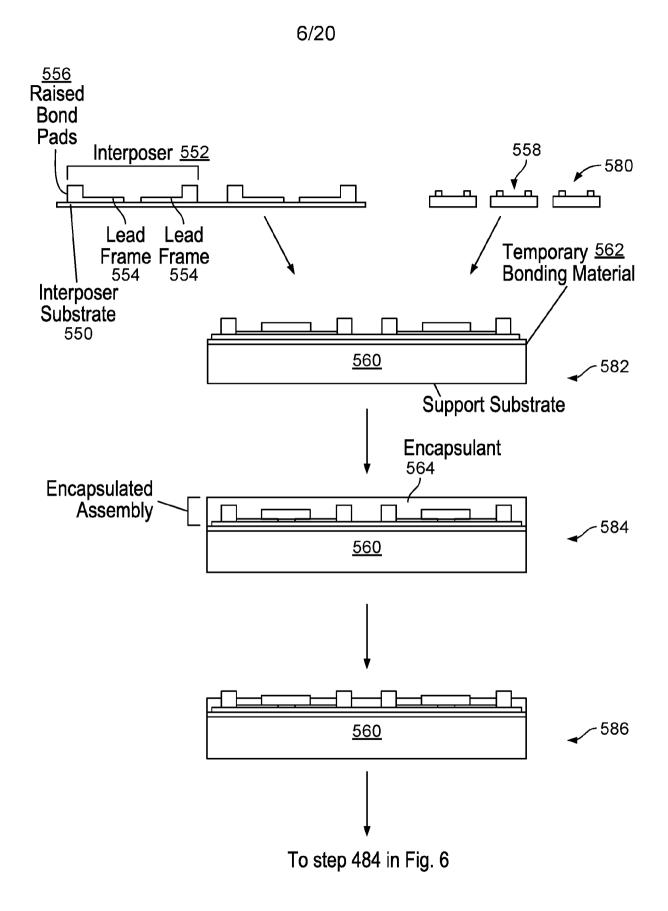

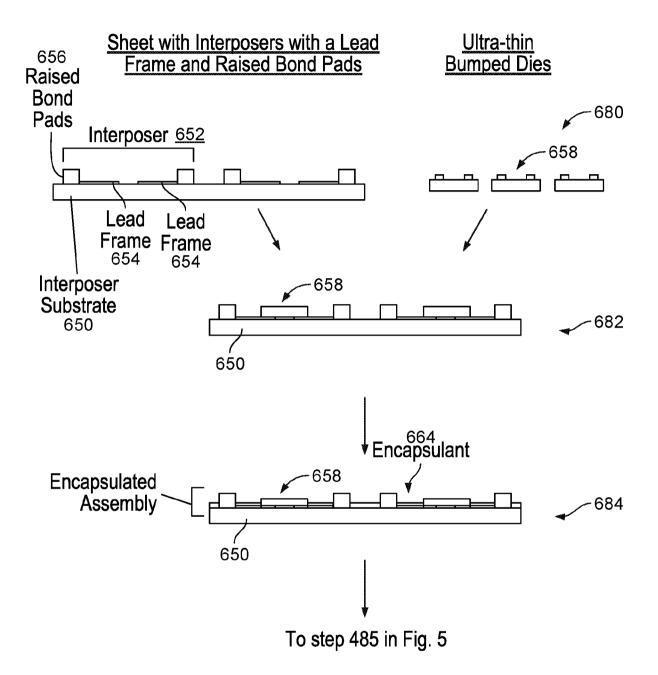

- [081] Figs. 5-8 are diagrams of fabrication and assembly of integrated circuit packages.

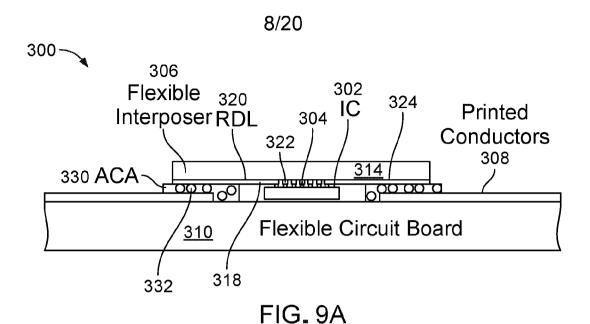

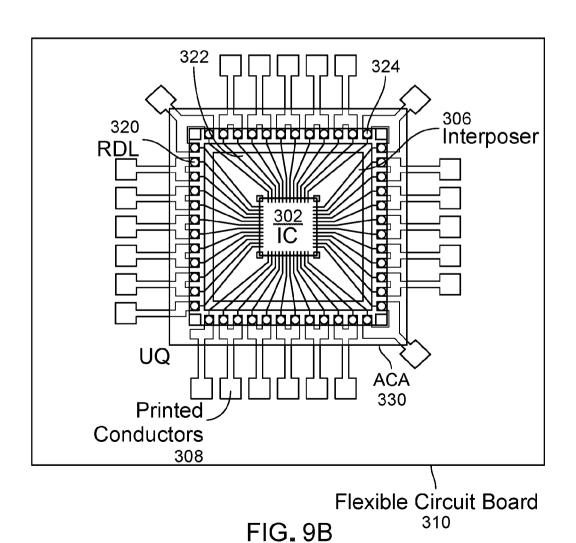

- 15 **[082]** Figs. 9A and 9B are side view and top view diagrams, respectively, of an integrated circuit package.

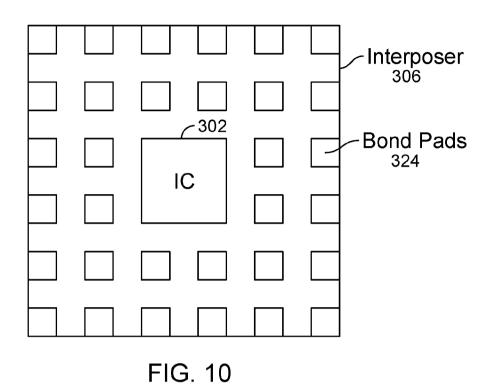

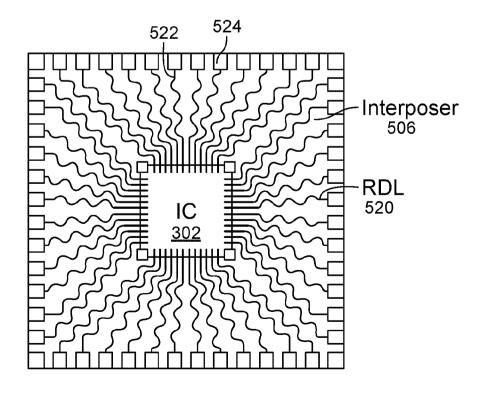

- [083] Figs. 10 and 11 are diagrams of integrated circuit packages.

- [084] Fig. 12 is a diagram of an integrated circuit package.

- [085] Fig. 13 is a flow chart.

- 20 [086] Figs. 14-17 are diagrams of integrated circuit packages.

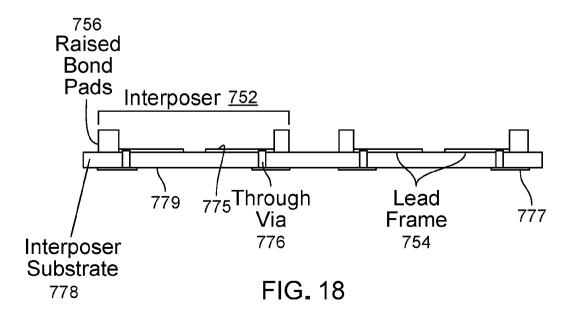

- [087] Fig. 18 is a diagram of an interposer assembly.

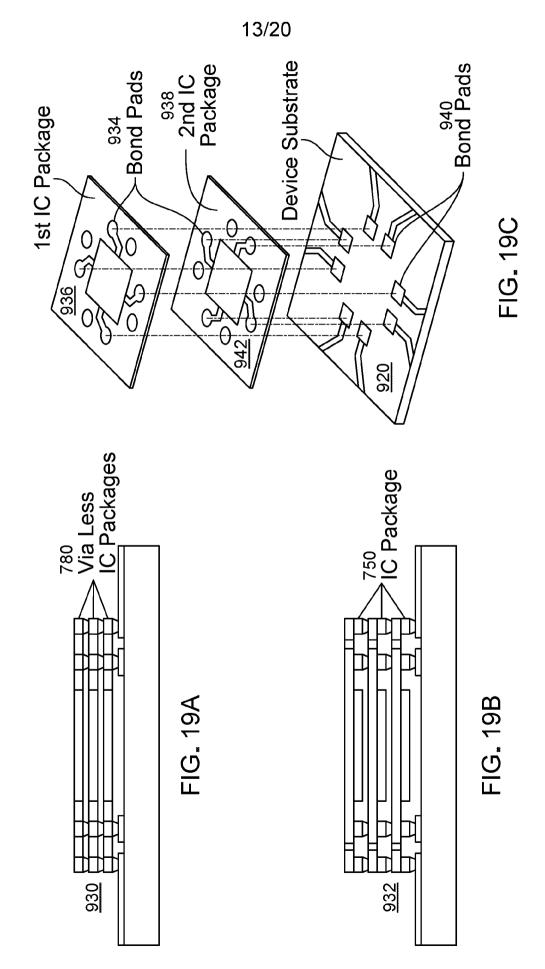

- [088] Figs. 19A-19C are diagrams of three-dimensional integrated circuit packages.

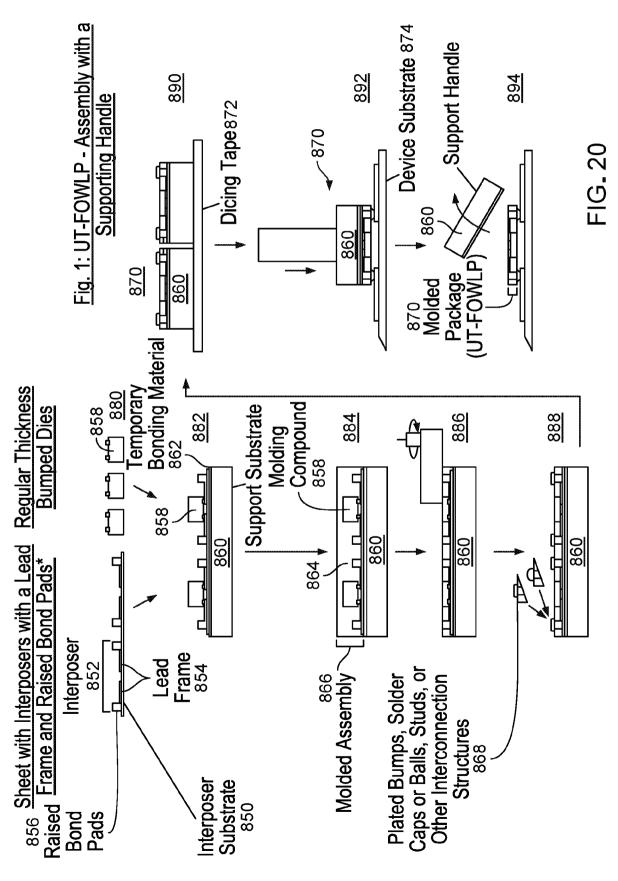

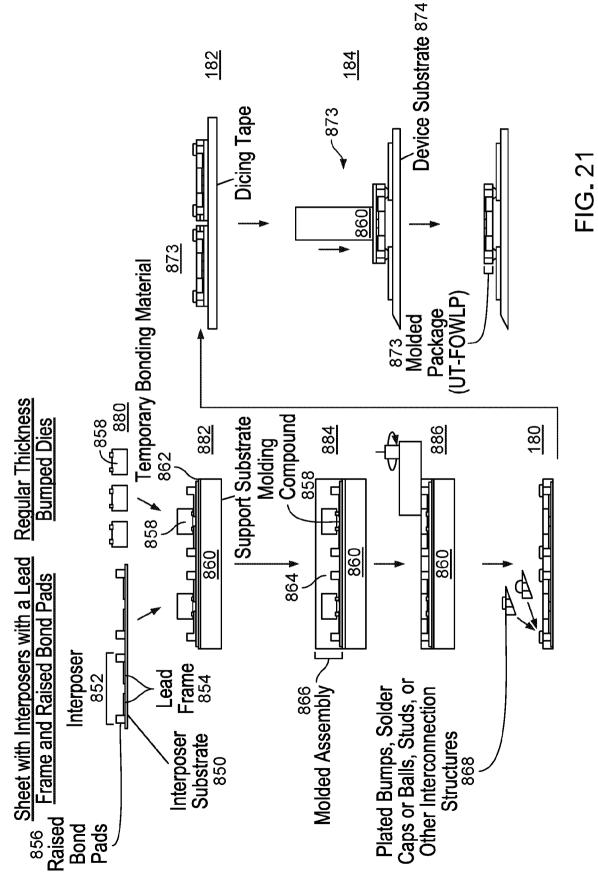

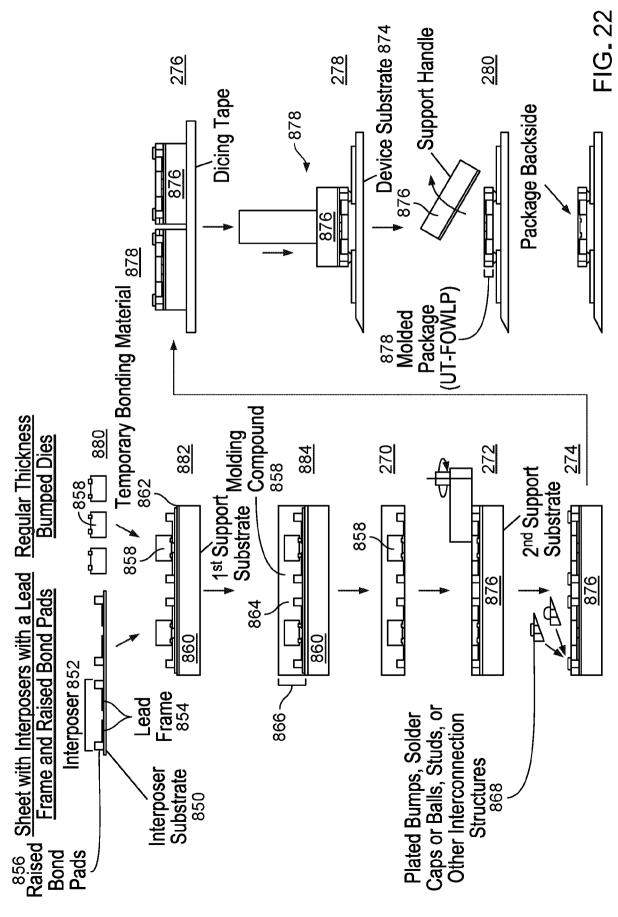

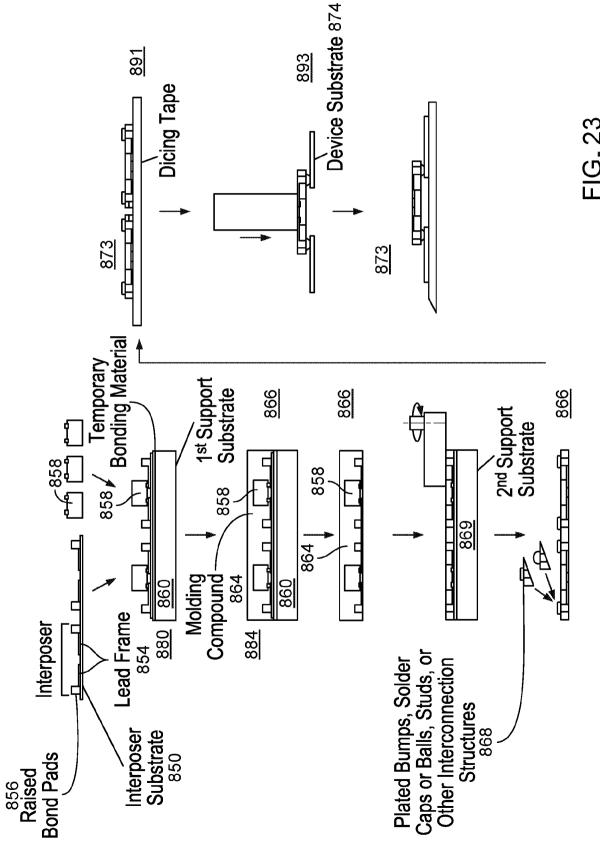

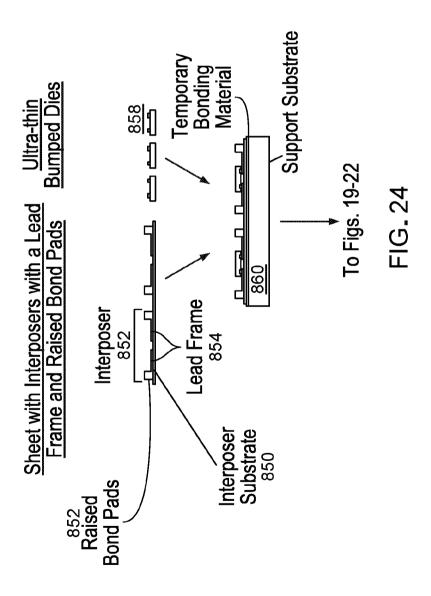

- [089] Figs. 20-24 are diagrams of fabrication and assembly of integrated circuit packages.

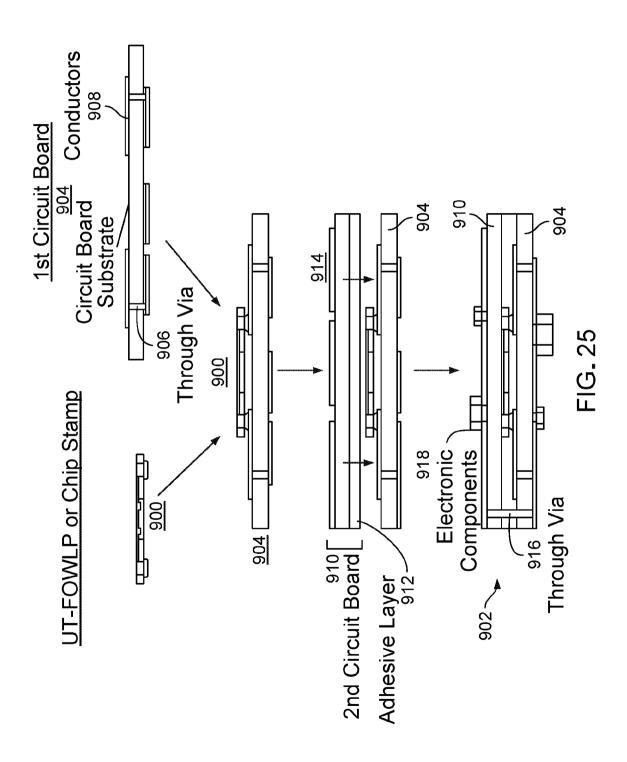

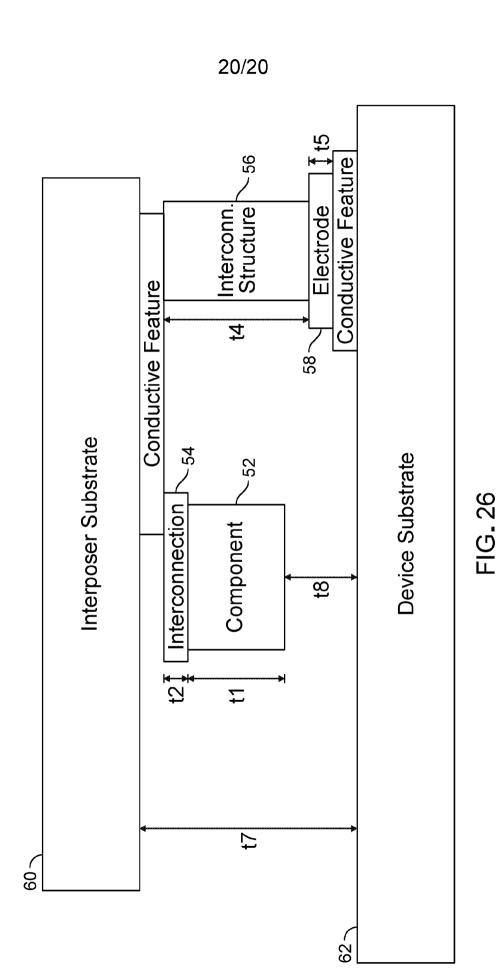

- 25 [090] Figs. 25 and 26 are diagrams of assembly of an integrated circuit package.

## **Detailed Description**

[091] We describe here an approach to connecting electronic components to substrates, such as printed circuit boards. Although this description sometimes refers to printed circuit boards, it is to be understood that other substrates can also be used. One or more electronic components are electrically connected to or formed on an interposer, and the interposer is electrically connected to the printed circuit board such that the one or more electronic components are positioned between the interposer and the printed circuit board. This arrangement enables an arrangement of electrical contacts of the one or more electronic components (e.g., a dense array of high resolution electrical contacts) to be connected with a different arrangement of electrical contacts on the printed circuit board (e.g., a less dense array of lower resolution electrical contacts). In this arrangement, all circuitry can be formed on the same side of the interposer, allowing the length of the signal lines to be reduced, which in turn reduces parasitic capacitance and resistance and improves device performance. In addition, because all circuitry is formed on the same side of the interposer, the package can be created without through vias formed through the body of the interposer, which can contribute to more straightforward manufacturing and a more reliable package.

5

10

15

20

25

30

**[092]** In some examples, the electronic component can be a discrete component that is fabricated separately and independently from the interposer, disposed on a surface of the interposer, and electrically connected to the interposer. Examples of discrete components can include a semiconductor die that includes one or more integrated circuits, passive components such as resistors, capacitors, inductors, sensors, microelectromechanical (MEMS) devices, light emitting diodes (LEDs), power sources, chemical or biological sensing elements, or other examples, or a combination of any two or more of them.

[093] In some examples, the electronic component can be formed on the surface of the interposer. In some cases, conductive features on the surface of the interposer can be configured into a certain geometry to form the electronic component (e.g., a planar capacitor, a filter, or another type of electronic component). In some cases, the electronic component can be formed on the surface of the interposer by an additive method such as direct write or screen printing (e.g., to form a printed transistor or another type of printed electronic component).

[094] In some examples, the electronic component can be embedded into a body of the interposer during fabrication of the interposer such that the electronic component forms an integral part of the interposer.

[095] Referring to Fig. 1, in a known mounting technique, an integrated circuit (IC) package 100 including an electronic component 102 is mounted on a printed circuit board 110. The electronic component 102 is mounted in a face-down orientation, meaning that bond pads 104 on the electronic component 102 face towards the printed circuit board 110. An interposer 106 disposed between the electronic component 102 and the printed circuit board 110 serves to electrically connect bond pads 104 on the electronic component 102 to electrical connection features, such as contact pads 108, on the printed circuit board.

5

10

15

20

25

30

[096] The pitch and line/space resolution of the bond pads 104 on the electronic component 102 can reflect the pitch and line/space resolution of the circuitry in the electronic component 102. By pitch, we mean the distance between an identical point in two adjacent features in a pattern of repeating features, such as bond pads. Pitch can be viewed as the sum of the width of a feature (e.g., a bond pad) and the width of the space on one side of the feature (e.g., a space filled by a material, such as an insulator) that separates that feature from an adjacent feature. By line/space resolution, we mean the size and spacing of the smallest features on the printed circuit boards, such as the conductor lines. The size of the smallest features can be approximately equal to the smallest line spacing. Features having a large line width and large line spacing are referred to as having a coarse line/space resolution; features having a small line width and small line spacing are referred to as having a fine line/space resolution. Sometimes, the pitch of the bond pads 104 on the electronic component 102 does not match the pitch of the contact pads 108 on the printed circuit board 110 to which the electronic component 102 is to be connected. For instance, some integrated circuits may reach a pitch of 10 microns, but printed circuit boards may not have contact pads 108 with the same pitch. For instance, the contact pads 108 on printed circuit boards are often larger and less closely spaced than the bond pads 104 on electronic components.

[097] The interposer 106 enables the electronic component 102 to be electrically connected to the printed circuit board 110 even if there is a mismatch between the pitch of the bond pads 104 on the electronic component 102 and the contact pads 108 on the printed circuit board 110. In the example of Fig. 1, the electronic component 102 is disposed on a top surface 112 of the interposer 106, and the interposer 106 is disposed on

a top surface of the printed circuit board 110. By top surface, we mean the surface of the interposer 106 that faces away from the printed circuit board 110. Circuitry (e.g., conductors) formed through a body 114 of the interposer enables the electronic component 102 to be electrically connected to interface electrodes 116 formed on a bottom surface 118 of the interposer 106, which can contact the contact pads 108 on the printed circuit board 110. By bottom surface, we mean the surface of the interposer 106 that faces the printed circuit board 110.

[098] A redistribution layer (RDL) 120 is disposed on the top surface 112 of the interposer 106 or forms an inner layer of a multilayer interposer. The redistribution layer 120 is formed of a conductive material such as aluminum, copper, gold, silver, or another conductive material, or a combination of any two or more of them. The redistribution layer 120 includes multiple, fine resolution conductive features, such as conductive lines 122. Each conductive line 122 is positioned such that one end of the conductive line aligns with a corresponding one of the bond pads 104 on the electronic component and the other end forms an RDL contact pad 124. The pitch of the RDL contact pads 124 can be greater than the pitch of the bond pads 104 of the electronic component 102. For example, the width of the bond pads 104 can be between about 10 μm and about 1,000 μm and the pitch of the bond pads 104 can be between about 20 μm and about 2,000 μm.

10

15

20

25

30

[099] Each RDL contact pad 124 is electrically connected to a conductive vertical interconnect structure 126 (sometimes referred to as a through via 126) formed through the thickness of the body 114 of the interposer 106. We use the term "through via" broadly to include, for example, any vertical interconnect that is used to electrically connect a component on the top surface of a substrate to a component on the bottom surface of a substrate. Each through via 126 connects one of the RDL contact pads 124 formed on the top surface 112 of the interposer 106 to a corresponding one of the interface electrodes 116 formed on the bottom surface 118 of the interposer. The interface electrodes 116 can be, for instance, solder balls, pillars, studs, bumps, pads, conductive particles, or other electrode structures. Each interface electrode 116 contacts a corresponding contact pad 108 on the printed circuit board 110. As a result, an electrical connection is established from each of the bond pads 104 on the electronic component 102, through the thickness of the interposer 106, and to a corresponding contact pad 108 on the printed circuit board 110.

[0100] The IC package 100 can be secured to the printed circuit board 110 by an underfill layer 128, such as a non-conductive polymer, e.g., a thermosetting polymer such

as an epoxy. The underfill layer 128 can help to resolve thermal mechanical issues arising from the coefficient of thermal expansion (CTE) mismatch between the silicon die or interposer and the printed circuit board to which the IC package is attached. The electronic component 102 and interposer 106 can be encased or encapsulated in a protective case 130, such as a plastic or ceramic case, that can provide mechanical or environmental protection to the electronic component 102 and the circuitry of the interposer 106.

5

10

15

20

25

30

[0101] Referring to Figs. 2A (side view) and 2B (top view), in an IC package 200, an electronic component 202 is mounted on a printed circuit board 210. An inverted interposer 206 electrically connects conductive features, such as bond pads 204, on the electronic component 202 to electrical connection features, such as contact pads 208, on the printed circuit board 210, thus creating an electrical connection between the electronic component 202 and the printed circuit board 210. In the example of Figs. 2A and 2B, the electronic component 202 is shown as a discrete component. In some examples, the electronic component 202 can be formed on the surface of the inverted interposer 206 or embedded within a body 214 of the inverted interposer 206. In some examples, the inverted interposer 206 can create an electrical connection between multiple electronic components 202 and the printed circuit board 210.

**[0102]** The inverted interposer 206 can be formed of silicon, glass, an organic material, or another material compatible with integrated circuit interconnection and packaging technologies. Example organic materials for the inverted interposer 206 can include polymers such as polyimide (PI), polytetraflouroethylene (PTFE), polyethylene (PET), composite materials such as glass-reinforced epoxy laminate sheets commonly used in printed circuit board fabrication, or a combination of any two or more of them. In the inverted interposer 206, the same surface of the interposer (e.g., a bottom surface 218 of the interposer 206) faces both the electronic component 202 and the printed circuit board 210. In this arrangement, the electronic component is positioned in a gap 215 between the inverted interposer 206 and the printed circuit board 210. The presence of the inverted interposer 206 enables the electronic component 202 to be electrically connected to the printed circuit board 210 even if there is a mismatch between the dimensions of the bond pads 204 on the electronic component 202 and the contact pads 208 on the printed circuit board 210.

[0103] A redistribution layer 220 is disposed on the bottom surface 218 of the inverted interposer 206, which is the same surface that faces both the electronic component 202

and the printed circuit board 210. The redistribution layer 220 includes multiple, fine resolution conductive features, such as conductive lines 222, each of which connects one of the bond pads 204 on the electronic component 202 to a corresponding RDL contact pad 224. In some examples, the bond pads 204 can include bumps and the conductive lines 222 connect the bumps of the bond pads 204 to the corresponding RDL contact pads 224. In order for the bond pads 204 or the bumps of the bond pads 204 on the electronic component 202 to contact the redistribution layer 220, the electronic component 202 is disposed in a face-up orientation such that the bond pads 204 on the electronic component 202 face away from the printed circuit board 220.

[0104] In some examples, the RDL contact pads 224 can be located toward the periphery of the interposer 206, resulting in a fan-out design of the conductive lines 222. In this arrangement, the contact pads 224 are positioned around the edges of the electronic component 202 such that the electronic component is inside of a shape defined by the contact pads 224. In some examples, the RDL contact pads can be formed into other arrangements, such as arranged in an array. The redistribution layer thus acts as a signal routing structure that routes signals from the bond pads 204 of the electronic component 202 to other locations. In some examples, the RDL contact pads 224 can be formed into an arrangement that aligns with the arrangement of the contact pads 208 on the printed circuit board 210.

[0105] Each RDL contact pad 224 can be in direct, physical and electrical contact with a corresponding interface electrode 216, such as a solder ball, pillar, stud, bump, pad, or other electrode structure. Each interface electrode 216 contacts a corresponding contact pad 208 on the printed circuit board 210. As a result, an electrical connection is established from a bond pad 204 on the electronic component 202 to a corresponding contact pad 208 on the printed circuit board 210.

**[0106]** In the IC package 200 of Fig. 2, the electrical connection between the electronic component 202 and the printed circuit board 210 is achieved without the use of through vias through a body 214 of the inverted interposer 206. Rather, the electrical connection is implemented through circuitry that is all formed on the same surface (e.g., the bottom surface 218) of the inverted interposer 206. The absence of through vias allows the IC package 200 to be fabricated using a more straightforward fabrication process, e.g., without the use of lithography and etching process steps used to form through vias through the body 214 of the interposer, thus reducing manufacturing costs. In addition,

the formation of all of the circuitry on the same surface of the inverted interposer 206, without the presence of through vias, can result in a more reliable IC package 200.

**[0107]** The formation of all of the circuitry on the same surface of the inverted interposer 206 also reduces the length of the signal lines between the bond pads on the electronic component 202 and the corresponding contact pads 208 on the printed circuit board 210. As a result, the parasitic capacitance and resistance along the signal lines is reduced, and hence the performance of the IC package 200 can be enhanced.

5

10

15

20

25

30

**[0108]** The IC package 200 can be secured to the printed circuit board 210 by an underfill layer 228, such as a non-conductive epoxy. In some examples, the inverted interposer 206 can be encased or encapsulated in a protective case 230, such as a plastic or ceramic case, that can provide mechanical or environmental protection. However, because the electronic component 202 and the circuitry of the inverted interposer 206 are already protected by their position adjacent the bottom surface 218 of the inverted interposer 206, such a protective case can be optional. The absence of a protective case can allow the IC package 200 to be fabricated with fewer process steps and less material, and thus fabrication can be more efficient and less expensive.

**[0109]** In some examples, the IC package 200 using the inverted interposer 206 can be assembled if the height of the electronic component 202 satisfies a criterion, such as that the height of the electronic component 202 plus the bond pads 204 and any desired clearance between the electronic component 202 and the printed circuit board 210 is equal to or smaller than the separation between the bottom surface 218 of the inverted interposer 206 and the printed circuit board 210 (known as the standoff height). For instance, the electronic component 202 can have a thickness that is no greater than the combination of a thickness of the electrodes 216 and a thickness of the contact pads 208 of the printed circuit board 210 less than the height of the bond pads 204. In a specific example, if the expected standoff height after bonding the inverted interposer 206 to the printed circuit board 210 is 50  $\mu$ m, then the IC package 200 can be compatible with electronic components that are less than about 50  $\mu$ m thick, less than about 40  $\mu$ m thick, less than about 30  $\mu$ m thick, less than about 25  $\mu$ m thick, less than about 20  $\mu$ m thick, less than about 10  $\mu$ m thick, or less than about 5  $\mu$ m thick.

**[0110]** In some examples, the overall height of the IC package 200 can be less in the configuration shown in Fig. 2 than if components of the same thickness were assembled according to the IC package 100. In the IC package 200, the electronic component 202 is disposed within a space between the bottom surface 218 of the inverted interposer 206

and the printed circuit board 210 that would have existed even without the presence of the electronic component 202. In contrast, in the IC package 100, the electronic component 102 is disposed on the top surface 112 of the interposer 106, increasing the height of the IC package 100 by an amount equal to at least the thickness of the electronic component 102. The low profile of the IC package 200 thus enables the IC package 200 to be used in applications for which thinner components are appropriate.

5

10

15

20

25

30

**[0111]** In the example of Fig. 2, the circuitry of the inverted interposer 206, such as the redistribution layer 220 and the interface electrodes 216, is formed on the bottom surface 218 of the inverted interposer 206. For instance, the redistribution layer 220 can be formed by deposition techniques such as plating, etching, thin film processing techniques, thick film processing techniques, direct write, or other techniques compatible with forming patterned conductors on a substrate.

**[0112]** In some examples, some or all of the circuitry of the inverted interposer 206, such as the redistribution layer 220, can be embedded within the body 214 of the inverted interposer 206. For instance, embedding some or all of the circuitry within the body 214 of the inverted interposer 206 can be useful if a complete electric circuit is formed on the bottom surface of the interposer, thus not allowing sufficient space on the surface of the interposer to create a network of conductors without conductor lines crossing. In an example, a portion of the redistribution layer 220 is buried in the body 214 of the interposer and accessed through blind vias. In some examples, a buried redistribution layer can be used if the pads 204 are arranged in an array pattern in order to allow access to the inner pads.

**[0113]** In some examples, additional electronic components can be disposed or formed on the bottom surface 218, on a top surface 212 of the inverted interposer 206, or both, or can be embedded within the body 214 of the inverted interposer 206.

**[0114]** In some examples, multiple electronic components 202 can be electrically connected to the printed circuit board 210 via electrical connections through a single inverted interposer 206. For instance, multiple electronic components 202 can be positioned between the inverted interposer 206 and the printed circuit board 210. In some cases, one or more electronic components 202 can be positioned between the inverted interposer 206 and the printed circuit board 210 and one or more electronic components can be mounted on the top surface 212 of the inverted interposer 206. In some cases, one or more electronic components can be embedded within the body 214 of the inverted interposer 206. By embedded, we mean formed within the material of the body 214.

**[0115]** Referring to Fig. 3, in an example approach to assembling an IC package with an inverted interposer, such as the IC package 200, the bond pads on an electronic component are each electrically connected to a corresponding conductive line on a bottom surface of an inverted interposer (600). For instance, the connection can be made using, soldering, adhesive bonding, thermocompression bonding, ultrasonic or thermosonic bonding, diffusion bonding, or other techniques, or a combination of any two or more of them. Each conductive line terminates in a contact pad that is in electrical contact with a corresponding interface electrode disposed on the bottom surface of the inverted interposer. In some examples, the contact pad of a conductive line can be in direct, physical contact with the corresponding interface electrode of the inverted interposer. In some examples, the contact pad can be in electrical contact with the interface electrode via an intermediate conductor, such as conductive adhesive.

5

10

15

30

[0116] The interface electrodes are each electrically connected to a corresponding contact pad on a printed circuit board (602), thus establishing a connection between the electronic component and the printed circuit board. For instance, the connection can be made using soldering, adhesive bonding, thermocompression bonding, ultrasonic or thermosonic bonding, diffusion bonding or other techniques, or a combination of any two or more of them. The IC package is secured to the printed circuit board, for instance, using an underfill layer, such as a non-conductive epoxy (604).

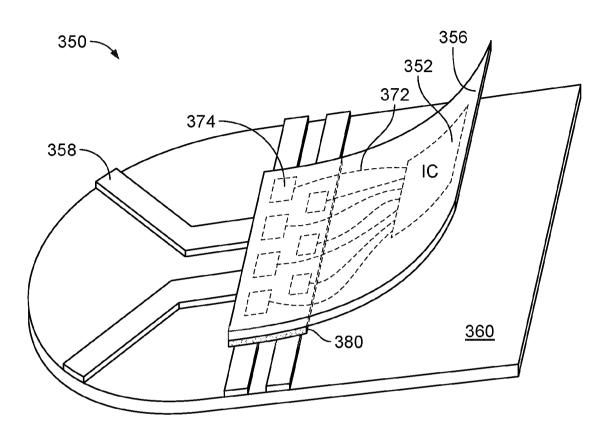

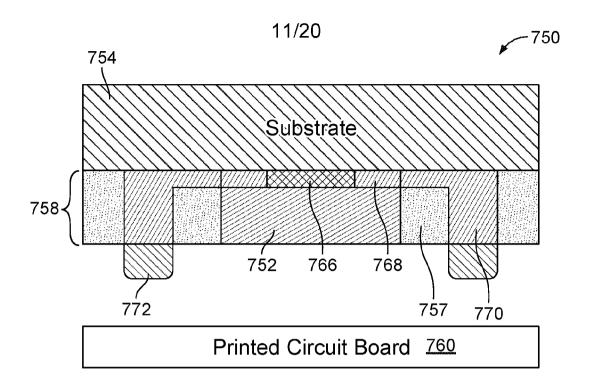

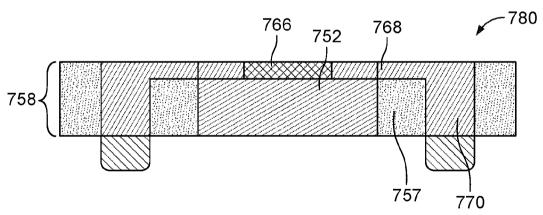

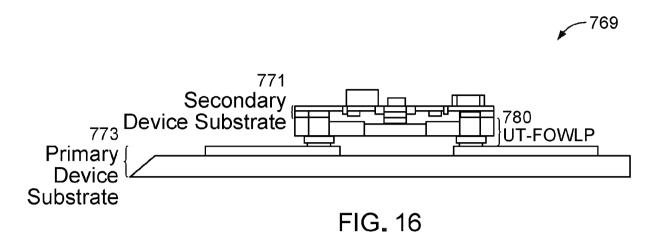

20 [0117] Referring to Fig. 4A, in an IC package 250, an electronic component 252 is mounted on a printed circuit board 260. An inverted interposer substrate 256 electrically connects conductive features on the electronic component 252, such as bond pads or bumps on the bond pads, to electrical connection features on the printed circuit board 260. The IC package is oriented such that the bottom surface of the inverted interposer substrate 256 faces both the electronic component 252 and the printed circuit board 260.

**[0118]** In the IC package 250, the bond pads on the electronic component 252 are in electrical contact with an interconnection system 258. The interconnection system 258 can be an adhesive, such as an anisotropic conductive adhesive, an isotropic conductive adhesive, a conductive adhesive. The interconnection system 258 can be an interconnection formed by soldering, adhesive bonding, ultrasonic or thermosonic bonding, thermocompression bonding, diffusion bonding, or other techniques, or a combination of any two or more of them.

[0119] The interconnection system 258 is in turn in electrical contact with a redistribution structure 262. By redistribution structure, we mean a network of

conductors, such as metal conductors, that redistributes the bond pads on the electronic component and that conducts electrical signals from the electronic component to the printed circuit board. A redistribution structure can be a three-dimensional structure that has conductors oriented in multiple directions, such as conductors oriented substantially parallel to the surface of the interposer substrate 256 and conductors oriented substantially perpendicular to the surface of the interposer substrate 256. The conductors in the redistribution structure 262 that are oriented substantially perpendicular to the surface of the interposer substrate 256 are oriented away from, rather than through, the interposer substrate 256.

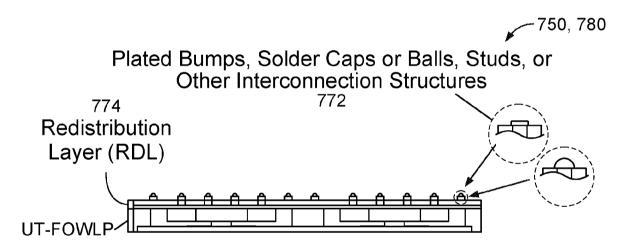

[0120] The redistribution structure 262 can include multiple conductive features. Each of 10 the conductive features of the redistribution structure 262 is in electrical contact with a corresponding conductive features of an electrode structure 264. The end 266 of each of the conductive features of the electrode structure 264 is configured to be in electrical contact with a corresponding electrical connection feature on the printed circuit board 260, such as a conductive pad or an electrode structure such as a solder ball, pillar, stud, 15 bump, or other electrode structure. As a result, an electrical connection is established between a bond pad on the electronic component 252 and a corresponding electrical connection feature on the printed circuit board 260. In some examples, the end 266 of one of the conductive features of the electrode structure 264 can be in direct, physical contact with the corresponding electrical connection feature on the printed circuit board 260. For 20 instance, the connection can be made by ultrasonic or thermosonic bonding, thermocompression bonding, diffusion bonding, or other techniques, or a combination of any two or more of them. In some examples, the end 266 of one of the conductive features of the electrode structure 264 can be in electrical contact with the corresponding electrical connection feature via an intermedia conductor, e.g., through a conductor 25 formed by soldering, adhesive bonding, wire bonding, or other techniques, or a combination of any two or more of them.

**[0121]** In some examples, the conductive features of the redistribution structure 262 are oriented to be substantially parallel to the bottom surface of the inverted interposer substrate 256 and the conductive features of the electrode structure 264 are oriented to be substantially perpendicular to the bottom surface of the inverted interposer substrate 256. The conductive features of the electrode structure 264 can be formed into an arrangement that aligns with the arrangement of the electrical connection features on the printed circuit board 260.

**[0122]** In some examples, an encapsulant 268 at least partially surrounds the electronic component 252, the redistribution structure 262, and the electrode structure 264. The encapsulant can be, e.g., a non-conductive polymer, such as liquid or film polymers, e.g., epoxies, silicones, polyimides, or other polymers. In some examples, the ends 266 of the conductive features of the electrode structure 264 can extend beyond a bottom surface of the encapsulant to provide a contact point with the printed circuit board 260. In some examples, the ends 266 of the conductive features of the electrode structure 264 can be flush with the bottom surface of the encapsulant. In some examples, no encapsulant is present.

[0123] In some examples, the redistribution structure 262 and the electrode structure 264 are formed of the same material, such as aluminum, copper, silver, gold, tin, alloys based on these metals, or another conductive material (e.g., as shown in Fig. 4C). For instance, the redistribution structure 262 and the electrode structure 264 can be a single, integral conductive feature, such as a conductive frame, e.g., a lead frame. In some examples, the redistribution structure 262 is formed of a different material than the electrode structure 264. For instance, the redistribution structure can be a redistribution layer that includes multiple, fine resolution conductive features, such as conductive lines (e.g., such as in the redistribution layer 220 of Fig. 2A), and the electrode structure can include solder balls, pillars, studs, bumps, pads or other electrode structures (e.g., such as the interface electrodes 216 of Fig. 2A).

**[0124]** In some examples, the IC package 252 has a height that equal to or less than the height of the electrode structure 264. In some examples, the sum of the heights of the IC package 252 and the interconnection system 258 is equal or less than the sum of the heights of the redistribution structure 262 and the electrode structure 264.

[0125] Referring to Fig. 4B, in some examples, the IC package 250 can be assembled if the height of the electronic component 252 satisfies a criterion, such as that the height of the electronic component 252 plus the redistribution structure 262 and any desired clearance between the electronic component 252 and the printed circuit board 260 is equal to or smaller than the standoff height between the bottom surface of the interposer256 and the printed circuit board 260.

**[0126]** Referring to Fig 4C, in some examples, an interposer structure 250' for mounting an electronic component 252' onto a printed circuit board (not shown) does not include a substrate on a top surface of the interposer structure 250'. In this configuration, the top surface of the redistribution structure 262' is exposed and coplanar with the top surface of

the encapsulant 268'. This exposure can provide opportunities to assemble additional components on top of the interposer structure 250', thus increasing electronics packaging density. This exposure can allow for the inclusion of additional components, such as passive electronic components (e.g., resistors, capacitors, filters, or other passive components), batteries, sensors, micro-electromechanical systems, or connectors, or other components. This exposure can provide an exposed area for components with which a user can interface, such as displays, optoelectronic components, touch sensors, switches, fingerprint detectors, or other components.

[0127] In the example of Fig. 4C, the redistribution structure 262' and the electrode structure 264' are formed of the same material and form a single, integral structure, such as a conductive frame, e.g., a lead frame. In some examples, the redistribution structure 262' and the electrode structure, 264' can be formed of different materials.

10

20

25

30

[0128] The IC packages 250, 250' can be rigid structures or flexible structures, such as structures that incorporate flexible electronic components.

15 **[0129]** In some examples, the IC package 252' has a height that is equal to or less than the height of the electrode structure 264'. In some examples, the sum of heights of the IC package 252' and the interconnection system 258' is equal to or less than the sum of the heights of the redistribution structure 262' and the electrode structure 264'.

**[0130]** Referring to Fig. 5, in an example approach to fabricating and assembling an IC package, such as the IC package 250 of Fig. 4A, an interposer substrate 450 including multiple interposers 452 is provided (481). Each interposer 452 includes a redistribution structure 454 and an electrode structure 456, such as raised bond pads. In the example shown, the redistribution structure 454 and the electrode structure 456 are formed of the same material; in some examples, the redistribution structure and the electrode structure 456 can be formed of different materials, such as to form a conductive frame.