**【特許請求の範囲】****【請求項 1】**

クロック信号に従ってスイッチングを行う複数のトランジスタ及び前記複数のトランジスタにそれぞれ接続された複数のコンデンサを含み、チャージポンプ動作により電源電圧を昇圧して昇圧電圧を生成する昇圧回路と、

所定の周波数を有する発振信号を生成する発振回路と、

前記発振回路によって生成された発振信号を設定された分周比で分周することにより、前記昇圧回路に供給されるクロック信号を生成する分周回路と、

フレーム同期信号又は発振信号又はクロック信号に含まれているパルスをカウントすることによりカウント値を得るカウンタと、

起動時に第1の分周比を前記分周回路に設定し、前記カウンタによって得られたカウント値が所定の値に達したときに第2の分周比を前記分周回路に設定することにより、前記昇圧回路に供給されるクロック信号の周波数を制御するクロック周波数制御回路と、

を具備する半導体集積回路。

**【請求項 2】**

前記第2の分周比の値が前記第1の分周比の値よりも大きく、前記クロック周波数制御回路が、前記カウンタによって得られたカウント値が所定の値に達したときに、前記昇圧回路に供給されるクロック信号の周波数を小さくする、請求項1記載の半導体集積回路。

**【請求項 3】**

前記発振回路によって生成された発振信号を分周することによりフレーム同期信号を生成するフレーム同期信号生成回路をさらに具備する、請求項1又は2記載の半導体集積回路。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、供給される電源電圧を昇圧して所望の昇圧電圧を生成する昇圧回路を含む半導体集積回路に関する。

**【背景技術】****【0002】**

例えば、液晶ドライバICにおいては、液晶ディスプレイを駆動するために各種の電源電圧が必要とされており、IC内部の昇圧回路において所望の電源電圧が生成される。そのような昇圧回路は、クロック信号に基づいて昇圧動作を行うが、そのクロック信号として、発振回路によって生成された発振信号を分周することにより得られるクロック信号が使用される。

**【0003】**

ところで、携帯電話等で使用されるCSTN (Color Super Twisted Nematic: カラー・スーパー・ツイスト・ネマティック) 液晶ディスプレイ用の液晶ドライバICにおいては、昇圧回路に供給されるクロック信号の周波数が所定の値よりも低いと、液晶ドライバICの電源が立ち上がらない場合がある。一方、クロック信号の周波数が適切な値よりも高い場合には、昇圧回路における消費電流が大きくなってしまう。

**【0004】**

しかしながら、昇圧回路に供給されるクロック信号の周波数は、一般に、MPU (マイクロプロセッサ) がEEPROM等の格納部から読み出したコマンドに基づいて設定されるので、その周波数を途中で変更することはできなかった。そのため、CSTN液晶ディスプレイ用の液晶ドライバICにおいては、クロック信号の周波数が高目に設定されており、それによって確実な起動が保証されるものの、昇圧回路における消費電流が増えてしまうという問題があった。

**【0005】**

関連する技術として、特許文献1には、必要最小限の消費電流で所望の出力電圧を得るチャージポンプ装置が開示されている。このチャージポンプ装置は、スイッチングにより

コンデンサを充電するチャージポンプ回路と、チャージポンプ回路の出力を分圧する分圧回路と、分圧回路の出力と基準電圧とを比較して誤差電圧を増幅する誤差増幅器と、誤差増幅器の出力を制御電圧としてチャージポンプ回路のスイッチング信号（クロック信号）を出力するVCO（Voltage Controlled Oscillator：電圧制御発振器）とを備えている。

### 【0006】

このチャージポンプ装置は、VCOをリングオシレータで構成したことにより、所望の出力電圧を得るために必要な最小限の消費電流でチャージポンプ動作を行うことを特徴としている。しかしながら、出力電圧をフィードバックすることによってクロック信号の周波数を制御すると、クロック信号の周波数がチャージポンプ回路の動作状態に依存して変動するので、クロック信号が他の回路に及ぼすノイズの影響も変動し、それに対する対策が必要となってしまう。

【特許文献1】特許第2614938号公報（第1、3頁、第1図）

### 【発明の開示】

#### 【発明が解決しようとする課題】

### 【0007】

そこで、上記の点に鑑み、本発明は、供給される電源電圧を昇圧して所望の昇圧電圧を生成する昇圧回路を含む半導体集積回路において、予め定められた周波数のクロック信号を用いながら、迅速な起動と消費電流の低減とを両立させることを目的とする。

### 【課題を解決するための手段】

### 【0008】

上記課題を解決するため、本発明に係る半導体集積回路は、クロック信号に従ってスイッチングを行う複数のトランジスタ及び複数のトランジスタにそれぞれ接続された複数のコンデンサを含み、チャージポンプ動作により電源電圧を昇圧して昇圧電圧を生成する昇圧回路と、所定の周波数を有する発振信号を生成する発振回路と、発振回路によって生成された発振信号を設定された分周比で分周することにより、昇圧回路に供給されるクロック信号を生成する分周回路と、フレーム同期信号又は発振信号又はクロック信号に含まれているパルスをカウントすることによりカウント値を得るカウンタと、起動時に第1の分周比を分周回路に設定し、カウンタによって得られたカウント値が所定の値に達したときに第2の分周比を分周回路に設定することにより、昇圧回路に供給されるクロック信号の周波数を制御するクロック周波数制御回路とを具備する。

### 【0009】

ここで、第2の分周比の値が第1の分周比の値よりも大きく、クロック周波数制御回路が、カウンタによって得られたカウント値が所定の値に達したときに、昇圧回路に供給されるクロック信号の周波数を小さくするようにしてても良い。また、半導体集積回路が、発振回路によって生成された発振信号を分周することによりフレーム同期信号を生成するフレーム同期信号生成回路をさらに具備するようにしても良い。

### 【発明の効果】

### 【0010】

本発明によれば、カウンタによって得られたカウント値が所定の値に達したときに昇圧回路に供給されるクロック信号の周波数を切り換えることにより、予め定められた周波数のクロック信号を用いながら迅速な起動と消費電流の低減とを両立させることができる。

### 【発明を実施するための最良の形態】

### 【0011】

以下、本発明を実施するための最良の形態について、図面を参照しながら詳しく説明する。なお、同一の構成要素には同一の参照番号を付して、説明を省略する。

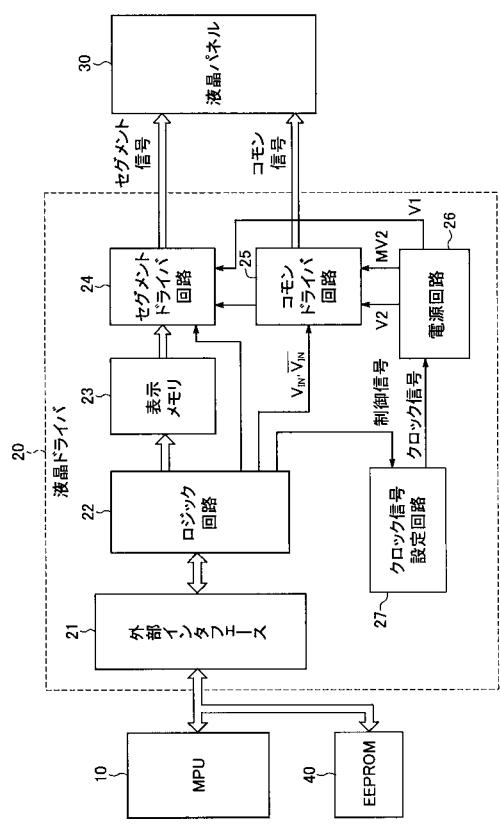

図1は、本発明の第1の実施形態に係る半導体集積回路（液晶ドライバ）及びその周辺回路の構成を示すブロック図である。液晶ドライバ20は、MPU（マイクロプロセッサ）10と、液晶パネル30とに接続されている。液晶ドライバ20は液晶パネル30に実装されており、これらは液晶モジュールを構成する。MPU10は、画像情報を表す画像

10

20

30

40

50

データの演算及び制御を行い、演算によって得られた表示用の画像データと、画像データの記憶領域を制御するアドレスと、書き込み制御信号や読み出し制御信号を含む各種の制御信号とを液晶ドライバ20に出力する。

【0012】

さらに、図1に示すように、MPU10及び液晶ドライバ20に、EEPROM40が接続されるようにしても良い。EEPROM40には、液晶ドライバ20における昇圧クロック信号の周波数を設定するためのコマンドや、液晶ドライバ20及びその周辺回路を制御するための各種のパラメータ等の情報が格納されている。MPU10は、EEPROM40に格納されている情報を読み出して、液晶ドライバ20及びその周辺回路に情報を送信する。なお、一般に、EEPROM40に格納される情報は、液晶モジュールメーカーによって設定されるので、携帯電話等を製造するセットメーカーにおいては、その内容を変更することができない。

【0013】

液晶ドライバ20は、表示用の画像データ等をMPU10から受信する外部インターフェース21と、受信された画像データを処理すると共に、液晶パネルにおける画像表示を制御するためのタイミング信号（差動信号 $V_{IN}$ 及び $V_{IN}$ バー）を生成するロジック回路22と、画像データを一時的に格納するための表示メモリ23と、表示メモリ23に格納されている画像データに基づいて、液晶パネルを駆動するためのセグメント信号を生成するセグメントドライバ回路24と、ロジック回路22から供給されるタイミング信号のレベルをシフトすることによりコモン信号を生成するコモンドライバ回路25とを有している。

【0014】

さらに、液晶ドライバ20は、外部から供給される電源電圧を昇圧回路によって昇圧して複数種類の電源電圧を発生し、これらの電源電圧をセグメントドライバ回路24及びコモンドライバ回路25に供給する電源回路26と、電源回路26内の昇圧回路に供給される昇圧クロック信号（以下、単に「クロック信号」という）の周波数を設定するクロック信号設定回路27とを有している。また、ロジック回路22は、電源回路26をスリープモードと通常動作モードとの間で切り換えるために、クロック信号設定回路27を制御するための制御信号を生成する。

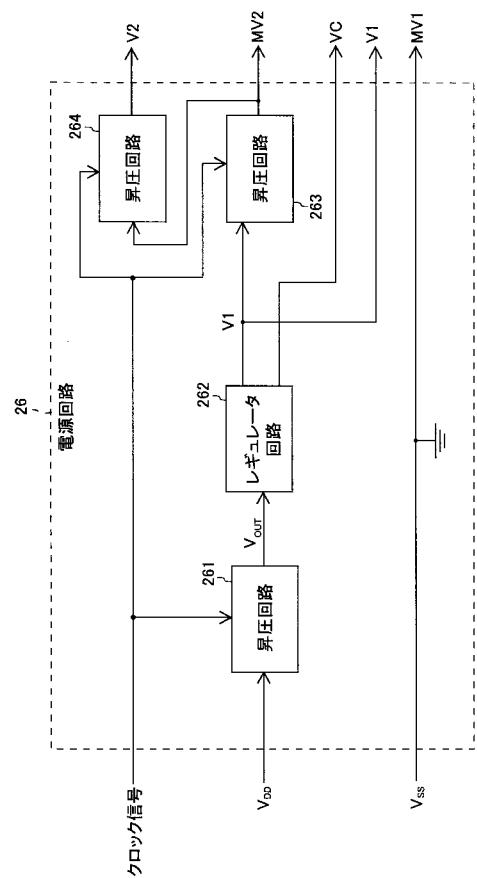

【0015】

図2は、図1に示す電源回路の構成を示すブロック図である。電源回路26は、外部から供給される電源電圧 $V_{DD}$ （例えば、3V）を昇圧して2倍の昇圧電圧 $V_{OUT}$ を生成する昇圧回路261と、昇圧回路261から出力される昇圧電圧 $V_{OUT}$ を安定化することによってセグメント信号生成用の電源電圧 $V_1$ （例えば、5V）及びコモン信号の中間電圧 $V_C$ （例えば、2.5V）を生成するレギュレータ回路262と、レギュレータ回路262から出力される電源電圧 $V_1$ を逆極性で昇圧してコモン信号生成用の電源電圧 $MV_2$ （例えば、-10V）を発生する昇圧回路263と、昇圧回路263から出力される電源電圧 $MV_2$ を逆極性で昇圧してコモン信号生成用の電源電圧 $V_2$ を発生する昇圧回路264とを含んでいる。なお、外部から供給される電源電圧 $V_{SS}$ （例えば、0V）は、セグメント信号生成用の電源電圧 $MV_1$ として用いられる。

【0016】

ここで、昇圧回路261、263、264の各々は、クロック信号に従ってスイッチングを行う複数のトランジスタ、及び、これらのトランジスタにそれぞれ接続された複数のコンデンサを含み、チャージポンプ動作により電源電圧を昇圧して昇圧電圧を生成する。一般に、昇圧回路の昇圧能力は、使用されるコンデンサの容量とクロック信号の周波数によって決まる。

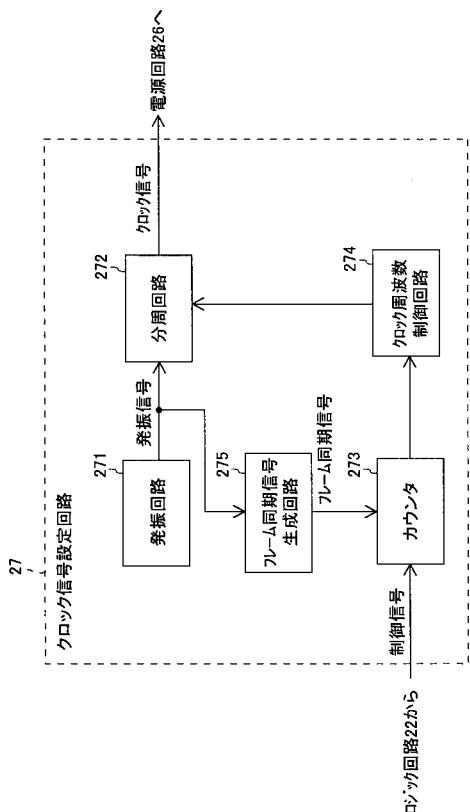

【0017】

図3は、図1に示すクロック信号設定回路の構成を示すブロック図である。クロック信号設定回路27は、所定の周波数を有する発振信号を生成する発振回路271と、発振回路271によって生成された発振信号を分周してクロック信号を生成する分周回路272

10

20

30

40

50

と、フレーム同期信号に含まれているパルスをカウントすることによりカウント値を得るカウンタ273と、カウンタ273によって得られたカウント値に基づいて、電源回路26(図2)内の昇圧回路に供給されるクロック信号の周波数を制御するクロック周波数制御回路274とを含んでいる。

【0018】

カウンタ273は、ロジック回路22(図1)から供給される制御信号が活性化されると、フレーム同期信号に含まれているパルスのカウントを開始する。フレーム同期信号は、フレーム同期信号生成回路275において発振信号を分周することにより生成しても良いし、外部から供給しても良い。

【0019】

また、分周回路272は、発振回路271によって生成された発振信号を、クロック周波数制御回路274によって設定された分周比で分周することにより、クロック信号を生成する。クロック周波数制御回路274は、起動時に第1の分周比を分周回路272に設定し、カウンタ273によって得られたカウント値が所定の値に達したときに第2の分周比を分周回路272に設定することにより、昇圧回路に供給されるクロック信号の周波数を制御する。

【0020】

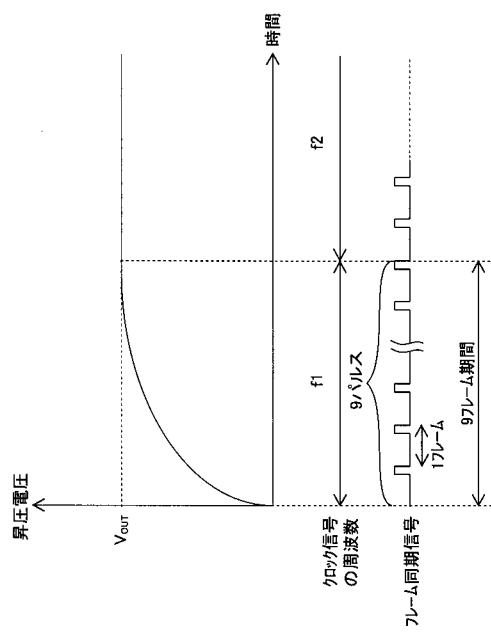

次に、本実施形態に係る半導体装置の動作について、図1～図4を参照しながら説明する。

図4は、起動時において昇圧回路261から出力される昇圧電圧の立ち上がりを示す波形図である。ここで、起動時とは、電源投入時と、スリープモードから通常動作モードへの移行時との両方を意味する。起動時において、ロジック回路22から供給される制御信号が活性化されると、カウンタ273は、フレーム同期信号に含まれているパルスのカウントを開始する。

【0021】

クロック周波数制御回路274は、起動時に第1の分周比を分周回路272に設定する。これにより、分周回路272から出力されるクロック信号の周波数は、 $f_1$ (例えば、 $20\text{ kHz}$ )となっている。カウンタ273は、カウント値が所定の値(例えば、「9」)に達したときに、その結果をクロック周波数制御回路274に出力する。これに応答して、クロック周波数制御回路274は、第1の分周比よりも大きい第2の分周比を分周回路272に設定する。これにより、分周回路272から出力されるクロック信号の周波数は、 $f_2$ (例えば、 $5\text{ kHz}$ )となる(ここで、 $f_2 < f_1$ とする)。

【0022】

その結果、起動時から9フレーム期間(約 $150\text{ msec}$ )においては、クロック信号の周波数が高いので昇圧電圧が急速に立ち上がり、その後はクロック周波数が低くなるので、昇圧回路261における消費電流が低減される。また、液晶ドライバICによっては、昇圧回路に供給されるクロック信号の周波数が所定の値( $f_0$ とする)よりも低いと電源が立ち上がらない場合があるが、本実施形態によれば、 $f_1 > f_0$ となるように発振回路271の発振周波数及び分周回路272における分周比を設定することにより、確実に電源を立ち上げることができる。

【0023】

一方、電源立ち上がり後の定常状態においては、他の回路に与えるノイズの影響の観点から、クロック信号の周波数は一定である方が良い。本実施形態においては、電源立ち上がり時点においてクロック信号の周波数を自動的に切り換えるが、その後はクロック信号の周波数を一定に保つ。これにより、クロック信号の周波数ゆれに起因するノイズの影響を低減することができる。また、昇圧電圧を監視するためのオペアンプ等のアナログ回路が不要であり、回路構成を簡単にすることができる。さらに、半導体集積回路の検査工程において、電源の立ち上がり時の評価を行う際にも、固定のクロック周波数に対して評価を行えば良いので検査が簡単になる。

【0024】

10

20

30

40

50

次に、本発明の第2の実施形態について説明する。

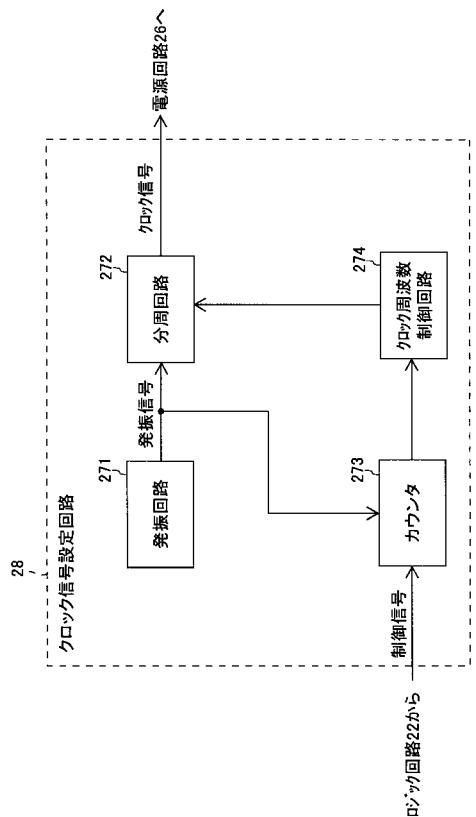

図5は、本発明の第2の実施形態に係る半導体集積回路において用いられるクロック信号設定回路の構成を示すブロック図である。第2の実施形態においては、図3に示すクロック信号設定回路27の替わりに、図5に示すクロック信号設定回路28が用いられる。その他の構成については、図1に示す第1の実施形態と同様である。

#### 【0025】

図5に示すように、クロック信号設定回路28は、所定の周波数を有する発振信号を生成する発振回路271と、発振回路271によって生成された発振信号を設定された分周比で分周することにより、電源回路26内の昇圧回路に供給されるクロック信号を生成する分周回路272と、発振回路271によって生成された発振信号に含まれているパルスをカウントすることによりカウント値を得るカウンタ273と、カウンタ273によって得られたカウント値に基づいて、昇圧回路に供給されるクロック信号の周波数を制御するクロック周波数制御回路274とを含んでいる。

#### 【0026】

カウンタ273は、ロジック回路22(図1)から供給される制御信号が活性化されると、発振信号に含まれているパルスのカウントを開始する。また、分周回路272は、発振回路271によって生成された発振信号を、クロック周波数制御回路274によって設定された分周比で分周することにより、クロック信号を生成する。クロック周波数制御回路274は、起動時に第1の分周比を分周回路272に設定し、カウンタ273によって得られたカウント値が所定の値に達したときに第2の分周比を分周回路272に設定することにより、昇圧回路に供給されるクロック信号の周波数を制御する。

#### 【0027】

上記においては、カウンタ273が、発振回路271によって生成される発振信号に含まれているパルスをカウントすることによりカウント値を得る場合について説明したが、カウンタ273が、分周回路272から出力されるクロック信号に含まれているパルスをカウントすることによりカウント値を得るようしても良い。

#### 【図面の簡単な説明】

#### 【0028】

【図1】本発明の第1の実施形態に係る半導体集積回路の構成を示すブロック図。

【図2】図1に示す電源回路の構成を示すブロック図。

30

【図3】図1に示すクロック信号設定回路の構成を示すブロック図。

【図4】起動時において昇圧回路から出力される昇圧電圧の立ち上がりを示す波形図。

【図5】第2の実施形態において用いられるクロック信号設定回路を示すブロック図。

#### 【符号の説明】

#### 【0029】

10 M P U、20 液晶ドライバ、21 外部インタフェース、22 ロジック回路、23 表示メモリ、24 セグメントドライバ回路、25 コマンドライバ回路、26 電源回路、27、28 クロック信号設定回路、30 液晶パネル、40 E E P R O M、261、263、264 昇圧回路、262 レギュレータ回路、271 発振回路、272 分周回路、273 カウンタ、274 クロック周波数制御回路、275 フレーム同期信号生成回路

40

【図1】

【図2】

【図3】

【図4】

【図5】

## フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

G 0 9 G 3/20 6 7 0 D

G 0 9 G 3/20 6 1 1 A

G 0 2 F 1/133 5 2 0

F ターム(参考) 2H093 NC03 NC16 NC27 NC34 NC35 NC50 ND39 ND40 NF13

5C006 AF51 AF53 AF61 AF67 AF72 BB12 BF22 BF42 BF49 FA11

FA47 FA48

5C080 AA10 BB05 DD08 DD26 FF12 JJ02 JJ04 JJ05

5H730 AA14 AS04 BB02 BB57 BB81 BB86 EE53 FF07 FG01 XC03