(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4330516号

(P4330516)

(45) 発行日 平成21年9月16日(2009.9.16)

(24) 登録日 平成21年6月26日(2009.6.26)

(51) Int.Cl.

F 1

G 11 C 11/413 (2006.01)

G 11 C 11/34 301 A

G 11 C 11/412 (2006.01)

G 11 C 11/34 335 A

G 11 C 11/40 301

請求項の数 14 (全 28 頁)

(21) 出願番号 特願2004-310078 (P2004-310078)

(22) 出願日 平成16年10月25日 (2004.10.25)

(65) 公開番号 特開2006-73165 (P2006-73165A)

(43) 公開日 平成18年3月16日 (2006.3.16)

審査請求日 平成19年10月24日 (2007.10.24)

(31) 優先権主張番号 特願2004-228553 (P2004-228553)

(32) 優先日 平成16年8月4日 (2004.8.4)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000005821

パナソニック株式会社

大阪府門真市大字門真1006番地

(74) 代理人 100098291

弁理士 小笠原 史朗

(72) 発明者 山上 由展

大阪府門真市大字門真1006番地 松下

電器産業株式会社内

審査官 須原 宏光

(56) 参考文献 特開2003-123479 (JP, A)

特開平06-338197 (JP, A)

最終頁に続く

(54) 【発明の名称】半導体記憶装置

## (57) 【特許請求の範囲】

## 【請求項 1】

電源電圧制御機能を有する半導体記憶装置であって、

ワード線と、

ビット線と、

電源線と、

前記ワード線と前記ビット線と前記電源線とに接続されたメモリセルと、

活性なワード線に接続された前記メモリセルに対しては、前記電源線を介して、所定の電源電圧を供給し、非活性なワード線に接続された前記メモリセルに対しては、前記電源線を介して、前記所定の電源電圧よりも低く、かつ、前記メモリセルがデータを保持できる最低レベル以上の電圧を供給するメモリセル電源電圧制御回路とを備え、

10

前記メモリセル電源電圧制御回路は、直列接続された第1～3のトランジスタを含み、前記第1のトランジスタは、前記所定の電源電圧が印加される電源端子と前記第2のトランジスタとに接続され、

前記第2のトランジスタは、前記第1のトランジスタと前記第2のトランジスタとの間に、ダイオード型にゲート接続され、

前記第3のトランジスタは、前記第2のトランジスタと接地端子とに接続され、

前記第1および第3のトランジスタは、外部から供給されるアドレス信号に基づいて制御されることを特徴とする、半導体記憶装置。

## 【請求項 2】

20

前記第2のトランジスタの閾値電圧の絶対値が、前記メモリセルに含まれる全てのトランジスタの閾値電圧の最大値以上であることを特徴とする、請求項1に記載の半導体記憶装置。

【請求項3】

前記メモリセル電源電圧制御回路は、前記アドレス信号が活性状態を示すときには前記所定の電源電圧を、前記アドレス信号が非活性状態を示すときには第2のトランジスタの閾値電圧を出力することを特徴とする、請求項2に記載の半導体記憶装置。

【請求項4】

前記メモリセル電源電圧制御回路は、前記ワード線が活性状態になる前に、前記メモリセルに前記所定の電源電圧を供給することを特徴とする、請求項1に記載の半導体記憶装置。 10

【請求項5】

前記メモリセル電源電圧制御回路は、複数の前記ワード線に接続された複数の前記メモリセルに対して同じ電源電圧を供給することを特徴とする、請求項1に記載の半導体記憶装置。

【請求項6】

前記電源線は、前記メモリセルが含まれるメモリセルアレイにおける基板電位供給領域に配線され、

前記メモリセル電源電圧制御回路は、前記基板電位供給領域に隣接し、かつ、ワード線ドライバ回路領域に隣接する領域に配置されることを特徴とする、請求項1に記載の半導体記憶装置。 20

【請求項7】

前記メモリセルに供給される電源電圧が前記メモリセルがデータを保持できる最低レベルの電圧よりも低くなることを防止するメモリセル電源電圧補償回路をさらに備える、請求項1に記載の半導体記憶装置。

【請求項8】

前記メモリセル電源電圧補償回路は、前記所定の電源電圧が印加される電源端子と前記電源線とに接続された電荷供給素子を含むことを特徴とする、請求項7に記載の半導体記憶装置。 30

【請求項9】

前記メモリセル電源電圧制御回路は、前記所定の電源電圧が印加される電源端子と接地端子との間に直列に接続された第1～3のトランジスタを備え、

前記第1のトランジスタは、前記所定の電源電圧が印加される電源端子に接続され、

前記第2のトランジスタは、ダイオード型にゲート接続され、

前記第1および第3のトランジスタは、外部から供給されるアドレス信号に基づいて制御され、

前記第1のトランジスタは、前記メモリセル電源電圧補償回路として機能することを特徴とする、請求項7に記載の半導体記憶装置。 40

【請求項10】

前記メモリセル電源電圧補償回路は、

前記電源線を介して前記メモリセルに供給される電源電圧と当該電源電圧の基準電圧とを比較する比較回路と、

前記比較回路から出力される信号に応じて、前記所定の電源電圧が印加される電源端子と前記電源線とを導通および短絡するスイッチ素子とを備え、

前記メモリセルに供給される電源電圧を前記基準電圧以上に保持することを特徴とする、請求項7に記載の半導体記憶装置。

【請求項11】

前記比較回路および前記スイッチ素子は、外部から供給されるアドレス信号が活性状態を示すときには動作を停止することを特徴とする、請求項10に記載の半導体記憶装置。

【請求項12】

10

20

30

40

50

前記ビット線をプリチャージするか否かを制御する制御信号が供給されるビット線プリチャージ制御信号線と、

前記ビット線と前記ビット線プリチャージ制御信号線とに接続され、前記制御信号に基づいてビット線をプリチャージするビット線プリチャージ回路と、

外部からの信号に基づいて前記制御信号を前記ビット線プリチャージ制御信号線に出力するビット線プリチャージ制御回路とをさらに備え、

前記ビット線プリチャージ制御回路は、活性な前記ワード線が非活性な状態になる際に、前記ワード線に接続された前記メモリセルの前記電源線に蓄積された電荷を、前記ビット線プリチャージ制御信号線に供給することを特徴とする、請求項1に記載の半導体記憶装置。

10

### 【請求項 1 3】

前記メモリセルの代替として使用可能な冗長救済用メモリセルと、前記冗長救済用メモリセルに供給される電源電圧を、前記メモリセル電源電圧制御回路から供給される電源電圧および接地電位のいずれかに切り替えるスイッチ素子とを含む冗長救済ブロックをさらに備え、

前記メモリセルの代替として使用されない冗長救済用メモリセルを含む冗長救済ブロックでは、前記スイッチ素子は接地電位を出力することを特徴とする、請求項1に記載の半導体記憶装置。

### 【請求項 1 4】

前記メモリセルの代替として使用可能な冗長救済用メモリセルと、前記メモリセルに供給される電源電圧を、前記メモリセル電源電圧制御回路から供給される電源電圧および接地電位のいずれかに切り替えるスイッチ素子とをさらに備え、

前記冗長救済用メモリセルによって代替されるメモリセルでは、前記スイッチ素子は接地電位を出力することを特徴とする、請求項1に記載の半導体記憶装置。

20

### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、半導体記憶装置に関し、より特定的には、メモリセルアレイ部の低消費電力化および高速化を実現する半導体記憶装置に関する。

#### 【背景技術】

30

#### 【0002】

近年、半導体集積回路では、プロセスの微細化に伴い、スタンバイ状態におけるトランジスタのリーク電流（オフリーク電流やゲートリーク電流など）の増加が問題となっている。また、近年では、S R A M、D R A M、R O M等の半導体記憶装置の容量は、飛躍的に増加している。このため、半導体集積回路では、内蔵される半導体記憶装置に含まれるメモリセルアレイの消費電力が、回路全体の消費電力のうちで大きな割合を占めるに至っている。したがって、半導体集積回路を低消費電力化するためには、半導体記憶装置に含まれるメモリセルアレイを低消費電力化することが効果的である。

#### 【0003】

半導体記憶装置に含まれるメモリセルアレイの低消費電力化に関する従来例としては、例えば、特許文献1に記載されている方法がある。特許文献1に記載の半導体記憶装置は、メモリセルを構成するN型M O Sトランジスタの基板電極にバックバイアス電圧を供給することにより、スタンバイ時におけるサブスレッショルド電流によるリーク電流を低減する。これにより、半導体記憶装置の低消費電力化が図られる。

40

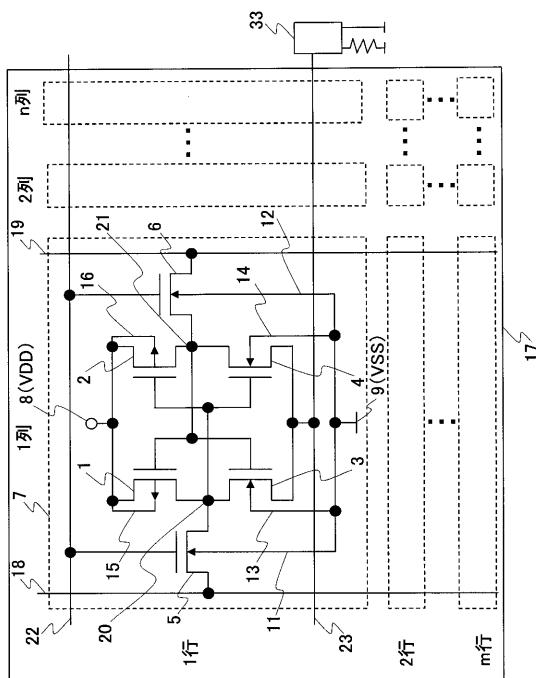

#### 【0004】

また、その他の従来例としては、特許文献2に記載されている方法がある。図17は、特許文献2に記載の半導体記憶装置の構成図である。図17に示す半導体記憶装置は、m行n列に配置された完全C M O S型のメモリセル7から構成されるメモリセルアレイ17を備える。メモリセル7は、負荷用P型M O S F E T（以下、負荷用P M O Sという）1および2、駆動用N型M O S F E T（以下、駆動用N M O Sという）3および4、並びに

50

、転送用N型MOSFET(以下、転送用NMOSという)5および6を備える。

【0005】

負荷用PMOS1および2のソース電極、負荷用PMOS1の基板電極15、並びに、負荷用PMOS2の基板電極16は、いずれも電源端子8(電源電圧VDD)に接続される。また、負荷用PMOS1および2のドレイン電極は、それぞれ、メモリセルの記憶ノード20および21に接続される。駆動用NMOS3の基板電極13、および、駆動用NMOS4の基板電極14は、共に接地端子9(接地電位VSS)に接続される。また、駆動用NMOS3および4のソース電極は、共にソース線23に接続され、ドレイン電極は、それぞれ、記憶ノード20および21に接続される。

【0006】

転送用NMOS5の基板電極11、および、転送用NMOS6の基板電極12は、共に接地端子9に接続される。また、転送用NMOS5および6のゲート電極は、共にワード線22に接続され、ドレイン電極はビット線18および19に、ソース電極は記憶ノード20および21にそれぞれ接続される。記憶ノード20は、負荷用PMOS2および駆動用NMOS4のゲート電極に接続され、記憶ノード21は、負荷用PMOS1および駆動用NMOS3のゲート電極に接続される。以上のように、メモリセル7内の負荷用PMOS1および2、並びに、駆動用NMOS3および4は、ラッチ回路を構成する。

【0007】

メモリセル7には、ソース線23を介して、スイッチ回路33が接続される。スイッチ回路33の構成の説明は省略するが、以下、その動作を簡単に説明する。スイッチ回路33は、活性状態にあるメモリセル7に接続されたソース線23に対しては、接地電位VSSを供給し、非活性状態にあるメモリセル7に接続されたソース線23に対しては、電源電圧VDDと接地電位VSSとの中間電位(特許文献2の実施形態では、0.5Vに設定されている)を供給する。

【0008】

メモリセル7が非活性状態であるときには、スイッチ回路33は、メモリセル7に接続されるソース線23の電位を上記の中間電位まで上げる。この結果、駆動用NMOS3および4の閾値電圧が基板バイアス効果により上昇し、メモリセル7からのサブスレッシュルド電流によるリーク電流が低減される。特許文献2に記載の半導体記憶装置は、以上のように、スイッチ回路によって各メモリセルの駆動用NMOSのソース電位を制御することにより、消費電力を低減する。

【特許文献1】特開平7-211079号公報

【特許文献2】特開平10-112188号公報

【発明の開示】

【発明が解決しようとする課題】

【0009】

しかしながら、上記従来の半導体記憶装置には、以下に述べるような問題がある。特許文献1および2に記載の半導体記憶装置は、いずれも基板バイアス効果によってトランジスタの閾値電圧を上げることにより、メモリセルからのリーク電流を低減する。したがって、これらの装置では、トランジスタの閾値電圧が上昇することにより、低電源電圧でのトランジスタの動作特性が悪化する。また、特許文献1に記載の半導体記憶装置においては、バックバイアス電圧を供給するための制御回路が必要であるため、回路の面積が増加するという問題がある。また、特許文献2に記載の半導体記憶装置においても、ソース線に電圧を供給するスイッチ回路が必要であるため、回路の面積が増加するという問題がある。

【0010】

それ故に、本発明は、メモリセルにおけるリーク電流を効果的に抑制することにより、低電源電圧での動作特性の優れた、低消費電力、かつ、高速な半導体記憶装置を提供することを目的とする。

【課題を解決するための手段】

10

20

30

40

50

## 【0011】

本発明の半導体記憶装置は、ワード線と、ビット線と、電源線と、ワード線とビット線と電源線とに接続されたメモリセルとに加えて、活性なワード線に接続されたメモリセルに対しては、電源線を介して、所定の電源電圧を供給し、非活性なワード線に接続されたメモリセルに対しては、電源線を介して、所定の電源電圧よりも低く、かつ、メモリセルがデータを保持できる最低レベル以上の電圧を供給するメモリセル電源電圧制御回路とを備える。

## 【0012】

また、メモリセル電源電圧制御回路は、直列接続された第1～3のトランジスタを備え、第1のトランジスタは、所定の電源電圧が印加される電源端子と第2のトランジスタとに接続され、第2のトランジスタは、第1のトランジスタと第2のトランジスタとの間にダイオード型にゲート接続され、第3のトランジスタは、第2のトランジスタと接地端子とに接続され、第1および第3のトランジスタは、外部から供給されるアドレス信号に基づいて制御される。

10

## 【0013】

また、第2のトランジスタの閾値電圧の絶対値が、メモリセルに含まれる全てのトランジスタの閾値電圧の最大値以上であることが好ましい。

## 【0014】

さらに、メモリセル電源電圧制御回路は、アドレス信号が活性状態を示すときには所定の電源電圧を、アドレス信号が非活性状態を示すときには第2のトランジスタの閾値電圧を出力することが好ましい。

20

## 【0015】

また、メモリセル電源電圧制御回路は、ワード線が活性状態になる前に、メモリセルに所定の電源電圧を供給することが好ましい。

## 【0016】

さらに、メモリセル電源電圧制御回路は、複数のワード線に接続された複数のメモリセルに対して同じ電源電圧を供給することが好ましい。

30

## 【0017】

また、電源線は、メモリセルが含まれるメモリセルアレイにおける基板電位供給領域に配線され、さらに、メモリセル電源電圧制御回路は、基板電位供給領域に隣接し、かつ、ワード線ドライバ回路領域に隣接する領域に配置されることが好ましい。

## 【0018】

また、本発明の半導体記憶装置は、メモリセルに供給される電源電圧がメモリセルがデータを保持できる最低レベルの電圧よりも低くなることを防止するためのメモリセル電源電圧補償回路を備えることが好ましい。

## 【0019】

メモリセル電源電圧補償回路は、所定の電源電圧が印加される電源端子と電源線とに接続された電荷供給素子を含んでいてもよい。

## 【0020】

また、第1のトランジスタは、メモリセル電源電圧補償回路として機能してもよい。

40

## 【0021】

また、メモリセル電源電圧補償回路は、電源線を介してメモリセルに供給される電源電圧とこの電源電圧の基準電圧とを比較する比較回路と、この比較回路から出力される信号に応じて、所定の電源電圧が印加される電源端子と電源線とを導通および短絡するスイッチ素子とを備えることにより、メモリセルに供給される電源電圧を基準電圧以上に保持することが好ましい。

## 【0022】

さらに、比較回路およびスイッチ素子は、外部から供給されるアドレス信号が活性状態を示すときには動作を停止することが好ましい。

## 【0023】

50

また、本発明の半導体記憶装置は、ビット線をプリチャージするか否かを制御する制御信号が供給されるビット線プリチャージ制御信号線と、ビット線とビット線プリチャージ制御信号線とに接続され、制御信号に基づいてビット線をプリチャージするビット線プリチャージ回路と、外部からの信号に基づいて制御信号をビット線プリチャージ制御信号線に出力するビット線プリチャージ制御回路とをさらに備え、活性なワード線が非活性な状態になる際に、ワード線に接続されたメモリセルの電源線に蓄積された電荷を、ビット線プリチャージ制御回路がビット線プリチャージ制御信号線に供給することが好ましい。

【0024】

より好ましくは、本発明の半導体記憶装置は、メモリセルの代替として使用可能な冗長救済用メモリセルと、冗長救済用メモリセルに供給される電源電圧を、メモリセル電源電圧制御回路から供給される電源電圧および接地電位のいずれかに切り替えるスイッチ素子を含む冗長救済ブロックを備えていてもよい。メモリセルの代替として使用されない冗長救済用メモリセルを含む冗長救済ブロックでは、スイッチ素子は接地電位を出力することが好ましい。

【0025】

さらに、本発明の半導体記憶装置は、メモリセルの代替として使用可能な冗長救済用メモリセルと、メモリセルに供給される電源電圧を、メモリセル電源電圧制御回路から供給される電源電圧および接地電位のいずれかに切り替えるスイッチ素子とを備えていてもよい。冗長救済用メモリセルによって代替されるメモリセルでは、スイッチ素子は接地電位を出力することが好ましい。

【発明の効果】

【0026】

本発明の半導体記憶装置は、活性なワード線に接続されたメモリセルに対しては、電源線を介して、所定の電源電圧を供給し、非活性なワード線に接続されたメモリセルに対しては、電源線を介して、所定の電源電圧よりも低く、かつ、メモリセルがデータを保持できる最低レベル以上の電圧を供給するメモリセル電源電圧制御回路を備える。したがって、本発明の半導体記憶装置は、メモリセルに記憶されるデータを正常に保持することができる限界の電圧（メモリセル保持電圧）まで、メモリセルに供給する電源電圧を低下させることができる。これにより、本発明の半導体記憶装置は、メモリセルからのリーク電流を低減し、半導体記憶装置の低消費電力化を実現する。また、本発明の半導体記憶装置は、メモリセルからのリーク電流を低減することにより、メモリセルからビット線に流れ出するリーク電流、あるいは、ビット線からメモリセルに流れ込むリーク電流を低減し、半導体記憶装置の書き込みおよび読み出し動作の高速化を実現する。さらに、本発明の半導体記憶装置は、従来の半導体記憶装置のように、基板バイアス効果によって閾値電圧を上昇させないことから、従来の半導体記憶装置と比較して、低電源電圧での動作性に優れている。

【0027】

メモリセル電源電圧制御回路は、直列接続された第1～3のトランジスタを備えており、第1のトランジスタが所定の電源電圧が印加される電源端子と第2のトランジスタとに接続され、第2のトランジスタが第1のトランジスタと第2のトランジスタとの間にダイオード型にゲート接続され、第3のトランジスタが第2のトランジスタと接地端子とに接続され、第1および第3のトランジスタが外部から供給されるアドレス信号に基づいて制御されるといった構成を有する。したがって、メモリセル電源電圧制御回路は、所定の電源電圧および第2のトランジスタの閾値電圧のいずれかを、ワード線の状態（活性あるいは非活性）に応じて、メモリセルに対して供給することが可能である。

【0028】

また、メモリセル電源電圧制御回路に含まれる第2のトランジスタの閾値電圧の絶対値は、メモリセルに含まれる全てのトランジスタの閾値電圧の最大値以上であり、さらに、メモリセル電源電圧制御回路は、アドレス信号が活性状態を示すときには所定の電源電圧を、アドレス信号が非活性状態を示すときには第2のトランジスタの閾値電圧を出力する

10

20

30

40

50

。これにより、メモリセル電源電圧制御回路は、周辺回路に含まれるトランジスタの特性とメモリセルに含まれるトランジスタの特性とが異なる場合においても、メモリセルに対してメモリセル保持電圧を供給することができる。

#### 【0029】

また、メモリセル電源電圧制御回路は、ワード線が活性状態になる前に、メモリセルに所定の電源電圧を供給する。すなわち、メモリセルに供給される電源が確実に復帰した後にワード線が活性化する。これにより、半導体記憶装置の高速な読み出しあり書き込み動作が実現される。

#### 【0030】

また、メモリセル電源電圧制御回路は、複数のワード線に接続された複数のメモリセルに対して同じ電源電圧を供給する。また、メモリセル電源電圧制御回路に接続される電源線は、メモリセルが含まれるメモリセルアレイにおける基板電位供給領域に配線され、メモリセル電源電圧制御回路は、基板電位供給領域に隣接し、かつ、ワード線ドライバ回路領域に隣接する領域に配置される。これにより、メモリセル電源電圧制御回路が付加されることによる半導体記憶装置の面積の増加を抑えることができる。

10

#### 【0031】

また、本発明の半導体記憶装置は、メモリセルに供給される電源電圧がメモリセルがデータを保持できる最低レベルの電圧よりも低くなることを防止するためのメモリセル電源電圧補償回路を備える。このメモリセル電源電圧補償回路は、所定の電源電圧が印加される電源端子と電源線とに接続された電荷供給素子を含むことにより、メモリセルからのリード電流による電源電圧の低下を防止する。これにより、非活性なワード線に接続されるメモリセルに対して、常に安定したメモリセル保持電圧が供給される。

20

#### 【0032】

また、本発明の半導体記憶装置は、メモリセル電源電圧制御回路に含まれる第1のトランジスタをメモリセル電源電圧補償回路として使用することも可能である。これにより、メモリセル電源電圧補償回路を付加することによる半導体記憶装置の面積の増加を防ぐことができる。

#### 【0033】

また、メモリセル電源電圧補償回路は、電源線を介してメモリセルに供給される電源電圧とこの電源電圧の基準電圧とを比較する比較回路と、この比較回路から出力される信号に応じて、所定の電源電圧が印加される電源端子と電源線とを導通および短絡するスイッチ素子とを備えることにより、メモリセルに供給される電源電圧を基準電圧以上に保持する。これにより、非活性なワード線に接続されるメモリセルに対して、常に安定したメモリセル保持電圧を供給することができる。

30

#### 【0034】

さらに、比較回路およびスイッチ素子は、外部から供給されるアドレス信号が活性状態を示すときには動作を停止する。これにより、ワード線が非活性な場合には、比較回路で消費される電力が削減でき、半導体記憶装置の低消費電力化が実現される。

#### 【0035】

また、本発明の半導体記憶装置は、ビット線をプリチャージするか否かを制御する制御信号が供給されるビット線プリチャージ制御信号線と、ビット線とビット線プリチャージ制御信号線とに接続され、制御信号に基づいてビット線をプリチャージするビット線プリチャージ回路と、外部からの信号に基づいて制御信号をビット線プリチャージ制御信号線に出力するビット線プリチャージ制御回路とをさらに備え、活性なワード線が非活性な状態になる際に、ワード線に接続されたメモリセルの電源線に蓄積された電荷を、ビット線プリチャージ制御回路がビット線プリチャージ制御信号線に供給する。これにより、電源線に蓄積された電荷が再利用されることから、半導体記憶装置の低消費電力化が実現される。

40

#### 【0036】

本発明の半導体記憶装置は、メモリセルの代替として使用可能な冗長救済用メモリセル

50

と、冗長救済用メモリセルに供給される電源電圧を、メモリセル電源電圧制御回路から供給される電源電圧および接地電位のいずれかに切り替えるスイッチ素子を含む冗長救済ブロックをさらに備える。また、メモリセルの代替として使用されない冗長救済用メモリセルを含む冗長救済ブロックでは、スイッチ素子は接地電位を出力する。これにより、冗長救済ブロックに含まれるメモリセルのリーク電流を削減することができ、半導体記憶装置の低消費電力化が実現される。

#### 【0037】

さらに、本発明の半導体記憶装置は、メモリセルの代替として使用可能な冗長救済用メモリセルと、メモリセルに供給される電源電圧を、メモリセル電源電圧制御回路から供給される電源電圧および接地電位のいずれかに切り替えるスイッチ素子とを備える。また、冗長救済用メモリセルによって代替されるメモリセルでは、スイッチ素子は接地電位を出力する。これにより、冗長救済ブロックによって置換されるメモリセルアレイのリーク電流が削減でき、半導体記憶装置の低消費電力化が実現される。10

#### 【発明を実施するための最良の形態】

#### 【0038】

##### (第1の実施形態)

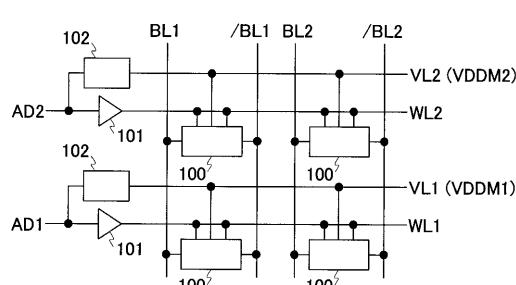

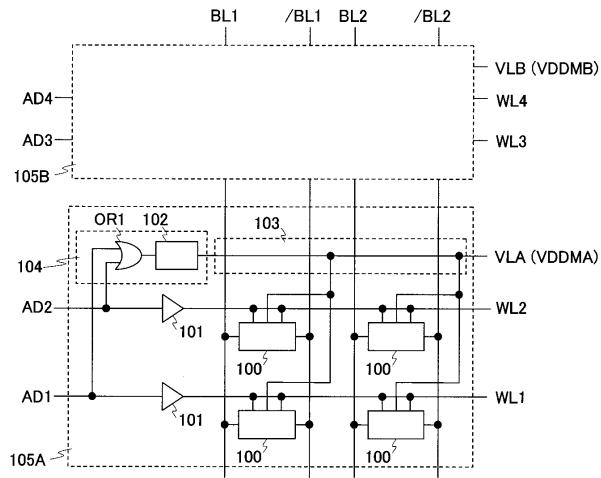

図1は、本発明の第1の実施形態に係る半導体記憶装置の構成図である。図1に示す半導体記憶装置は、メモリセル100、ワード線ドライバ回路101、メモリセル電源電圧制御回路102、ワード線WL1およびWL2、ビット線BL1、BL2、/BL1および/BL2、並びに、電源線VL1およびVL2を備える。メモリセル100は、ワード線WL1(またはWL2)、ビット線BL1および/BL1(またはBL2および/BL2)、並びに、電源線VL1(またはVL2)に接続される。20

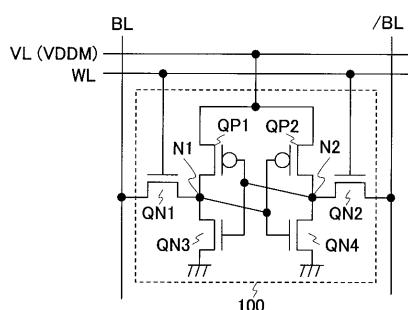

#### 【0039】

次に、図2を参照しながらメモリセル100の構成を説明する。図2に示すメモリセル100は、P型MOSトランジスタQ P1およびQ P2、並びに、N型MOSトランジスタQ N1～Q N4を備える。P型MOSトランジスタQ P1およびQ P2のソース電極は、いずれも電源線VLに接続される。また、P型MOSトランジスタQ P1およびQ P2のドレイン電極は、それぞれ、メモリセルの記憶ノードN1およびN2に接続される。P型MOSトランジスタQ P1およびQ P2のソース電極には、電源線VLを介して、メモリセル電源電圧制御回路102からメモリセル電源電圧V D D Mが供給される。30

#### 【0040】

N型MOSトランジスタQ N3およびQ N4のソース電極は共に接地される。N型MOSトランジスタQ N3およびQ N4のドレイン電極は、それぞれ、記憶ノードN1およびN2に接続される。

#### 【0041】

N型MOSトランジスタQ N1およびQ N2のソース電極は、それぞれ、記憶ノードN1およびN2接続される。N型MOSトランジスタQ N1およびQ N2のゲート電極は、共にワード線WLに接続される。N型MOSトランジスタQ N1のドレイン電極は、ビット線BLに接続され、N型MOSトランジスタQ N2のドレイン電極は、ビット線/BLに接続される。N型MOSトランジスタQ N1およびQ N2のゲート電極には、ワード線WLを介して、ワード線ドライバ回路101からアドレス信号A Dが入力される。40

#### 【0042】

記憶ノードN1は、P型MOSトランジスタQ P2およびN型MOSトランジスタQ N4のゲート電極に接続され、記憶ノードN2は、P型MOSトランジスタQ P1およびN型MOSトランジスタQ N3のゲート電極に接続される。以上のように、メモリセル100内のP型MOSトランジスタQ P1およびQ P2、並びに、N型MOSトランジスタQ N3およびQ N4は、ラッチ回路を構成する。

#### 【0043】

このラッチ回路は、データを記憶し保持する。メモリセル100は、ワード線がHレベルの時にデータの読み出し、または、書き込みを行う。データの読み出しとは、ラッチ回50

路に記憶したデータを、ビット線 B L および / B L に出力することであり、データの書き込みとは、ビット線 B L および / B L を介して伝送された相補のデータを、ラッチ回路に入力し記憶することである。また、メモリセル 100 は、ワード線が L レベルの時には、データの読み出し、および、書き込みを行わず、ラッチ回路に記憶されたデータを保持する。

#### 【 0 0 4 4 】

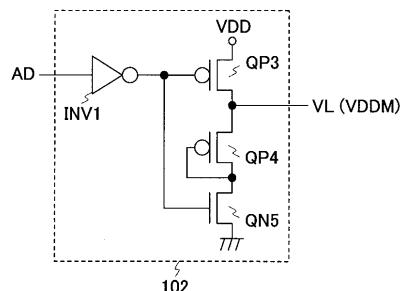

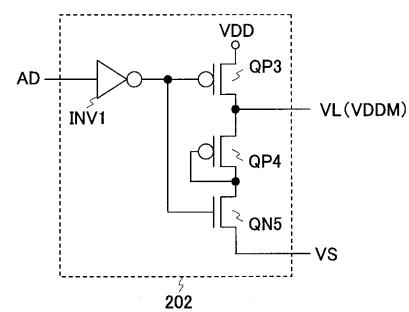

次に、図 3 を参照しながらメモリセル電源電圧制御回路 102 の構成を説明する。図 3 に示すメモリセル電源電圧制御回路 102 は、インバータ IN V 1、P 型 MOS トランジスタ Q P 3 および Q P 4、並びに、N 型 MOS トランジスタ Q N 5 を備える。メモリセル電源電圧制御回路 102 は、メモリセルが接続されるワード線の状態（活性あるいは非活性）に応じて、メモリセルに供給する電源電圧を制御する回路である。 10

#### 【 0 0 4 5 】

P 型 MOS トランジスタ Q P 3 のソース電極は、電源端子 V D D に接続され、ドレン電極は、電源線 V L および P 型 MOS トランジスタ Q P 4 のソース電極に接続され、ゲート電極は、インバータ IN V 1 の出力に接続される。P 型 MOS トランジスタ Q P 4 は、P 型 MOS トランジスタ Q P 3 と N 型 MOS トランジスタ Q N 5 との間に、ダイオード型にゲート接続される。すなわち、P 型 MOS トランジスタ Q P 4 のゲート電極およびドレン電極は、N 型 MOS トランジスタ Q N 5 のドレン電極に接続され、P 型 MOS トランジスタ Q P 4 のソース電極は、P 型 MOS トランジスタ Q P 3 のドレン電極および電源線 V L に接続される。N 型 MOS トランジスタ Q N 5 のゲート電極は、インバータ IN V 1 の出力に接続され、また、ソース電極は接地される。 20

#### 【 0 0 4 6 】

次に、図 3 を参照しながらメモリセル電源電圧制御回路 102 の動作を説明する。インバータ IN V 1 に H レベルのアドレス信号 A D が入力された場合は、P 型 MOS トランジスタ Q P 3 のゲート電極、および、N 型 MOS トランジスタ Q N 5 のゲート電極は、L レベルとなる。この結果、P 型 MOS トランジスタ Q P 3 はオンになり、N 型 MOS トランジスタ Q N 5 はオフになるため、電源電圧 V D D がメモリセル電源電圧 V D D M として、メモリセル電源電圧制御回路 102 から出力される。

#### 【 0 0 4 7 】

これに対して、インバータ IN V 1 に L レベルのアドレス信号 A D が入力された場合は、P 型 MOS トランジスタ Q P 3 のゲート電極、および、N 型 MOS トランジスタ Q N 5 のゲート電極は、H レベルとなる。この結果、P 型 MOS トランジスタ Q P 3 はオフになり、N 型 MOS トランジスタ Q N 5 はオンになる。この場合、電源線 V L の電位は、ダイオード型に接続された P 型 MOS トランジスタ Q P 4 の閾値電圧の絶対値（以下、V T P という）になり、P 型 MOS トランジスタ Q P 4 の閾値電圧の絶対値 V T P (< V D D ) が、メモリセル電源電圧 V D D M として、メモリセル電源電圧制御回路 102 から出力される。 30

#### 【 0 0 4 8 】

次に、図 1 に示す本実施形態に係る半導体記憶装置の動作について説明する。例えば、図 1 において、H レベルのアドレス信号 A D 1 がワード線 W L 1 に入力されたとすると、ワード線 W L 1 は活性状態になり、ワード線 W L 1 に接続されたメモリセル 100 は活性状態になる。この場合、ワード線 W L 1 に接続されたメモリセルに供給されるメモリセル電源電圧 V D D M 1 は、上述したように電源電圧 V D D になる。このとき、L レベルのアドレス信号 A D 2 が、ワード線 W L 2 に入力されたとすると、ワード線 W L 2 は非活性状態になり、ワード線 W L 2 に接続されたメモリセル 100 は非活性状態になる。この場合、ワード線 W L 2 に接続されたメモリセルに供給されるメモリセル電源電圧 V D D M 2 は V T P になる。 40

#### 【 0 0 4 9 】

従来の半導体記憶装置では、ワード線が活性状態あるいは非活性状態にかかわらず、メモリセル電源電圧が電源電圧 V D D であるのに対して、本実施形態に係る半導体記憶装置

10

20

30

40

50

は、上記のワード線W L 2に接続されたメモリセルのように、非活性なワード線に接続されたメモリセルのメモリセル電源電圧をV T Pまで下げる。本実施形態に係る半導体記憶装置は、非活性なワード線に接続されたメモリセルに供給されるメモリセル電源電圧を低くすることにより、メモリセルからのリーク電流を低減する。

#### 【0050】

しかし、メモリセル電源電圧を低くしすぎると、メモリセルに記憶されたデータが消去されてしまうため、メモリセル電源電圧は、メモリセルが正常にデータを保持する電圧に保たれていなければならない。以下、図2を参照しながら、本実施形態に係る半導体記憶装置によれば、メモリセル電源電圧V D D Mを電源電圧V D DからV T Pまで下げるこ10によって、メモリセルに記憶されたデータを正常に保持しつつ、リーク電流を低減することが可能であることを説明する。

#### 【0051】

図2に示すメモリセル100には、P型MOSトランジスタQ P 1およびQ P 2、並びに、N型MOSトランジスタQ N 3およびQ N 4によって構成されるラッチ回路が含まれる。このラッチ回路はデータを記憶する。データが正常に保持されるためには、ラッチ回路が正常に動作していればよく、ラッチ回路が正常に動作するためには、P型MOSトランジスタQ P 1およびQ P 2の一方、および、N型MOSトランジスタQ N 3およびQ N 4の一方がオン状態であれば良い。したがって、これらMOSトランジスタに供給される電圧は、ラッチ回路が正常に動作する限界の電圧（以下、メモリセル保持電圧という）まで下げるこ20が可能である。

#### 【0052】

メモリセル100に含まれる、2つのP型MOSトランジスタQ P 1およびQ P 2が同一サイズであり、かつ、2つのN型MOSトランジスタQ N 3およびQ N 4が同一サイズである場合には、P型MOSトランジスタQ P 1およびQ P 2の閾値電圧の絶対値V T P、並びに、N型MOSトランジスタQ N 3およびQ N 4の閾値電圧（以下、V T Nという）のうち高い方の電圧が、メモリセル保持電圧になる。これらのトランジスタが構成するラッチ回路は、V T PおよびV T Nのいずれかの高い方の電圧がメモリセル電源電圧V D D Mとしてメモリセル100に供給されれば正常に動作する。本実施形態に係る半導体記憶装置では、V T Pの絶対値がV T Nよりも大きいと仮定した。したがって、本実施形態に係る半導体記憶装置は、メモリセル電源電圧V D D MがV T Pの状態で、データを30正常に保持する。

#### 【0053】

リーク電流は、メモリセルに供給されるメモリセル電源電圧に応じて増減することから、本実施形態に係る半導体記憶装置は、メモリセル電源電圧を通常の電源電圧V D DからV T Pに下げるこにより、リーク電流を低減する。

#### 【0054】

130nmプロセスの半導体記憶装置の実験では、N型MOSトランジスタの閾値電圧V T Nが0.30V、P型MOSトランジスタの閾値電圧V T Pが0.32Vの場合には、メモリセル電源電圧が少なくとも0.30V前後であれば、メモリセル内のデータが正常に保持されることが確認された。

#### 【0055】

以上のように、本実施形態に係る半導体記憶装置は、非活性なワード線に接続されたメモリセルに供給されるメモリセル電源電圧を、トランジスタの閾値電圧V T Pまで下げるこにより、メモリセルのリーク電流による消費電力を低減する。これにより、半導体記憶装置の低消費電力化が可能になる。また、本実施形態に係る半導体記憶装置は、従来の半導体記憶装置のように、基板バイアス効果によってトランジスタの閾値電圧を上げないことから、低電源電圧での動作特性が優れている。

#### 【0056】

また、リーク電流は、半導体記憶装置の動作速度にも影響を与える。特に、メモリセルから流れ出るリーク電流や、メモリセルに流れ込むリーク電流は、メモリセルの読み出し50

時や書き込み時に弊害になる。したがって、メモリセルからビット線に流れ出すリーク電流、および、ビット線からメモリセルに流れ込むリーク電流を低減することは、半導体記憶装置の高速化を可能にする。

【0057】

例えば、図2のメモリセル100からHレベルのデータ（ノードN1にHレベル、ノードN2にLレベルが記憶されている）が読み出される場合には、メモリセル100と同一ビット線上に接続された、Lレベルのデータ（ノードN1にLレベル、ノードN2にHレベルが記憶されている）が記憶されているメモリセルからのリーク電流は、メモリセル100の読み出し動作を妨害し、読み出し速度を遅くする原因になる。また、メモリセル100に対して、Hレベルのデータが書き込まれる場合も同様に、メモリセル100と同一ビット線上に接続された、Lレベルのデータが記憶されているメモリセルからのリーク電流は、メモリセル100の書き込み動作を妨害し、書き込み速度を遅くする原因になる。10

【0058】

本実施形態に係る半導体記憶装置は、非活性なワード線に接続されたメモリセルに供給されるメモリセル電源電圧を、トランジスタの閾値電圧VTPまで下げるによって、非活性なメモリセルからビット線に流れ出るリーク電流を低減する。これにより、リーク電流によるメモリセルの読み出しおよび書き込みの妨害が抑えられることから、本実施形態に係る半導体記憶装置によれば、読み出しおよび書き込み速度の高速化が可能となる。

【0059】

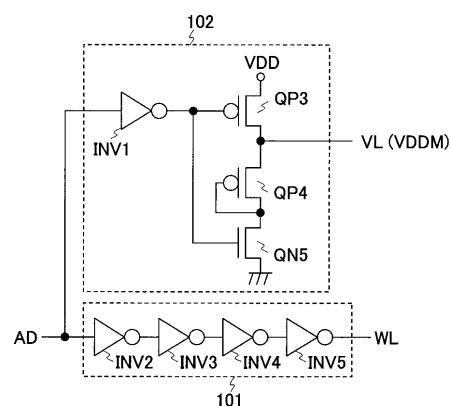

また、半導体記憶装置の読み出しおよび書き込みを高速に行うためには、メモリセル100が活性状態になる前に、メモリセル電源電圧VDDMがメモリ保持電圧VTPから電源電圧VDDに切り替わることが必要である。本実施形態に係る半導体記憶装置は、ワード線ドライバ回路101を用いて、外部からのアドレス信号ADを遅延させることにより、メモリセル100が活性状態になる前に、メモリセル電源電圧VDDMをメモリ保持電圧VTPから電源電圧VDDに切り替える。以下、図4を参照してアドレス信号ADを遅延させる方法を説明する。20

【0060】

図4は、ワード線ドライバ回路101の構成と、メモリセル電源電圧制御回路102とを示す図である。ワード線ドライバ回路101は、インバータINV2～INV5を備える。図4に示すように、メモリセル電源電圧制御回路102では、入力から出力までのゲート段数が2段であるのに対して、ワード線ドライバ回路101では、入力から出力までのゲート段数が4段になっている。したがって、アドレス信号ADが同時にワード線ドライバ回路101とメモリセル電源電圧制御回路102とに入力されると、ワード線ドライバ回路101から出力される信号は、ゲートの段数の違いから、メモリセル電源電圧制御回路102から出力される信号に対して遅延する。30

【0061】

このように、本実施形態に係る半導体記憶装置は、ワード線ドライバ回路101を用いて、アドレス信号ADを遅延させ、メモリセル電源電圧が電源電圧VDDに確実に切り替わった後、メモリセルを活性化する。これにより、メモリセルの読み出しおよび書き込み動作の高速化を可能にする。40

【0062】

近年の半導体記憶装置では、メモリセルアレイ以外の周辺回路に含まれるトランジスタの閾値電圧と比較して、メモリセルアレイに含まれるトランジスタの閾値電圧の絶対値が高く設定される場合がある。これは、プロセスの微細化に伴い増加するトランジスタのリーク電流を低減し、半導体記憶装置の消費電力を抑えるためである。特に、大容量のメモリセルアレイを搭載した半導体記憶装置では、メモリセルアレイで消費される電力が半導体記憶装置全体の消費電力の大部分を占めるため、上記のように、メモリセルアレイに含まれるトランジスタの閾値電圧の絶対値を、周辺回路に含まれるトランジスタの閾値電圧より高く設定することにより、半導体記憶装置の低消費電力化が図られる。

【0063】

10

20

30

40

50

本実施形態に係る半導体記憶装置では、メモリセル保持電圧は、メモリセル電源電圧制御回路により、メモリセルに含まれるトランジスタの閾値電圧の絶対値  $V_{TP}$  に制御される。図3に示すメモリセル電源電圧制御回路102では、ダイオード型にゲート接続されたP型MOSトランジスタQ<sub>P</sub>4によって、メモリセル保持電圧は制御される。したがって、メモリセルアレイに含まれるトランジスタの特性と、メモリセルアレイ以外の周辺回路に含まれるトランジスタの特性とが異なる場合においても、P型MOSトランジスタQ<sub>P</sub>4の特性と、メモリセルアレイに含まれるトランジスタの特性とを一致させれば、メモリセル電源電圧制御回路は、メモリセルアレイに対して、常に最適なメモリセル保持電圧を供給することが可能である。

## 【0064】

10

なお、 $V_{TN}$ が $V_{TP}$ の絶対値よりも大きい場合には、メモリセル保持電圧は $V_{TN}$ になる。この場合、メモリセル電源電圧制御回路102に含まれるP型MOSトランジスタQ<sub>P</sub>4を、閾値電圧 $V_{TN}$ を有するN型MOSトランジスタに置き換えればよい。

## 【0065】

## (第2の実施形態)

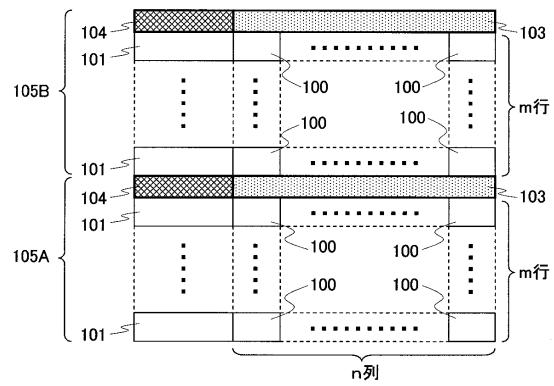

図5は、本発明の第2の実施形態に係る半導体記憶装置の構成図である。図5に示す半導体記憶装置は、メモリセルアレイ105Aとメモリセルアレイ105Bとを備える。メモリセルアレイ105Aは、メモリセル100、ワード線ドライバ回路101、メモリセル電源電圧制御回路102、OR回路OR1、ワード線WL1およびWL2、並びに、電源線VL<sub>A</sub>を備える。メモリセルアレイ105Bについては、ワード線WL3、WL4および電源線VL<sub>B</sub>以外の構成要素は、メモリセルアレイ105Aと同様であるので、図5においてはメモリセルアレイ105Bの構成の詳細は省略した。また、メモリセル100、ワード線ドライバ回路101、および、メモリセル電源電圧制御回路102は、第1の実施形態で説明したものと同じであるので、ここではこれらの構成要素の説明は省略する。

20

## 【0066】

30

図5に示す本実施形態に係る半導体記憶装置に含まれるメモリセルアレイ105Aと、図1に示す第1の実施形態に係る半導体記憶装置とは、以下の2点で相違する。すなわち、メモリセルアレイ105Aでは、アドレス信号AD1およびAD2を入力とするOR回路OR1が、メモリセル電源電圧制御回路102の前段に設けられている。また、メモリセルアレイ105Aでは、メモリセル電源電圧制御回路102から、ワード線WL1およびWL2に接続される全てのメモリセル100に対して、同じメモリセル電源電圧 $V_{DDMA}$ が供給される。図5に示す本実施形態に係る半導体記憶装置に含まれるメモリセルアレイ105Bと、図1に示す第1の実施形態に係る半導体記憶装置との相違点も、これと同じである。

## 【0067】

40

以下、以上のように構成された本実施形態に係る半導体記憶装置の動作を説明する。まず、メモリセルアレイ105Aに含まれるOR回路OR1は、アドレス信号AD1とAD2の論理和を出力する。メモリセル電源電圧 $V_{DDMA}$ は、OR回路OR1から出力された信号によって制御される。例えば、アドレス信号AD1とAD2のいずれかがHレベルであれば、OR回路OR1からは、Hレベルの信号が出力されるため、メモリセル電源電圧制御回路102から出力されるメモリセル電源電圧 $V_{DDMA}$ は、電源電圧 $V_{DD}$ になる。一方、アドレス信号AD1とAD2の両方がLレベルであれば、OR回路OR1からはLレベルの信号が出力されるため、メモリセル電源電圧制御回路102から出力されるメモリセル電源電圧 $V_{DDMA}$ は、メモリ保持電圧 $V_{TP}$ になる。

## 【0068】

50

以上のような構成を有するメモリセルアレイ105A（または105B）を、実際の半導体記憶装置に配置する例を図6に示す。一般に半導体記憶装置のメモリセルアレイでは、メモリセルに含まれるP型MOSトランジスタおよびN型MOSトランジスタに基板電位を供給するために、基板電位を供給するための領域（以下、基板電位供給領域という）

が一定の間隔ごとに設けられる。図6では、m行のメモリセル100ごとに基板電位供給領域103が設けられる。また、通常、基板電位供給領域103に隣接し、ワード線ドライバ回路101の占める領域であるワード線ドライバ回路領域に挟まれた部分には、回路の存在しない空白領域104が存在する。

【0069】

この空白領域104に、図5に示されるOR回路OR1とメモリセル電源電圧制御回路102とを配置し、さらに、基板電位供給領域103に、図5に示す電源線VLA(またはVLB)を配置することにより、半導体記憶装置の面積を増大することなく、OR回路OR1およびメモリセル電源電圧制御回路102を配置することができる。

【0070】

以上のように、本実施形態に係る半導体記憶装置は、複数のワード線から供給されるアドレス信号の論理和を求めるOR回路を備え、1つのメモリセル電源電圧制御回路によって異なるワード線に接続されたメモリセルを制御する。これにより、半導体記憶装置の面積の増大を抑えつつ、第1の実施形態に係る半導体記憶装置と同様の効果を得ることができる。

【0071】

(第3の実施形態)

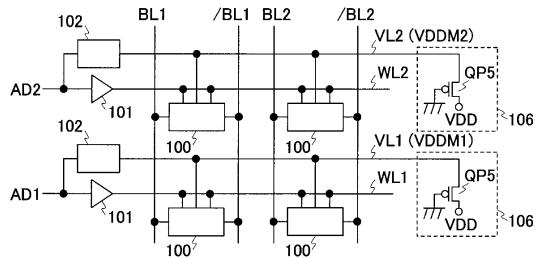

本発明の第3の実施形態に係る半導体記憶装置は、図7に示すように、第1の実施形態に係る半導体記憶装置にメモリセル電源電圧補償回路106を加えたものである。したがって、ここではメモリセル電源電圧補償回路106の構成、および、その動作について説明する。

【0072】

メモリセル電源電圧補償回路106は、P型MOSトランジスタQ P 5を含んでいる。P型MOSトランジスタQ P 5のソース電極は、電源端子V DDに接続され、ドレイン電極は、メモリセル電源電圧V DDM 1(またはV DDM 2)を供給する電源線V L 1(またはV L 2)に接続され、ゲート電極は、接地される。メモリセル電源電圧補償回路106は、ワード線W L 1(またはW L 2)の状態にかかわらず、P型MOSトランジスタQ P 5から電源線V L 1(またはV L 2)に電荷を供給する。以下、図7を参照しながら、電源線V L 1に接続されたメモリセル電源電圧補償回路106の動作を説明する。

【0073】

まず、Hレベルのアドレス信号A D 1が入力され、ワード線W L 1が活性状態になった場合を考える。この場合、メモリセル電源電圧V DDM 1は電源電圧V DDと一致し、ワード線W L 1に接続されるメモリセル100には電源電圧V DDが供給される。また、P型MOSトランジスタQ P 5のドレイン電極にも電源電圧V DDが供給される。したがって、P型MOSトランジスタQ P 5のソース-ドレイン間には電位差はなく、P型MOSトランジスタQ P 5には電流は流れない。したがって、この場合においては、メモリセル電源電圧補償回路106から電源線V L 1に対して、電荷は供給されない。

【0074】

次に、アドレス信号A D 1がLレベルとなり、ワード線W L 1が非活性状態になった場合を考える。この場合、メモリセル電源電圧V DDM 1はメモリセル保持電圧V TPに一致し、ワード線W L 1に接続されるメモリセル100には、メモリセル保持電圧V TPが供給される。また、P型MOSトランジスタQ P 5のドレイン電極にも、メモリセル保持電圧V TPが供給される。メモリセル保持電圧V TPは、電源電圧V DDよりも低いため、P型MOSトランジスタQ P 5のソース-ドレイン間に電位差が発生し、P型MOSトランジスタQ P 5に電流が流れる。すなわち、メモリセル電源電圧補償回路106は、電源線V L 1に電荷を供給する。

【0075】

第1の実施形態で述べたように、メモリセル100にはリーク電流が流れる。このために、メモリセル100に供給されるメモリセル電源電圧V DDM 1には電圧降下が起こる。そこで、メモリセル電源電圧補償回路106を設け、メモリセル電源電圧補償回路10

10

20

30

40

50

6 から電源線 V L 1 に供給される電荷量が、電源線 V L 1 に接続された全てのメモリセル 100 におけるリーク電流による電荷の損失量と一致するようにする。これにより、非活性なワード線 W L 1 に接続されるメモリセル 100 に供給されるメモリセル電源電圧 V D D M 1 は、メモリセル保持電圧 V T P に保たれる。

【 0076 】

以上のように、本実施形態に係る半導体記憶装置は、メモリセル 100 におけるリーク電流による電荷の損失を、メモリセル電源電圧補償回路 106 によって補償する。これにより、非活性なワード線に接続されるメモリセル 100 に対して、安定したメモリセル保持電圧を供給することができる。

【 0077 】

なお、本実施形態ではメモリセル電源電圧補償回路 106 を構成する要素として、P 型 MOS トランジスタを用いたが、リーク電流による電荷量の損失を補うことが可能な素子であれば、P 型 MOS トランジスタの代わりに、N 型 MOS トランジスタや抵抗素子などを用いてもよい。

【 0078 】

また、本実施形態では、リーク電流によって損失した電荷量を、メモリセル電源電圧補償回路 106 によって補償する例を示したが、メモリセル電源電圧制御回路 102 に含まれる P 型 MOS トランジスタ Q P 3 も同様に、メモリセル 100 に対して、電荷を供給する構成を有する。したがって、メモリセル電源電圧補償回路 106 を設計する場合には、P 型 MOS トランジスタ Q P 3 の電荷供給能力を考慮して設計してもよい。これにより、メモリセル電源電圧補償回路 106 によって補償する電荷量を低減することも可能である。特に、メモリセルにおけるリーク電流による電荷の損失量を補償できるだけの十分な電荷供給能力が P 型 MOS トランジスタ Q P 3 にある場合には、メモリセル電源電圧補償回路 106 を設けなくとも良い。これにより、メモリセル電源電圧補償回路 106 を除去することができ、回路の面積を小さくできる。

【 0079 】

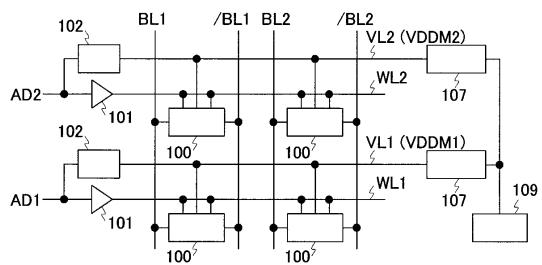

( 第 4 の実施形態 )

本発明の第 4 の実施形態に係る半導体記憶装置は、図 8 に示すように、第 1 の実施形態に係る半導体記憶装置にメモリセル電源電圧補償回路 107、および、メモリセル保持参照電圧発生回路 109 を加えたものである。したがって、ここでは、メモリセル電源電圧補償回路 107 およびメモリセル保持参照電圧発生回路 109 について、回路の構成およびその動作を説明する。

【 0080 】

図 8 に示すように、メモリセル電源電圧補償回路 107 の一端は、電源線 V L 1 ( または V L 2 ) に接続され、他端はメモリセル保持参照電圧発生回路 109 の出力に接続される。

【 0081 】

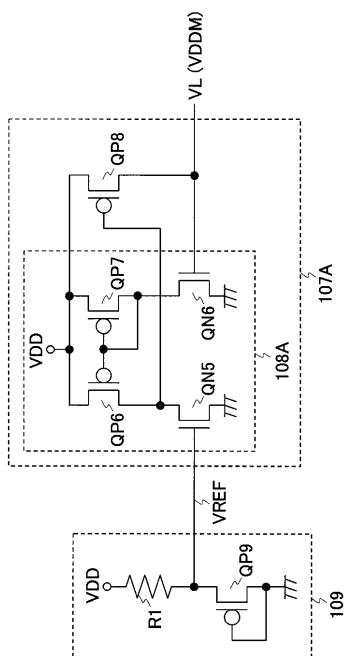

図 9 に、メモリセル電源電圧補償回路 107 の構成の一例 ( 以下、メモリセル電源電圧補償回路 107 A という ) と、メモリセル保持参照電圧発生回路 109 の構成とを示す。図 9 に示すメモリセル電源電圧補償回路 107 A は、P 型 MOS トランジスタ Q P 6 ~ Q P 8、並びに、N 型 MOS トランジスタ Q N 5 および Q N 6 を備える。

【 0082 】

P 型 MOS トランジスタ Q P 6 および Q P 7 のソース電極は、共に電源端子 V D D に接続され、ドレイン電極は、それぞれ N 型 MOS トランジスタ Q N 5 および Q N 6 のドレイン電極に接続される。また、P 型 MOS トランジスタ Q P 6 および Q P 7 のゲート電極は、共に P 型 MOS トランジスタ Q P 7 のドレイン電極に接続される。一方、N 型 MOS トランジスタ Q N 5 および Q N 6 のソース電極は共に接地され、ゲート電極は、それぞれ、メモリセル保持参照電圧発生回路 109 の出力および電源線 V L に接続される。

【 0083 】

P 型 MOS トランジスタ Q P 6 および Q P 7、並びに、N 型 MOS トランジスタ Q N 5

10

20

30

40

50

およびQ N 6は、差動増幅回路108Aを構成する。差動増幅回路108Aの出力は、P型MOSトランジスタQ P 8のゲート電極に接続される。また、P型MOSトランジスタQ P 8のソース電極は、電源端子V D Dに接続され、ドレイン電極は、電源線V Lに接続される。

【0084】

メモリセル電源電圧補償回路107Aには、メモリセル保持参照電圧発生回路109が接続される。メモリセル保持参照電圧発生回路109は、ダイオード型にゲート接続されたP型MOSトランジスタQ P 9と、抵抗素子R 1とを備える。メモリセル保持参照電圧発生回路109の出力( P型MOSトランジスタQ P 9と抵抗R 1の接合部)からは、メモリ保持参照電圧V R E Fが出力される。このP型MOSトランジスタQ P 9は、メモリセルに含まれるP型MOSトランジスタと同じ特性を有することから、メモリセル保持参照電圧発生回路109から出力されるメモリ保持参照電圧V R E Fは、メモリ保持電圧V T Pと一致する。

【0085】

以下、図9を参照しながらメモリセル電源電圧補償回路107Aの動作を説明する。メモリセル電源電圧補償回路107Aにメモリセル電源電圧V D D Mが供給されると、差動増幅回路108Aは、メモリセル電源電圧V D D Mとメモリセル保持参照電圧V R E Fとを比較し、その結果を増幅してP型MOSトランジスタQ P 8のゲート電極に出力する。メモリセル電源電圧V D D Mがメモリセル保持参照電圧V R E Fよりも低い場合には、差動増幅回路108Aは、Lレベルの信号をP型MOSトランジスタQ P 8のゲート電極に出力する。また、メモリセル電源電圧V D D Mが、メモリセル保持参照電圧V R E Fよりも高い場合には、差動増幅回路108Aは、Hレベルの信号をP型MOSトランジスタQ P 8のゲート電極に出力する。

【0086】

P型MOSトランジスタQ P 8のゲート電極に差動増幅回路108AからLレベルの信号が入力されると、P型MOSトランジスタQ P 8はオンになり、電源端子V D Dから電源線V Lに対して電荷が供給される。したがって、メモリセル電源電圧V D D Mは上昇する。一方、P型MOSトランジスタQ P 8のゲート電極に差動増幅回路108AからHレベルの信号が入力されると、P型MOSトランジスタQ P 8はオフになり、メモリセル電源電圧V D D Mには影響はない。

【0087】

メモリセル電源電圧V D D Mがメモリセル保持参照電圧V R E Fよりも低い場合には、メモリセル電源電圧V D D Mは、差動増幅回路108Aにより、メモリセル保持参照電圧V R E Fに一致するまで上昇する。メモリセル電源電圧V D D Mがメモリセル保持参照電圧V R E Fに一致するまで上昇すると、P型MOSトランジスタQ P 8はオフになり、メモリセル電源電圧V D D Mの上昇が止まる。このようにして、メモリセル電源電圧補償回路107Aは、メモリセル電源電圧V D D Mの電圧が降下した場合において、差動増幅回路108AとP型MOSトランジスタQ P 8との作用により、メモリセル電源電圧V D D Mの電圧を上げる。特に、メモリセル電源電圧V D D Mがメモリセル保持電圧V T Pである場合には、メモリセル電源電圧補償回路107Aは、メモリセル電源電圧をメモリセル保持参照電圧V R E F付近に保持する。

【0088】

第3の実施形態ですでに述べたように、非活性なワード線に接続されるメモリセルに供給されるメモリセル電源電圧V D D Mは、リーク電流の影響により、メモリセル保持電圧V T Pから降下する場合がある。しかし、本実施形態に係る半導体記憶装置は、メモリセル電源電圧補償回路107Aを備えることにより、非活性なメモリセルからのリーク電流によるメモリセル電源電圧V D D Mの電圧降下を補償する。これにより、メモリセルに安定したメモリセル電源電圧V D D Mを供給することができる。

【0089】

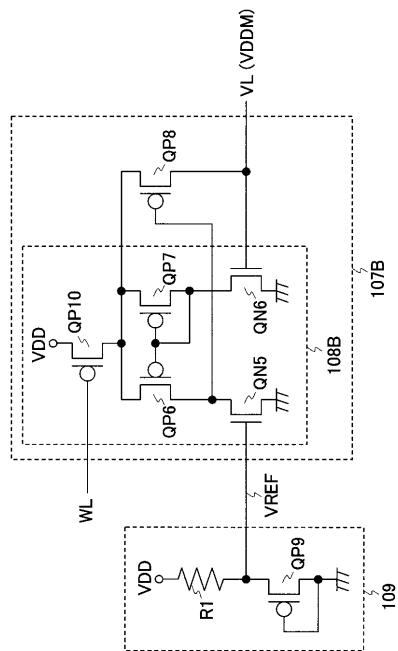

次に、図10にメモリセル電源電圧補償回路107の他の構成例(以下、メモリセル電

10

20

30

40

50

源電圧補償回路 107B という)を示す。図 10 に示すメモリセル電源電圧補償回路 107B は、ワード線 WL で制御される P 型 MOS トランジスタ QP10 を、メモリセル電源電圧補償回路 107A に追加したものである。P 型 MOS トランジスタ QP10 のソース電極は、電源端子 VDD に接続され、ドレイン電極は、P 型 MOS トランジスタ QP6 ~ QP8 に接続され、ゲート電極は、ワード線 WL に接続される。その他の構成要素については、メモリセル電源電圧補償回路 107A と同じである。

#### 【0090】

以上のように構成されたメモリセル電源電圧補償回路 107B の動作を説明する。まず、ワード線 WL から P 型 MOS トランジスタ QP10 に L レベルの信号が入力された場合には、P 型 MOS トランジスタ QP10 はオンになり、メモリセル電源電圧補償回路 107B は、メモリセル電源電圧補償回路 107A と同様の動作を行う。10

#### 【0091】

次に、ワード線 WL から P 型 MOS トランジスタ QP10 に H レベルの信号が入力された場合には、P 型 MOS トランジスタ QP10 はオフになり、差動増幅回路 108B および P 型 MOS トランジスタ QP8 は動作しない。したがって、メモリセル電源電圧補償回路 107B は、メモリセルが非活性な場合にのみ動作を行う。

#### 【0092】

以上のように、図 10 に示すメモリセル電源電圧補償回路 107B を備えた半導体記憶装置は、P 型 MOS トランジスタ QP10 によって差動増幅回路 108B の動作を制御することにより、メモリセル電源電圧補償回路 107B が必要なメモリセルが非活性な場合においてのみ、差動増幅回路 108B を動作させる。これにより、メモリセル電源電圧補償回路 107B において消費される電力を最小限に抑えることができる。20

#### 【0093】

##### (第 5 の実施形態)

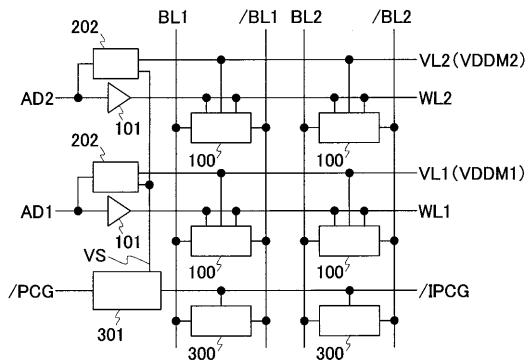

図 11 は、本発明の第 5 の実施形態に係る半導体記憶装置の構成図である。図 11 に示す半導体記憶装置は、メモリセル 100、ワード線ドライバ回路 101、メモリセル電源電圧制御回路 202、ピット線プリチャージ回路 300、ピット線プリチャージ制御回路 301、ワード線 WL1 および WL2、ピット線 BL1、BL2、/BL1 および /BL2、電源線 VL1 および VL2、ピット線プリチャージ制御信号線 /IPC G、並びに、メモリセル電荷供給線 VS を備える。メモリセル 100 およびワード線ドライバ回路 101 は、第 1 の実施形態で説明したものと同じであるので、ここではこれらの構成要素の説明は省略する。30

#### 【0094】

ピット線プリチャージ回路 300 は、ピット線 BL1 および /BL1 ( または BL2 および /BL2 )、並びに、ピット線プリチャージ制御信号線 /IPC G に接続される。また、ピット線プリチャージ制御回路 301 は、ピット線プリチャージ制御信号線 /IPC G、および、メモリセル電荷供給線 VS に接続される。ピット線プリチャージ制御回路 301 には、外部からピット線プリチャージ信号 /PC G が入力される。本実施形態に係る半導体記憶装置は、ピット線プリチャージ回路 300、および、ピット線プリチャージ制御回路 301 を備えることにより、ピット線 BL1、BL2、/BL1 および /BL2 を、H レベルまたはハイインピーダンス状態に制御する。40

#### 【0095】

次に、図 12 を参照しながらメモリセル電源電圧制御回路 202 の構成を説明する。メモリセル電源電圧制御回路 202 と、図 3 に示すメモリセル電源電圧制御回路 102 とは以下の点で相違する。すなわち、メモリセル電源電圧制御回路 202 に含まれる N 型 MOS トランジスタ QN5 のソース電極は、メモリセル電荷供給線 VS を介して、ピット線プリチャージ制御回路 301 に接続される。その他の構成要素については、メモリセル電源電圧制御回路 102 と同じであるので、ここでは説明を省略する。また、メモリセル電源電圧制御回路 202 は、メモリセル電源電圧制御回路 102 と同様に、メモリセルが接続されるワード線の状態 ( 活性あるいは非活性 ) に応じて、メモリセルに供給する電源電圧50

を制御する。

【0096】

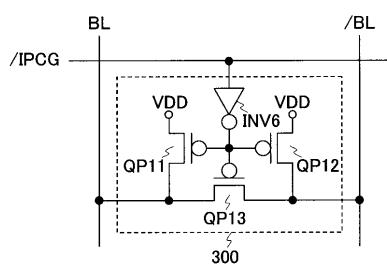

次に、図13を参照しながらビット線プリチャージ回路300の構成を説明する。ビット線プリチャージ回路300は、P型MOSトランジスタQ P 1 1 ~ Q P 1 3、および、インバータINV6を備える。インバータINV6の入力は、ビット線プリチャージ制御信号線 / IPCGに接続される。また、インバータINV6の出力は、P型MOSトランジスタQ P 1 1 ~ Q P 1 3のゲート電極に接続される。

【0097】

P型MOSトランジスタQ P 1 1 およびQ P 1 2のソース電極は、いずれも電源端子V DDに接続される。また、P型MOSトランジスタQ P 1 1 およびQ P 1 2のドレイン電極は、それぞれ、ビット線BLおよび/BLに接続される。P型MOSトランジスタQ P 1 3のソース電極およびドレイン電極は、それぞれ、ビット線BLおよび/BLに接続される。

【0098】

以上のように構成されたビット線プリチャージ回路300の動作を説明する。ビット線プリチャージ制御信号線 / IPCGからHレベルの信号がインバータINV6に入力されると、P型MOSトランジスタQ P 1 1 ~ Q P 1 3のゲート電極は、Lレベルとなる。この結果、P型MOSトランジスタQ P 1 1 ~ Q P 1 3がオンになるため、ビット線BLおよび/BLは、Hレベルにプリチャージされる。

【0099】

一方、ビット線プリチャージ制御信号線 / IPCGからLレベルの信号がインバータINV6に入力されると、P型MOSトランジスタQ P 1 1 ~ Q P 1 3のゲート電極は、Hレベルとなる。この結果、P型MOSトランジスタQ P 1 1 ~ Q P 1 3がオフになるため、ビット線BLおよび/BLは、ハイインピーダンス状態になる。

【0100】

一般に半導体記憶装置に設けられる各ビット線プリチャージ回路は、全てのワード線が非活性状態である場合には活性状態に制御され、各ビット線をHレベルにプリチャージする。一方、いずれかのワード線が活性状態である場合には、各ビット線プリチャージ回路は非活性状態に制御され、各ビット線に影響を与えない。したがって、この場合、各ビット線はハイインピーダンス状態になる。以下、ビット線プリチャージ回路300が、ビット線プリチャージ制御回路301によって制御されることにより、同様の動作をすることを説明する。

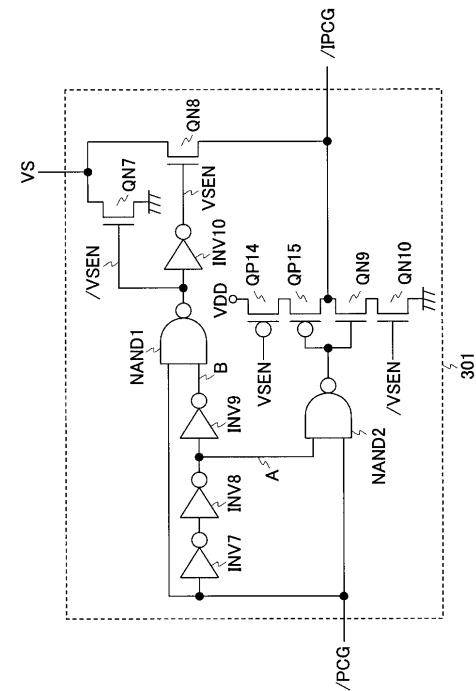

【0101】

まず、図14を参照しながらビット線プリチャージ制御回路301の構成を説明する。ビット線プリチャージ制御回路301は、N型MOSトランジスタQ N 7 ~ Q N 1 0、P型MOSトランジスタQ P 1 4 およびQ P 1 5、インバータINV7 ~ INV10、並びに、NAND回路NAND1およびNAND2を備える。

【0102】

N型MOSトランジスタQ N 7のドレイン電極は、メモリセル電荷供給線VSに接続され、ソース電極は接地される。また、N型MOSトランジスタQ N 7のゲート電極は、NAND回路NAND1の出力に接続される。以下、N型MOSトランジスタQ N 7のゲート電極とNAND回路NAND1の出力とを接続するノードをノード/VSENと呼ぶ。N型MOSトランジスタQ N 7は、NAND回路NAND1から出力される信号に応じて、メモリセル電荷供給線VSと接地とを導通または開放する。

【0103】

N型MOSトランジスタQ N 8のドレイン電極は、メモリセル電荷供給線VSに接続され、ソース電極は、ビット線プリチャージ制御信号線 / IPCGに接続される。また、N型MOSトランジスタQ N 8のゲート電極は、インバータINV10の出力に接続される。以下、N型トランジスタQ N 8のゲート電極とインバータINV10の出力とを接続するノードをノードVSENと呼ぶ。N型MOSトランジスタQ N 8は、インバータINV

10

20

30

40

50

10から出力される信号に応じて、メモリセル電荷供給線V<sub>S</sub>とピット線プリチャージ制御信号線/I<sub>P</sub>C<sub>G</sub>とを導通または開放する。

【0104】

N型MOSトランジスタQN9およびQN10、並びに、P型MOSトランジスタQP14およびQP15は、クロックインバータを構成する。以下に、その構成を説明する。

【0105】

N型MOSトランジスタQN9のソース電極は、N型MOSトランジスタQN10のドレイン電極に接続され、ドレイン電極は、ピット線プリチャージ制御信号線/I<sub>P</sub>C<sub>G</sub>に接続される。また、N型MOSトランジスタQN9のゲート電極は、NAND回路NAND2の出力に接続される。N型MOSトランジスタQN10のソース電極は接地され、ゲート電極は、ノード/V<sub>SEN</sub>を介して、NAND回路NAND1の出力に接続される。

10

【0106】

P型MOSトランジスタQP14のソース電極は、電源端子V<sub>DD</sub>に接続され、ドレイン電極は、P型MOSトランジスタQP15のソース電極に接続される。また、P型MOSトランジスタQP14のゲート電極は、ノードV<sub>SEN</sub>を介して、インバータINV10の出力に接続される。P型MOSトランジスタQP15のドレイン電極は、ピット線プリチャージ制御信号線/I<sub>P</sub>C<sub>G</sub>に接続され、ゲート電極は、NAND回路NAND2の出力に接続される。

【0107】

以上のように構成されるクロックインバータは、NAND回路NAND2から出力される信号、NAND回路NAND1から出力される信号、および、インバータINV10から出力される信号に応じて、ピット線プリチャージ制御信号線/I<sub>P</sub>C<sub>G</sub>をHレベル、Lレベルあるいはハイインピーダンス状態に制御する。

20

【0108】

次に、インバータINV7～INV9、並びに、NAND回路NAND1およびNAND2について説明する。インバータINV7～INV9は、直列に接続される。インバータINV7には、ピット線プリチャージ信号/P<sub>C</sub>Gが入力される。インバータINV9の出力には、NAND回路NAND1の一方の入力が接続される。以下、インバータINV9とNAND回路NAND1とを接続するノードをノードBと呼ぶ。インバータINV7～INV9は、このノードBを介してNAND回路NAND1に入力される信号を遅延する。また、NAND回路NAND1の他方の入力には、ピット線プリチャージ信号/P<sub>C</sub>Gが入力される。

30

【0109】

また、NAND回路NAND2の一方の入力には、ピット線プリチャージ信号/P<sub>C</sub>Gが入力される。NAND回路NAND2の他方の入力は、インバータINV8の出力に接続される。以下、NAND回路NAND2とインバータINV8とを接続するノードをノードAと呼ぶ。

【0110】

次に、以上のように構成されたピット線プリチャージ制御回路301の動作を説明する。Hレベルのピット線プリチャージ信号/P<sub>C</sub>Gがピット線プリチャージ制御回路301に入力された場合、NAND回路NAND1には、Hレベルのピット線プリチャージ信号/P<sub>C</sub>G、および、ノードBを介してLレベルの信号が入力される。したがって、NAND回路NAND1は、Hレベルの信号をN型MOSトランジスタQN7のゲート電極、および、インバータINV10に出力する。この結果、N型MOSトランジスタQN7がオンになることから、図12に示すN型MOSトランジスタQN5のソース電極は、メモリセル電荷供給線V<sub>S</sub>を介して接地される。また、インバータINV10は、N型MOSトランジスタQN8のゲート電極に、Lレベルの信号を出力することから、N型MOSトランジスタQN8はオフになる。

40

【0111】

また、NAND回路NAND2には、Hレベルのピット線プリチャージ信号/P<sub>C</sub>G、

50

20

30

40

50

および、ノードAを介してHレベルの信号が入力される。したがって、NAND回路NAND2は、Lレベルの信号をクロックインバータに出力する。ノードVSENにはインバータINV10からLレベルの信号が出力されるため、P型MOSトランジスタQ14はオンになる。また、P型MOSトランジスタQ15には、NAND回路NAND2からLレベルの信号が出力されるため、P型MOSトランジスタQ15はオンになる。したがって、ビット線プリチャージ制御信号線/IPCGには、クロックインバータからHレベルの信号が供給される。

#### 【0112】

一方、Lレベルのビット線プリチャージ信号/IPCGが、ビット線プリチャージ制御回路301に入力された場合には、NAND回路NAND1およびNAND2から、共にHレベルの信号が出力される。この結果、N型MOSトランジスタQN9およびQN10は共にオンになり、ビット線プリチャージ制御信号線/IPCGは接地される。また、この場合も、N型MOSトランジスタQN7がオンになることから、N型MOSトランジスタQN5のソース電極は、メモリセル電荷供給線VSを介して接地される。

#### 【0113】

以上のように、ビット線プリチャージ制御回路301は、ビット線プリチャージ信号/IPCGがHレベルの場合には、ビット線プリチャージ制御信号線/IPCGに供給する信号をHレベルに制御し、また、ビット線プリチャージ信号/IPCGがLレベルの場合には、ビット線プリチャージ制御信号線/IPCGに供給する信号をLレベルに制御する。

#### 【0114】

また、上述したように、ビット線プリチャージ制御信号線/IPCGにHレベルの信号が供給されると、ビット線プリチャージ回路300は、ビット線BLおよび/BLをプリチャージする。また、ビット線プリチャージ制御信号線/IPCGにLレベルの信号が供給されると、ビット線プリチャージ回路300は、ビット線BLおよび/BLに影響を与えない。したがって、ビット線BLおよび/BLは、ハイインピーダンス状態になる。

#### 【0115】

さらに、本実施形態に係る半導体記憶装置は、全てのワード線が非活性状態である場合には、Hレベルのビット線プリチャージ信号/IPCGがビット線プリチャージ制御回路301に入力されることにより、ビット線プリチャージ制御信号線/IPCGに接続された全てのビット線プリチャージ回路300を活性状態に制御し、全てのビット線BL1、BL2、/BL1および/BL2をプリチャージする。

#### 【0116】

また、いずれかのワード線が活性状態である場合には、Lレベルのビット線プリチャージ信号/IPCGが、ビット線プリチャージ制御回路301に入力されることにより、本実施形態に係る半導体記憶装置は、ビット線プリチャージ制御信号線/IPCGに接続された全てのビット線プリチャージ回路300を非活性状態に制御し、全てのビット線BL1、BL2、/BL1および/BL2をハイインピーダンス状態にする。

#### 【0117】

以上のように、本実施形態に係る半導体記憶装置は、ビット線プリチャージ制御回路301を備えることにより、ビット線プリチャージ回路300を一般的のビット線プリチャージ回路と同様に動作させる。

#### 【0118】

また、ビット線プリチャージ制御回路301に入力されるビット線プリチャージ信号/IPCGが、HレベルまたはLレベルいずれの場合にも、図12に示すN型MOSトランジスタQN5のソース電極は、メモリセル電荷供給線VSを介して接地されることから、メモリセル電源電圧制御回路202は、第1の実施形態におけるメモリセル電源電圧制御回路102と同様に動作する。したがって、本実施形態に係る半導体記憶装置は、第1の実施形態に係る半導体記憶装置と同様に、半導体記憶装置の低消費電力化や高速化といった効果を有する。

#### 【0119】

10

20

30

40

50

さらに、本実施形態に係る半導体記憶装置は、上記の効果に加えて、電源線 V L 1 ( または V L 2 ) に蓄積された電荷を、ビット線プリチャージ制御信号線 / I P C G に供給することによって電荷を再利用することにより、半導体記憶装置のさらなる低消費電力化を実現する。以下、この効果を図 1 4 を参照しながら詳しく説明する。

【 0 1 2 0 】

例えば、図 1 1 において、アドレス信号 A D 1 が H レベルから L レベルへと変わり、ワード線 W L 1 が活性状態から非活性状態に変わる場合を考える。ワード線 W L 1 が非活性状態になると、ワード線 W L 1 に接続された全てのメモリセル 1 0 0 が非活性状態になる。この場合、第 1 の実施形態に係る半導体記憶装置においては、図 1 に示すメモリセル電源電圧制御回路 1 0 2 によって、メモリセル電源電圧 V D D M 1 が電源電圧 V D D から V T P に変わる際、電源線 V L 1 に蓄えられていた電荷は、N 型 M O S トランジスタ Q N 5 のソース電極から接地端子に排出される。

【 0 1 2 1 】

これに対して、本実施形態に係る半導体記憶装置では、ワード線 W L 1 が非活性状態になり、さらに、ビット線プリチャージ信号 / P C G が L レベルから H レベルに変わると、ビット線プリチャージ制御回路 3 0 1 に設けられたインバータ I N V 7 ~ I N V 9 による遅延時間の間、N A N D 回路 N A N D 1 の 2 つの入力が共に H レベルとなる。したがって、この時間の間では N A N D 回路 N A N D 1 から L レベルの信号が出力され、この結果、N 型 M O S トランジスタ Q N 7 がオフになり、N 型 M O S トランジスタ Q N 8 がオンになる。

【 0 1 2 2 】

N 型 M O S トランジスタ Q N 7 がオフ状態であり、N 型 M O S トランジスタ Q N 8 がオン状態であると、メモリセル電源電圧制御回路 2 0 2 に含まれる N 型 M O S トランジスタ Q N 5 と、ビット線プリチャージ制御信号線 / I P C G とが導通する。この結果、メモリセル電源電圧 V D D M 1 が電源電圧 V D D から V T P に変わる際、電源 V L 1 に蓄えられていた電荷は、メモリセル電荷供給線 V S を介して、ビット線プリチャージ制御信号線 / I P C G に供給される。

【 0 1 2 3 】

また、このときノード V S E N は H レベルであり、ノード / V S E N は L レベルであるため、クロックインバータの出力はハイインピーダンス状態であり、クロックインバータは、ビット線プリチャージ制御信号線 / I P C G に影響を与えない。

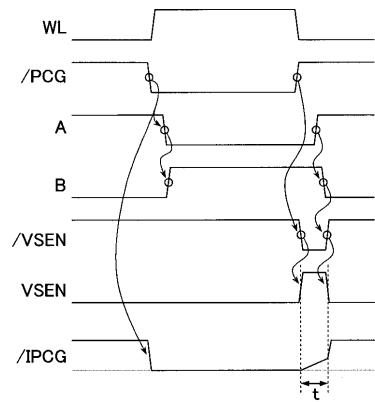

【 0 1 2 4 】

以上の動作をタイミングチャートに示したものが図 1 5 である。図 1 5 は、ワード線 W L が H レベルから L レベルに変わり、ビット線プリチャージ信号 / P C G が L レベルから H レベルに変わる場合に、ビット線プリチャージ信号 / P C G が入力されてから、ノード B に供給される信号が L レベルに変わるまでの時間 t の間 ( すなわち、インバータ I N V 7 ~ I N V 9 による遅延時間の間 ) 、ビット線プリチャージ制御信号線 / I P C G に電源線 V L 1 から電荷が供給され、供給された電荷によってビット線プリチャージ制御信号線 / I P C G の電位が徐々に上昇することを示す。

【 0 1 2 5 】

以上のように、本実施形態に係る半導体記憶装置は、ワード線が活性状態から非活性状態に変わる場合において、電源線 V L 1 に蓄えられた電荷をビット線プリチャージ制御信号線 / I P C G に供給し電荷を再利用する。これにより、半導体記憶装置のさらなる低消費電力化が実現される。

【 0 1 2 6 】

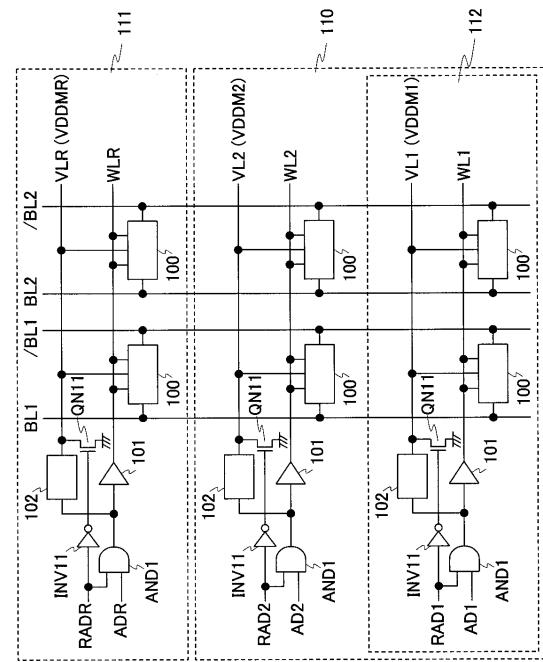

( 第 6 の実施形態 )

図 1 6 は、本発明の第 6 の実施形態に係る半導体記憶装置の構成図である。図 1 6 に示す半導体記憶装置は、メモリセルアレイ 1 1 0 およびメモリセルアレイ 1 1 1 を含む。メモリセルアレイ 1 1 0 は、メモリセル 1 0 0 、ワード線ドライバ回路 1 0 1 、メモリセル電源電圧制御回路 1 0 2 、ワード線 W L 1 および W L 2 、電源線 V L 1 および V L 2 、N

10

20

30

40

50

型MOSトランジスタQN11、AND回路AND1、並びに、インバータINV11を備える。メモリセルアレイ111に含まれるワード線WLRおよび電源線VLR以外の構成要素は、メモリセルアレイ110と同様である。また、メモリセル100、ワード線ドライバ回路101、および、メモリセル電源電圧制御回路102は、第1の実施形態で説明したものと同じであるので、ここではこれらの構成要素の説明は省略する。

#### 【0127】

一般に半導体記憶装置は、製品の歩留まりの向上のために、正規のメモリセルアレイ以外に、予め予備のメモリセルアレイを搭載している。半導体記憶装置の検査工程において、正規のメモリセルアレイ内に欠陥のあるメモリセルが存在すると判定された場合には、その欠陥箇所を予備のメモリセルによって置換し、その半導体記憶装置を良品として完成させる、いわゆる冗長救済が行われる。本実施形態に係る半導体記憶装置は、メモリセルアレイ111を、正規のメモリセルアレイ110のための冗長救済用のメモリセルアレイ(以下、冗長救済ブロックという)として備える。

#### 【0128】

以下、上記の冗長救済ブロックの構成について説明する。冗長救済ブロックには、外部からアドレス信号ADRと冗長救済アドレス信号RADRとが入力される。冗長救済アドレス信号RADRは分岐され、一方はAND回路AND1に、他方はインバータINV11に入力される。冗長救済ブロックは、これらアドレス信号ADRおよび冗長救済アドレス信号RADRによって制御される。以下、図16を参照しながら冗長救済ブロックの動作を説明する。

#### 【0129】

まず、冗長救済が行われない場合について説明する。冗長救済が行われない場合には、冗長救済ブロックに入力されるアドレス信号ADR、および、冗長救済アドレス信号RADRは、共にLレベルに設定される。したがって、AND回路AND1の各入力信号はLレベルであるため、AND回路AND1からは、Lレベルの信号が出力される。出力されたLレベルの信号はワード線WLRに入力されるため、冗長救済ブロックに含まれるメモリセル100は非活性状態になる。したがって、ワード線WLRに接続されるメモリセル100は、ビット線BL1、BL2、/BL1および/BL2には影響を与えない。

#### 【0130】

また、分岐された冗長救済アドレス信号RADRの他方は、インバータINV11によってHレベルに変換され、変換された信号は、N型MOSトランジスタQN11のゲート電極に入力される。N型MOSトランジスタQN11は、ゲート電極にHレベルの信号が入力されたためにオンになる。これにより、電源線VLRは接地され、メモリセル電源電圧VDDMRは接地レベルになる。

#### 【0131】

冗長救済が行われない場合には、正規のメモリセルアレイに入力される冗長救済アドレス信号RAD1は、Hレベルに設定される。したがって、正規のメモリセルアレイに含まれるAND回路AND1からは、アドレス信号AD1と同じ信号が出力される。AND回路AND1から出力された信号は、ワード線ドライバ回路101およびメモリセル電源電圧制御回路102に入力される。

#### 【0132】

また、正規メモリセルに含まれるN型MOSトランジスタQN11のゲート電極には、インバータINV11によってLレベルに変換された冗長救済アドレス信号RAD1が入力される。このため、N型MOSトランジスタはオフになり、電源線VL1には、メモリセル電源電圧制御回路102から出力されるメモリセル電源電圧VDDM1が供給される。

#### 【0133】

以上のように、冗長救済が行われない場合には、冗長救済ブロックは、正規のメモリセルアレイ110に影響を与えず、正規のメモリセルアレイは、通常の動作を行う。また、本実施形態の半導体記憶装置は、冗長救済ブロックに含まれる非活性なメモリセル100

10

20

30

40

50

のメモリセル電源電圧V D D M Rを、N型MOSトランジスタQ N 1 1によって接地レベルにすることにより、これらメモリセル1 0 0からのリーク電流を削減し、半導体記憶装置の消費電力を抑える。

【0134】

次に、冗長救済が行われる場合について説明する。ここでは、例えば、ワード線W L 1に接続されるメモリセル1 0 0のいずれかに欠陥があるとし、ワード線W L 1に接続されるメモリセル1 0 0が冗長救済により、冗長救済ブロック内のワード線W L Rに接続されるメモリセル1 0 0に置換されるとする。すなわち、メモリセルアレイ1 1 1によってメモリセルアレイ1 1 2が置換される場合を考える。

【0135】

この場合、冗長救済信号R A D 1はLレベルに、冗長救済信号R A D 2およびR A D RはHレベルに設定される。また、アドレス信号A D 1が選択される代わりに、冗長救済用のアドレス信号A D Rが選択されるように設定される。アドレス信号A D 1はLレベルに設定される。

【0136】

メモリセルアレイ1 1 2に入力される冗長救済アドレス信号R A D 1とアドレス信号A D 1は共にLレベルであるため、ワード線W L 1に接続されるメモリセル1 0 0は、非活性状態になる。したがって、ワード線W L 1に接続されるメモリセル1 0 0は、ビット線B L 1、B L 2、/B L 1および/B L 2に影響を与えない。また、N型MOSトランジスタQ N 1 1のゲートにインバータI N V 1 1からHレベルの信号が入力されるため、電源線V L 1は接地され、メモリセル電源電圧V D D M 1は接地レベルになる。

【0137】

一方、冗長救済アドレス信号R A D RはHレベルであるため、冗長救済ブロックに含まれるA N D回路A N D 1からは、アドレス信号A D Rと同じ信号が出力される。A N D回路A N D 1から出力された信号は、ワード線W L Rおよびメモリセル電源電圧制御回路1 0 2に入力される。また、N型MOSトランジスタQ N 1 1のゲート電極には、インバータI N V 1 1によってLレベルに変換された信号が入力される。このため、N型MOSトランジスタはオフになり、電源線V L Rには、メモリセル電源電圧制御回路1 0 2から出力されるメモリセル電源電圧V D D M Rが供給される。

【0138】

以上のように、冗長救済が行われる場合には、冗長救済ブロックは、正規のメモリセルアレイに代わって動作する。また、本実施形態に係る半導体記憶装置では、欠陥が存在するメモリセルアレイのメモリセルを非活性状態にし、また、N型MOSトランジスタQ N 1 1によって、これらのメモリセルのメモリセル電源電圧を接地レベルにする。これにより、メモリセルからのリーク電流を削減し、半導体記憶装置の消費電力を抑えることができる。

【0139】

なお、本実施形態に係る半導体記憶装置における冗長救済方法は、第1～第5の実施形態に係る半導体記憶装置に容易に適用することができ、また、他の実施形態においても同様の効果を奏する。

【0140】

また、以上の説明では、発明の理解を容易にするために、本発明の半導体記憶装置は、図1、図5、図7、図8、図11および図16に示すように、少数のメモリセル1 0 0、ワード線ドライバ回路1 0 1、メモリセル電源電圧制御回路1 0 2または2 0 2、O R回路O R 1、メモリセル電源電圧補償回路1 0 6または1 0 7、メモリセル保持参照電圧発生回路1 0 9、ビット線プリチャージ回路3 0 0、ビット線プリチャージ制御回路3 0 1、インバータI N V 1 1、A N D回路A N D 1、N型MOSトランジスタQ N 1 1などを備えることとしたが、上記の構成要素を多数備えていてもよい。そのような構成を有する半導体記憶装置が、本発明の半導体記憶装置と同じ効果を奏することは説明するまでもない。

10

20

30

40

50

## 【産業上の利用可能性】

## 【0141】

本発明の半導体記憶装置は、非活性なメモリセルに供給するメモリセル電源電圧を、メモリセルに含まれるトランジスタの閾値電圧まで下げるにより、メモリセルからのリーコンデンサー電流を低減することから、低消費電力および高速な半導体記憶装置を必要とする機器などに利用することができる。

## 【図面の簡単な説明】

## 【0142】

【図1】本発明の第1の実施形態に係る半導体記憶装置の構成を示す図

【図2】本発明の第1の実施形態に係る半導体記憶装置に備えられるメモリセルの構成を示す図 10

【図3】本発明の第1の実施形態に係る半導体記憶装置に備えられるメモリセル電源電圧制御回路の構成を示す図

【図4】本発明の第1の実施形態に係る半導体記憶装置に備えられるワード線ドライバ回路の構成を示す図

【図5】本発明の第2の実施形態に係る半導体記憶装置の構成を示す図

【図6】本発明の第2の実施形態に係る半導体記憶装置を配置したレイアウト図

【図7】本発明の第3の実施形態に係る半導体記憶装置の構成を示す図

【図8】本発明の第4の実施形態に係る半導体記憶装置の構成を示す図

【図9】本発明の第4の実施形態に係る半導体記憶装置に備えられるメモリセル電源電圧補償回路の構成の一例と、メモリセル保持参照電圧発生回路の構成を示す図 20

【図10】本発明の第4の実施形態に係る半導体記憶装置に備えられるメモリセル電源電圧補償回路の構成の一例と、メモリセル保持参照電圧発生回路の構成を示す図

【図11】本発明の第5の実施形態に係る半導体記憶装置の構成を示す図

【図12】本発明の第5の実施形態に係る半導体記憶装置に備えられるメモリセル電源電圧制御回路の構成を示す図

【図13】本発明の第5の実施形態に係る半導体記憶装置に備えられるピット線プリチャージ回路の構成を示す図

【図14】本発明の第5の実施形態に係る半導体記憶装置に備えられるピット線プリチャージ制御回路の構成を示す図 30

【図15】本発明の第5の実施形態に係る半導体記憶装置の動作を示すタイミングチャート

【図16】本発明の第6の実施形態に係る半導体記憶装置の構成を示す図

【図17】従来の半導体記憶装置の構成を示す図

## 【符号の説明】

## 【0143】

100 メモリセル

101 ワード線ドライバ回路

102、202 メモリセル電源電圧制御回路

103 基板電位供給領域

104 空白領域

105A、105B、110、111、112 メモリセルアレイ

106、107A、107B メモリセル電源電圧補償回路

108A、108B 差動増幅回路

109 メモリセル保持参照電圧発生回路

300 ピット線プリチャージ回路

301 ピット線プリチャージ制御回路

QN1～QN11 N型MOSトランジスタ

QP1～QP15 P型MOSトランジスタ

INV1～INV10 インバータ

40

50

O R 1 OR回路

A N D 1 AND回路

N A N D 1、N A N D 2 N A N D回路

R 1 抵抗素子

W L、W L 1 ~ W L 4、W L R ワード線

B L、B L 1、B L 2、/ B L、/ B L 1、/ B L 2 ビット線

V L、V L 1、V L 2、V L A、V L B、V L R 電源線

V S メモリセル電荷供給線

/ I P C G ビット線プリチャージ制御信号線

A D、A D 1 ~ A D 4、A D R アドレス信号

10

/ P C G ビット線プリチャージ信号

V D D M、V D D M 1、V D D M 2、V D D M A、V D D M B、V D D M R メモリセル電源電圧

V D D 電源端子または電源電圧

V R E F メモリセル保持参照電圧

V T P、V T N メモリ保持電圧

R A D 1、R A D 2、R A D R 冗長救済信号

【図 1】

【図 3】

【図 2】

【図 4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

### 【図15】

【図16】

### 【図17】

---

フロントページの続き

(58)調査した分野(Int.Cl. , DB名)

G 11 C 11 / 41

G 11 C 11 / 40