(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5094482号

(P5094482)

(45) 発行日 平成24年12月12日(2012.12.12)

(24) 登録日 平成24年9月28日(2012.9.28)

(51) Int.Cl.

HO4L 12/56 (2006.01)

F 1

HO4L 12/56 300D

請求項の数 6 (全 21 頁)

(21) 出願番号 特願2008-58703 (P2008-58703)

(22) 出願日 平成20年3月7日 (2008.3.7)

(65) 公開番号 特開2009-218743 (P2009-218743A)

(43) 公開日 平成21年9月24日 (2009.9.24)

審査請求日 平成23年2月25日 (2011.2.25)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】処理装置及びその処理方法

## (57) 【特許請求の範囲】

## 【請求項 1】

受信されたIPパケットを処理する処理装置であって、

第1の記憶手段を制御する制御手段と、

フラグメントされたIPパケットの受信状況を示すデータが第2の記憶手段から前記第1の記憶手段へ転送されている間に、前記IPパケットのヘッダが正常に受信されたか否かを判断し、その判断の結果に応じて前記第1の記憶手段に記憶されたデータの更新を前記制御手段に指示する処理手段と、を有し、

前記処理手段は、前記受信されたIPパケットの識別子を前記制御手段に通知し、前記制御手段が前記第1の記憶手段に記憶されていないと判断したデータを前記第2の記憶手段から前記第1の記憶手段へ転送している間に、前記IPパケットのヘッダが正常に受信されたか否かを判断することを特徴とする処理装置。

## 【請求項 2】

前記処理手段は、前記受信されたIPパケットの識別子を前記制御手段に通知し、前記制御手段が前記フラグメントされたIPパケットの受信状況を示すデータを前記第2の記憶手段から前記第1の記憶手段へ転送している間に、前記IPパケットのヘッダが正常に受信されたか否かを判断することを特徴とする請求項1に記載の処理装置。

## 【請求項 3】

前記制御手段は、前記フラグメントされたIPパケットの、フラグメントされる前のパケットにおける位置に応じた順序で、前記第2の記憶手段から前記第1の記憶手段にデー

タを転送することを特徴とする請求項 1 又は 2 に記載の処理装置。

【請求項 4】

前記処理手段は、前記フラグメントされた IP パケットのうち、正常に受信された IP パケットを示すデータが記憶されるように、前記第 1 の記憶手段に記憶されたデータの更新を前記制御手段に指示することを特徴とする請求項 1 乃至 3 の何れか 1 項に記載の処理装置。

【請求項 5】

受信された IP パケットを処理する処理装置の処理方法であって、

制御手段が、第 1 の記憶手段を制御する制御工程と、

処理手段が、フラグメントされた IP パケットの受信状況を示すデータが第 2 の記憶手段から前記第 1 の記憶手段へ転送されている間に、前記 IP パケットのヘッダが正常に受信されたか否かを判断し、その判断の結果に応じて前記第 1 の記憶手段に記憶されたデータの更新を前記制御手段に指示する処理工程と、を有し、

10

前記処理工程では、前記受信された IP パケットの識別子を前記制御工程に通知し、前記制御工程が前記第 1 の記憶手段に記憶されていないと判断したデータを前記第 2 の記憶手段から前記第 1 の記憶手段へ転送している間に、前記 IP パケットのヘッダが正常に受信されたか否かを判断することを特徴とする処理装置の処理方法。

【請求項 6】

コンピュータを請求項 1 乃至 4 の何れか 1 項に記載の処理装置として機能させるためのプログラム。

20

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、IP (Internet protocol) 通信を利用するアプリケーション機器や、IP 通信制御機器におけるプロトコル処理に関し、特に、複数のフラグメントパケットに分割して送信された IP パケットの受信技術に関する。また、IP プロトコル処理の高速化を TOE (TCP/IP Offload Engine) 技術によって実現する組み込み機器に好適である。

【背景技術】

【0002】

プロトコル処理の中でプロセッサ処理量が大きい処理の 1 つに IP リアセンブルがある。IP 通信では、送信元或いは伝送経路上で 1 つの IP パケットを複数の IP パケットに分割して転送し、受信側で分割元の 1 つのパケットを復元して受信するメカニズムがある。1 つの IP パケットを複数の IP パケットに分割して転送する処理は IP フラグメント (IP Fragmentation) と呼ばれている。一方、分割された複数の IP パケットを受信し、元の IP パケットに復元する処理は IP リアセンブル (IP Reassembly) と呼ばれている。IP リアセンブルは、RFC 791 に仕様が公開されている。

30

【0003】

また、IP リアセンブルには、RFC 791 に記載の処理方法と、RFC 815 に記載の処理方法の 2 つのアルゴリズムが知られている。本発明は、前者の方法に関与するものであるので、前者の方法について紹介しておく。尚、ここでは、前者の IP リアセンブル処理方法を、ビットマップテーブル方式と呼称する。

40

【0004】

ビットマップテーブル方式による IP リアセンブルでは、受信側が送信元 IP パケットのペイロードデータの 8 オクテット分を 1 ビットに割り当てたビットテーブルを用意する。IP データグラムは最大長が 65535 オクテットであるため、用意するビットテーブルは、約 8 キロビットの長さが必要である。そして、到着する各フラグメントパケットのペイロードデータを保存しながら、フラグメントデータのオフセット位置と長さに相当する、該ビットテーブルのビットをセットしていくことで、フラグメントデータの受信状況を管理する。その後、送信元の IP パケットのペイロード長さに相当するビットテーブル上のビットが全てセットされると、分割元の IP パケットの再組み立てに必要なデータが

50

揃ったことを意味し、IPリアサンブル処理の完了となる。

#### 【0005】

近年、ネットワーク通信が急速に高速化しており、既に民生用にギガビットネットワーク対応のイーサネット（登録商標）製品が普及している。更に、現在IEEE802.3ワーキンググループにおいて40メガビット／秒、或いは100メガビット／秒の伝送速度を実現可能な規格が標準化されようとしている。こうしたネットワーク通信の高速化に伴い、IP通信を利用するアプリケーションも送受信するデータ量も増大しており、通信端末機器にとって通信プロトコル処理にかかる負荷が高くなっている。

#### 【0006】

従来、IP通信のプロトコル処理は、TCP/IP（Transmission Control Protocol / Internet Protocol）プロトコルスタックというソフトウェアで実現されることが多い。IP通信機能を有する組み込み機器においても、IPプロトコル処理をソフトウェアで実装する場合が多い。しかし、小規模な組み込み機器では、製造コストや電力消費量の面で有利である、動作周波数が低いCPUを搭載することが多いため、必要なソフトウェアによるプロトコル処理のプロセッサ負荷が高くなってしまう。

#### 【0007】

そのため、従来の処理では高い通信性能を実現することが困難になってきている。また、通信処理にかかる処理負荷が原因で、アプリケーション処理にCPUリソースを十分に割り当てられないことも問題となる。

#### 【0008】

このような問題への対策として、プロセッサの通信処理負荷を軽減し、高速なIP通信を実現するTOE（TCP/IP Offload Engine）と総称される技術がある。このTOEとは、アプリケーションを実行するプロセッサとは別の処理手段により、TCP/IPプロトコル処理の高速化を図る技術である。

#### 【0009】

TOEでは、プロトコル処理全体又は一部をハードウェア処理（集積回路）で実行して高速化するケースが多い。また、組み込み機器においては、TOEをLSI化してチップに内蔵する実装も行われている。

#### 【特許文献1】特開2007-274056号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0010】

上述したビットマップテーブル方式のIPリアサンブルでは、分割前のIPパケットの最大パケットサイズに対応するために必要なテーブルサイズは1Kバイト（8192バイト）である。また、IPリアサンブルの同時並行処理数と同数のビットマップテーブルが必要となる。通信の高速化により単位時間あたりの受信IPパケット数が増加すると、並行処理するIPリアサンブルも増加し、ビットマップテーブルに必要なメモリサイズが増加してしまう。

#### 【0011】

一方、上述のTOE技術によってハードウェア処理でIPリアサンブルの高速化を実現するためには、アクセス遅延が小さいオンチップメモリ上にビットテーブルを形成することが望ましい。しかしながら、並行処理可能な数に見合う大きなメモリ容量が必要となり、メモリコストが高価であるオンチップメモリでは、メモリコストが高くなってしまう。一方、小容量のメモリでは並行処理可能な数に制限が生じることが問題となる。

#### 【0012】

このビットデータでフラグメントデータの到着状況を管理する先行技術として、例えば特許文献1がある。特許文献1では、IPフラグメントの分割サイズを狭い範囲に限定することで、フラグメントパケットに暗黙的な断片番号を付与し、フラグメントパケットの受信状況の管理を単純化して高速化している。

#### 【0013】

10

20

30

40

50

この方法では、予めIPパケットを分割するサイズを限定しているので、フラグメントパケットの受信状況を管理するビット幅を8Kビットよりも小さくすることが可能であるため、IPリアセンブルに必要なメモリサイズを縮小することができる。しかしながら、分割サイズを狭い範囲に制限するため、任意サイズのフラグメントパケットのIPリアセンブルを実行するには不適である。

#### 【0014】

本発明は、フラグメントされたIPパケットのリアセンブル処理を高速化し、並行処理にかかるメモリコストを減少させることを目的とする。

#### 【課題を解決するための手段】

#### 【0015】

本発明は、受信されたIPパケットを処理する処理装置であって、第1の記憶手段を制御する制御手段と、フラグメントされたIPパケットの受信状況を示すデータが第2の記憶手段から前記第1の記憶手段へ転送されている間に、前記IPパケットのヘッダが正常に受信されたか否かを判断し、その判断の結果に応じて前記第1の記憶手段に記憶されたデータの更新を前記制御手段に指示する処理手段と、を有することを特徴とする。

10

#### 【発明の効果】

#### 【0017】

本発明によれば、フラグメントされたIPパケットのリアセンブル処理を高速化し、並行処理にかかるメモリコストを減少させることができる。

#### 【発明を実施するための最良の形態】

20

#### 【0018】

以下、図面を参照しながら発明を実施するための最良の形態について詳細に説明する。

#### 【0019】

##### 【第1の実施形態】

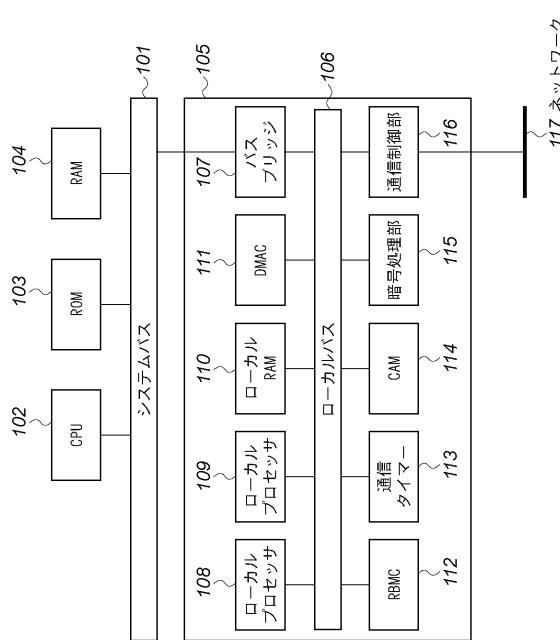

図1は、第1の実施形態におけるネットワーク通信装置の構成の一例を表すブロック図である。図1に示すように、CPU102、ROM103、RAM104がシステムバス101に接続されている。ここで、CPU102は、ROM103に格納されたシステムプログラムをRAM104に読み出して実行する。RAM104は、システムプログラムを実行時に使用される主記憶装置である。

#### 【0020】

30

105に示すプロックは、本発明に係るIPプロトコル処理装置であり、システムバス101に接続されている。IPプロトコル処理装置105は、CPU102によって実行されるアプリケーションの通信に必要なTCP/IPプロトコル処理、及びネットワーク117へのデータ送受信を実行する。

#### 【0021】

IPプロトコル処理装置105において、バスブリッジ回路107は、内部のローカルバス106をシステムバス101に接続するもので、ローカルバス106とシステムバス101間のデータ転送が可能である。そして、IPプロトコル処理装置105と、CPU102、ROM104、RAM104で構成される外部のシステムとは、それぞれのバス回路が相互に接続されて通信データや制御データの入出力をバス転送によって行える仕組みになっている。

40

#### 【0022】

また、TCP/IPプロトコル処理を実行するための2つのローカルプロセッサ108、109、ローカルRAM110、データ転送を行うためのDMAコントローラ(DMA C)111がローカルバス106に接続されている。更に、IPリアセンブルのビットテーブル処理を実行するリアセンブルビットマップコントローラ(RBMC)112、プロトコル処理のタイマー処理に利用する通信タイマー113がローカルバス106に接続されている。更に、プロトコル処理の様々な管理情報の格納と検索を行うための連想メモリであるCAM(Content Addressable Memory)114がローカルバス106に接続されている。更に、暗号化通信処理に必要な暗号化/復号化の計算処理を実行する暗号処理部1

50

15、ネットワーク117に対してデータ送受信を行う通信制御部116がローカルバス106に接続されている。

【0023】

IPプロトコル処理装置105は、IPプロトコル処理を複数のプロセッサ処理による並列処理で実行する。更に、111から115の各ハードウェア処理部を利用し、TCP/IPプロトコルのパケット送受信と、送信フロー制御や輻輳制御、通信エラー制御、更にIPsecやSSL/TLS等の暗号通信プロトコル処理を実行する。

【0024】

また、ローカルプロセッサ108、109が実行するプログラムはROM103に保存されており、IPプロトコル処理装置105の起動時にローカルRAM109上にコピーされる。ローカルプロセッサ108、109は、ローカルRAM109からプログラムを読み出して実行する。

【0025】

尚、図1では、2個のローカルプロセッサ108、109が図示されているが、ソフトウェア処理を実行するプロセッサの個数は2つに限定されるものではない。

【0026】

DMAC111は、IPプロトコル処理装置105の内部又は外部のメモリデバイスやハードウェアモジュール間における送受信データや制御データの転送処理を行う。RBM C112は、ビットマップ方式(RFC791)のIPリアセンブルアルゴリズムで使用するビットテーブルのビット操作処理や、RAM104との間でビットテーブルのデータ転送を行う。

【0027】

通信タイマー113は、IPリアセンブルにおけるタイムアウト時間の計測や、TCPプロトコル通信における再送処理、確認応答送信などの各種タイマーで必要な時間計測のように、IPプロトコル処理における様々なタイムアウト処理に利用される。暗号処理部115は、IPsecやSSL(Secure Socket Layer)/TLS(Transport Layer Security)などの暗号通信プロトコル処理で処理負荷が大きい暗号化/復号化の演算処理を実行する。

【0028】

通信制御部116は、ネットワーク117のMAC処理(伝送メディア制御処理)や、フレームデータの送受信を行う機能が実装される。ネットワーク117は、例えばイーサネット(登録商標)のような有線ネットワークであるが、無線ネットワークや、光ファイバーネットワーク等であっても良い。

【0029】

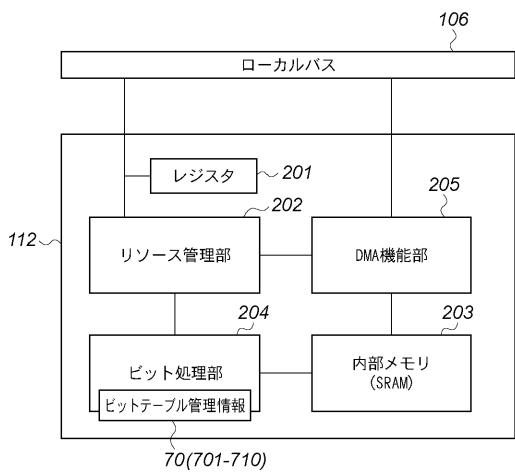

ここで、RBM C112の実施構成の一例を、図2を参照して説明する。図2は、第1の実施形態におけるRBM Cの構成の一例を表すブロック図である。

【0030】

RBM C112は、レジスタ201、リソース管理部202、内部メモリ(SRAM)203、ビット処理部204、DMA機能部205で構成される。まず、レジスタ201はRBM C112の設定や起動などの制御インターフェースであり、複数のレジスタセットである。そして、このレジスタ201に対してローカルプロセッサ108、109が読み書きを行い、RBM C112を設定、制御する。

【0031】

リソース管理部202は、複数のビットテーブルのデータ管理を行う。管理情報データは、図1に示すローカルRAM109に記憶される。ビット処理部204は、内部メモリ203に格納されたビットテーブルデータの任意の範囲に対してビット操作処理を行う。このビット操作処理には、任意長のビット列に対して全ビットを1にセット、全ビットを0にクリア、値が1であるビット数のカウント、全ビットを1にセットしたときに0から1に変化したビット数のカウントが含まれる。

【0032】

10

20

30

40

50

内部メモリ 203 は、この例ではアクセス遅延が非常に小さいメモリとして実装される。R BMC112 は、内部メモリ 203 上にビット処理部 204 がビット操作処理を行うビットテーブルデータを一時格納する。ビット処理部 204 のビット操作処理において、内部メモリ 203 に対してデータの読み書きが実行される。

#### 【0033】

DMA 機能部 205 は、リソース管理部 202 によって制御され、内部メモリ 203 と R BMC112 の外部にあるメモリとの間でビットテーブルのデータ転送を実行する。

#### 【0034】

以上の構成において、IP リアセンブルのビットテーブルを RAM104 に確保する。

そして、R BMC112 がビットテーブルのビット操作処理を行うときには対象のビット

テーブルデータを内部メモリ 203 に一時格納し、一時格納したビットテーブルデータに

対してビット操作処理を実行する。

#### 【0035】

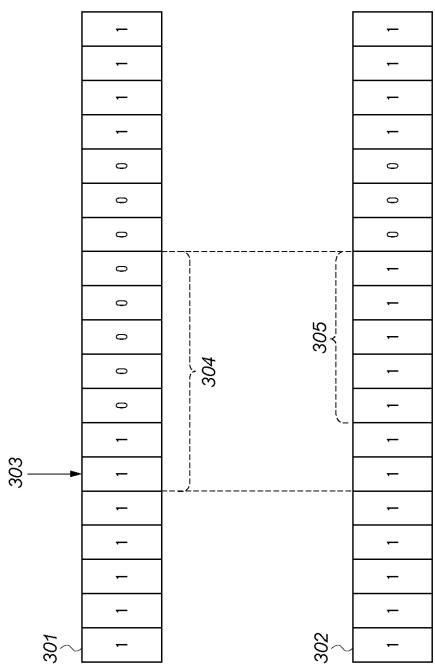

ここで、IP リアセンブルのビットテーブルのビット操作処理を、図 3 を参照して説明

する。IP リアセンブルで使用するビットテーブルは、先頭ビットから順番に各ビットが

分割元 IP パケットのペイロードの先頭から 8 オクテット毎にマッピングされる。即ち、

各ビットは、IP リアセンブルによって対応する 8 オクテットが受信済みであるか否かを

記憶しておくフラグである。例えば、図 3 に示すビットテーブル 301 で、値が 1 である

ビットが対応する 8 オクテットは、既に受信済みであることを表している。

#### 【0036】

IP リアセンブルでは、受信したフラグメントパケットの IP ヘッダの内容から、その

フラグメントパケットが運ぶフラグメントデータについて、分割前の IP パケットのペイ

ロードにおけるフラグメントオフセットとフラグメントサイズを得ることができる。この

情報を元に、受信したフラグメントデータが対応するビット範囲の各ビットを、受信済み

を表す 1 に書き込んでいく。また、最後尾のフラグメントパケットを受信すると、分割元

の IP パケットの全長を得ることができ、ビットテーブル上で必要なビット幅が確定する

。従って、分割元 IP パケットのペイロード長分のビット列が全て値 1 で埋まったとき、

分割元の IP パケットを構成する全てのフラグメントデータを受信したことになる。

#### 【0037】

図 3 に示す例では、301 のビットテーブルで、303 は受信したフラグメントデータ

の分割元 IP パケットペイロードにおけるオフセット位置を表し、304 はフラグメント

データに対応するビット幅を表している。ここで、ビットテーブルはフラグメントされた

IP パケットの受信状況を管理するためのテーブルである。

#### 【0038】

ビット処理部 204 は、フラグメントデータを受信すると、303 の位置から 304 の

幅だけ各ビットに 1 を書き込む。その結果、301 のビットデータは 302 に示すように

更新される。305 に表す部分は、新規に 0 から 1 に変化したビットであることを表して

いる。ビット処理部 204 はこのようなビット操作処理を実行する。

#### 【0039】

また、ビット処理部 204 は値が 0 から 1 に変化したビット数をカウントし、R BMC

112 のレジスタ 201 に新規に受信したフラグメントデータサイズを設定する。

#### 【0040】

上述したように、ビット処理部 204 は、アクセス遅延が小さい内部メモリ 203 上の

データに対してビット操作処理を行う。これにより、IP リアセンブルを高速化するこ

ができるため、内部メモリ 203 は、例えば SRAM を実装することが考えられる。

#### 【0041】

しかし、アクセス遅延の小さい内部メモリ 203 に、並行処理する全ての IP リアセン

ブルのビットテーブルを置くことは、並行処理可能な IP リアセンブル数に応じたメモリ

容量が必要となり、メモリコストが非常に高くなってしまう。

#### 【0042】

10

20

30

40

50

従って、全てのビットテーブルはRAM104に確保し、IPリアサンブルで処理対象となるビットテーブルデータだけを内部メモリ203にコピーし、一時格納することで、内部メモリ203のメモリコストを抑えることができる。

#### 【0043】

第1の実施形態では、並行処理する各IPリアサンブルに対してIPリアサンブルIDという識別子を付与し、ビットテーブルに対応付けて管理する。そして、RAM104上のビットテーブルのうち、ビット操作処理の実行頻度が高いビットテーブルを内部メモリ203に一時格納しておくようとする。

#### 【0044】

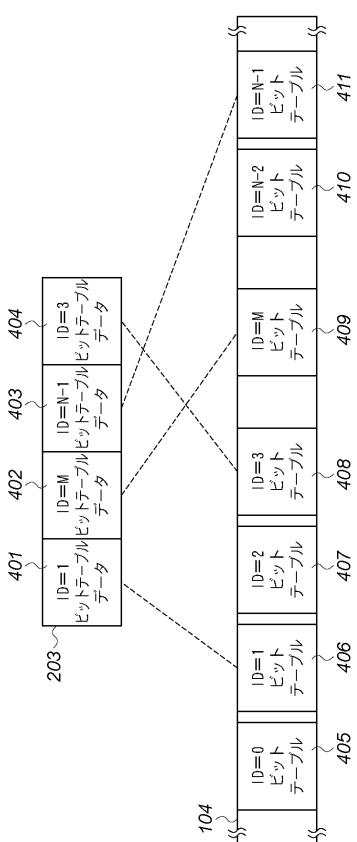

図4は、IPリアサンブルのビットテーブルをIPリアサンブル識別子で管理する状態を示す図である。この例では、ある時点において、RAM104上に処理途中であるN個のビットテーブルが確保されており、内部メモリ203には4個のビットテーブルが一時格納されている状態を示している。10

#### 【0045】

図4に示すように、RAM104には、405～411に示すN個のビットテーブルが任意のメモアドレスに配置されている。このうち、IPリアサンブルIDが1、3、M、N-1であるビットテーブル406、408、409、411が、それぞれ内部メモリ203の401、402、403、404に示す場所に一時格納されている。

#### 【0046】

即ち、この内部メモリ203へのデータの格納方法は、ビットテーブルサイズを単位とするフルアソシエイティブ方式である。図4に示す内部メモリ203の使用例では、ある時点において、IPリアサンブルIDが1、3、M、N-1であるビットテーブルが内部メモリ203に置かれている。従って、その時点から次に受信するフラグメントパケットが、これらのIPリアサンブルの何れかであれば、RAM104から内部メモリ203にビットテーブルを転送する必要がない。20

#### 【0047】

しかしながら、内部メモリ203にビットテーブルを格納していないIPリアサンブルのフラグメントパケットを受信した場合、処理対象であるビットテーブルをRAM104から内部メモリ203にコピーする必要がある。また、例えば内部メモリ203にビットテーブルを格納する空きが無い場合、一時格納しているビットテーブルの何れかをRAM104に書き戻し、空いた場所に次の処理対象となるビットテーブルを一時格納する必要が生じる。30

#### 【0048】

そのため、RBM C112内のリソース管理部202において、リアサンブルID毎にビットテーブルの管理を行う。リソース管理部202がIPリセンブルID毎に保持するビットテーブル管理情報70は、次の701～710を含む。701はリアサンブルIDである。702はこのビットテーブルを使用するIPリアサンブルにおいて最後に処理したIPリアサンブルの処理時刻の記録である。703は最後に処理したIPリアサンブルの時間間隔(到着間隔)の記録である。704はRAM104にあるビットテーブルのメモアドレスである。705は内部メモリ203にビットテーブルが一時格納されているか否かを示すフラグである。706～710は内部メモリ203にビットテーブルを一時格納しているときに使用するパラメータである。40

#### 【0049】

706は内部メモリ203上のビットテーブルデータのアドレスであり、707はその内部メモリ203上でのビットテーブルデータのサイズを示す。708はビットテーブルデータが内部メモリ203で変更されたかを示すフラグである。そして、709はビットテーブルの変更されたビット範囲の先頭位置を意味するオフセットアドレスであり、710は変更範囲を示すデータサイズである。各ビットテーブルの管理情報をローカルRAM110に保存し、RBM C112のリソース管理部202によって更新される。

#### 【0050】

50

リソース管理部 202 は、RAM104 からビットテーブルデータを転送して内部メモリ 203 に格納するとき、ビットテーブルデータを一時格納する空きがあるか否かを、ビットテーブル管理情報をチェックして判定する。また、空きがない場合には、ビットテーブル管理情報にある最後に処理した IP リアセンブルの時間間隔 703 を比較し、最も長い到着間隔である IP リアセンブルのビットテーブルを選択する。選択されたビットテーブルは内部メモリ 203 から RAM104 にデータを書き戻し、内部メモリ 203 に空き領域を作成する。

#### 【0051】

このようにして、IP リアセンブルでビットテーブルを内部メモリ 203 に一時格納していない場合にも、RAM104 から内部メモリ 203 にビットテーブルデータを転送して一時格納することを実行する。10

#### 【0052】

尚、内部メモリ 203 及び RAM104 間のデータ転送は、RBMC112 内の DMA 機能部 205 が実行する。

#### 【0053】

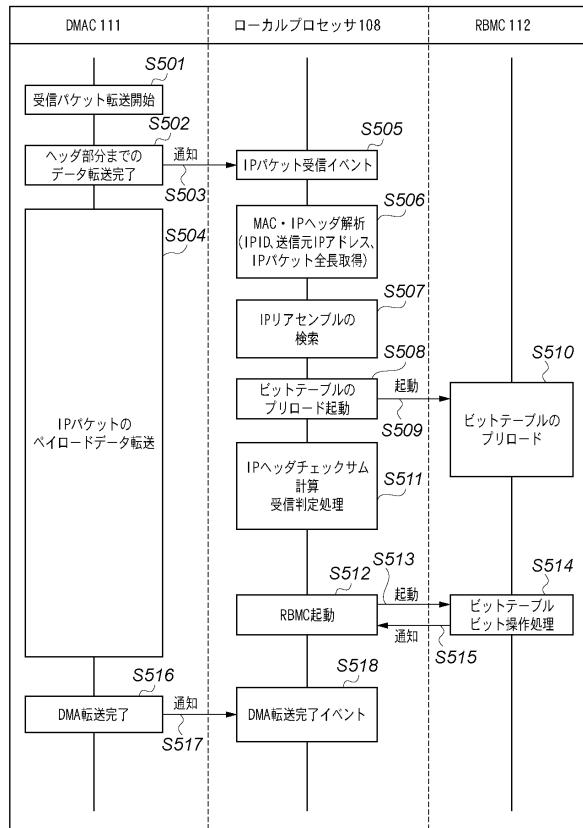

次に、IP プロトコル処理装置 105 で実行される IP リアセンブルの全体的な処理の流れを、図 5 を参照して説明する。図 5 は、IP リアセンブルにおける DMA C111、RBMC112、ローカルプロセッサ 108 の時間的な処理シーケンスを示す図である。尚、図 5 に示す例は、受信 IP パケットがフラグメントパケットであることを前提としたシーケンスである。20

#### 【0054】

通信制御部 116 が IP パケットを受信すると、はじめに DMA C111 が S501 で受信 IP パケットの転送を開始し、通信制御部 116 から RAM104 へ転送が行われる。また、受信 IP パケットの先頭から IP ヘッダまでの部分に相当するサイズのデータは RAM104 に転送されると共に、ローカル RAM110 へも同時転送される。そして、S502 で IP パケットの転送が、先頭の MAC ヘッダ（リンク層フレームのヘッダ）と IP ヘッダ部分に相当するデータサイズまで終わると、ローカルプロセッサ 108 へ受信通知（S503）を行う。更に、DMA C111 は通知を行った後も、S504 で引き続きペイロード部分の転送を続行する。

#### 【0055】

一方、ローカルプロセッサ 108 は、S505 で DMA C111 からの通知を受けて、IP パケットの受信処理を開始する。即ち、ローカルプロセッサ 108 は受信 IP パケット全体が RAM104 に転送されるのを待たずに、IP パケットの受信処理を開始する。次に、ローカルプロセッサ 108 は S506 でローカル RAM110 に転送された MAC ヘッダと IP ヘッダの内容を解析する。ここで、宛先 MAC アドレス、宛先 IP アドレスが受信可能であるかチェックする。更に、S506 で IP パケットヘッダの内容に基づきフラグメントパケットであるかを判定する。30

#### 【0056】

次に、S506 でフラグメントパケットであることが判定されると、S507 で、その受信フラグメントパケットを対象とする IP リアセンブルのリアセンブル ID の検索処理を行う。続いて、S508 で RBMC112 に対して S507 で検索されたリアセンブル ID に対応するビットテーブルのプリロードを起動（S509）する。このプリロードは、処理対象のビットテーブルデータを内部メモリ 203 に一時格納する処理である。40

#### 【0057】

起動指示により、RBMC112 は、S510 で内部メモリ 203 にそのリアセンブル ID のビットテーブルが格納されているかを調べ、格納されていない場合は RAM104 に確保されているビットテーブルを一時格納する。即ち、S510 で RAM104 と内部メモリ 203 の間でビットテーブルのデータ転送を行う。

#### 【0058】

一方、ローカルプロセッサ 108 は、RBMC112 のプリロードを起動した後、その50

処理完了を待たずに、S511で受信IPパケット（即ちフラグメントパケット）のIPヘッダチェックサムの検証を実行する。IPヘッダのチェックサムが正しいならば、IPヘッダの内容が正しいので、そのIPパケットは受信可能であると判定する。

#### 【0059】

次に、S512でRBM C112に対して、ビットテーブルへのビット操作処理を起動（S513）する。そして、ローカルプロセッサ108は、S514のビット操作処理の完了を待機する。

#### 【0060】

起動指示により、RBM C112は、S514で内部メモリ203に一時格納しておいたビットテーブルデータに対するビット操作処理を実施する。この処理でビット値を0から1に変更したビット数分のデータサイズ、即ち新規に受信したフラグメントサイズを、レジスタ201に設定し、処理完了を通知（S515）する。10

#### 【0061】

ここで、ローカルプロセッサ108が通知を受信すると、IPリアセンブル処理で新規に受信したフラグメントデータサイズを得ることができる。

#### 【0062】

一方、DMAC111がS516で、受信IPパケットの全体をRAM104に転送し終えると、ローカルプロセッサ108に転送完了を通知（S517）する。これにより、ローカルプロセッサ108がS518でDMA転送完了通知を受信すると、ローカルプロセッサ108はこのIPパケットの受信処理を終了する。20

#### 【0063】

以上がIPプロトコル処理装置105で実行されるIPリアセンブルの全体的な処理の流れである。

#### 【0064】

第1の実施形態では、S511でIPヘッダチェックサム検証後に受信IPパケットが受信可能であるかを判定している。しかし、その判定後のS514でIPリアセンブルのビットテーブルのビット操作処理に至った段階で、RBM C112が内部メモリ203にビットテーブルデータを格納するのではない。前段のS508でRBM C112にビットテーブルのプリロードを起動している。つまり、ローカルプロセッサ108がS511でIPヘッダチェックサムの検証を行っている間にRBM C112はS510でプリロード処理を実行する。30

#### 【0065】

このような処理シーケンスにより、ローカルプロセッサ108のIPパケット受信処理とRBM C112のプリロード処理を並列的に実行する。これにより、RBM C112が内部メモリ203にビットテーブルデータを一時格納する際に、内部メモリ203とRAM104の間でデータ転送が発生したとしても、その時間的なオーバーヘッドは無視することができる。

#### 【0066】

S511の結果、IPパケットが受信可能であるならば、S512でIPリアセンブルを実行する。ここで、既に内部メモリ203にはビットテーブルデータが格納されているため、S514のビット操作処理は高速に実行される。もし、S511でIPパケットが受信不可と判定した場合でも、S510では内部メモリ203にビットテーブルデータを確保しただけであるため、ビットテーブルの状態を変更していないことは明白である。40

#### 【0067】

次に、上述したIPリアセンブルの処理シーケンスにおけるS506～S808で実行されるローカルプロセッサ108の処理を、図6及び図7を参照して詳しく説明する。

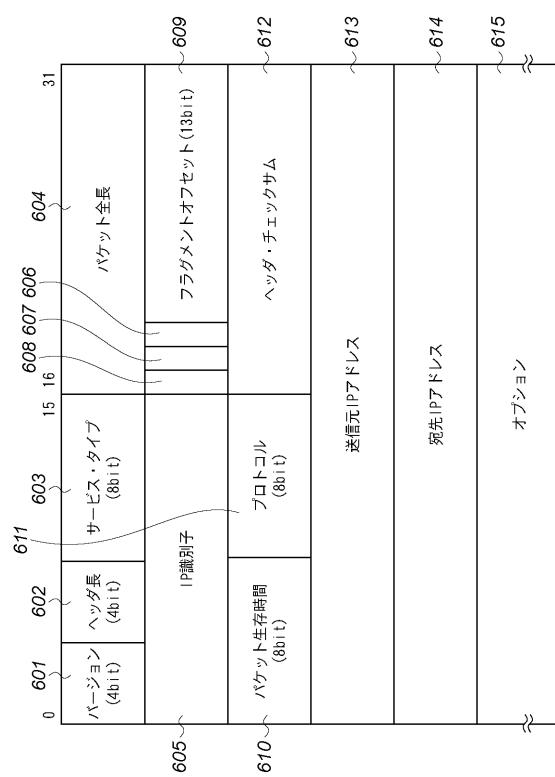

#### 【0068】

図6は、IP v4（IPバージョン4）パケットのIPヘッダのフォーマットを示す図である。IPパケットがフラグメントパケットであるか否かは、フラグメント継続フラグ606とフラグメントオフセット609で判定する。フラグメント継続フラグ606が150

であれば、このIPパケットがフラグメントパケットであり、更に後続するフラグメントデータを運ぶ別のIPパケットが存在していることを示す。

#### 【0069】

また、フラグメント継続フラグ606が0であるが、フラグメントオフセット609が0でなければ、このIPパケットはフラグメントデータの最後尾を運ぶフラグメントパケットである。このような判定方法により、受信したIPパケットがフラグメントパケットであるかを判定する。

#### 【0070】

また、同じ分割元パケットを構成するフラグメントパケットは、IPヘッダ内のIP識別子605、プロトコル611、送信元IPアドレス613、宛先IPアドレス614の4つのフィールド値が同一でなければならない。

10

#### 【0071】

第1の実施形態では、これらの4つのパラメータとIPリアセンブルを識別するためのリアセンブルIDを関連付けてCAM114に検索エントリデータを保存する。この検索エントリデータの保存は、新規のIPリアセンブルを開始し、新規のリアセンブルIDを決定したときに実行する。また、フラグメントパケット受信時のIPリアセンブルの検索処理は、CAM114に対して、IPヘッダから得られる4つのフィールドを検索キーとしてリアセンブルIDを検索することである。この検索の結果、リアセンブルIDが見つからなかった場合は、新規のIPリアセンブルを開始し、新規のIPリアセンブルを決定する。

20

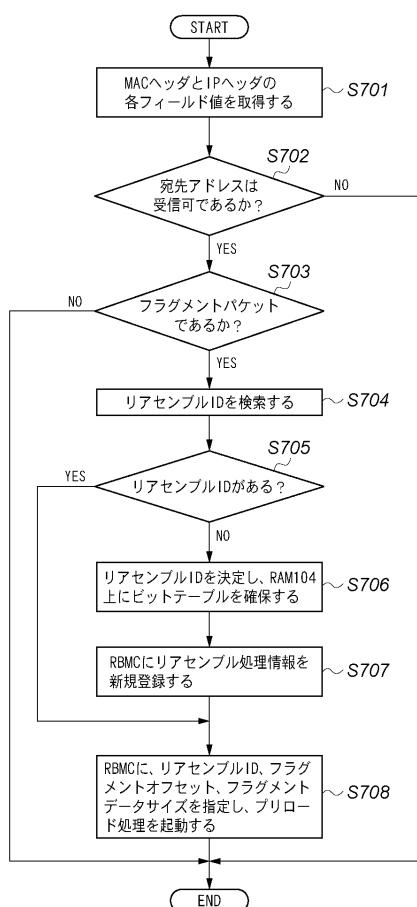

#### 【0072】

図7は、ローカルプロセッサ108の処理(図5のS505～S508)を示すフローチャートである。まずS701で、受信IPパケットのMACヘッダとIPヘッダの各種パラメータを読み出して取得する。次に、S702で宛先MACアドレスと宛先IPアドレスが受信可能であるかを判定する。判定した結果、受信できないアドレスである場合は、その受信パケットを破棄し、この処理を終了する。

#### 【0073】

また、宛先MACアドレスと宛先IPアドレスが共に受信可能なアドレスである場合はS703へ処理を進める。このS703では、S701で取得したIPヘッダ内のフラグメント継続フラグ606とフラグメントオフセット609の値により、このIPパケットがフラグメントパケットであるか否かを調べる。ここで、フラグメントパケットでは無い場合、IPリアセンブルを実行しないで、通常のIPパケット受信の処理を実行する。

30

#### 【0074】

一方、S703でフラグメントパケットであると判定した場合はS704へ処理を進め、フラグメントパケットのリアセンブルIDを取得するために検索処理を実行する。尚、この検索処理については上述した通りであるので、その説明は省略する。

#### 【0075】

続いて、S705でリアセンブルIDが検索できたか否かを判定し、検索できなかった場合はS706へ処理を進める。このS706では、フラグメントパケットは新規にIPリアセンブルを開始する必要があるので、新しいリアセンブルIDを決定する。そして、パケットのIP識別子、プロトコル、送信元IPアドレス、宛先IPアドレスの4つの値に新しいリアセンブルIDを関連付けて、CAM114に検索エントリを登録しておく。更に、新規のリアセンブルIDに対応するビットマップテーブルをRAM104上に確保する。続くS707では、S706で新規に決定したリアセンブルIDと、RAM104上に確保したビットテーブルのメモリアドレスをRBMC112のレジスタ201に設定する。このとき、RBMC112のリソース管理部202が新しいIPリアセンブルのビットテーブル管理情報をローカルRAM110に作成する。

40

#### 【0076】

また、S705でリアセンブルIDが検索できた場合及びS707での処理を終了した場合はS708へ処理を進める。このS708では、リアセンブルID、IPヘッダから

50

取得したフラグメントオフセット 609、IP パケットのペイロードの長さであるフラグメントデータサイズ、RBM C112 のレジスタ 201 に設定してプリロード処理を起動する。

#### 【0077】

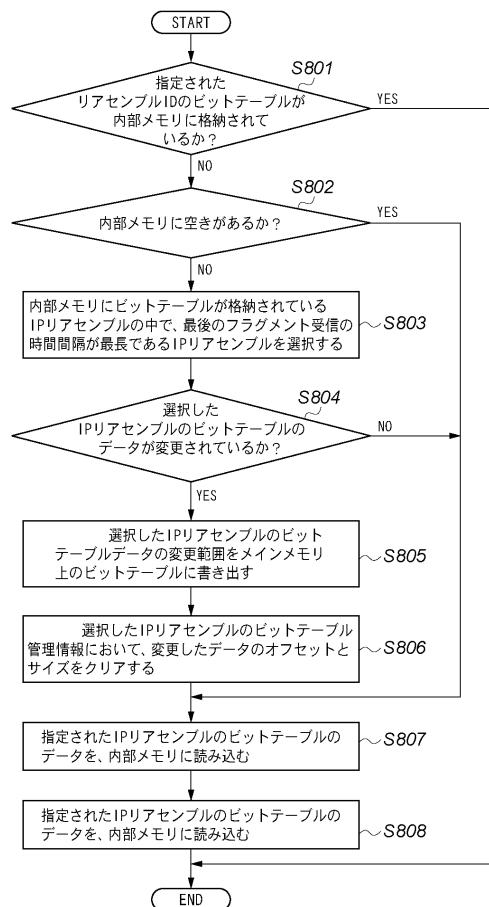

次に、上述した IP リアセンブルの処理シーケンスにおける S510 で実行される RBM C112 のビットテーブルのプリロード処理を、図 8 を用いて説明する。

#### 【0078】

図 8 は、ビットテーブルのプリロード処理を示すフローチャートである。まず S801 では、レジスタ 201 に指定にされたリアセンブル ID に対応するビットテーブルが内部メモリ 203 に一時格納されているかを調べる。ここで、内部メモリ 203 に格納されていれば、この処理を終了する。

10

#### 【0079】

また、指定されたリアセンブル ID のビットテーブルが内部メモリ 203 に格納されていなければ S802 へ処理を進め、内部メモリ 203 にビットテーブルを格納する空きがあるか否かを調べる。もし空きがあれば S807 へ処理を進め、空きが無ければ S803 へ処理を進める。

#### 【0080】

S803 では、内部メモリ 203 にビットテーブルを格納している IP リアセンブルについて、各々が最後に処理されたときの前回処理からの時間間隔を比較し、最も時間間隔が長い IP リアセンブルを選択する。ここでは、リソース管理部 202 が IP リセンブル ID 每に保持するビットテーブル管理情報 70 を参照し、内部メモリ格納フラグ 705 がオンであるビットテーブル管理情報の中で、最後に処理した IP リアセンブルの時間間隔 703 の値で比較する。即ち、ビットテーブル管理情報の 703 の値が最も大きいリアセンブル ID を選択する。

20

#### 【0081】

次に、S804 で、選択したリアセンブル ID の内部メモリ 203 上のビットテーブルが変更されたかを調べる。ここでは、選択されたリアセンブル ID のビットテーブル管理情報で 708 の内部メモリデータ変更フラグがオンであるかをチェックする。もし、変更されていれば S805 へ処理を進め、そうでなければ S807 へ処理を進める。

#### 【0082】

S805 では、選択されたリアセンブル ID の内部メモリ 203 上のビットテーブルが変更された範囲だけを RAM104 上にあるビットテーブルに書き戻す処理を行う。RB M C112 は、ビット操作処理の際、ビットテーブル管理情報の 709 のデータ変更オフセットと、710 のデータ変更サイズを更新する。そのため、書き戻す必要のあるビットテーブルの変更部分は 709 から 710 の範囲である。ここでは、内部メモリ 203 上のビットテーブルの変更部分だけを RAM104 上のビットテーブルに書き込んで反映する。

30

#### 【0083】

次に、S806 では、RAM104 に書き戻したビットテーブルについて、管理情報の 705 から 710 の全てのフィールドをクリアし、S807 へ処理を進める。

40

#### 【0084】

この S807 では、指定されたリアセンブル ID のビットテーブルデータを内部メモリ 203 に読み込む。内部メモリ 203 上の読み込む場所は、S802 で見つかった空きであるか、S803 で選択したリアセンブル ID のビットテーブルがあった場所である。

#### 【0085】

次に、S808 で、レジスタ 201 に設定されたフラグメントオフセットとフラグメントデータサイズの範囲のビットテーブルデータを優先して先に、内部メモリ 203 に転送する。この部分以外のビットテーブルデータは後から転送する。これは、ビットテーブルの全体を内部メモリ 203 に転送する前に、ビット操作処理が起動された場合に、直ちにビット操作処理を行うことを可能にするためである。以上のようにして、ビットテーブル

50

のプリロード処理が実行される。

#### 【0086】

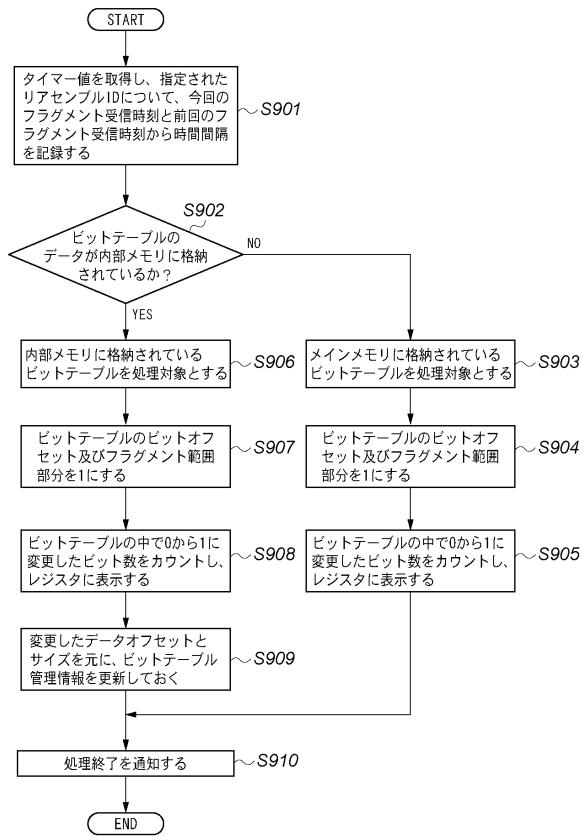

次に、上述したIPリアセンブルの処理シーケンスにおけるS514で実行されるRBMC112のビットテーブルのビット操作処理を、図9を用いて説明する。

#### 【0087】

図9は、ビットテーブルのビット操作処理を示すフローチャートである。まずS901で、通信タイマー113から現在のタイマー値を取得して現在時刻を求める。また、指定されたリアセンブルIDのビットテーブル管理情報中の最後に処理したIPリアセンブルの処理時刻702との差分値を求め、1個前に処理実行したIPフラグメントパケットとの時間間隔を取得する。そして、管理情報の702と703のフィールドを更新する。 10

#### 【0088】

次に、S902で、指定されたリアセンブルIDのビットテーブルが内部メモリ203上に一時格納されているかを調べる。ここでは、RBMC112のリソース管理部202がそのリアセンブルIDのビットテーブル管理情報の内部メモリ格納フラグ705がオンであるかを調べ、オンであるときはS906へ処理を進め、オフであるならばS903へ処理を進める。

#### 【0089】

このS903では、RAM104にあるビットテーブルに対して直接ビット操作を施す処理モードとなる。次に、S904では、RAM104上のそのビットテーブルに対してレジスタ201に指定されたフラグメントオフセットと、フラグメントデータサイズに対応するビット範囲を1にセットする。そして、S905では、RAM104上のビットテーブルの中で0から1に変更されたビットの数をレジスタ201に設定して、S910へ処理を進める。 20

#### 【0090】

一方、S906では、内部メモリ203上のビットテーブルデータに対してビット操作を施すモードとなる。次に、S907では、内部メモリ203上のそのビットテーブルに対してレジスタ201に指定されたフラグメントオフセットと、フラグメントデータサイズに対応するビット範囲を1にセットする。そして、S908では、RAM104上のビットテーブル中で0から1に変更されたビットの数をレジスタ201に設定する。次に、S909で、内部メモリ203上のビットテーブルで変更した部分のデータオフセットとサイズをビットテーブル管理情報の709と710にそれぞれ記録しておく。そして、S910へ処理を進める。 30

#### 【0091】

このS910では、ビット操作処理の終了をローカルプロセッサ108に通知し、この処理を終了する。

#### 【0092】

尚、S902からS903へ処理を進める場合、アクセス遅延の大きいRAM104上のビットテーブルに対してビット操作処理を行う。そのため、S902からS906へ処理を進める、内部メモリ203にあるビットテーブルへのビット操作処理に比較して処理にかかる時間が大きくなってしまう。しかし、上述した図5に示すシーケンスのように、RBMC112のプリロード処理を実行するので、S902からS906へ処理を進めることになり、ビット操作処理を高速に行うことが可能である。 40

#### 【0093】

本実施形態によれば、RFC791に記載のIPリアセンブル方法において、RBMC112がアクセス遅延の小さい内部メモリ203にビットテーブルを一時格納してビット操作処理を行えるため、ビット操作処理の高速化を実現できる。

#### 【0094】

また、受信したフラグメントパケットのIPパケット受信処理の実行と、RBMC112のプリロード処理が並列処理化されるため、RBMC112が内部メモリ203にビットテーブルを格納するための時間的なオーバーヘッドを無視可能である。 50

**【0095】**

更に、プリロード処理において、内部メモリ203に空きがない場合に、フラグメントパケットの時間的な到着間隔の大きいIPリアサンプルのビットマップテーブルをRAM104に書き戻すような制御を行う。それゆえ、フラグメントパケットの到着間隔の短い、即ちIPリアサンプルの処理頻度が高いビットテーブルを優先的に内部メモリ203に格納しておくことができ、RAM104と内部メモリ203間のビットテーブルのデータ転送を減らすことが可能となる。

**【0096】****[第2の実施形態]**

次に、図面を参照しながら本発明に係る第2の実施形態を詳細に説明する。尚、第2の実施形態におけるIPプロトコル装置の構成は、第1の実施形態で説明した図1及び図2と同様である。即ち、図1に示すIPプロトコル処理装置105、図2に示す内部構成は同じであり、リアサンプルビットマップコントローラ(RBMC)112も、第1の実施形態の構成と同じとする。

10

**【0097】**

第1の実施形態では、RBMC112の内部メモリ203に並行して処理を行っている全ビットテーブルの中から、直近に処理されたIPリアサンプルの幾つかについてビットテーブルの全体データを内部メモリ203に一時格納していた。しかし、第2の実施形態では、内部メモリ203に一時格納するデータはRAM104上に確保している全ビットテーブルについて各々の一部データのみを一時格納する。

20

**【0098】**

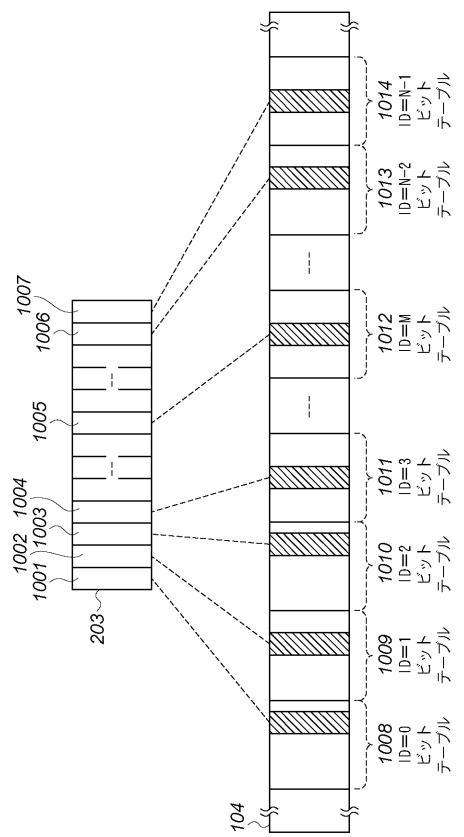

図10は、全ビットテーブルの一部分データのみを内部メモリ203に格納する状態を示す図である。1008～1014はRAM104にN個のIPリアサンプルの全ビットテーブルが確保されていることを表している。また、内部メモリ203の1001～1007には、ビットテーブル1008～1014における一部データのみが格納されていることを表している。

**【0099】**

この例では、リアサンプルIDが0のビットテーブル1008の一部データが1001に格納されており、リアサンプルIDがMのビットテーブル1012の一部データが1005に格納されている。

30

**【0100】**

尚、内部メモリ203への格納方式はダイレクトマップ方式とする。即ち、内部メモリ203では、各ビットテーブルの一部データの格納場所とサイズを固定に定義し、個々の格納場所に格納する対象データは、RAM104上に確保された各ビットテーブルの1Kオクテットの範囲に限定化する。

**【0101】**

このような内部メモリ203の格納方法では、格納するデータサイズを小さくすることで、内部メモリ203に必要なメモリサイズを小さくすることが可能である。また、内部メモリ203に格納するデータサイズを1回のIPリアサンプルに必要となる最大サイズ分を格納するようにする。これにより、RBMC112のプリロード処理でRAM104と内部メモリ203間で転送するデータサイズを、ビットテーブル全体を転送するよりも小さくすることが可能である。

40

**【0102】**

ここで、内部メモリ203に格納するサイズは、IPプロトコル処理装置105が接続するネットワークのMTU値を元にして決定する。例えば、一般的なイーサネット(登録商標)の場合、MTUは1500であるので、1つのIPパケットが運ぶペイロードの最大長は、IPヘッダの最小サイズを引いた1480である。

**【0103】**

よって、1つのフラグメントパケットが運ぶフラグメントデータは最大長が1480となり、必要なビットテーブルデータは185ビットである。つまり、各ビットテーブルに

50

ついて 24 バイト (192 ビット) 分のビットデータを格納すれば、1 回のフラグメントパケットの IP リアセンブルでは十分なデータサイズになる。

#### 【 0104 】

また、第 1 の実施形態では、ビットテーブル全体を内部メモリ 203 に一時格納しているが、1 つのビットテーブルに必要なサイズは 1K バイト (8192 ビット) であるため、約 40 倍の個数のビットテーブルを一時格納することが可能とある。

#### 【 0105 】

しかしながら、第 1 の実施形態では、RBM C 112 のプリロード処理で、既に内部メモリ 203 にビットテーブルが確保されている場合は、RAM 104 からビットテーブルデータを転送する必要が無かった。つまり、同じ IP リアセンブルが、連続的に処理する場合や、単位時間当たりの実行頻度が大きい場合には、ビットテーブルデータの転送回数を減らす効果がある。10

#### 【 0106 】

逆に、第 2 の実施形態の方法は、フラグメントパケットが重複するフラグメントデータを持つことが頻発する状況でない限り、毎回の IP リアセンブルにおいて RAM 104 と内部メモリ 203 へのデータ転送が発生してしまう。

#### 【 0107 】

しかし、ビットテーブルデータの転送サイズが小さく、また、前述したように IP リアセンブルが、ローカルプロセッサ 108 の IP パケット受信処理と、RBM C 112 のプリロード処理が並列的に実行される。20

#### 【 0108 】

このことから、RAM 104 と内部メモリ 203 間のビットテーブルデータ転送にかかる時間的オーバーヘッドは無視でき、IP リアセンブル処理速度の低下にはならない。

#### 【 0109 】

また、同時に並行処理可能な IP リアセンブルの数により、アクセス遅延の小さい内部メモリ 203 にかかるメモリコストを低減することが可能になる。

#### 【 0110 】

##### [ 第 3 の実施形態 ]

次に、図面を参照しながら本発明に係る第 3 の実施形態を詳細に説明する。尚、第 3 の実施形態における IP プロトコル装置の構成は、第 1 の実施形態で説明した図 1 と同様である。即ち、図 1 に示す IP プロトコル処理装置 105 の内部構成は同じである。しかし、第 1 の実施形態で説明したリアセンブルビットマップコントローラ (RBM C) の内部構成が異なる。30

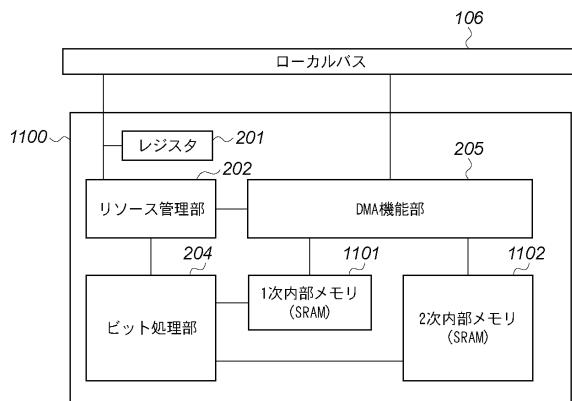

#### 【 0111 】

図 11 は、第 3 の実施形態における RBMC の構成の一例を示す図である。1100 は図 2 に示す RBMC 112 に相当する第 3 の実施形態における RBMC である。RBMC 1100 は、レジスタ 201、リソース管理部 202、1 次内部メモリ 1101、ビット処理部 204、DMA 機能部 205、2 次内部メモリ 1102 で構成される。尚、図 2 に示す構成と同様なものには同一の符号を付している。

#### 【 0112 】

RBMC 1100 の構成において、第 1 の実施形態との違いは、内部メモリ 203 を、1 次内部メモリ 1101 と 2 次内部メモリ 1102 の 2 つとしたことである。40

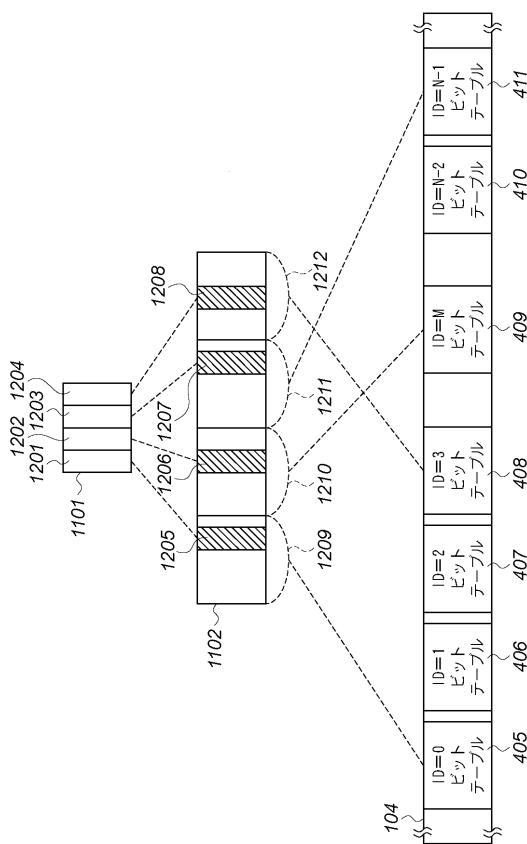

#### 【 0113 】

図 12 は、第 3 の実施形態におけるビットテーブルデータの内部メモリへの格納方法を示す図である。RAM 104 には、並行して処理を行っている全ての IP リアセンブルのビットテーブル 405 ~ 411 を確保している。そして、2 次内部メモリ 1102 には、RAM 104 の任意のアドレスに確保されたビットテーブルの内、4 個のビットテーブルが一時格納されている。図 12 に示す例では、リアセンブル ID が 0、3、M、N - 1 の 4 個のビットテーブル 405、408、409、411 が 2 次内部メモリ 1102 の 1209 ~ 1212 の場所に格納されている。更に、2 次内部メモリ 1102 に一時格納され50

ている各ビットテーブルの一部分データ 1205～1208が1次内部メモリ 1101 の

1201～1204に格納されている。

#### 【0114】

この格納方法は、1次内部メモリ 1101への格納は2次内部メモリ 1102に対する

ダイレクトマップ方式である。

#### 【0115】

また、2次内部メモリ 1102への格納では、RAM 104上の任意のアドレスに配置

されたビットテーブルに対してビットテーブルサイズ単位でのフルアソシエイティブ方式

である。

#### 【0116】

このような RBMC 1100 の構成及びビットテーブルデータの格納方法では、フラグ

メントパケットの到着間隔が短く、単位時間当たりの I P リアセンブル処理の回数が多い

ビットテーブルを優先して2次内部メモリ 1102 に格納しておく。このようにすることで、

RAM 104へのビットテーブルデータの転送を少なくすることが可能となる。

#### 【0117】

更に、1次内部メモリ 1101 と 2 次内部メモリ 1102 の間では、ビットテーブルの

中の一部データのみを転送するため、データ転送のオーバーヘッドを極小化できる。

#### 【0118】

また、1次内部メモリ 1101 と 2 次内部メモリ 1102 は、RBMC 1100 内部で

高速にデータ転送を行うことが可能である。よって、1次内部メモリ 1101 へのビット

操作処理により書き込みが行われると同時に、2次内部メモリ 1102 に書き込むよう

にするライトスルー (write through) 制御を行い、1次メモリ及び2次メモリ間のデータ

同期制御を簡便化する。

#### 【0119】

更に、I P リアセンブルで処理対象となるビットテーブルが2次内部メモリ 1102 に

存在しない場合は、RAM 104 から処理対象の範囲のデータのみ直接、1次内部メモリ

1101 に直接転送することでプリロード処理を高速化する。このプリロード処理では、

上述のライトスルー制御を行う場合、1次内部メモリ 1101 のデータは書き戻す必要が

ない。

#### 【0120】

このように、ビットマップテーブル方式の I P リアセンブルで複数の I P リアセンブル

を並列的に実行する場合にも、ビットテーブルをアクセス遅延の小さいメモリ上に置いて

ビット操作処理の高速化とメモリに必要な容量を抑えることが可能となる。本発明は I P

プロトコル通信を高速に実行する通信端末機器や、TOEにおいて好適である。

#### 【0121】

上述した実施形態によれば、ビットテーブルのビット操作処理をアクセス遅延の小さい

第 2 の記憶手段に保持するデータに対して実行することで、I P リアセンブルの高速化を

図ることができる。

#### 【0122】

また、処理途中である全ての I P リアセンブルのビットテーブルを第 1 の記憶手段に配

置し、ビット操作を行うビットテーブルのデータだけをアクセス遅延の小さい第 2 の記憶

手段に置くことで、第 2 の記憶手段に必要な記憶容量を少なくすることができる。例えば

、第 1 の記憶手段に SDRAM、第 2 の記憶手段に SRAM を用い、一般にメモリコスト

が高価な SRAM を小容量で実装し、安価な SDRAM には少なくとも全ビットテーブル

を保存可能な大容量で実装することでメモリコストを抑えることができる。つまり、I P

リアセンブルの並行処理可能な数を低メモリコストで拡大することができる。

#### 【0123】

更に、ビット操作処理を行うビットテーブルのデータを処理開始の事前に第 2 の記憶

手段に用意し、フラグメントパケットの到着間隔が短い I P リアセンブルのビットテーブル

データを優先的に第 2 の記憶手段に保持する。これにより、第 1 の記憶手段と第 2 の記憶

10

20

30

40

50

手段の間で発生するデータ転送の時間的なオーバーヘッドを平均的に小さくできるため、IPアリアンブルの処理高速化が可能となる。

**【0124】**

尚、本発明は複数の機器（例えば、ホストコンピュータ、インターフェース機器、リーダ、プリンタなど）から構成されるシステムに適用しても、1つの機器からなる装置（例えば、複写機、ファクシミリ装置など）に適用しても良い。

**【0125】**

また、前述した実施形態の機能を実現するソフトウェアのプログラムコードを記録した記録媒体を、システム或いは装置に供給し、そのシステム或いは装置のコンピュータ（CPU若しくはMPU）が記録媒体に格納されたプログラムコードを読み出し実行する。これによっても、本発明の目的が達成されることは言うまでもない。10

**【0126】**

この場合、コンピュータ読み取り可能な記録媒体から読み出されたプログラムコード自体が前述した実施形態の機能を実現することになり、そのプログラムコードを記憶した記録媒体は本発明を構成することになる。

**【0127】**

このプログラムコードを供給するための記録媒体として、例えばフレキシブルディスク、ハードディスク、光ディスク、光磁気ディスク、CD-ROM、CD-R、磁気テープ、不揮発性のメモリカード、ROMなどを用いることができる。

**【0128】**

また、コンピュータが読み出したプログラムコードを実行することにより、前述した実施形態の機能が実現されるだけでなく、次の場合も含まれることは言うまでもない。即ち、プログラムコードの指示に基づき、コンピュータ上で稼働しているOS（オペレーティングシステム）などが実際の処理の一部又は全部を行い、その処理により前述した実施形態の機能が実現される場合である。20

**【0129】**

更に、記録媒体から読み出されたプログラムコードがコンピュータに挿入された機能拡張ボードやコンピュータに接続された機能拡張ユニットに備わるメモリに書込む。その後、そのプログラムコードの指示に基づき、その機能拡張ボードや機能拡張ユニットに備わるCPUなどが実際の処理の一部又は全部を行い、その処理により前述した実施形態の機能が実現される場合も含まれることは言うまでもない。30

**【図面の簡単な説明】**

**【0130】**

【図1】第1の実施形態におけるネットワーク通信装置の構成の一例を表すブロック図である。

【図2】第1の実施形態におけるRBCMの構成の一例を表すブロック図である。

【図3】IPアリアンブルにおけるビットテーブルのビット操作処理を説明するための図である。

【図4】IPアリアンブルのビットテーブルをIPアリアンブル識別子で管理する状態を示す図である。40

【図5】IPアリアンブルにおけるDMAC111、RBCM112、ローカルプロセッサ108の時間的な処理シーケンスを示す図である。

【図6】IPv4（IPバージョン4）パケットのIPヘッダのフォーマットを示す図である。

【図7】ローカルプロセッサ108の処理（図5のS505～S508）を示すフローチャートである。

【図8】ビットテーブルのプリロード処理を示すフローチャートである。

【図9】ビットテーブルのビット操作処理を示すフローチャートである。

【図10】全ビットテーブルの一部分データのみを内部メモリ203に格納する状態を示す図である。50

【図11】第3の実施形態におけるR B M Cの構成の一例を示す図である。

【図12】第3の実施形態におけるビットテーブルデータの内部メモリへの格納方法を示す図である。

【符号の説明】

【0131】

|     |                                |    |

|-----|--------------------------------|----|

| 101 | システムバス                         |    |

| 102 | C P U                          |    |

| 103 | R O M                          |    |

| 104 | R A M                          |    |

| 105 | I P プロトコル処理装置                  | 10 |

| 106 | ローカルバス                         |    |

| 107 | バスブリッジ                         |    |

| 108 | ローカルプロセッサ                      |    |

| 109 | ローカルプロセッサ                      |    |

| 110 | ローカルR A M                      |    |

| 111 | D M A コントローラ ( D M A C )       |    |

| 112 | リアセンブルビットマップコントローラ ( R B M C ) |    |

| 113 | 通信タイマー                         |    |

| 114 | C A M                          |    |

| 115 | 暗号処理部                          | 20 |

| 116 | 通信制御部                          |    |

| 117 | ネットワーク                         |    |

| 201 | レジスタ                           |    |

| 202 | リソース管理部                        |    |

| 203 | 内部メモリ                          |    |

| 204 | ビット処理部                         |    |

| 205 | D M A 機能部                      |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図 9】

【図 10】

【図 11】

【図 12】

---

フロントページの続き

(72)発明者 今尾 英司

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 安藤 一道

(56)参考文献 特開2006-005878 (JP, A)

特開平11-261649 (JP, A)

特開平05-327771 (JP, A)

特開2006-014143 (JP, A)

特開2007-274056 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H04L 12/56