# (19) United States

### (12) Patent Application Publication (10) Pub. No.: US 2007/0018239 A1 Chen et al.

Jan. 25, 2007 (43) **Pub. Date:**

### (54) SEA-OF-FINS STRUCTURE ON A SEMICONDUCTOR SUBSTRATE AND METHOD OF FABRICATION

(75) Inventors: Howard H. Chen, Yorktown Heights, NY (US); Louis C. Hsu, Fishkill, NY (US); Jack A. Mandelman, Flat Rock, NC (US); Chun-Yung Sung, Poughkeepsie, NY (US)

> Correspondence Address: FREDERICK W. GIBB, III GIBB INTELLECTUAL PROPERTY LAW FIRM, LLC 2568-A RIVA ROAD **SUITE 304** ANNAPOLIS, MD 21401 (US)

(73) Assignee: International Business Machines Corporation, Armonk, NY

(21) Appl. No.: 11/185,646 (22) Filed: Jul. 20, 2005

#### **Publication Classification**

(51) Int. Cl. H01L 29/76 (2006.01) (52) U.S. Cl. ......257/329

#### **ABSTRACT** (57)

A semiconductor device and a method of fabricating a semiconductor device, wherein the method comprises forming, on a substrate, a plurality of planarized fin bodies to be used for customized fin field effect transistor (FinFET) device formation; forming a nitride spacer around each of the plurality of fin bodies; forming an isolation region in between each of the fin bodies; and coating the plurality of fin bodies, the nitride spacers, and the isolation regions with a protective film. The fabricated semiconductor device is adapted to be used in customized applications as a customized semiconductor device.

FIG. 7B

**FIG. 10A**

FIG. 11A

FIG. 12A

FIG. 13A

FIG. 15A

FIG. 16B

**FIG. 16A**

**FIG. 17A**

FIG. 19A

FIG. 20

#### SEA-OF-FINS STRUCTURE ON A SEMICONDUCTOR SUBSTRATE AND METHOD OF FABRICATION

#### BACKGROUND OF THE INVENTION

[0001] 1. Field of the Invention

[0002] The embodiments of the invention generally relate to integrated circuit technology, and, more particularly, to methods to form a customized field effect transistor (FET).

[0003] 2. Description of the Related Art

[0004] Motivation to form FinFET devices on very thin silicon rail as the body of a metal oxide semiconductor field effect transistor (MOSFET) is driven by the need for shorter gate lengths, lower leakage currents, and a higher level of device integration. The lack of a reliable high-k gate stack to limit the leakage current makes the three-dimensional structure of thin body, known as a "fin" in U.S. Pat. No. 6,252,284, the complete disclosure of which is herein incorporated by reference, very attractive in 90-nanometer process node and beyond. The fin body is normally gated on three sides to gain better control of the channel potential, thus resulting in better short channel effect and scalability. Methods for forming such FinFET devices face significant challenges such as sub-lithographic dimension control of the fin width in a manufacturing environment, and surface planarity to facilitate back-end-of-line metallization. Although the fin dimensions in the conventional devices may be defined by any conventional lithographic methods. it is desirable to further reduce the fin dimension to less than 30 nm, which is beyond the capability of existing lithographic technology.

#### SUMMARY OF THE INVENTION

[0005] In view of the foregoing, an embodiment of the invention provides a method of fabricating a semiconductor device, wherein the method comprises forming, on a substrate, a plurality of planarized fin bodies to be used for customized fin field effect transistor (FinFET) device formation; forming a nitride spacer around each of the plurality of fin bodies; forming an isolation region in between each of the fin bodies; and coating the plurality of fin bodies, the nitride spacers, and the isolation regions with a protective film. The method may further comprise removing the protective film; forming FinFET devices from a first type of the fin bodies; forming fin capacitors from a second type of fin bodies; and forming metal interconnects on the FinFET devices and the fin capacitors, wherein formation of each of the FinFET devices preferably comprises forming a gate conductor over the first type of fin bodies; forming a channel region below the gate conductor; and configuring source/ drain regions adjacent to the channel region.

[0006] The method may further comprise exposing the first type of fin bodies by removing the gate conductor from the first type of fin bodies; and forming a region of semi-conductor resistance in the exposed first type of fin bodies. Additionally, the method may further comprise doping a selective portion of the gate conductor to produce a region of semiconductor resistance in the gate conductor. Furthermore, the method may further comprise connecting a plurality of the fin capacitors in parallel using a first level of the metal interconnects. Moreover, the method may further

comprise forming a plurality of diodes in the fin bodies; and connecting the diodes in series. Also, the method may further comprise selectively removing the nitride spacer in selected areas of the semiconductor device adapted to be formed into source/drain regions of the FinFET; and forming an epitaxial material in the selected areas. Preferably, the fabricated semiconductor device is adapted to be used in customized applications as a customized semiconductor device.

[0007] Another aspect of the invention provides a method of forming a semiconductor device to be used in very large scale integrated circuit (VLSI) applications, wherein the method comprises forming, on a substrate, an array of fin bodies comprising silicon and adapted to be used in customized fin field effect transistor (FinFET) construction; forming nitride spacers around each fin body in the array of fin bodies; separating each the fin body from one another; and applying a protective film over the array of separated fin bodies. The method may further comprise removing the protective film; forming FinFET devices from a first type of fin body; forming fin capacitors from a second type of fin body; and forming metal interconnects on the FinFET devices and the fin capacitors, wherein formation of each of the FinFET devices preferably comprises forming a gate conductor over the first type of fin body; forming a channel region below the gate conductor; and configuring source/ drain regions adjacent to the channel region.

[0008] The method may further comprise exposing the first type of fin body by removing the gate conductor from the first type of fin body; and forming a region of semiconductor resistance in the exposed first type of fin body. Moreover, the method may further comprise doping a selective portion of the gate conductor to produce a region of semiconductor resistance in the gate conductor. Additionally, the method may further comprise connecting a plurality of the fin capacitors in parallel using a first level of the metal interconnects. Also, the method may further comprise forming a plurality of diodes in the fin body; and connecting the diodes in series. Furthermore, the method may further comprise selectively removing the nitride spacers in selected areas of the semiconductor device adapted to be formed into source/drain regions of the FinFET; and forming an epitaxial material in the selected areas. Preferably, the formed semiconductor device is adapted to be used in customized applications as a customized semiconductor device.

[0009] Another embodiment of the invention provides a semiconductor device adapted to be used in customized applications as a customized semiconductor device comprising a substrate; a plurality of planarized fin bodies on the substrate, wherein the fin bodies are adapted to be used for customized fin field effect transistor (FinFET) device formation; a nitride spacer around each of the plurality of fin bodies; and a protective film on the plurality of fin bodies, the nitride spacers, and the isolation regions, wherein the plurality of planarized fin bodies are preferably adapted to be used for any of customized fin resistor, customized fin capacitor, and customized diode device formation.

[0010] These and other aspects of embodiments of the invention will be better appreciated and understood when considered in conjunction with the following description and the accompanying drawings. It should be understood, how-

ever, that the following description, while indicating preferred embodiments of the invention and numerous specific details thereof, is given by way of illustration and not of limitation. Many changes and modifications may be made within the scope of the embodiments of the invention without departing from the spirit thereof, and the embodiments of the invention include all such modifications.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0011] The embodiments of the invention will be better understood from the following detailed description with reference to the drawings, in which:

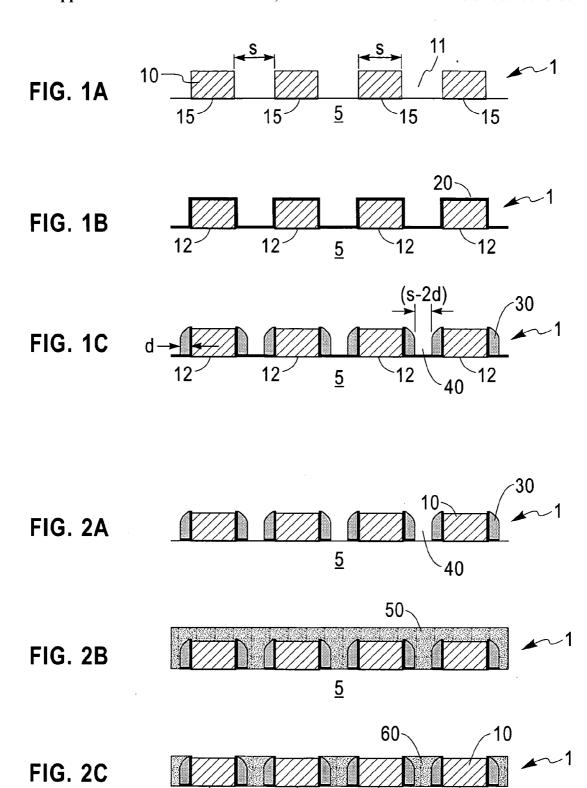

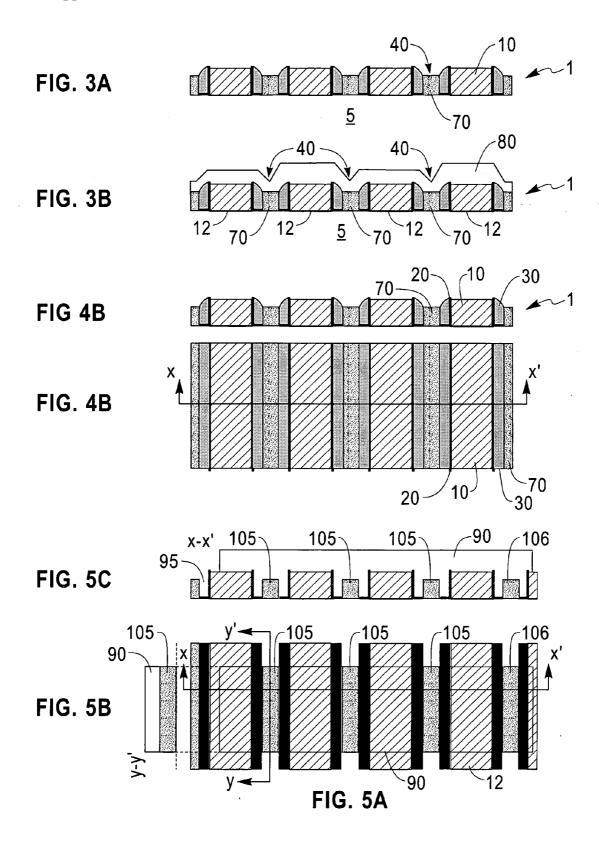

[0012] FIGS. 1(A) through 3(B) illustrate schematic diagrams of successive steps of forming a sea-of-fins (SOF) substrate according to an embodiment of the invention;

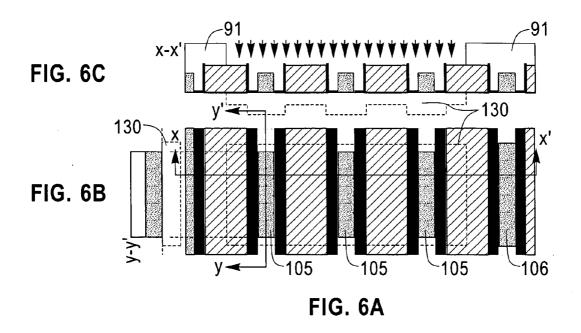

[0013] FIGS. 4(A) through 17(B) illustrate schematic diagrams of successive steps of forming a FinFET device using the SOF substrate of FIG. 3(B) according to an embodiment of the invention;

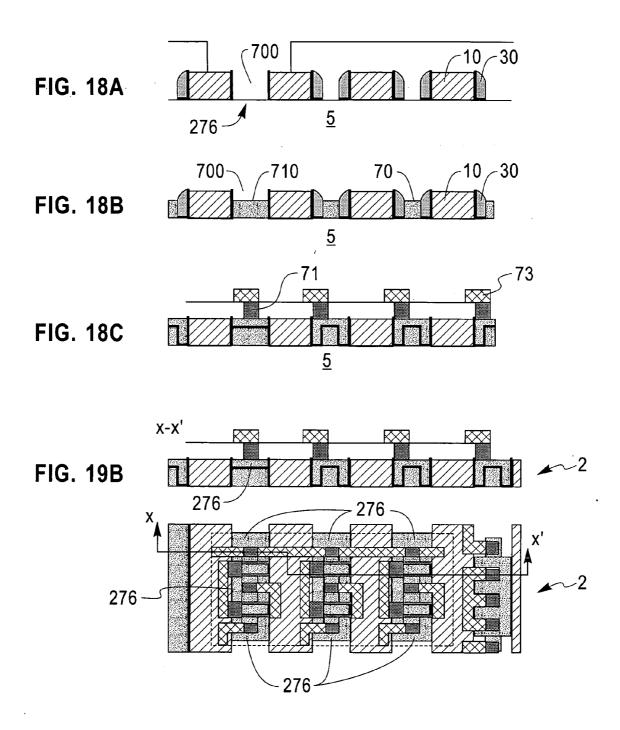

[0014] FIGS. 18(A) through 19(B) illustrate schematic diagrams of successive steps of forming a FinFET device according to an alternate embodiment of the invention; and

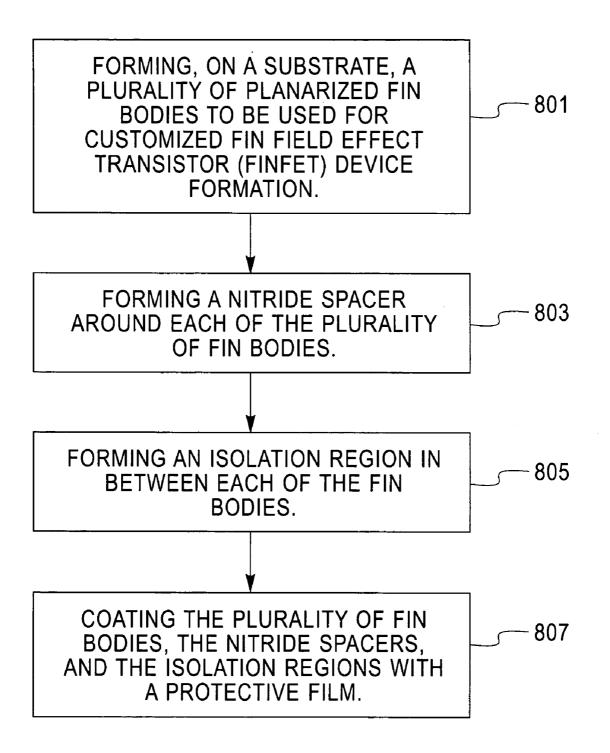

[0015] FIG. 20 is a flow diagram illustrating a preferred method according to an embodiment of the invention.

# DETAILED DESCRIPTION OF PREFERRED EMBODIMENTS OF THE INVENTION

[0016] The embodiments of the invention and the various features and advantageous details thereof are explained more fully with reference to the non-limiting embodiments that are illustrated in the accompanying drawings and detailed in the following description. It should be noted that the features illustrated in the drawings are not necessarily drawn to scale. Descriptions of well-known components and processing techniques are omitted so as to not unnecessarily obscure the embodiments of the invention. The examples used herein are intended merely to facilitate an understanding of ways in which the embodiments of the invention may be practiced and to further enable those of skill in the art to practice the embodiments of the invention. Accordingly, the examples should not be construed as limiting the scope of the embodiments of the invention.

[0017] As mentioned, it is desirable to further reduce the fin dimension to less than 30 nm, which is beyond the capability of existing lithographic technology. The embodiments of the invention achieve this by providing a technique of forming a semiconductor substrate with a prefabricated sea-of-fins (SOF) structure and a technique to customize each SOF substrate and form a variety of microelectronic devices and integrated circuit chips using such a SOF substrate. Referring now to the drawings, and more particularly to FIGS. 1(A) through 20, where similar reference characters denote corresponding features consistently throughout the figures, there are shown preferred embodiments of the invention.

[0018] The embodiments of the invention utilize sublithographic patterning techniques including sidewall spacer image transfer or phase shift technology. According to the embodiments of the invention, one method to form fin patterns in the 30 nm range is to use the sidewall spacers. Since sidewall spacers are formed by depositing and etching a layer of dielectric material of uniform thickness, the dimension of the spacers can be controlled in the range of interest. Consequently, the dimensions of fins and isolation space can be precisely controlled as well. Formation of fin devices using sidewall spacer image transfer techniques include techniques taught in U.S. Pat. No. 6,794,718, the complete disclosure of which, in its entirety, is herein incorporated by reference, where fins with at least two crystalline orientations are formed.

[0019] The following diagrams illustrate the processing steps to fabricate the sea-of-fins substrate. FIGS. 1(A) through 3(B) illustrate schematic diagrams of successive steps of forming a SOF substrate 1 according to an embodiment of the invention. As shown in FIG. 1(A), a layer of dielectric (oxide) material 10 on a silicon substrate 5 and an etching process is performed to form a line-space pattern 's' of the dielectric material 10. It is preferable to include a thin nitride etch stop barrier 15 under the mandrel oxide 10 to facilitate the safe removal of certain regions 11 of mandrel oxide 10 later in the process in order to gain access to the substrate 5. The line spacing 's' can be set to 120 nm, which is approximately equal to three times the dimension of the fin body. The thickness of the oxide material 10 is preferably in the range of 50 to 100 nm. Next, a thin layer of low-k dielectric material 20 is deposited on the surface of the etched oxide pattern 12 to lower the parasitic capacitance as indicated in FIG. 1(B). The thickness of low-k liner 20 is approximately 5 to 10 nm. As shown in FIG. 1(C), dielectric (nitride) spacers 30 are formed on the sidewalls of the isolation patterns 12 by first depositing the material with a thickness of 'd' (approximately 40 nm) followed by directional reactive ion etching. The resulting gap 40 between the two spacers 30 is equal to (s-2d), which is preferably in the range of 40 nm for the fin body structure.

[0020] Next, the low-k film 20 is etched in the gap areas 40 to expose the silicon substrate 5 underneath as depicted in FIG. 2(A). Then, as indicated in FIG. 2(B), epitaxy 50 is selectively grown from the silicon 5 at the bottom of the gaps 40, until the epitaxy 50 fills the gaps 40 and covers the entire top surface of the structure 1. The epitaxial material 50 inside the gap 40 comprises single crystalline material. A chemical mechanical polishing (CMP) process is performed to remove the silicon on the top of the structure 1 until the oxide 10 of the isolation pattern 12 is exposed. A slight over-etch may be performed to ensure that the silicon layer 50 is completely removed from the top surface of oxide 10, while single crystalline silicon 60 remains inside the gap areas as provided in FIG. 2(C).

[0021] Then, the fin-body silicon 60 is recessed to a predetermined depth by a timed etching process such that silicon pillars (what shall eventually constitute the fin bodies) 70 formed inside the gaps 40 have identical heights after etching as illustrated in FIG. 3(A). Thereafter, the wafer 1 is cleaned and coated with a protective film 80 as depicted in FIG. 3(B). Accordingly, the preparation of a SOF wafer 1 comprising a plurality of fins 70 and isolations 12 is complete and ready for device fabrication.

[0022] FIGS. 4(A) through 17(B) illustrate schematic diagrams of successive steps of forming a FinFET device using the SOF substrate 1 of FIG. 3(B). As indicated in the cross-sectional view of FIG. 4(A) and the top view of FIG.

4(B), the protective film 80 (of FIG. 3(B)) is removed. Next, the nitride spacers 30 on the sidewalls of the isolation regions 95 are removed as shown in FIGS. 5(A) through 5(C). A mask 90 is used to define the fin body region 105, 106. The X-X' cross-sectional view is shown in FIG. 5(C) and the Y-Y' cross-sectional view is shown in FIG. 5(B). The length of each stripe of fin body 105, 106 is determined after silicon etching by Cl<sub>2</sub> plasma. The oxide isolation region 12 between adjacent body units 105 is used to isolate the devices and support the metal interconnects, which are formed in subsequent processing steps. The body regions 105 in FIGS. 5(A) through 5(C) are used to form FinFETs and the body region 106 in FIGS. 5(A) and 5(C) is used to form fin capacitors. A second mask 91 is then used to define the well regions of the device as indicated in FIGS. 6(A) through 6(C). After an ion implant process occurs (as depicted by the downward arrows in FIG. 6(C)), the well junction 130 is formed.

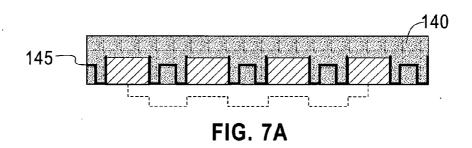

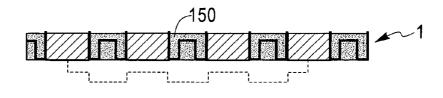

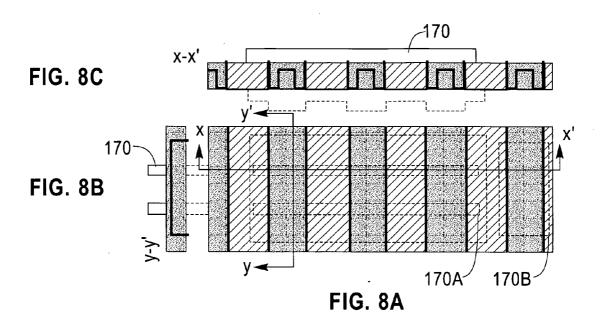

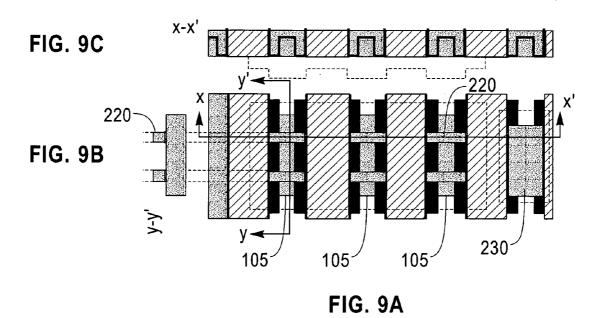

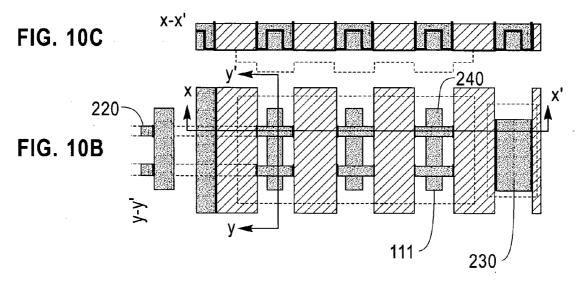

[0023] In the next step of the process, a gate dielectric 145 is formed via thermal oxidation of a high-k film deposition as shown in FIG. 7(A). Here, a polysilicon layer 140 is deposited via chemical vapor deposition (CVD). Next, excessive polysilicon material 140 on the surface of the sea-of-fins structure 1 is removed with a second CMP process. The reserved spacer areas 150 are now filled with polysilicon as shown in FIG. 7(B). Then, as illustrated in FIGS. 8(A) through 8(C), the gate is defined with a third mask 170, where region 170A is used to form the fin gates of the transistors and region 170B is used for the top electrode of a capacitor. As shown in FIGS. 9(A) through 9(C), the next steps involve performing an etch process that removes CVD polysilicon with Cl<sub>2</sub> plasma to define the gate electrodes 220 and the top capacitor electrode 230.

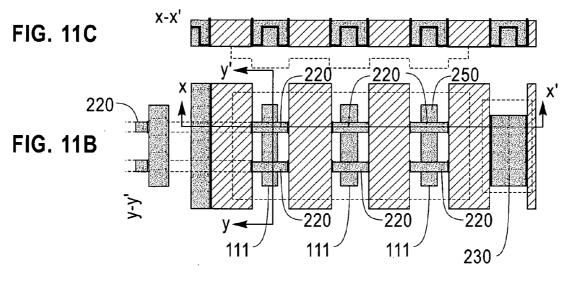

[0024] After gate patterning, the process involves selectively removing the high-k dielectric 145 from the fin sidewalls in non-gate areas 240 as indicated in FIGS. 10(A) through 10(C). Then, the exposed sidewalls of the fins 105 are doped with an appropriate n+ or p+ dopant to form the source and drain junctions on the exposed body regions 250 as indicated in FIGS. 11(A) through 11(C). The channels (not shown) of the FinFETs 111 are protected from being contaminated by the source/drain doping by the overlying gate conductor 220, and the junction edge is aligned to the gate edge. It is preferable to use a plasma immersion implant tool for gas phase doping or a high angle single wafer implanter for angled ion implantation. Halo doping, if desired, could be introduced by angled ion implantation, and conformal doping schemes such as solid phase doping are also acceptable.

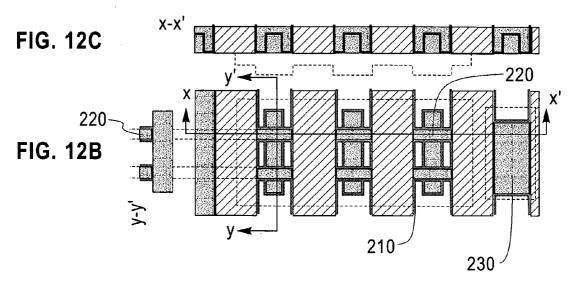

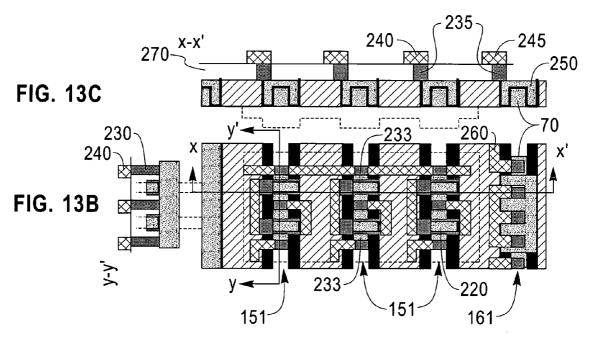

[0025] Next, a thin layer of dielectric 210 is deposited and a reactive ion etching process is used to form the sidewall spacers 210 for the gate, source, drain, and oxide area of the device as illustrated in FIGS. 12(A) through 12(C). Next, as shown in FIGS. 13(A) through 13(C), metal interconnects 240, 245 are formed via back-end-of-line processes that include insulating material deposition, planarization, via formation, and metal deposition. For example, CVD tungsten studs 230, 235 in FIGS. 13(A) through 13(C) are used to connect aluminum or copper wires 260 with the gates 220, as well as the bodies in the source/drain areas 233. With the dimension of the metal interconnects 240, 245 in the range of 40 nm, fin-transistor devices 151 are shown in the left

portions of FIGS. 13(A) and 13(C) and fin capacitor devices 161 are shown on the right portions of FIGS. 13(A) and 13(C).

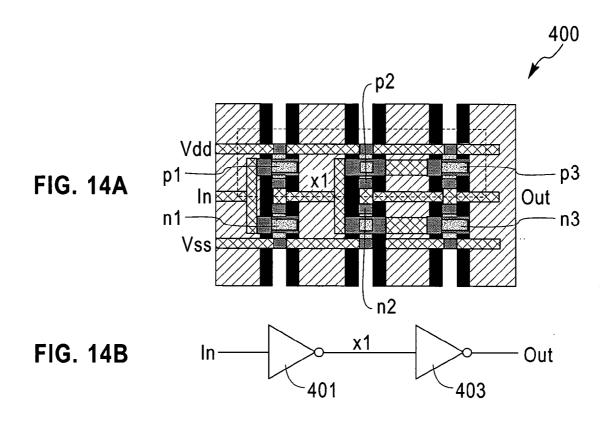

[0026] FIGS. 14(A) and 14(B) show the implementation of a two-stage inverter chain 400, with a first inverter 401, comprising the first pMOS device p1 and the first nMOS device n1, and a second inverter 403, comprising the second pMOS device p2 and the second NMOS device n2 according to the embodiments of the invention. The width of p2 and n2 can be doubled by connecting p2 with p3 in parallel, and connecting n2 with n3 in parallel. Multiple gates with different sizes can therefore be easily implemented and customized on the sea-of-fins substrate 1 provided by the embodiments of the invention.

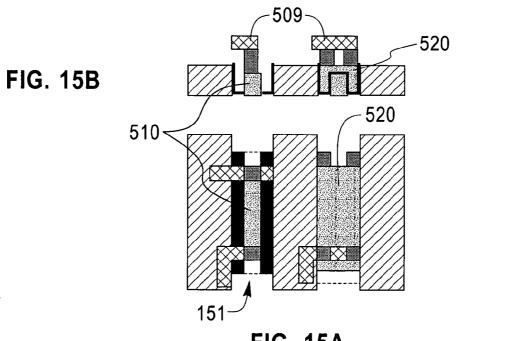

[0027] FIGS. 15(A) and 15(B) illustrate two embodiments of fin resistors according to the embodiments of the invention. A first resistor 510 is formed by the body of the FinFET 151. During gate conductor patterning, the gate conductor is removed from the region where a resistor is desired. Then, appropriate gas phase doping or ion implantation is introduced into the exposed fin to obtain the desired resistance. The contacts 509, which are similar to the source and drain contacts, are made on the opposite ends of the fin structure. A second resistor 520 is formed from the gate conductor material such as polysilicon. To achieve the desired resistance, the area of gate conductor that will contain the resistor 520 should be blocked from gate doping. A separate mask (not shown) and doping process is then used to introduce the appropriate amount of dopant into the gate conductor to achieve the desired resistance. This separate doping step may be done before or after the standard gating doping

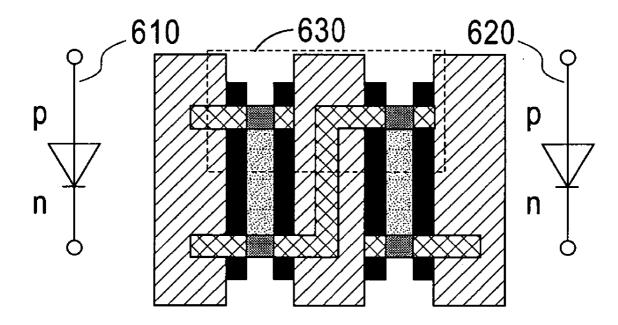

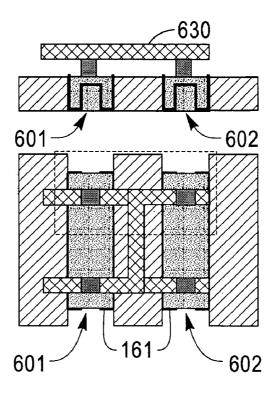

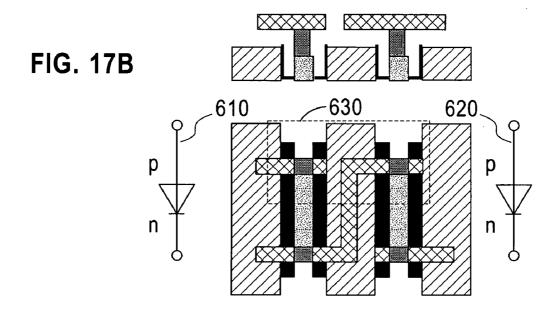

[0028] FIGS. 16(A) and 16(B) illustrate the structure of two fin capacitors 601, 602 connected in parallel by a first level metallization 603. The fin capacitors 601, 602 generally comprise a large area of the fin body 161 or multiple fin bodies to provide sufficient capacitance. For enhanced capacitance, the fin capacitors 601, 602 may include adjacent source or drain diffusions to provide carriers for the formation of inversion layers (not shown). FIGS. 17(A) and 17(B) depict the structure of electrostatic discharge (ESD) protection devices 610, 620. Two diodes 610 and 620 are formed in the fin bodies and connected in series. The diodes 610, 620 may provide a lateral or a combined lateral/vertical doping profile, which could be introduced after the removal of gate conductor from the region where the diodes 610, 620 are to be formed. To protect a device (not shown) from excessive voltage with positive or negative polarity, the device (not shown) should be connected to the junction of the two diodes 610, 620.

[0029] FIGS. 18(A) through 18(C) illustrate a process to reduce the source and drain contact resistance in a FinFET device. According to FIG. 18(A), the nitride spacers 30 are selectively removed in the source/drain areas 276 during SOF substrate preparation. Next, epitaxy 710 is grown to fill the gaps 700 (FIG. 18(B)). Due to the removal of the sidewall spacers 30, the widened source/drain areas 276 are approximately three times as wide as the fin body area (which will constitute the gate) 70. Next, the source/drain regions 276 are interconnected by vias 71 and metal interconnects 73 during a back end-of-the line (BEOL) process thereby providing larger contact area and lower contact

resistance as illustrated in FIG. **18**(C). FIGS. **19**(A) and **19**(B) show the top and cross-sectional views, respectively, of a modified sea-of-fins structure **2** with widened source/drain regions **276**.

[0030] The sea-of-fins (SOF) substrate 1, 2 provided by the embodiments of the invention can be prefabricated and mass-produced by the wafer suppliers. The dimension of fin bodies 105, 106 can also be custom-designed and produced by the chip manufacturers. Since many of the SOF processing steps provided by the embodiments of the invention are self-aligned and the finished FinFET devices have a coplanar structure for both the gate regions 220 and the adjacent isolation regions 12, it is possible to achieve further device scaling beyond the 30 nm range.

[0031] FIG. 20, with reference to FIGS. 1(A) through 19(B), illustrates a flow diagram of a method of fabricating a semiconductor device, wherein the method comprises forming (801), on a substrate 5, a plurality of planarized fin bodies 70 to be used for customized fin field effect transistor (FinFET) device formation; forming (803) a nitride spacer 30 around each of the plurality of fin bodies 70; forming (805) an isolation region 12 in between each of the fin bodies 70; and coating (807) the plurality of fin bodies 70, the nitride spacers 30, and the isolation regions 12 with a protective film 80.

[0032] The several embodiments of the invention can be formed into integrated circuit chips. The resulting integrated circuit chips can be distributed by the fabricator in raw wafer form (that is, as a single wafer that has multiple unpackaged chips), as a bare die, or in a packaged form. In the latter case the chip is mounted in a single chip package (such as a plastic carrier, with leads that are affixed to a motherboard or other higher level carrier) or in a multichip package (such as a ceramic carrier that has either or both surface interconnections or buried interconnections). In any case the chip is then integrated with other chips, discrete circuit elements, and/or other signal processing devices as part of either (a) an intermediate product, such as a motherboard, or (b) an end product. The end product can be any product that includes integrated circuit chips, ranging from toys and other low-end applications to advanced computer products having a display, a keyboard or other input device, and a central pro-

[0033] Generally, the embodiments of the invention provide a method of fabricating SOF substrates consistent with high-volume, high-yield, and low-cost semiconductor manufacturing. Moreover, the embodiments of the invention provide a technique of how the SOF substrates are used to design and fabricate high-performance integrated circuits.

[0034] Wafer substrates with pre-fabricated fin structures allow chip manufacturers achieve better control of the fin dimensions in the 30 nm range. However, an array of fins 105, 106 and isolation spaces 12 prepared on a semiconductor substrate 5 prior to shipping to a semiconductor foundry has never heretofore been demonstrated prior to the techniques provided by the embodiments of the invention. Due to the economies of scale, substrate providers can supply such pre-fabricated SOF substrates 1, 2 at a lower cost. Such prefabricated SOF substrates 1, 2 would also be highly marketable because chip manufacturers would no longer have to contend with the technical and economic difficulties of producing well-controlled sub-lithographic-width fins within their own processes.

[0035] The foregoing description of the specific embodiments will so fully reveal the general nature of the embodiments of the invention that others can, by applying current knowledge, readily modify and/or adapt for various applications such specific embodiments without departing from the generic concept, and, therefore, such adaptations and modifications should and are intended to be comprehended within the meaning and range of equivalents of the disclosed embodiments. It is to be understood that the phraseology or terminology employed herein is for the purpose of description and not of limitation. Therefore, while the embodiments of the invention has been described in terms of preferred embodiments, those skilled in the art will recognize that the embodiments of the invention can be practiced with modification within the spirit and scope of the appended claims.

What is claimed is:

1. A method of fabricating a semiconductor device, said method comprising:

forming, on a substrate, a plurality of planarized fin bodies to be used for customized fin field effect transistor (FinFET) device formation;

forming a nitride spacer around each of said plurality of fin bodies:

forming an isolation region in between each of said fin bodies; and

coating said plurality of fin bodies, said nitride spacers, and the isolation regions with a protective film.

**2**. The method of claim 1, further comprising:

removing said protective film;

forming FinFET devices from a first type of said fin bodies;

forming fin capacitors from a second type of fin bodies; and

forming metal interconnects on said FinFET devices and said fin capacitors.

**3**. The method of claim 2, wherein formation of each of said FinFET devices comprises:

forming a gate conductor over said first type of fin bodies;

forming a channel region below said gate conductor; and

configuring source/drain regions adjacent to said channel region.

4. The method of claim 3, further comprising:

exposing said first type of fin bodies by removing said gate conductor from said first type of fin bodies; and

forming a region of semiconductor resistance in the exposed first type of fin bodies.

- 5. The method of claim 3, further comprising doping a selective portion of said gate conductor to produce a region of semiconductor resistance in said gate conductor.

- **6**. The method of claim 2, further comprising connecting a plurality of said fin capacitors in parallel using a first level of said metal interconnects.

- 7. The method of claim 2, further comprising:

forming a plurality of diodes in said fin bodies; and connecting said diodes in series.

8. The method of claim 1, further comprising:

selectively removing said nitride spacer in selected areas of said semiconductor device adapted to be formed into source/drain regions of said FinFET; and

forming an epitaxial material in said selected areas.

- **9**. The method of claim 1, wherein the fabricated semiconductor device is adapted to be used in customized applications as a customized semiconductor device.

- 10. A method of forming a semiconductor device to be used in very large scale integrated circuit (VLSI) applications, said method comprising:

forming, on a substrate, an array of fin bodies comprising silicon and adapted to be used in customized fin field effect transistor (FinFET) construction;

forming nitride spacers around each fin body in said array of fin bodies;

separating each said fin body from one another; and applying a protective film over the array of separated fin bodies.

**11**. The method of claim 10, further comprising: removing said protective film;

forming FinFET devices from a first type of fin body;

forming fin capacitors from a second type of fin body; and

forming metal interconnects on said FinFET devices and said fin capacitors.

12. The method of claim 11, wherein formation of each of said FinFET devices comprises:

forming a gate conductor over said first type of fin body; forming a channel region below said gate conductor; and configuring source/drain regions adjacent to said channel region.

13. The method of claim 12, further comprising:

exposing said first type of fin body by removing said gate conductor from said first type of fin body; and

- forming a region of semiconductor resistance in the exposed first type of fin body.

- **14**. The method of claim 12, further comprising doping a selective portion of said gate conductor to produce a region of semiconductor resistance in said gate conductor.

- **15**. The method of claim 11, further comprising connecting a plurality of said fin capacitors in parallel using a first level of said metal interconnects.

- 16. The method of claim 11, further comprising:

forming a plurality of diodes in said fin body; and connecting said diodes in series.

17. The method of claim 10, further comprising:

selectively removing said nitride spacers in selected areas of said semiconductor device adapted to be formed into source/drain regions of said FinFET; and

forming an epitaxial material in said selected areas.

- 18. The method of claim 10, wherein the formed semiconductor device is adapted to be used in customized applications as a customized semiconductor device.

- 19. A semiconductor device adapted to be used in customized applications as a customized semiconductor device comprising:

- a substrate:

- a plurality of planarized fin bodies on said substrate, wherein the fin bodies are adapted to be used for customized fin field effect transistor (FinFET) device formation;

a nitride spacer around each of said plurality of fin bodies; an isolation region in between each of said fin bodies; and

- a protective film on said plurality of fin bodies, said nitride spacers, and the isolation regions.

- 20. The semiconductor device of claim 19, wherein said plurality of planarized fin bodies are adapted to be used for any of customized fin resistor, customized fin capacitor, and customized diode device formation.

\* \* \* \* \*